Selective etching of carbon-doped low-k dielectrics

A low dielectric constant material, selective technology, used in circuits, electrical components, semiconductor devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example

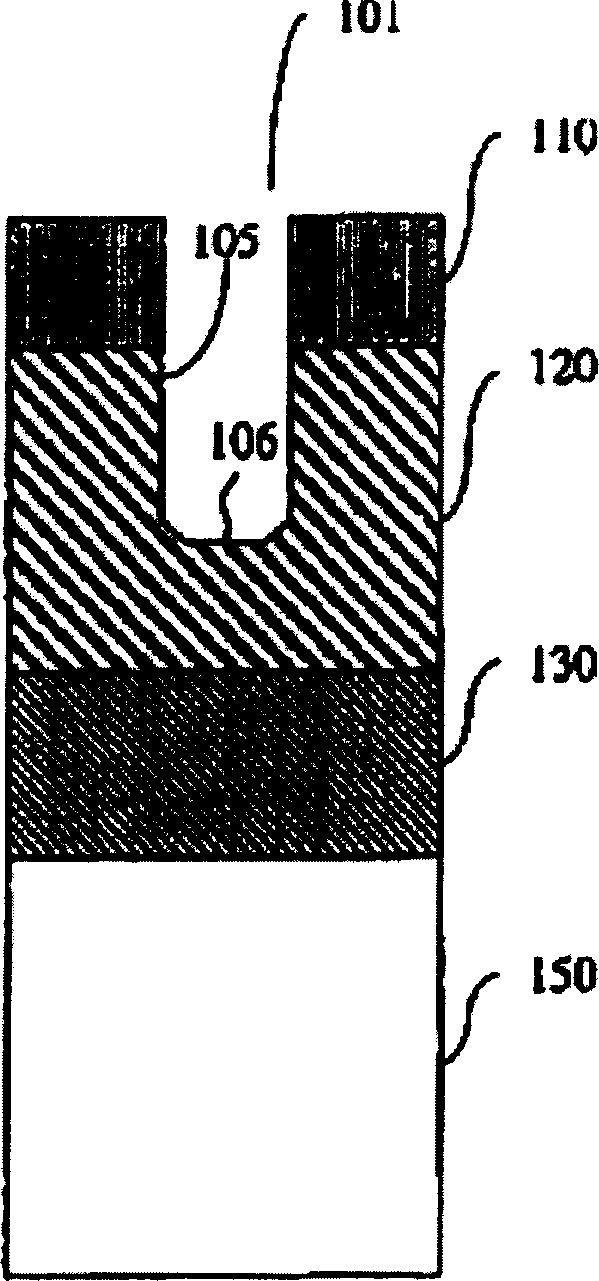

[0043] The following example describes the use of the method of the present invention to etch the low-k material layer 120 on the substrate 150 . An example of the substrate 150 is, for example, a silicon wafer with a diameter of 200 mm (8 inches) or 300 mm (12 inches). Such as figure 1 As shown, the wafer 150 is covered with a barrier / liner layer 130 with a thickness of hundreds of angstroms, a low dielectric constant material layer 120 with a thickness of 0.4-1.5 microns, and a mask layer 110 with a thickness of about 1930 angstroms. The mask layer 110 is patterned for etching a defined pattern of features 101 .

[0044] In the following examples, the mask layer is a photoresist such as "RISTON" manufactured by duPont de Nemours Chemical Company. The low dielectric constant material layer includes carbon-doped dielectric materials, such as organosilicate glass (OSG) doped with CH3, organic polymers (such as benzene cyclobutene, parylene, polytetrafluoroethylene, etc.) , p...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More