Self-alignment of metal and via using selective deposition

a technology of selective deposition and self-alignment, which is applied in the direction of basic electric elements, semiconductor/solid-state device manufacturing, electric apparatus, etc., can solve the problems of limiting the pitch or spacing between exposed features, the critical dimension (cd) or resolution of patterned features is becoming more difficult to produce, and the challenge of photolithographic misalignment,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

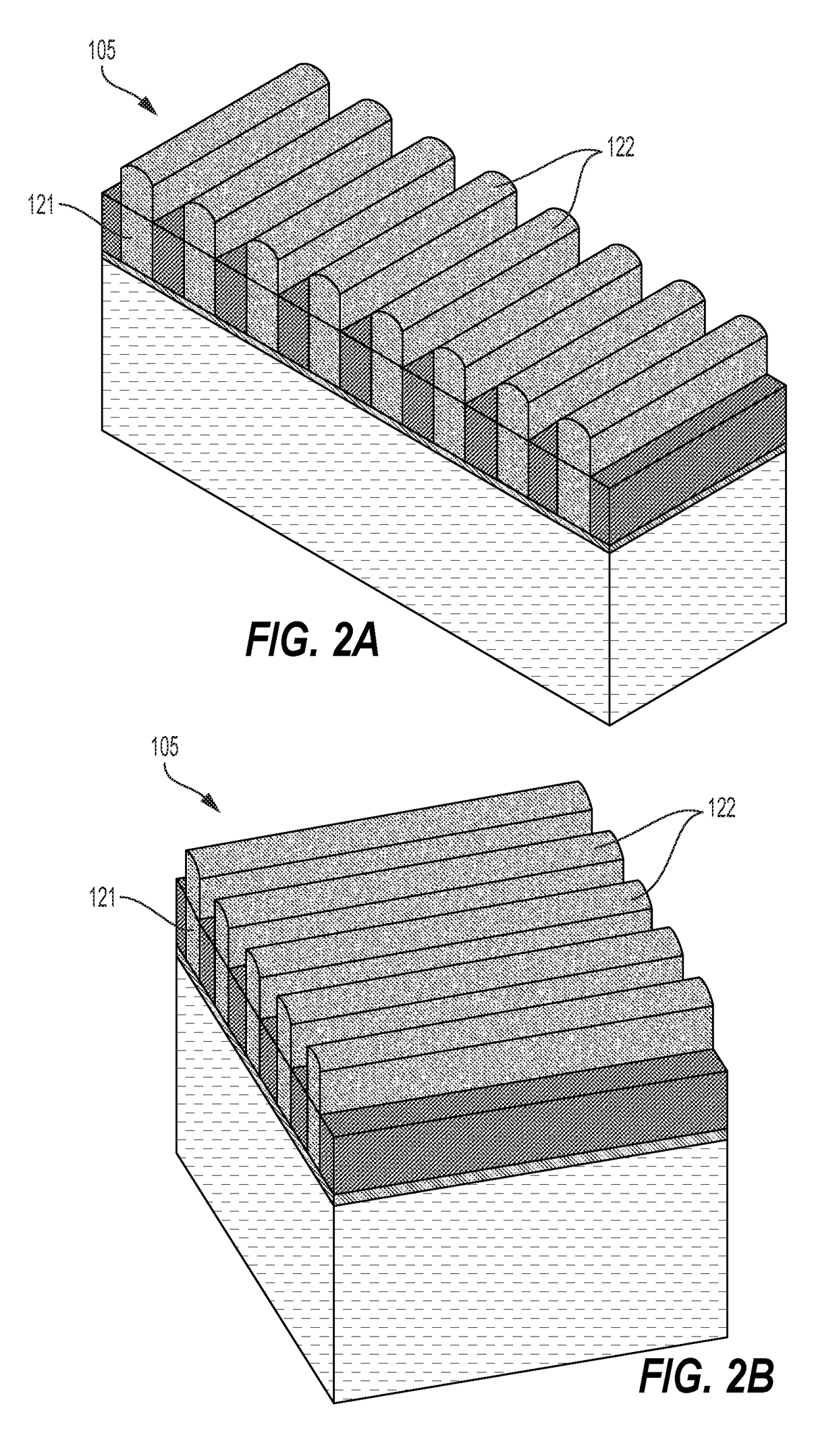

[0026]Techniques herein include methods of patterning substrates such as for back end of line (BEOL) metallization processes. Techniques herein enable fully self-aligned vias and lines. Processes herein include using selective deposition, protective films and combination etch masks for accurately patterning a substrate. Such combinations mitigate overlay errors by using underlying structures to self-align patterns, and protect sensitive dielectric materials from being degraded.

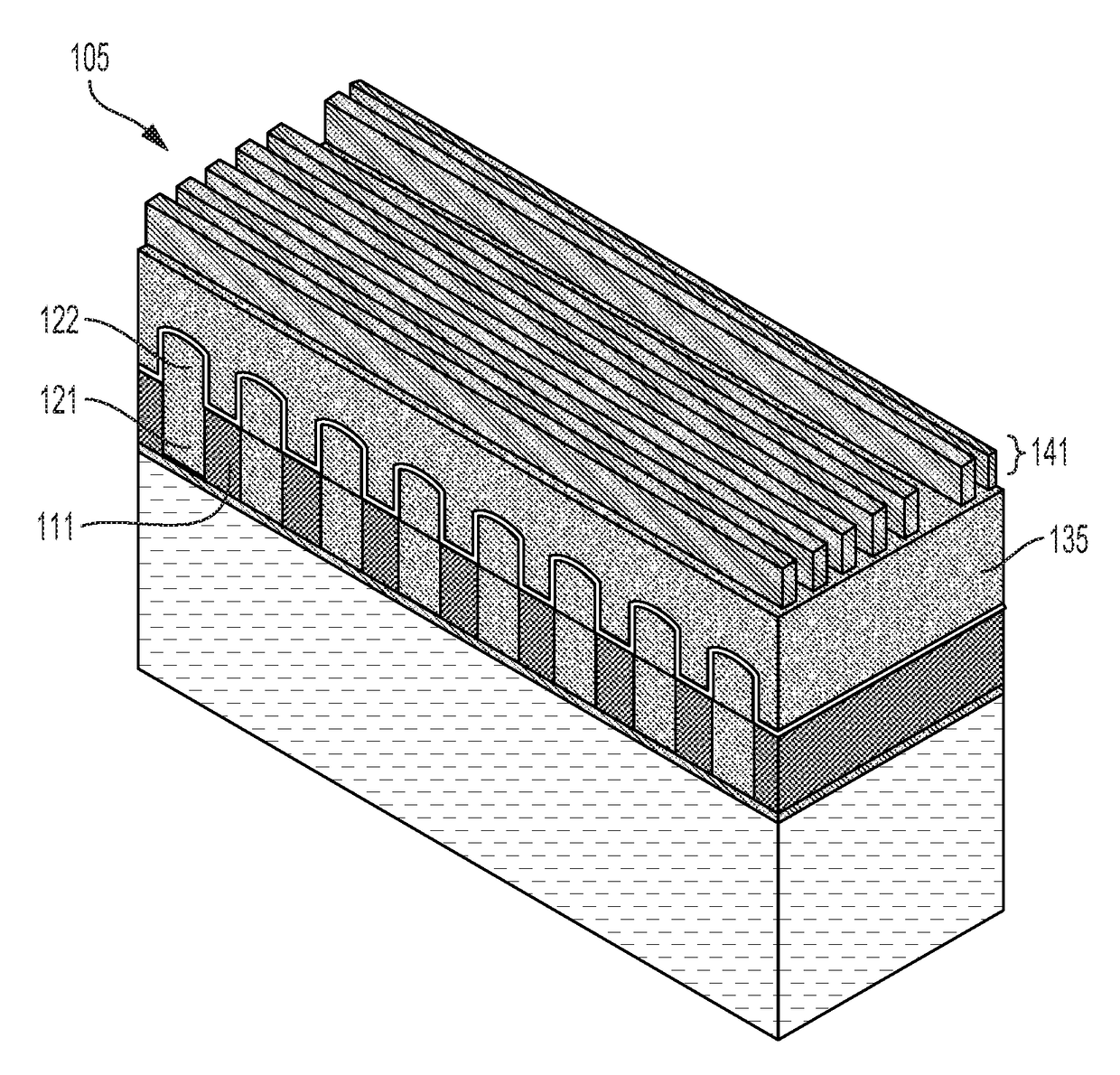

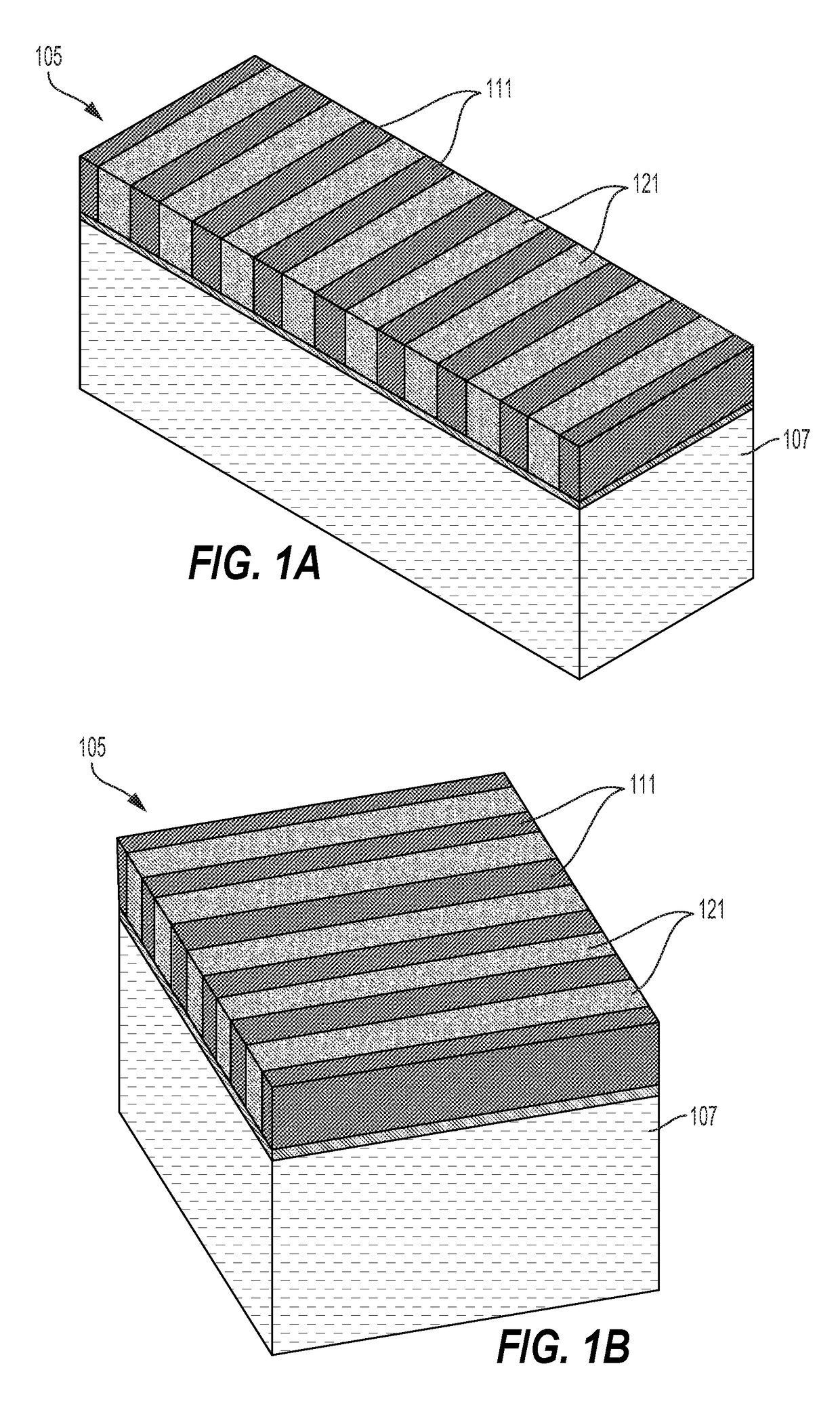

[0027]One embodiment includes a method for patterning a substrate such as a semiconductor wafer. Referring now to FIGS. 1A and 1B, a substrate is received having first metal lines 111 that alternate with first dielectric lines 121 on a working surface of the substrate 105. The first metal lines 111 and the first dielectric lines 121 are uncovered and define a planar surface together. Such a surface can result from a chemical-mechanical polishing (CMP) step. Note that the entire working surface of the substrate...

PUM

| Property | Measurement | Unit |

|---|---|---|

| dielectric | aaaaa | aaaaa |

| etch resistivity | aaaaa | aaaaa |

| dielectric lines | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More