Transistor and formation method thereof

A technology of transistors and crystal orientations, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as leakage currents, achieve performance assurance, reduce interference, and suppress leakage currents

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

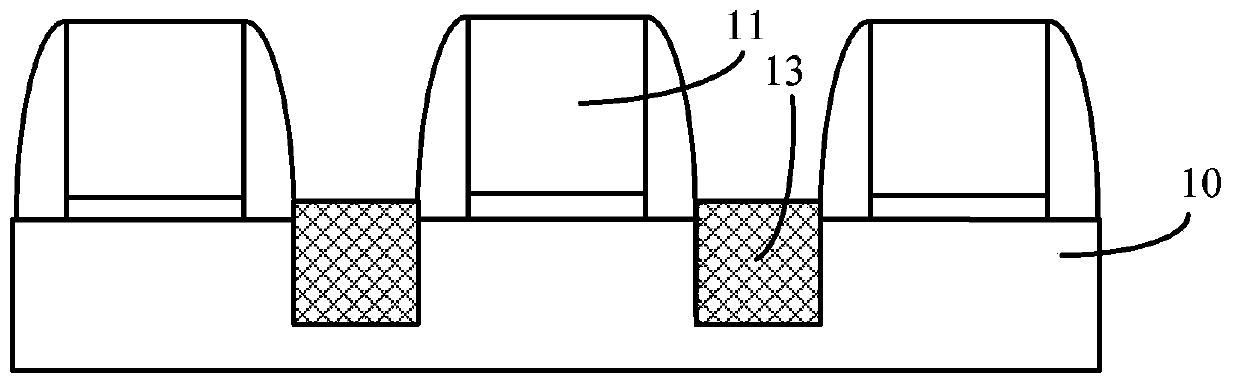

[0037] As mentioned in the background art, leakage current is easily generated in the transistor with the stress layer formed in the prior art.

[0038] The inventors of the present invention found that with the improvement of chip integration and the reduction of the size of the transistor, the size of the source region, the drain region and the channel region of the transistor are also reduced accordingly, so that the diffusion of dopant ions in the source region and the drain region The phenomenon is more obvious; when ion diffusion occurs at the bottom of the source region and the drain region, leakage current is easily generated between the bottom of the source region and the drain region. Please continue to refer image 3 , there are dopant ions in the stress layer 13 to form a source region and a drain region, wherein, once the dopant ions near the bottom of the stress layer 13 are diffused, a leakage current can be generated; moreover, the bottom of the stress layer 13...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More