Structure and manufacturing method of terminal voltage-division region for super-junction device

A technology of super junction device and voltage division area, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc. It can solve problems such as large interface charges, reduce breakdown voltage, and affect voltage division effect, so as to achieve voltage division effect Good, reduce the electric field intensity, improve the effect of device reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

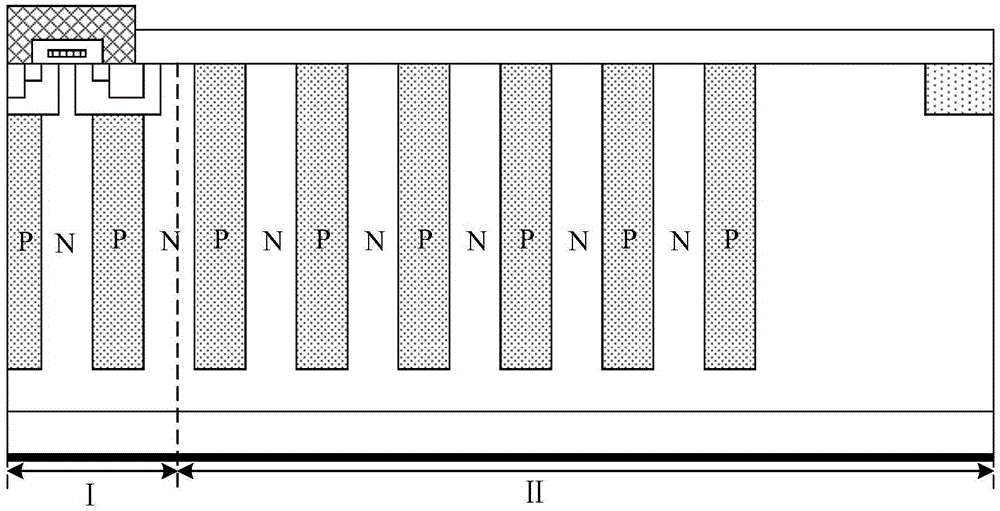

[0033] The following takes N-type super junction devices as an example to introduce the working principle of super junction devices, such as figure 1 The structure of a super-junction device shown includes an active region I and a terminal region II, both of which are alternating P-column and N-column structures.

[0034] Ⅰ. Active area:

[0035] When the device is turned off, that is, when the voltage of the gate is 0, two reverse biased PN junctions are formed laterally, the left P column and the middle vertical conductive N column form a PN junction reverse bias, and the right P column and the middle The vertical conductive N-column forms a PN junction reverse bias, the depletion layer of the PN junction increases, and a horizontal electric field is established; when the doping concentration and width are properly controlled, the middle N-column can be completely depleted, so that in the middle The N-pillar has no free charge, which is equivalent to an intrinsic semiconduc...

Embodiment 2

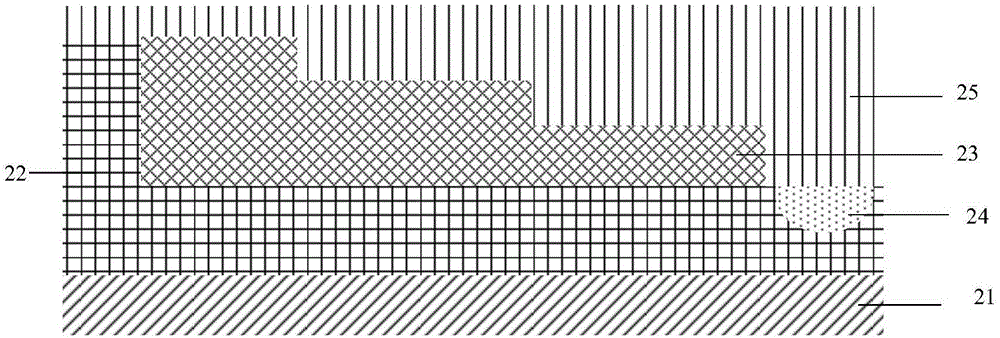

[0041] Such as figure 2 As shown, the structure of a terminal voltage division region of a super junction device provided by Embodiment 2 of the present invention includes:

[0042] a first conductivity type substrate 21;

[0043] an epitaxial layer 22 of the first conductivity type disposed on the substrate 21 of the first conductivity type;

[0044] The epitaxial layer 22 is provided with a second conductivity type doped column 23 in the voltage dividing region, and the second conductivity type doped column 23 in the voltage division region is not in contact with the second conductivity type doped column in the active region , the doped column 23 of the second conductivity type in the voltage dividing region is stepped, and the vertical height of the step decreases one by one from one end close to the active region to one end far away from the active region;

[0045] The side of the epitaxial layer away from the active region is provided with a heavily doped region 24 of ...

Embodiment 3

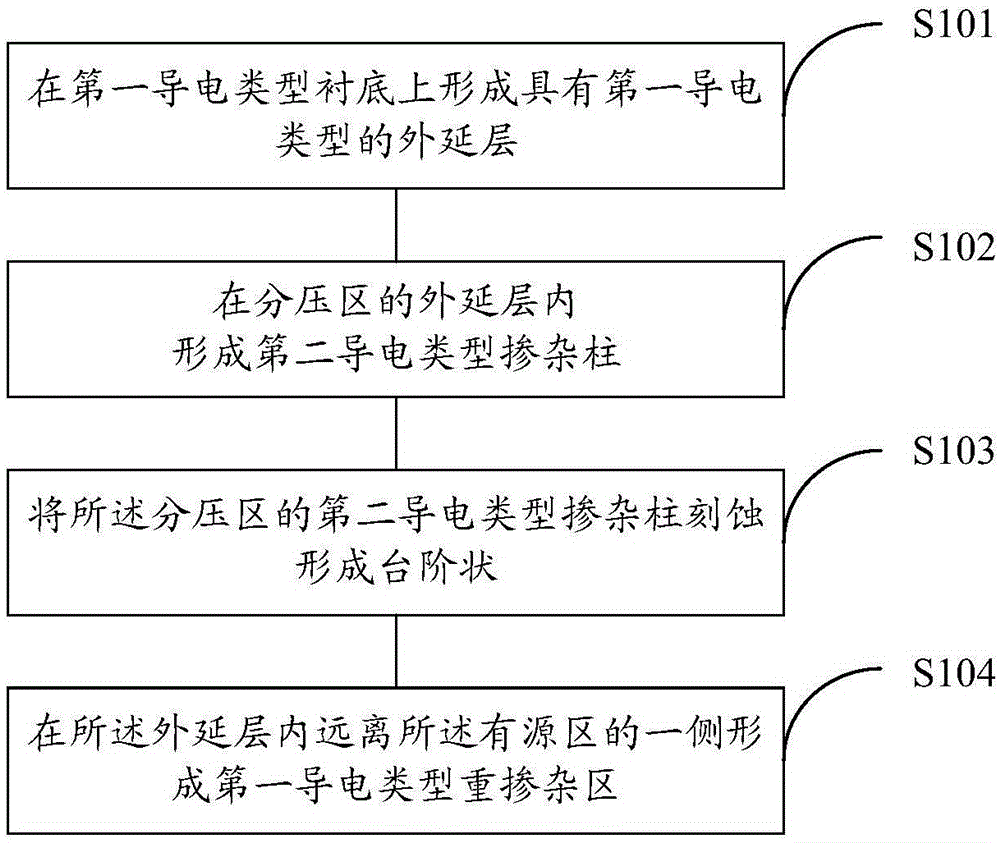

[0062] The following takes an N-type semiconductor as an example to describe in detail the manufacturing process of the voltage dividing region at the end of the super junction device provided by the embodiment of the present invention. Such as Figure 4 (a) ~ 4 (g) As shown in FIG. 2 , it is a schematic structural diagram of each stage in the manufacturing process of the epitaxial wafer for super-junction devices disclosed in Embodiment 2 of the present invention.

[0063] In the first step, as shown in Fig. 4(a), an N-type silicon single wafer is used as the substrate 1, and the front side of the single wafer is cleaned.

[0064] In the second step, as shown in FIG. 4( b ), an N-type epitaxial layer 2 is grown on the substrate 1 , and P columns 3 are formed in the N-type epitaxial layer 2 .

[0065] Here, the P column 3 and the P column in the active region are formed simultaneously by the same process, multiple epitaxial implantation techniques can be used, and the formed ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More