Patents

Literature

206results about How to "Improved contact characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

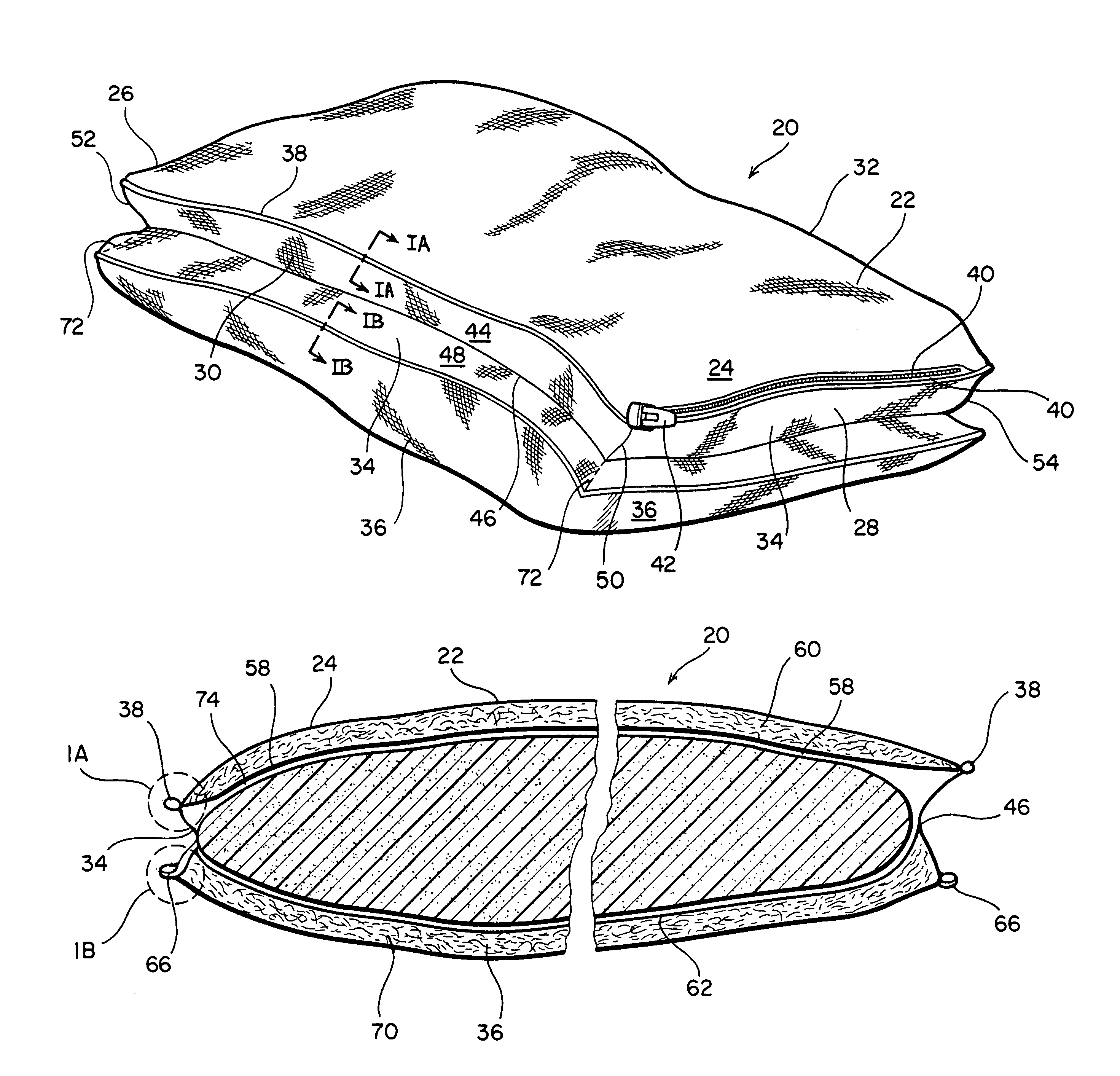

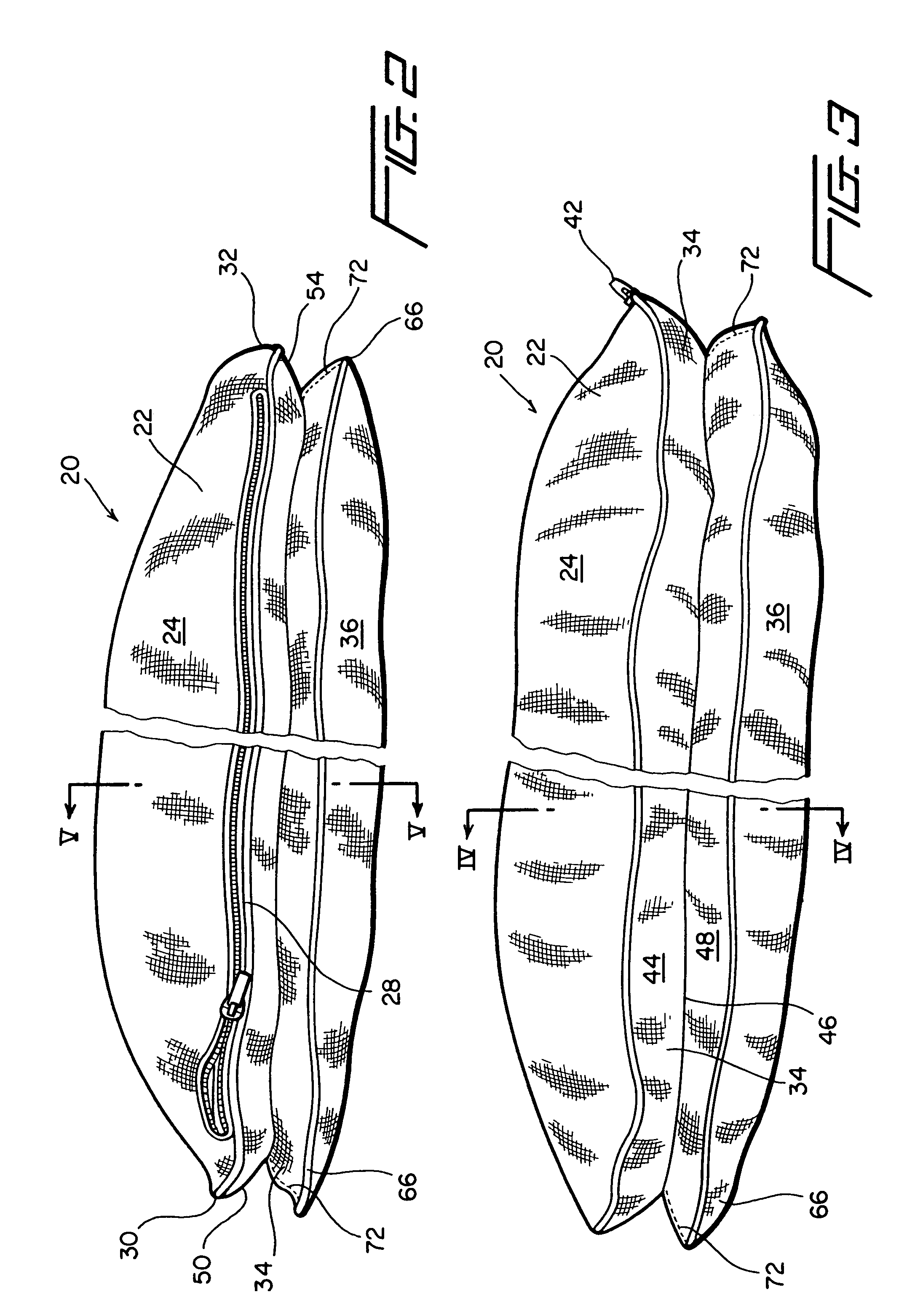

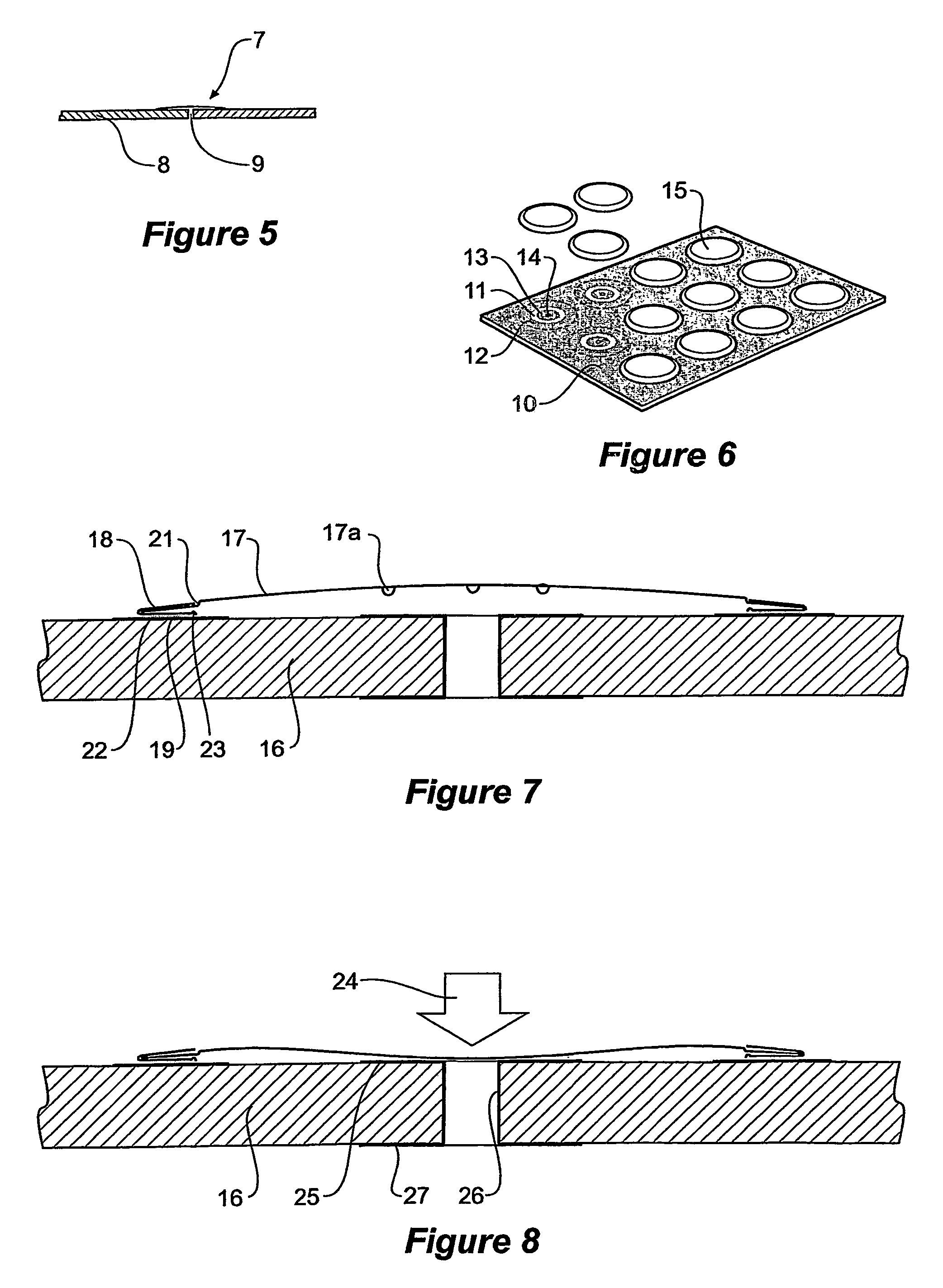

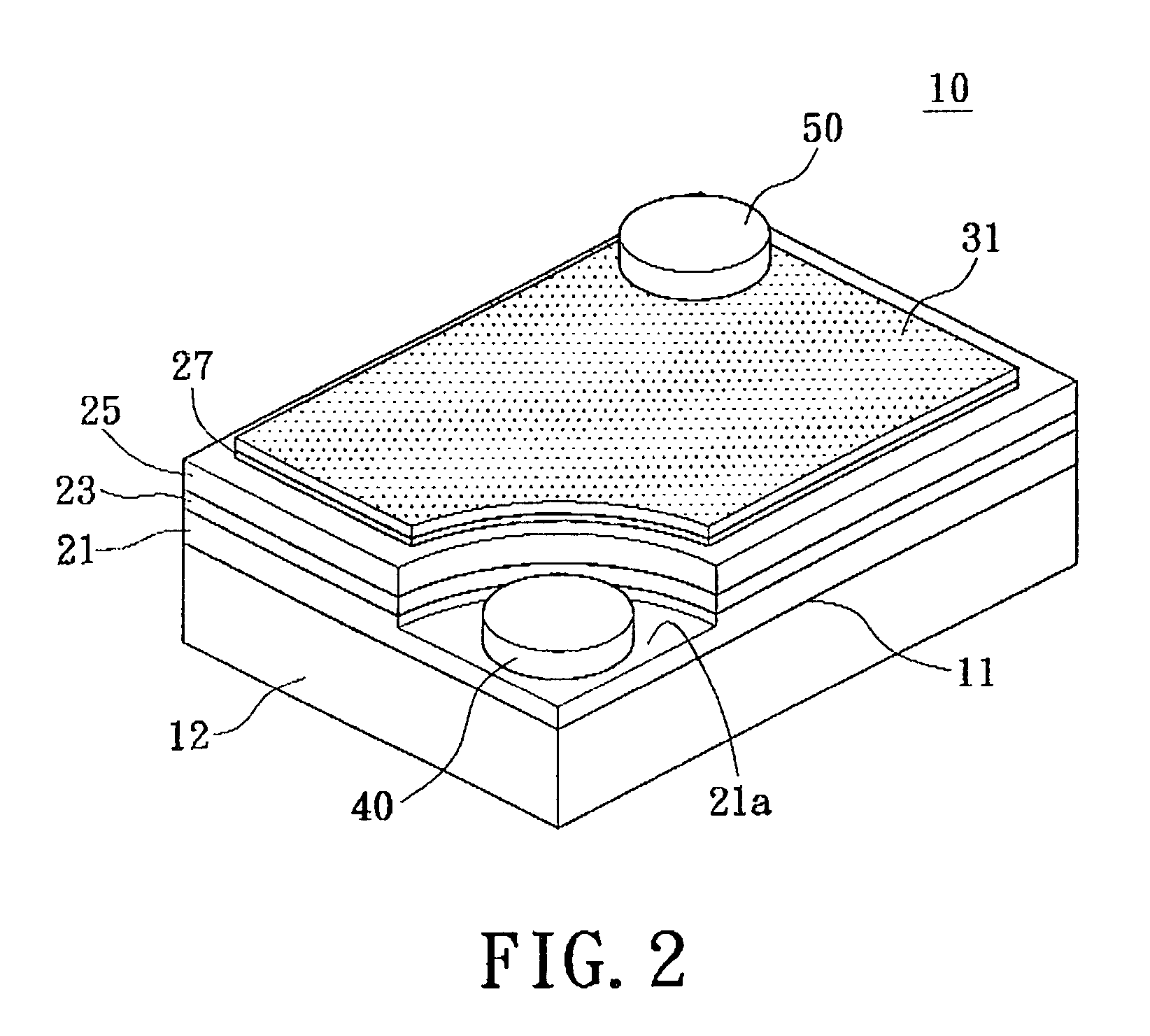

Cushioning device and method of producing the same

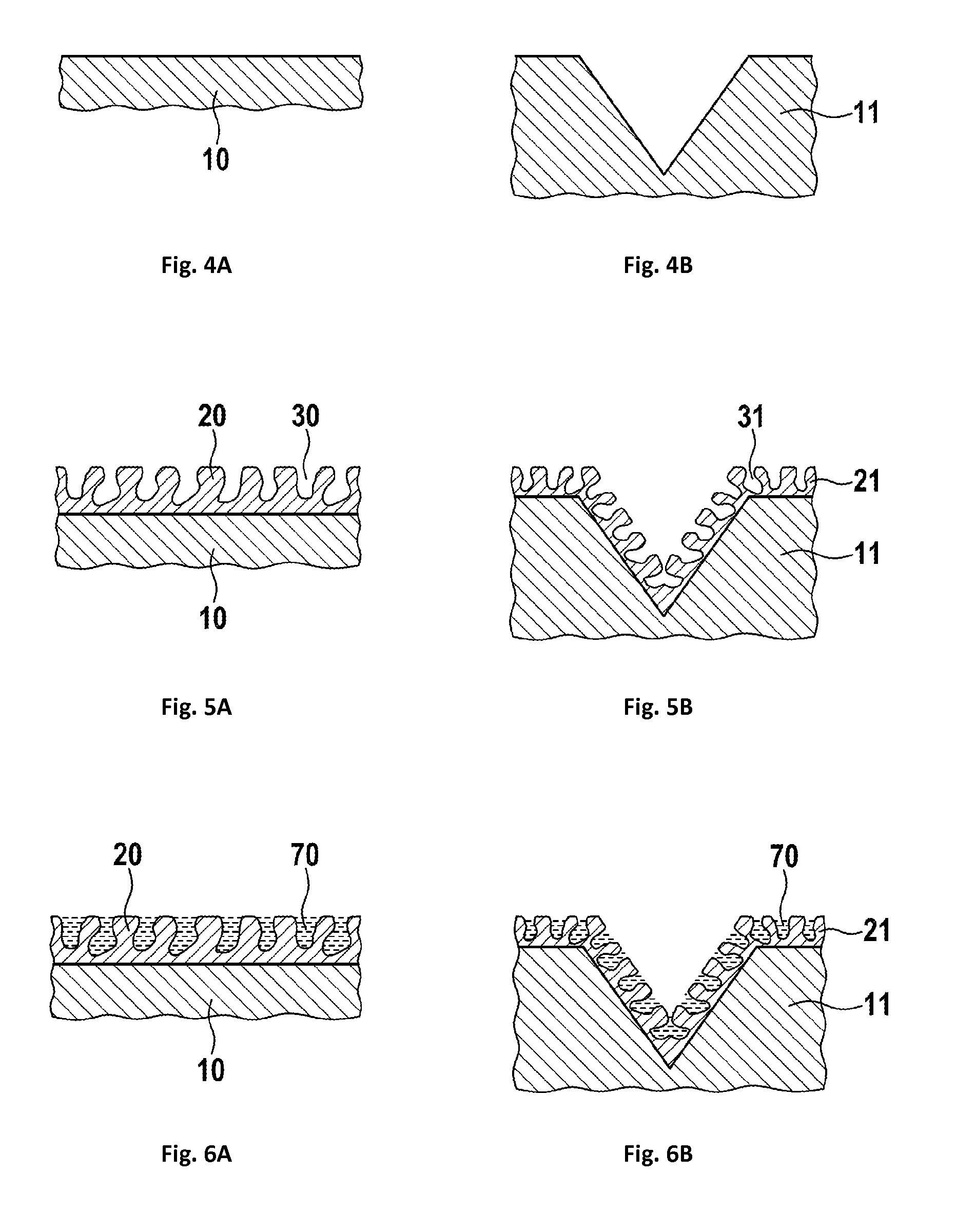

InactiveUS6988286B2Improved contact characteristicsGood “look and feelPillowsSofasFiberFilling materials

A cushioning apparatus such as a pillow which includes an upper pocket with reception cavity for receiving preferably loose or grouped non-integral filler material such as down, fiberfill or fiber-balls and another pocket for receiving additional filler material such as a foam core filler material. The foam core filler material is preferably an integrated or monolithic foam body of, for example, visco-elastic or alternate polyurethane foam. The core preferably has a non-planar upper surface contour allowing for a relatively thin, consistent height upper pocket thickness. The pillow also preferably includes a lower pocket joined about its periphery to the upper pocket such as by way of an intermediate gusset panel with beading and with the lower pocket also receiving loose or non-integrated filler material and with the bottom surface of the core preferably having a convex surface such as one symmetrical with the top surface.

Owner:CARPENTER CO

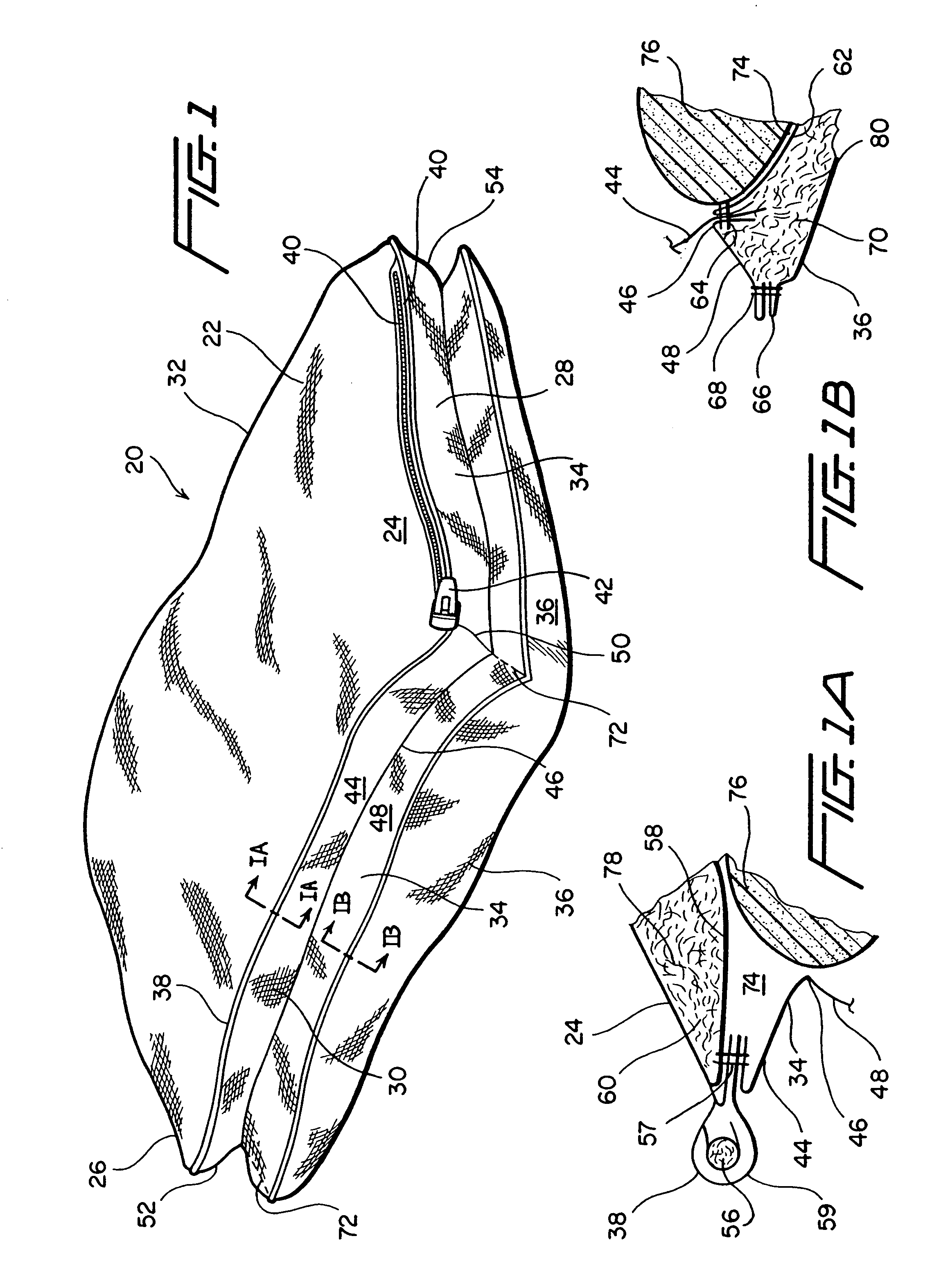

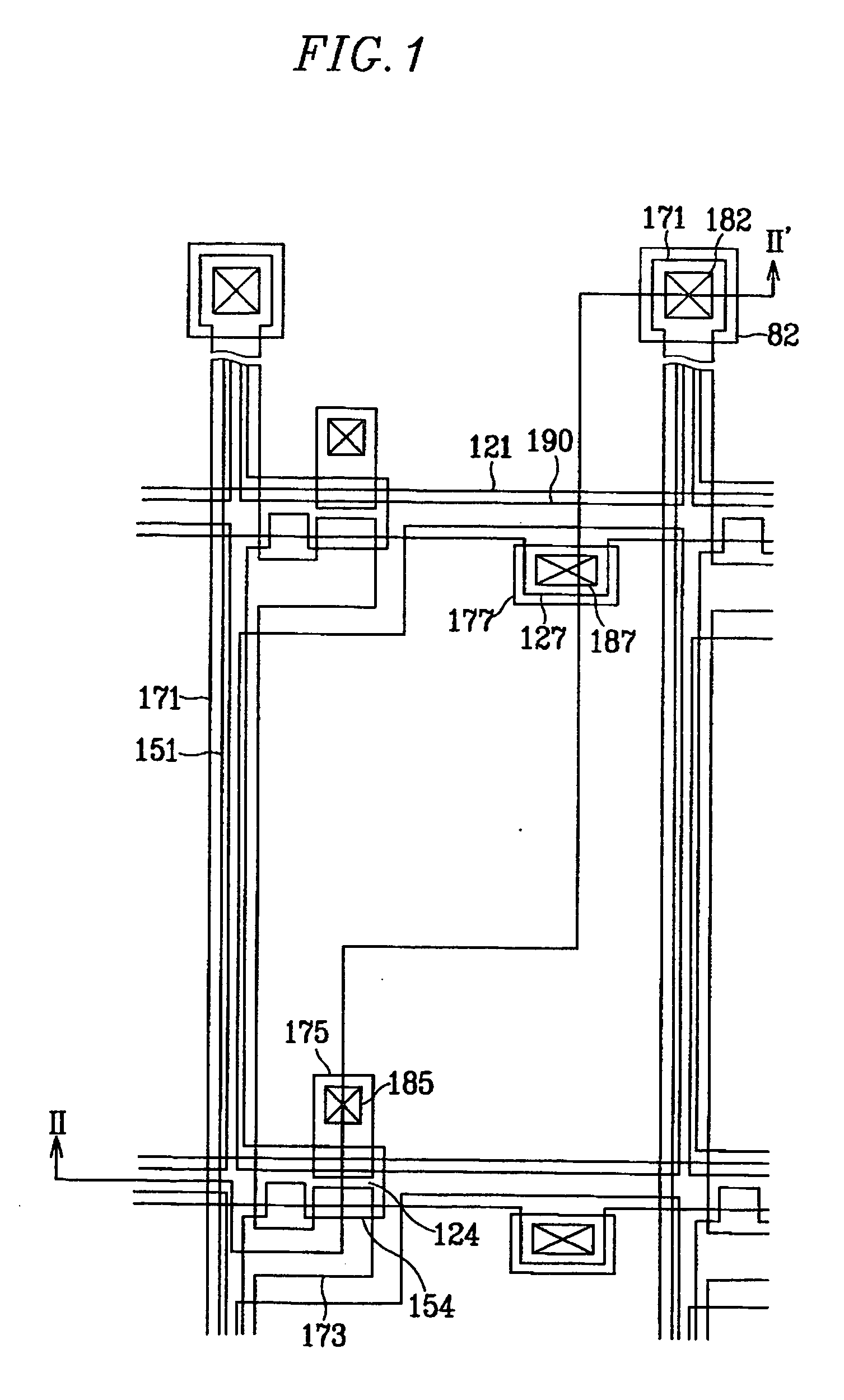

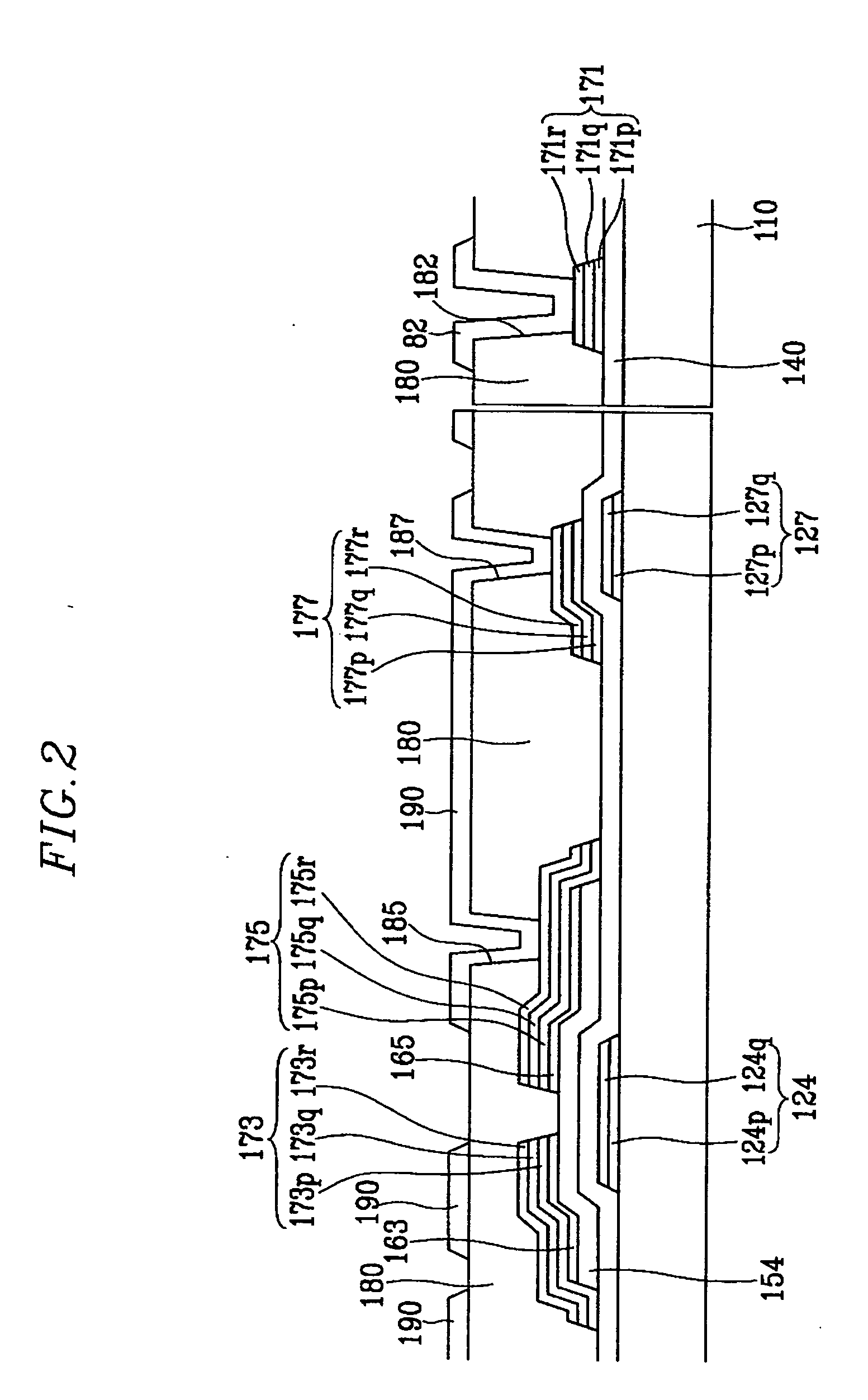

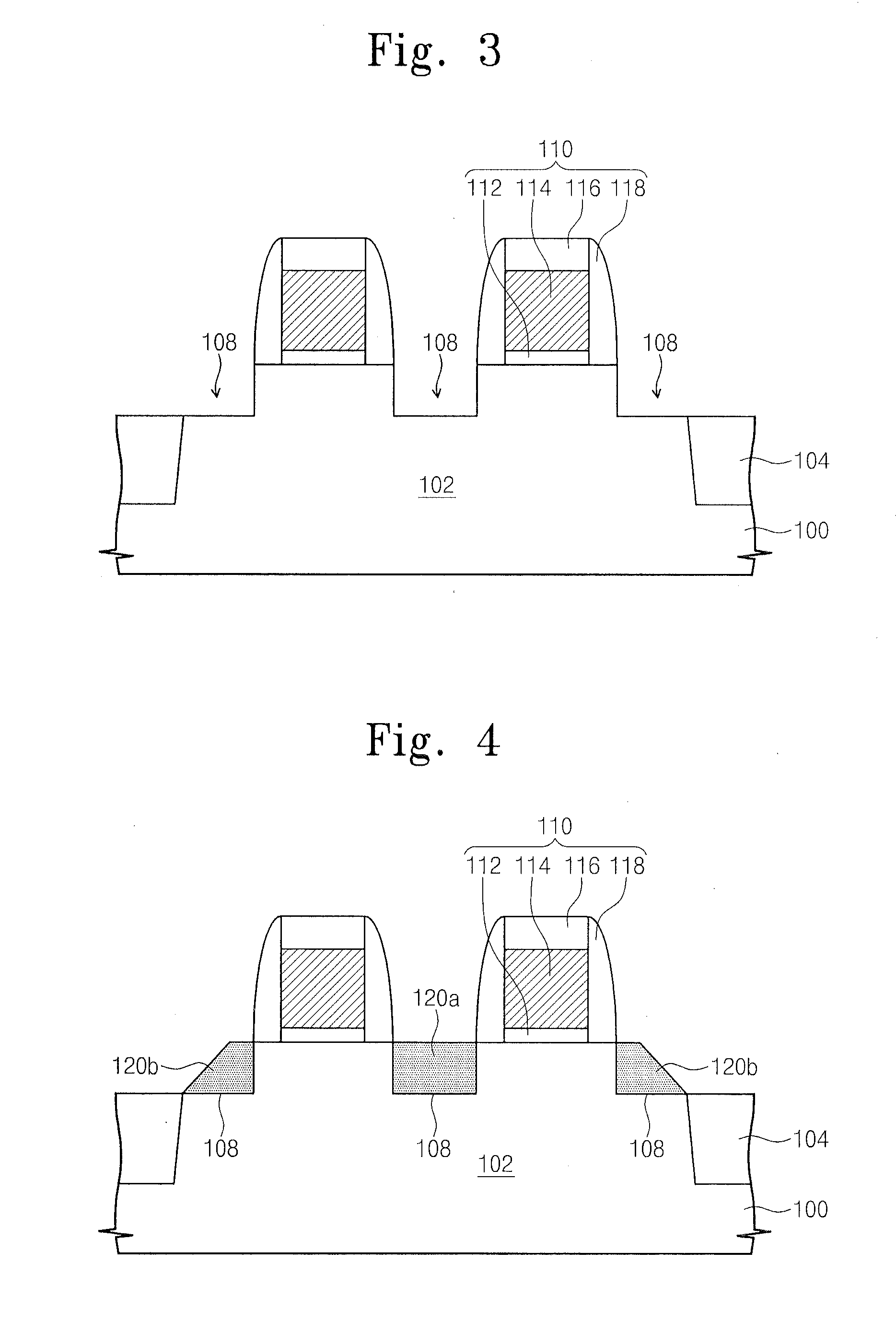

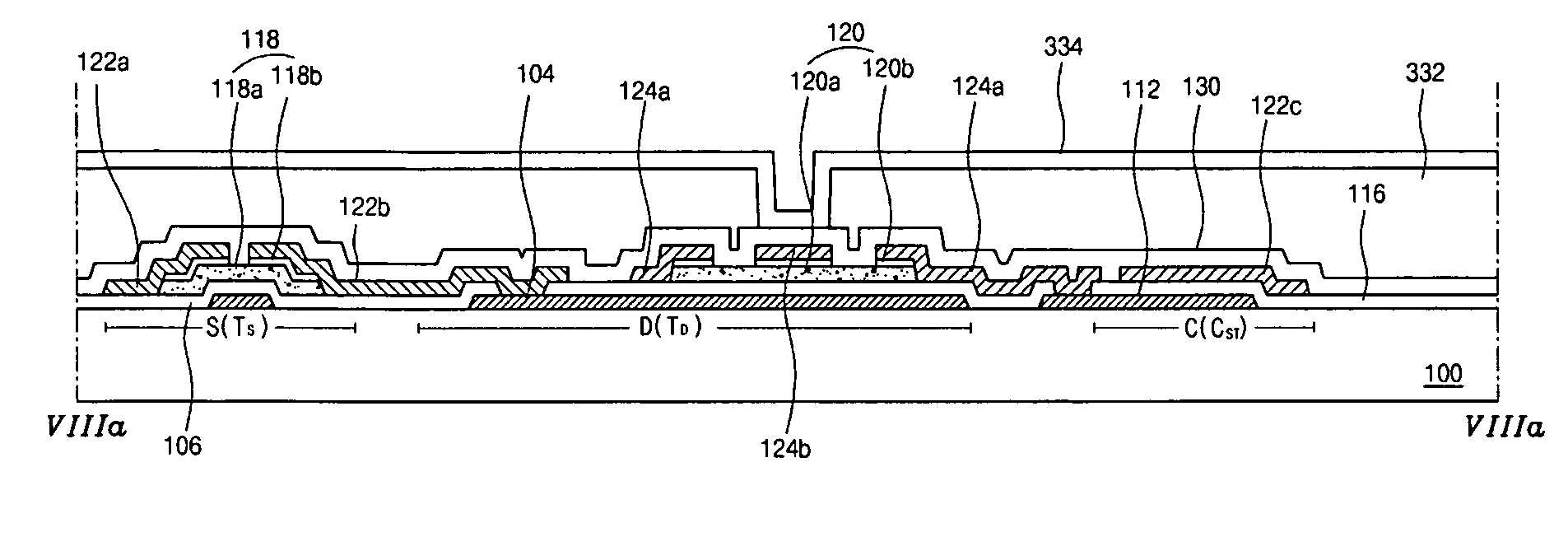

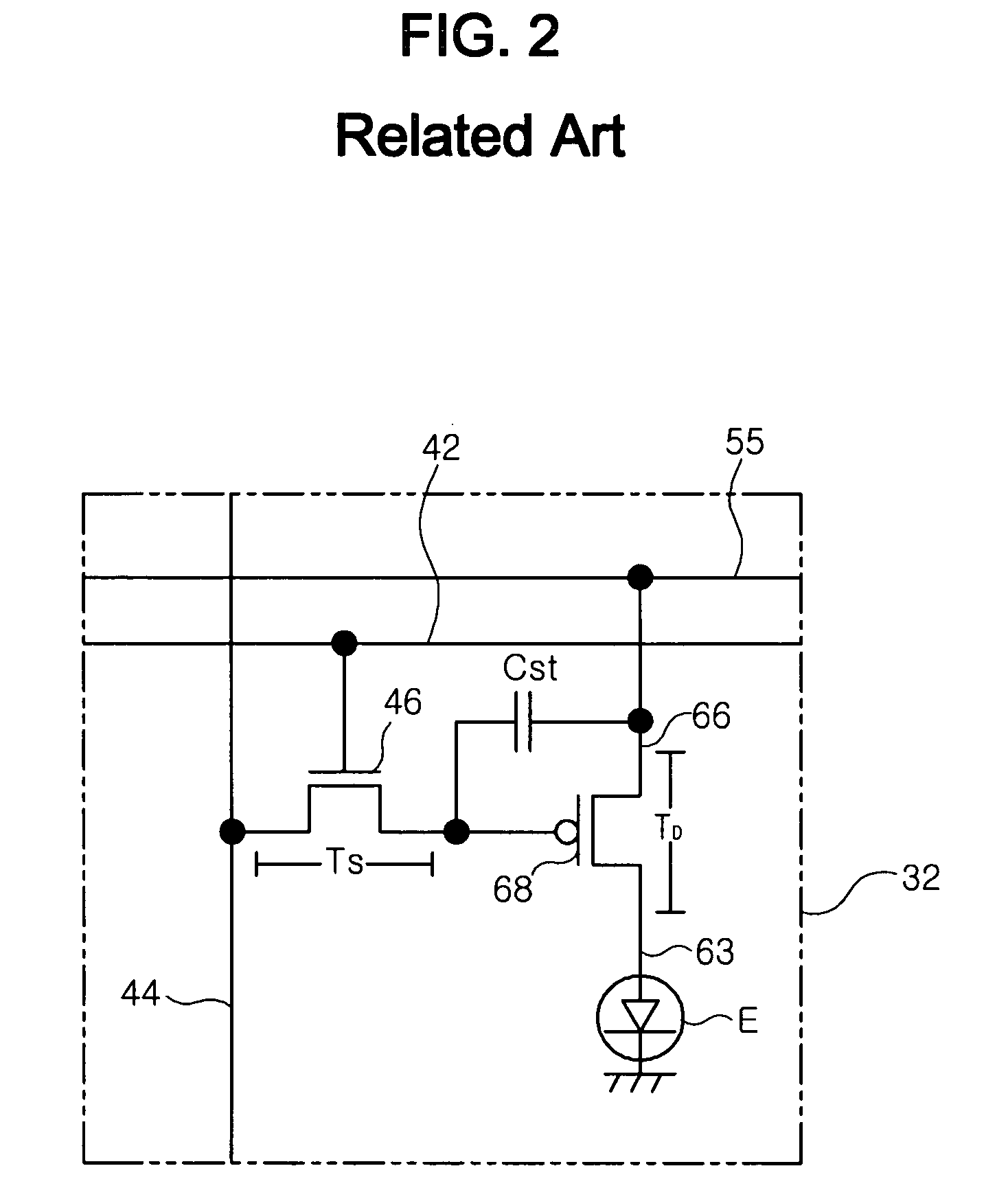

Thin film transistor array panel and method for manufacturing the same

InactiveUS20060050192A1Low resistivityImproved contact characteristicsSolid-state devicesNon-linear opticsNiobiumOptoelectronics

The present invention provides a TFT array panel and a manufacturing method of the same, which has signal lines including a lower layer of an Al containing metal and an upper layer of a molybdenum alloy (Mo-alloy) comprising molybdenum (Mo) and at least one of niobium (Nb), vanadium (V), and titanium (Ti). Accordingly, undercut, overhang, and mouse bites which may arise in an etching process, are prevented, and TFT array panels that have signal lines having low resistivity and good contact characteristics are provided.

Owner:SAMSUNG DISPLAY CO LTD

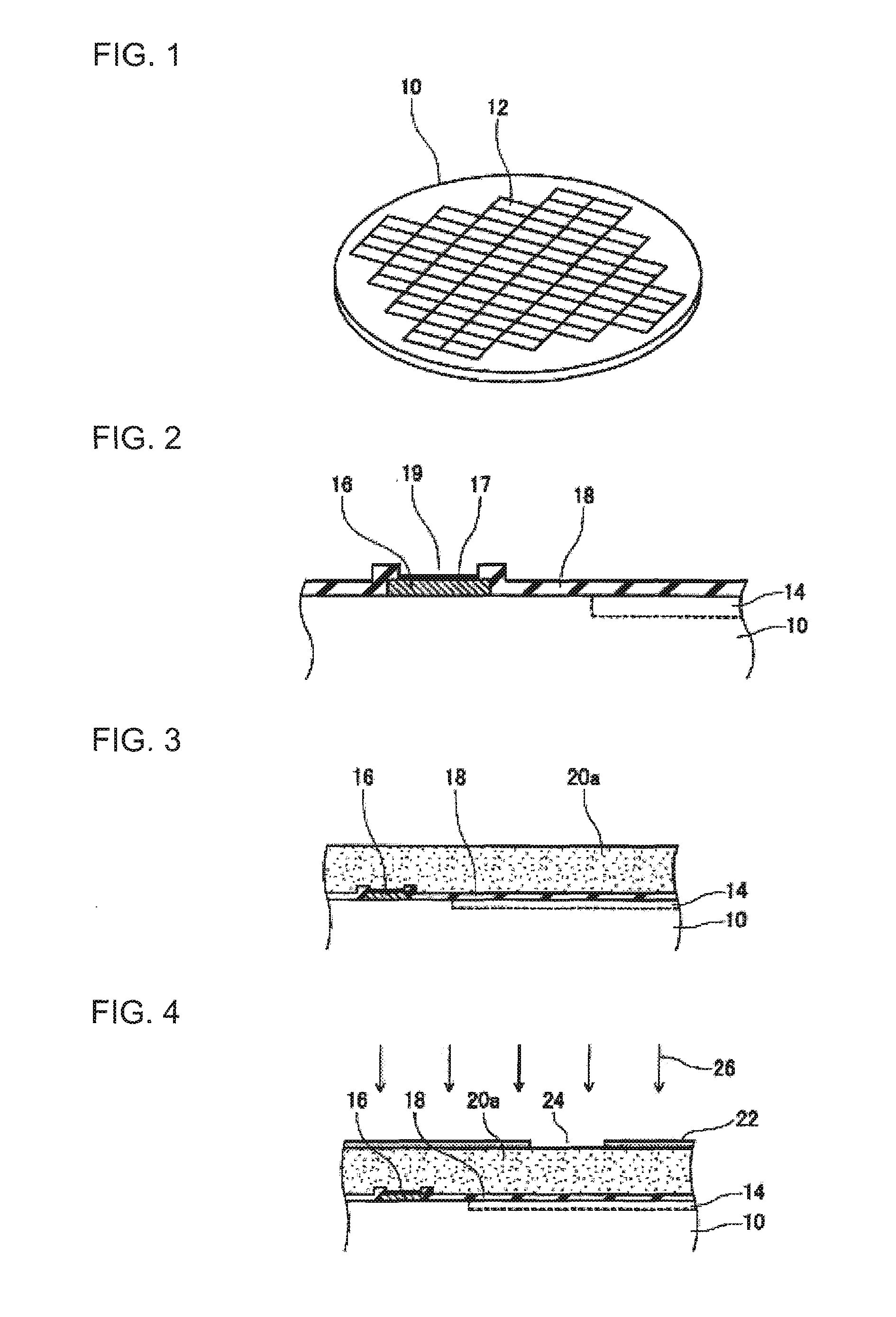

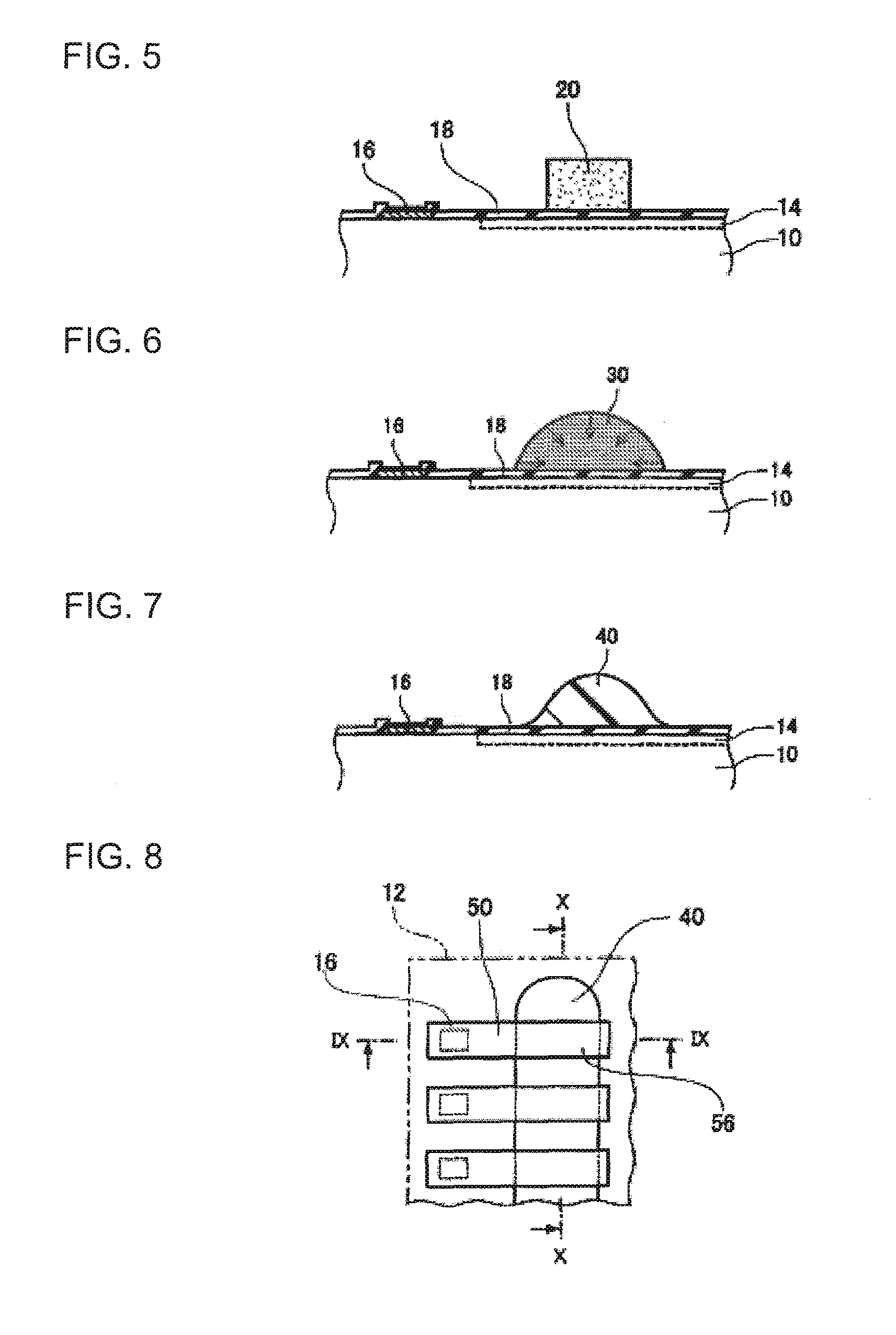

Method for manufacturing semiconductor device

InactiveUS20070026660A1Improved contact characteristicsInhibit migrationSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A method for manufacturing a semiconductor device, including: (a) forming an energy cured resin layer on a semiconductor substrate having an electrode pad and a passivation film; (b) fusing the resin layer without being cured and shrunk by a first energy supply processing; (c) forming a resin boss by curing and shrinking the resin layer after fusion by a second energy supply processing; and (d) forming an electrical conducting layer which is electrically connected to the electrode pad and passes through over the resin boss.

Owner:138 EAST LCD ADVANCEMENTS LTD

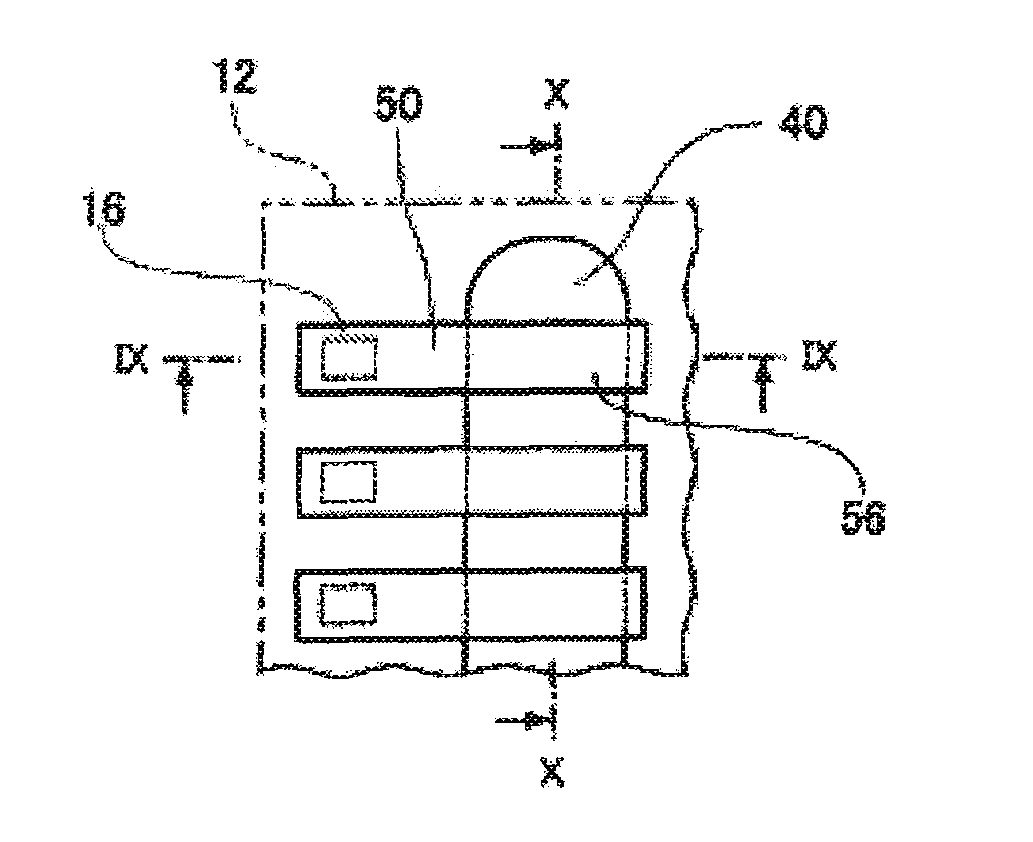

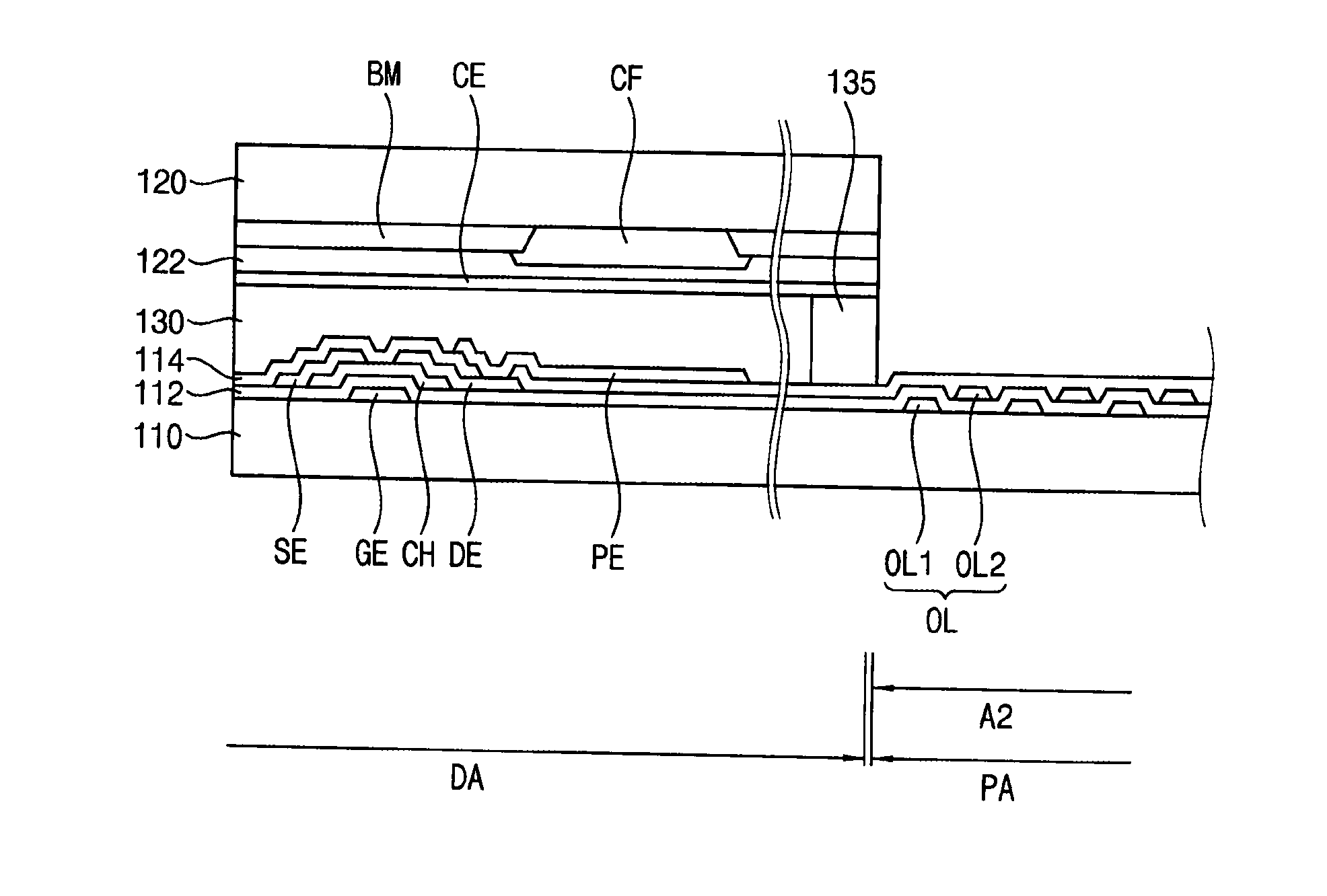

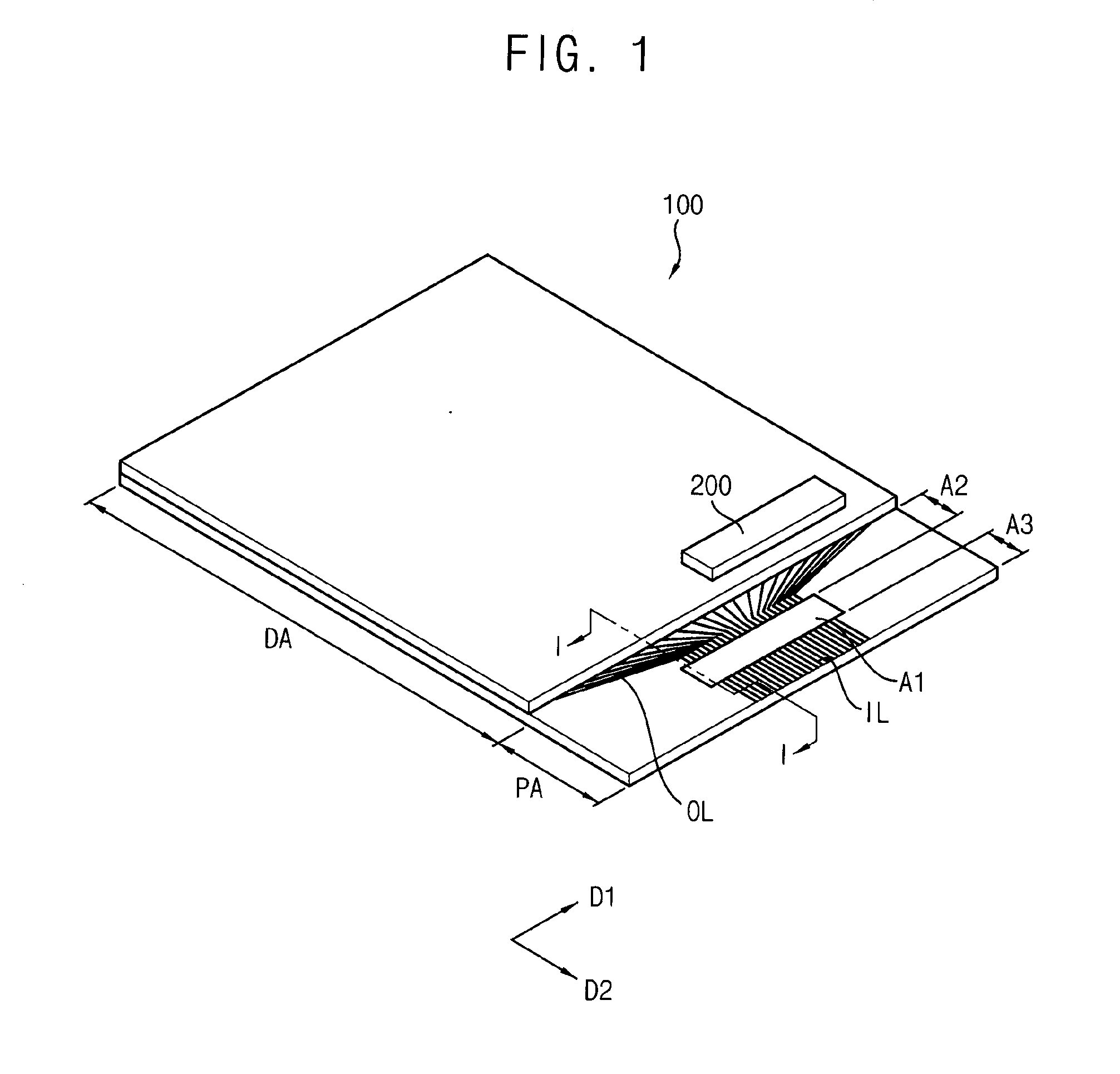

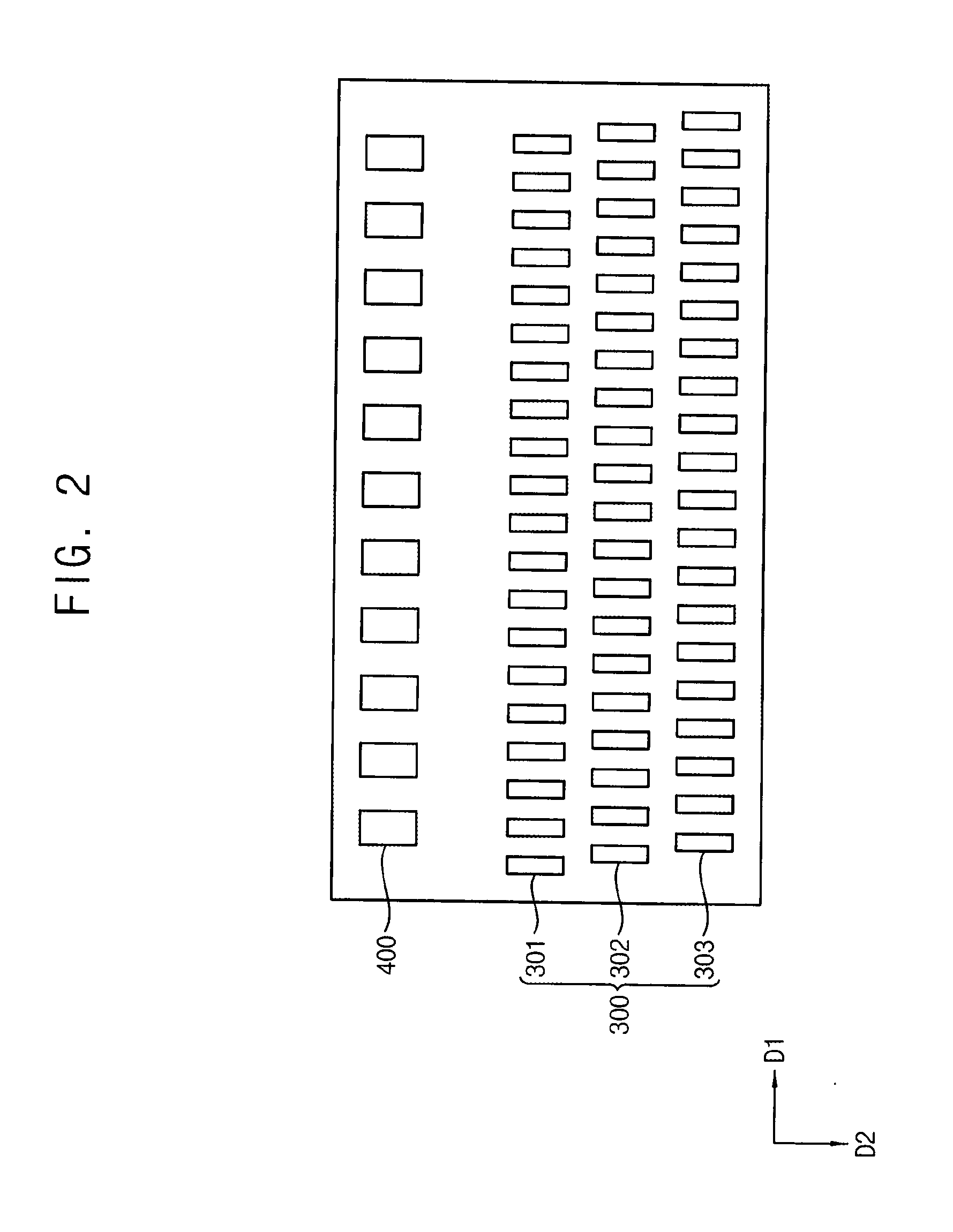

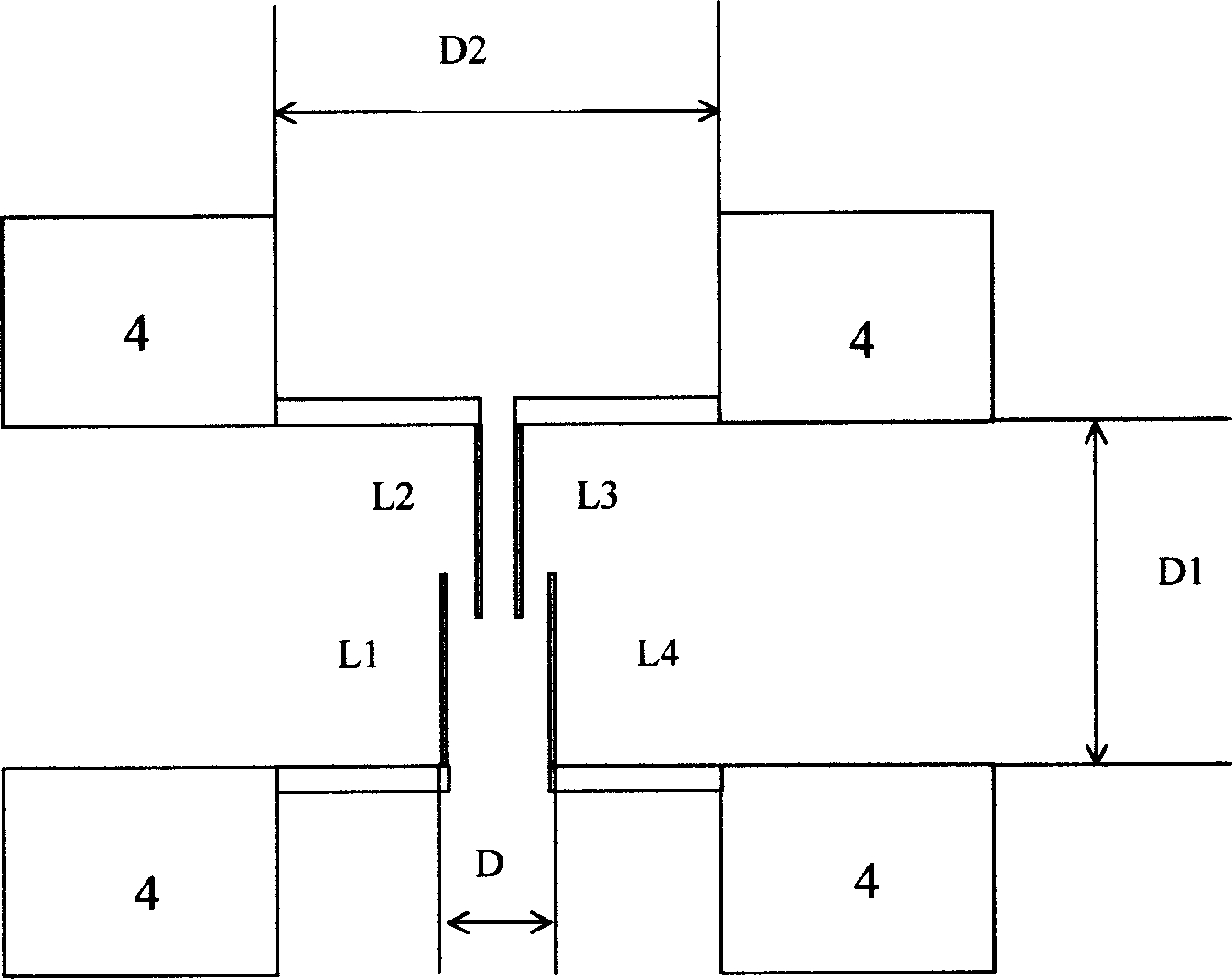

Display panel, display apparatus having the same and method of manufacturing the same

ActiveUS20150187803A1Improve electrical contact characteristicsSpeed up the flowSolid-state devicesSemiconductor/solid-state device manufacturingPeripheralElectrical and Electronics engineering

A display panel includes a display area configured to display an image, and a peripheral area adjacent to the display area. The peripheral area includes a pad area in which a plurality of output pads are disposed. The output pads are arranged in a matrix formed having M row*N column (M and N are normal numbers, M is 3 or larger than 3). Each of the output pads has a center of the output pad spaced apart from a center of an adjacent output pad by a distance D in a first direction. Each of the output pads is spaced apart from an adjacent output pad by a gap. Each of the output pads has a center of the output pad spaced apart from a center of an adjacent output pad by a pitch P in a second direction which is substantially perpendicular to the first direction. An equation “P<D / (M−1)” is satisfied.

Owner:SAMSUNG DISPLAY CO LTD

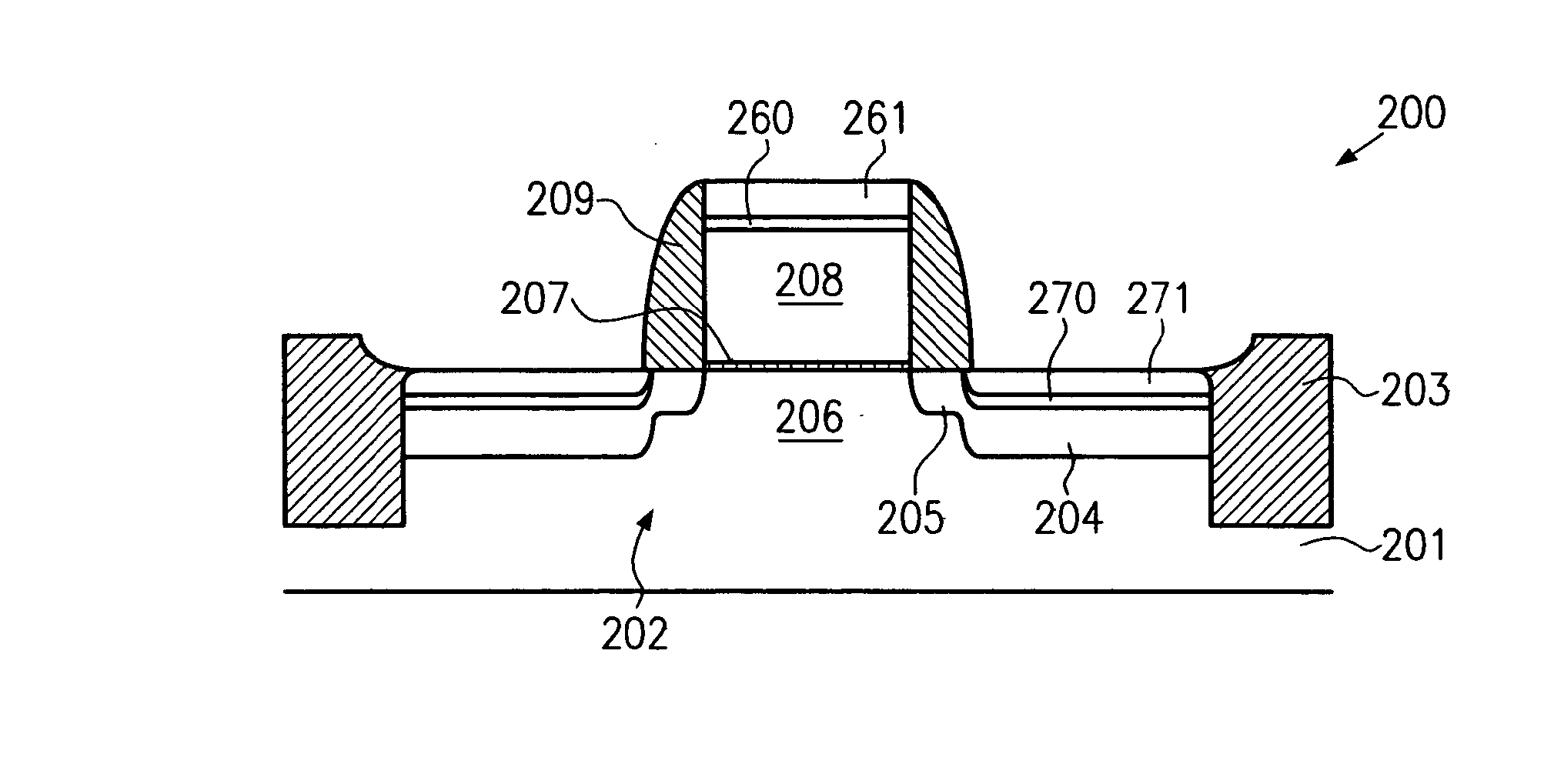

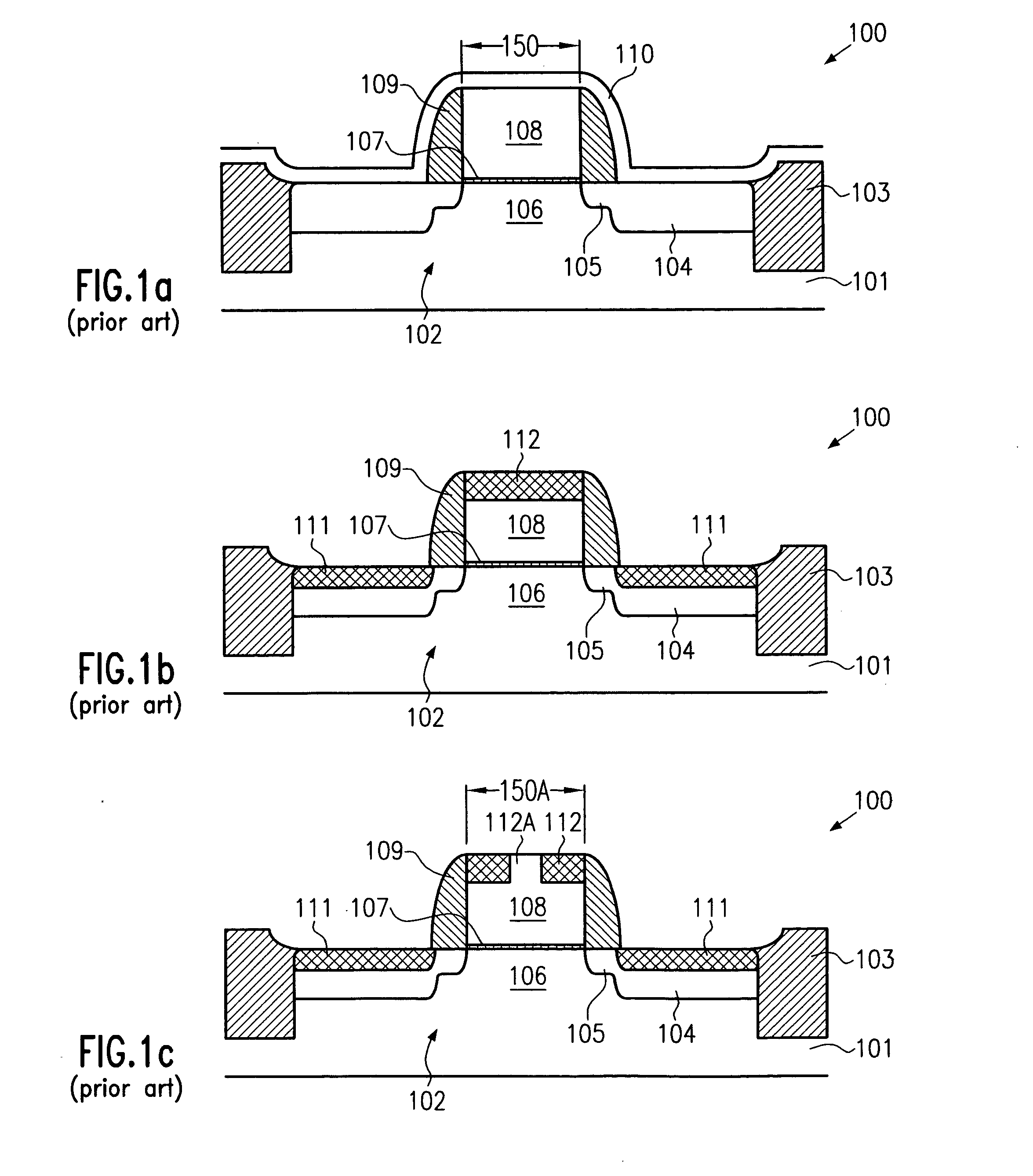

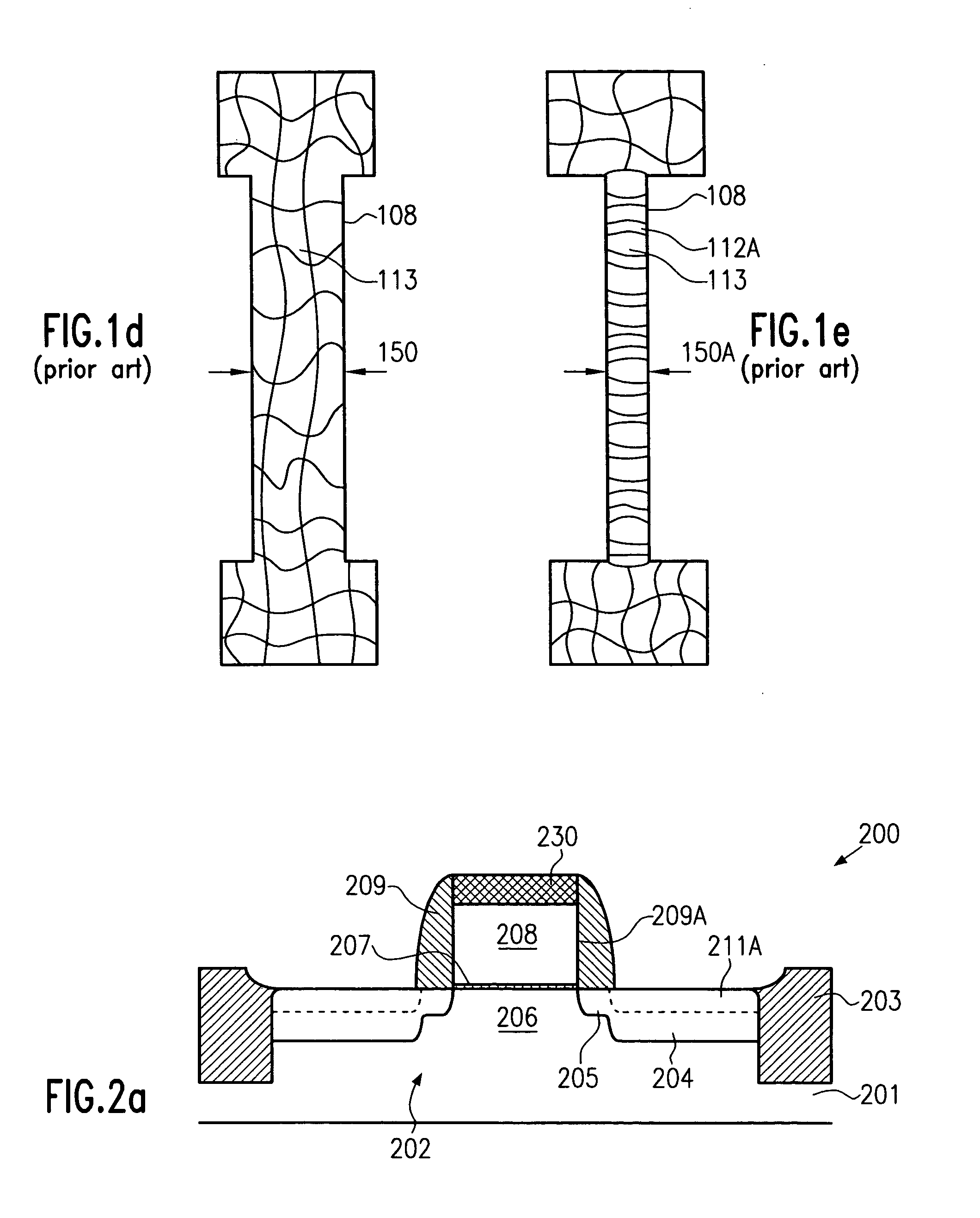

Semiconductor device having a nickel/cobalt silicide region formed in a silicon region

InactiveUS20050070082A1Improve bindingImproved contact characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceDevice material

By forming a buried nickel silicide layer followed by a cobalt silicide layer in silicon-containing regions, such as a gate electrode of a field effect transistor, the superior characteristics of both silicides may be combined so as to provide the potential for further device scaling without unduly compromising the sheet resistance and the contact resistance of scaled silicon circuit features.

Owner:ADVANCED MICRO DEVICES INC

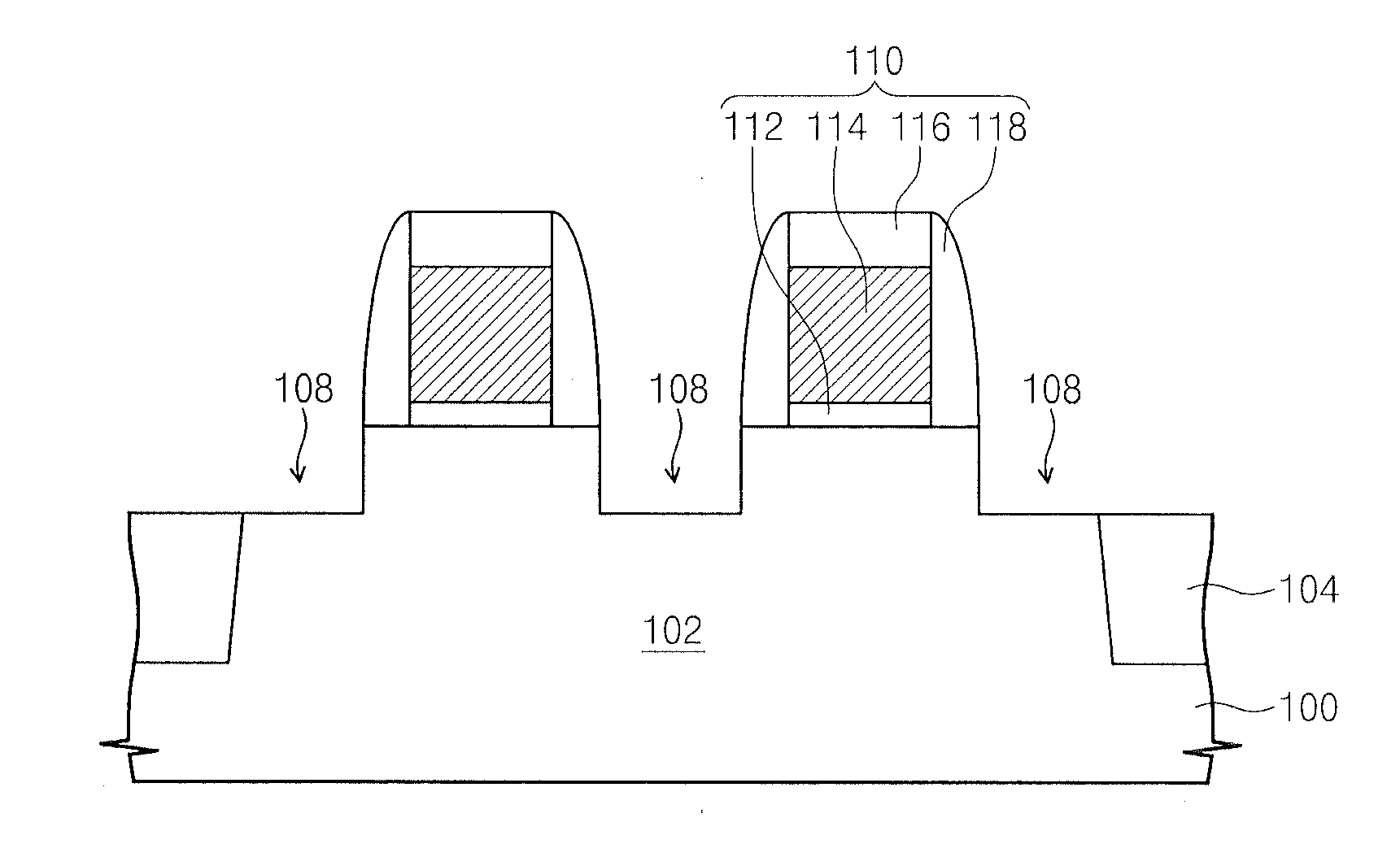

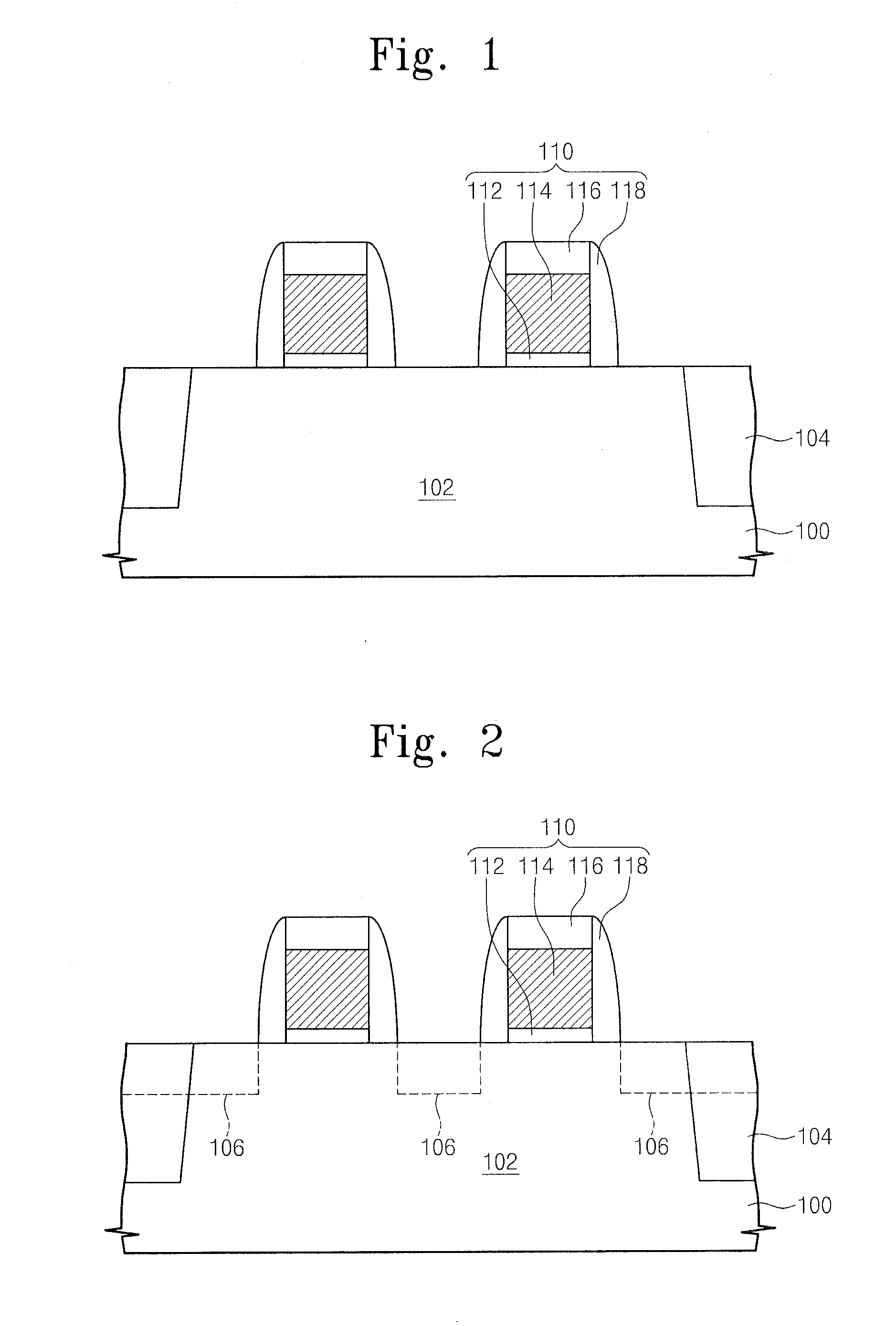

Semiconductor device and method of fabricating the same

InactiveUS20120329252A1Reduce variationImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsDevice material

A semiconductor device may include a semiconductor substrate with an active region, a gate line disposed on the active region, an epitaxial pattern disposed on the semiconductor substrate beside the gate line, the epitaxial pattern including a semiconductor material different from the semiconductor substrate, and a capping pattern disposed on the epitaxial pattern. The capping pattern may improve contact with contact plug and may reduce variation in mean ion depths of an associated field effect transistor.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device and method for manufacturing the same

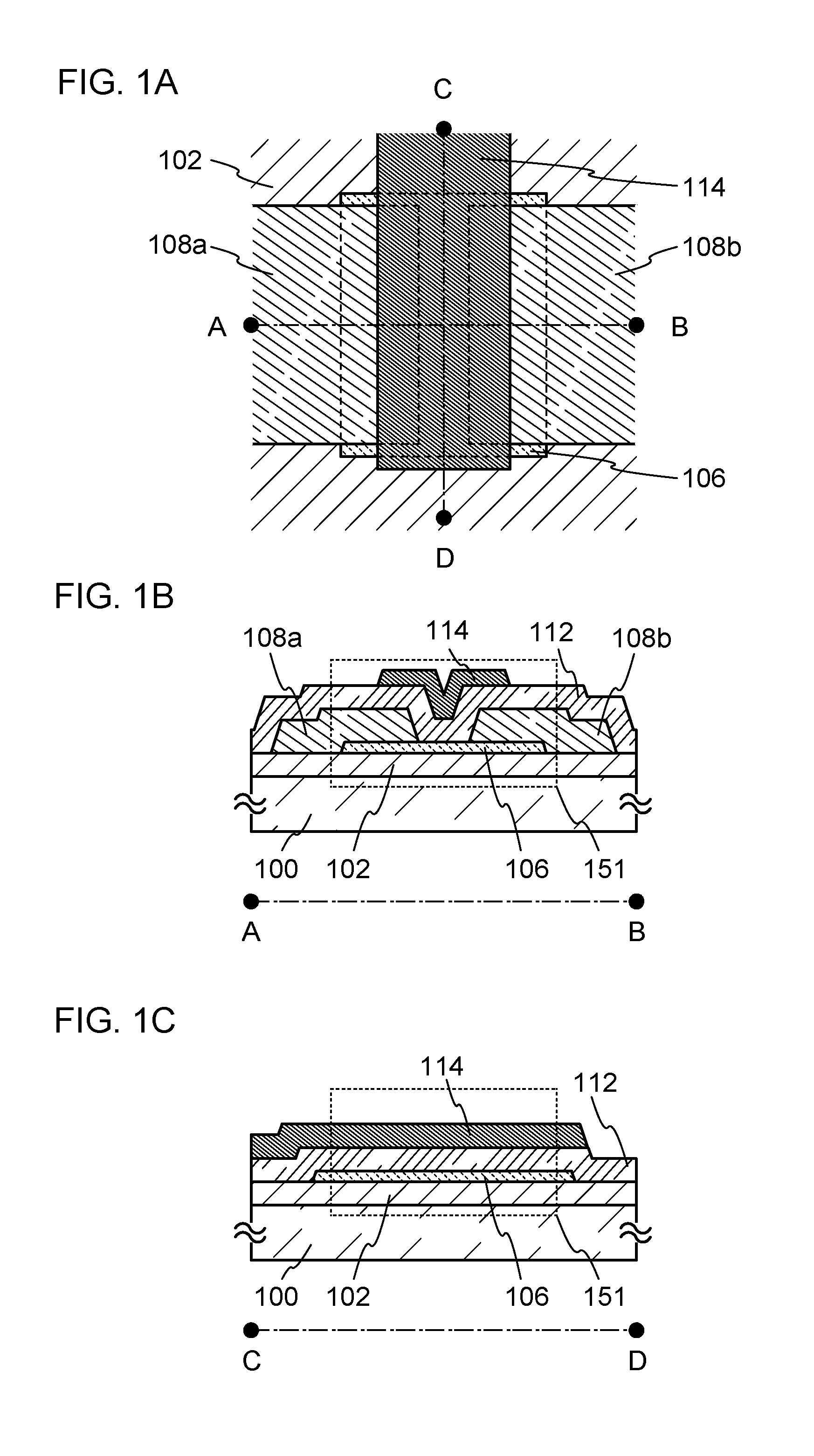

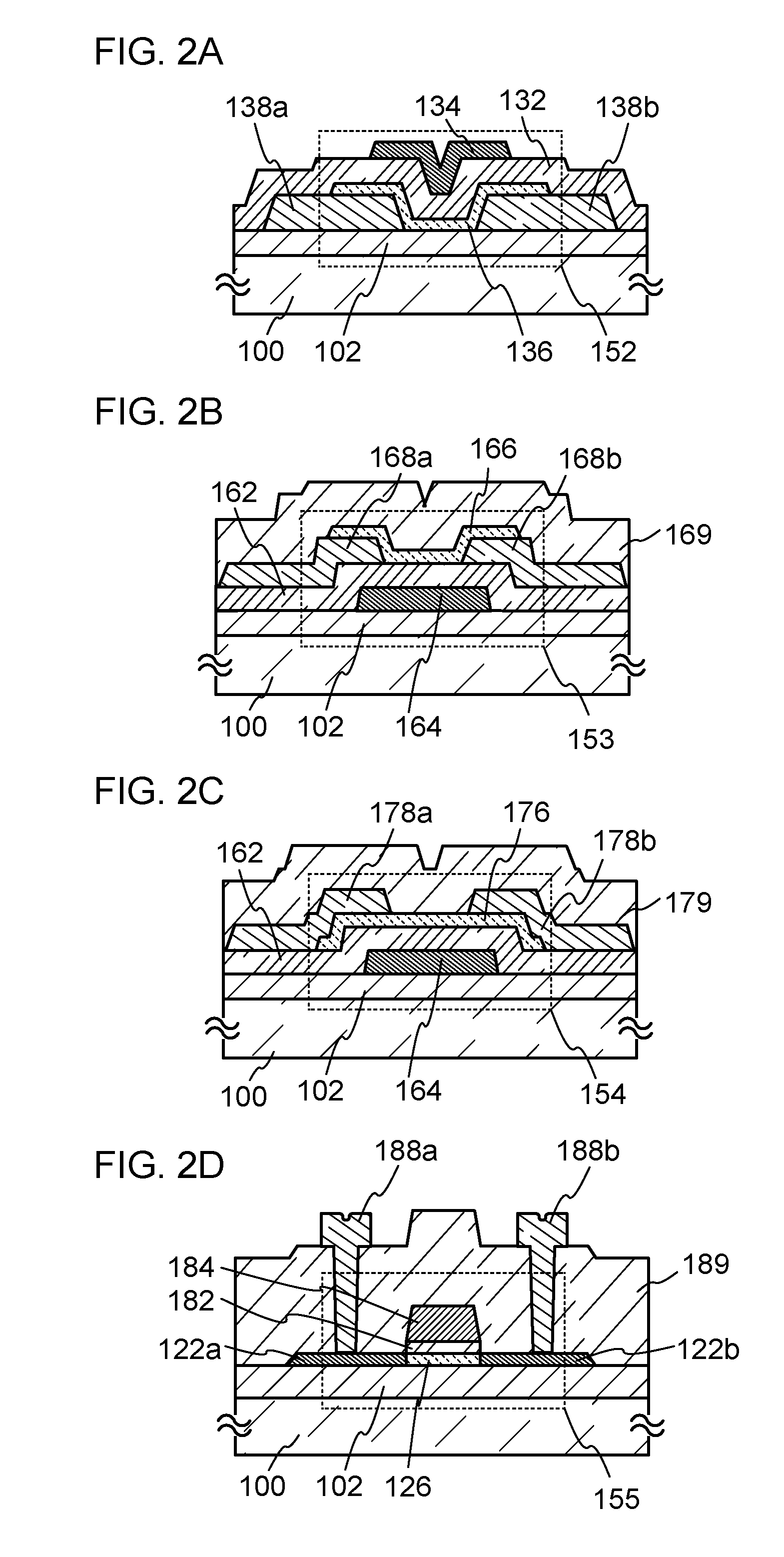

ActiveUS20120112183A1Sufficient characteristicImproved contact characteristicsTransistorSolid-state devicesCharge-carrier densityNitrogen

An object is to provide a semiconductor device including an oxynitride semiconductor whose carrier density is controlled. By introducing controlled nitrogen into an oxide semiconductor layer, a transistor in which an oxynitride semiconductor having desired carrier density and on characteristics is used for a channel can be manufactured. Further, with the use of the oxynitride semiconductor, even when a low resistance layer or the like is not provided between an oxynitride semiconductor layer and a source electrode and between the oxynitride semiconductor layer and a drain electrode, favorable contact characteristics can be exhibited.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device manufacturing device

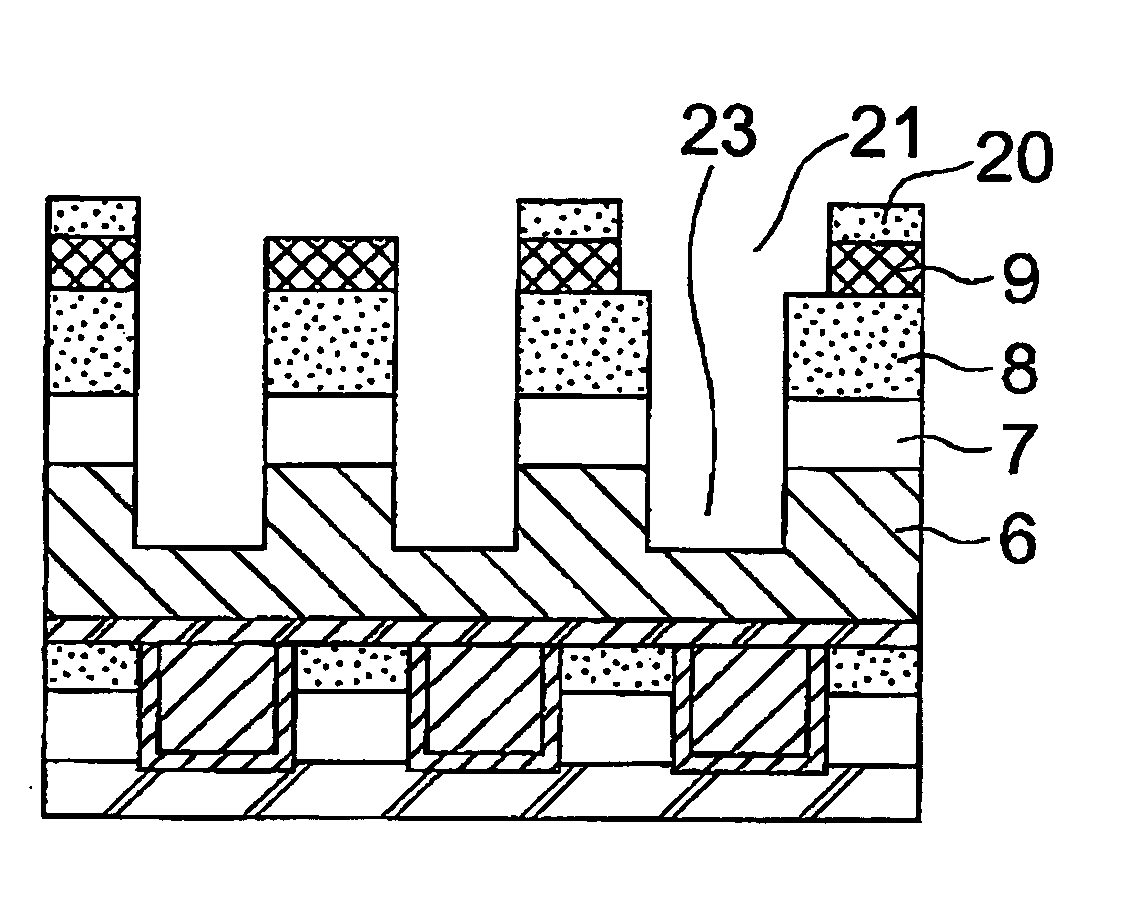

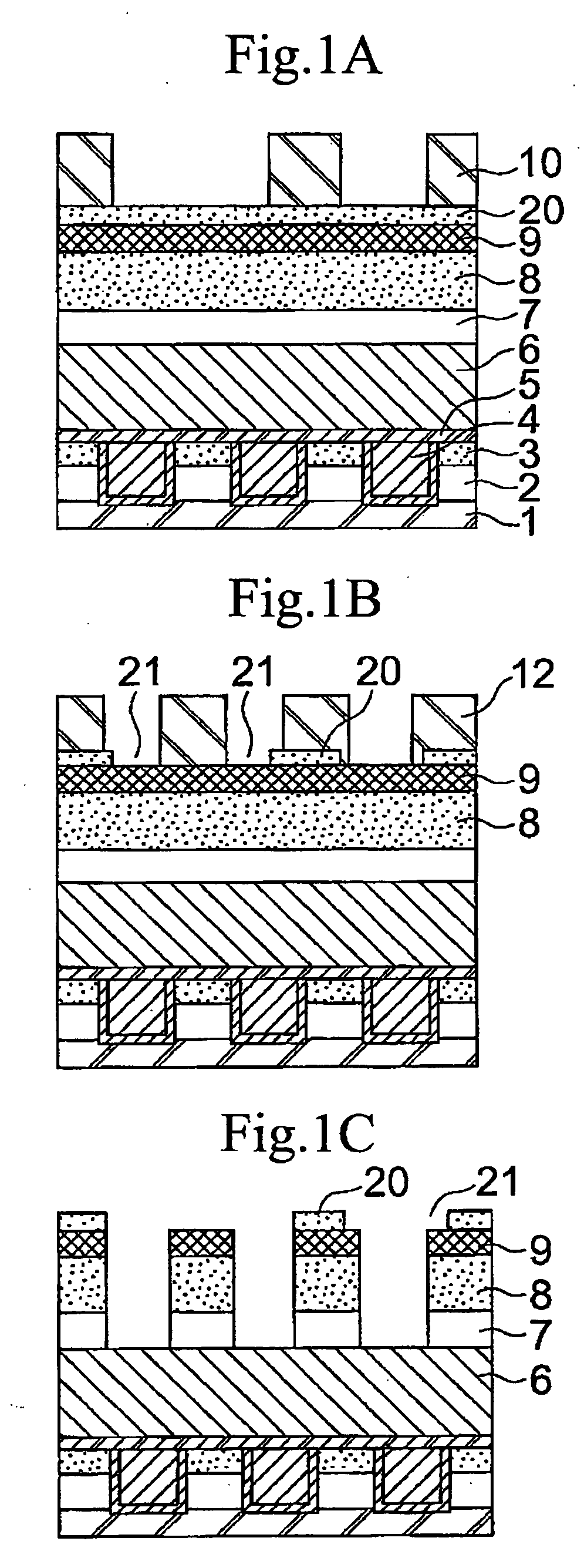

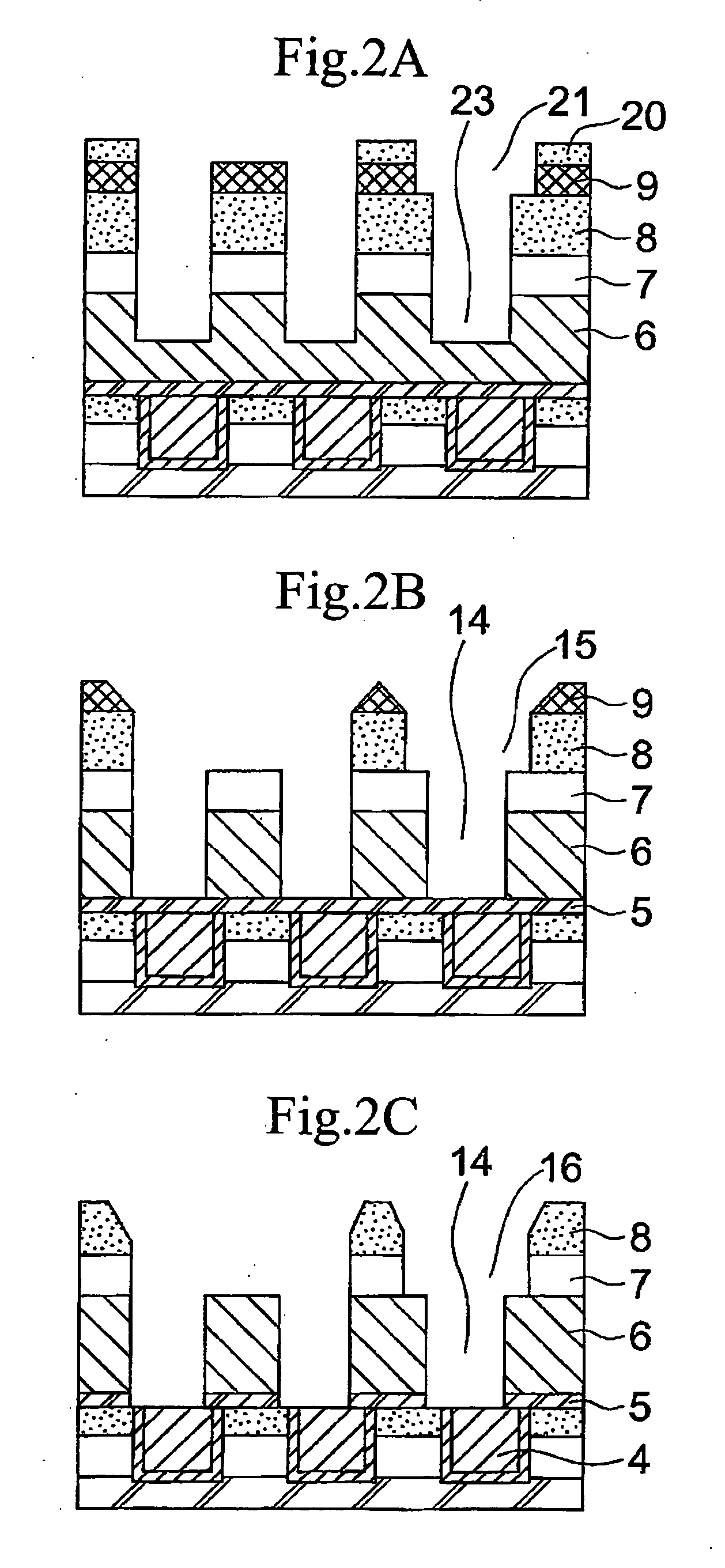

InactiveUS20060166482A1Accurate connectionImproved contact characteristicsSemiconductor/solid-state device manufacturingDevice materialSemiconductor

A process for production of a semiconductor device having a multi-layer wiring of dual damascene structure in a low-dielectric constant interlayer insulating film. The process consists of the following steps. A first insulating film (6) and a second insulating film (7) are formed. A first to third mask forming layers (8), (9), and (20) are formed. The third mask forming layer is patterned so as to form the third mask for the wiring groove pattern. A resist mask of the connecting hole pattern is formed on the second mask forming layer including the third mask. The third mask and the second and first mask forming layers are etched, and the second insulating film is etched. The second mask of the wiring groove pattern is formed by using the third mask, and the connecting hole is made to the middle of the first insulating film. The first mask forming layer is etched by using the second mask, and the first mask of the wiring groove pattern is formed, and the first insulating film remaining at the bottom of the connecting hole is etched so as to make the connecting hole. The wiring groove is formed in the second insulating film by using the first or second mask.

Owner:SONY CORP

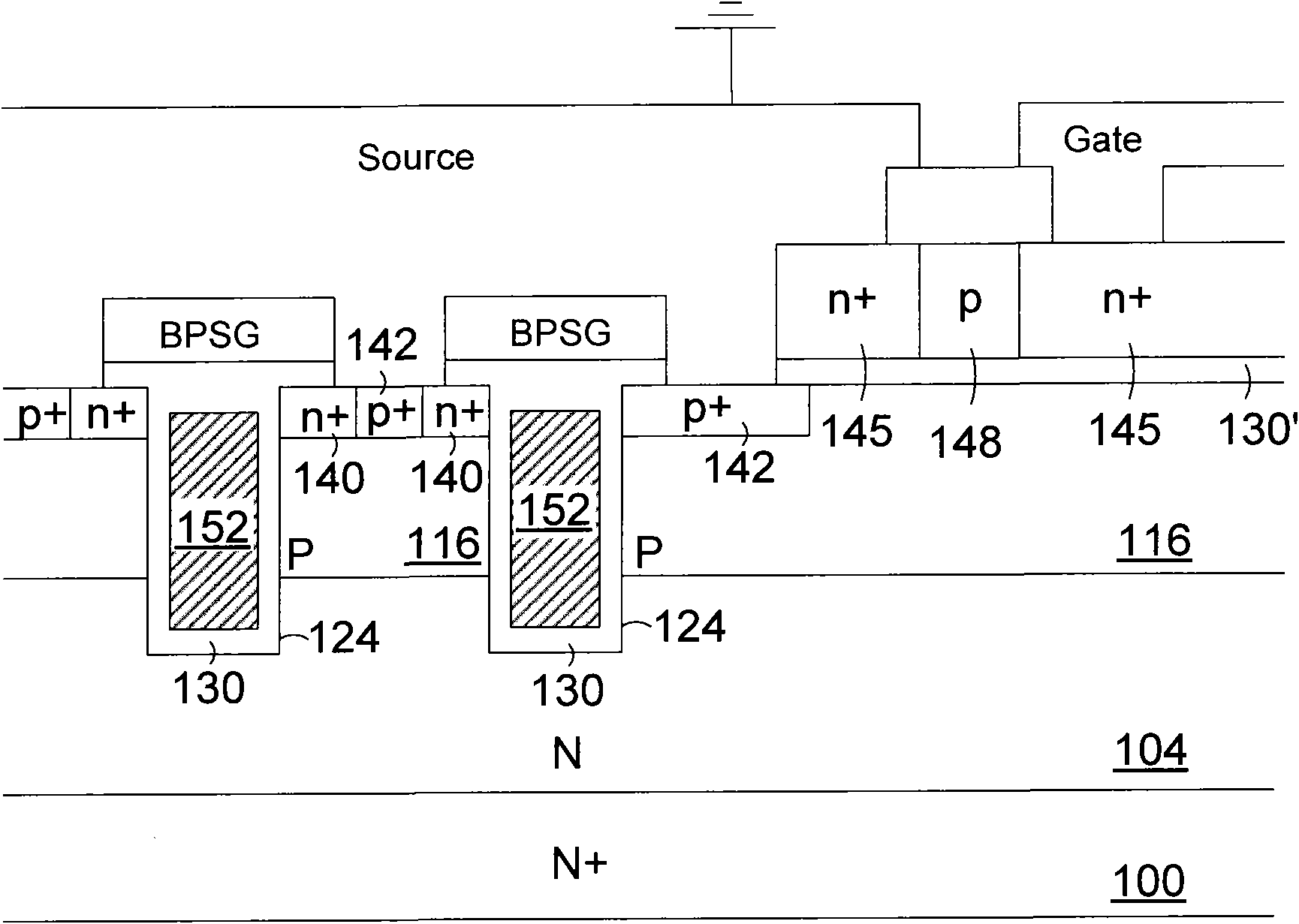

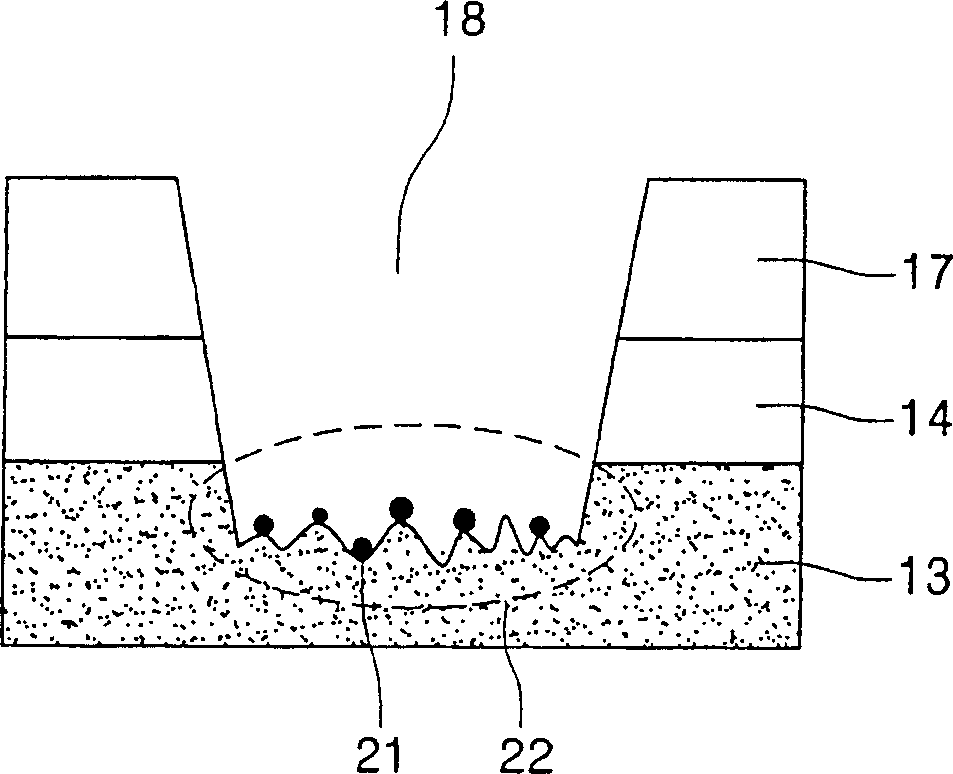

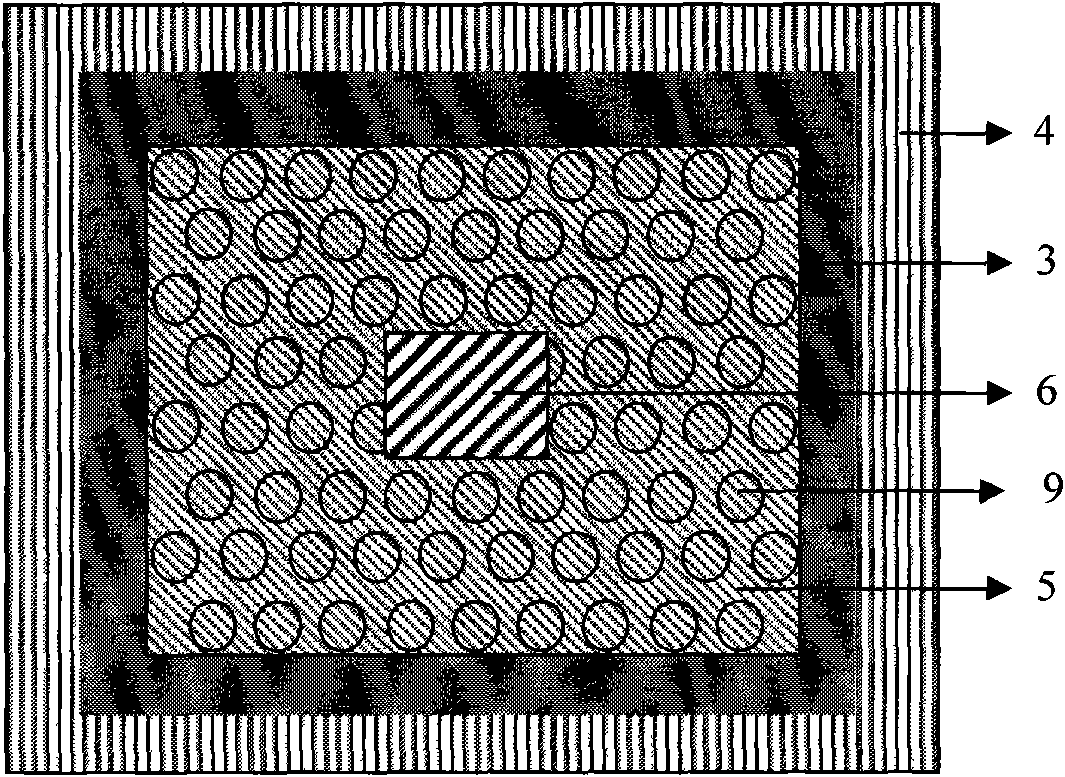

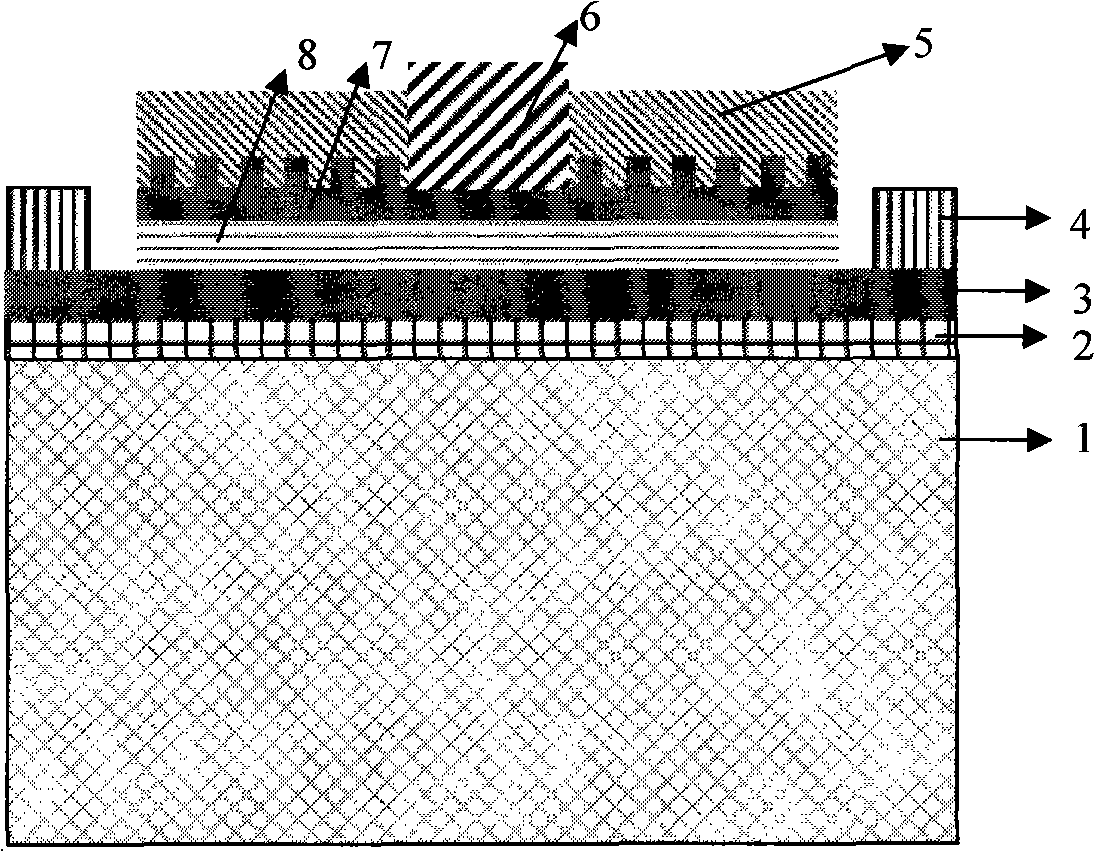

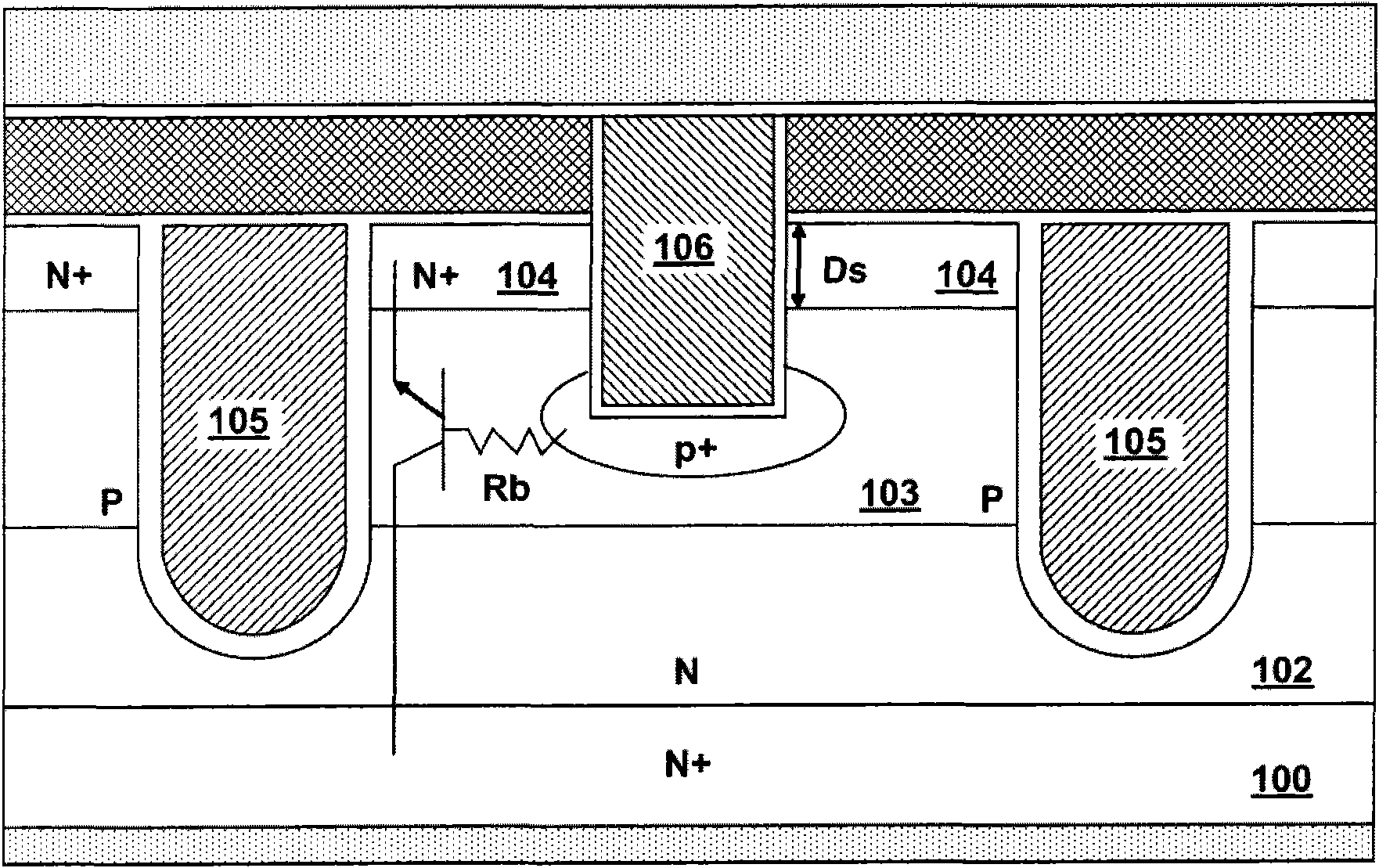

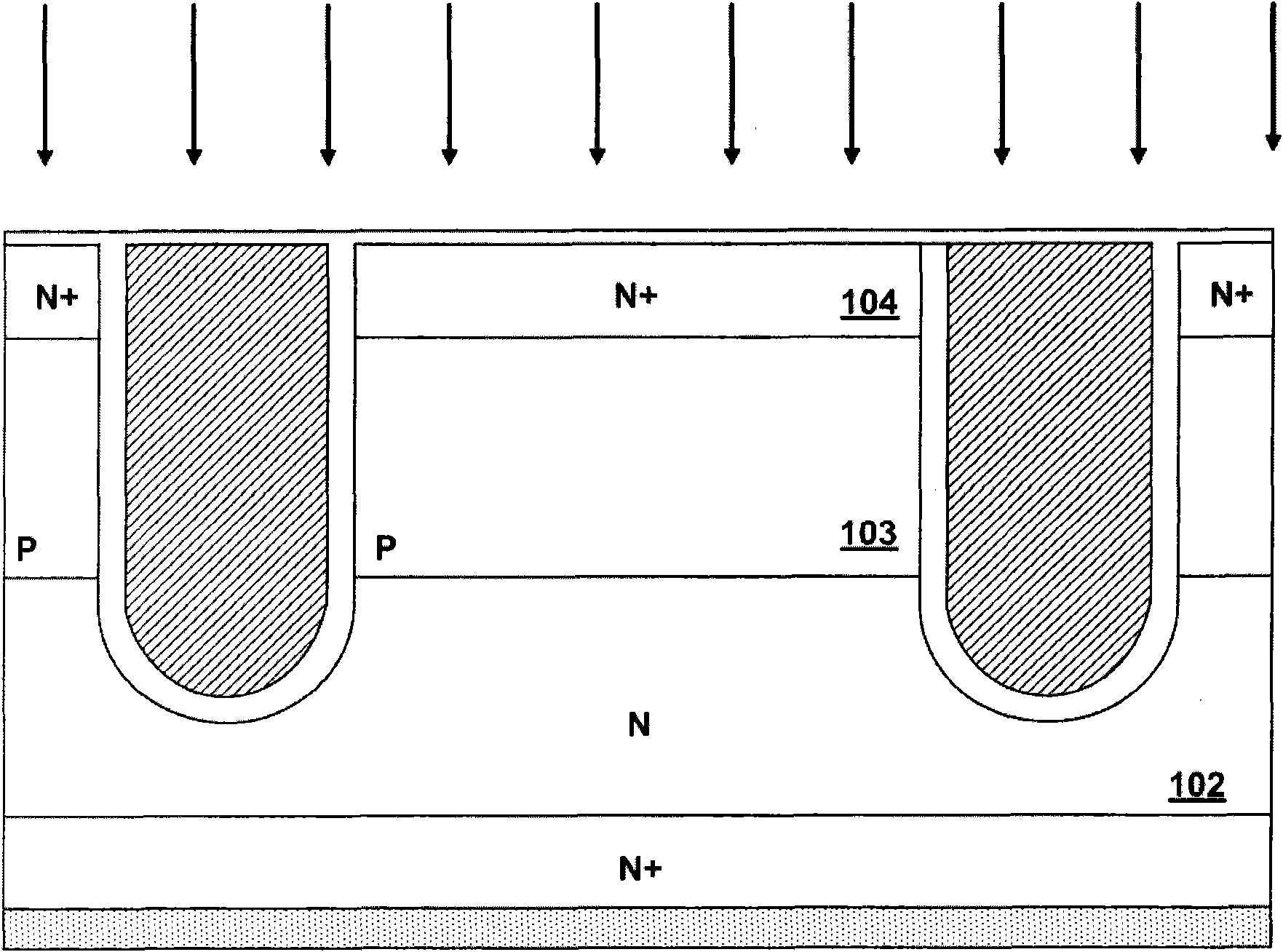

Trench metal-oxide semiconductor field effect transistor (MOSFET) and manufacture method thereof

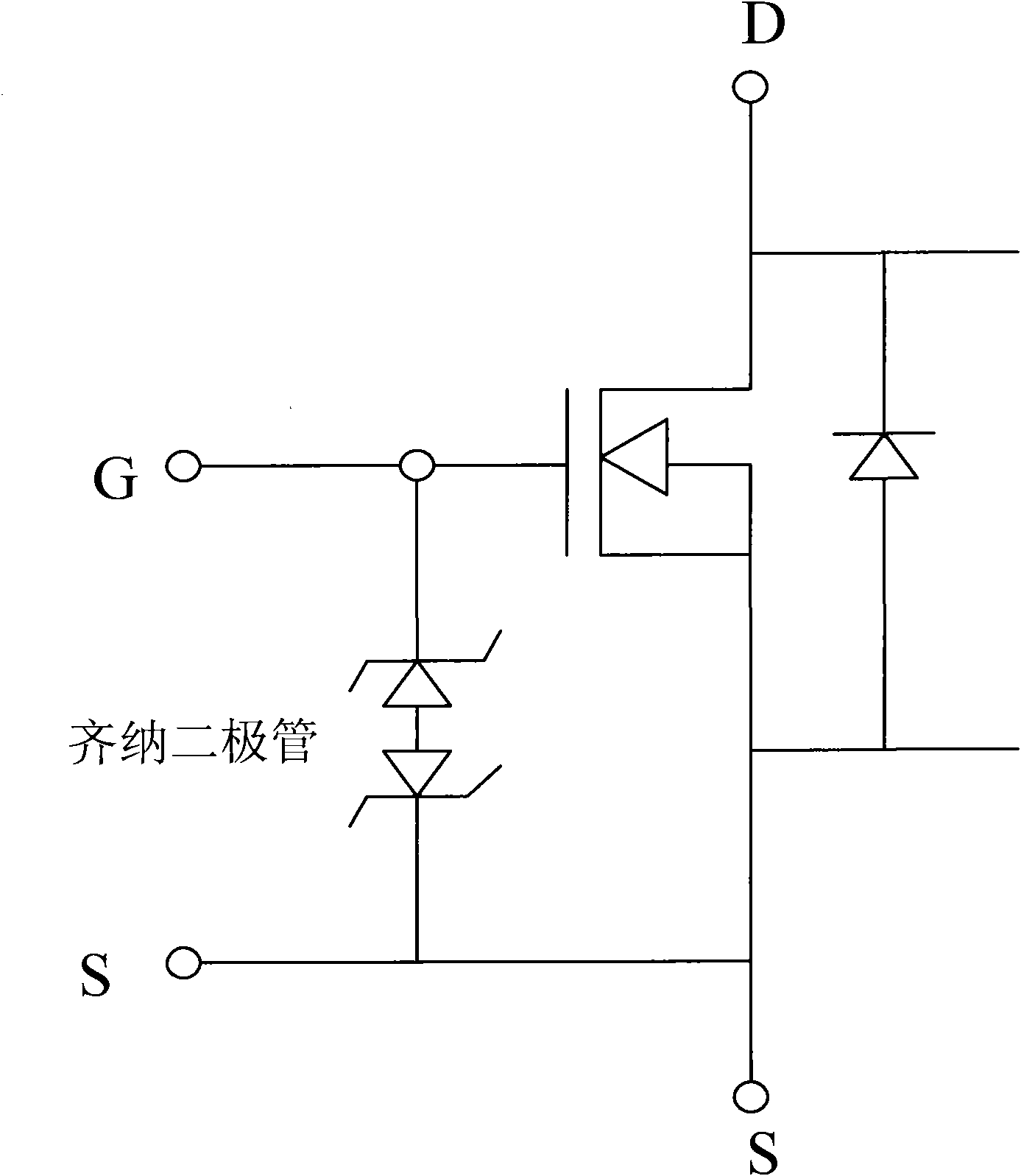

InactiveCN102097433AImproved contact characteristicsAvoid shortingSemiconductor/solid-state device detailsSolid-state devicesTrench mosfetEngineering

The invention discloses a trench metal-oxide semiconductor field effect transistor (MOSFET) and a manufacture method thereof. The trench MOSFET comprises ESD (Electro-Static Discharge) protection diodes, and a trench grid arranged below each ESD contact trench is used as a buffer layer to avoid the short circuit between a source electrode and a grid electrode.

Owner:FORCE MOS TECH CO LTD

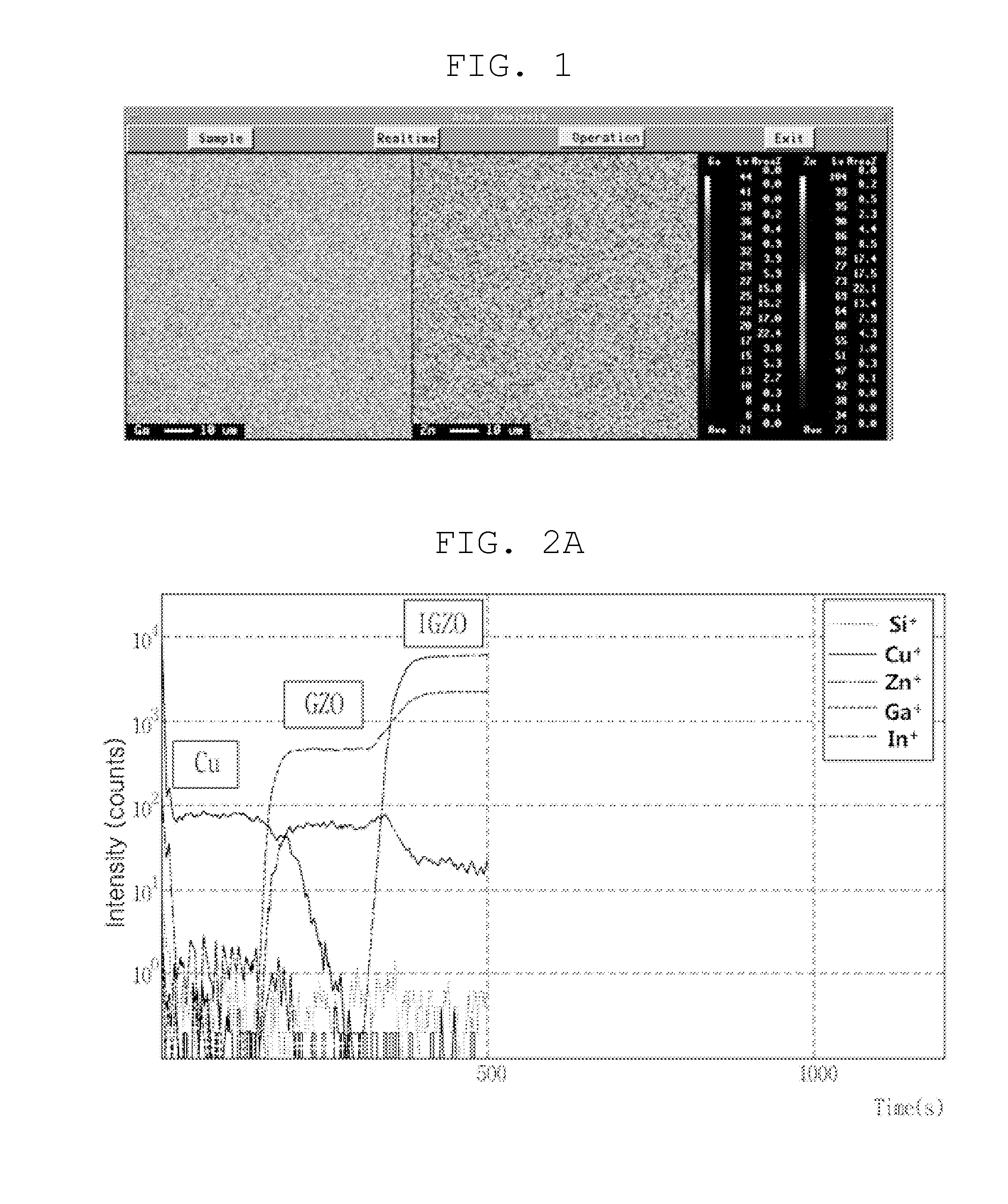

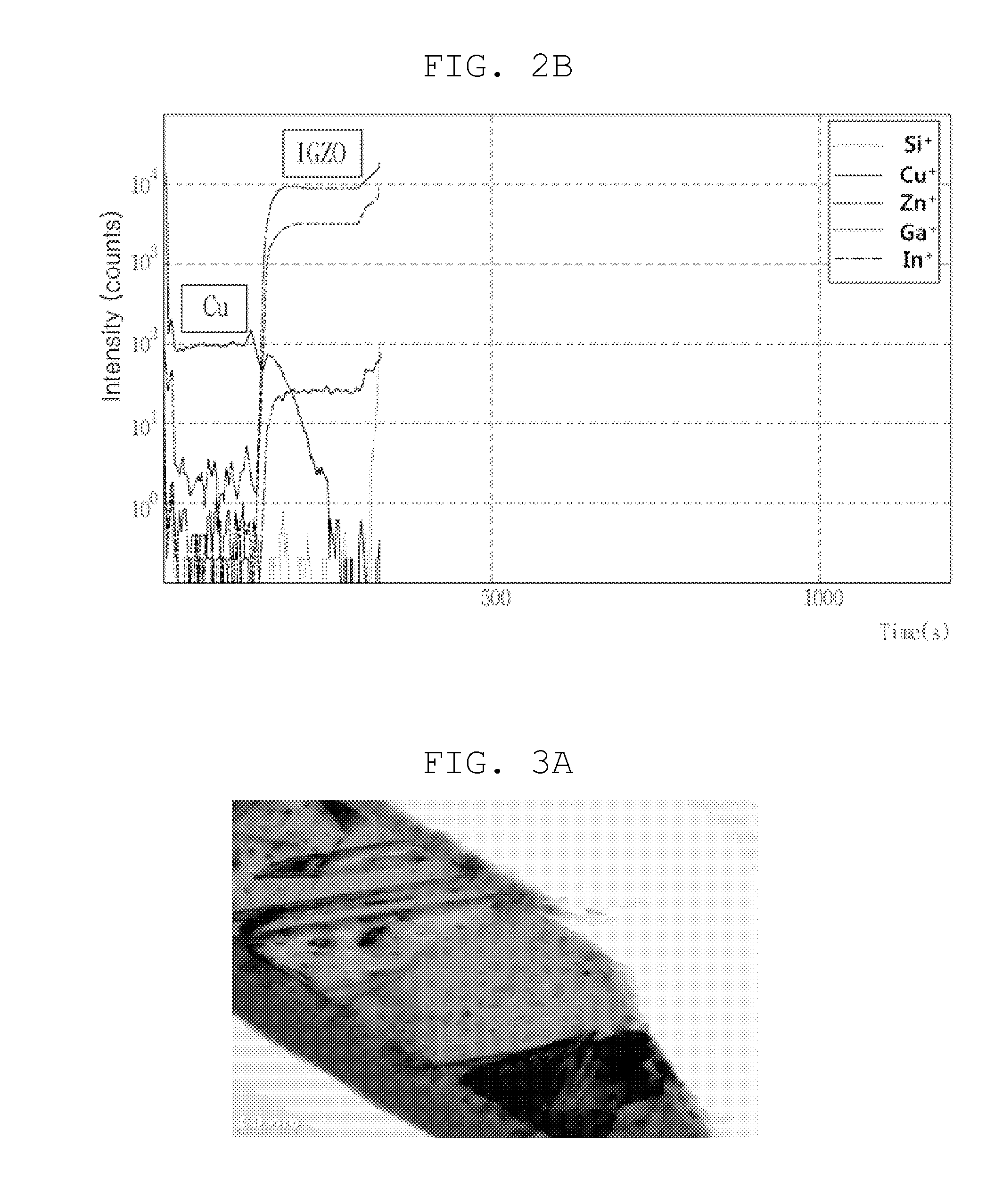

Zinc oxide-based sputtering target, method of manufacturing the same, and thin-film transistor having barrier layer deposited using the same

InactiveUS20130341181A1Improve contact characteristicHigh transmittanceCellsVacuum evaporation coatingZincOxide

A zinc oxide (ZnO)-based sputtering target, a method of manufacturing the same, and a thin-film transistor (TFT) having a barrier layer deposited using the same. The zinc oxide-based sputtering target includes a sinter containing zinc oxide doped with gallium oxide, the content of the gallium oxide ranging, by weight, from 10 to 50 percent of the sinter, and a backing plate bonded to the rear surface of the sinter to support the sinter. The zinc oxide-based sputtering target can be subjected to direct current (DC) sputtering, and improve the contact and etching characteristics of a barrier layer that is deposited using the same.

Owner:SAMSUNG DISPLAY CO LTD +2

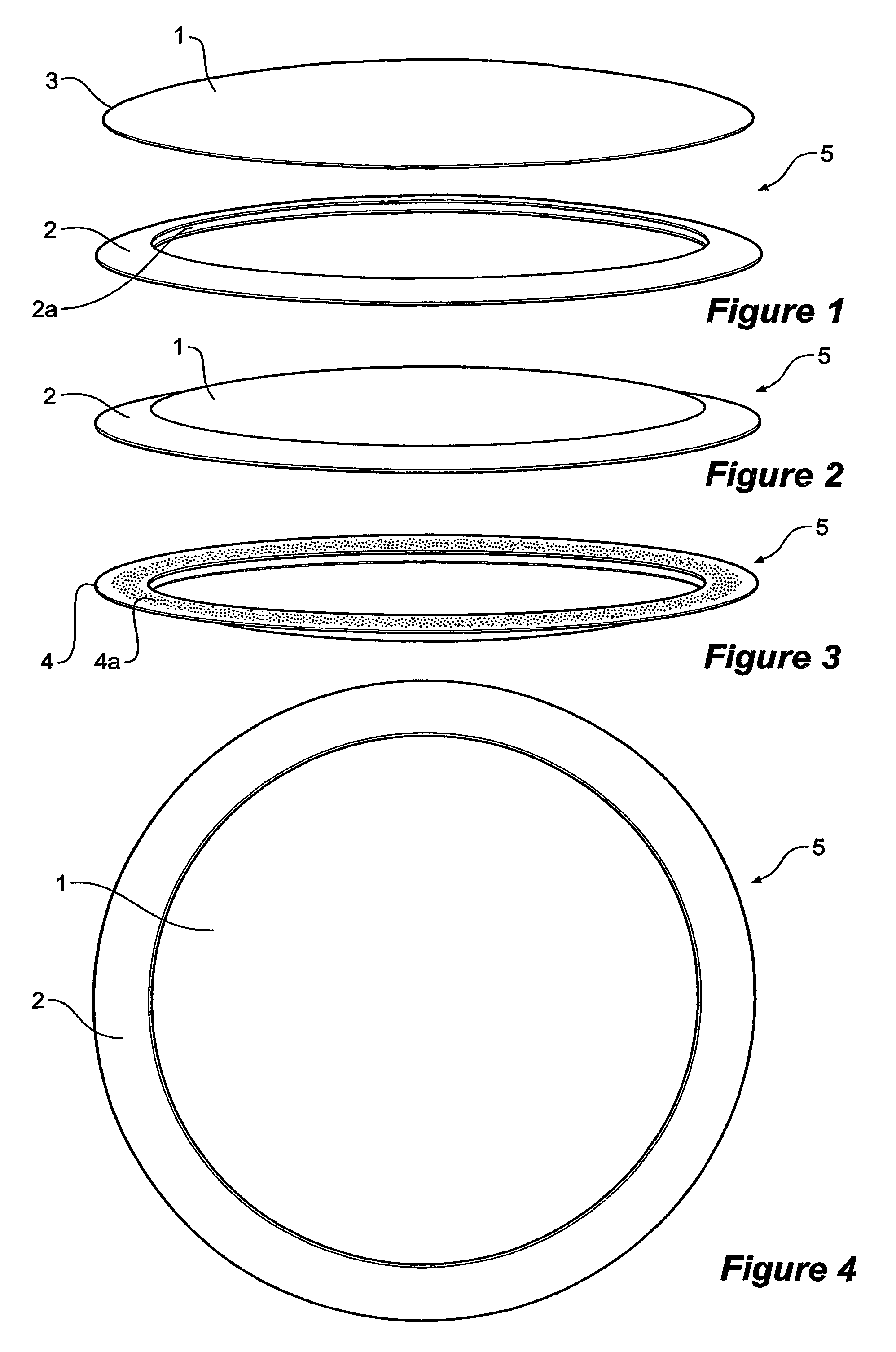

Switch element

InactiveUS7381913B2Avoid overextensionImproved contact characteristicsContact surface shape/structureMovable contactsSurface mountingConductive materials

A switch element for surface mounting onto a printed circuit board which has a bearer element (2) and a contact element (1). Both the bearer element and the contact element are formed from an electrically conductive material and the contact element being formed from a resilient material. The bearer element and the contact element can be of an integral construction or are separate components assembled together. By this construction the bearer element comprises a peripheral retainer for the contact element. In one arrangement the bearer element has an inwardly facing C-shaped cross sectional shape to provide a recess to act as a peripheral retainer for the contact element by receiving at least a portion of the rim of the contact element in the C-shaped member recess.

Owner:SJOSTROM PHILIP ADRIAN

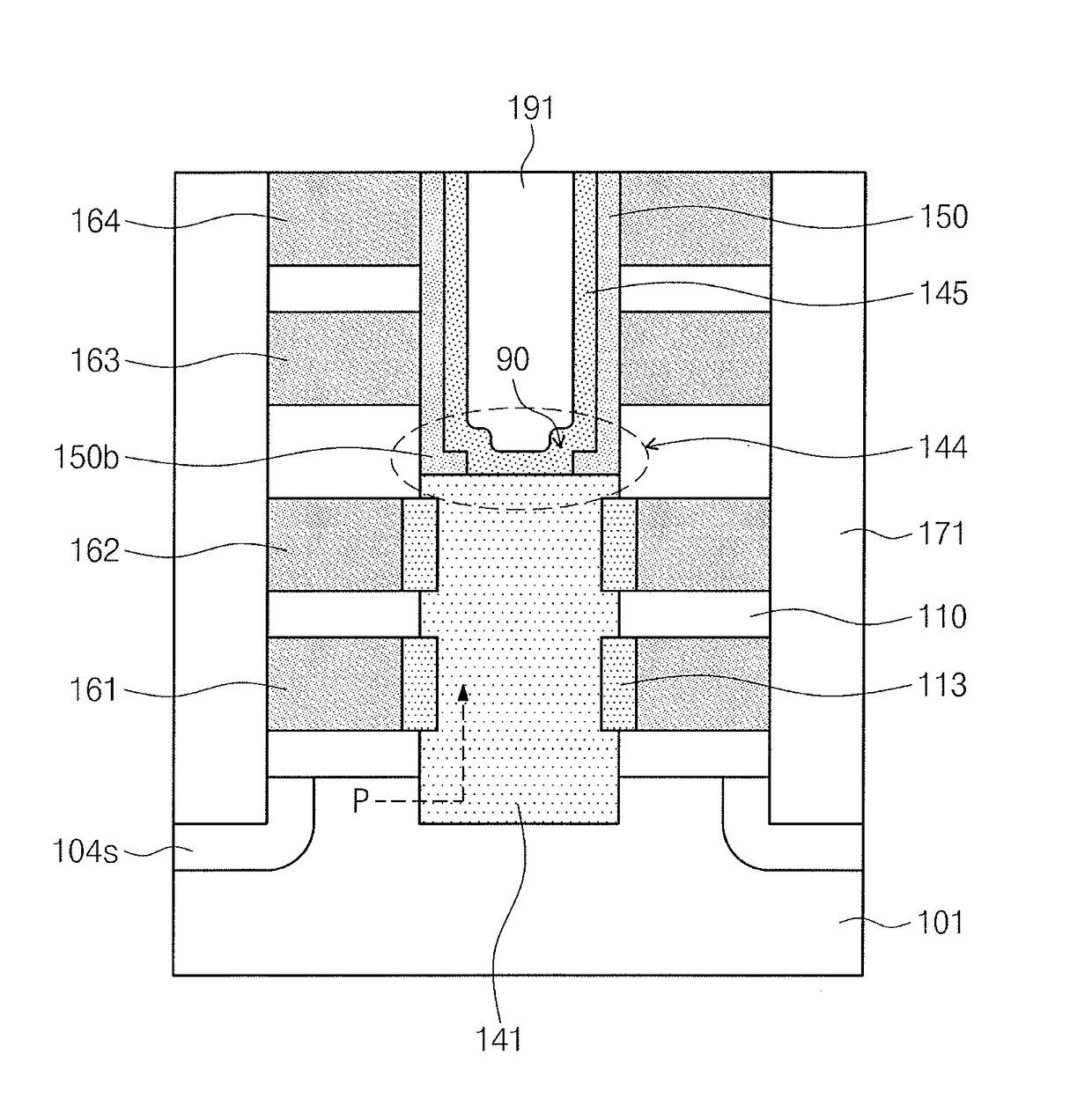

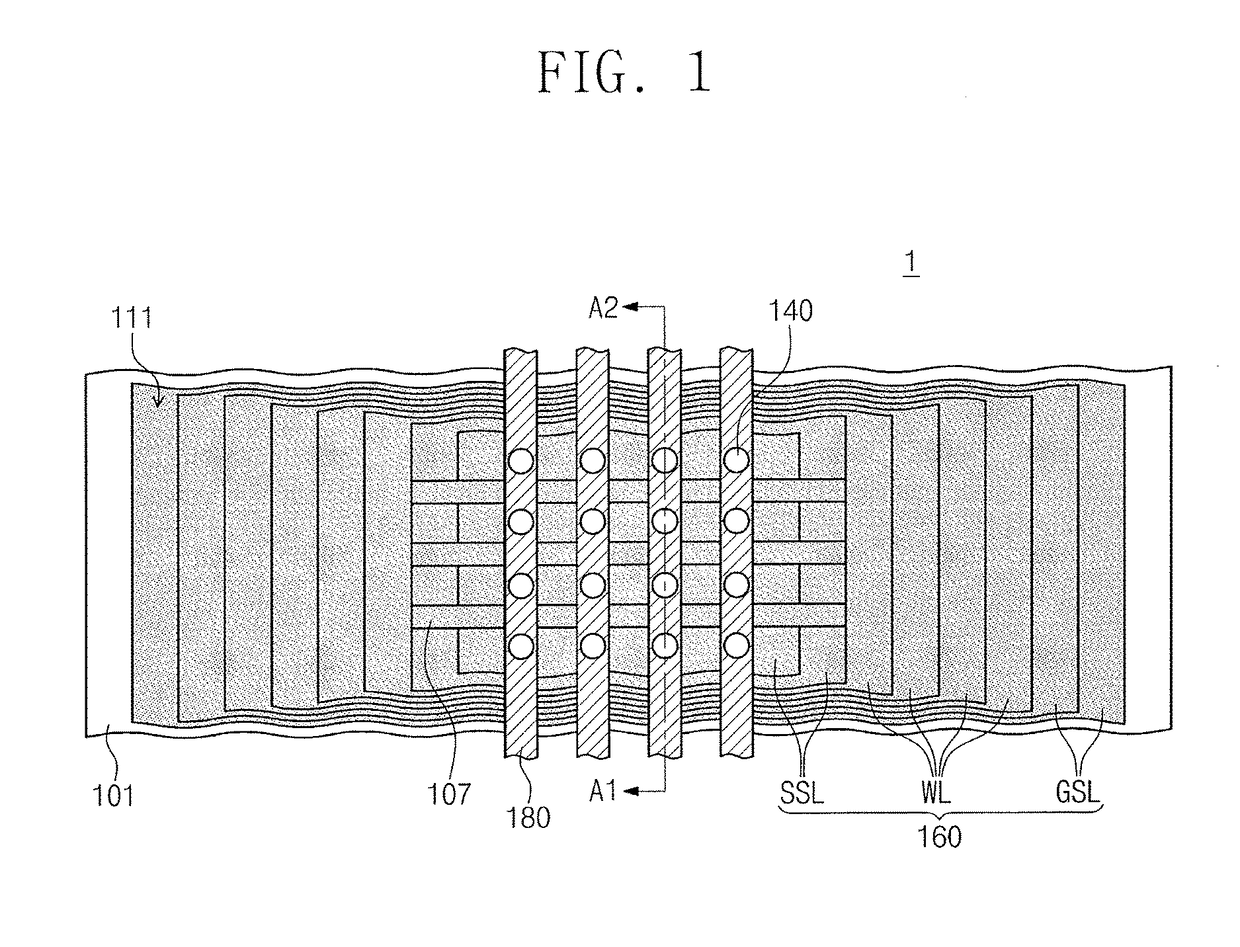

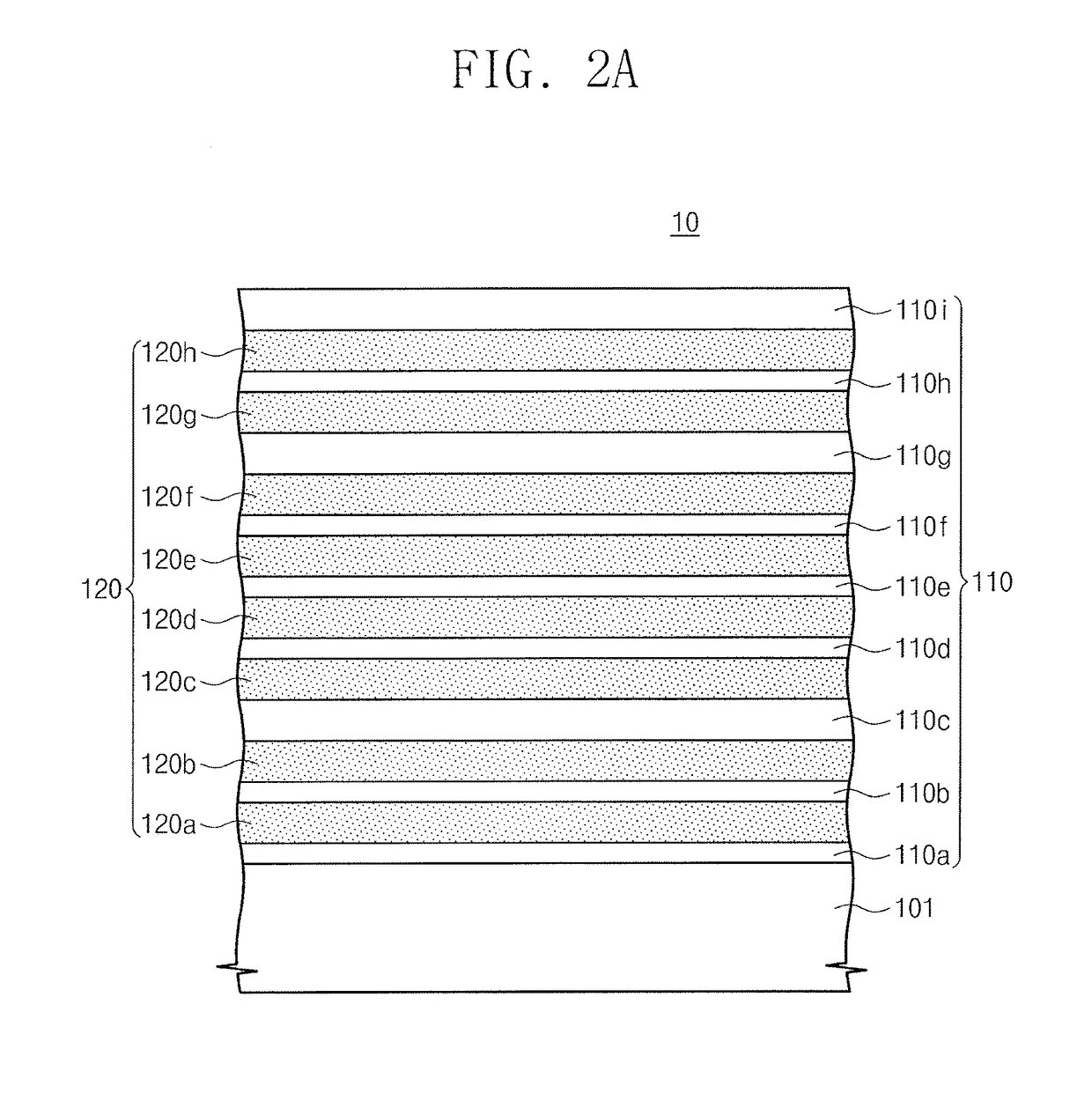

Semiconductor memory devices and methods for fabricating the same

ActiveUS20170287929A1Excellent electrical propertiesContact characteristicSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringVertical channel

The inventive concepts provide semiconductor memory devices and methods for fabricating the same. The semiconductor memory device may include a plurality of gates vertically stacked on a substrate, a vertical channel filling a channel hole vertically penetrating the plurality of gates, and a memory layer vertically extending on an inner sidewall of the channel. The vertical channel may include a lower channel filling a lower region of the channel hole and electrically connected to the substrate, and an upper channel filling an upper region of the channel hole and contacting the lower channel. The upper channel may extend along the memory layer and the lower channel in the upper region of the channel hole and may have a uniform thickness.

Owner:SAMSUNG ELECTRONICS CO LTD

Test electrode for single unidimensional nano material and fabricating method thereof

InactiveCN1603807AEfficient preparationIncrease flexibilityMaterial analysis by electric/magnetic meansIsolation layerIon beam

This invention discloses a single one-dimension nanometer test electrode and its process method. The electrode comprises the following: a underlay with its thickness at 0.5 to 2 mm; an isolation layer on the underlay with the single one-dimension nanometer material distributing on the isolation layer. The metal electrode comprises electrode wire contacted with the material and connection part as lead wire. This method realizes the single one-dimension nanometer material accurate position on the base plate by use of focus ion beam system with high-resolution rate.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

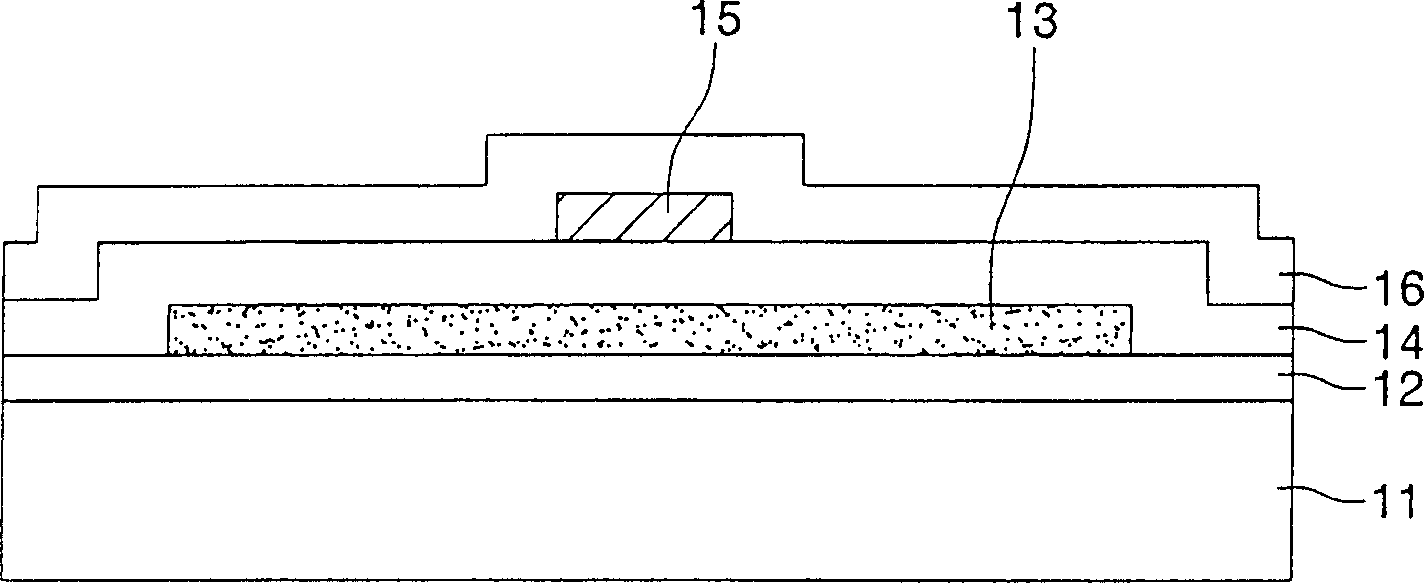

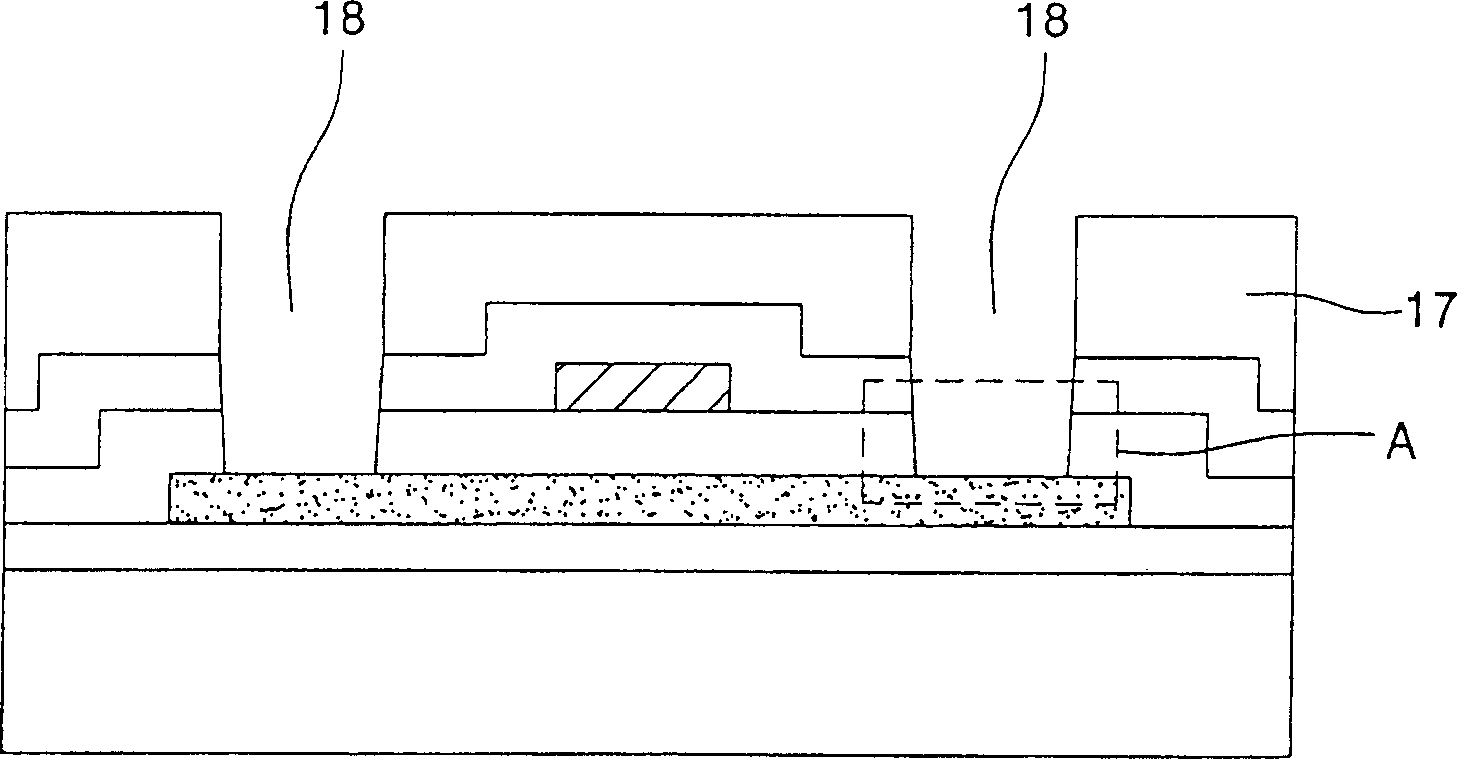

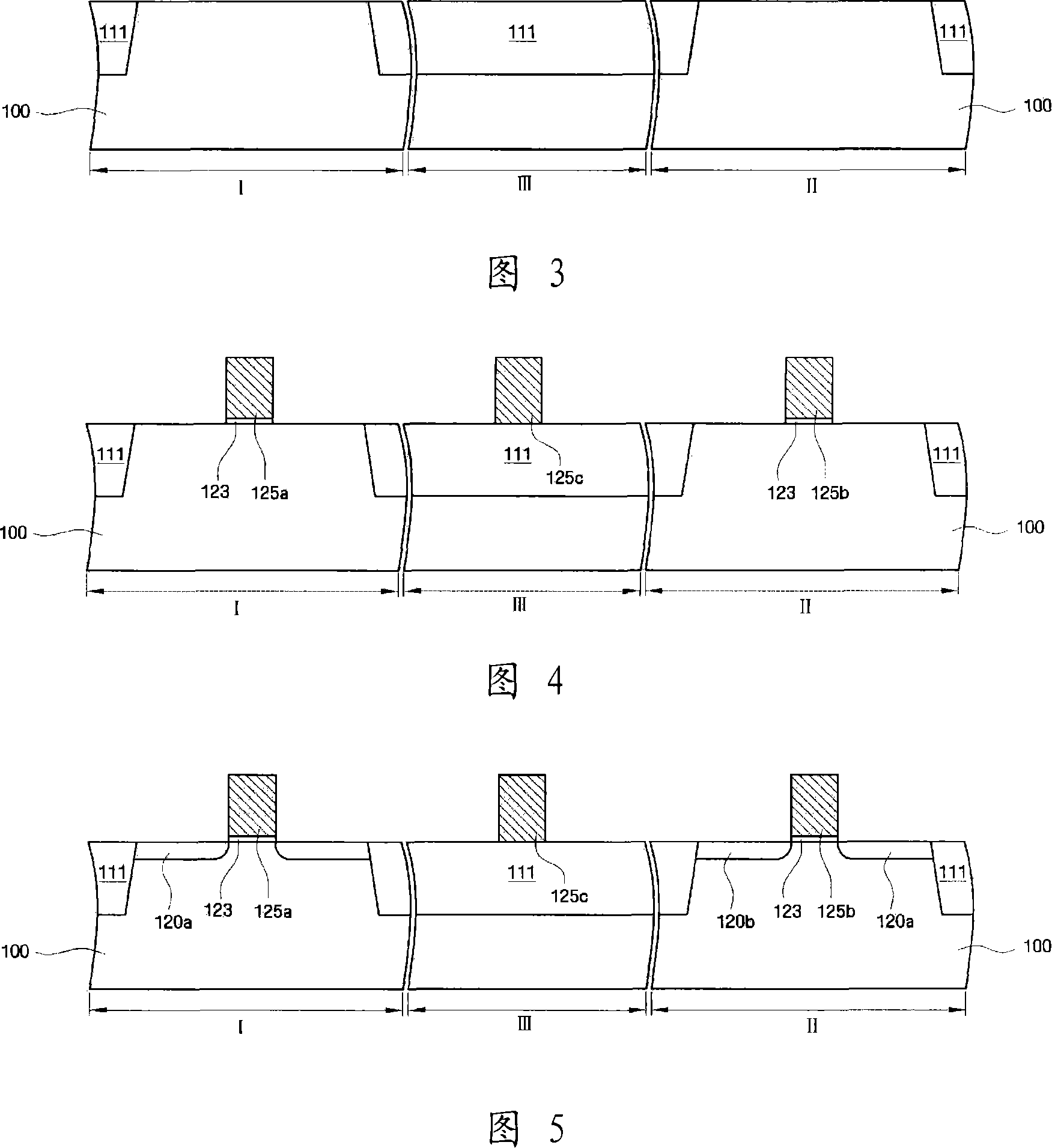

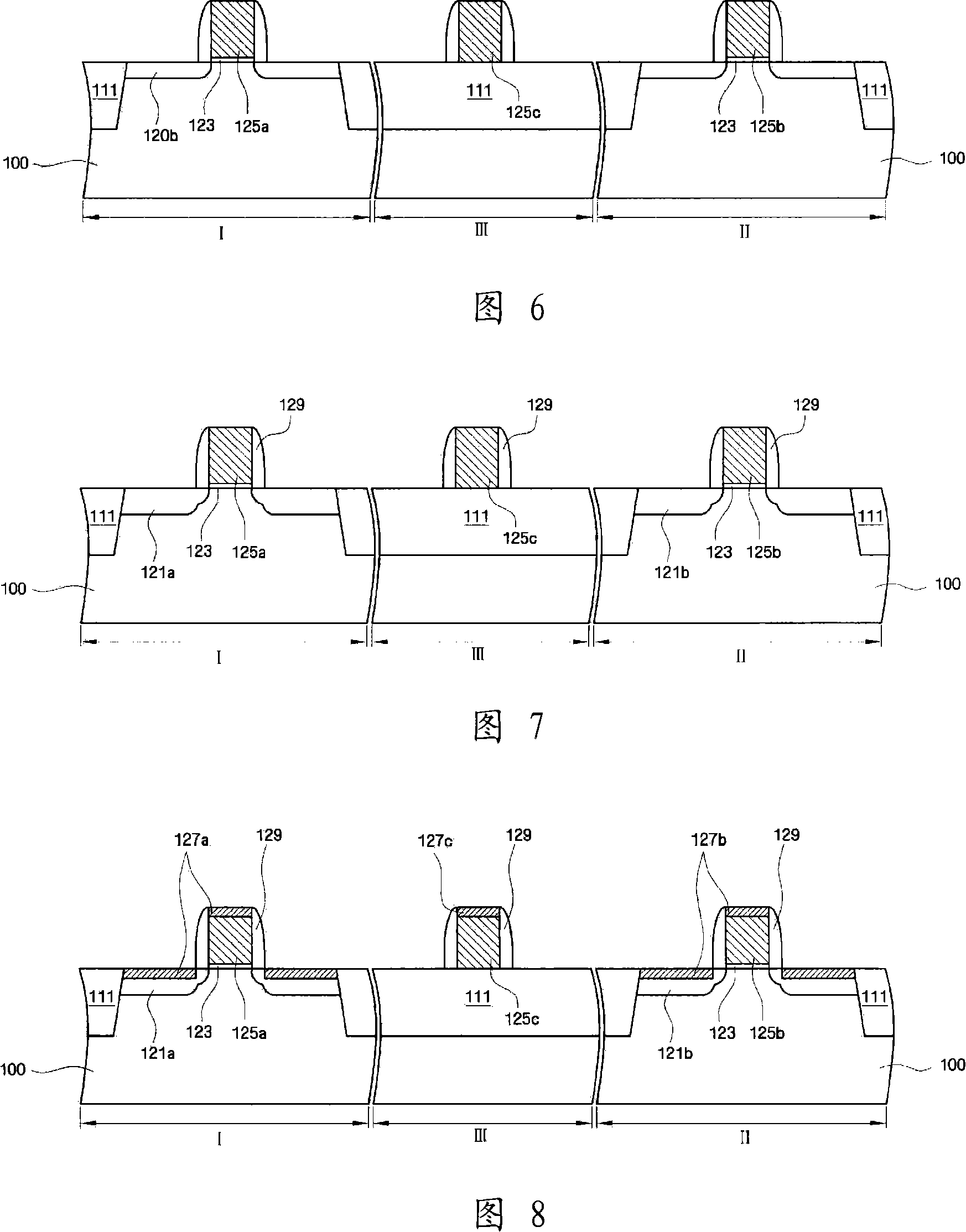

Semiconductor device and method of fabricating the same

ActiveCN1725511AImproved contact characteristicsTransistorSemiconductor/solid-state device detailsCorrosionHigh selectivity

The present invention relates to a semiconductor device and a manufacturing method thereof. When a contact hole of a semiconductor layer and a source and drain electrode, a through-hole of a positive electrode and the source and drain electrode, a through-hole between connecting metal lines or a contact hole of the through-holes, are formed, at least one type of dry-process corrosion of high corrosion rate and high selectivity is used for dry-process corrosion; wet-process corrosion is adopted in the final corrosion treatment, so as to form the contact holes, the through-holes or the contact holes of the through-holes, which are provided with various conical angles and a plurality of contours; residues that are produced by corrosion can be completely eliminated in the wet-process and dry-process treatment; therefore, the contact holes, the through-holes or the contact holes of the through-holes have excellent contact characteristics. The semiconductor device comprises a substrate, a film transistor that is formed on the substrate and is provided with a semiconductor layer, a grid insulation layer, a grid electrode and a interlayer dielectric, and contact holes that penetrates the grid insulation layer and the interlayer dielectric, is exposed on the surface of the semiconductor layer and is provided with a plurality of contours. The upper part of the contact holes is provided with a contour for the wet-process corrosion; and the lower part has at least one of the contours for the wet-process corrosion and the dry-process corrosion.

Owner:SAMSUNG DISPLAY CO LTD

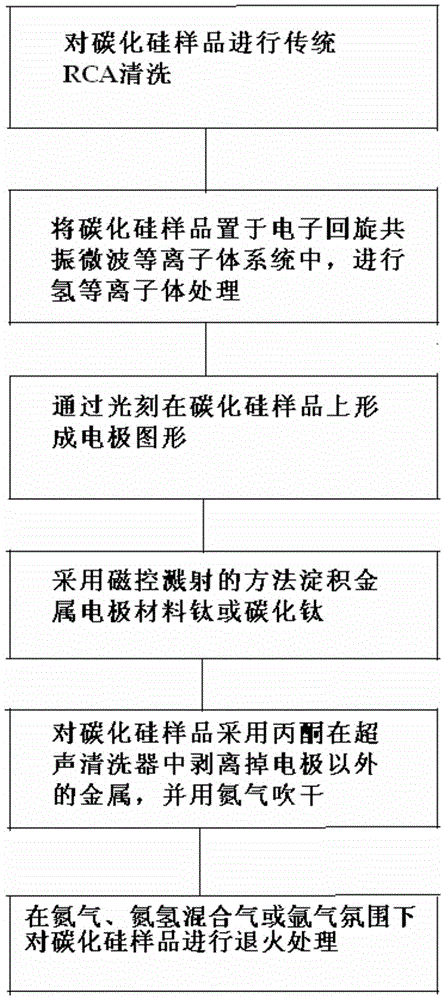

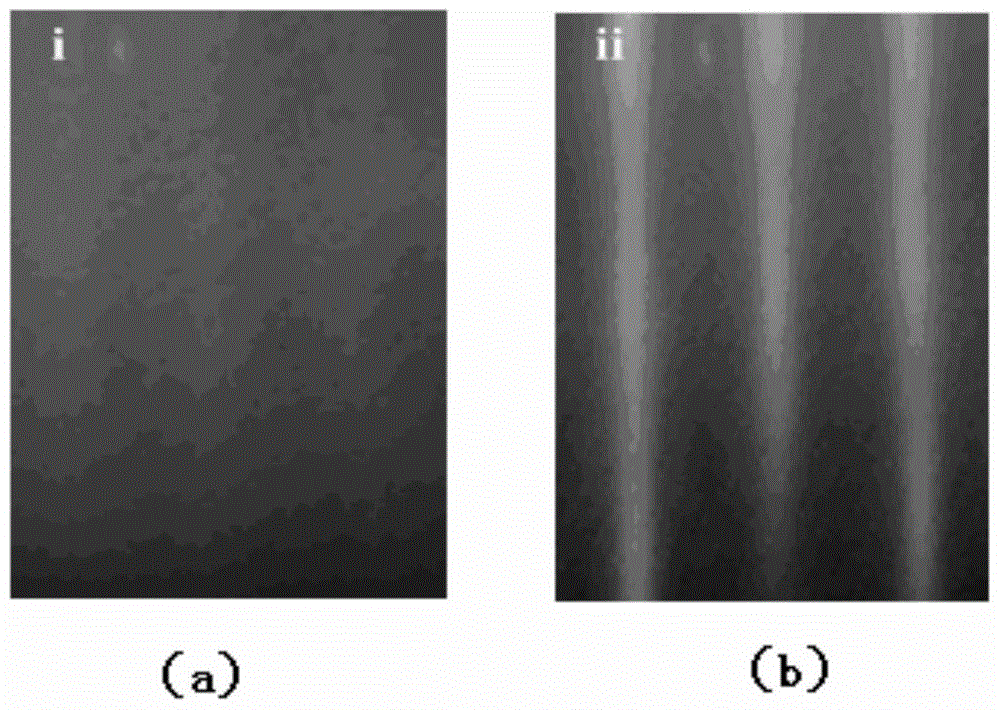

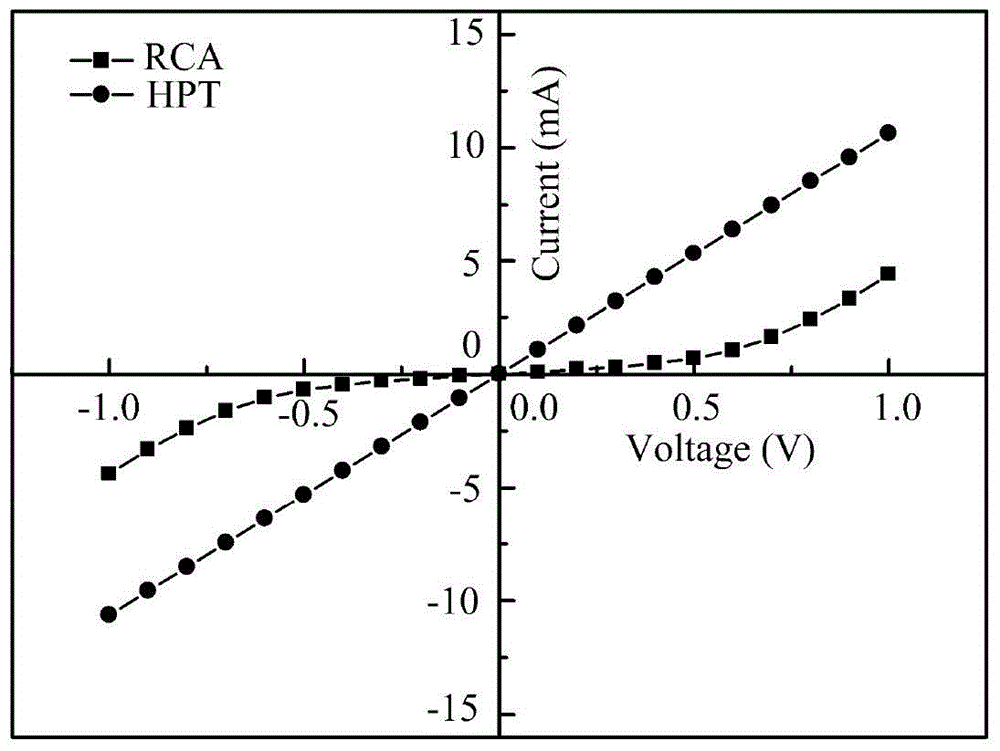

Method for increasing ohmic contact characteristic of silicon carbide semiconductor

InactiveCN105702712AEffective cleaning and passivationDecrease the density of surface statesSemiconductor devicesRCA cleanTitanium carbide

The invention relates to the field of microelectronic technology, a method for improving the ohmic contact characteristics of a silicon carbide semiconductor, comprising the following steps: (1) performing traditional RCA cleaning on a silicon carbide sample; (2) placing the silicon carbide sample in electron cyclotron resonance microwave plasma In the bulk system, hydrogen plasma treatment is carried out; (3) electrode pattern is formed on the silicon carbide sample by photolithography; (4) metal electrode material titanium or titanium carbide is deposited by magnetron sputtering; (5) The silicon sample was stripped of metal other than the electrodes in an ultrasonic cleaner with acetone, and dried with nitrogen; (6) the silicon carbide sample was annealed in a nitrogen atmosphere. In the present invention, after pre-treating the surface of silicon carbide with hydrogen plasma generated by an electron cyclotron resonance system, the surface of silicon carbide is effectively cleaned and passivated, and the surface state density is significantly reduced, and combined with low work function metal titanium or titanium carbide and relatively The silicon carbide substrate with high doping concentration has a low barrier height of Ti / SiC contact, and good ohmic contact can be formed under low temperature annealing conditions.

Owner:DALIAN UNIV OF TECH

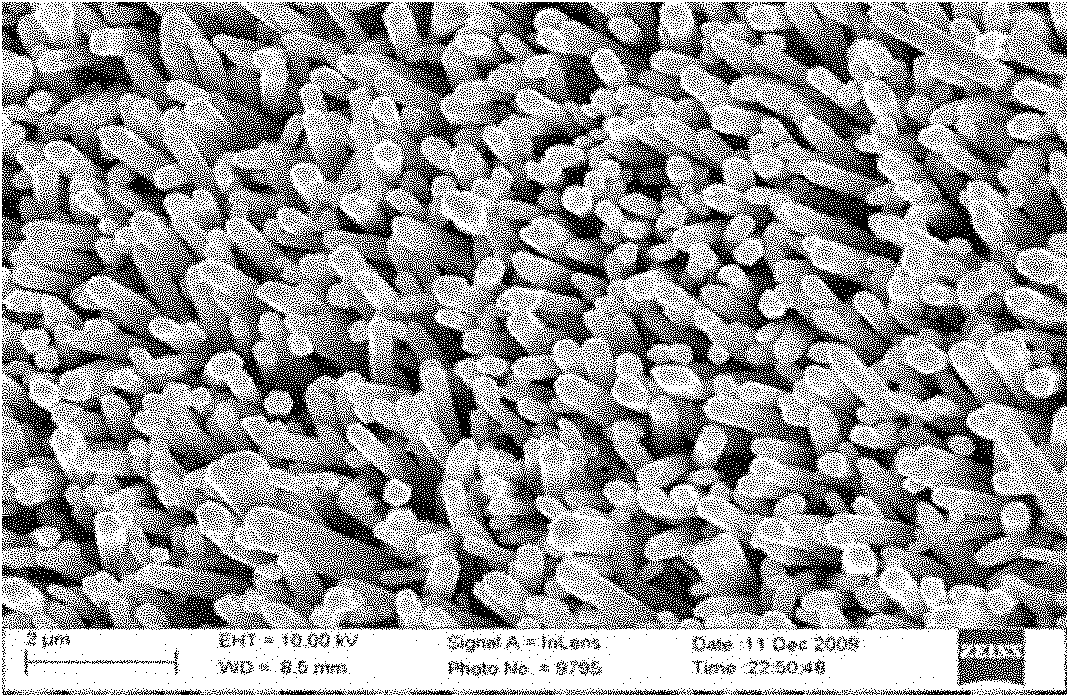

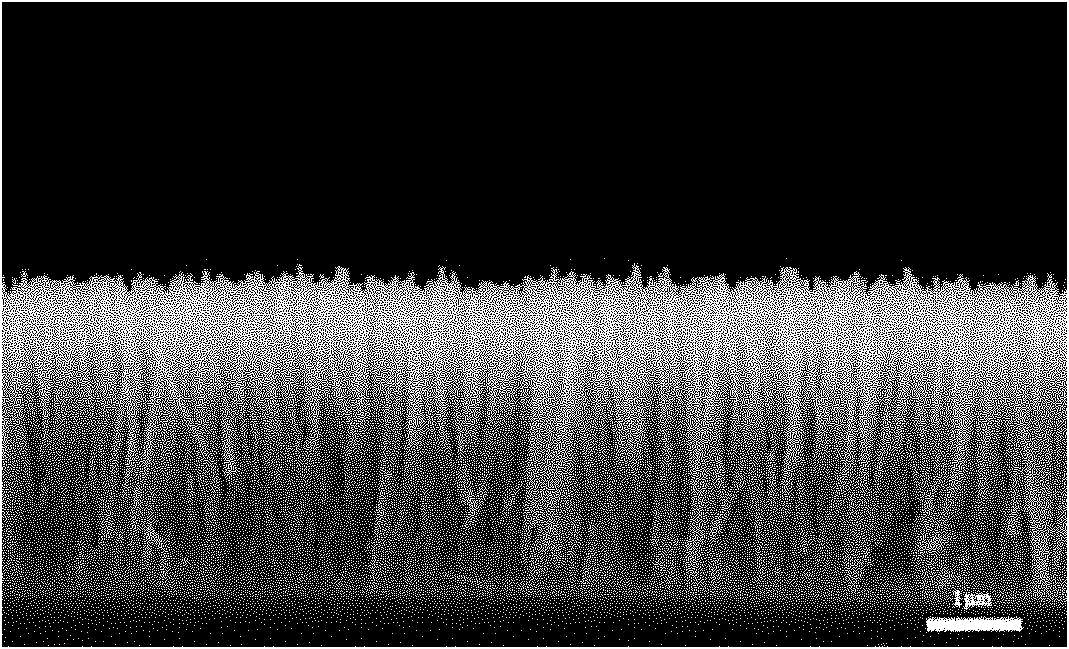

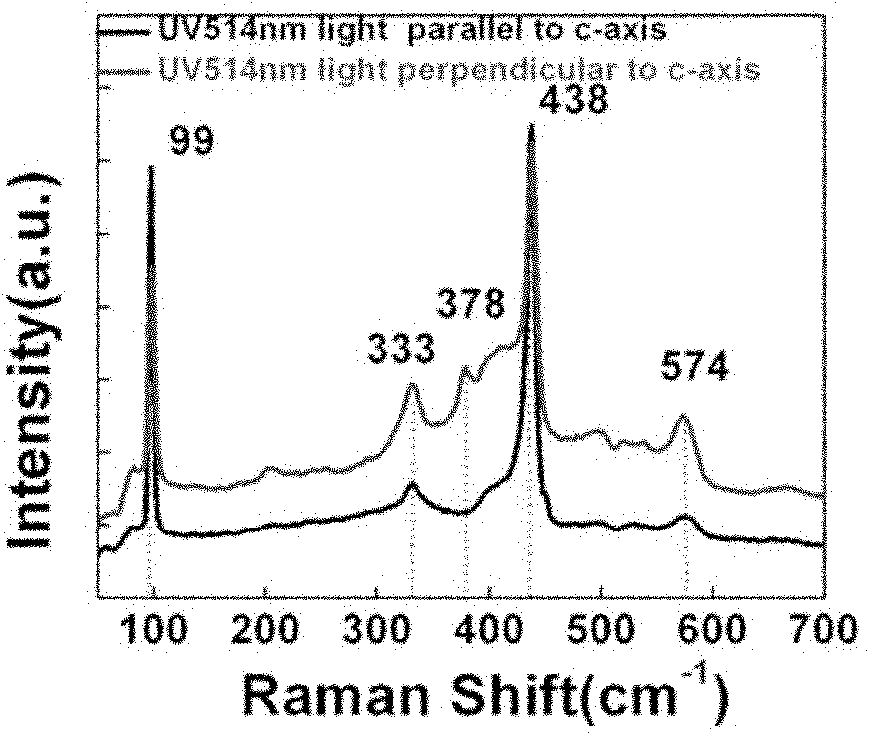

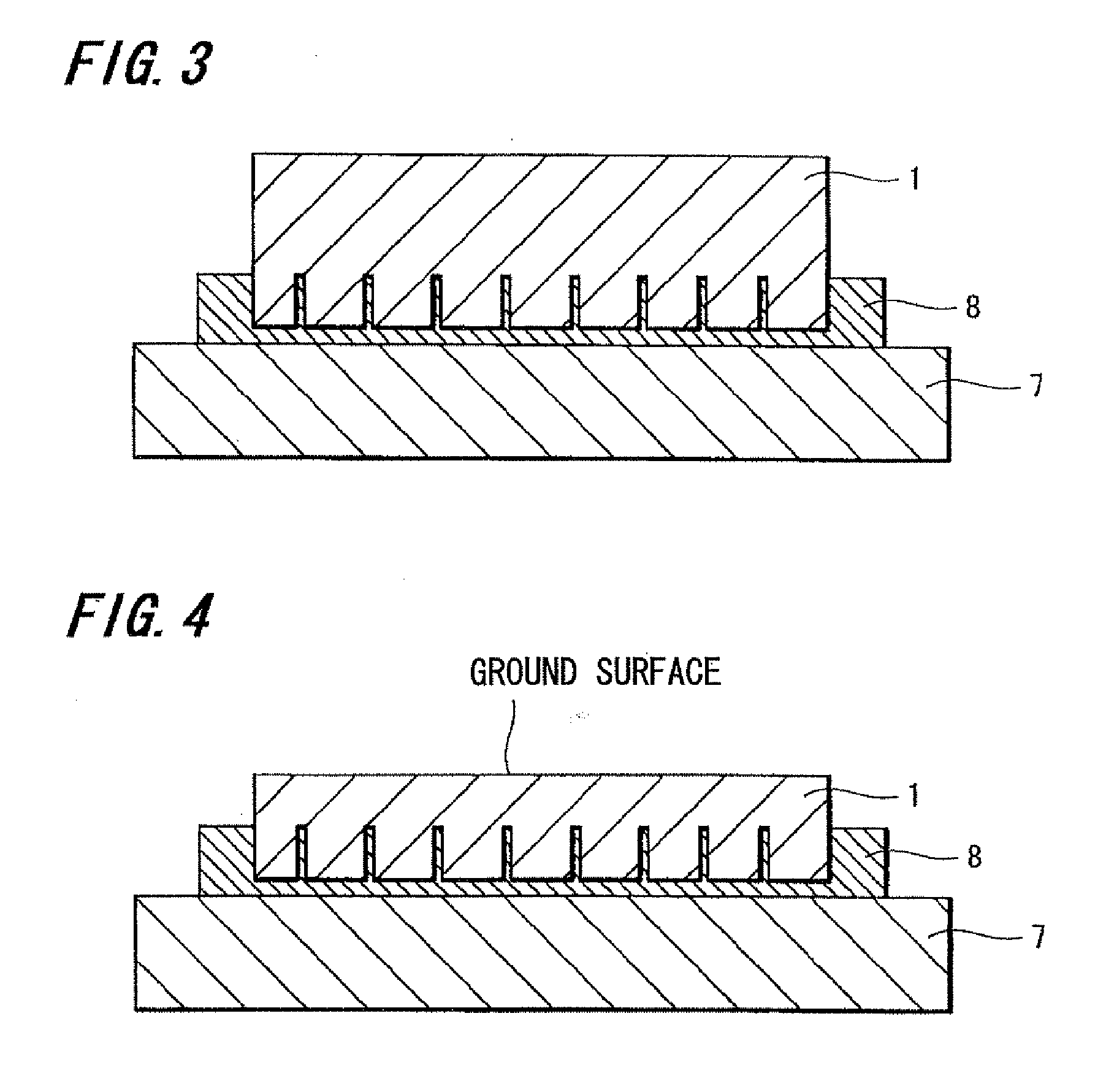

Method for preparing Schottky contact ZnO nano array ultraviolet detection device

InactiveCN102142482APromote absorptionImprove photoelectric response performanceDecorative surface effectsFinal product manufacturePhotoresistFluorine doping

The invention provides a method for preparing a Schottky contact ZnO nano array ultraviolet detection device. The method comprises the following steps of: growing a ZnO nano array on a piece of cleaned fluorine-doped tin oxide (FTO) conductive glass; spinning polymethyl methacrylate (PMMA) photoresist on the well grown ZnO nano array so that the photoresist permeates the gaps of the array; performing pre-drying so that the photoresist is tightly adhered with the array; performing oxygen plasma etching after pre-drying to etch the PMMA photoresist at the end part of the array so as to facilitate electrode deposition of the next step; performing deposition of metal electrodes with thickness of 50 to 100 nanometers by using a vacuum coating machine; performing annealing treatment so that the electrodes are better contacted with the ZnO nano array; and finally, leading out copper leads from the Pt electrode and the FTO electrode to perform a photoelectric performance test. The ultraviolet of the prepared device can be irradiated from the back, and the device has simple structure, low cost and stable performance and provides possibility for later practical application.

Owner:UNIV OF SCI & TECH BEIJING

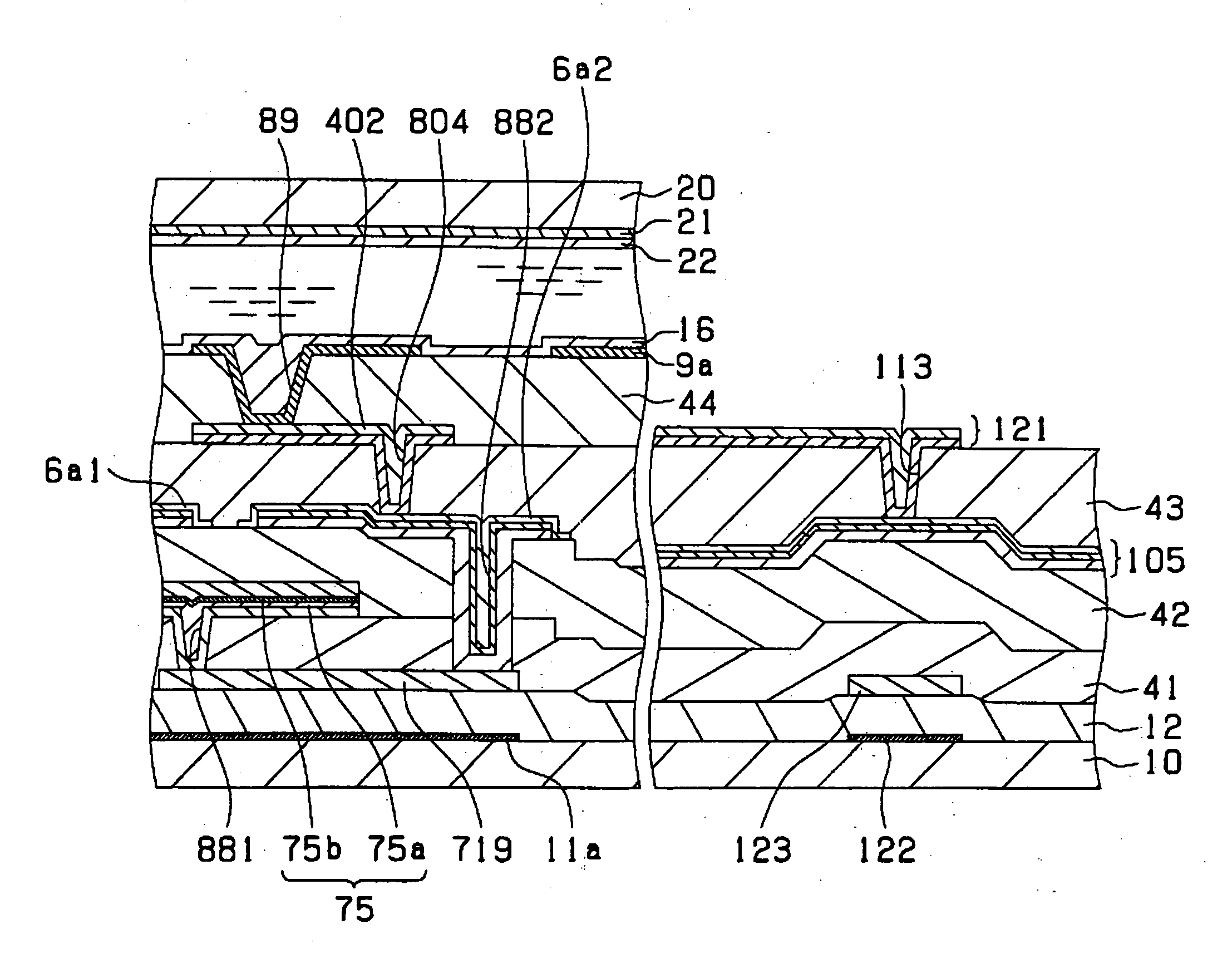

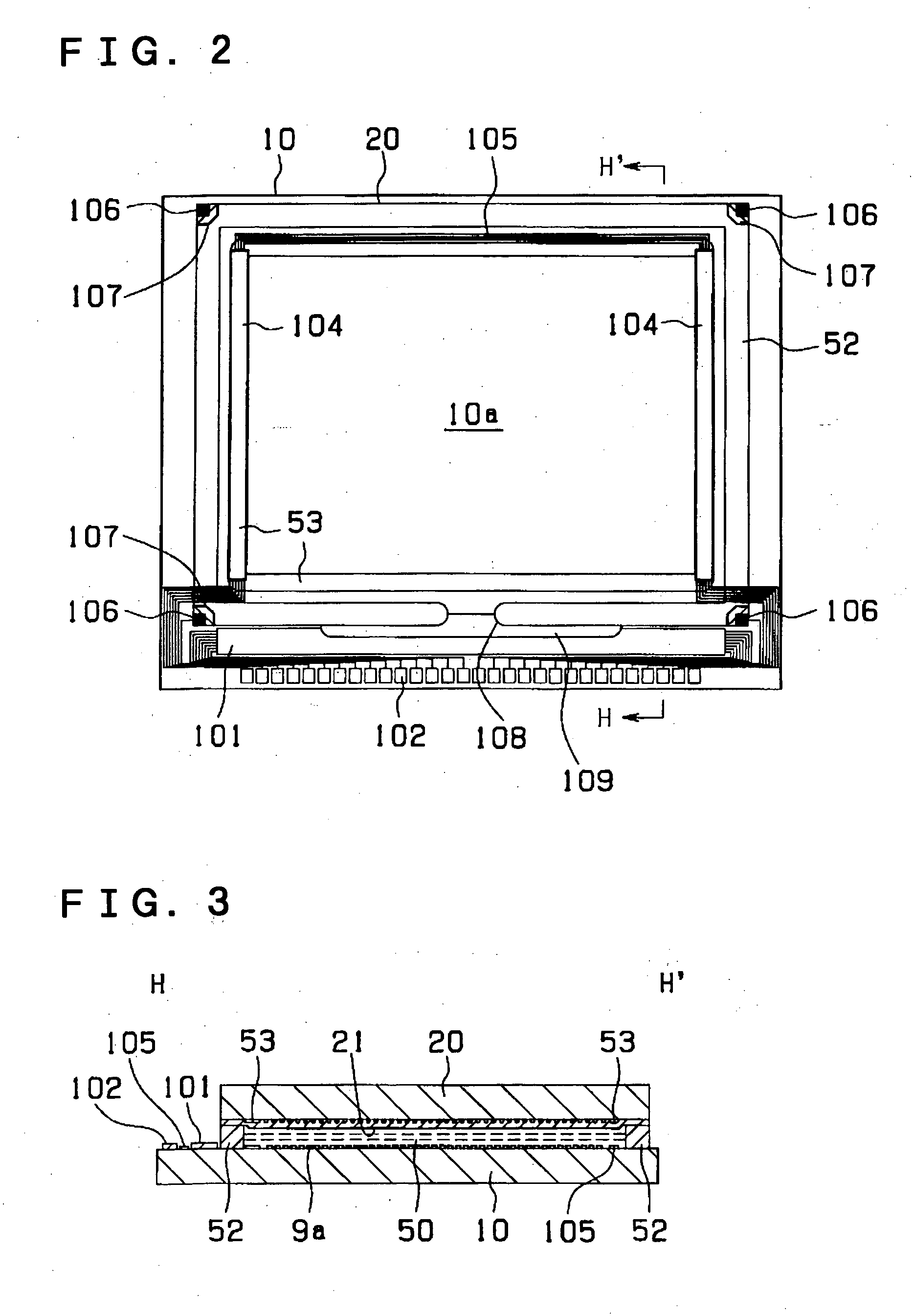

Substrate having a planarization layer and method of manufacture therefor, substrate for electro-optical device, electro-optical device, and electronic apparatus

InactiveUS20040207087A1Uniform openingImproved contact characteristicsTransistorSemiconductor/solid-state device testing/measurementElectrical and Electronics engineeringElectronic equipment

A plurality of film formation layers where film formation patterns are formed, respectively, interlayer films which are formed between the plurality of film formation layers, respectively, a plurality of sub-interlayer-film wiring patterns, which are formed in film formation layers beneath the planarized interlayer films of the interlayer films, a plurality of contact holes formed in the planarized interlayer films in order to connect the plurality of sub-interlayer-film wiring patterns and the film formation patterns of layers above the planarized interlayer films, and one or more dummy patterns which are formed on a plurality of positions under the plurality of contact holes and which are formed in one or more film formation layers under the plurality of sub-interlayer-film wiring patterns, respectively so as to control the positions of the surfaces of the plurality of sub-interlayer-film wiring patterns.

Owner:SEIKO EPSON CORP

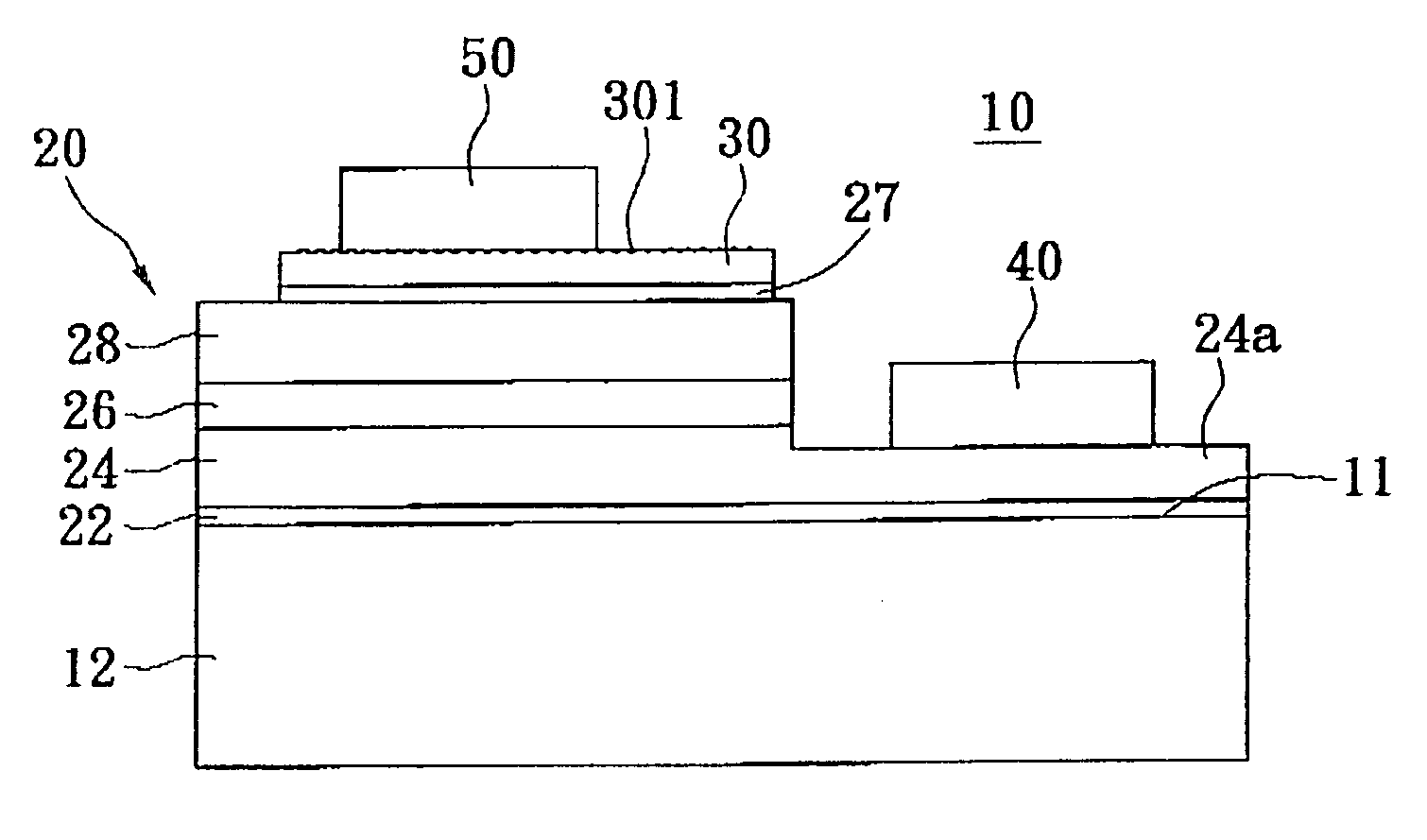

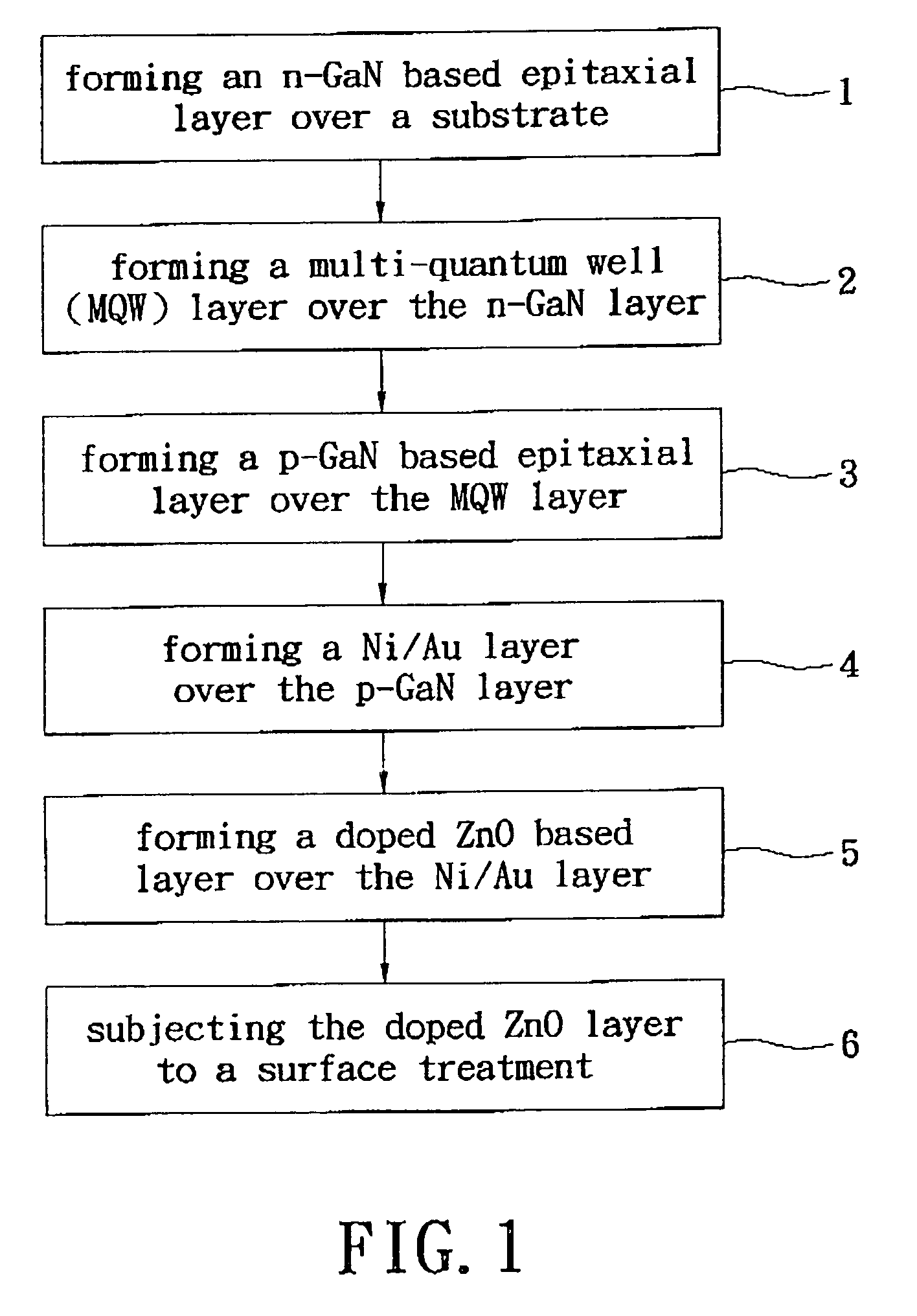

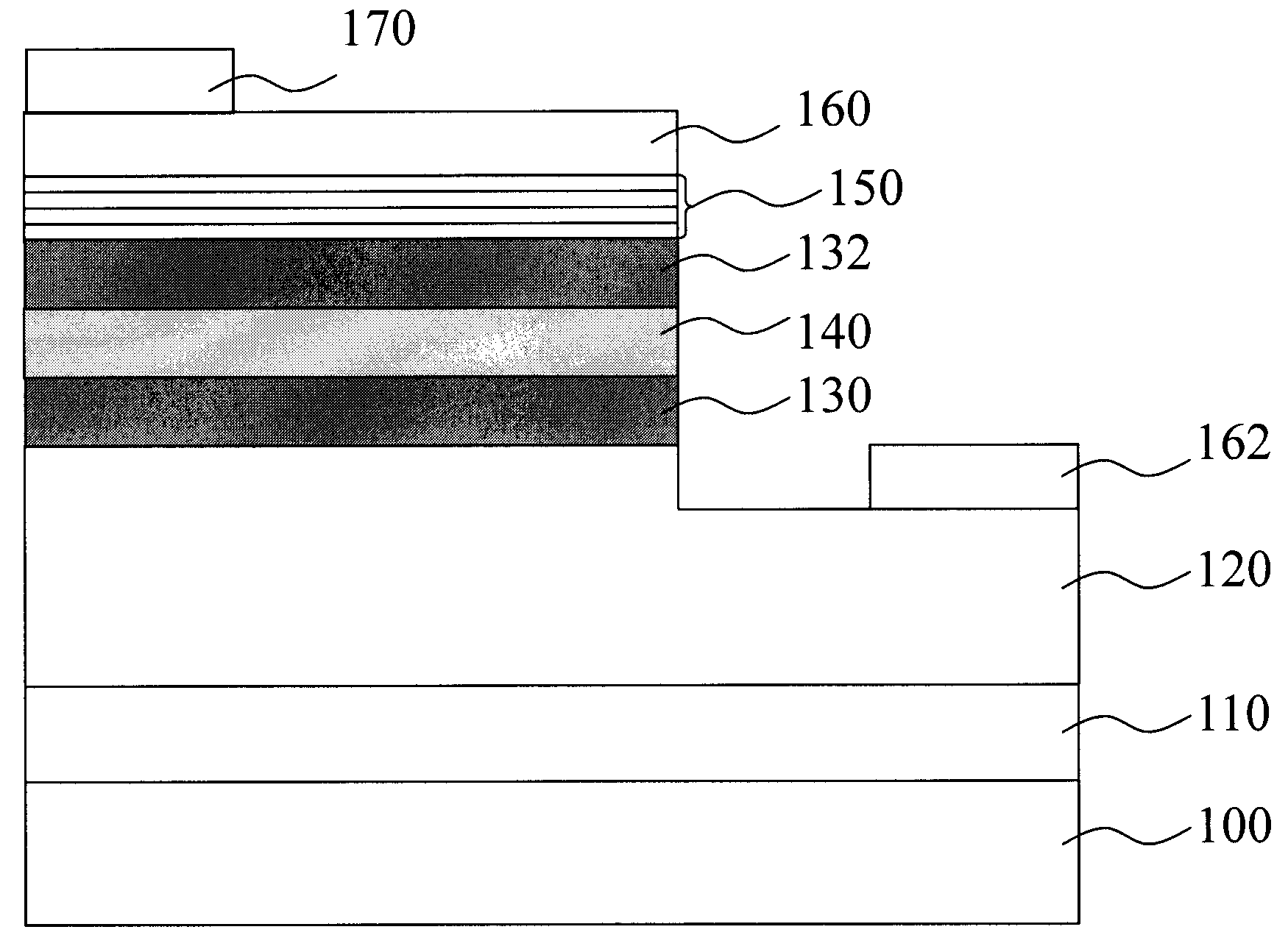

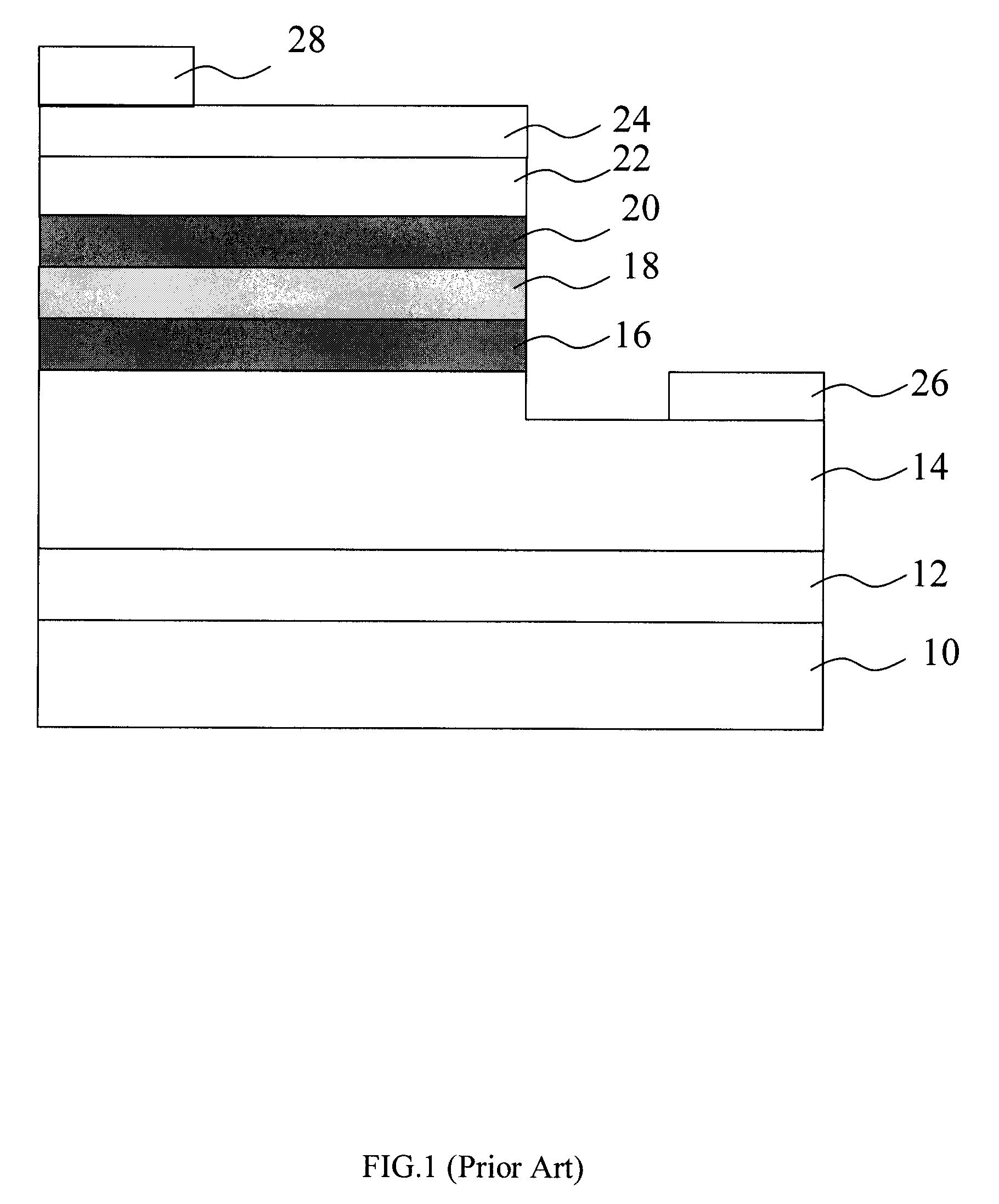

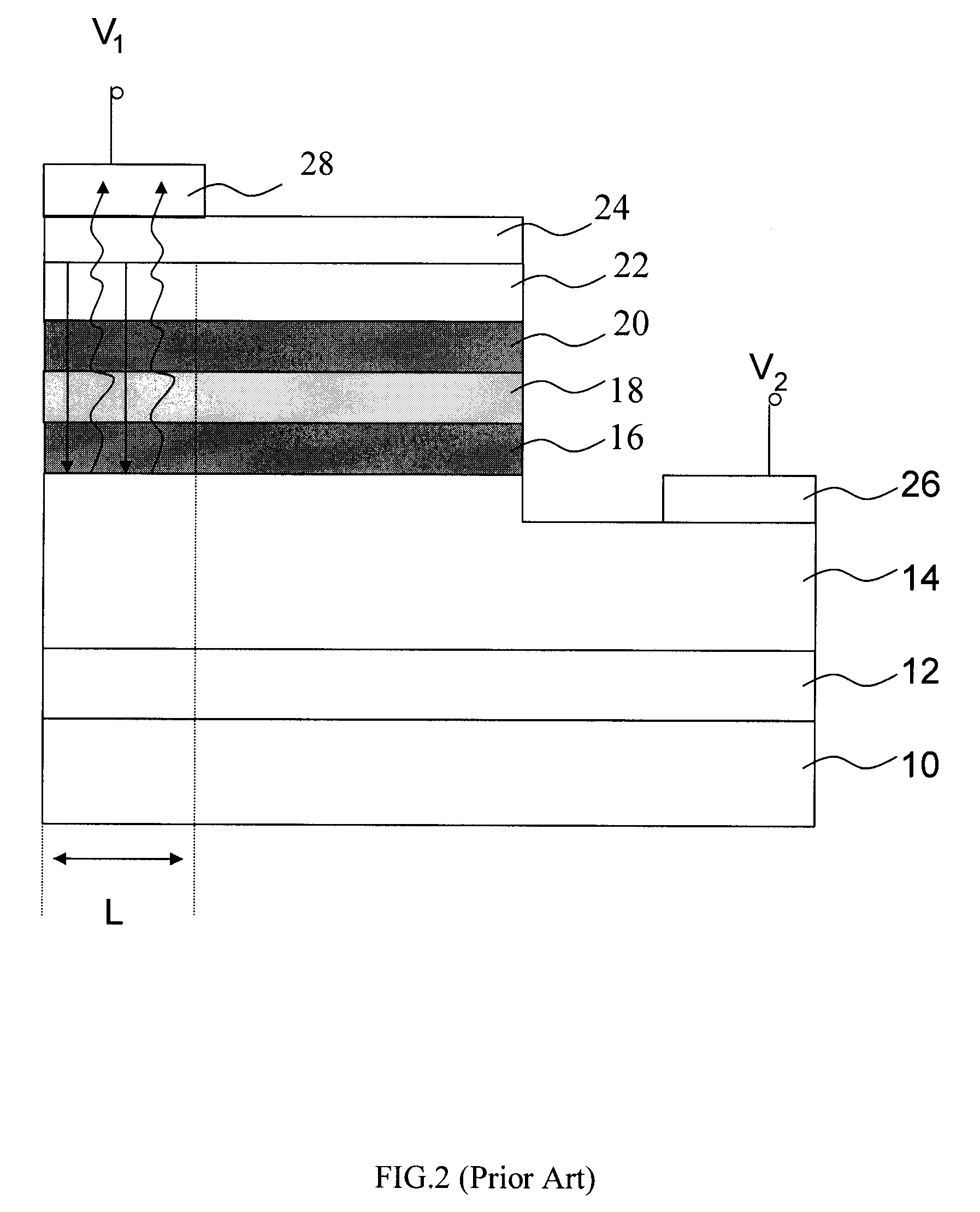

Gallium nitride based compound semiconductor light-emitting device

InactiveUS6992331B2Good light transmissionLow conductivitySolid-state devicesSemiconductor/solid-state device manufacturingOhmic contactGallium nitride

Disclosed are a GaN based compound semiconductor light emitting diode (LED) and a manufacturing method therefor. In the LED, a combination of a light extraction layer and an adaptive layer is formed over a multi-layer epitaxial structure,wherein the light extraction layer is a light transmissible impurity doped metal oxide and the adaptive layer is a Ni / Au layer used to enhance ohmic contact between the light extraction layer and the multi-layer epitaxial structure.

Owner:SEMILEDS OPTOELECTRONICS CO LTD

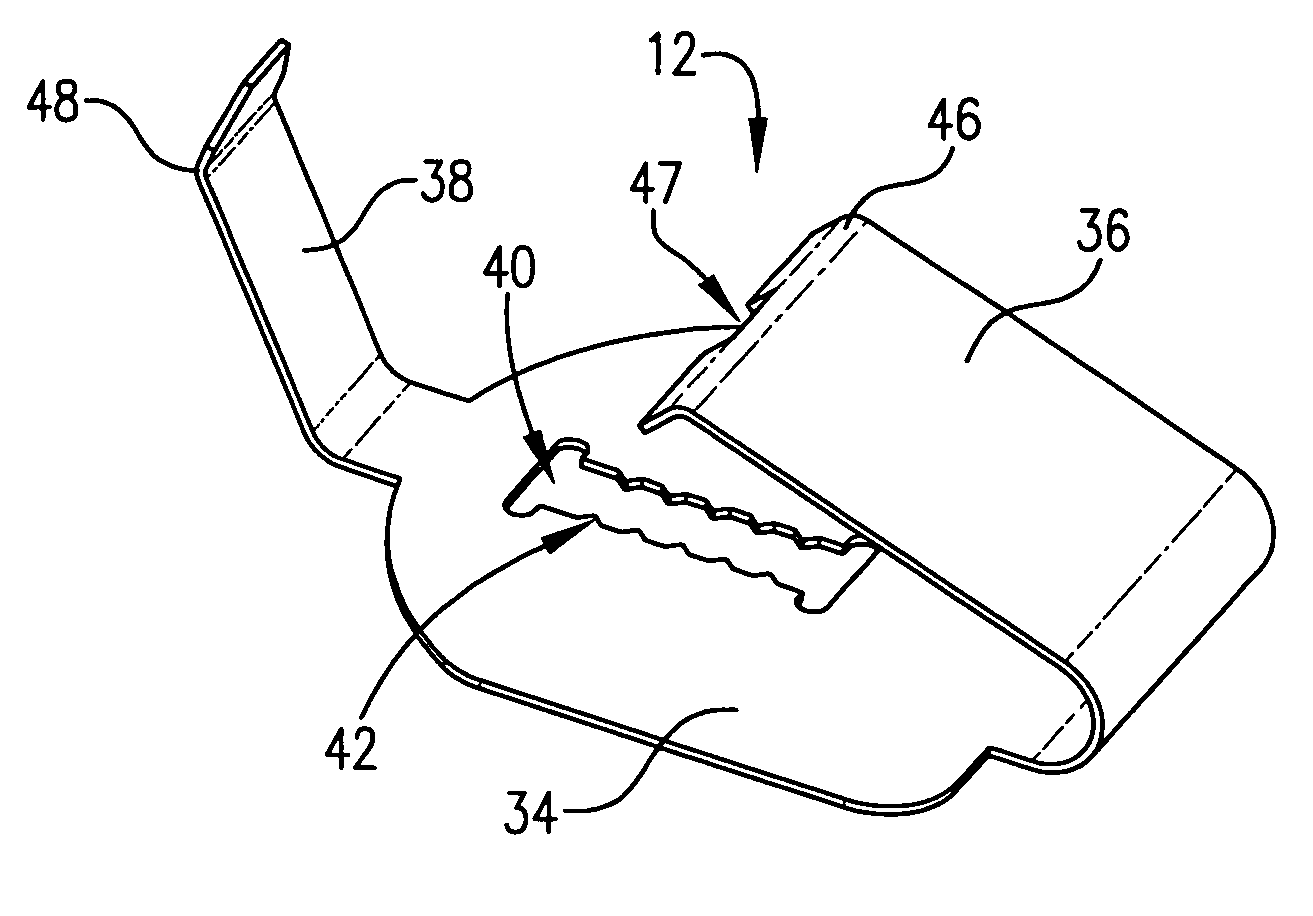

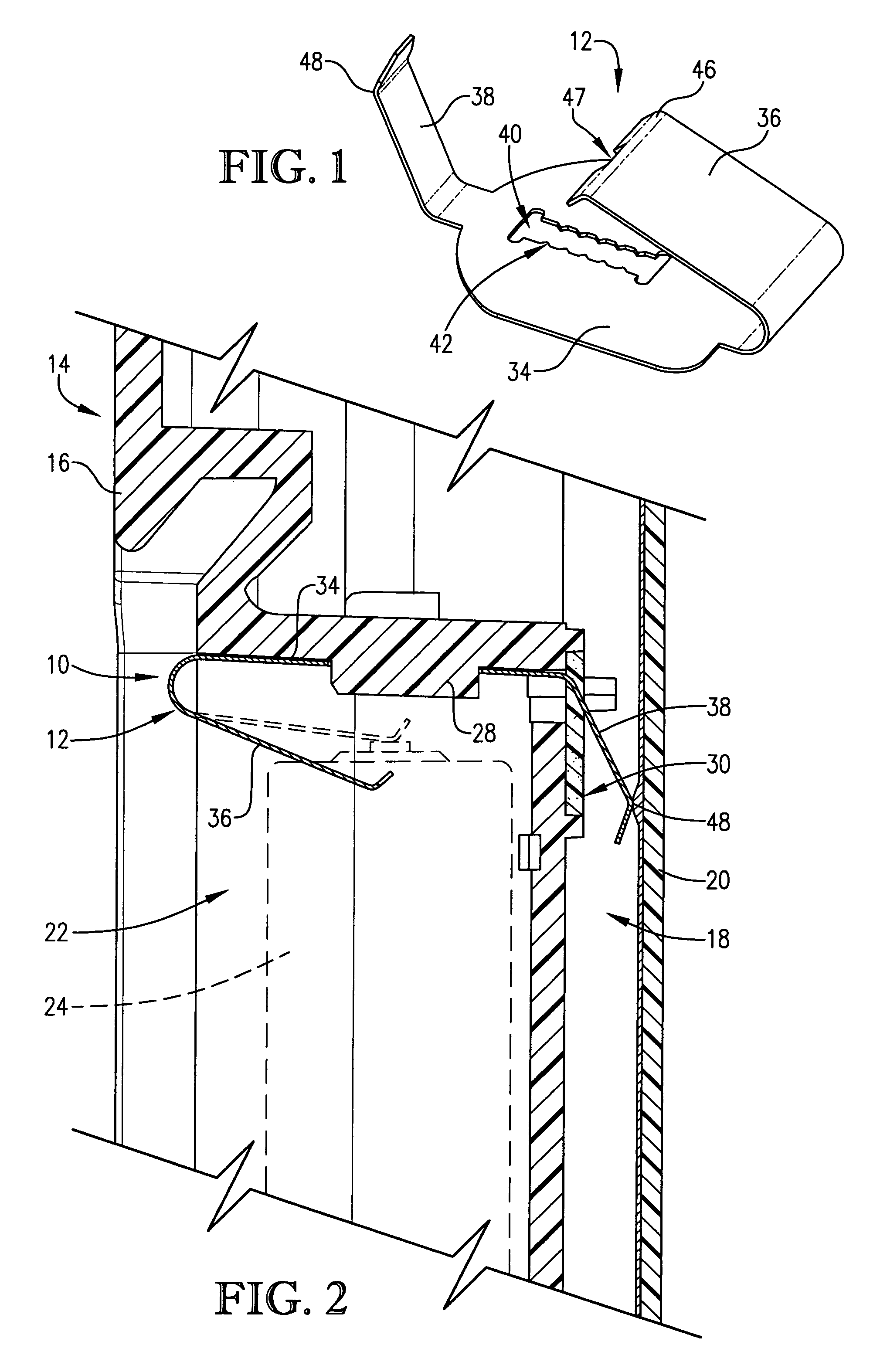

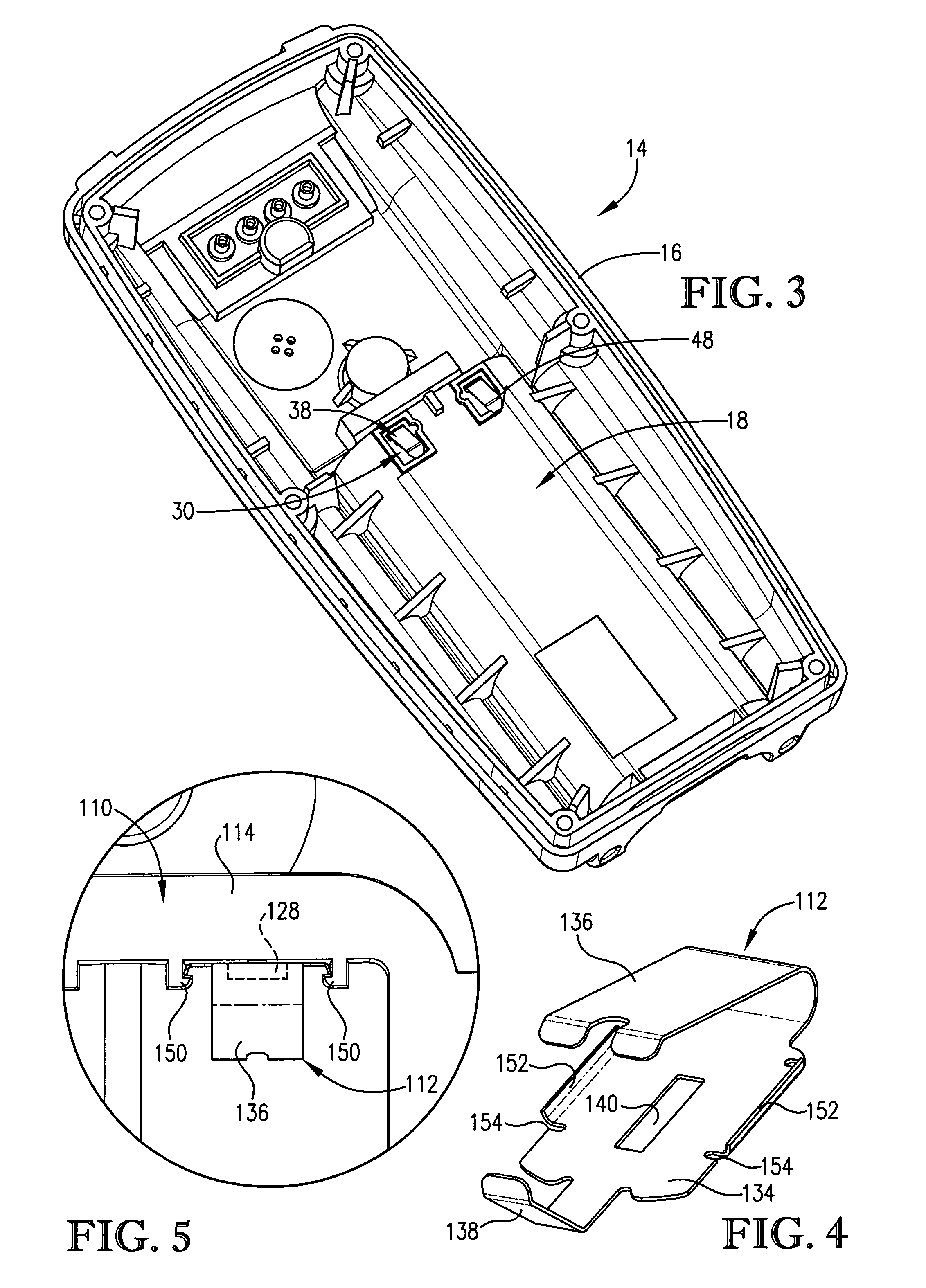

Battery contact mechanism including single-piece battery contact spring

ActiveUS7170006B1Improved contact characteristicsIncreased durabilitySecuring/insulating coupling contact membersSoldered/welded conductive connectionsHand heldElectronic component

A battery contact mechanism (10) including a battery contact spring (12) for electrically connecting a battery (24) with electronic componentry (20) within a battery-powered device (14), such as, for example, a portable, hand-held GPS unit or personal digital assistant (PDA). The battery contact mechanism (10) includes a single-piece battery contact spring (12), including a center section (34), an upper tang (36) for contacting the battery (24), and a lower tang (38) for contacting the electronic componentry (20); a post or rib projection (28) for securing the spring (12) within the device (14); and a sealant reservoir (30) for preventing leakage of moisture or other substances to the electronic componentry (20).

Owner:GARMIN

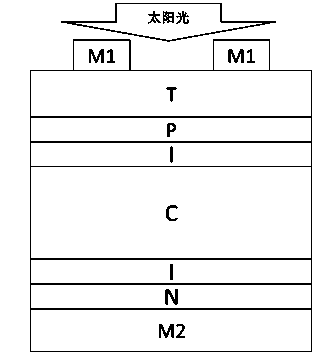

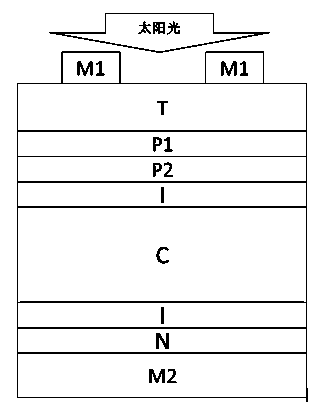

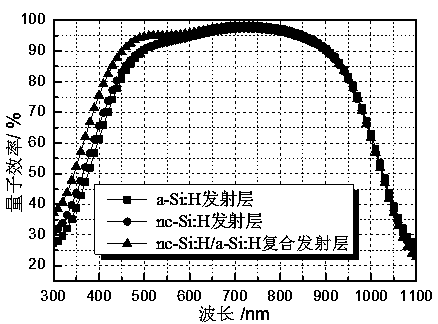

Method for preparing silicon heterojunction solar cell containing composite emission layer

ActiveCN103915523AReduced series resistanceReduce absorptionFinal product manufacturePhotovoltaic energy generationNanocrystalline siliconCrystalline silicon

The invention provides a method for preparing a silicon heterojunction solar cell containing a composite emission layer. The method includes the steps that an amorphous silicon back field N is deposited on one face of a substrate C on which a double-faced intrinsic amorphous silicon passivation layer I is deposited, an amorphous silicon layer P2 with the uniform structure is prepared on the face opposite to the amorphous silicon back field N under the conditions that doping concentration, hydrogen dilution and power density are low, a nanocrystalline silicon layer P1 with the uniform structure is prepared under the conditions that the doping concentration, the hydrogen dilution and the power density are improved, and an amorphous silicon / nanocrystalline silicon composite structure formed by the two silicon films serves as the emission layer of the silicon heterojunction solar cell. Materials have the advantages of being high in transmittance and conductivity through the structure, on the basis, the passivation effect of the surface of crystalline silicon can be improved, short wave response and output characteristics of the cell are improved, and the method for preparing the silicon heterojunction solar cell is simple and easy to carry out.

Owner:捷造科技(宁波)有限公司

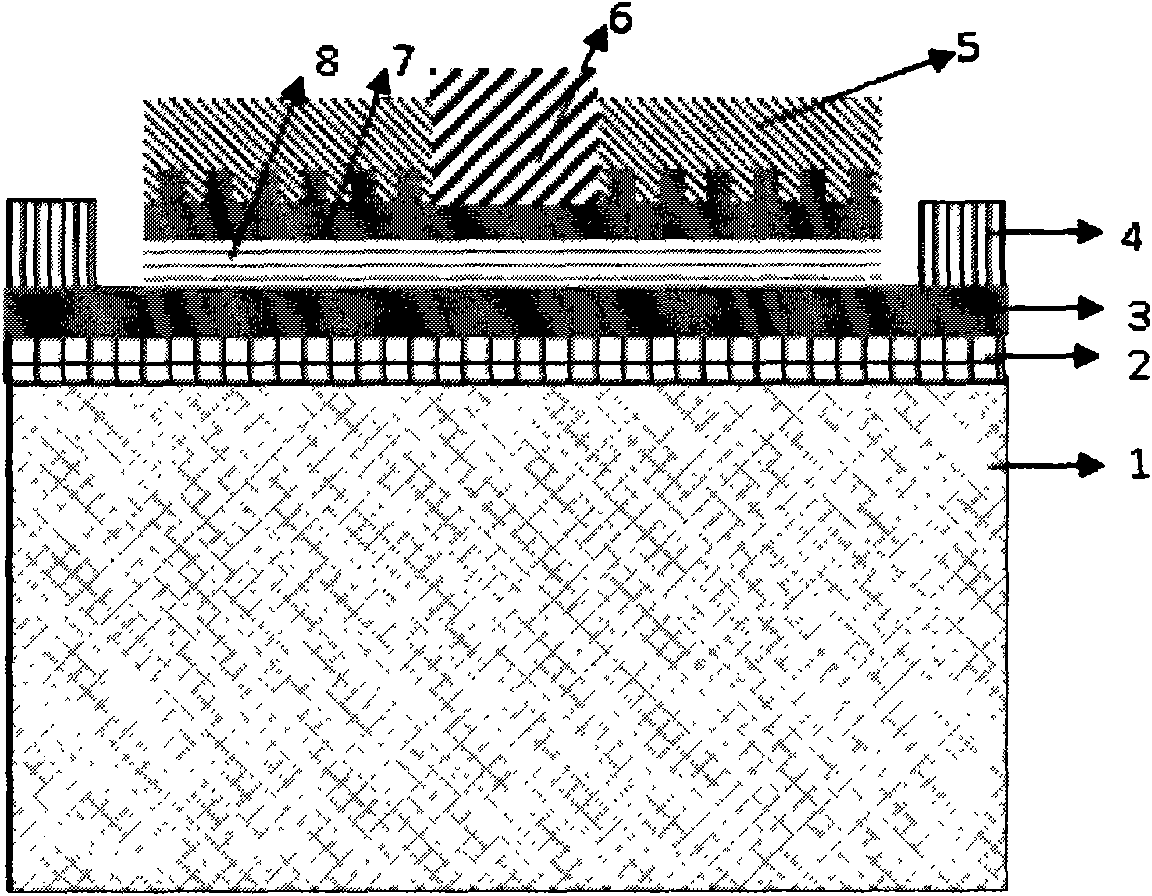

Plasmon-enhancement-based quantum well infrared detector and preparation method thereof

InactiveCN102185002AIncreases the probability of electronic transitions from the ground stateGood contact characteristics and current spreading abilityFinal product manufactureSemiconductor devicesInfrared detectorMetal grating

The invention discloses a Plasmon-enhancement-based quantum well infrared detector and a preparation method thereof. The detector comprises a Si-GaAs substrate, an AlAs buffering layer, an AlAs:Si lower contact layer positioned on the buffering layer, a multi-quantum well layer, an AlAs:Si upper contact layer positioned on the multi-quantum well layer, a metal film, an upper electrode and an annular lower electrode, wherein the AlAs buffering layer is positioned on the substrate; the multi-quantum well layer is positioned on the AlAs:Si lower contact layer; the metal film and the upper electrode are positioned on the AlAs:Si upper contact layer; the metal film has a grating structure; the upper electrode is embedded in the metal grating structure; and the annular upper electrode is positioned on the lower contact layer and winds around the metal film, the upper contact layer and the multi-quantum well layer. In the detector, through the local area characteristic of Plasmon and the frequency-selecting characteristic of a raster, signals are enhanced and filtered, the absorption efficiency of a quantum well is improved, and the sensitivity of the quantum well infrared detector is increased.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

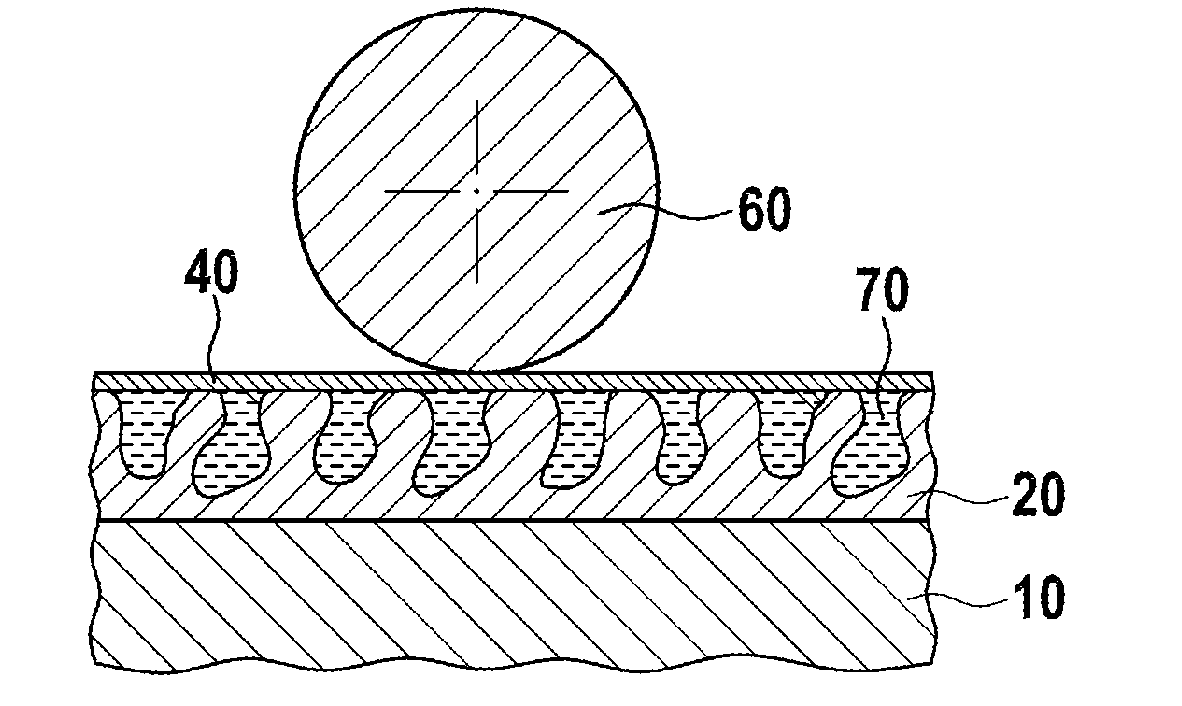

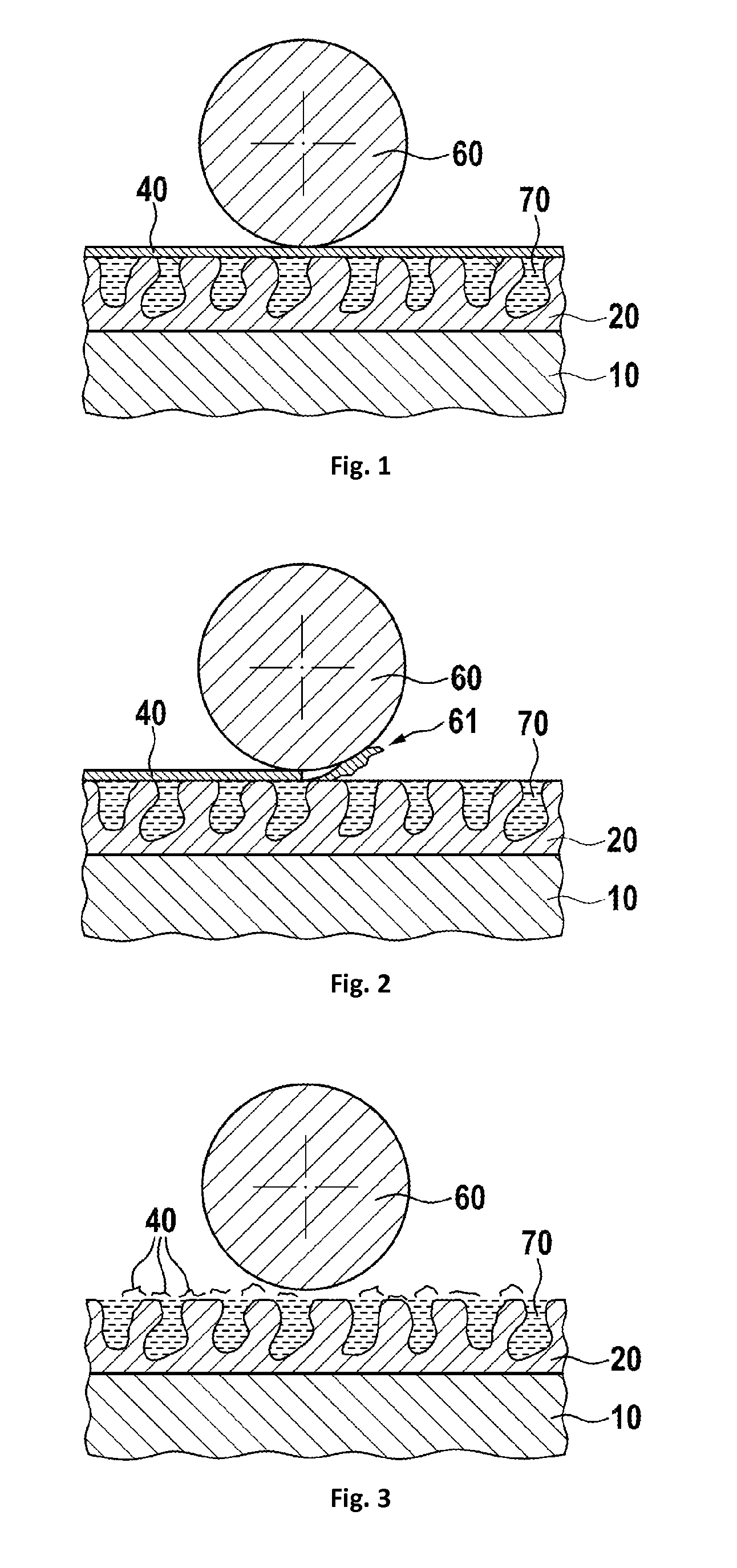

Self-Lubricating Slipring

ActiveUS20150288121A1Extended service lifeSafe storageRotary current collectorNon-rotary current collectorLubricantSlip ring

A slip ring has a slip ring track with a contact area, the contact area containing a plurality of pores or cavities. A lubricant is held within these pores and cavities and is enclosed by a top coating. When a slip ring brush is sliding over the slip ring track, it rubs off particles of the top coating, therefore opening some of the pores or cavities which release parts of the lubricant contained therein. This lubricant reduces surface friction of the slip ring brush at the slip ring track and therefore further wear, which results in an extended lifetime.

Owner:SCHLEIFRING & APPBAU

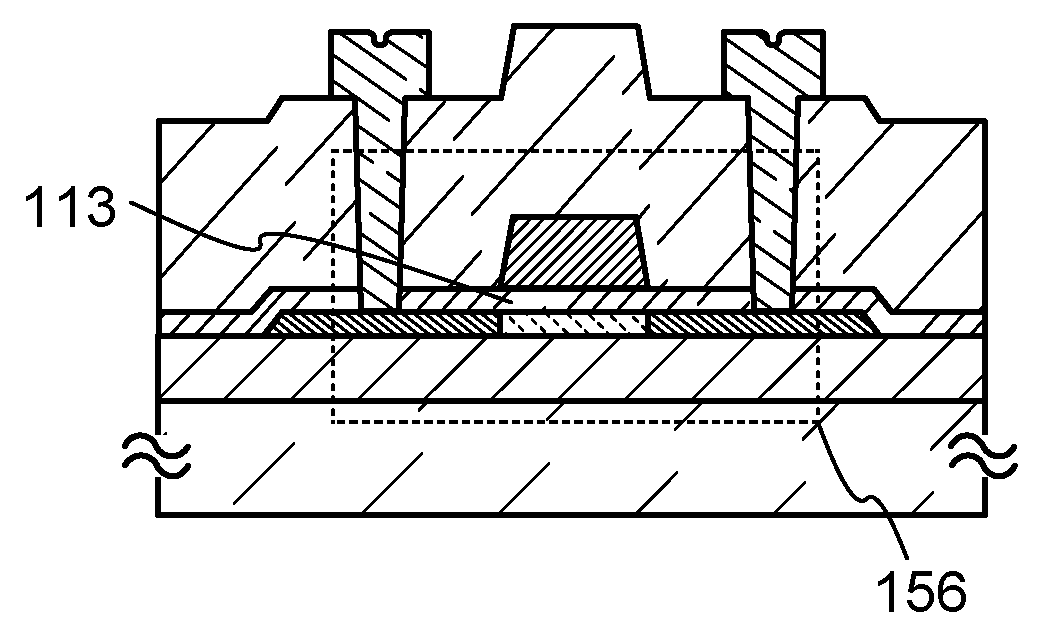

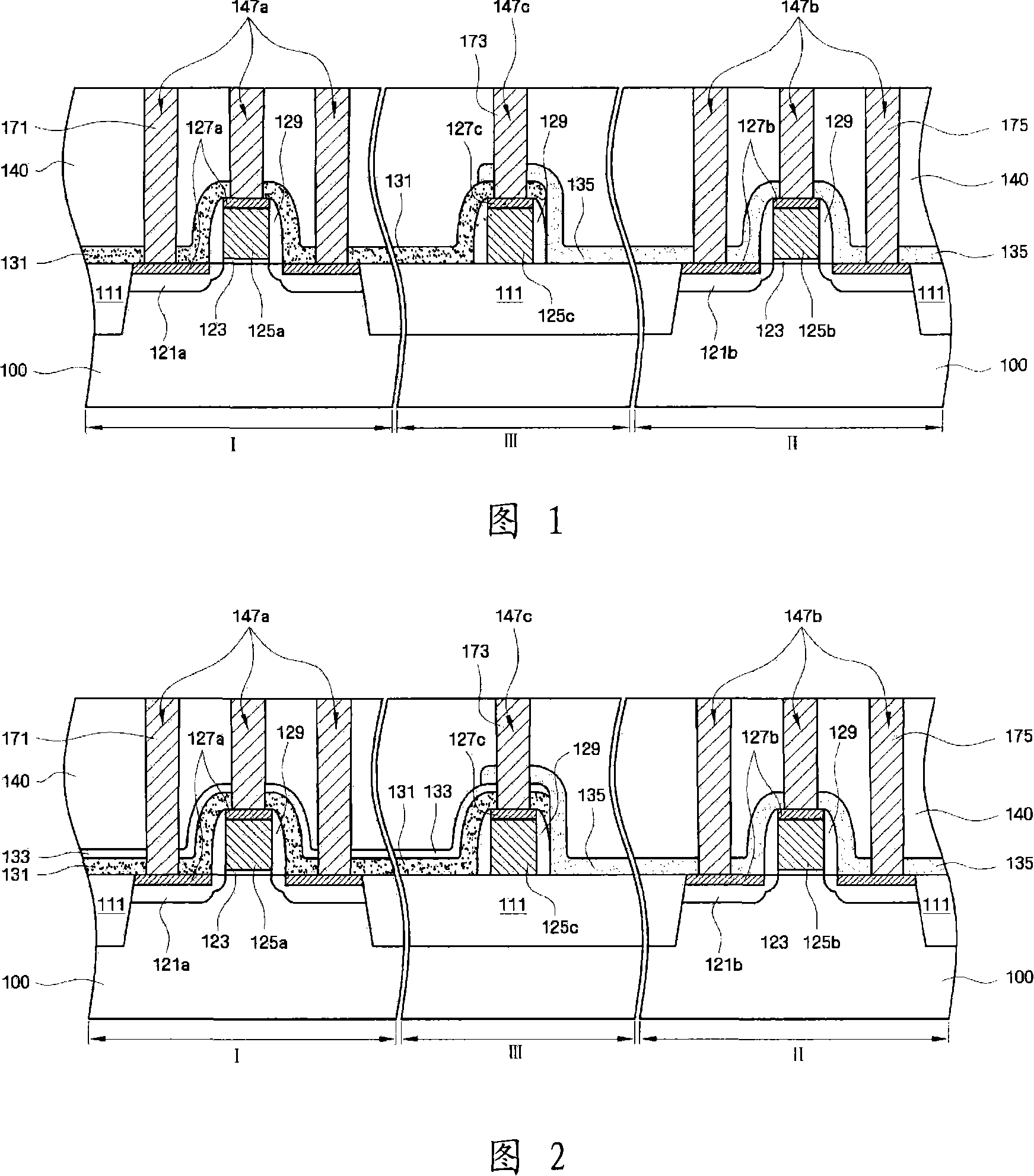

Semiconductor device and method of fabricating the same

ActiveCN101154629AImproved contact characteristicsImprove reliabilityTransistorSemiconductor/solid-state device detailsDielectricSemiconductor

A semiconductor device comprises: a first stress film covering af first transistor zone and at least a part of a third gate electrode in the boundary zone; a second stress film covering a second transistor zone and overlapping with at least a part of the first stress film on the third gate electrode in the boundary zone; and an interlayer dielectric film formed on the first and the second stress films. The semiconductor device also comprises: a plurality of first contact hole passing through the interlayer dielectric film in the first transistor zone and the first stress film; a plurality of second contact hole passing through the interlayer dielectric film in the second transistor zone and the second stress film; and a third contact hole passing through the interlayer dielectric film in the interface zone, the second stress film and the first stress film. A depressed portion at the upper side of the third electrode formed on the third contact hole has a depth larger or equal to the depth of the depressed portion at the upper side of the first gate electrode of the first contact hole.

Owner:SAMSUNG ELECTRONICS CO LTD

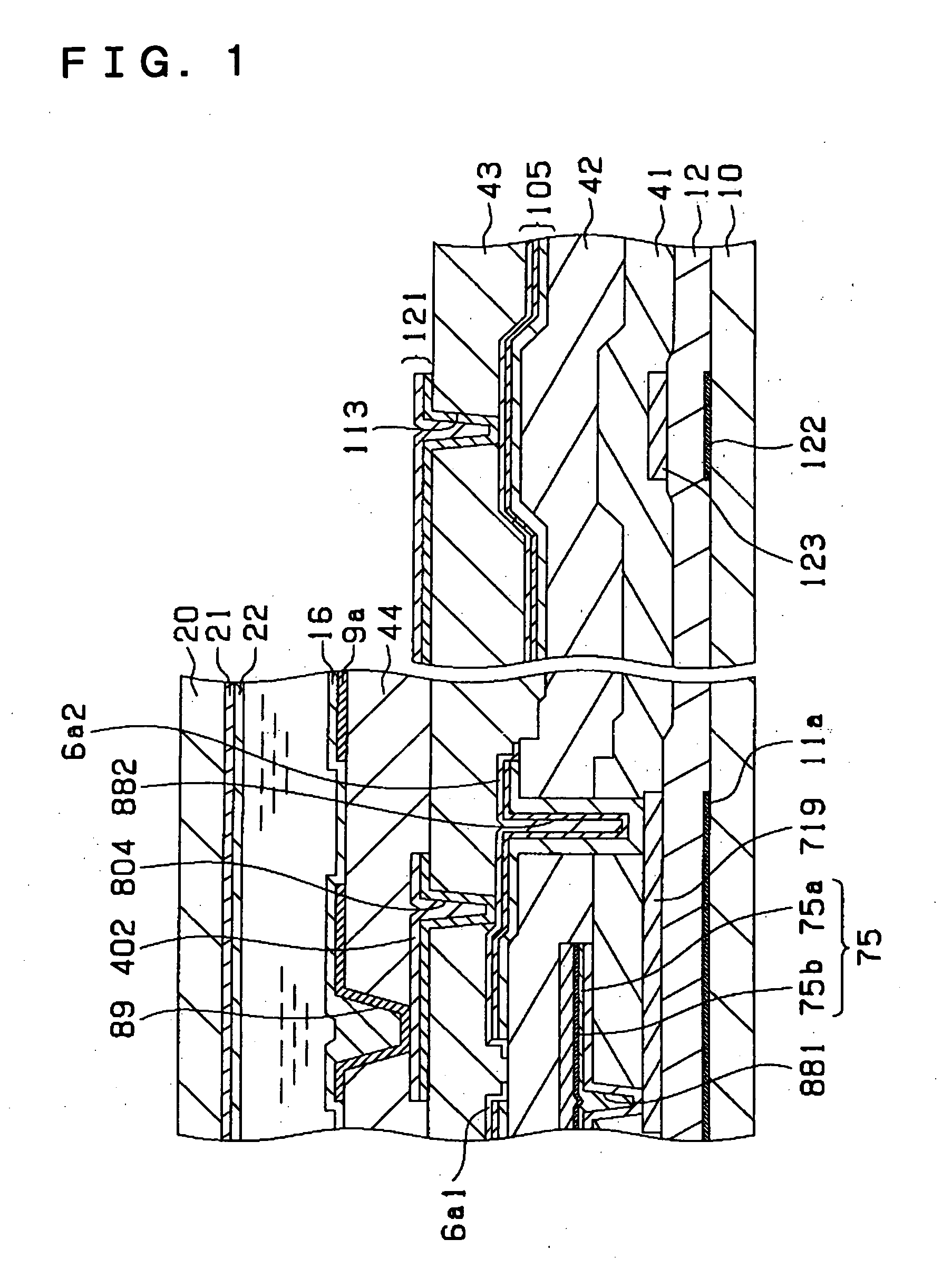

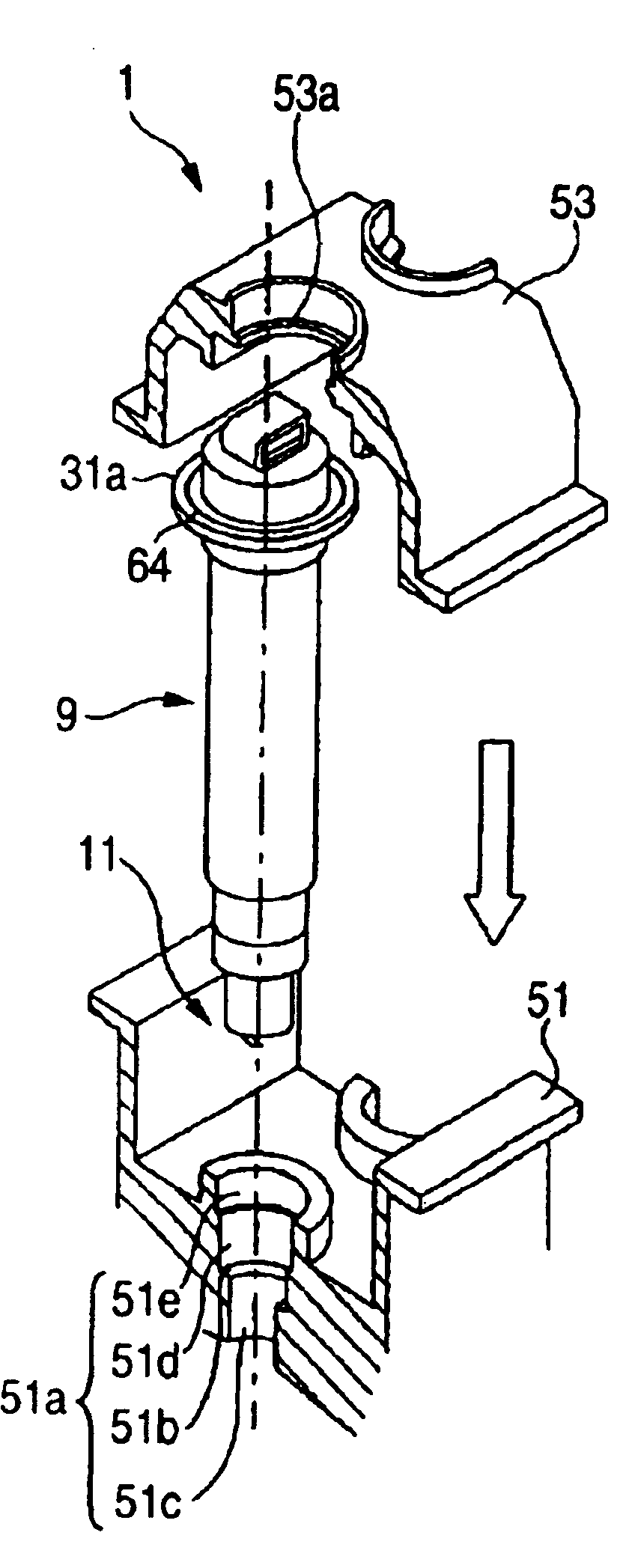

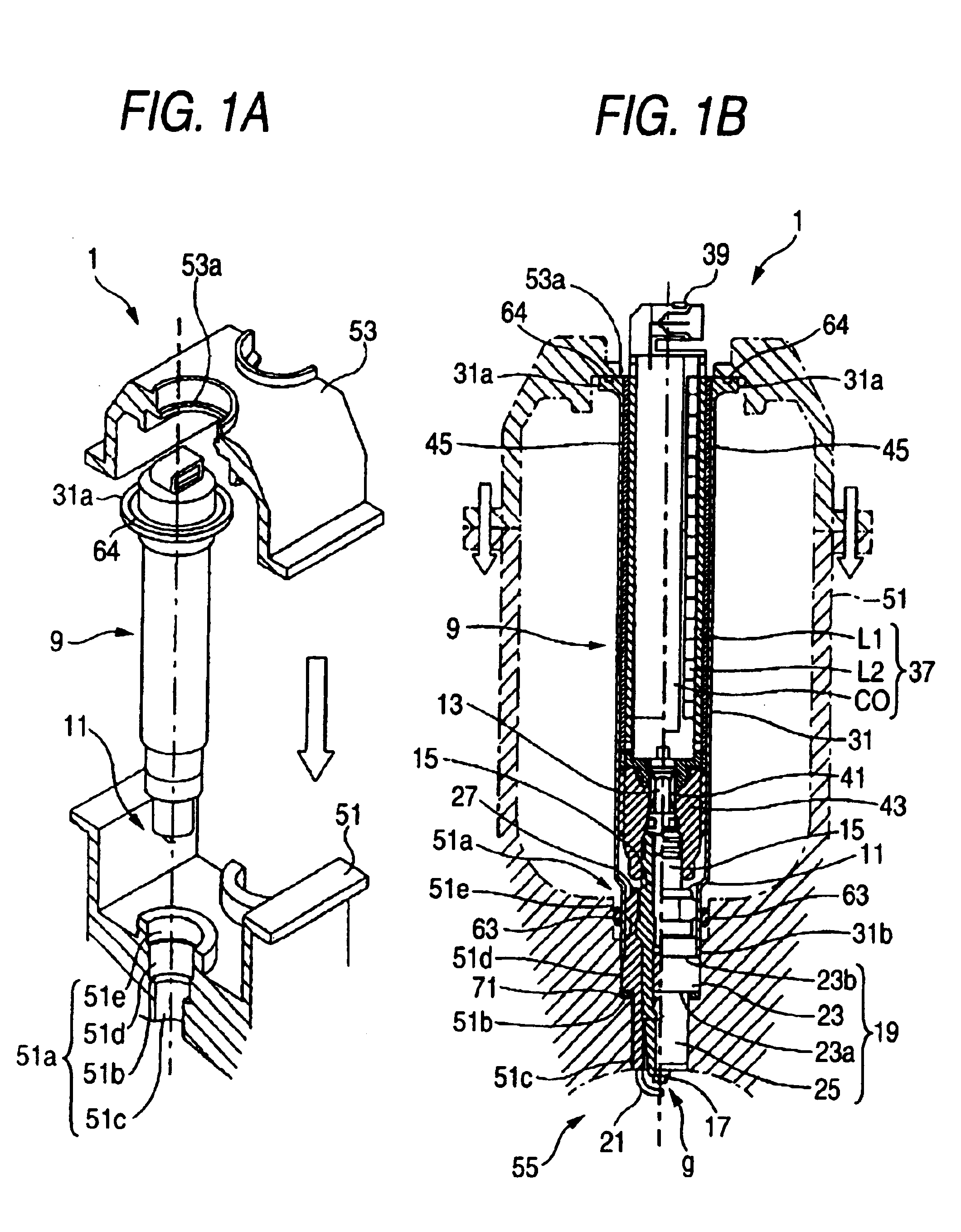

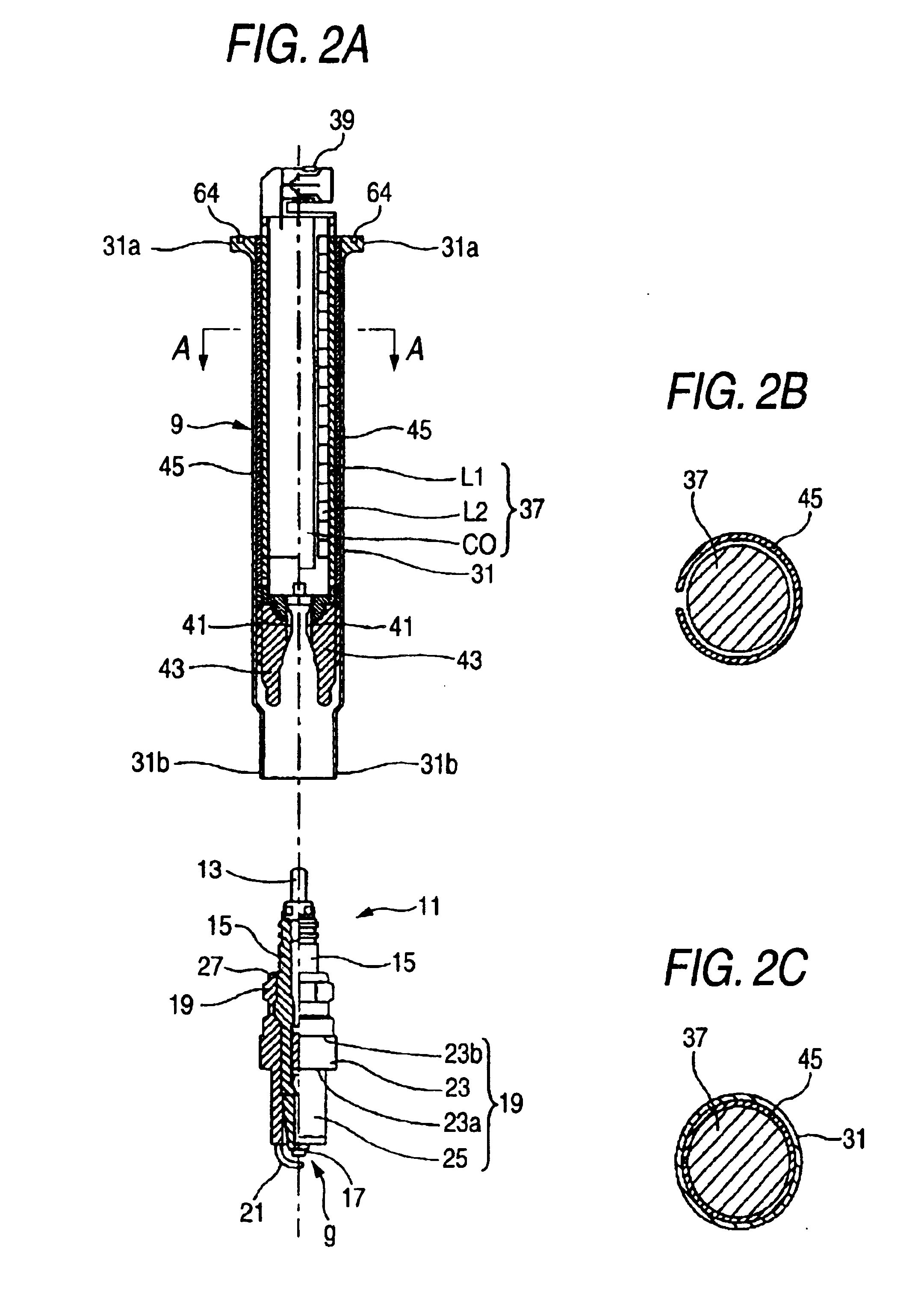

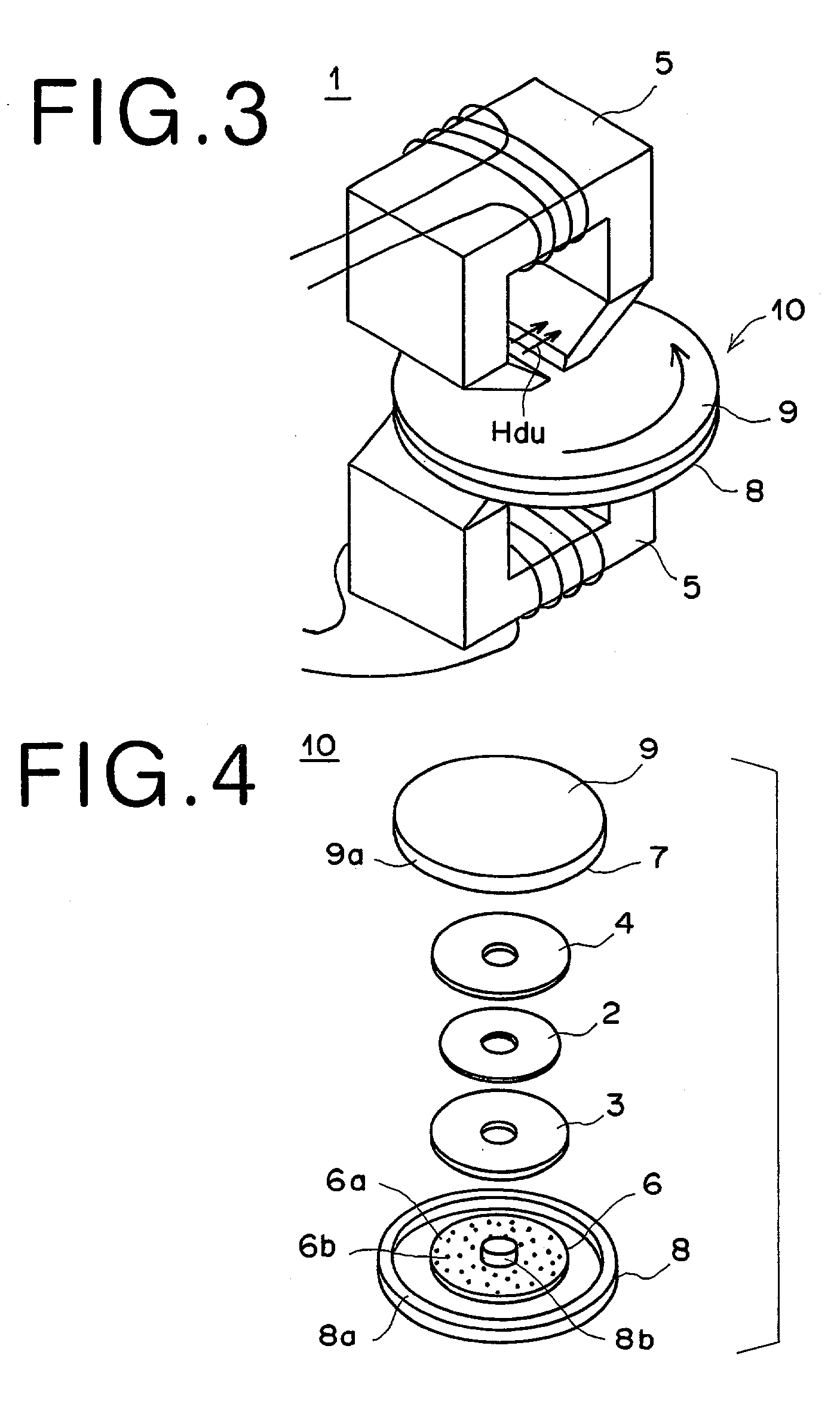

Ignition coil, and internal combustion engine ignition device

InactiveUS6880540B2Accurate detectionImproved contact characteristicsSparking plugsTransformersIgnition coilCylinder head

An object of the present invention is to provide an ignition coil which has a structure to make it possible to connect the ignition coil to a spark plug directly and in which an installation space need not be changed largely when the ignition coil is mounted in a cylinder head, and an internal combustion engine ignition system having the ignition coil.In the present invention, a protection metal pipe (31) of an ignition coil (9) is formed so that a rear end side portion of a spark plug (11) in the rear of a rear end surface (23b) of a collar portion (23) in a metal shell (19) can be received in the inside of the protection metal pipe (31) from a front end (31b). The ignition coil (9) has a structure in which the ignition coil (9) is directly connected to the spark plug (11). The protection metal pipe (31) of the ignition coil (9) is formed to serve also as a plughole pipe, so that the outer diameter of the protection metal pipe (31) can be enlarged up to the outer diameter of a conventional plughole pipe. As a result, a space for installing a coil body portion (37) can be secured largely in the inside of the protection metal pipe (31), so that the installation space need not be changed largely when the ignition coil is mounted in a cylinder head.

Owner:NGK SPARK PLUG CO LTD

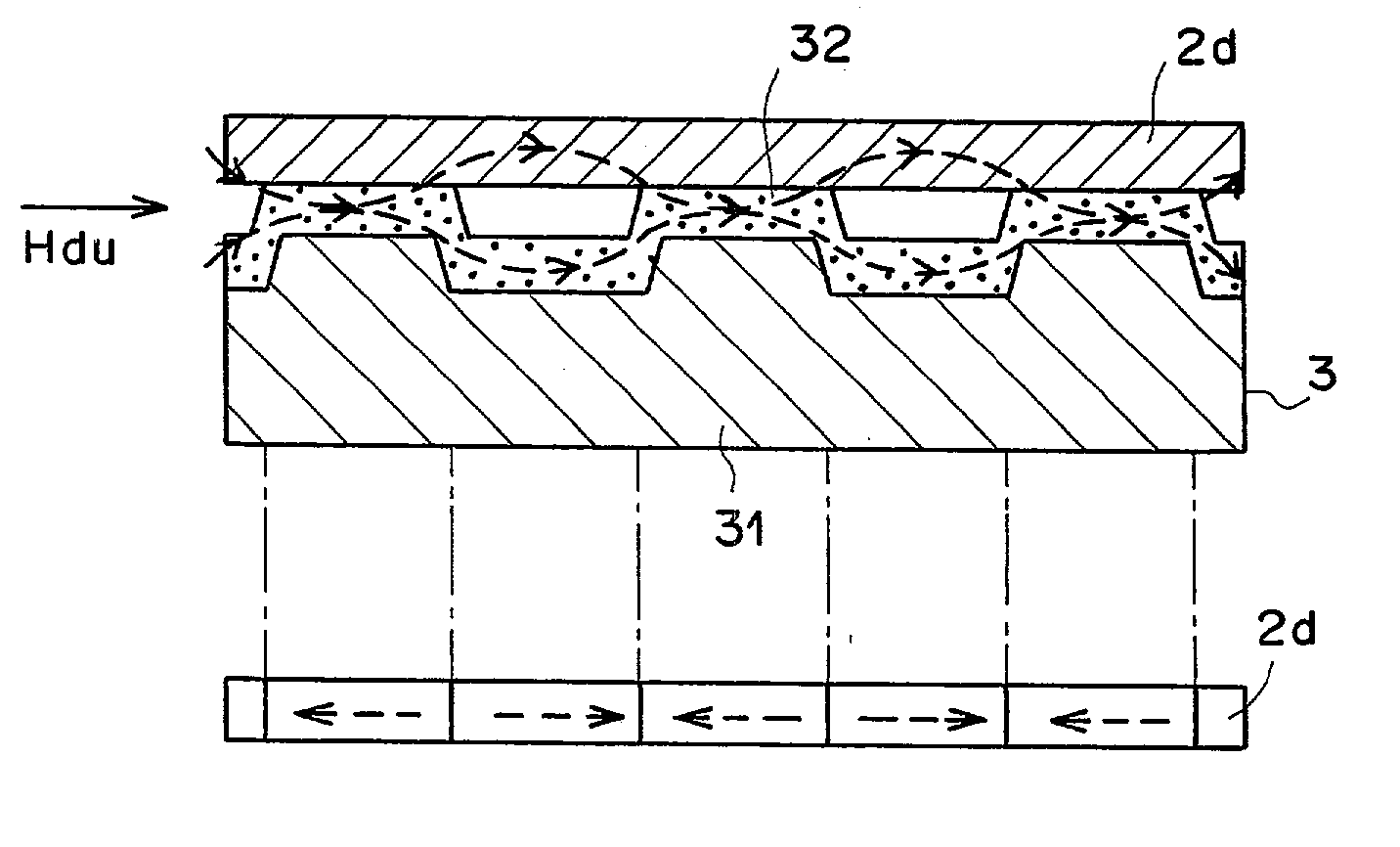

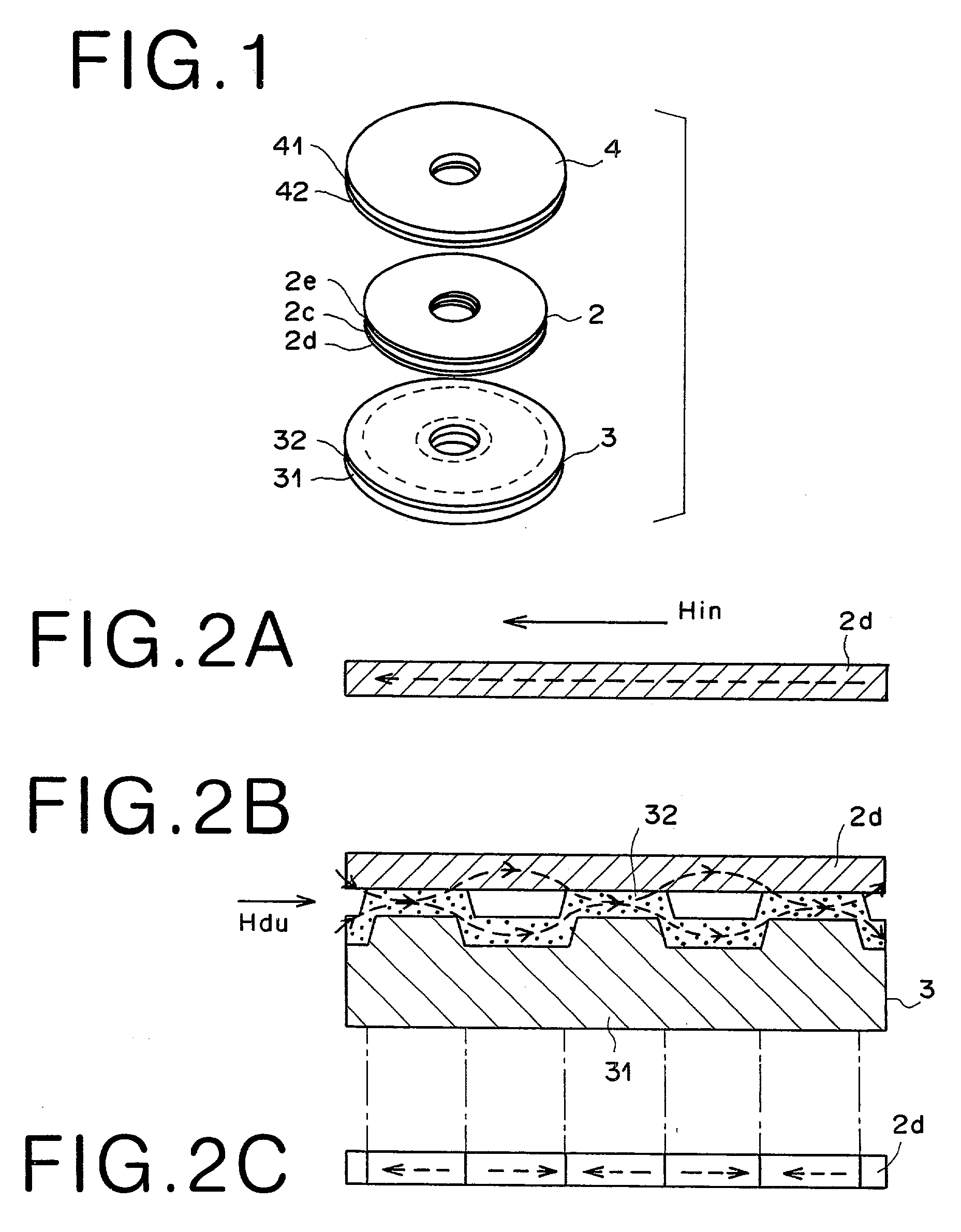

Magnetic transfer master medium

InactiveUS20020187295A1Great degree of contactEasy to flattenMagnetic materials for record carriersRecord information storageYoung's modulusCondensed matter physics

Signal omissions are prevented from occurring in the magnetic data transferred to a slave medium by magnetic transfer employing a magnetic transfer master medium. A master medium formed of a material and having a thickness wherein the bow stiffness=Ebd3 / 12 thereof is in the range greater than or equal to 0.3 N.m2 and less than or equal to 370 N.m2, for a sample piece thereof having a width defined of 1 m and an arbitrary length, and utilizing the Young's modulus E obtained by use of a vibration reed method on sample having a length of 50 mm, an arbitrary width b, and a thickness d.

Owner:FUJIFILM HLDG CORP

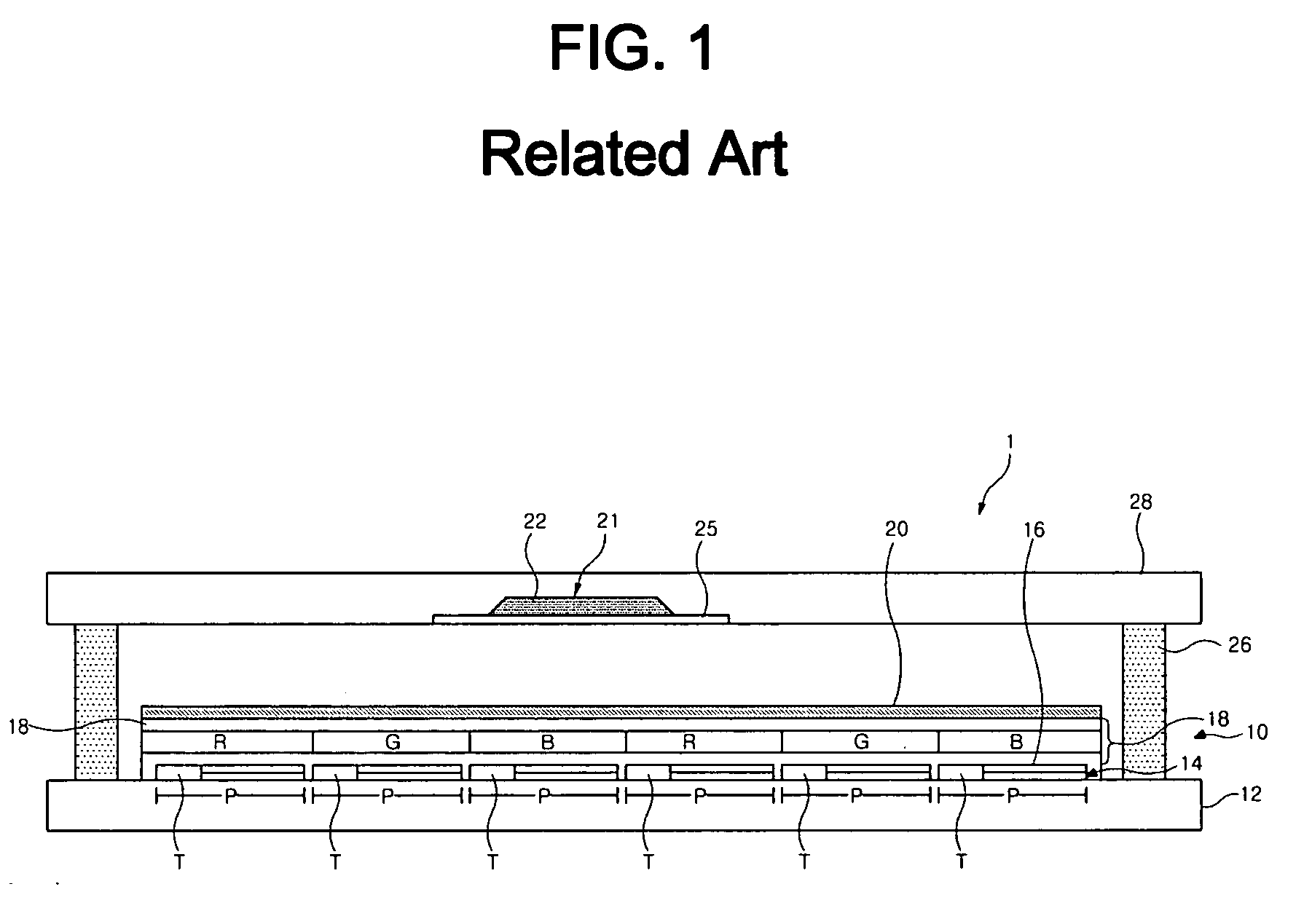

Dual panel type organic electroluminescent display device and method for fabricating the same

ActiveUS20080012481A1Increase brightnessEasy to produceDischarge tube luminescnet screensElectroluminescent light sourcesIndium tin oxideContact layer

An organic electroluminescent device includes a switching element and a driving element connected to the switching element on a substrate in a pixel region, an overcoat layer on the switching element and the driving element, a first contact layer on the overcoat layer, the first contact layer being made of one of molybdenum and indium tin oxide, a cathode on the first contact layer, the cathode connected to the driving element through the first contact layer, an emitting layer on the cathode, and an anode on the emitting layer.

Owner:LG DISPLAY CO LTD

Light emitting diode structure

InactiveUS20070290214A1Promote generationImprove conductivitySolid-state devicesSemiconductor devicesSemiconductor materialsContact layer

A LED (Light Emitting Diode) structure with a contact layer of a multiple structure includes a nucleation layer disposed on a substrate; a conductive buffer layer disposed on the nucleation layer; an active layer disposed between an upper and a lower confinement layer, wherein the structure of active layer includes a semiconductor material mainly doped with III-V group; the contact layer made of the multilayer structure disposed on the upper confinement layer; and a transparent electrode disposed on the contact layer made of a multilayer structure; and an electrode contacted with the conductive buffer layer and isolated from the active layer and the transparent electrode.

Owner:EPILEDS TECH

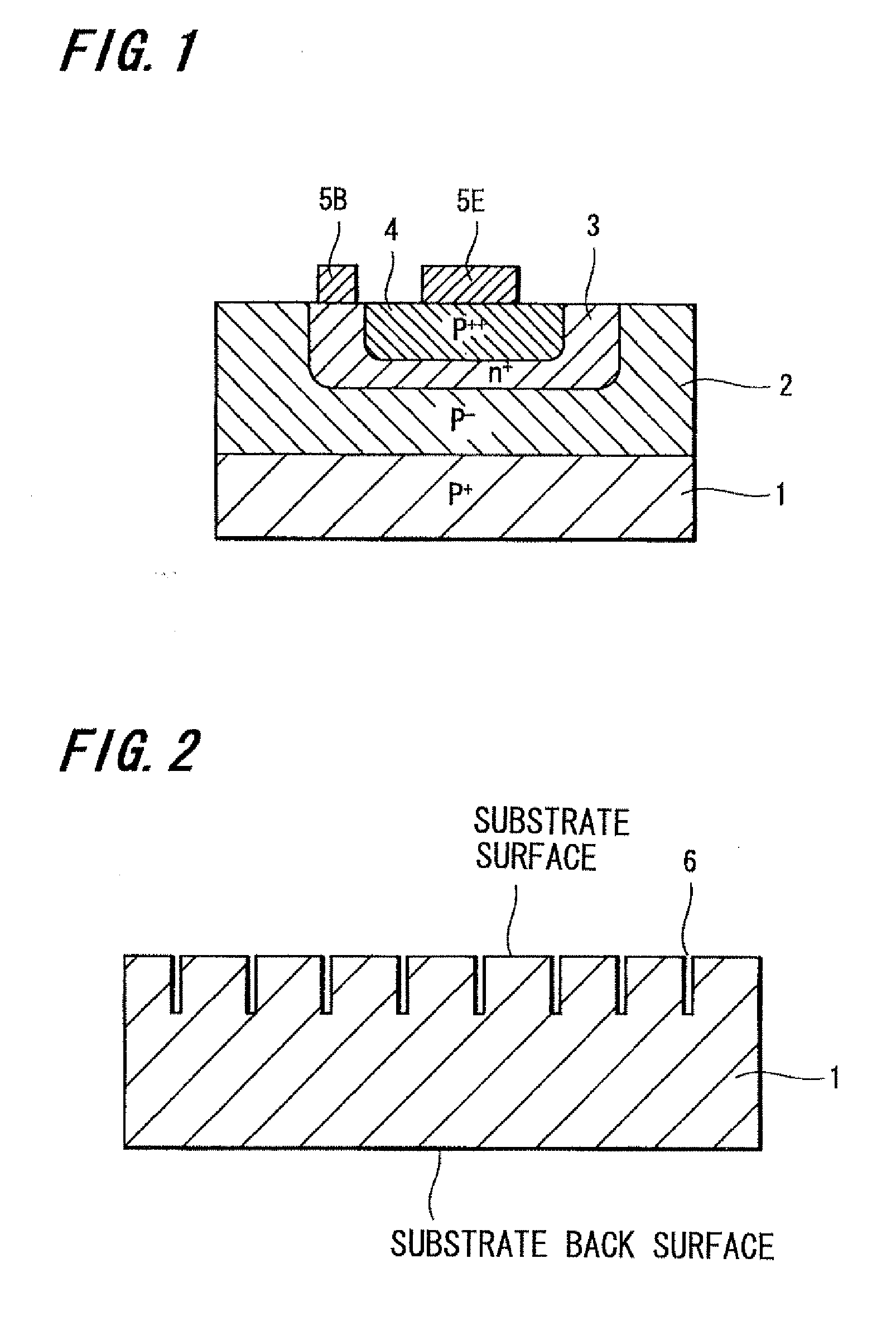

Method of manufacturing semiconductor device

InactiveUS20100190296A1Improve contact characteristicEasily separateSolid-state devicesSemiconductor/solid-state device manufacturingCarbon filmEngineering

The present invention provides a method of manufacturing a semiconductor device in which a thinned substrate of a semiconductor or semiconductor device is handled without cracks in the substrate and treated with heat to improve a contact between semiconductor back surface and metal in a high yield and a semiconductor device may be manufactured in a high yield. In the method of manufacturing a semiconductor device according to the present invention, a notched part is formed from a surface to a middle in a semiconductor substrate by dicing and the surface of the substrate is fixed to a support base. Next, a back surface of the substrate is ground to thin the semiconductor substrate and then a metal electrode and a carbon film that is a heat receiving layer are sequentially formed on the back surface of the substrate. Next, the carbon film is irradiated with light at a power density of 1 kW / cm2 to 1 MW / cm2 for a short time of 0.01 ms to 10 ms to transfer heat from the carbon film and alloy an interface between a semiconductor and the metal electrode. Subsequently, the semiconductor substrate is separated at the notched part into pieces.

Owner:SUCCESS INT CORP +1

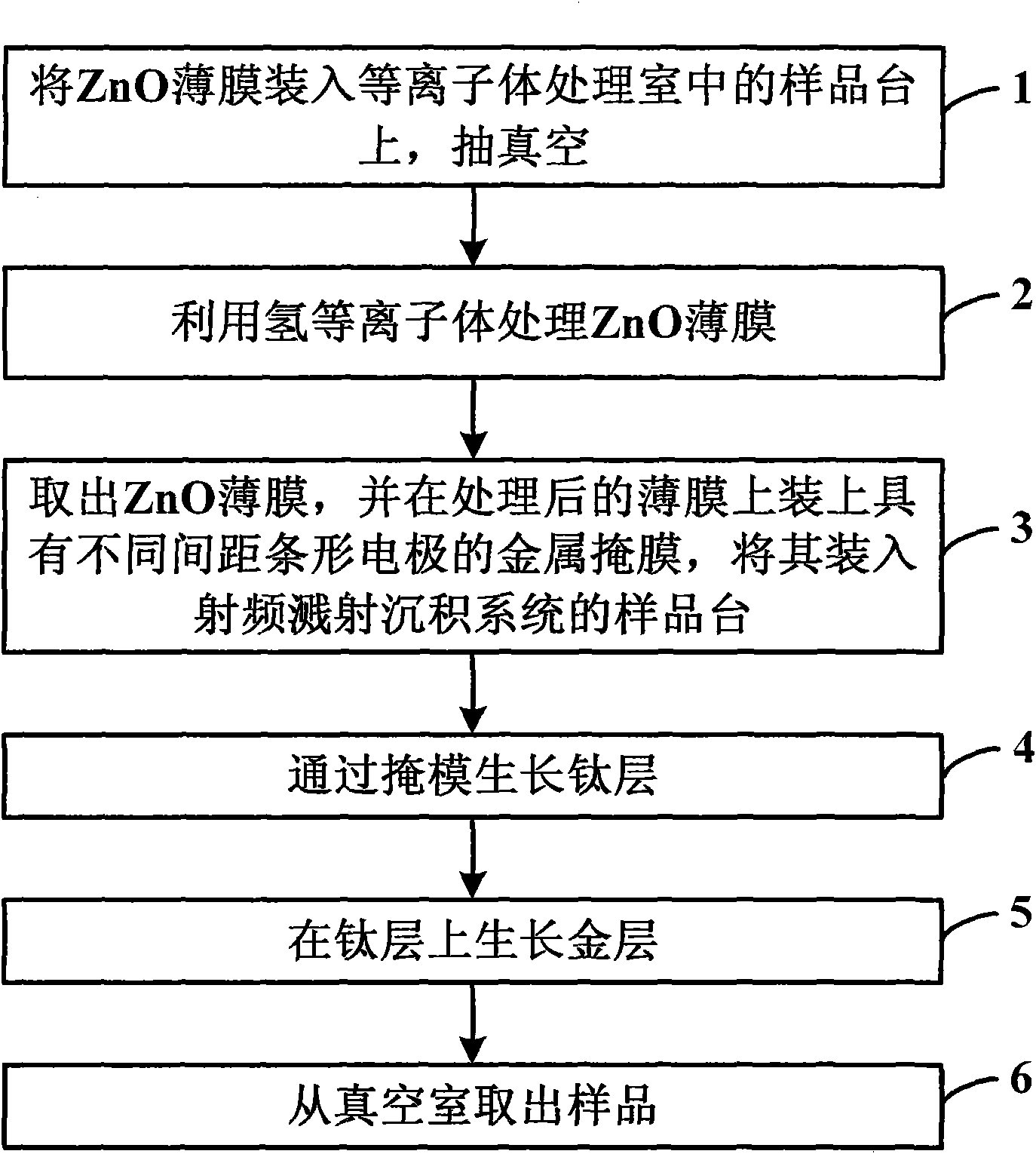

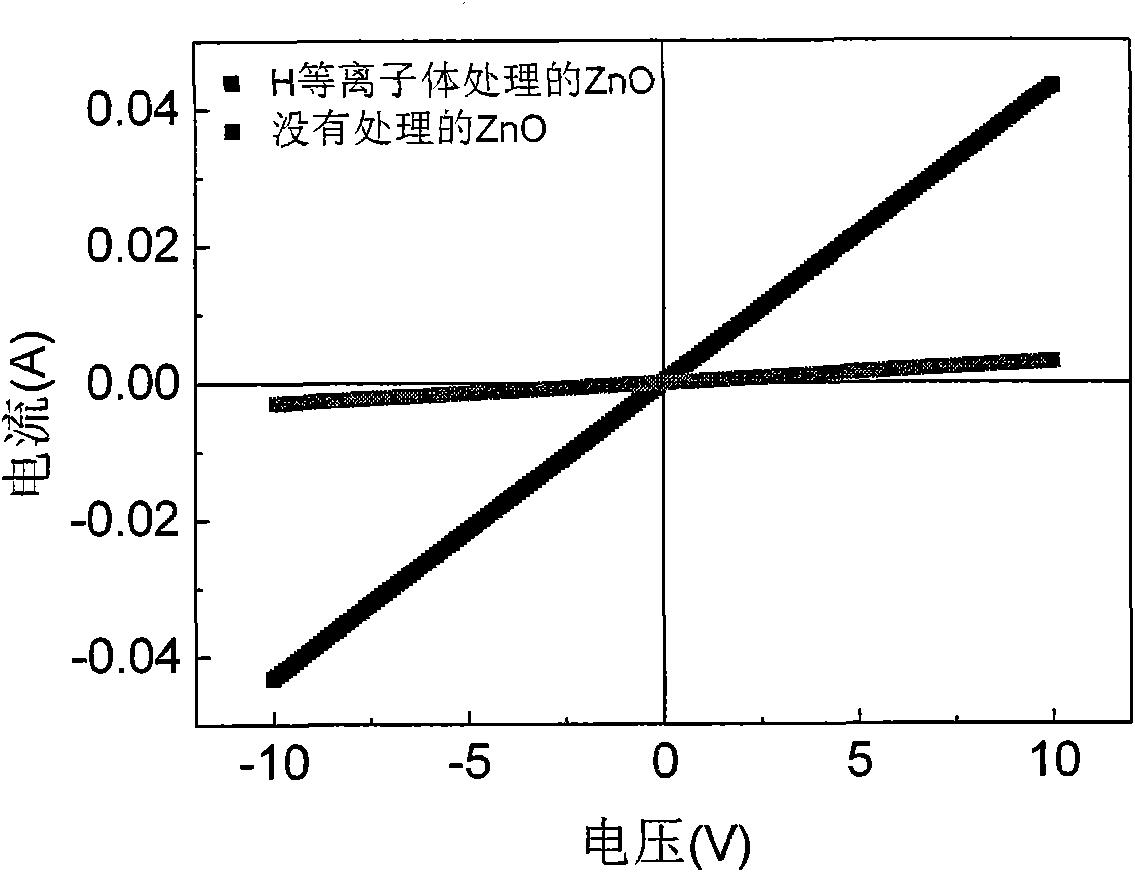

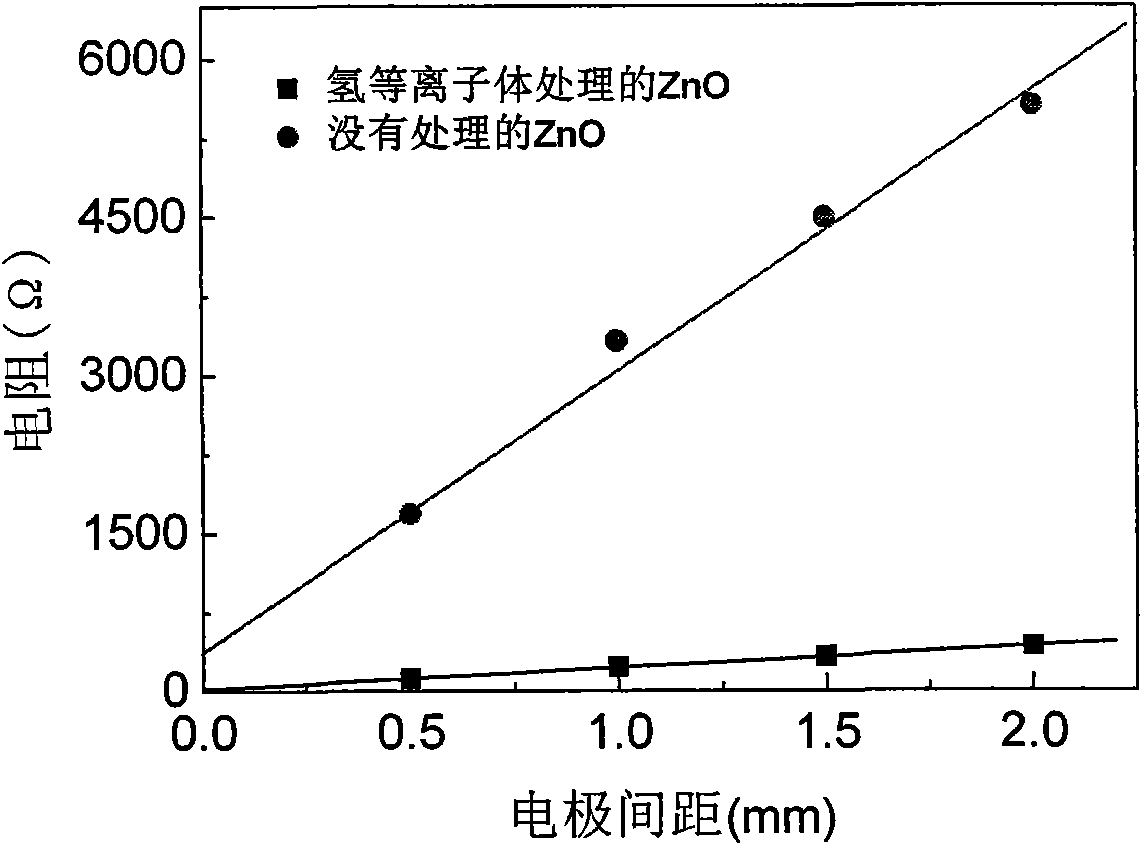

Method for improving ohmic contact of ZnO film

InactiveCN101685776AImproved contact characteristicsIncrease the carrier concentrationLaser detailsSemiconductor/solid-state device manufacturingHydrogenHigh energy

The invention discloses a method for improving the ohmic contact of a ZnO film, which comprises the following steps of: utilizing a hydrogen plasma to treat an electrode contact area of the ZnO film before a metal electrode is deposited; and then depositing a double-layer metal electrode in the electrode contact area of the ZnO film treated by the hydrogen plasma to form the ohmic contact. The treatment of the hydrogen plasma causes hydrogen to be diffused into the ZnO film, which improves the carrier concentration of the ZnO film in the contact area, and reduces the resistivity of the ZnO film in the contact area so as to remarkably reduce the contact resistance of the ZnO film and metal and improve the ohmic contact characteristics thereof. In addition, in MS technology, sputtered particles have higher energy, so ZnO / Ti interfacial atoms can be fully mixed, and the adhesion of the Ti / Au contact on the ZnO film can be improved. The ohmic contact with good adhesion and low contact resistance can be obtained by the method, and a foundation is laid for realizing ZnO film electronic devices.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

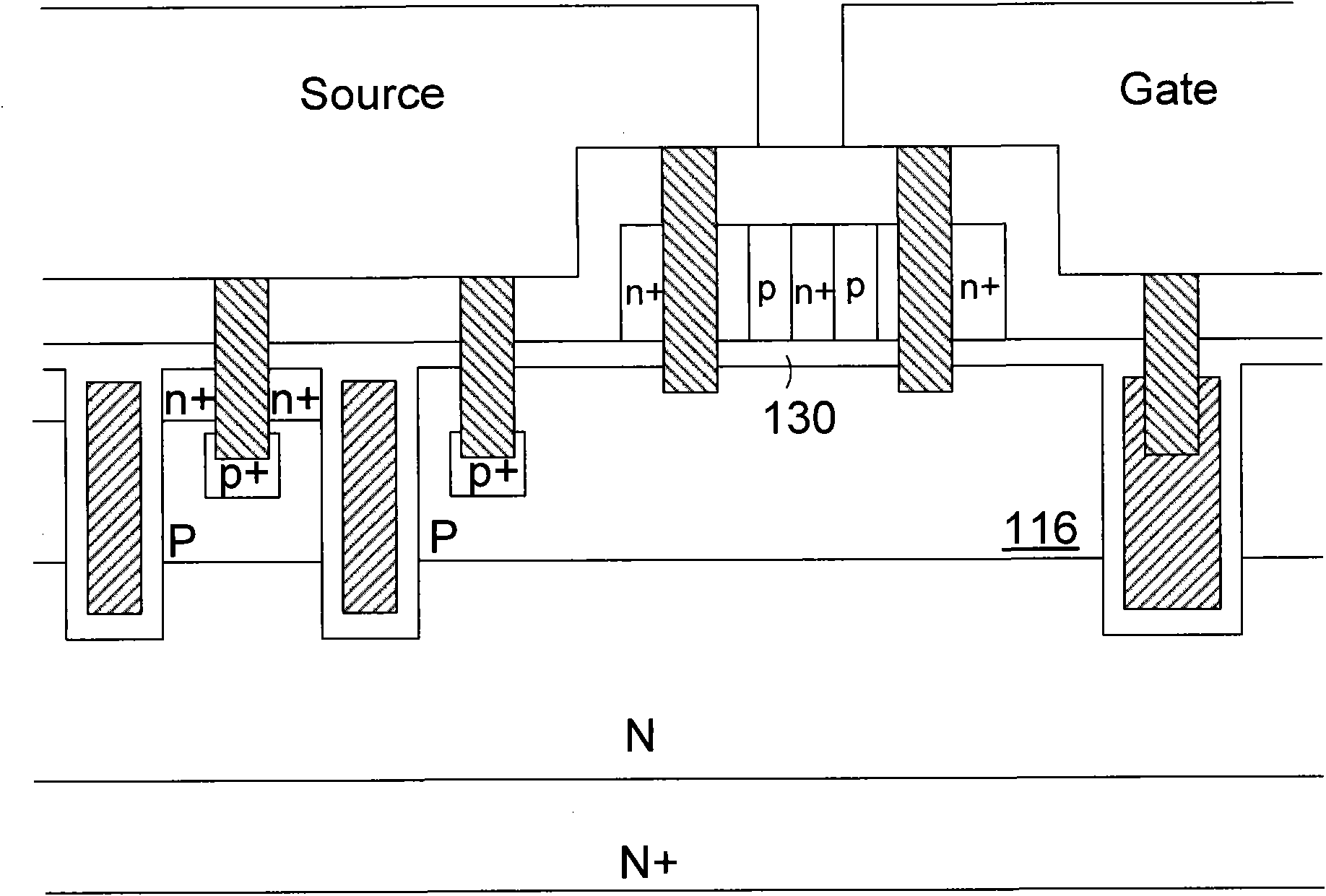

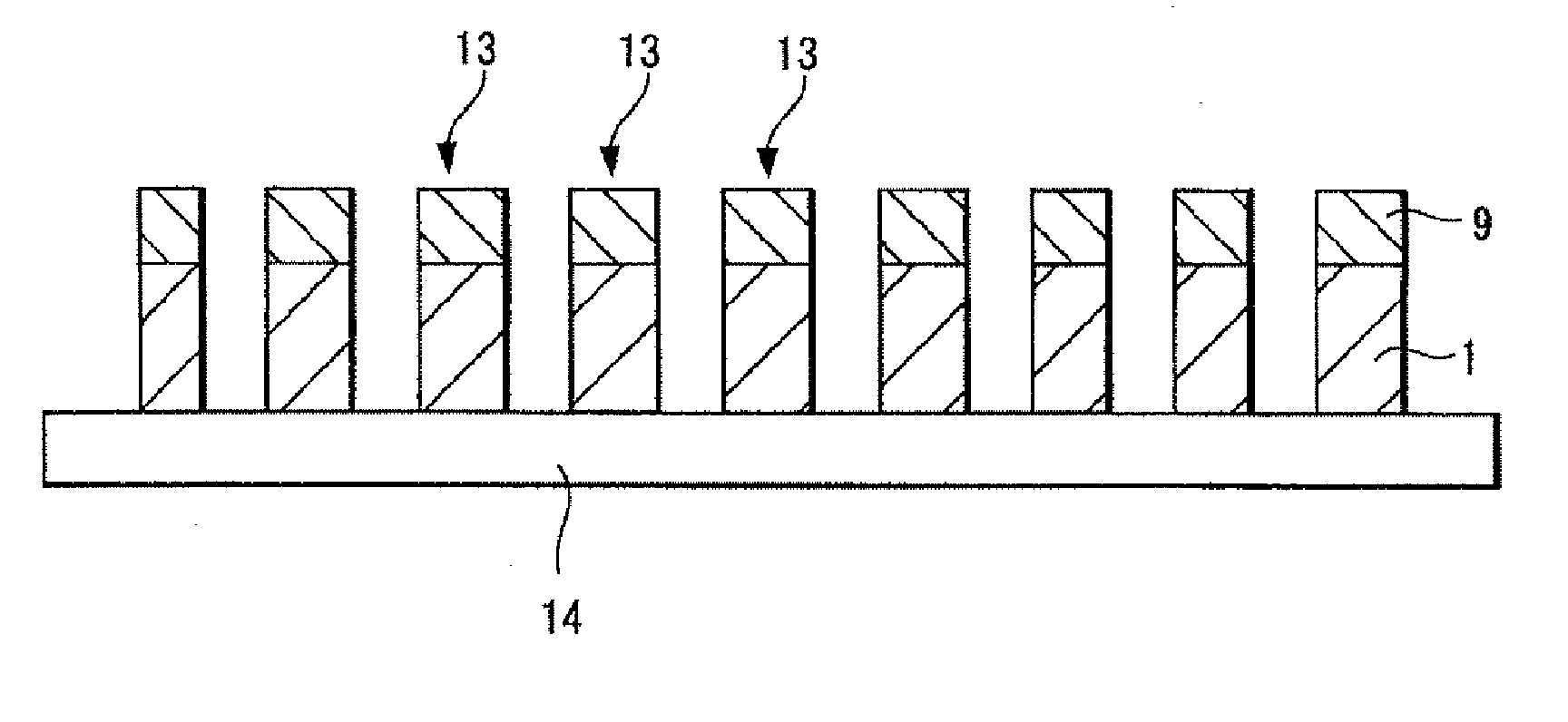

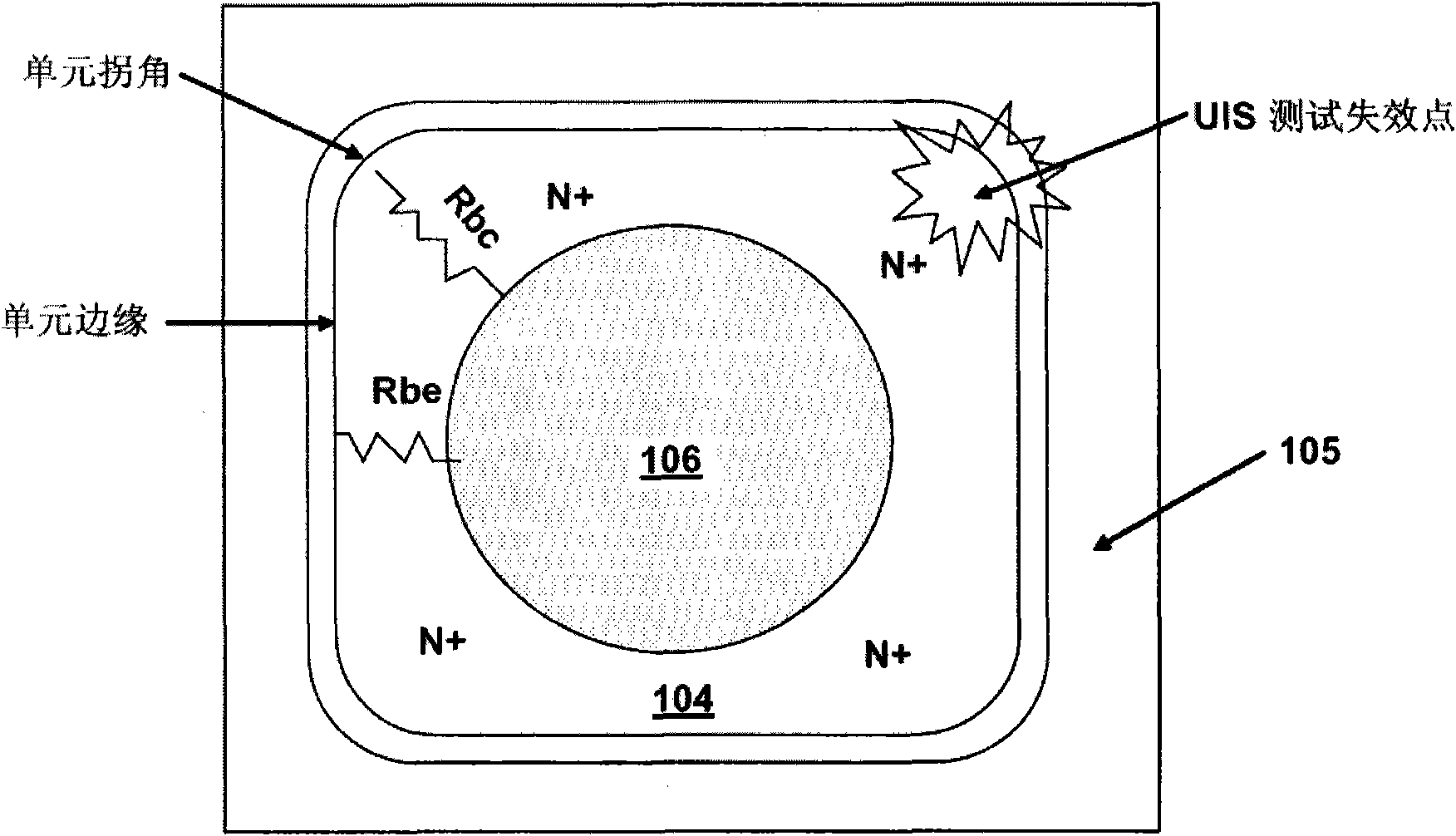

Trench MOSFET

ActiveCN101989602ASmall structural resistanceReduced injection efficiencyTransistorSemiconductor/solid-state device manufacturingTrench mosfetBody contact

The invention discloses a trench metal-oxide-semiconductor field effect transistor (MOSFET) structure and a manufacturing method thereof. Different from a source area of a trench MOSFET formed by a method in the prior art, the source area of the structure is formed by ion implantation and diffusion of majority carriers in the source area at the opening of a source body contact trench, so that the concentration distribution of the majority carriers of the source area is Gaussian distribution from the source body contact trench to a channel area along the surface of an epitaxial layer, and the junction depth of the source area is gradually reduced from the source body contact trench to the channel area. A trench MOSFET device with the structure has better avalanche breakdown property compared with the prior art. Correspondingly, in the manufacturing process, the invention discloses a manufacturing method only needing a mask plate for three times, and the production cost is greatly reduced.

Owner:FORCE MOS TECH CO LTD