Patents

Literature

228 results about "Resolution rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Resolution Rate refers to the rate at which your company fulfills service requests. It’s worth noting that customers may have different resolution expectations depending on the channel they use to contact you with a service request.

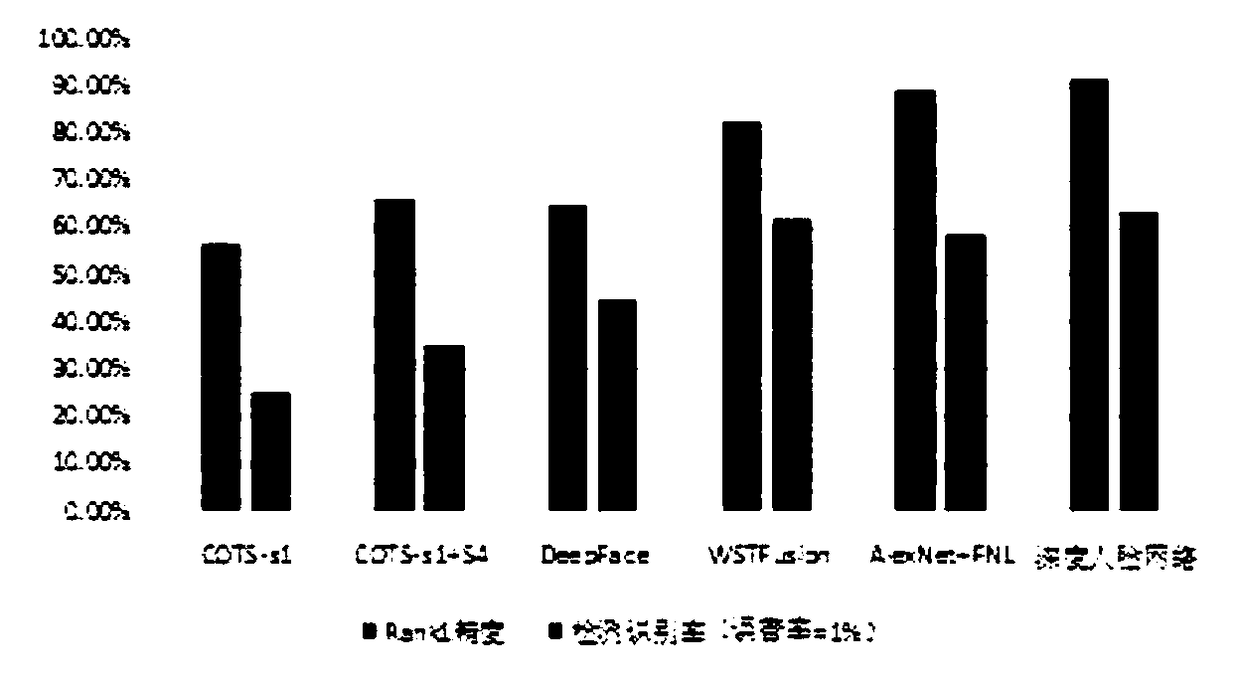

Face recognition method based on deep neural network

ActiveCN108304788AOptimize alignment resultsImprove recognition accuracyCharacter and pattern recognitionNeural architecturesFace detectionFeature extraction

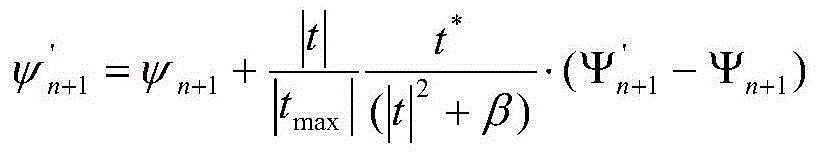

The invention relates to a face recognition method based on a deep neural network. A high recognition accuracy rate is realized while the network structure is simplified and the computing time cost islowered. The face recognition method comprises steps of face detection, face alignment, feature extraction and identity comparison. At the face detection and face alignment steps: An automatic codingnetwork (CFAN) from a coarse level to a fine level is used for detecting five facial key points; according to the detected five facial key points, rotary cutting and calibration are carried out to form a forward attitude face image with the pixel of 256*256*3; and on the basis of a plurality of cascaded stack type automatic coding networks, a face alignment result is optimized step by step at a face image with a higher resolution rate. At the feature extraction and identity comparison steps: a face feature is extracted by using a ten-layer deep face network, wherein the ten-layer deep face network consists of seven convolution layers and three fully connected layers; and distinguishing is carried out by training and testing.

Owner:SHAANXI JUYUN INFORMATION TECH CO LTD

Method for measuring forest by unmanned aerial vehicle aerial photography remote sensing

InactiveCN101008676AEasy to transportShort preparation time for launchElectromagnetic wave reradiationAviationImage resolution

This invention discloses one forest measurement method without human aviation cameral remote sensor, which adopts aviation device as remote platform without human and integrated digital codes camera, difference GPS and top platform, wherein, it uses digital camera technique to get high earth resolution rate without human remove image with large proportion rules fully in use of high flexible machine without special plane spot and capable of flying under clouds.

Owner:BEIJING FORESTRY UNIVERSITY

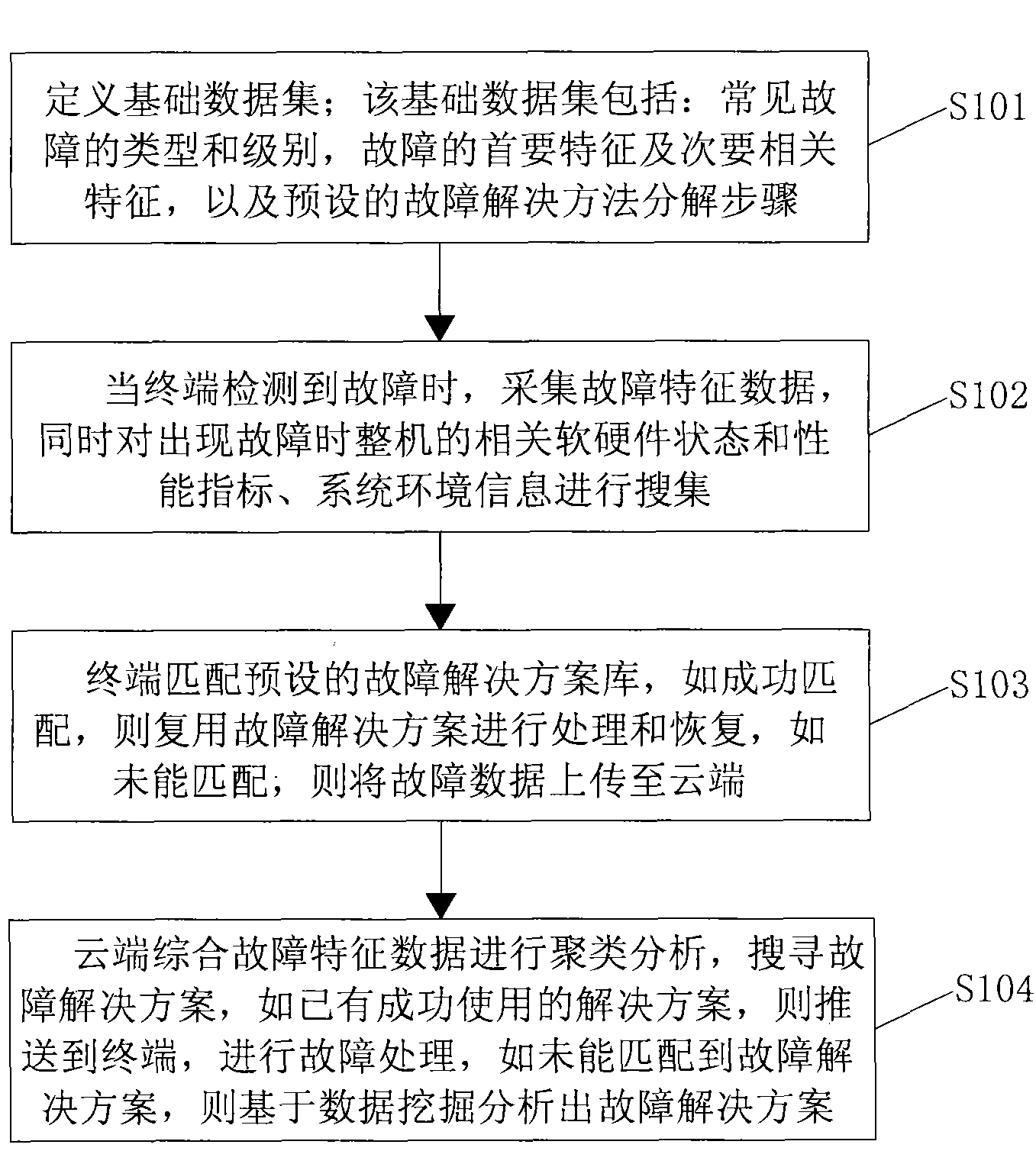

Terminal automatic fault diagnosis and restoration method on basis of data mining

InactiveCN103838637AImprove autonomous fault resolution capabilitiesImprove efficiencyFault responseSpecial data processing applicationsRestoration methodData acquisition

The invention discloses a terminal automatic fault diagnosis and restoration method on the basis of data mining. The terminal automatic fault diagnosis and restoration method includes that a terminal acquires fault characteristic data, a cloud side analyzes a fault resolution scheme on the basis of data mining and instructs the terminal to realize fault self-restoration, the terminal gains higher and higher fault self-resolution rate by continuously learning and accumulating fault characteristics and fault resolution schemes, and can automatically process most of normal faults. By the terminal automatic fault diagnosis and restoration method, conventional manual centralized judgment, analysis and processing is changed into fault reason analysis of data accumulation and mining, and on the basis of a fault resolution analysis and recommending mechanism of a parallel distribution and automatic 'exploration-feedback' mechanism and by 'learning' and 'sharing' fault characteristics and resolutions among the terminals, automatic fault resolution capability of the terminals are constantly improved, and finally, a centralized management mechanism which is quite easy to encounter bottleneck is transformed into a mode based on automatic management, diagnosis and restoration of various terminals.

Owner:JIANGSU ZHILIAN TIANDI TECHNOLOGY CO LTD

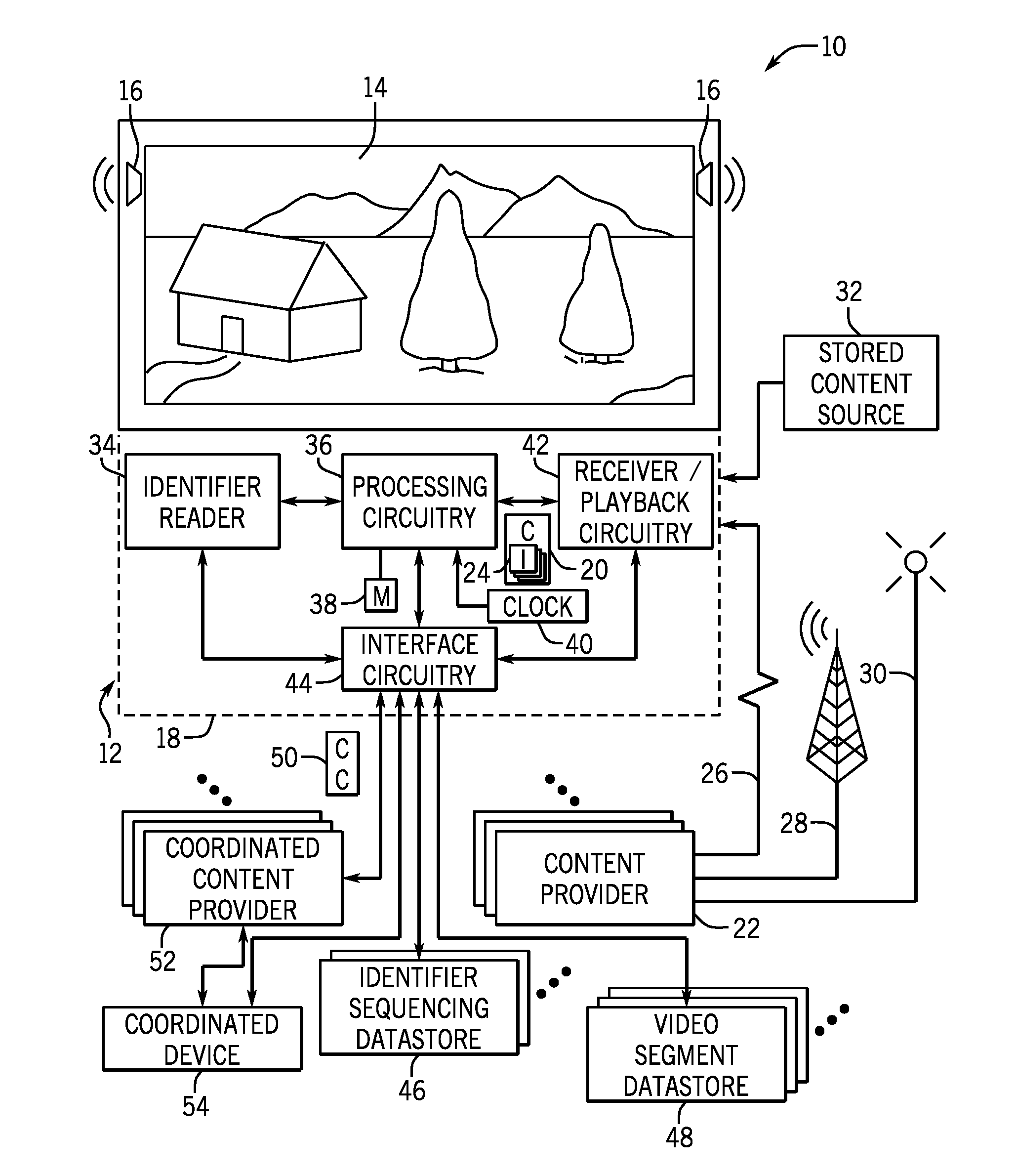

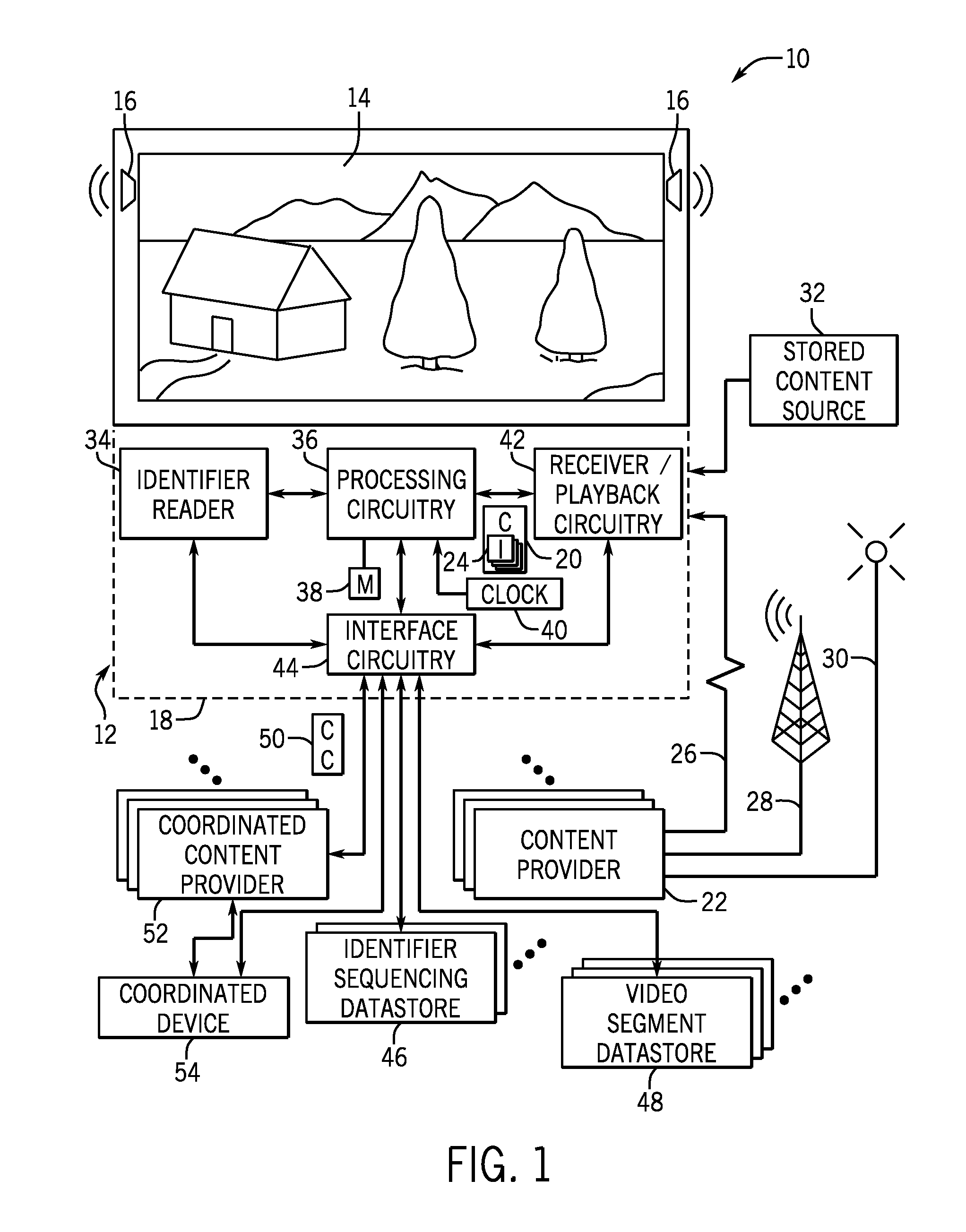

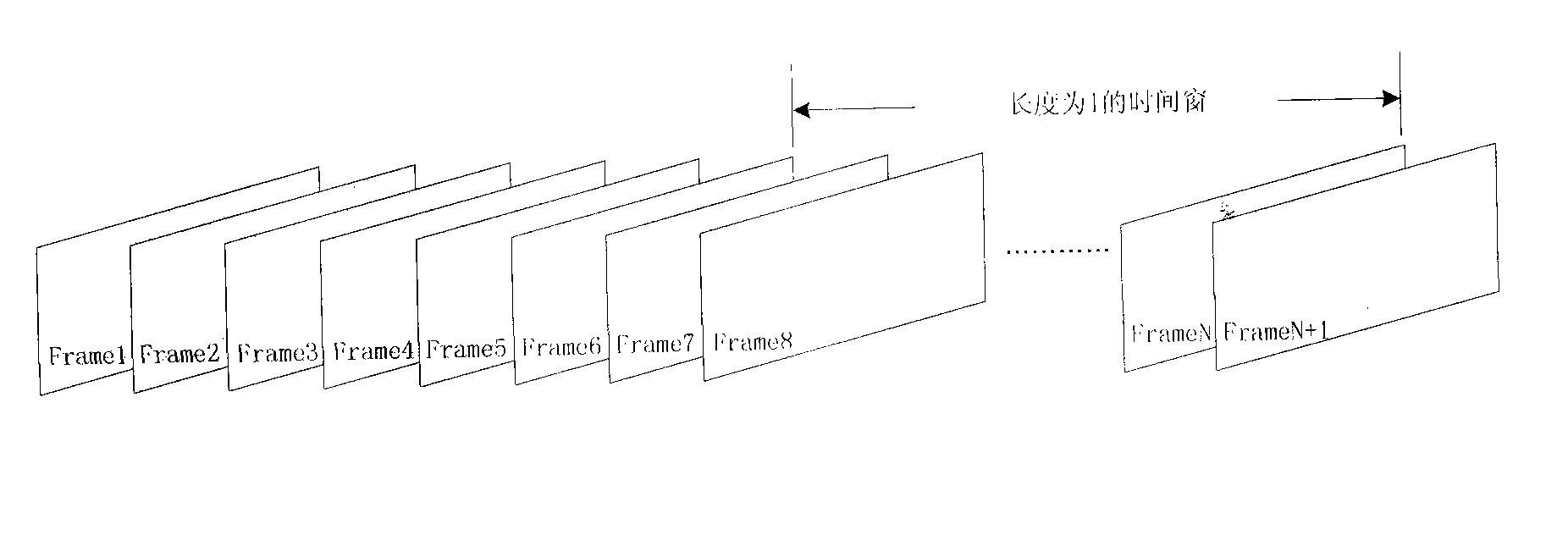

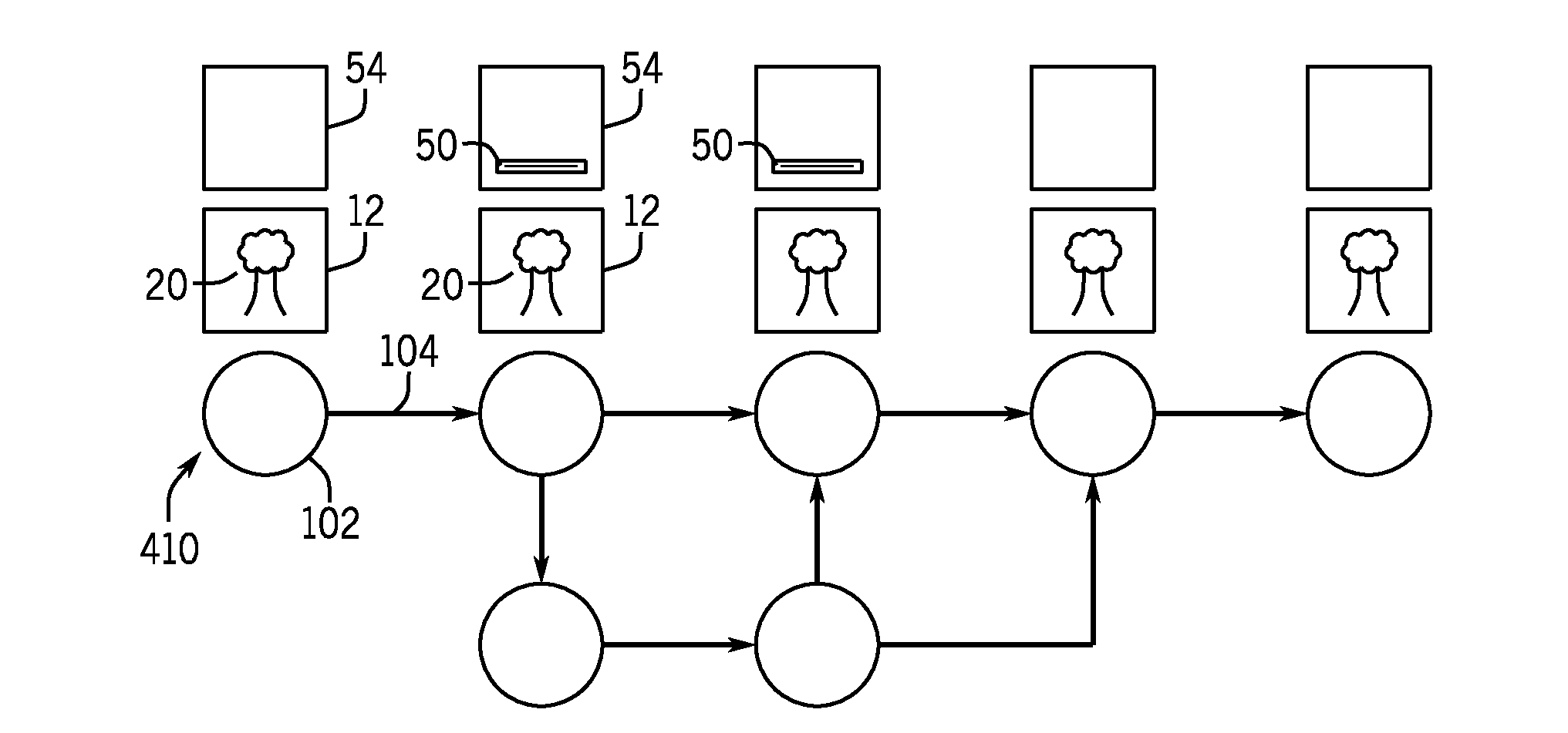

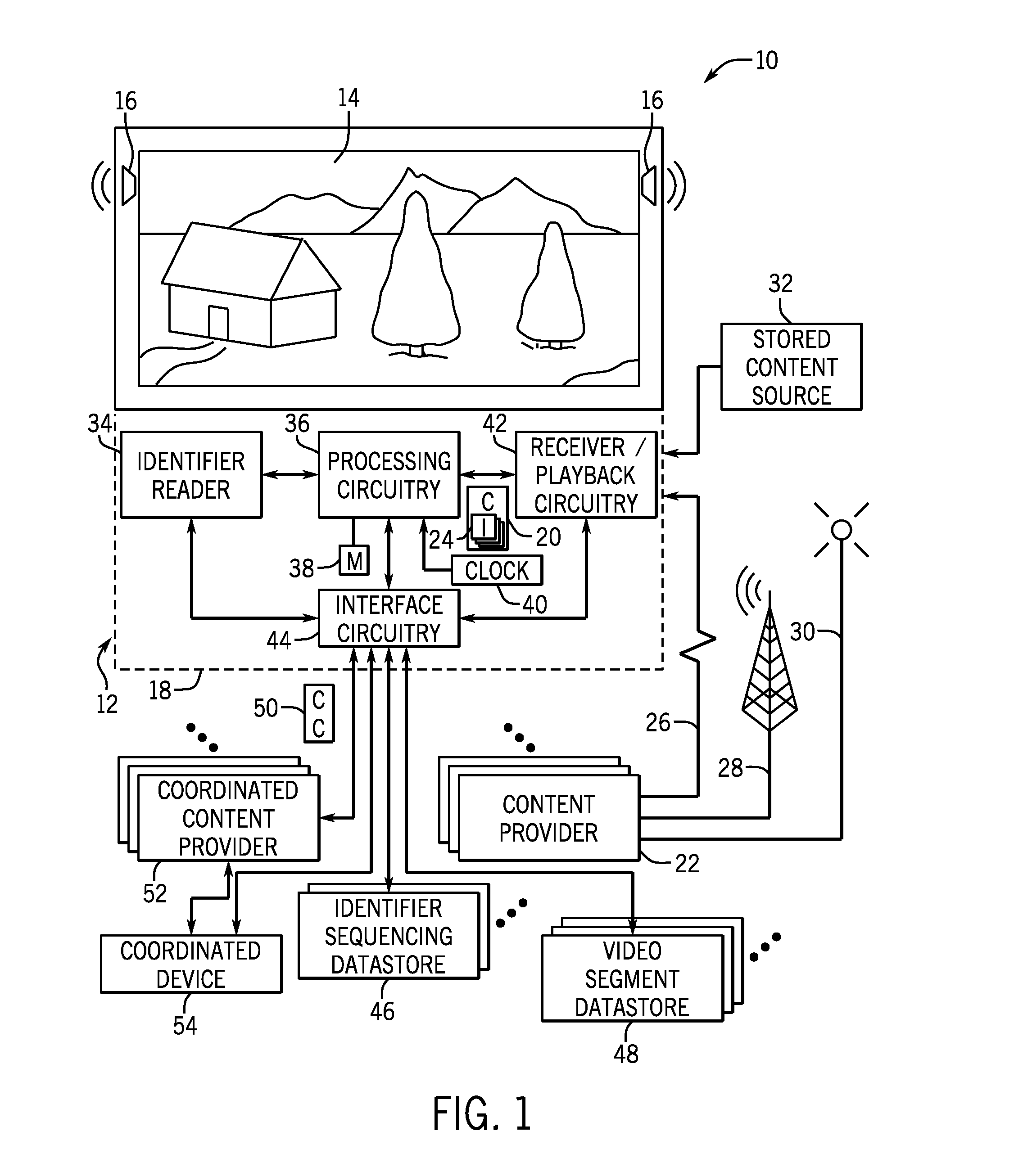

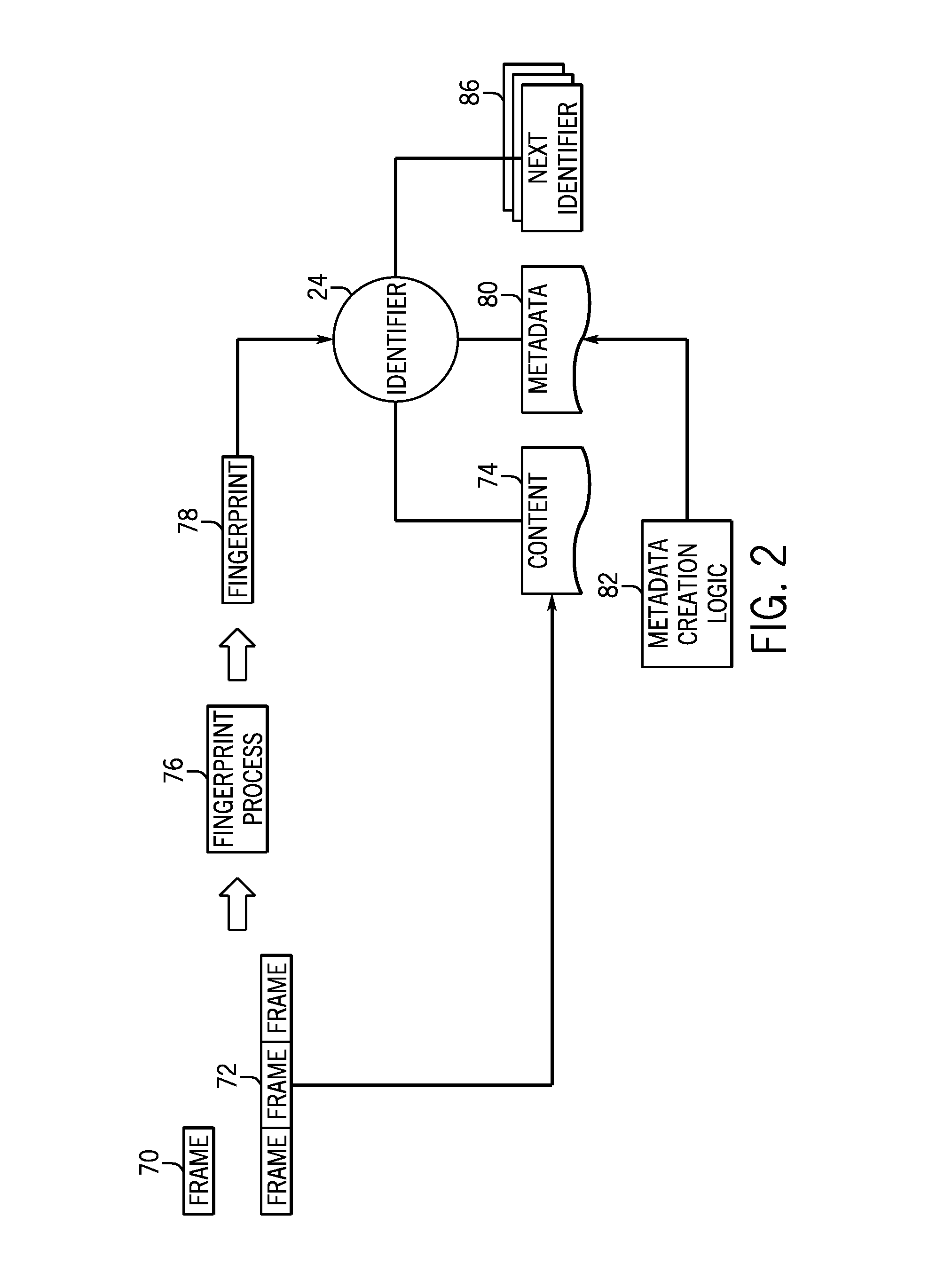

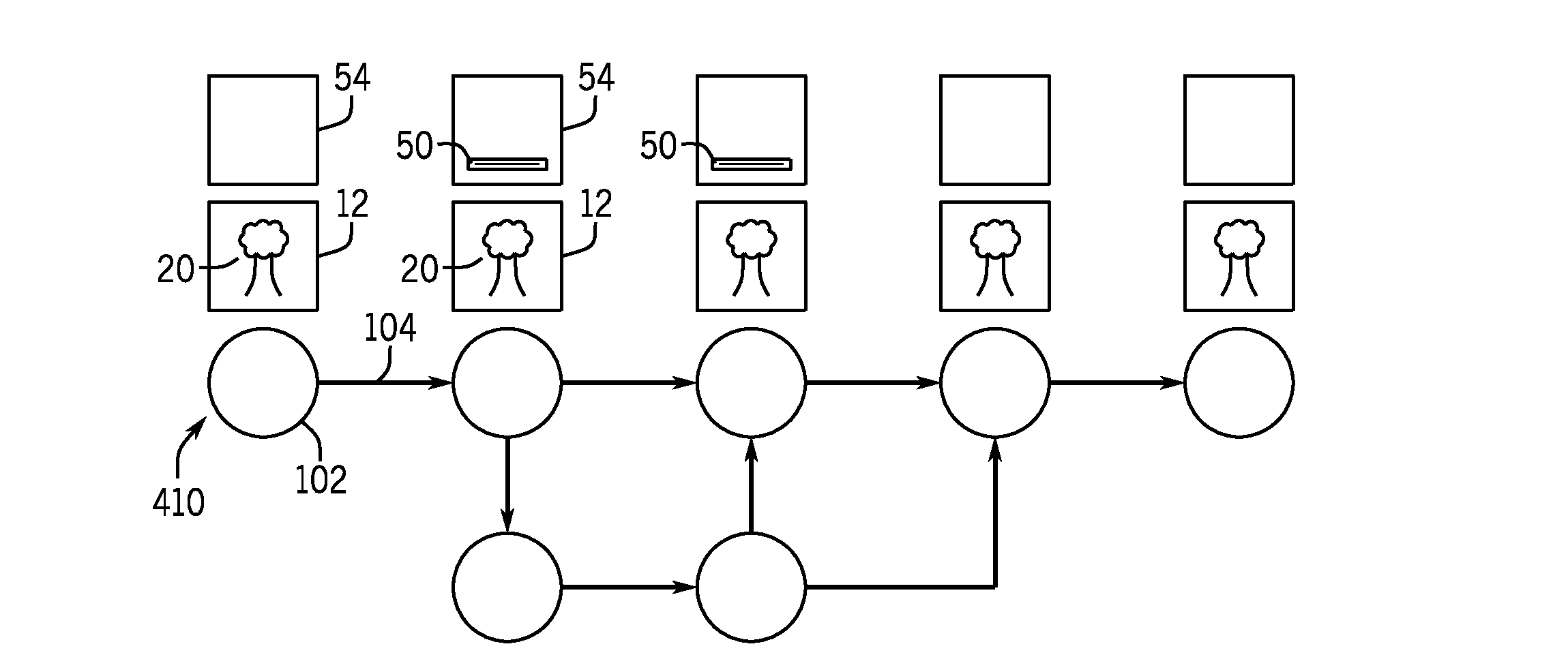

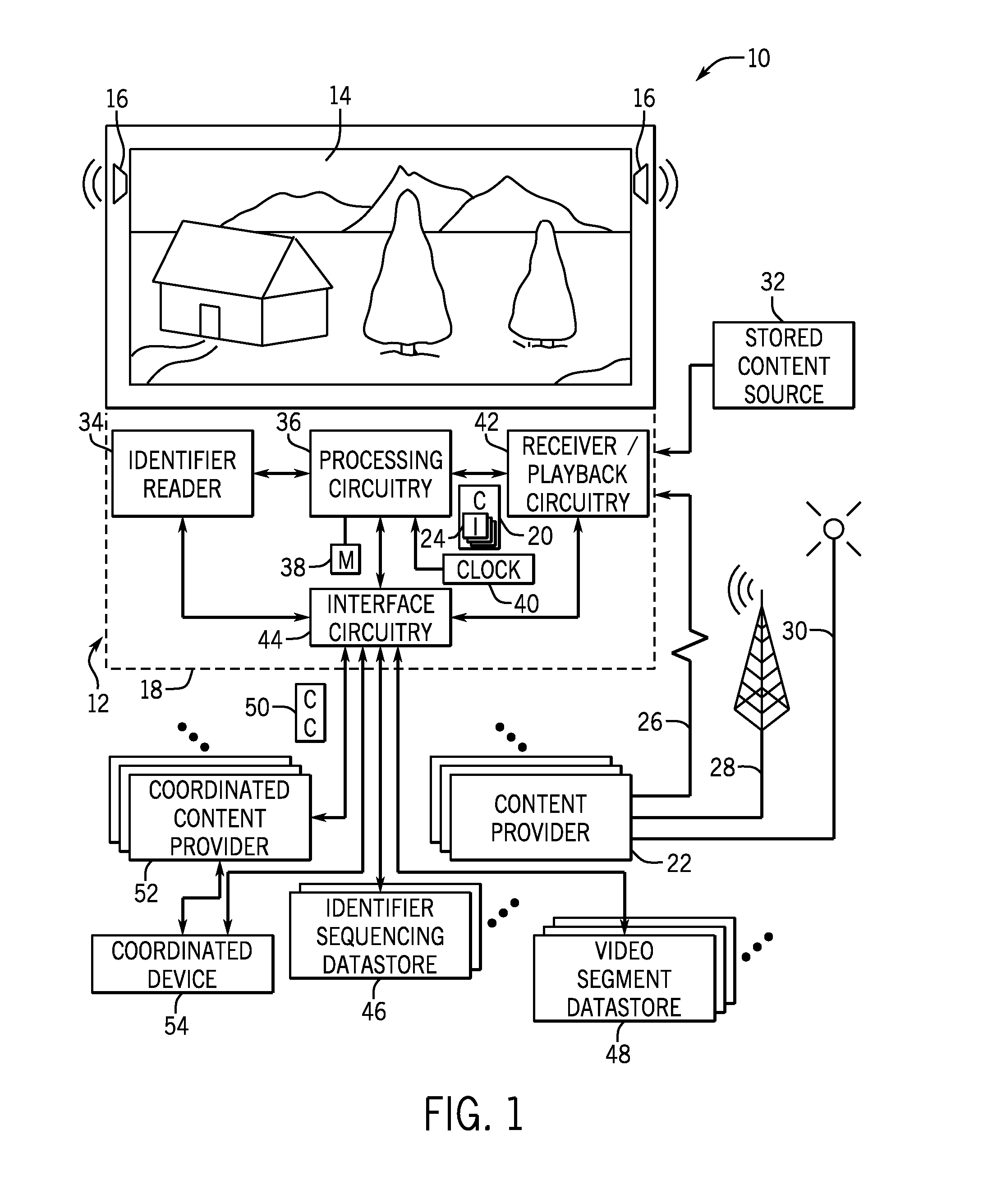

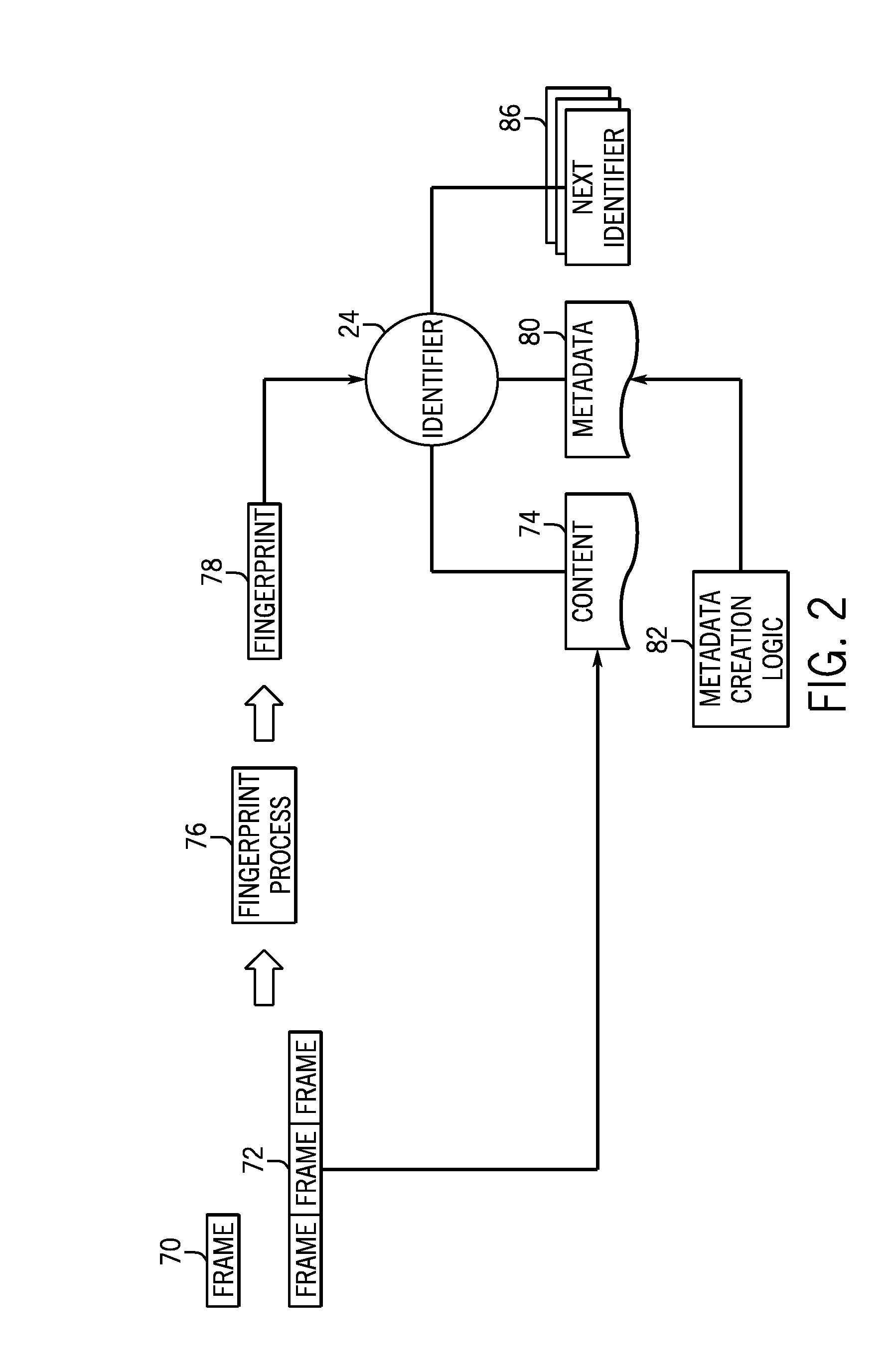

Fingerprint-defined segment-based content delivery

ActiveUS20150221336A1Television system detailsElectronic editing digitised analogue information signalsDigital contentFragment identifier

Digital content, such as video, audio, multimedia, and similar files may be segmented at a determined frame resolution rate and analyzed to determine a fingerprint for each content segment. An identifier that uniquely identifies each content segment may be determined based on the fingerprint of the respective content segment. The identifier may be associated with data relating to the content segment and with one or more identifiers that uniquely identify other content segments of the content. The content segment identifiers may be used to construct a content segment sequencing representation that represents the playback of the content segments in playback order.

Owner:NBCUNIVERSAL

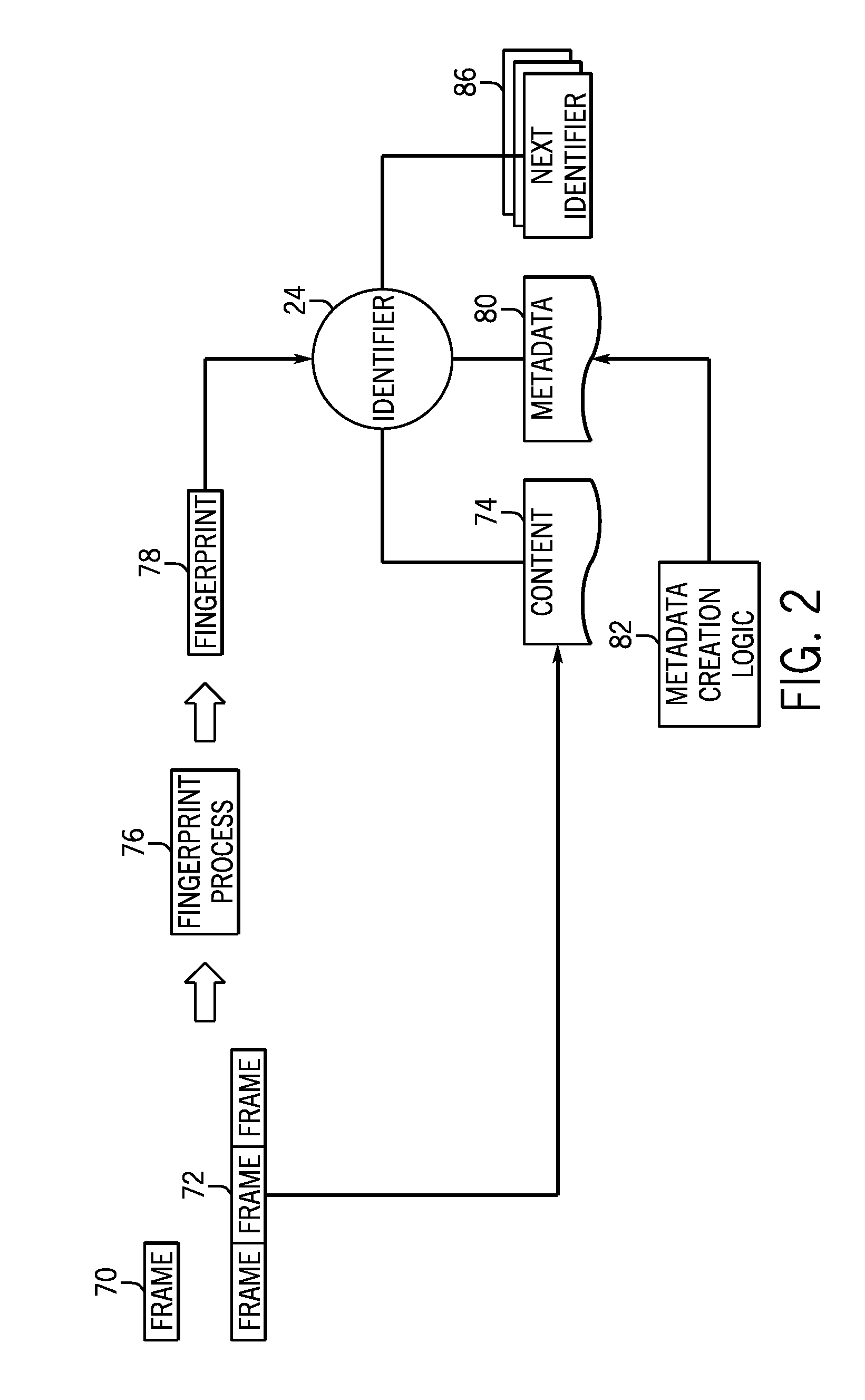

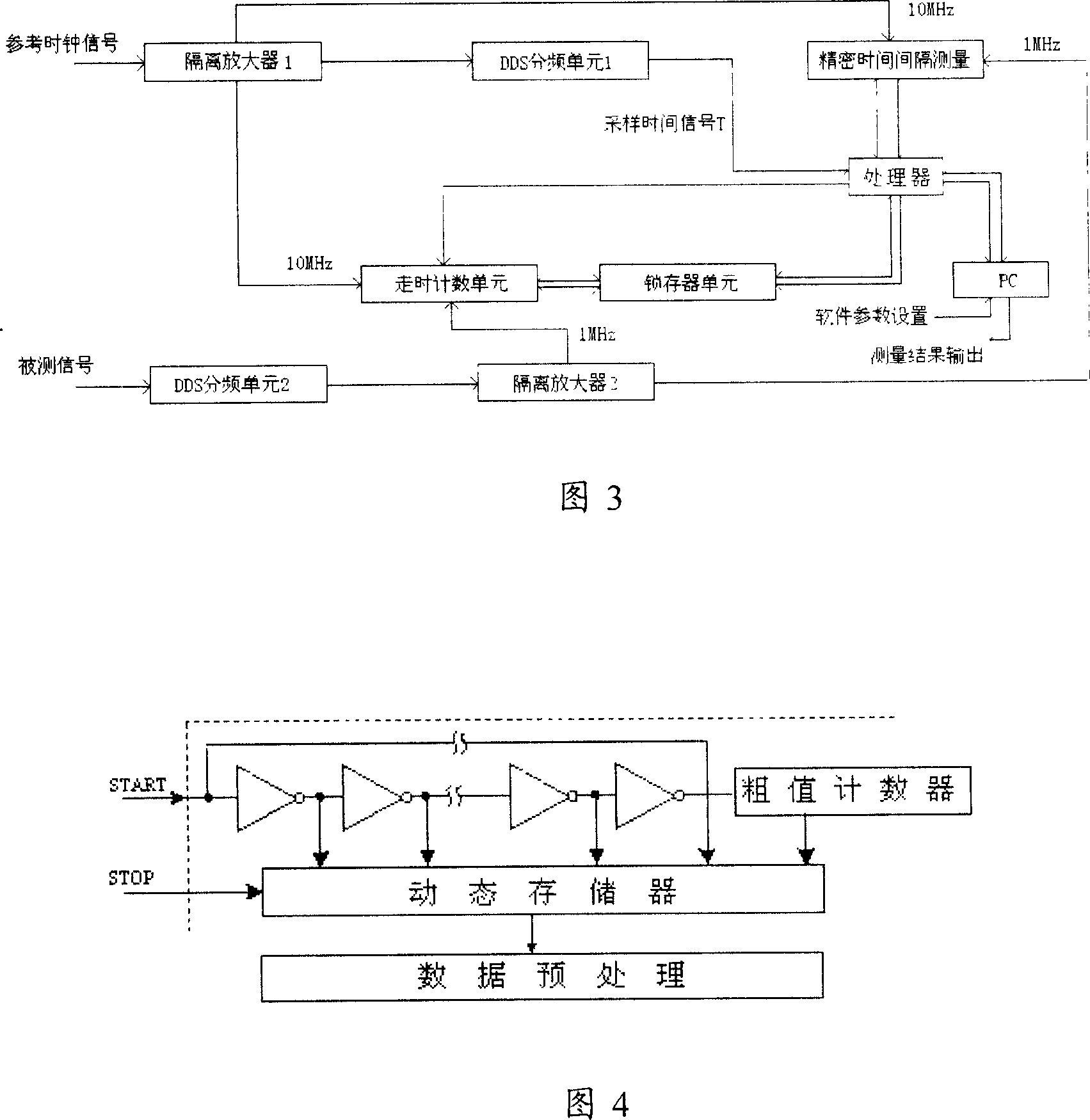

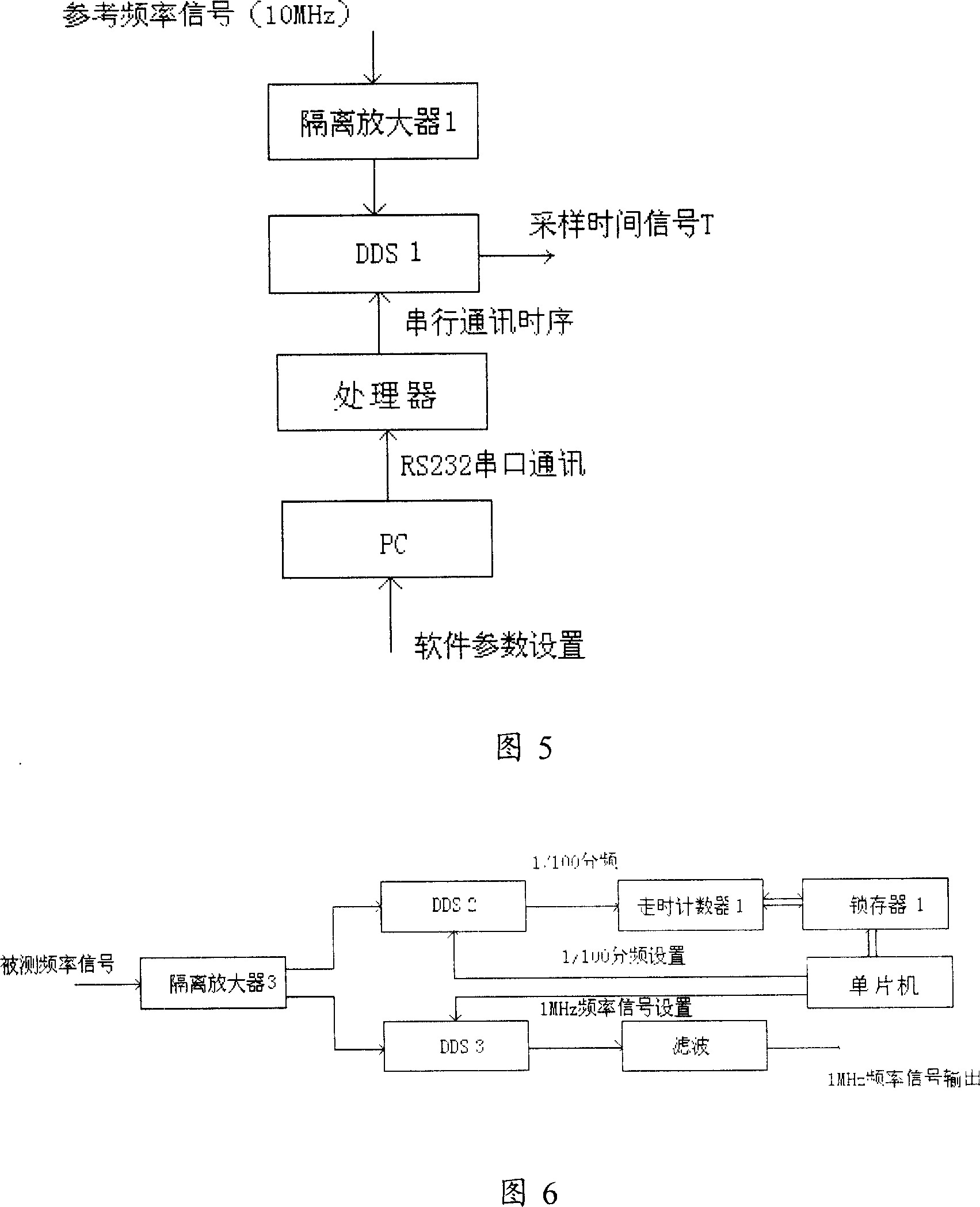

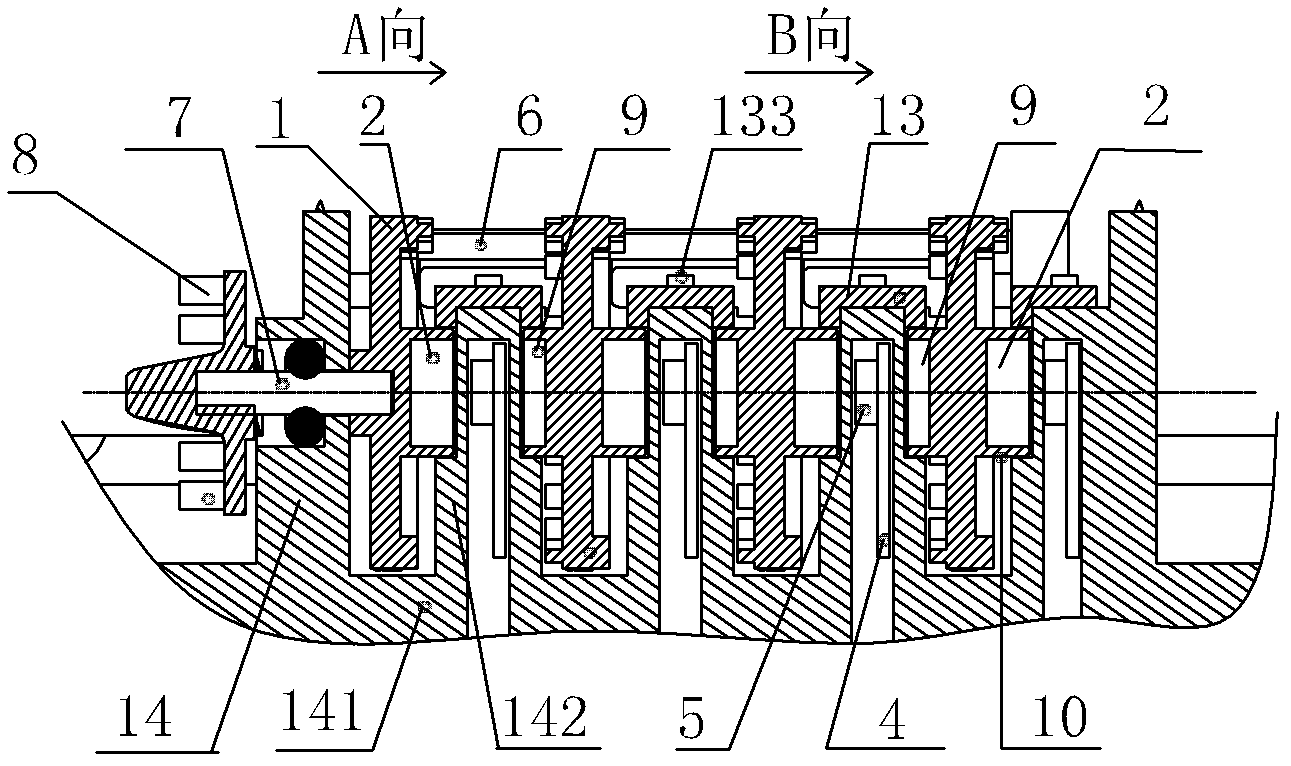

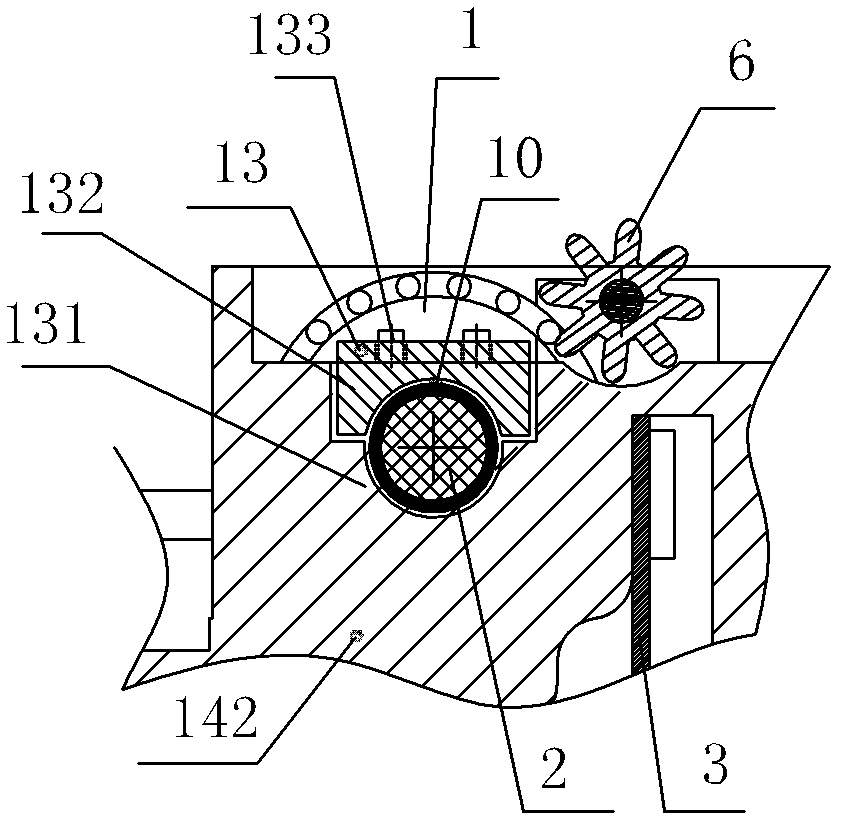

Improved method and apparatus for measuring stability of frequency of time domain signal

InactiveCN1963543AReasonable compositionSimple compositionFrequency to phase shift conversionHeterodyning/beat-frequency comparisonFrequency stabilizationProcess measurement

This invention discloses one method and device to improve time zone signals frequency stability measurement, which comprises the following steps: reference time signals are processed through DDS technique to get stable and accurate circle signals; expending measurement frequency signals range to get better reference signals and signals to be tested at fine time measurement; using DDS unit to process measurement frequency signals; when circle sample time singles come, according to fine time measurement module minimum resolution rate to test signals to be tested with reference time signals minimum phase difference to make the meter work to fulfill frequency signal measurement.

Owner:JIANGHAN UNIVERSITY

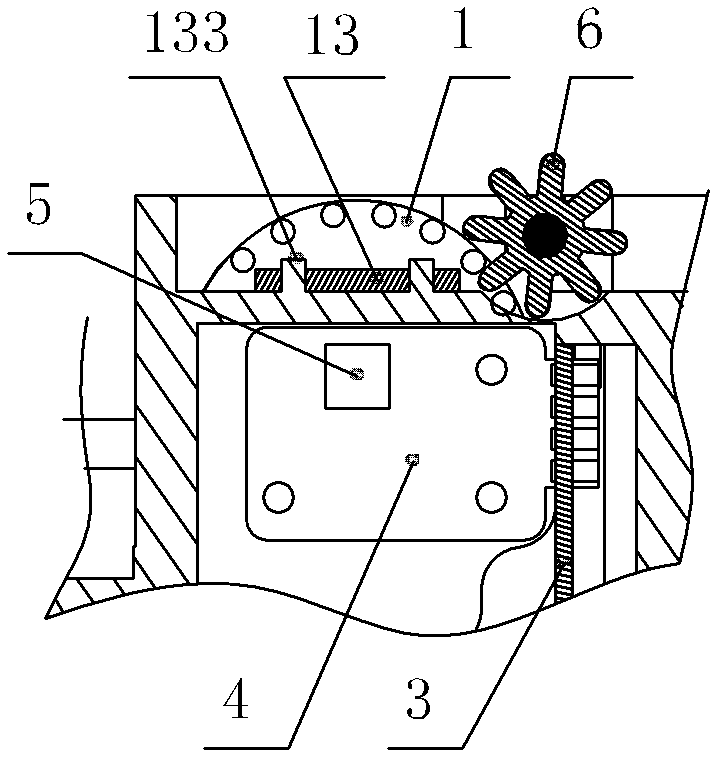

Electronic direct reading counter of meter

ActiveCN102628703AAccurate readingStable readingVolume indication and recording devicesCouplingImage resolution

An electronic direct reading counter of a meter comprises a plurality of number reading wheels and a plurality of carry coupling wheels installed on one side of the number reading wheels in parallel through a wheel shaft and corresponding to the number reading wheels. The electronic direct reading counter is characterized in that the plurality of number reading wheels are sectioned by the coaxial line and installed on a counter support at intervals, a permanent magnet and a magnetic shielding plate are respectively arranged on shaft core parts on two sides of each number reading wheel, a magnetic induction angle sensor corresponding to the coaxial line of the shaft core permanent magnet of the number reading wheel is respectively arranged between the number reading wheels, and the magnetic induction angle sensor is installed on an assembly circuit board of the magnetic induction angle sensor in welding mode. The electronic direct reading counter has the advantages of being capable of achieving 360-degree full-circle measurement of the number reading wheel and accurate and stable in reading. The measurement resolution rate depends on analog-to-digital conversion actual accuracy. The number wheel carries '0' when meeting '9', and number is read from low order to high order in carry. Enough referenced information is provided, repeated code and error code cannot happen, electronic components are reduced substantially, and product fault risk is greatly reduced.

Owner:SHENZHEN JASON DIGITAL TECH CO LTD

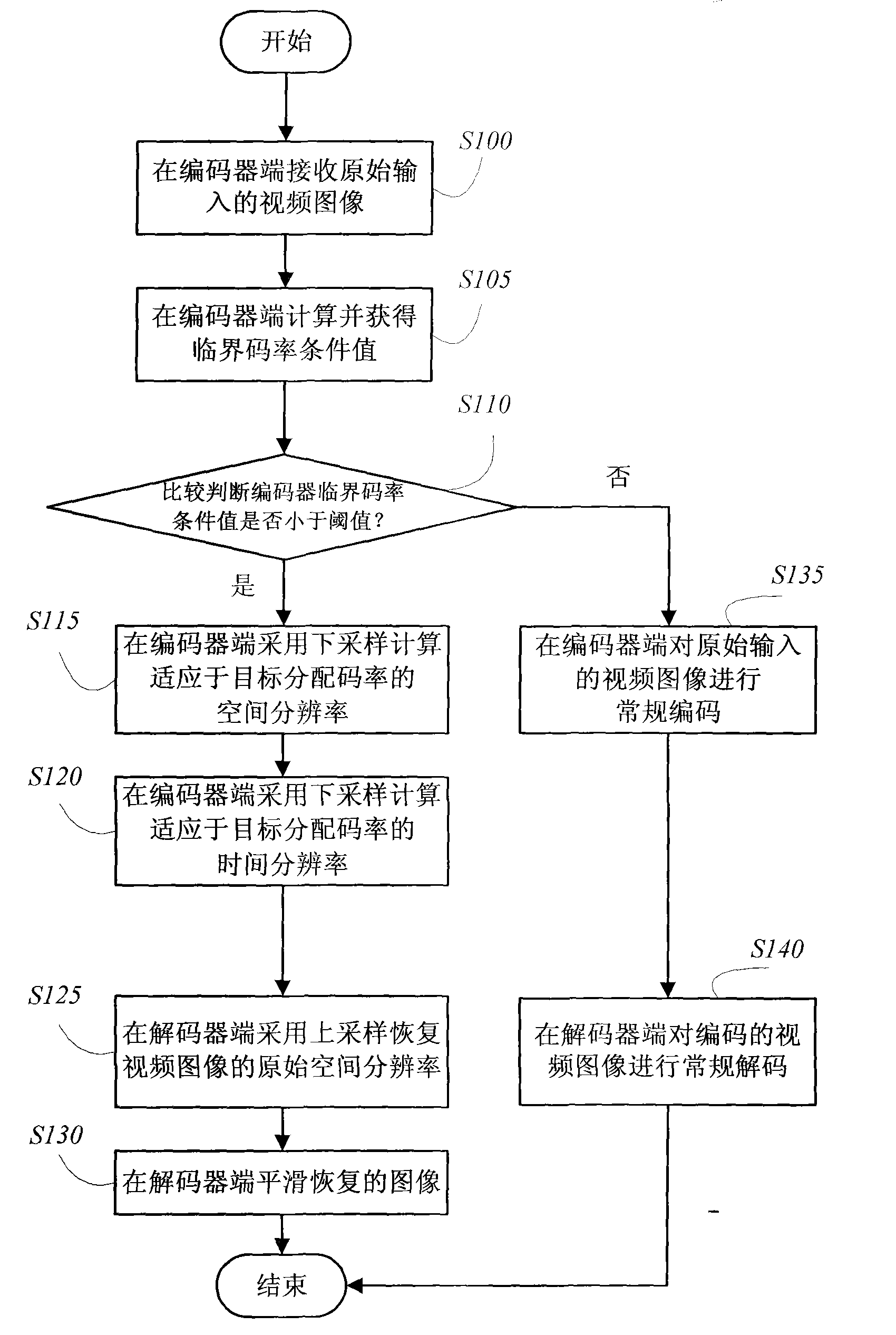

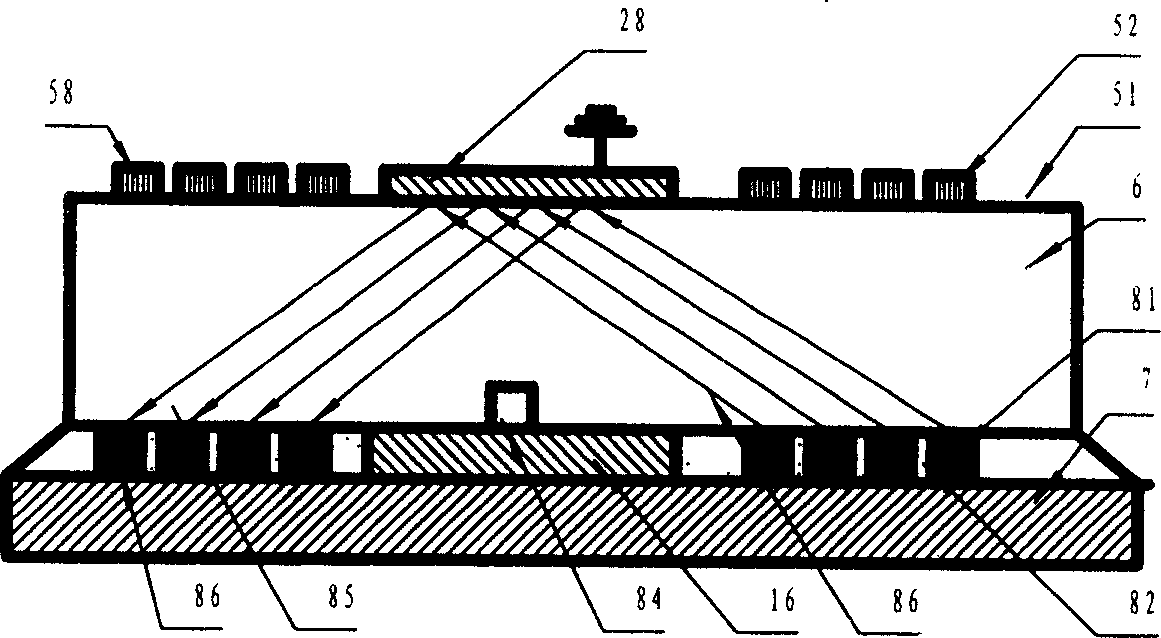

Image processing method of self-adaptive time domain and spatial domain resolution ratio frame

InactiveCN101778275AEasily damagedReduce computational complexityPulse modulation television signal transmissionDigital video signal modificationTime domainImaging processing

The invention relates to the field of video image processing and provides an image processing method of a self-adaptive time domain and spatial domain resolution ratio frame. The method comprises the following steps: A. an encoder computes and obtains the conditional value of the critical code rate according to the variation of an input video image and a target distribution code rate; B. the encoder compares the conditional value and the threshold value of the critical code rate; if the conditional value of the critical code rate is less than the threshold value, i.e. when the target distribution code rate is less than the critical code rate, the image resolution ratio which is adaptive to the target distribution code rate is obtained through the under-sampling; otherwise, the conventional coding processing is carried out; and C. the encoder recovers and receives the original resolution rate of the image through the upsampling and carries out the conventional coding processing. The method does not cause that the imaged decoded by the encoder produces serious distortion caused by the over-compression or over-quantization of the encoder in the situation of ensuring the low code rate.

Owner:SHENZHEN TEMOBI SCI &TECH

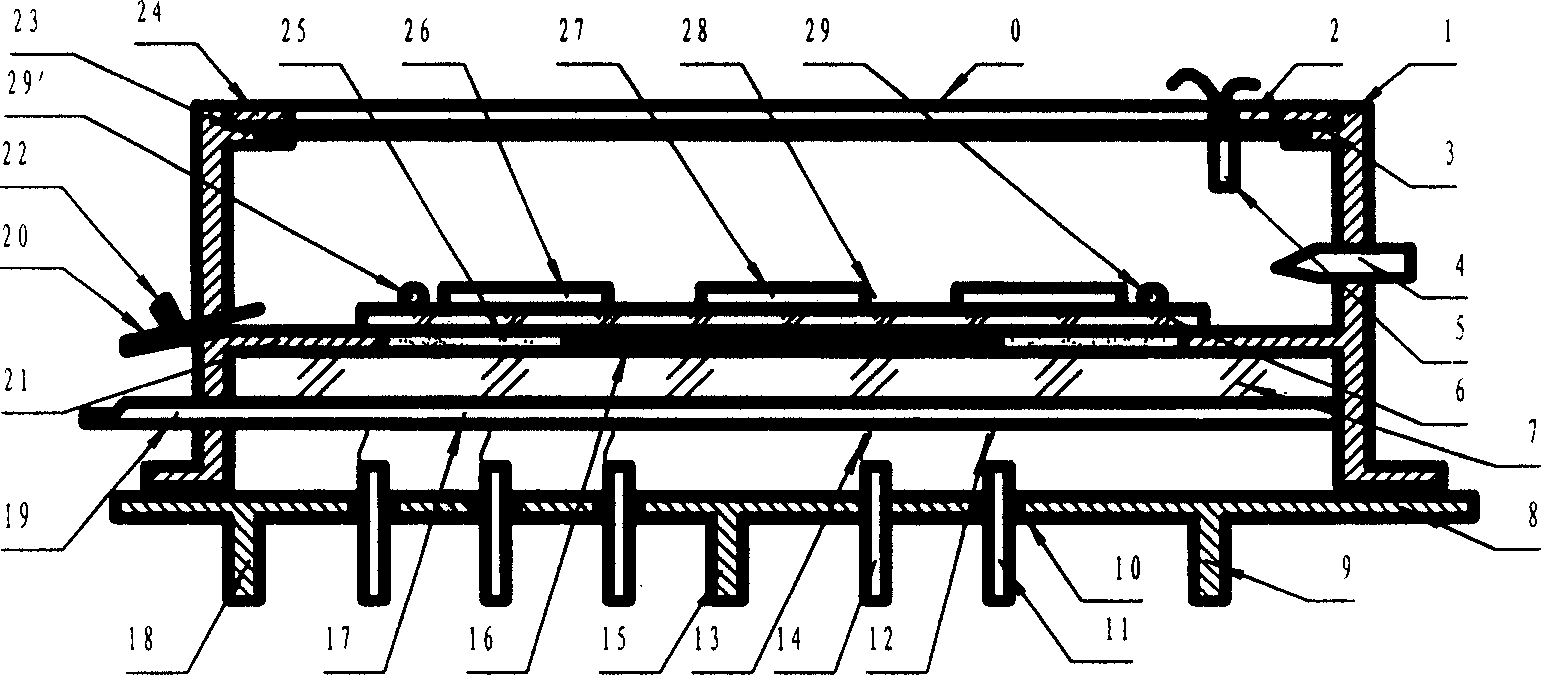

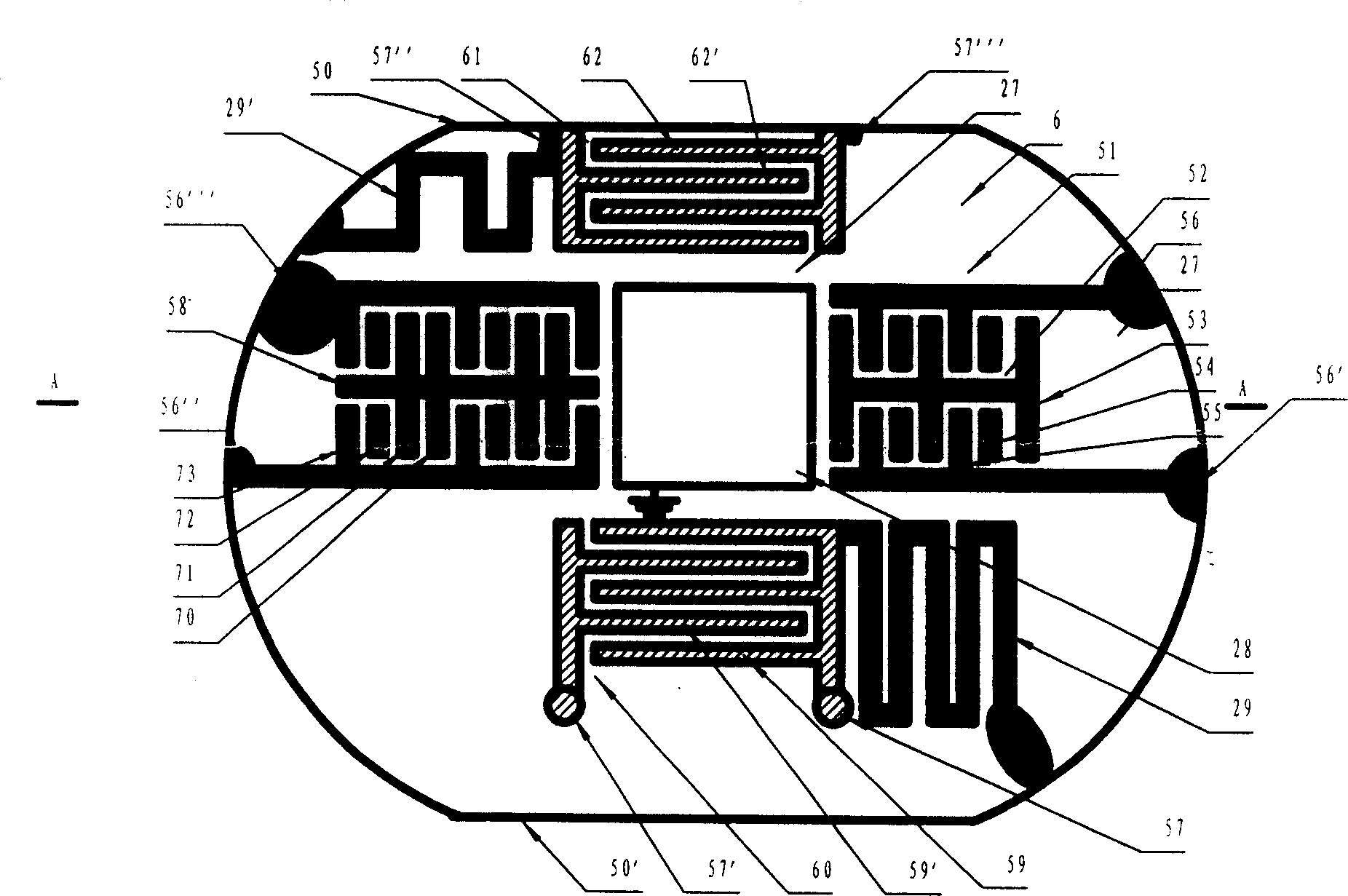

Monolithic piezoelectric and ferroelectric crystal multifunctional dew point humidity sensor

This invention discloses a single disk piezoelectricity electrical transistor multi-function dew-point humidity sensor, which comprises the following: sensor outer shell with Kefa tube shell 1 and Kefa tube socket 8; piezoelectricity transistor sensitive element 6 fixed inside the sensor shell; semi-conductive cooling device 7 of the outer single machine control and outer interface legs of the Kefa tube socket 8. It realizes the cooling and heat feedback control, sensitive characteristics compensation and adjusting signals and conversion, which improve the accuracy, resolution rate and dynamic range and pollution status identification of the sensors.

Owner:王世光 +1

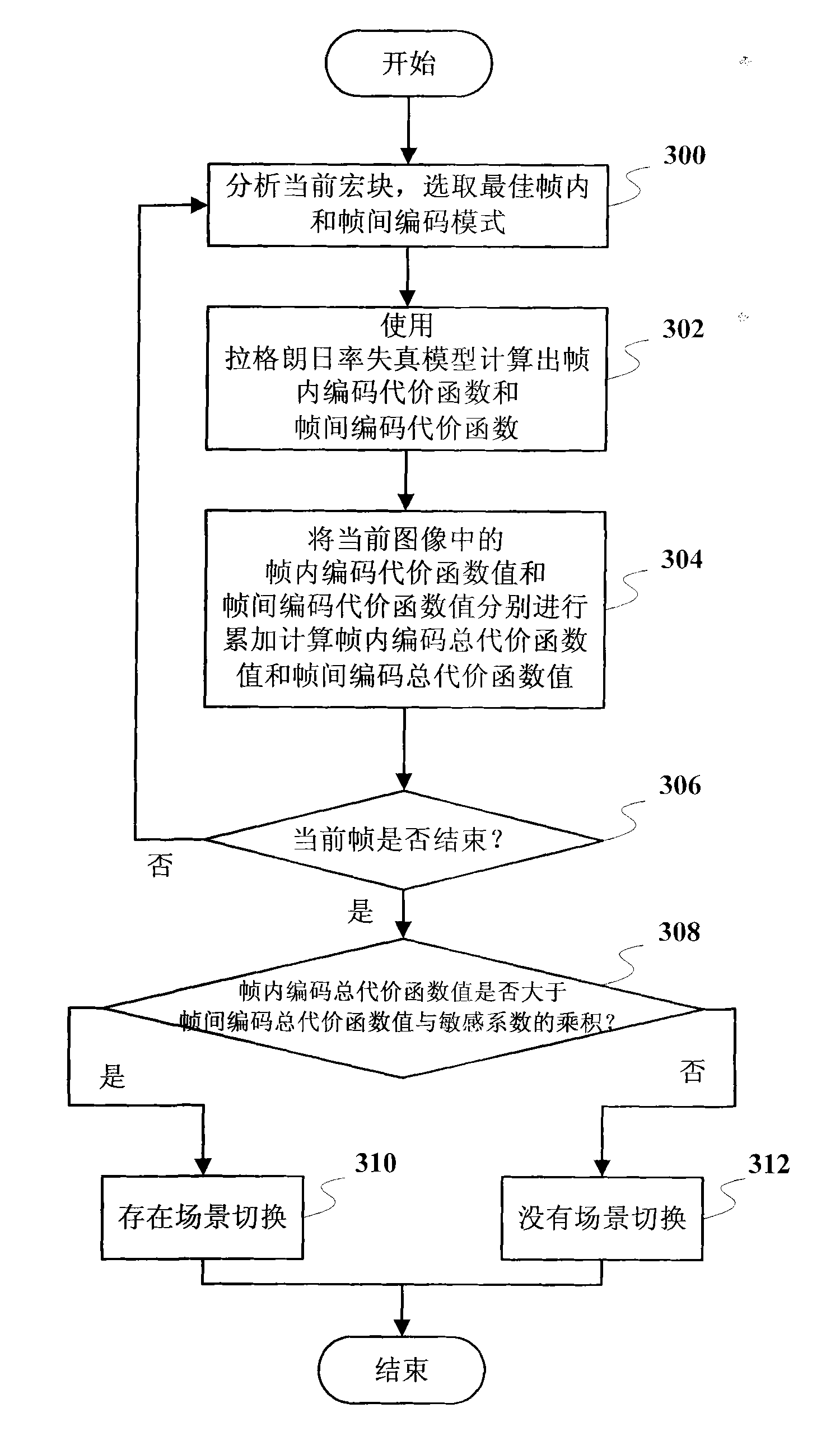

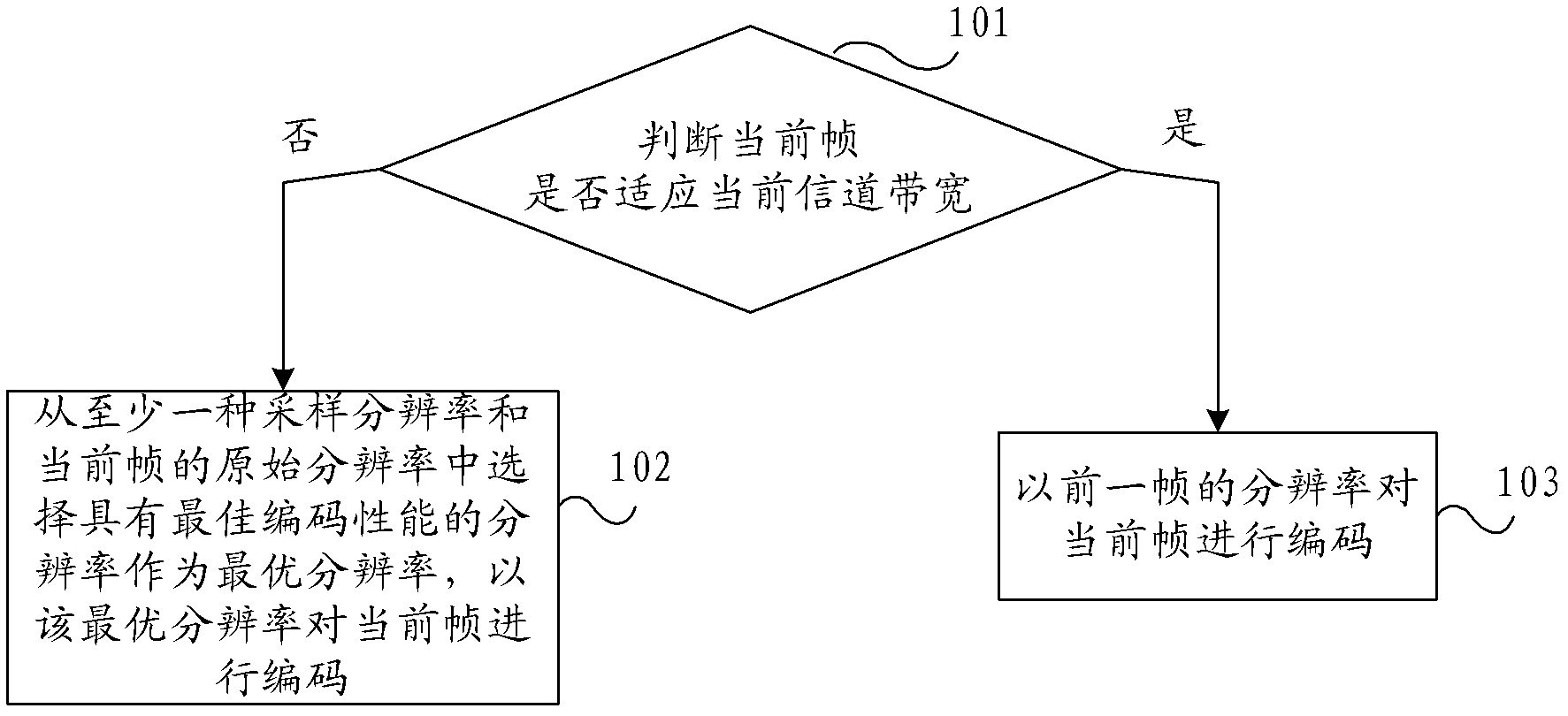

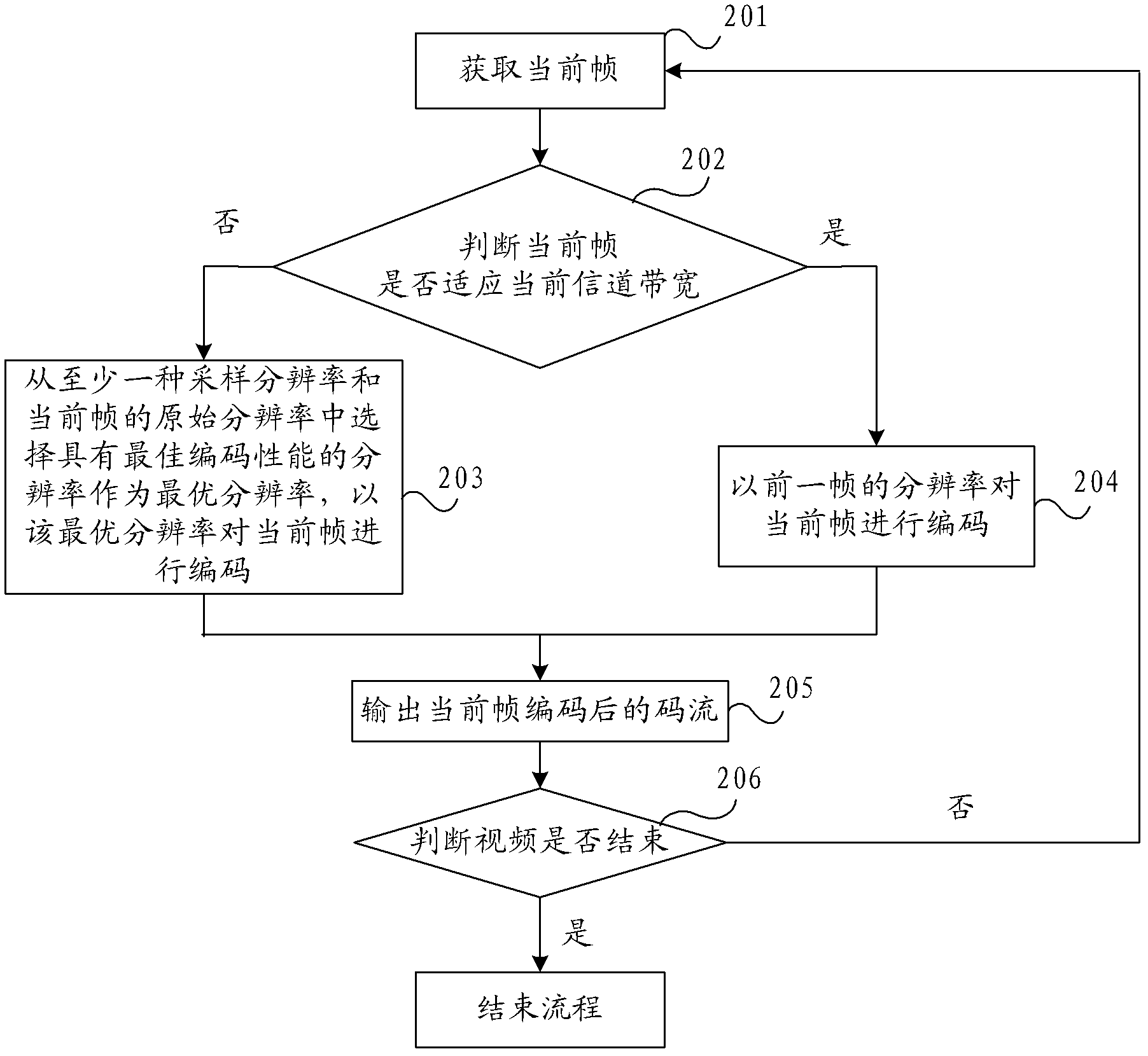

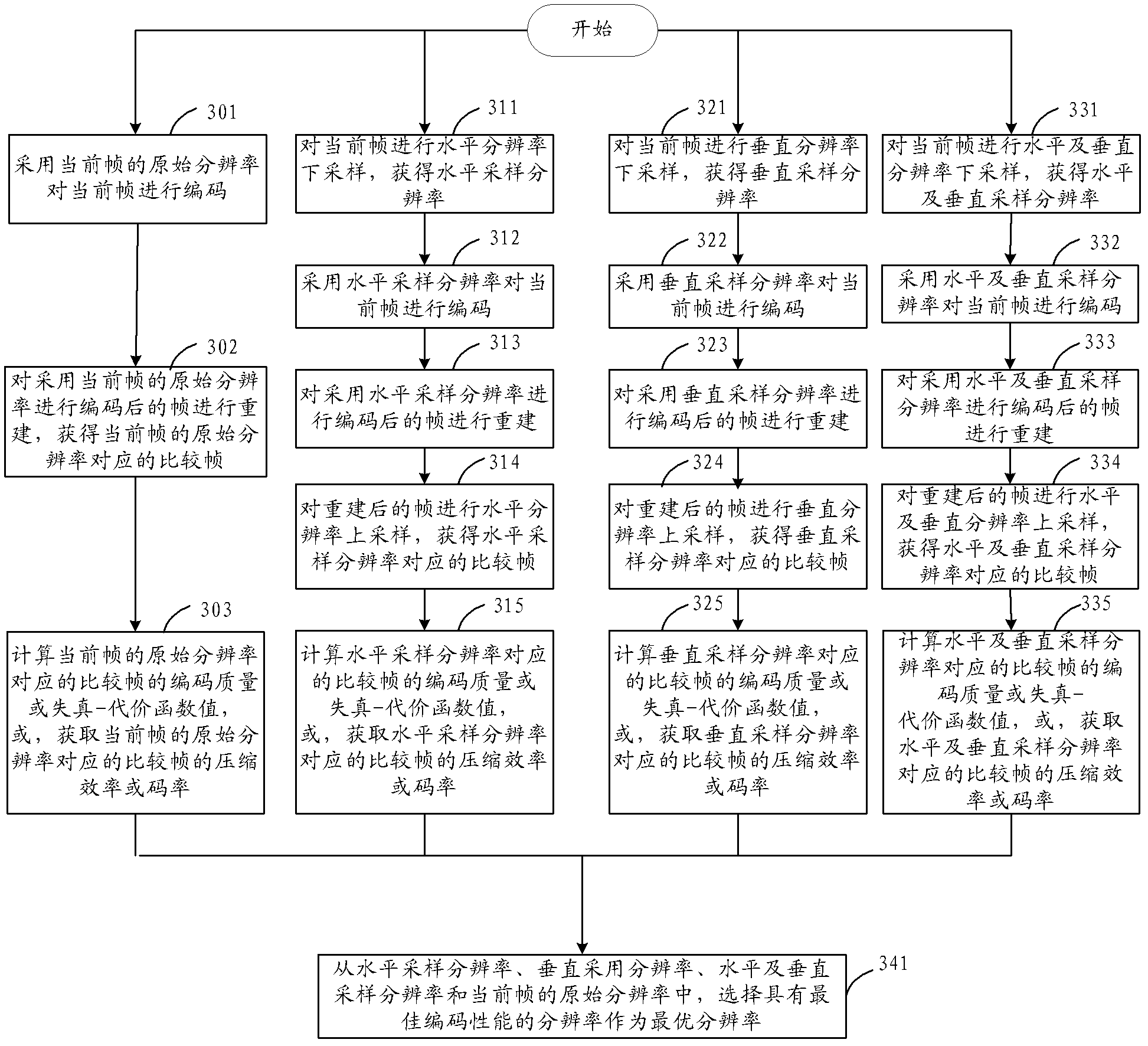

Video coding method and video coder

ActiveCN102883157AQuality improvementAvoid block effectTelevision systemsDigital video signal modificationCurrent channelVideo encoding

The invention provides a video coding method and a video coder. The video coding method comprises the following steps: judging whether a current frame is adapted to a current channel bandwidth; if so, judging that the current frame is not an inter domain routing protocol (IDR) frame; otherwise, judging that the current frame is an IDR frame; when the current frame is the IDR frame, selecting an optimal resolution ratio from a sampling resolution ratio and an original resolution ratio of the current frame; when the current frame is not the IDR frame, coding the current frame at the resolution ratio of a former frame. By adopting the video coding method and the video coder provided by the invention, the best resolution ratio can be selected timely according to the current channel status; the block effect caused by adopting a fixed resolution rate under a narrow band condition is avoided, and the video coding quality is improved.

Owner:ZHEJIANG UNIV +1

Fingerprint-defined segment-based content delivery

ActiveUS20150220636A1Video data indexingDigital data processing detailsDigital contentFragment identifier

Digital content, such as video, audio, multimedia, and similar files may be segmented at a determined frame resolution rate and analyzed to determine a fingerprint for each content segment. An identifier that uniquely identifies each content segment may be determined based on the fingerprint of the respective content segment. The identifier may be associated with data relating to the content segment and with one or more identifiers that uniquely identify other content segments of the content. The content segment identifiers may be used to construct a content segment sequencing representation that represents the playback of the content segments in playback order.

Owner:NBCUNIVERSAL

Fingerprint-defined segment-based content delivery

ActiveUS20150220635A1Video data indexingDigital data processing detailsDigital contentFragment identifier

Digital content, such as video, audio, multimedia, and similar files may be segmented at a determined frame resolution rate and analyzed to determine a fingerprint for each content segment. An identifier that uniquely identifies each content segment may be determined based on the fingerprint of the respective content segment. The identifier may be associated with data relating to the content segment and with one or more identifiers that uniquely identify other content segments of the content. The content segment identifiers may be used to construct a content segment sequencing representation that represents the playback of the content segments in playback order.

Owner:NBCUNIVERSAL

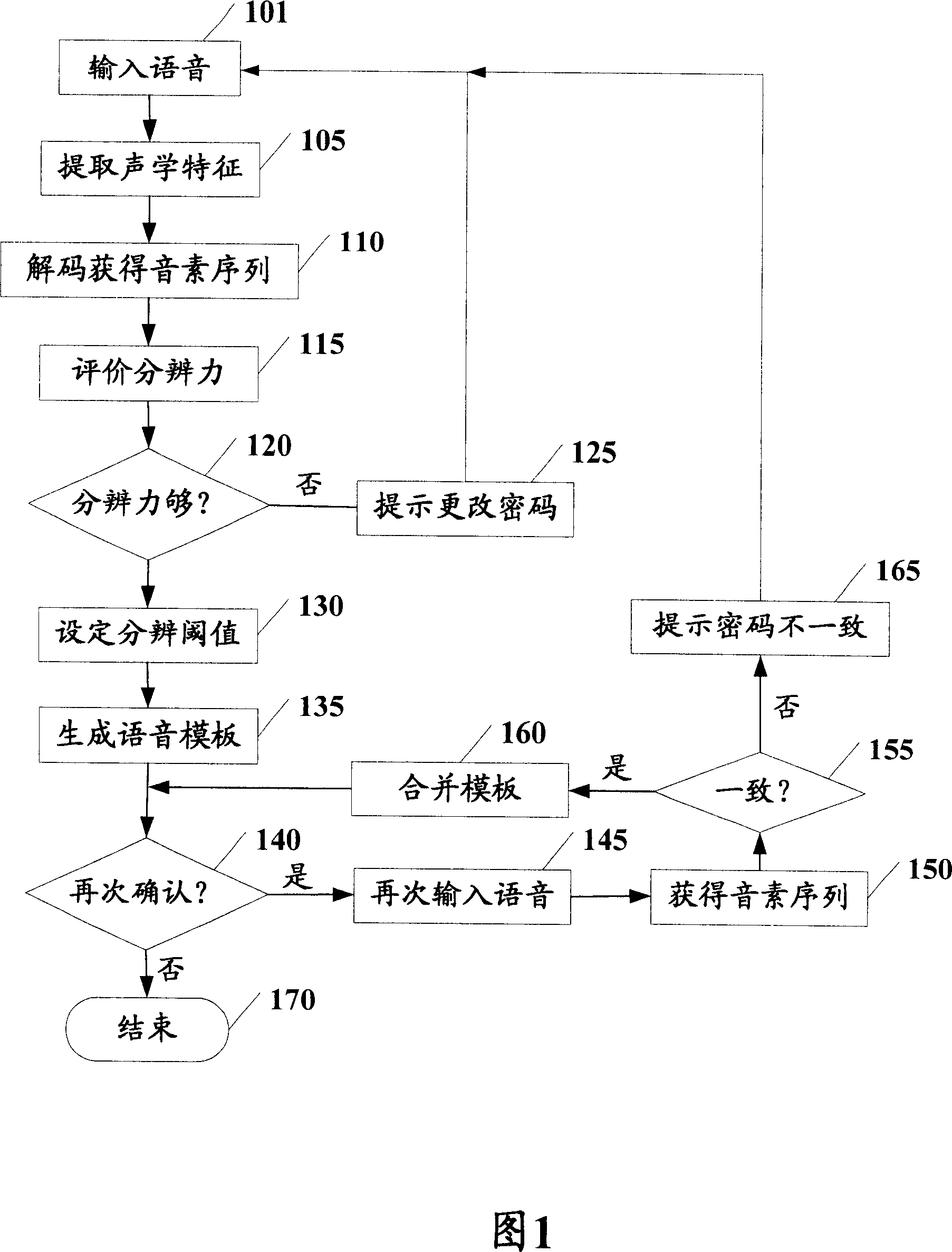

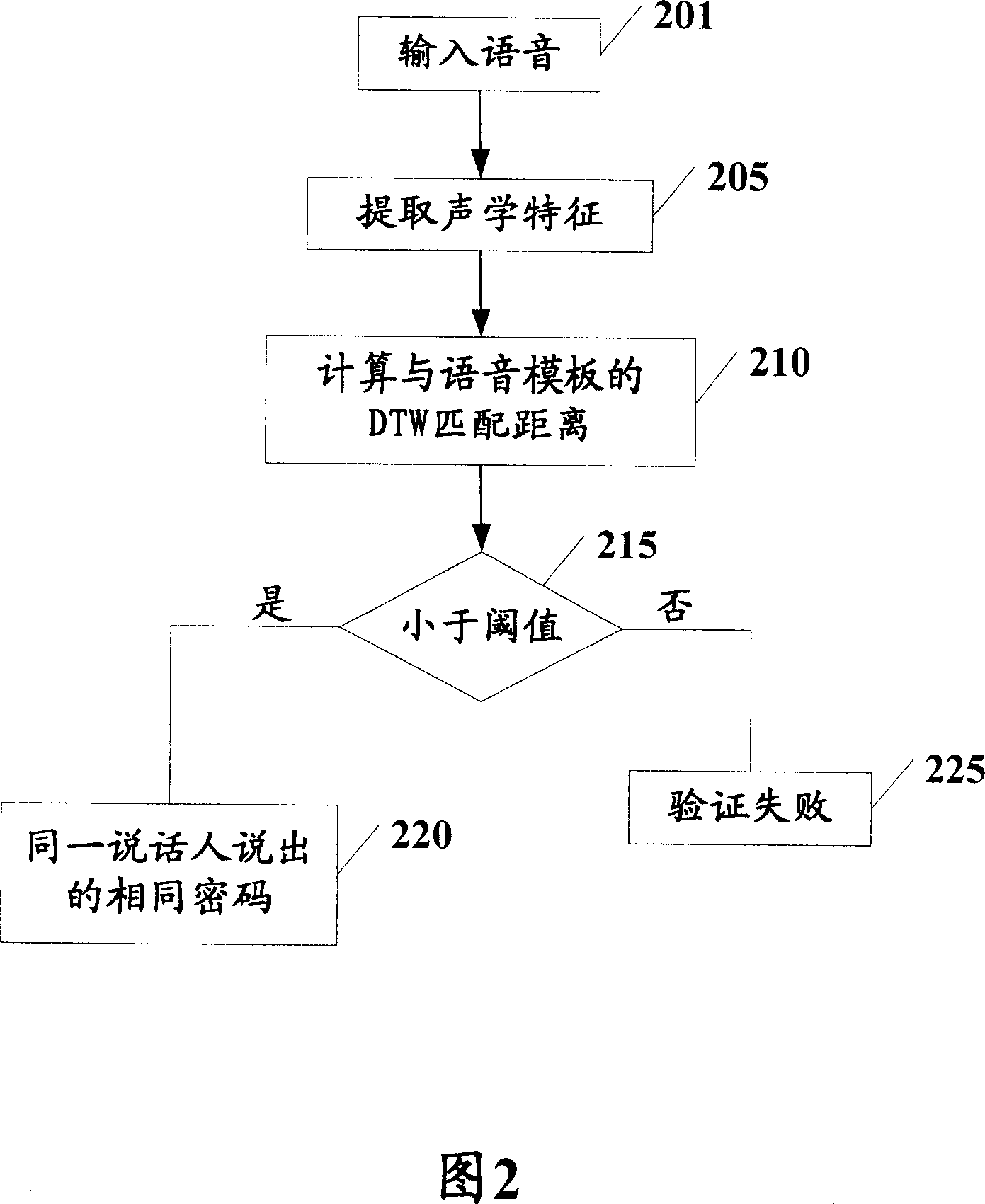

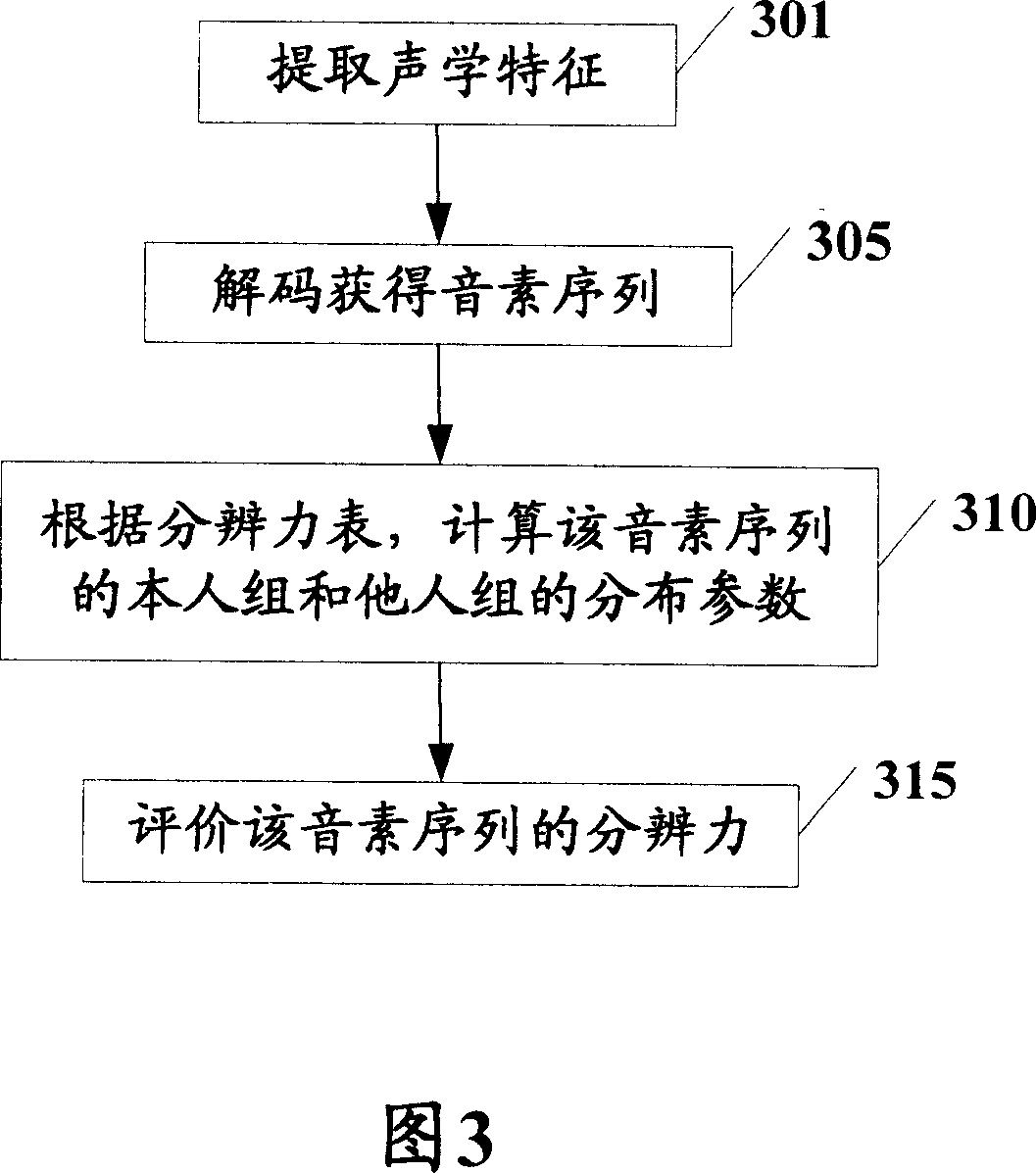

Method for estimating distinguish of voice, registering and validating authentication of speaker and apparatus thereof

This invention provides one speaker identification register method and device, test method and device, sound evaluation resolution method and identification system, wherein, the method comprises the following steps: inputting speaker sound; getting sound sequence according to above input sound; according to sound resolution list evaluating sound sequence resolution rate, wherein, the above sound resolution list comprises each sound resolution force as valve value; providing sound module to sound.

Owner:KK TOSHIBA

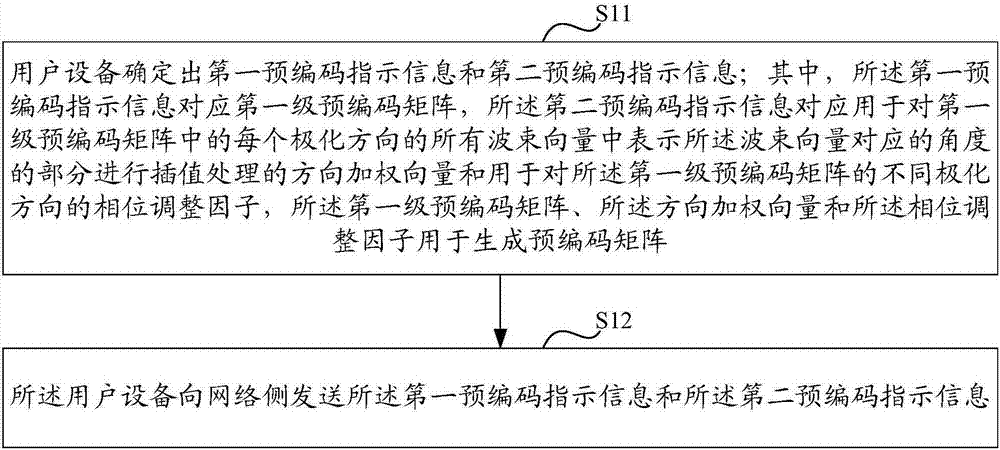

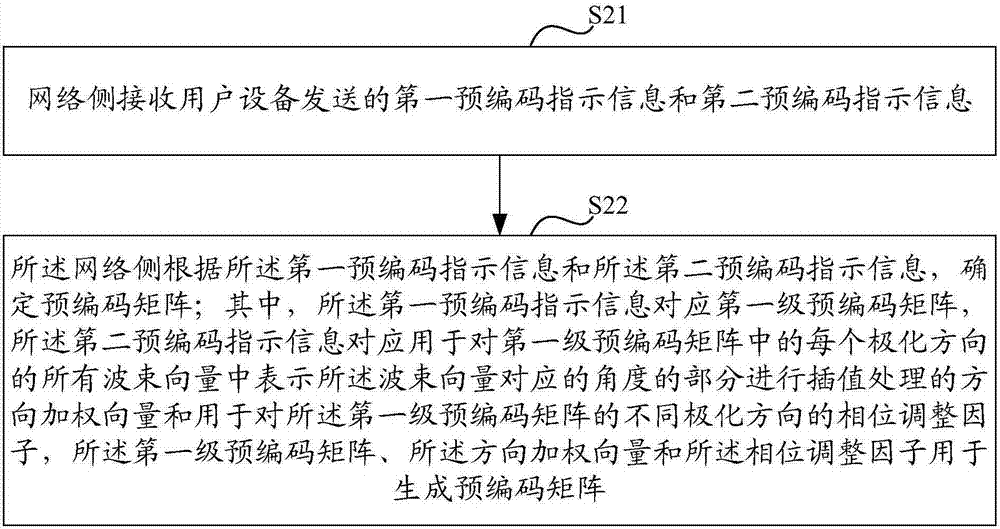

Methods and apparatuses for transmitting coding indication information and determining precoding matrix

ActiveCN105450273AFlexible adjustment of resolutionSame transmit powerSpatial transmit diversityAnalogue-digital convertersImage resolutionResolution rate

The invention discloses methods and apparatuses for transmitting coding indication information and determining a precoding matrix. With the methods and apparatuses, the resolution ratio of the code word in the codebook that is generated based on combination of a wave beam vector subgroup with column selection can not be adjusted flexibly. The method comprises: first precoding indication information and second precoding indication information are determined, wherein the first precoding indication information corresponds to a first-stage precoding matrix and the second precoding indication information corresponds to direction weighting vectors for carrying out interpolation processing on parts representing corresponding angles of the wave beam vectors in all wave beam vectors at each polarization direction in the first-stage precoding matrix and phase adjusting factors applied to different polarization directions of the first-stage precoding matrix. And the first-stage precoding matrix, the direction weighting vectors, and the phase adjusting factors are used for generating a precoding matrix. With the direction weighting vectors, the resolution rate of the precoding matrix can be adjusted flexibly.

Owner:DATANG MOBILE COMM EQUIP CO LTD

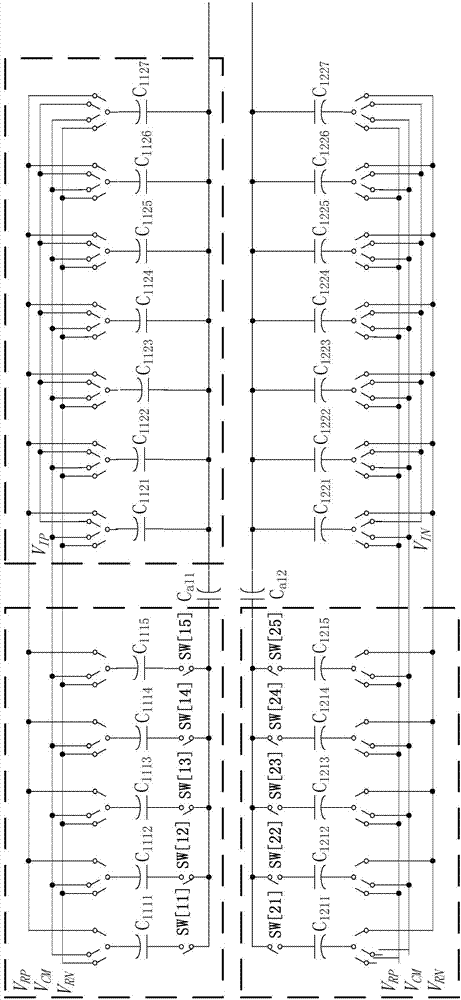

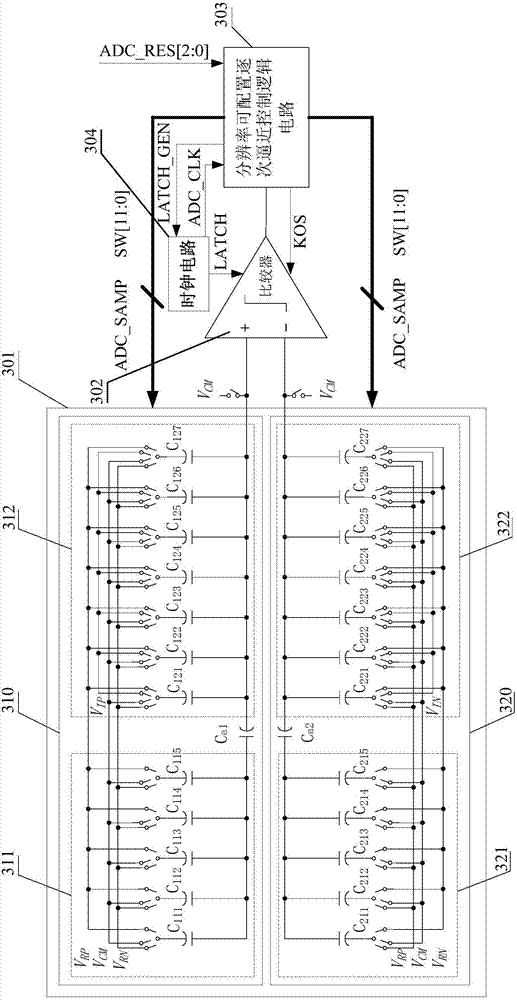

SAR ADC (successive approximation register analog-to-digital converter) with resolution configurable

ActiveCN104506195AGood dynamic characteristicsEasy layout and wiringAnalogue/digital conversionElectric signal transmission systemsFrequency spectrumResolution rate

The invention discloses an SAR ADC (successive approximation register analog-to-digital converter) with resolution configurable. The SAR ADC comprises a capacitive-type ADC, a comparator, a resolution rate-configuring SAR control logic circuit and a clock circuit. Compared with the conventional resolution rate configuring technical scheme of the SAR ADC, the SAR ADC has the advantages that a switch is not required to plug in the capacitive-type ADC to configure digits of the capacitive-type ADC, and the resolution rate of the ADC is directly configured based on the SAR control logic algorithm; a configuring switch is omitted in a capacitor array, thus locating and wiring of the layout is convenient and simple, and less stray capacitance and stray resistance is introduced among key nodes such as an upper plate and a lower plate of a capacitor; better performance is imparted, noise floor, outputting signal frequency spectrum, of the SAR ADC is decreased to the normal level under resolution rate modes, harmonic waves are eliminated, and dynamic behavior and static behavior of the ADC are remarkably improved.

Owner:GIGADEVICE SEMICON (BEIJING) INC

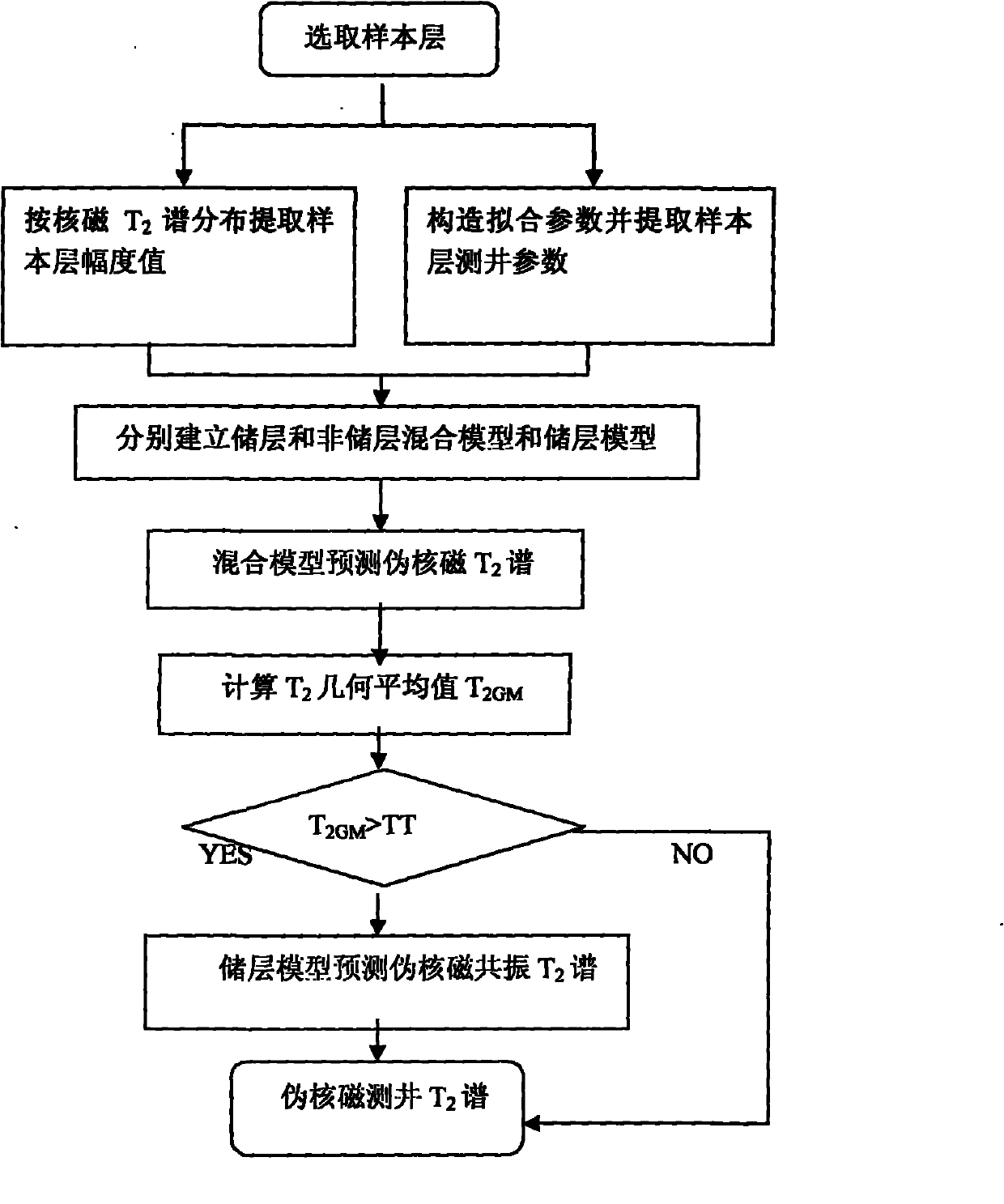

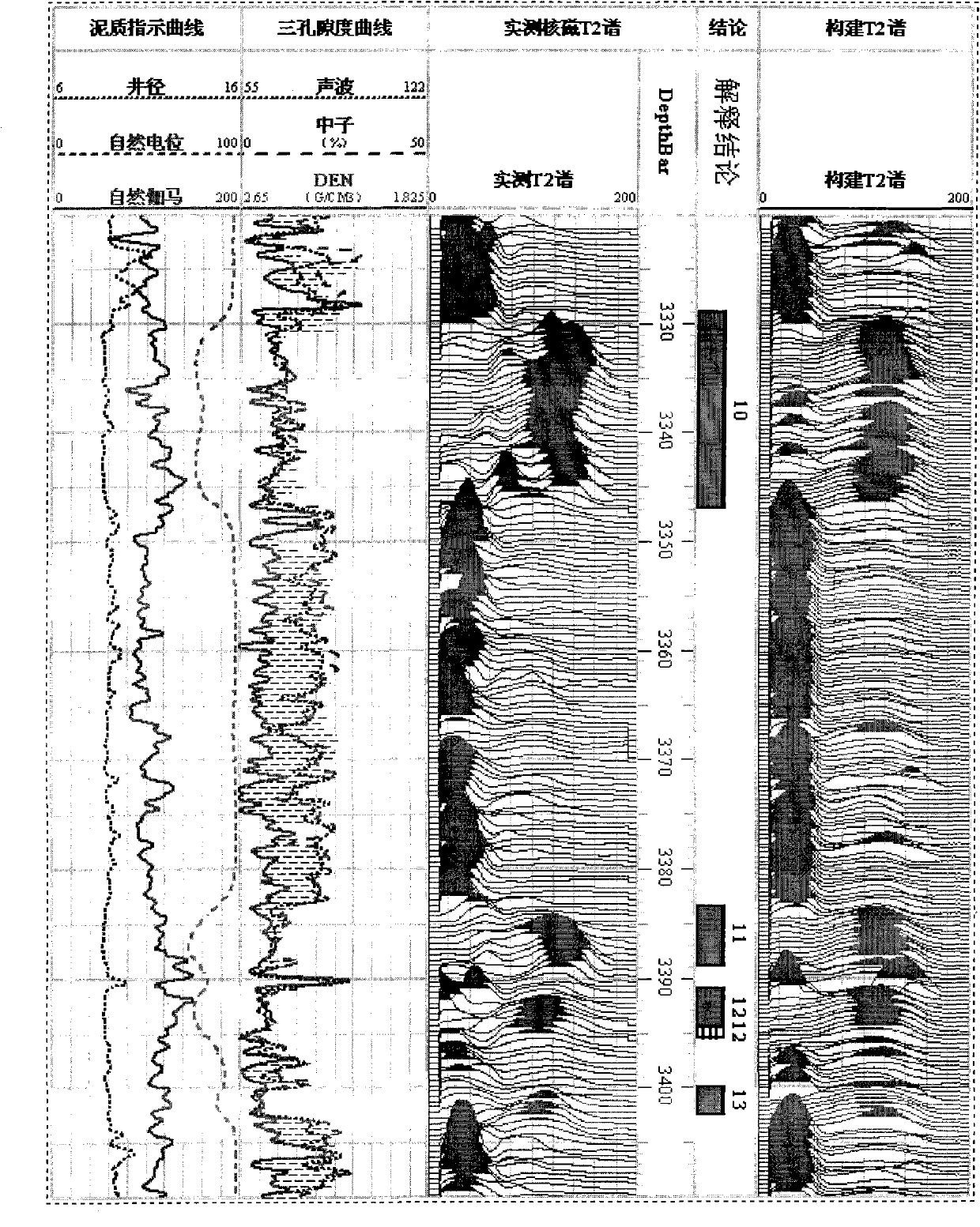

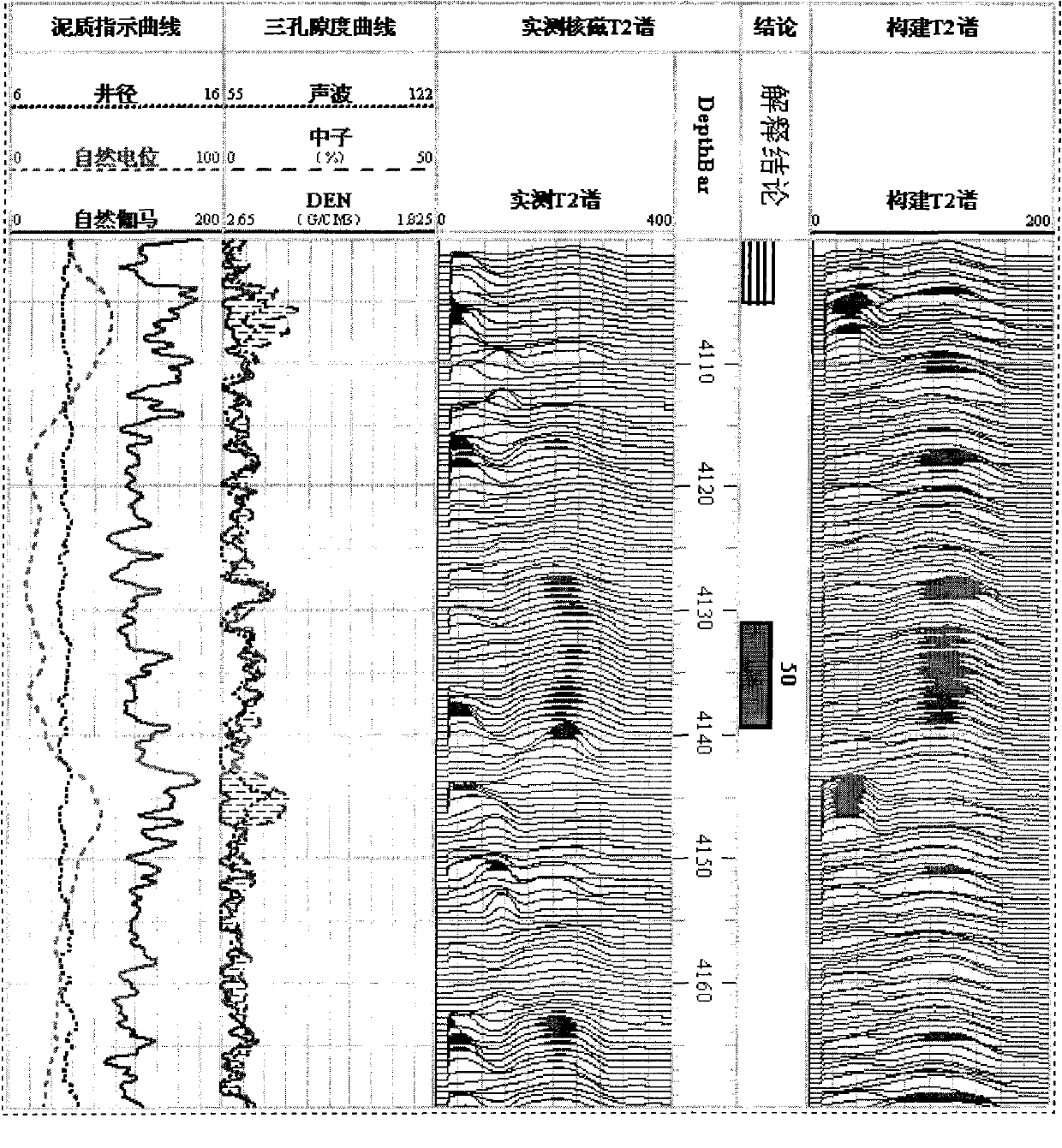

Method for constructing pseudo nuclear magnetic T2 spectrum by using conventional logging data

ActiveCN102042011AGood application effectHigh resolutionElectric/magnetic detection for well-loggingBorehole/well accessoriesNMR - Nuclear magnetic resonanceImage resolution

The invention discloses a method for constructing a pseudo nuclear magnetic T2 spectrum by using conventional logging data, which solves the technical problems that the conventional logging technology cannot accurately evaluate hole structure parameters and the nuclear magnetic logging price is high. The method comprises the following steps of: splitting two-dimensional information of a nuclear magnetic T2 spectrum for reflecting a hole structure into one-dimensional information according to the composition, establishing an empirical relationship between the one-dimensional information and the conventional logging data, and then assembling the one-dimensional information and the conventional logging data into corresponding two-dimensional information so as to realize transformation of the logging data from the one-dimensional information to the two-dimensional information, namely construct the two-dimensional nuclear magnetic logging T2 spectrum by using the one-dimensional conventional logging data. The method has remarkable actual application effect; the pseudo nuclear magnetic logging T2 spectrum is remarkably similar to the actually measured nuclear magnetic logging T2 spectrum on morphology, succeeds the advantage that the resolution rate of the conventional logging technology is higher than that of the nuclear magnetic resonance technology, and can evaluate the physical property of a reservoir, evaluate the hole structure of the reservoir and perform comprehensive evaluation of the complex reservoir as the actually measured nuclear magnetic T2 spectrum; and the method has great popularization value.

Owner:CHINA PETROCHEMICAL CORP +1

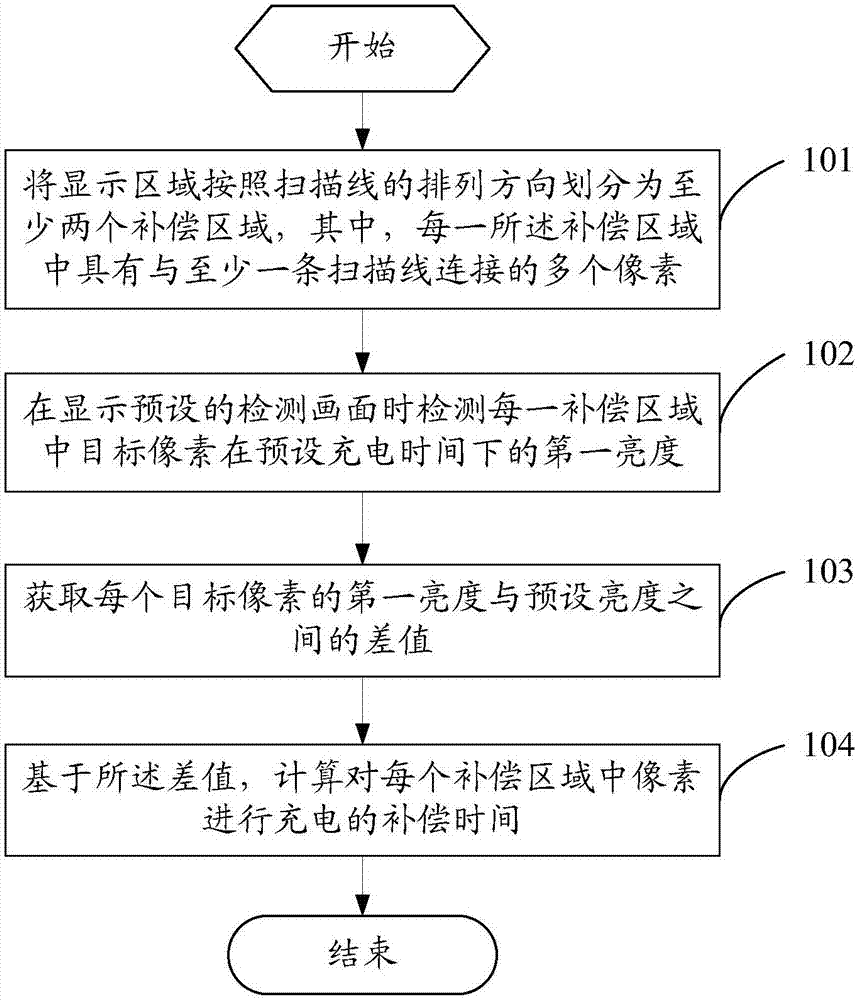

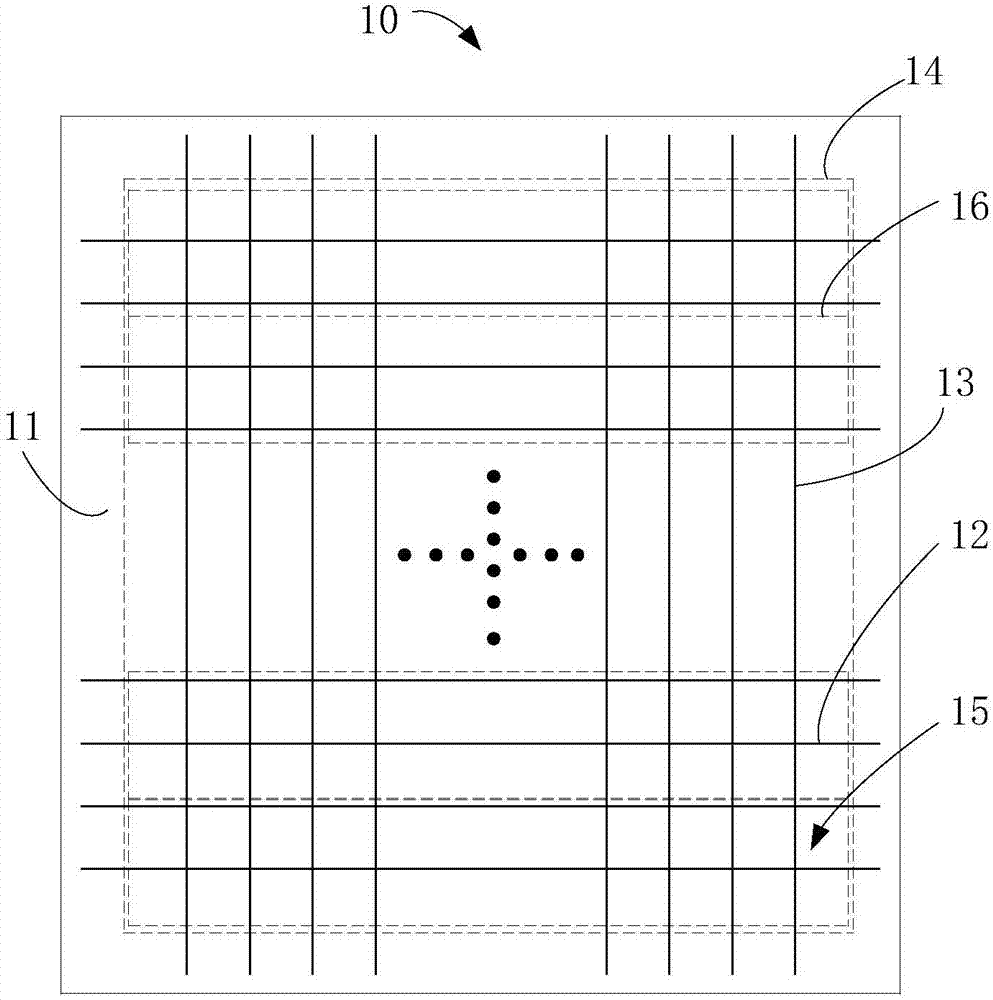

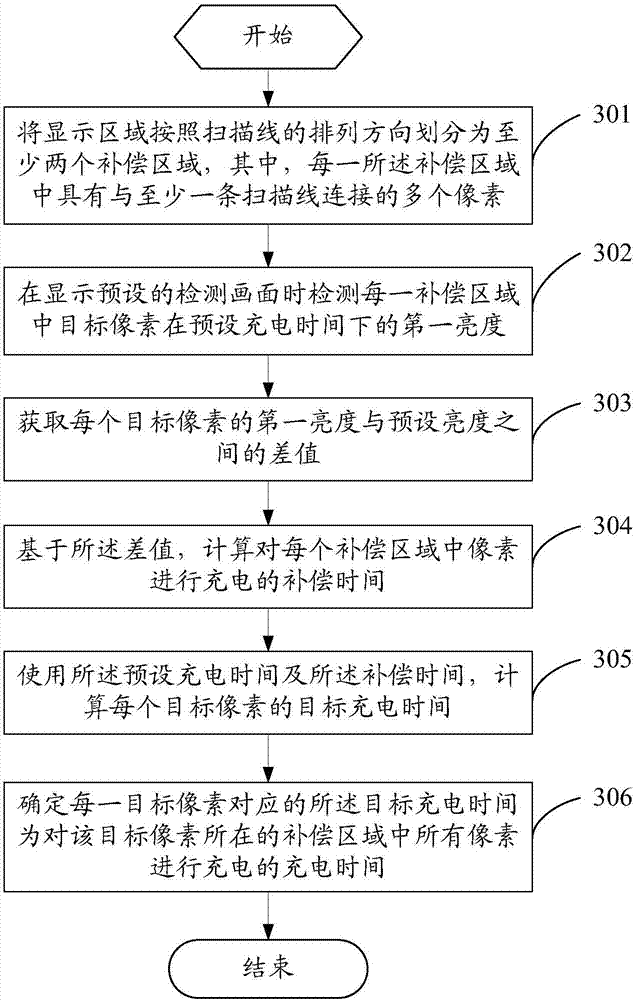

Detecting method and device of pixel charging compensation, its compensation method and display device

InactiveCN107516495AMinimize charging varianceSolve the insufficient charging timeStatic indicating devicesPixel densityImage resolution

The invention provides a detecting method and a device of pixel charging compensation, its compensation method and a display device. The detecting method includes steps of classifying a display zone of the display device into at least two compensation zones, and detecting the first brightness of a target pixel in every compensation zone; calculating the compensation time of charging the pixel in the compensation zone where the target pixel locates according to the differential value of the first brightness and the preset brightness. Thus, after compensating the pixel charging time in the compensation zone by the detected compensation time, the charging time of every pixel is approximately the same, so that the charging difference of pixels on different positions caused by the improvement of resolution rate, pixel density and image refreshing rate and delay of the signal line is reduced, the charging uniformity and sufficient charging time of pixels at different positions are guaranteed; besides, the brightness of different positions on the display zone of the display device is uniform.

Owner:BOE TECH GRP CO LTD

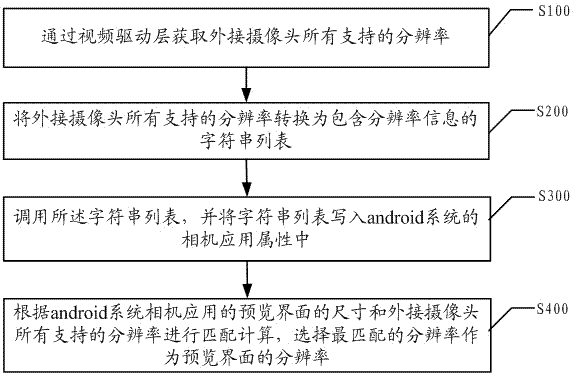

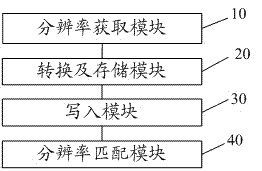

Resolution ratio acquiring method and device of external camera of android system

ActiveCN103546689AImprove compatibilityImprove matchTelevision system detailsColor television detailsImage resolutionComputer compatibility

The invention discloses a resolution ratio acquiring method and device of an external camera of an android system. The resolution ratio acquiring method includes acquiring all supported resolution rates of the external camera by a video driving layer, and converting the supported resolution rates of the external camera into a character string list containing resolution rate information; calling the character string list and writing the same into a camera application attribute of the android system; matching and calculating according to size of a preview interface of a camera application of the android system and the supported resolution rates of the external camera, and selecting the most matching resolution rate as resolution rate of the preview interface. By the resolution ratio acquiring method and device, different supported resolution rates of the external camera can be displayed by the camera application of the android system, the resolution rate of the external camera can be better matched with a display screen of an android system terminal, compatibility of the android system for the external camera is improved, and display effect is greatly improved.

Owner:TCL CORPORATION

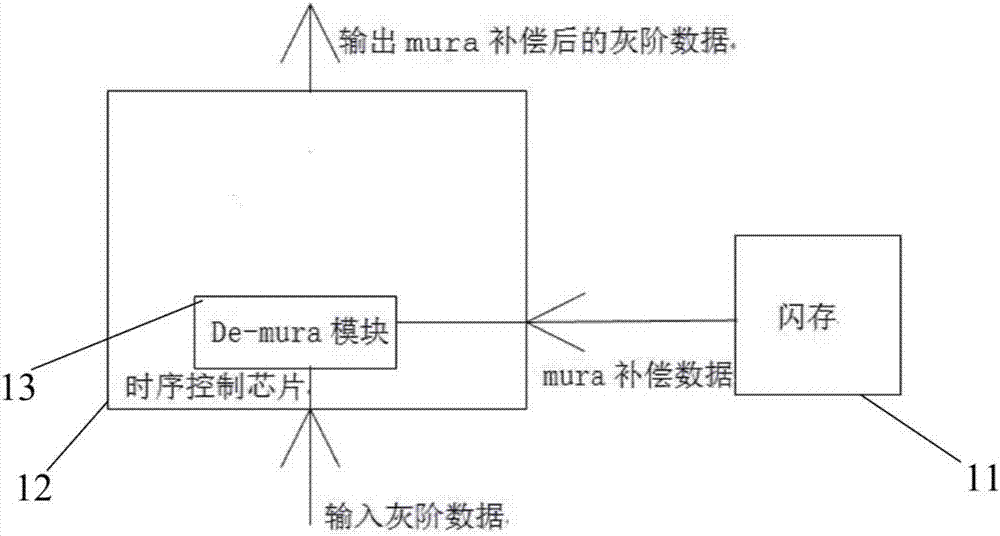

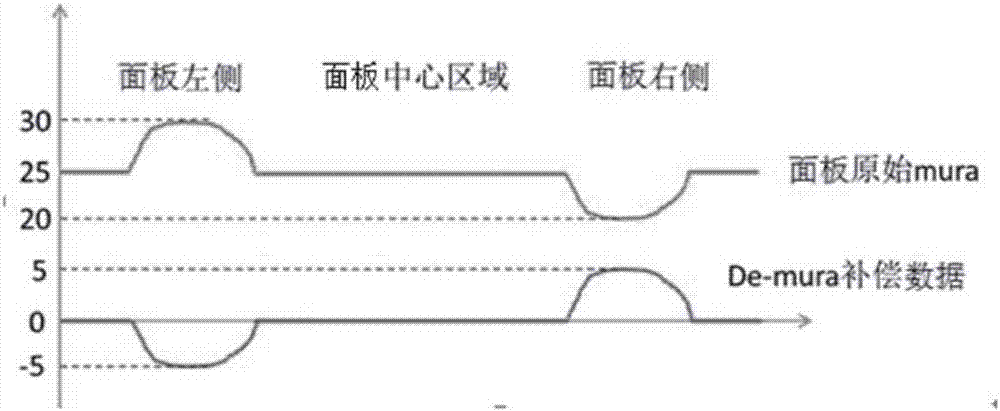

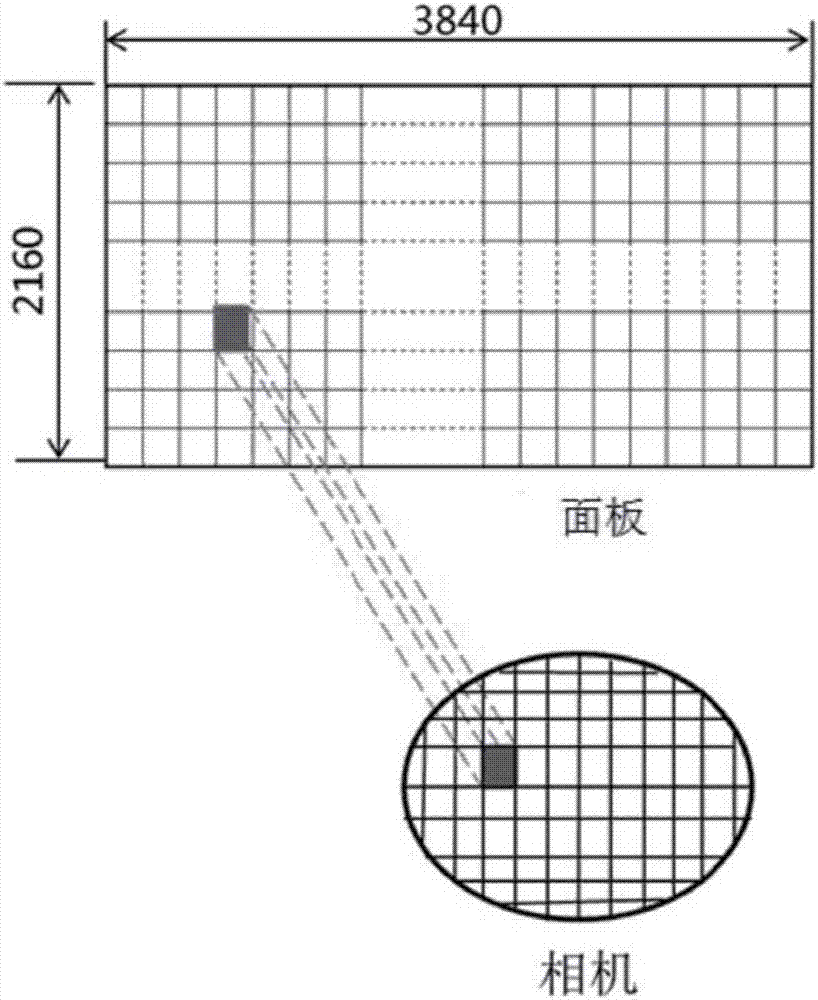

Mura treatment method specific to ultrahigh resolution panel

ActiveCN107203056AHigh cost savingsStatic indicating devicesNon-linear opticsDatum referenceUltrahigh resolution

The invention relates to a mura treatment method specific to an ultrahigh resolution panel. The method includes steps of S10, shooting actual mura state of the whole panel regionally by an industrial camera according to the resolution rate of the industrial camera; when one zone of the shooting panel is displays a gray scale, the rest zones of the panel display 0 gray scale; step 20, acquiring mura compensation data matrix of every zone of the panel according to corresponding relationship between the gray scale and brightness of the panel acquired in advance and actual mura state of every zone of the panel; step 30, combining the mura compensation data matrixes of every zone of the panel to acquire the mura compensation data matrix corresponding to the whole panel; selecting corresponding mura compensation data according to the compensation data reference value position. The mura treatment method specific to the ultrahigh resolution panel uses the specification of the industrial camera of the existing mura compensation system reasonably, realizes the accurate mura compensation of the ultrahigh resolution panel, and reduces the high cost for replacing the industrial camera specification in the mura compensation system.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

Interface layout device and interface layout method

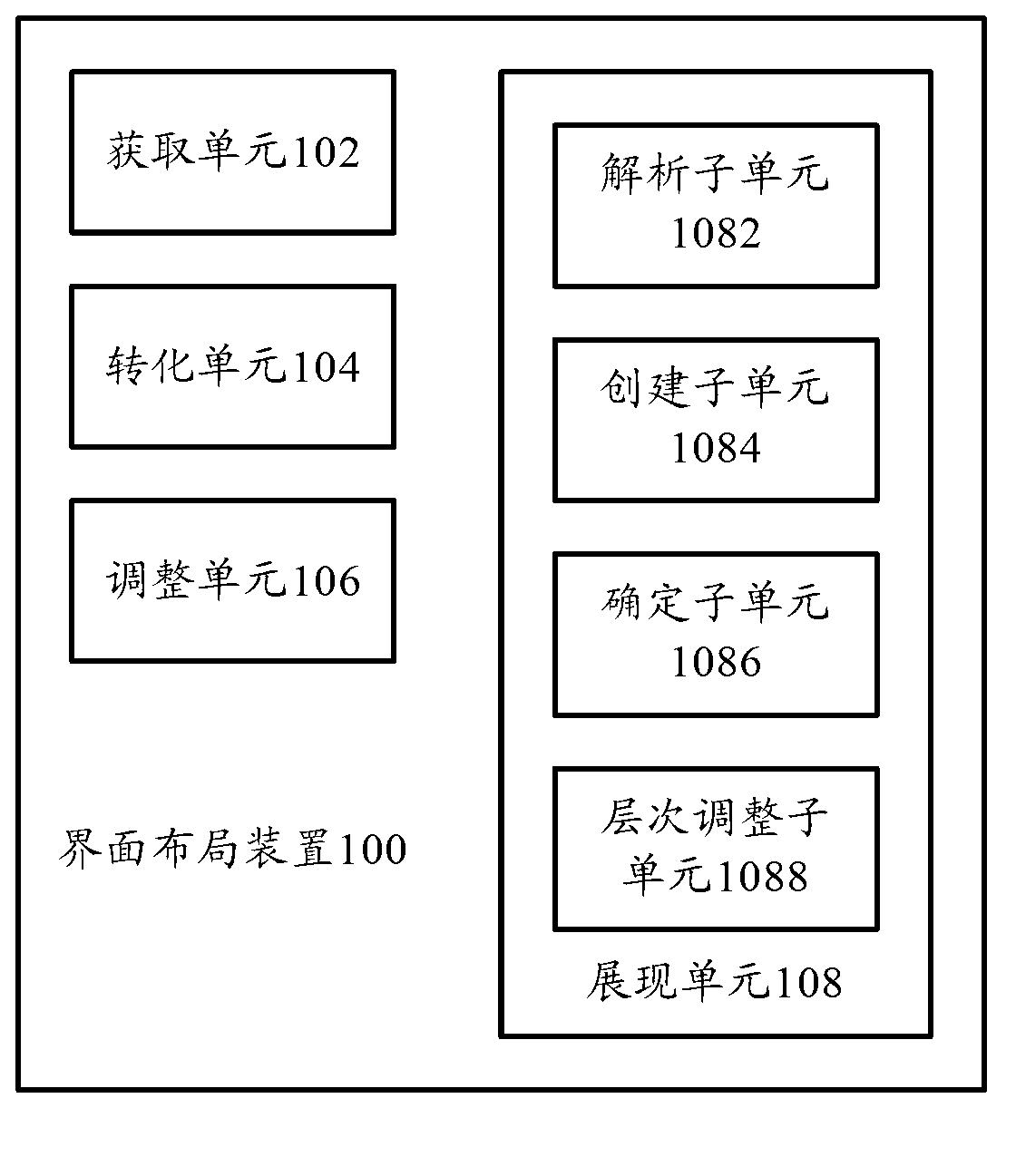

ActiveCN103176797AIn line with business habitsSpecific program execution arrangementsTarget controlImage resolution

The invention provides an interface layout device. The interface layout device comprises an acquiring unit, a converting unit, an adjusting unit, and a displaying unit. The acquiring unit is used for selecting a target region in a first interface according to a received selection command, and acquiring a target control in the target region, the converting unit is used for converting information of the target control to information of a preset model, and displaying the target control in a second interface according to layout of the target control in the first interface, the adjusting unit is used for adjusting layout of the target control in the second interface according to a received adjustment command, and / or adding a container control in the second interface, and saving the adjusted second interface, and the displaying unit is used for displaying the adjusted second interface when the adjusted second interface is loaded. The invention further provides an interface layout method. Through the technical scheme, streaming type layout and free layout can be combined, users can place the control in the streaming type layout according to requirements, and an interface can be suitable for various kinds of resolution rates and suitable for different service habits.

Owner:YONYOU NETWORK TECH

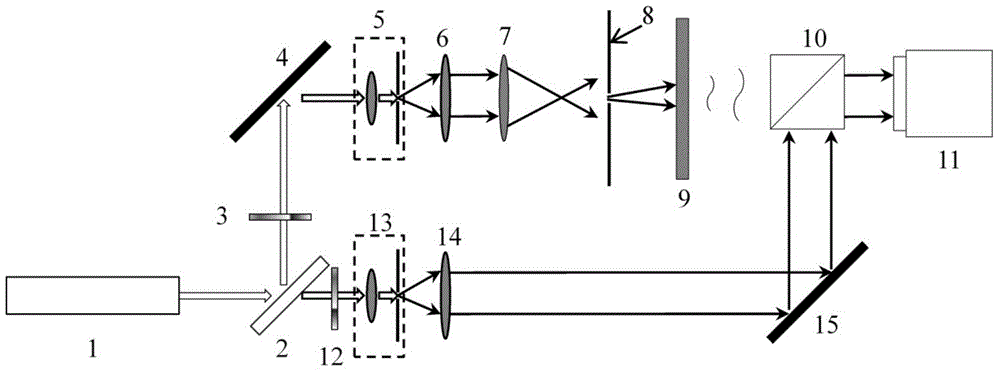

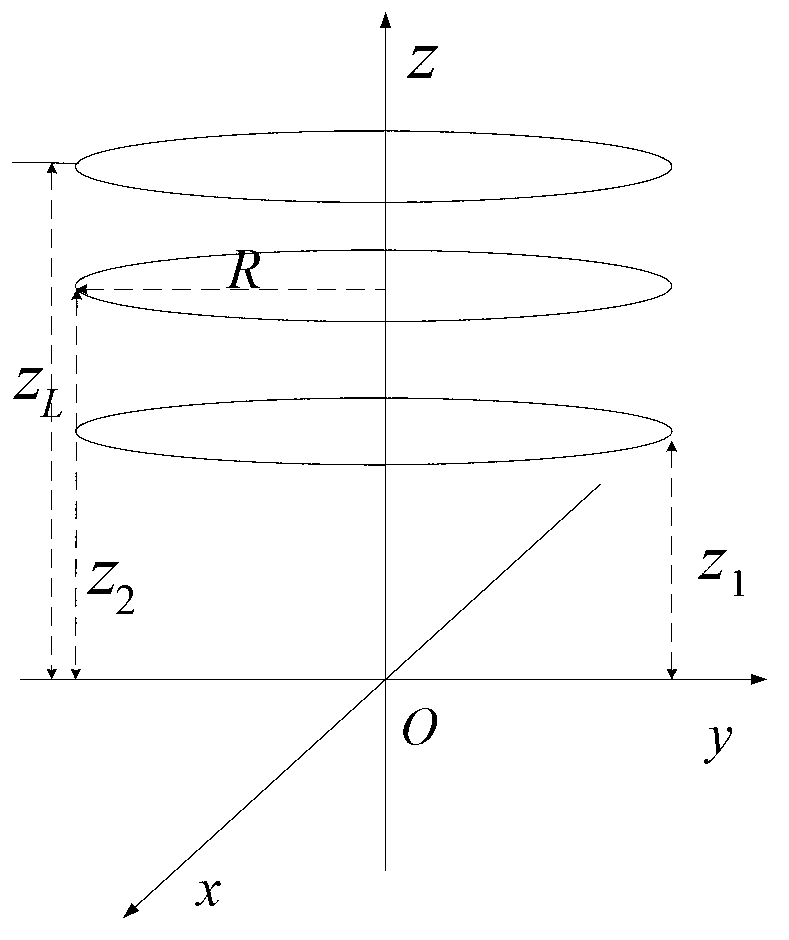

High-resolution digital holographic microscopy imaging device and high-resolution digital holographic microscopy imaging method

ActiveCN104808469AHigh resolutionFast convergenceInstrumentsTarget surfaceDigital holographic microscopy

The invention discloses a high-resolution digital holographic microscopy imaging device and a high-resolution digital holographic microscopy imaging method. Based on a normal holographic device, the high-resolution digital holographic microscopy imaging device is improved by adding a distribution-known random phase plate between a small-hole diaphragm and an imaging device, so that more object light information can be scattered on a target surface of the imaging device after a sample to be tested is added. The high-resolution digital holographic microscopy imaging method includes the steps of collecting a group of holographic data, processing the holographic data by a filtering method to obtain distribution of object diffraction spots on the target surface of the imaging device, processing the diffraction spots by an improved iterative restoration algorithm similar to coherent diffractive imaging, and finally restoring a restructured image with the resolution rate much higher than that of a normal holographic image. The high-resolution digital holographic microscopy imaging device and the high-resolution digital holographic microscopy imaging method have the advantage that a solution for current low-resolution digital holographic microscopy imaging is provided.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

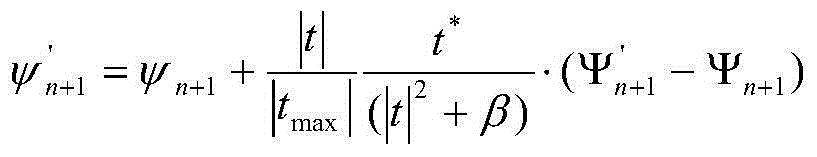

Video resolution enhancing method and module based on FPGA (field programmable gate array)

InactiveCN103248797AHighly integratedImprove portabilityTelevision system detailsGeometric image transformationDigital videoDisplay device

The invention relates to a processing method and a hardware module for enhancing the resolution of a digital video file with an ordinary resolution and then outputting the digital video file onto a high-definition display device for real time display. The method comprises the following steps of sequentially storing each frame image of a digital video material with low resolution rate into a cache of a FPGA embedded system; utilizing a standard interpolation algorithm (bilinear interpolation and bicubic interpolation and the like) to reasonably estimate and insert an undefined pixel value between two adjacent pixel point on each frame image, amplifying each frame image, maintaining the smoothness and contrast ratio of the image, improving the resolution rate of each frame image, i.e. the resolution rate of the video; and finally, sequentially and continuously outputting each processed frame image to the display device. The method and the module can be widely applied to the fields such as family life, medical imaging, security monitoring, intelligent car control and outdoor video advertisement and has the characteristics of high output resolution rate, strong real-time property, small size, simplicity and convenience in operation, low cost, high reliability and the like.

Owner:BEIJING ZHIGUANG BOYUAN SCI & TECH

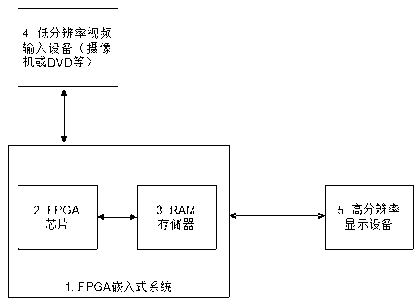

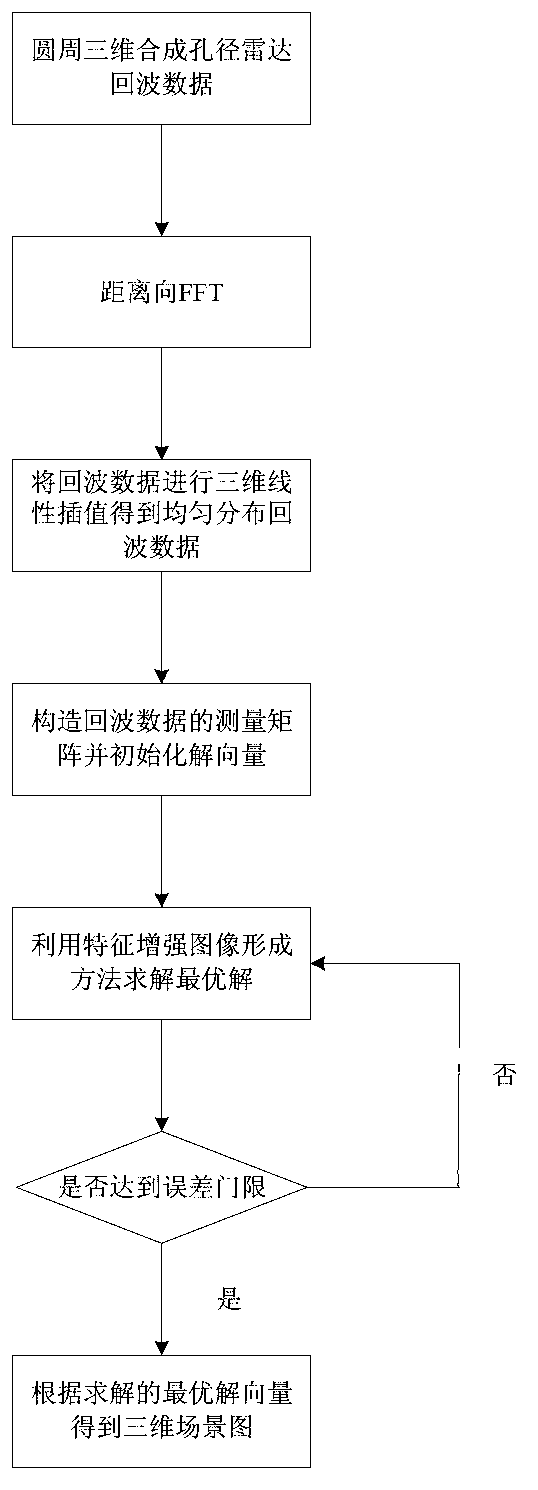

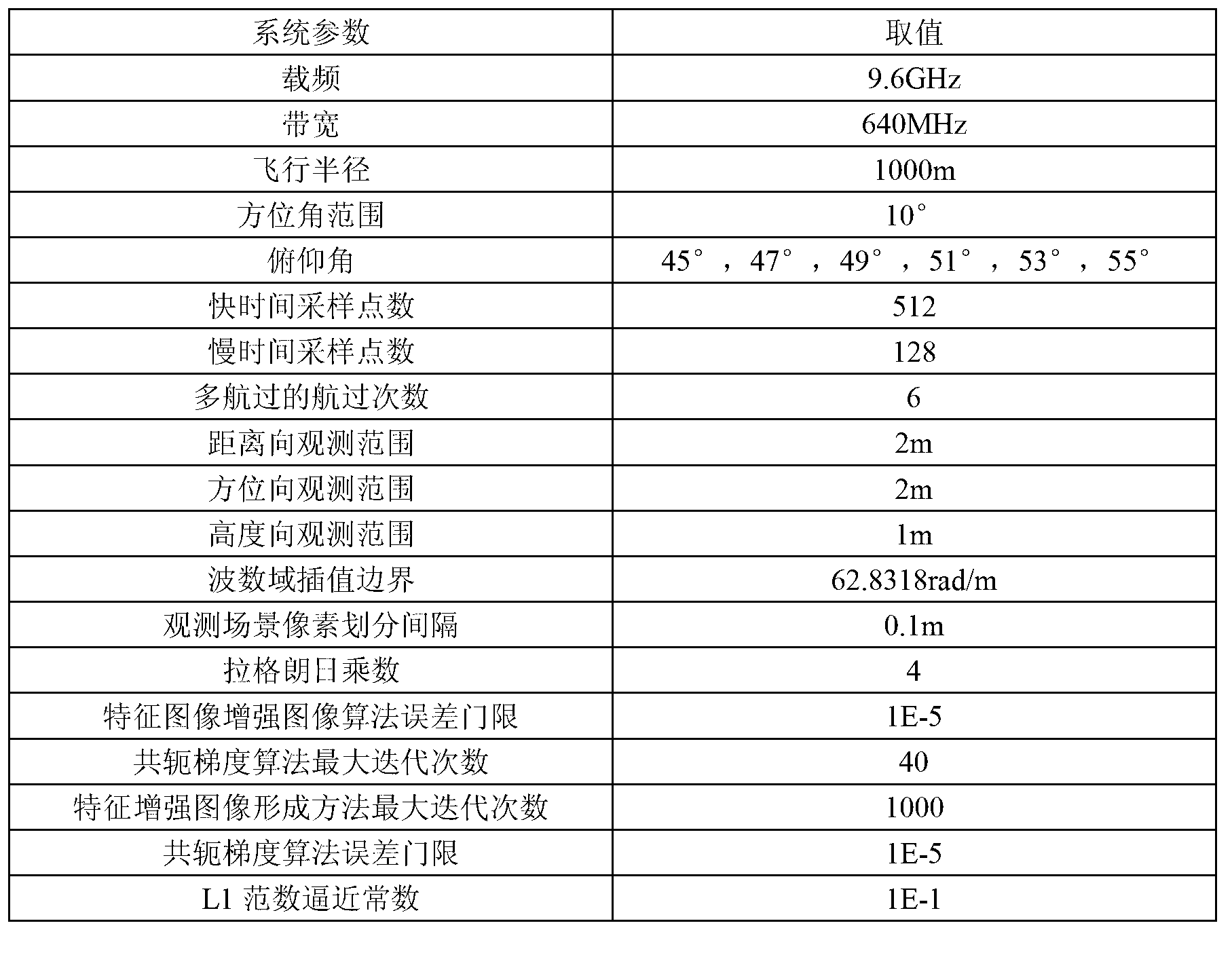

Multi-pass circumference SAR three-dimensional imaging method

ActiveCN102914773AOvercoming the problem of high sidelobesSparse solution vectorRadio wave reradiation/reflectionFast Fourier transformRadar

The invention discloses a multi-pass circumference SAR three-dimensional imaging method. The method comprises the following steps of: carrying out distance compression processing on distance data; carrying out fast one-dimensional Fourier transform (FFT) so as to convert the data into a wave number domain; carrying out a three-dimensional linear interpolation to obtain a uniformly distributed data format under a right-angle coordinate system; constructing a linear observing model of a radar echo signal in the wave number domain; constructing an optimized target function by using a weighted L1 norm; and solving an optimized solution vector by using an iterative algorithm in a characteristic enhanced image forming method. Therefore, a three-dimensional imaging result of a target scene is obtained, the three-dimensional imaging is realized, a side band is effectively reduced, the resolution rate is improved, and a good image focusing effect is realized.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

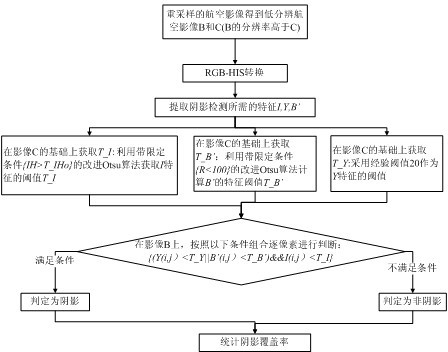

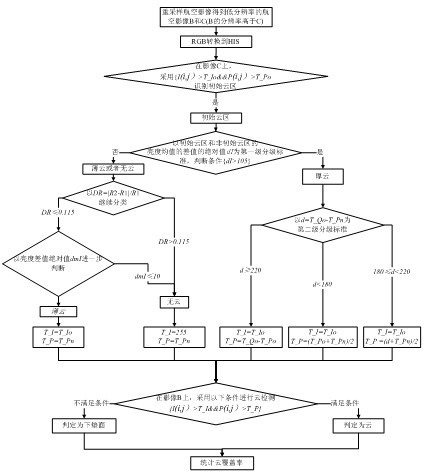

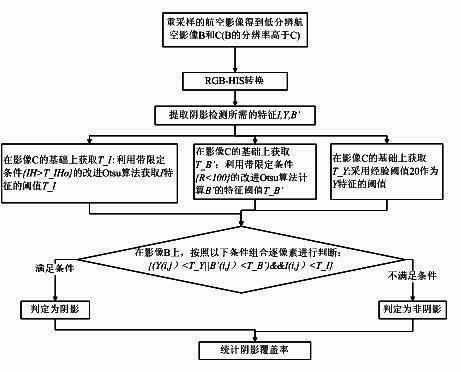

Method for automatically evaluating color quality of image during aerial photography in real time

The invention provides a method for automatically evaluating the color quality of an image during aerial photography in real time. The method includes re-sampling an aerial image obtained by aerial photography at first; acquiring two aerial images with different resolution rates; realizing shadow detection and cloud detection; evaluating the color quality of the image according to shadow coverage and cloud coverage which are obtained by the shadow detection and the cloud detection; and outputting a quality evaluation report. The method is high in timeliness and automation degree and fast in processing speed, and full-automatic detection is supported. In addition, different threshold acquisition methods are provided for the shadow detection and the cloud detection, detection precision can be effectively improved, and automation and precision are guaranteed.

Owner:WUHAN UNIV

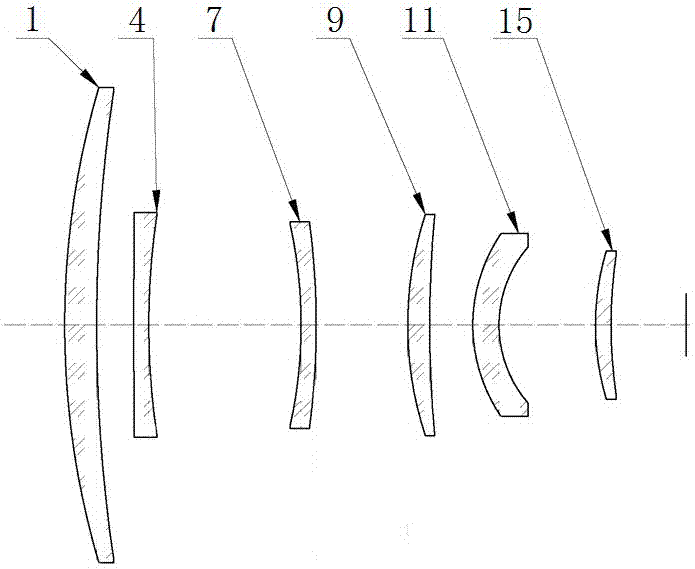

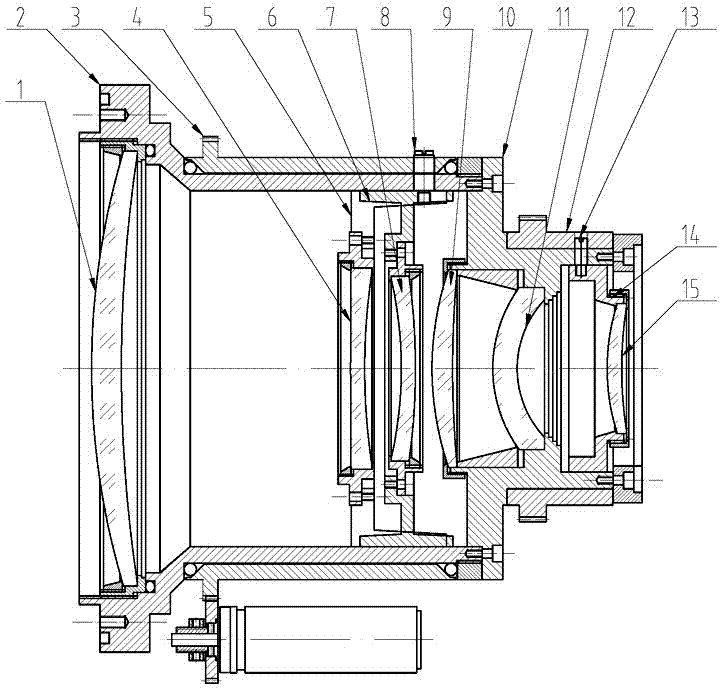

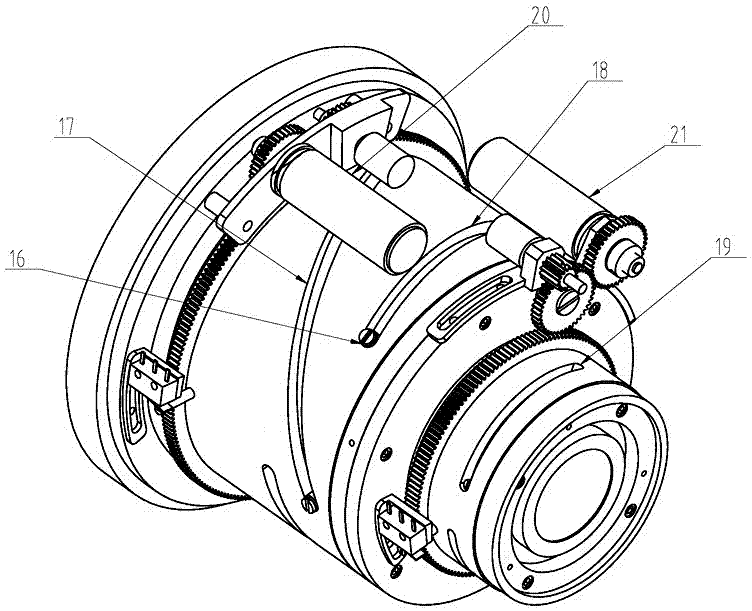

Infrared continuous zoom lens with long wave of 25 to 75mm and working method thereof

The invention relates to a 25-75mm long-wave infrared continuous zoom lens and its working method. The optical system of the lens is provided with a front solid group lens A, a front variable power group lens B, and a compensation group in sequence along the incident direction of light from front to back. Lens C, rear fixed group lens D, and focusing group lens E, the front fixed group lens A includes a positive crescent lens A-1 with a convex surface facing forward; The crescent lens B-1; the compensation group lens C includes a negative crescent lens C-1 with the concave surface facing forward; the post-fixation lens D includes a positive crescent lens D-1 with a convex surface facing forward and a The negative crescent lens D-2 on the back side of the shaped lens D-1 and the convex surface facing forward; the focusing group lens E includes a positive crescent lens E-1 with the convex surface facing forward. The lens has a small number of aspheric surfaces, which effectively reduces the difficulty and cost of processing, and is easy to guarantee the quality, high resolution and good image quality.

Owner:FUJIAN FUGUANG TIANTONG OPTICS

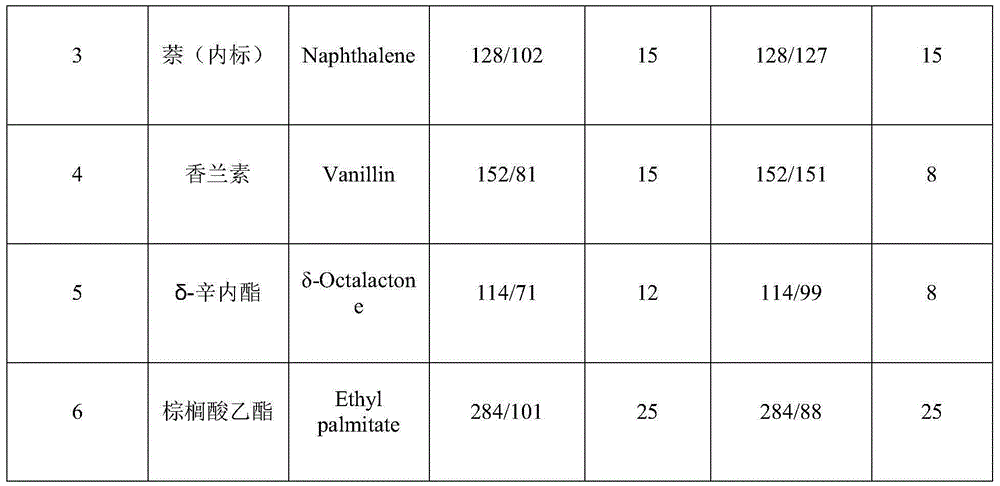

Method for accurate characterization and evaluation of milky aroma characteristic in cigarette aroma

InactiveCN105092729AAvoid subjectivitySimple and fast operationComponent separationImage resolutionResolution rate

The invention discloses a method for accurate characterization and evaluation of a milky aroma characteristic in a cigarette aroma. Quantitative data of aroma substances is obtained through an HS-GC-MS / MS detection method, and a cigarette milky aroma note index N is calculated and constructed through a corresponding aroma substance threshold. The method is simple to operate, difficult to interference of impurities, and accurate in detection results. The selectivity and the sensitivity of the GC-MS / MS are higher than those of GC-MS, and the problems that the GC-MS is low in sensitivity, lack of resolution rate, poor in selectivity, prone to production of false-positive results and unable to provide enough qualitative / quantitative information and the like are avoided. The cigarette milky aroma characteristic is correspondingly described and expressed from a substance base perspective, the subjectivity of sensory smoke panel tests is avoided, and the milky aroma style of cigarette products is objectively comprehensively characterized and evaluated.

Owner:CHINA TOBACCO YUNNAN IND

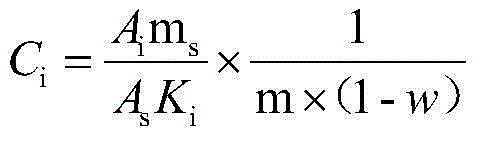

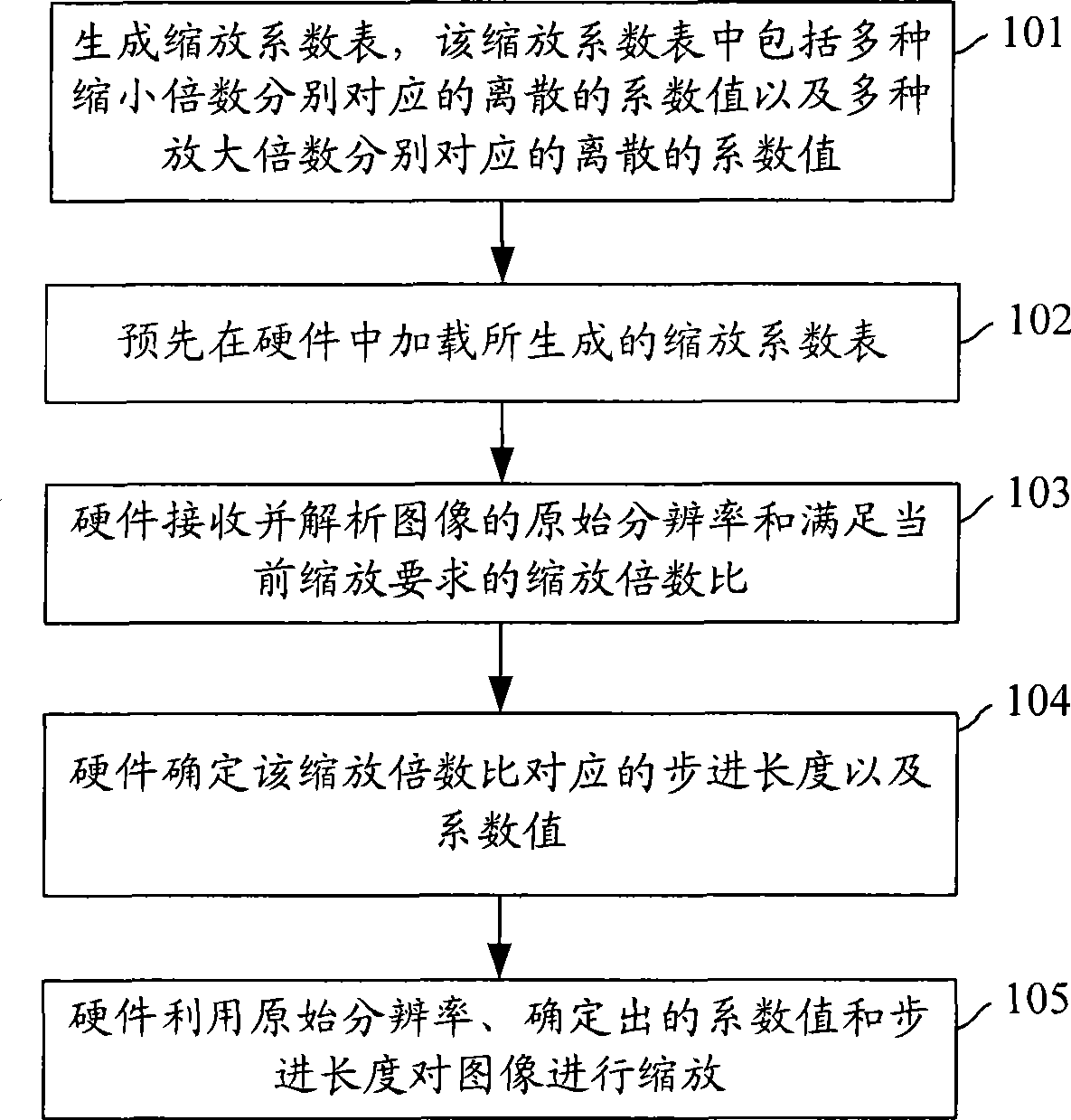

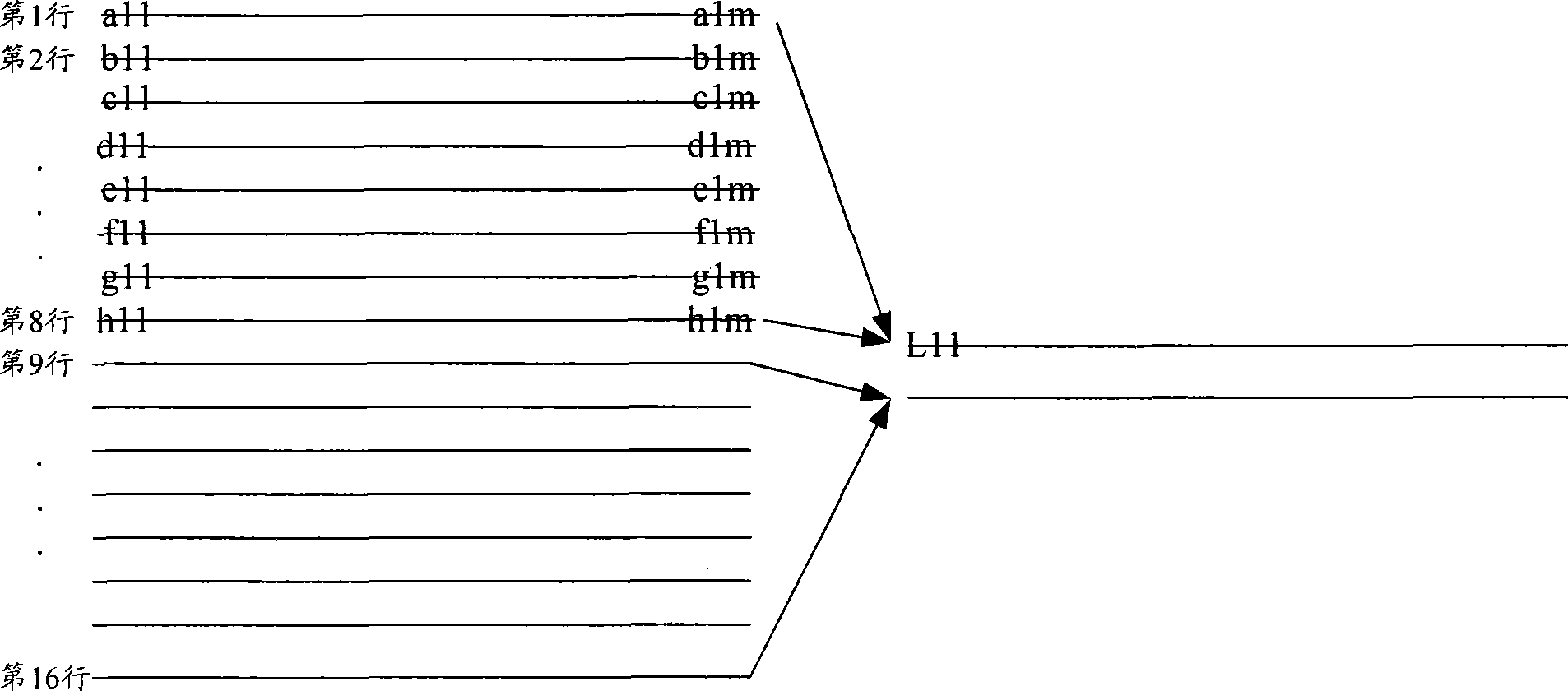

Method and device for zooming image

ActiveCN101465954AImprove practicalityMeet flexibility requirementsTelevision system detailsColor television detailsImage resolutionTime ratio

The invention discloses an image zooming method and device. The method comprises: a pre-generated zooming coefficient table is loaded and the zooming coefficient table comprises discrete coefficient values respectively corresponding to a plurality of reduction times and the discrete coefficient values respectively corresponding to a plurality of magnification times; the original resolution rate is received and a zooming times ratio required by the present zooming is satisfied; according to the zooming times ratio, the zooming coefficient table is searched and the stepping length as well as the coefficient value corresponding to the zooming times ratio are determined; by utilizing the determined stepping length, rows or columns of the original pixel which participates in each zooming are controlled, the pixel value of the original pixel in the rows or columns of the original pixel which participates in the zooming is multiply-accumulated with the determined coefficient value, the zoomed rows or columns are obtained, and the zooming is finished until the present image is determined according to the original resolution rate.

Owner:ZHEJIANG UNIVIEW TECH CO LTD

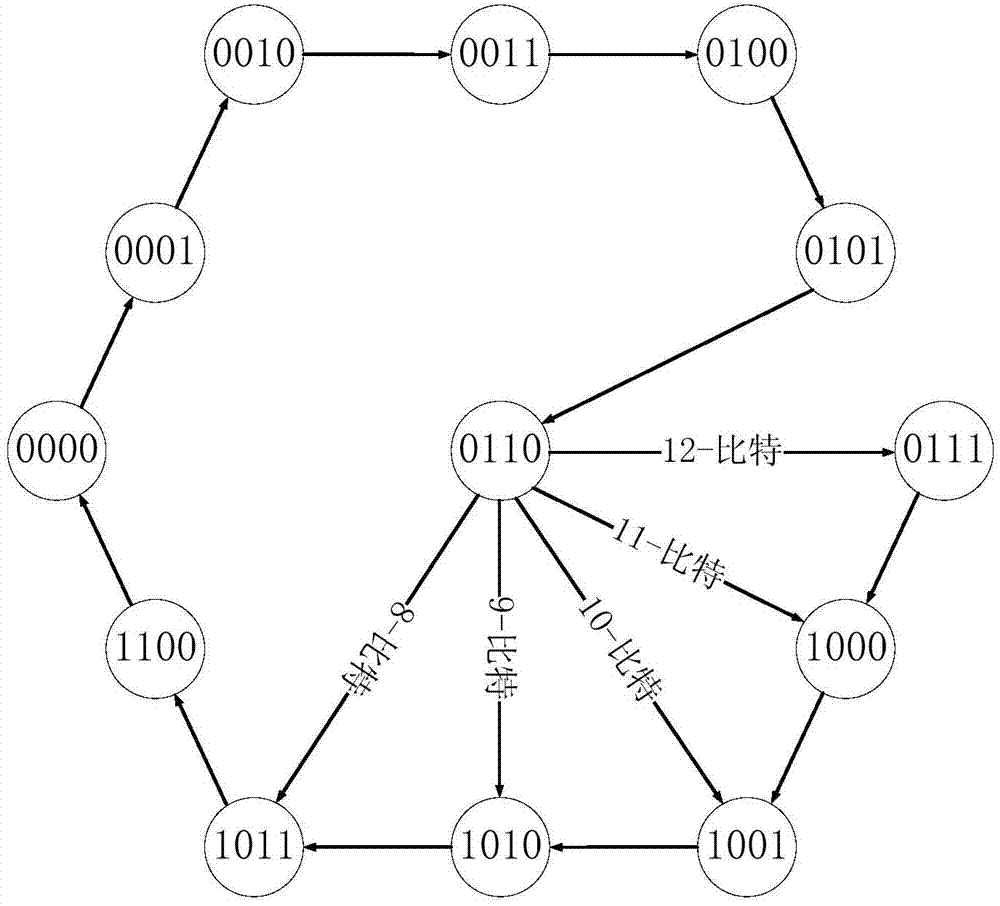

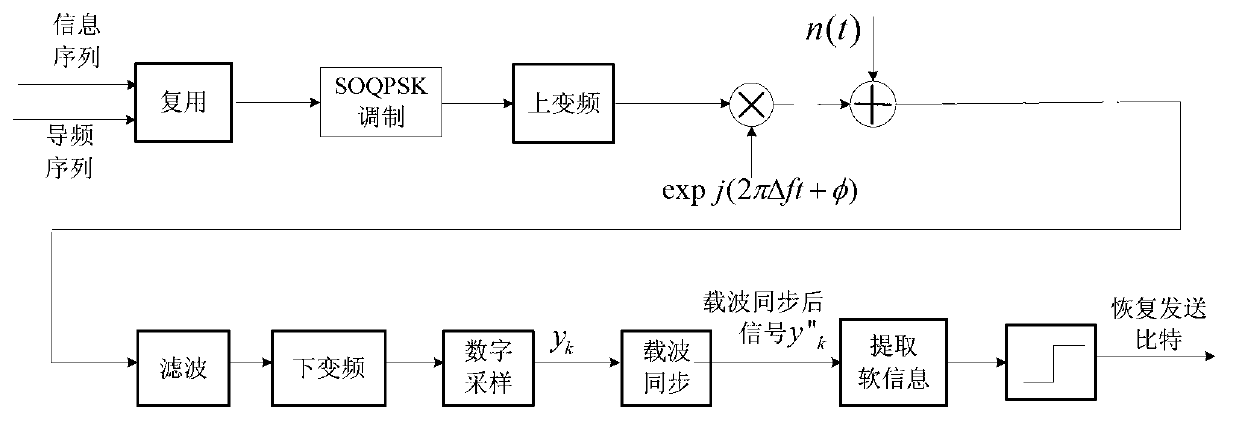

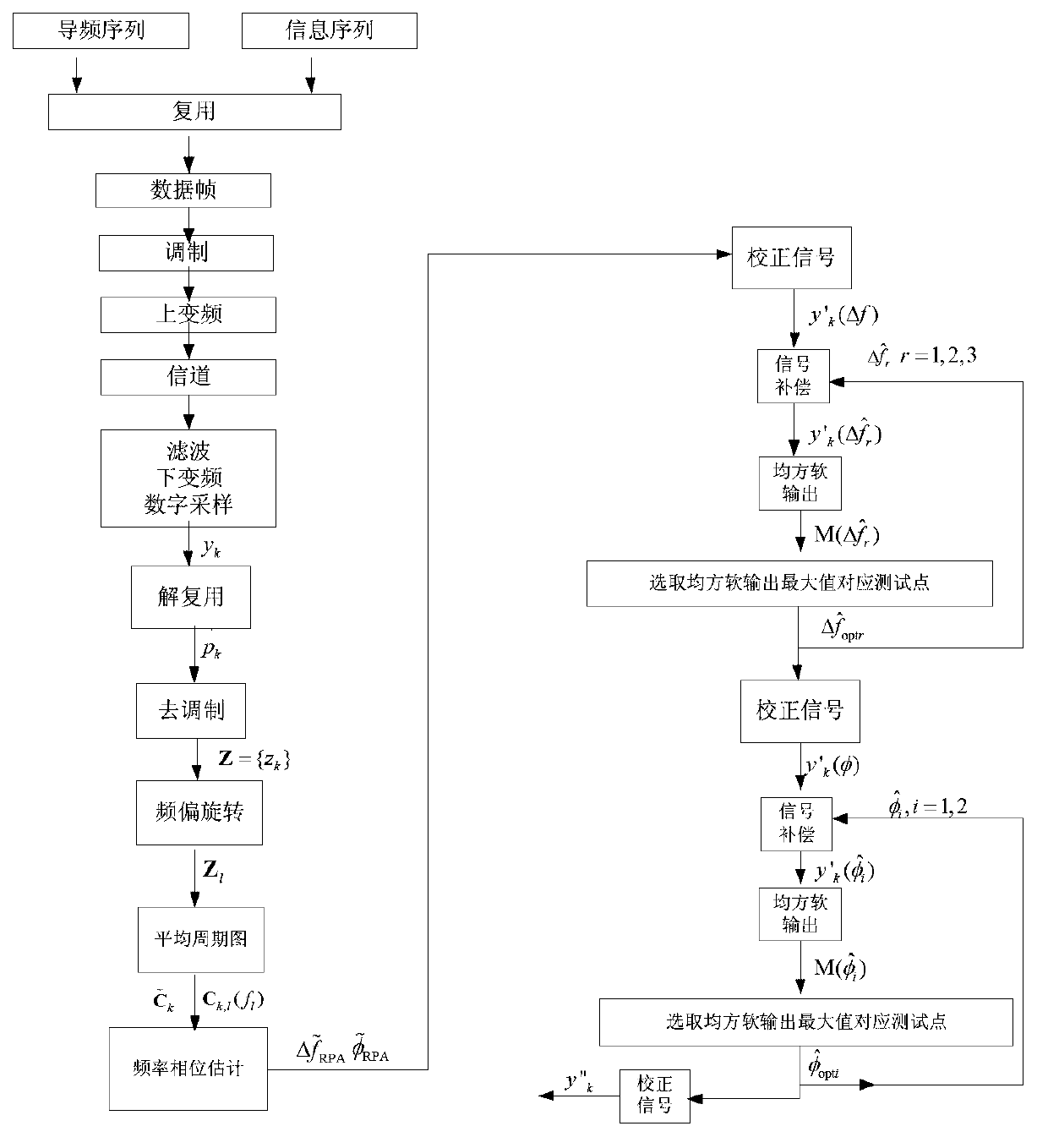

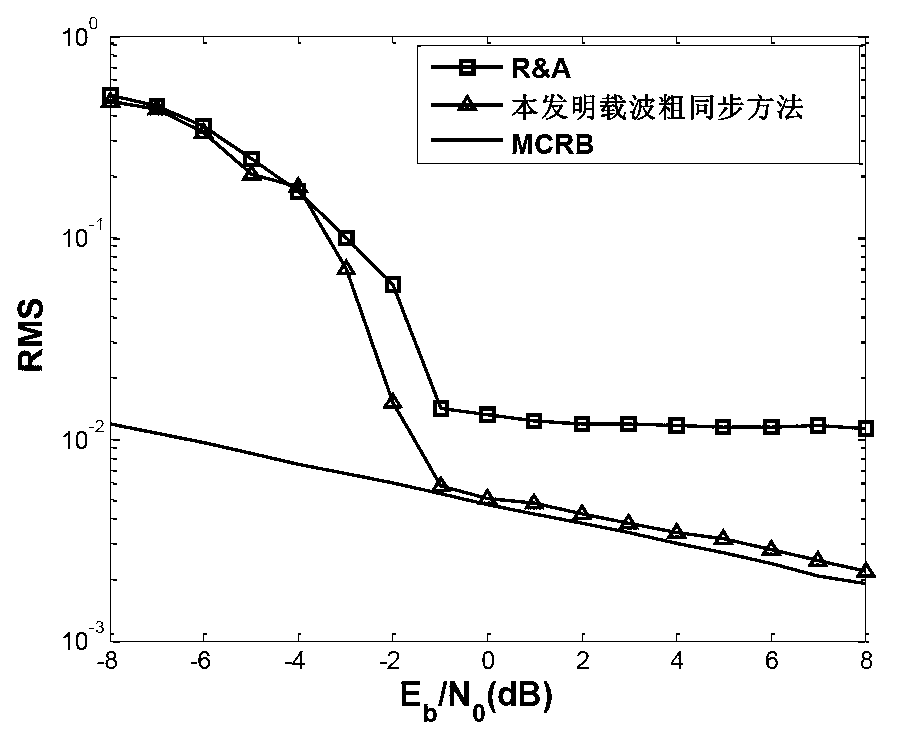

Carrier synchronization method based on rotation average period map and demodulation soft information

InactiveCN103281280AHigh spectral resolutionImprove estimation accuracyMulti-frequency code systemsFrequency spectrumCarrier frequency offset

The invention discloses a carrier synchronization method based on a rotation average period map and demodulation soft information and mainly aims at solving problems in the prior art, such as low carrier rough estimate accuracy, large pilot frequency expense and large carrier fine synchronization search operation amount. The method is realized by the following steps of carrying out demultiplexing on digitally sampled base band complex signals to obtain received pilot frequency signals; utilizing the pilot frequency signals to obtain the rough estimate values of a carrier frequency offset and a carrier phase offset by a carrier rough synchronization method; utilizing the carrier rough estimate values to correct the received signals; and respectively carrying out one-dimensional progressive search on the frequency offset and the phase offset by the corrected signals to obtain accurate frequency offset and phase offset values and realize carrier fine synchronization. With carrier rough synchronization disclosed by the invention, not only is the frequency spectrum resolution rate increased, but also higher estimate accuracy can be obtained at a low cost of the pilot frequency. Through carrier fine synchronization disclosed by the invention, search points are effectively reduced, the search efficiency is improved, and the operation amount is reduced. The method can be used for satellites and short-frame burst communication in high-speed movement.

Owner:XIDIAN UNIV

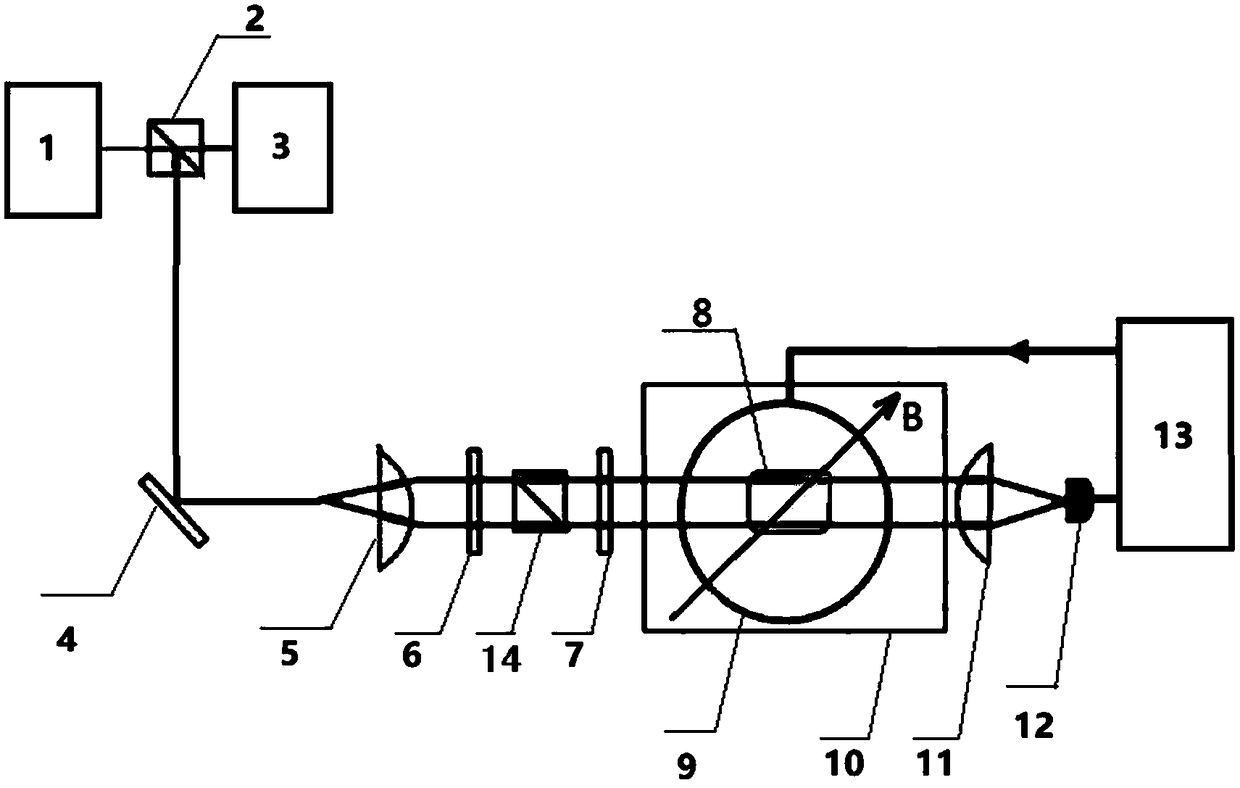

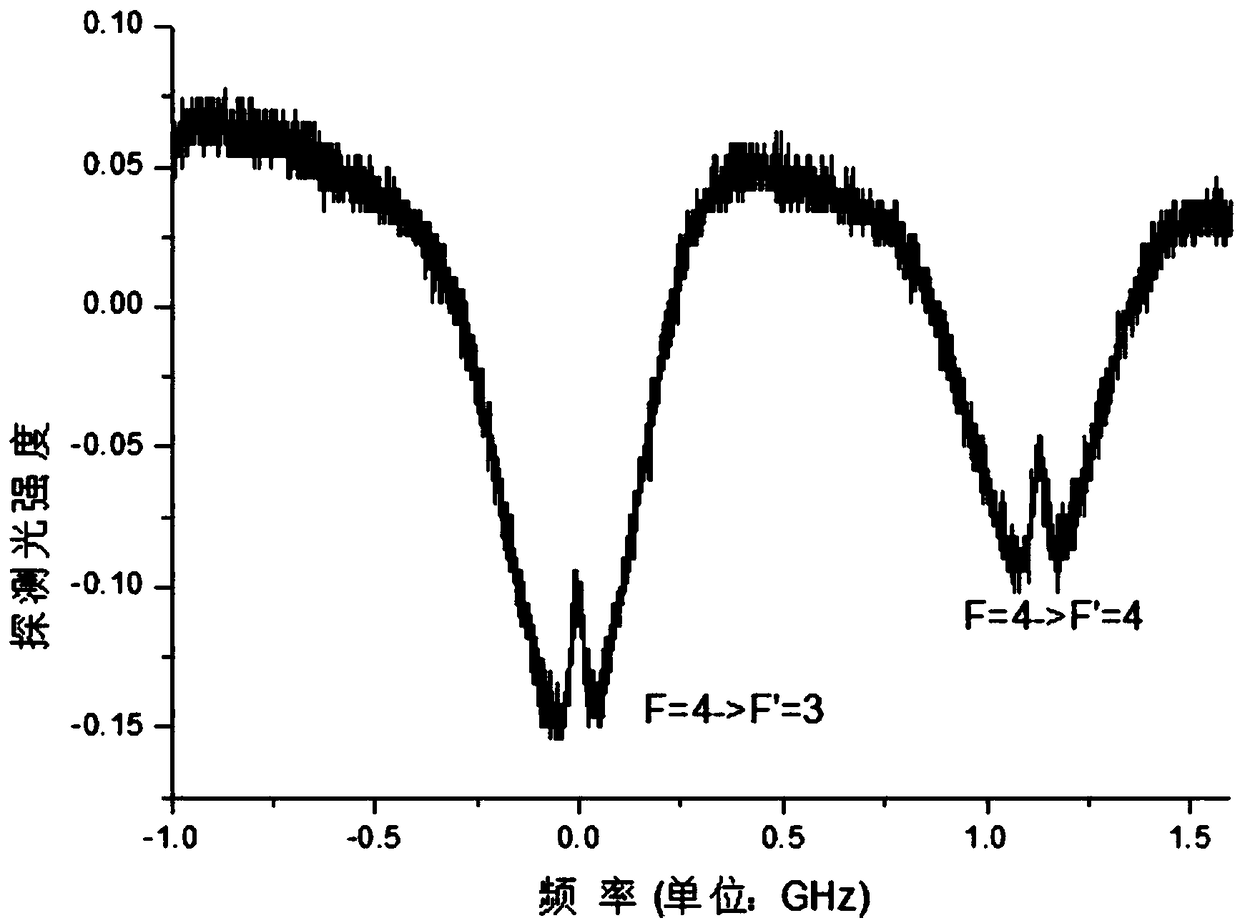

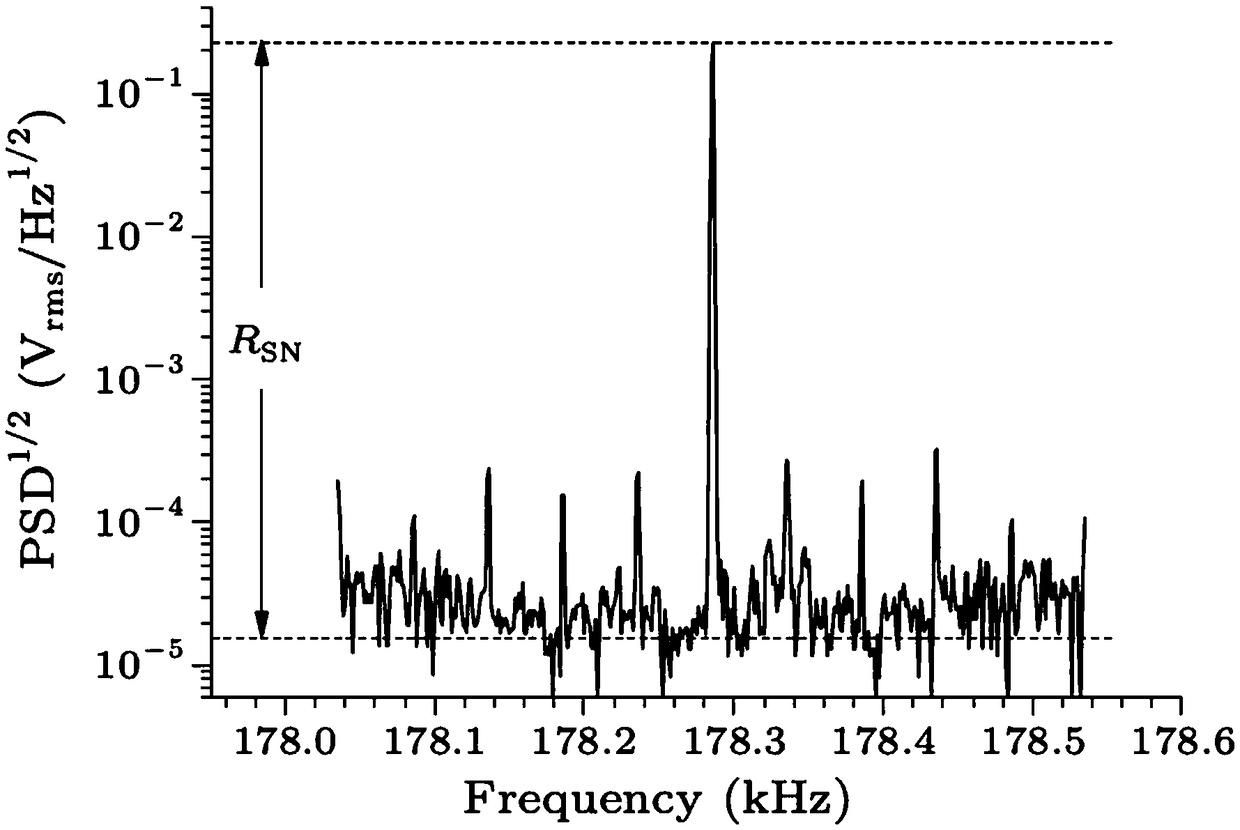

Cesium atom magnetometer

InactiveCN108919146ATimely and accurate magnetic field measurementHigh sensitivityMagnetic field measurement using magneto-optic devicesLow noiseClosed loop

The invention discloses a cesium atom magnetometer comprising a laser, a first polarization beam splitter, a laser frequency stabilization module, a reflecting mirror, a beam expander, a half wave plate, a second polarization beam splitter, a quarter wave plate, a cesium atom bubble, a radio frequency field coil, a magnetic shielding barrel, a lens, a photoelectric detector and a phase-locked module. By applying the self-made 894nm external cavity semiconductor laser, a laser frequency stabilization device and a low-noise magnetic field measurement environment are established, and the double-resonant cesium atom magnetometer based on combination of optical pumping and radio frequency magnetic resonance phases is realized. Through parameter optimization of the magnetometer and closed-loop measurement, the external magnetic field measured by the magnetometer achieves the ultimate sensitivity of 19fT / Hz<1 / 2> and the intrinsic sensitivity of 8.6pT / Hz<1 / 2>, the spatial resolution rate is less than 2cm, and the cesium atom magnetometer is a precision measurement powerful tool for studying of high excited level of atoms and molecules, and has important application value in the aspects ofbiomedicine, geophysics, quantum frequency markers, military detection and the like.

Owner:ZHEJIANG UNIV

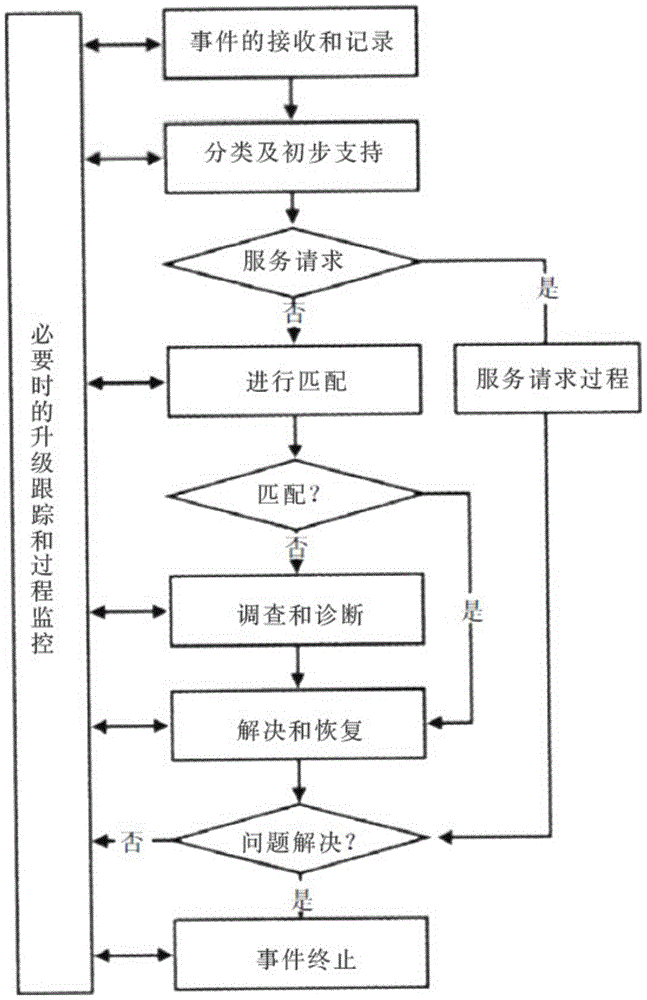

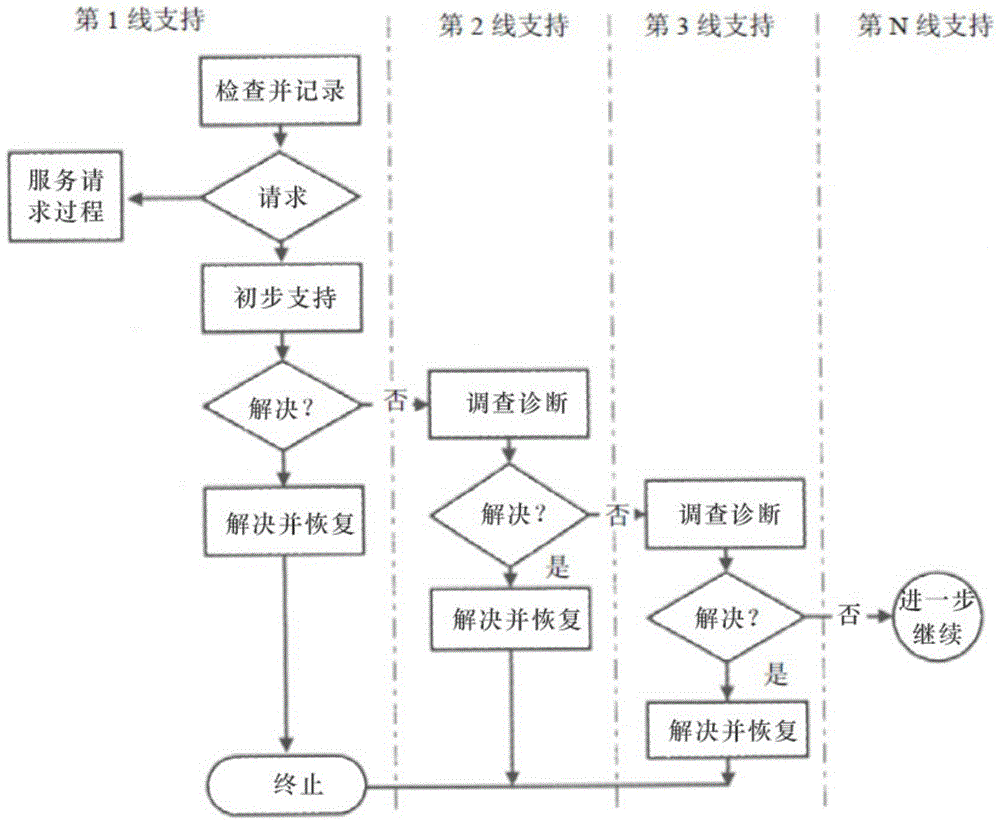

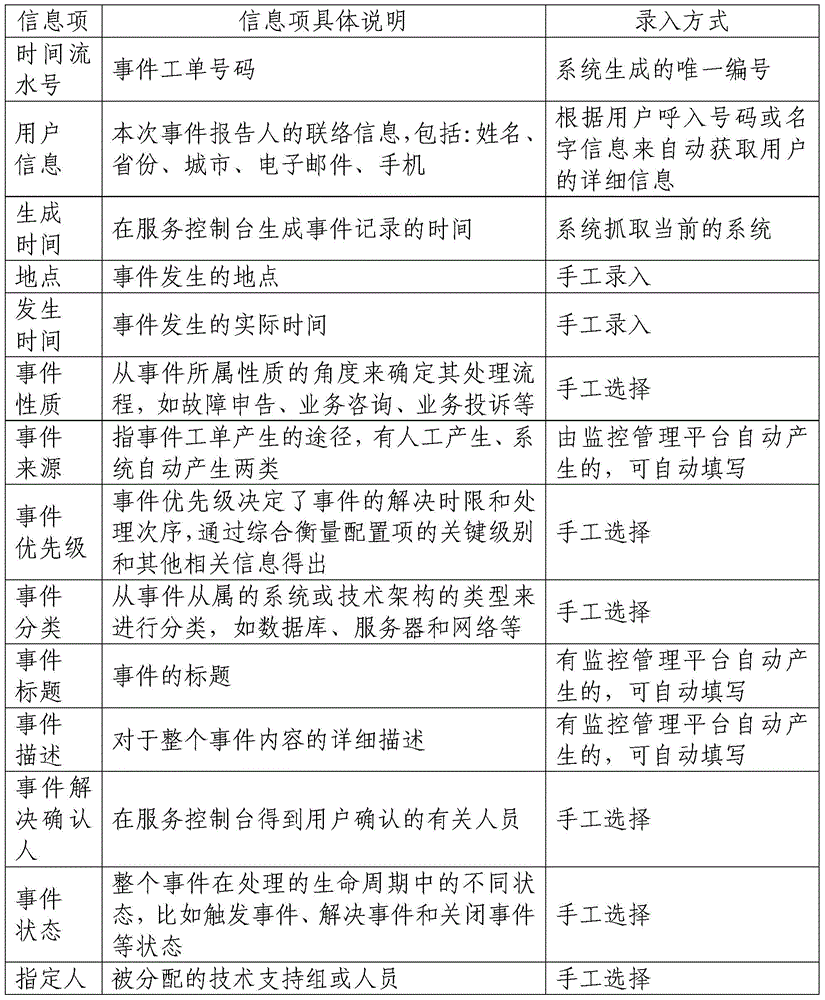

Small and medium-sized enterprise event management process

Disclosed is a small and medium-sized enterprise event management process. The process comprises the following steps: recording and accepting events; performing classification and online support; performing coupling; performing investigation and diagnosis; performing solution and recovery; and ending the events. Through such a management process, occurring events can be rapidly solved and service is recovered within an allowable cost scope, the stability of an enterprise service system is maintained, a highest possible event solution rate can be obtained, and satisfaction of a user is improved.

Owner:YILAN YUNLIAN TECH CO LTD

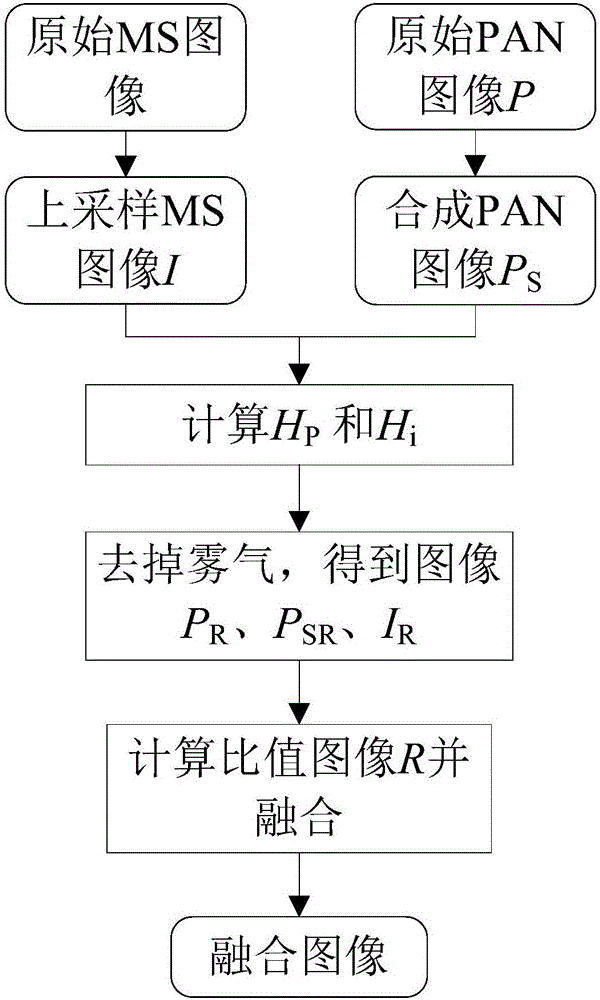

Improved method for fusing remote-sensing multispectrum with full-color image

InactiveCN106327455AReduce spectral distortionEnhance spatial detailImage enhancementImage analysisColor imageImage resolution

The invention discloses an improved method for fusing improved remote-sensing multispectrum with a full-color image. The improved method comprises steps of adopting a cubic convolution mode to up-sample an original MS image to a resolution ratio of an original PAN image to obtain an up-sampling image MS, using an average method on an original PAN image to perform down-sampling to obtain a resolution ratio of an MS image spatial, adopting the cubic convolution method to up-sample to the original PAN spatial resolution rate to obtain an synthetic PAN image, 2) using the original PAN image to calculate a fog value of a PAN waveband, using the original MS image to calculate the fog value of each MS waveband, removing fog in the up-sampling MS image, the original PAN image and the synthetic PAN image according to the fog value of the PAN waveband and the fog value of each MS waveband to obtain an image Ir, an image Pr and an image Psr, 3) performing deviation on pixels close to 0 in the image Psr, obtaining a proportion image according to the image Pr and the image Psr and using the image Ir, the proportion image and the fog value of each MS waveband to obtain a fusion image.

Owner:INST OF REMOTE SENSING & DIGITAL EARTH CHINESE ACADEMY OF SCI