Semiconductor device manufacturing device

a manufacturing device and semiconductor technology, applied in semiconductor/solid-state device manufacturing, basic electric elements, electric devices, etc., can solve the problems of low dielectric constant film, copper presents difficulties in patterning by dry etching, and resist removal step is liable to damage, so as to achieve small alignment differences

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

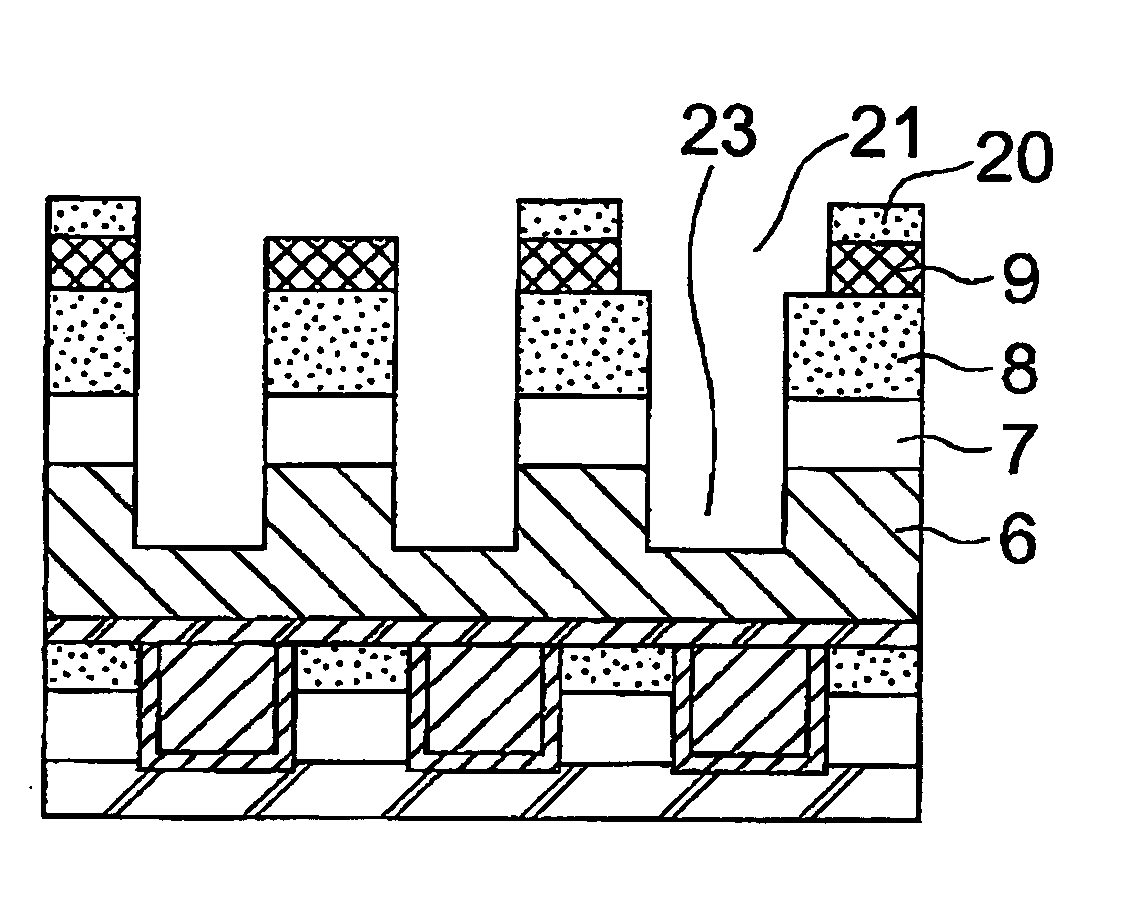

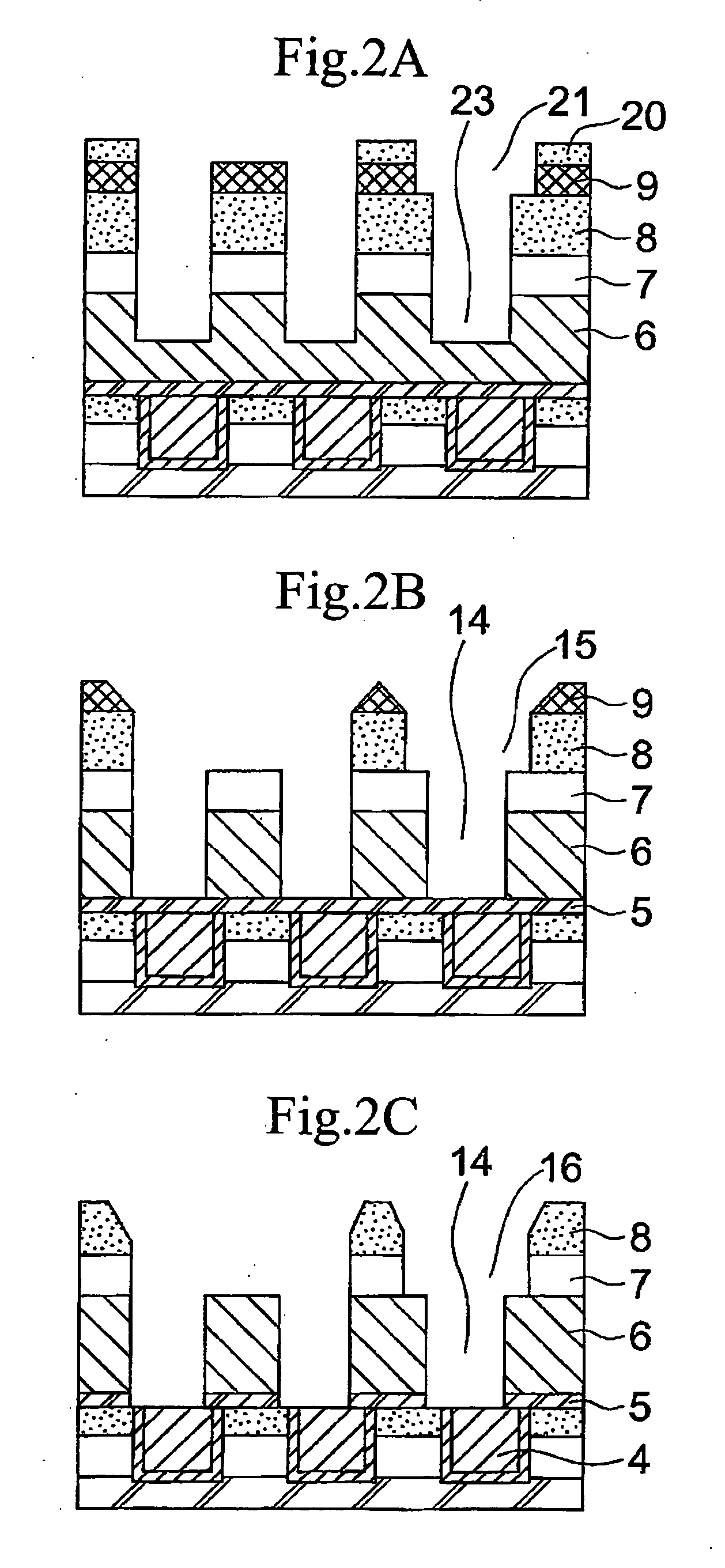

[0085] This embodiment demonstrates the process for production of a semiconductor device according to the first aspect of the present invention. FIGS. 1 to 3 are sectional views each showing the steps of forming the dual damascene structure on the semiconductor substrate by the process employed in this embodiment. Identical symbols are used to indicate those parts in FIGS. 1 to 3 and those parts in FIG. 7 to 9, which function in the same way. This applies also to FIGS. 4 to 6.

[0086] The process of this embodiment starts with the first step shown in FIG. 1A. A substrate (not shown) is coated with an underlying insulating film 1 by deposition. On the underlying insulating film 1 is formed an interlayer insulating film which is composed of an organic film 2 and a silicon oxide (SiO2) film 3. In the interlayer insulating film is formed a buried wiring 4 of copper (Cu) film, which is 250 nm thick.

[0087] On the Cu wiring 4 is formed a silicon carbide (SiC) film 5, 50 nm thick, as an oxi...

embodiment 2

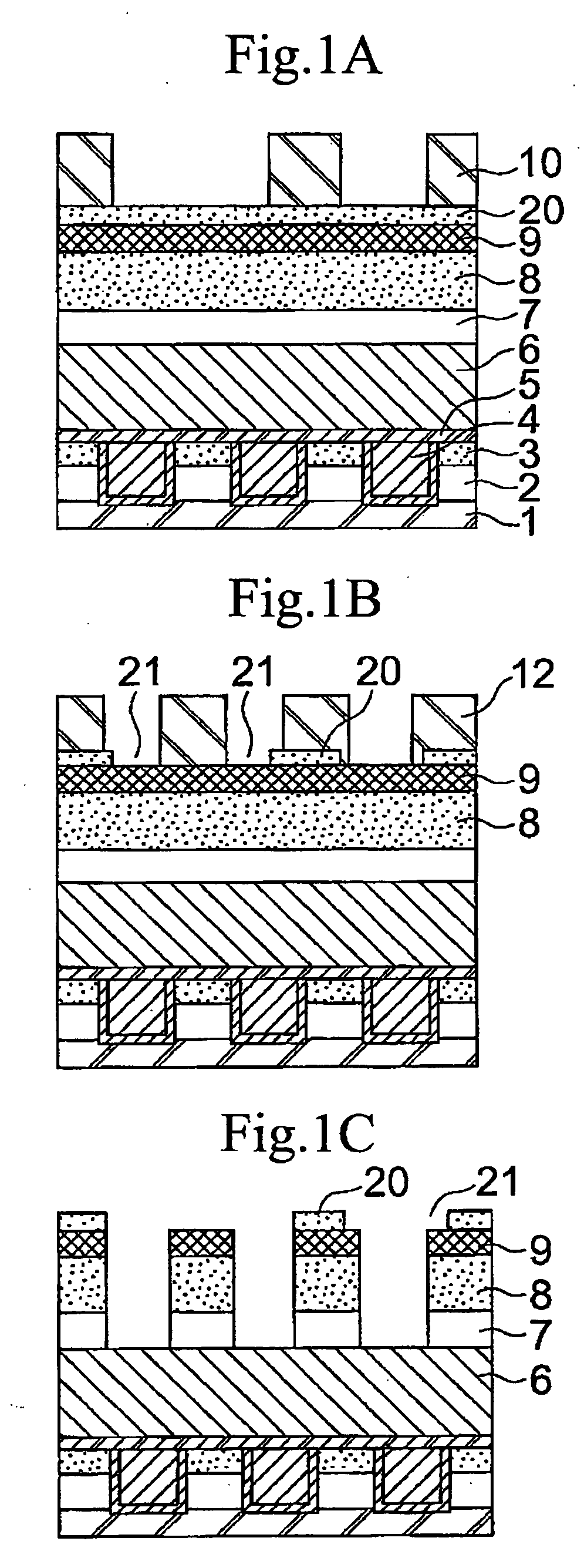

[0137] This embodiment demonstrates the process for production of a semiconductor device according to the second aspect of the present invention. FIGS. 4 to 6 are sectional views each showing the steps of forming the dual damascene structure by the method employed in this embodiment.

[0138] As in Embodiment 1, the process of this embodiment starts with the first step shown in FIG. 4A. A substrate (not shown) is coated with an underlying insulating film 1 by deposition. On the underlying insulating film 1 is formed an interlayer insulating film which is composed of an organic film 2 and a silicon oxide (SiO2) film 3. In the interlayer insulating film is formed a buried wiring 4 of copper (Cu) film.

[0139] On the buried wiring 4 of Cu film is formed a silicon carbide (SiC) film 5, 50 nm thick, as an oxidation preventing film. Then, a carbon-containing silicon oxide (SiOC) film 6, 400 nm thick, is formed. Further, a polyaryl ether (PAE) film 7, 200 nm thick, is formed, which is an orga...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More