Silicon carbide groove-shaped metal-oxide-semiconductor field-effect transistors (MOSFETs) and fabrication method thereof

A silicon carbide trench and silicon carbide substrate technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as unfavorable long-term stable operation of devices, reduced gate dielectric reliability, and reduced device conduction characteristics. , to reduce the reliability of blocking work, improve the carrier mobility, and reduce the overlap area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

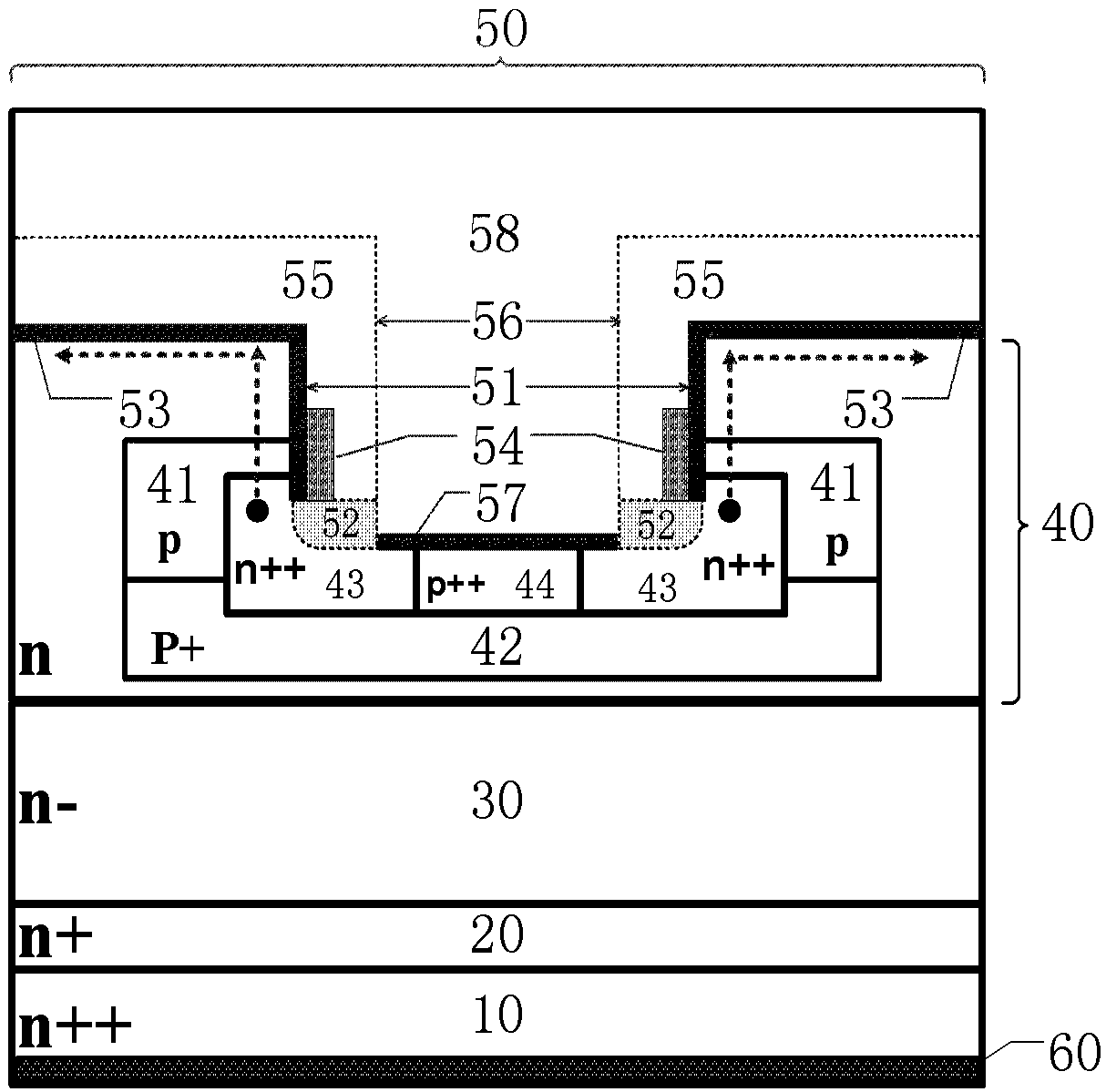

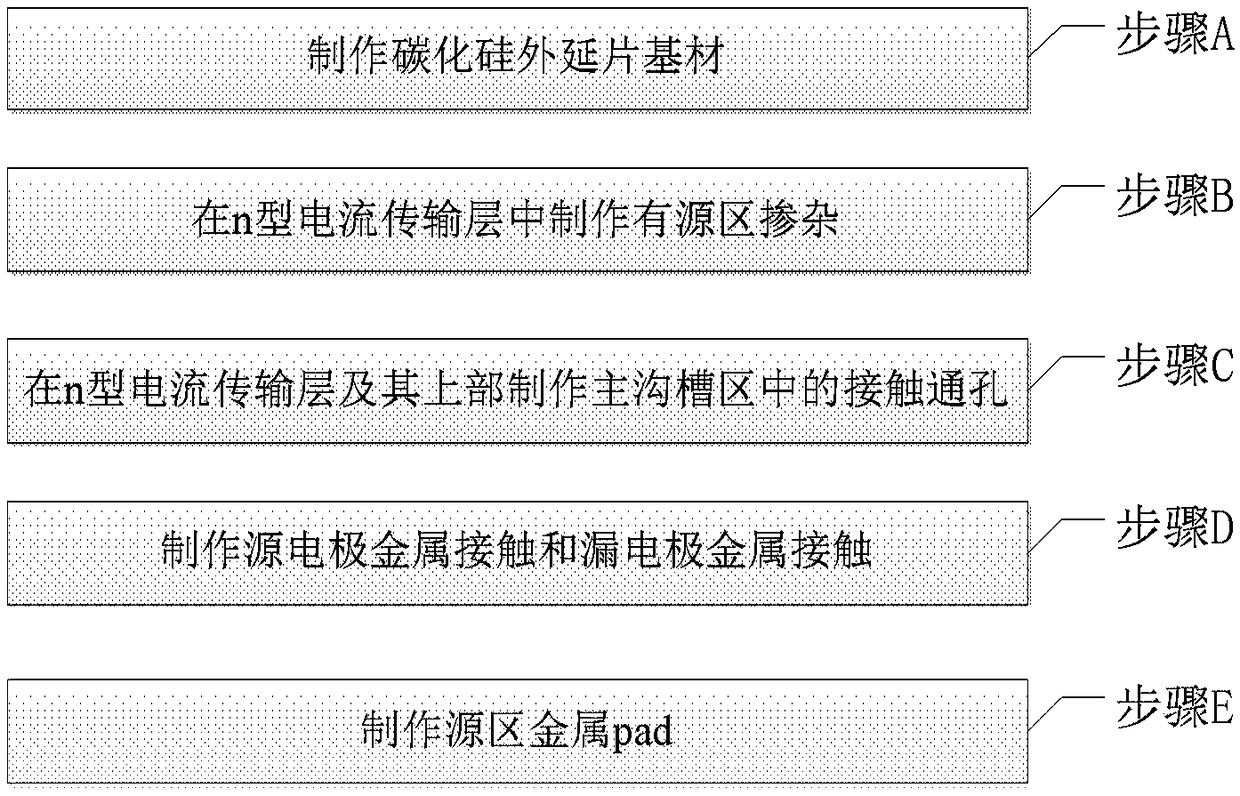

[0090] figure 2 It is a schematic diagram of the steps of the preparation method, such as figure 2 Shown, described preparation method comprises:

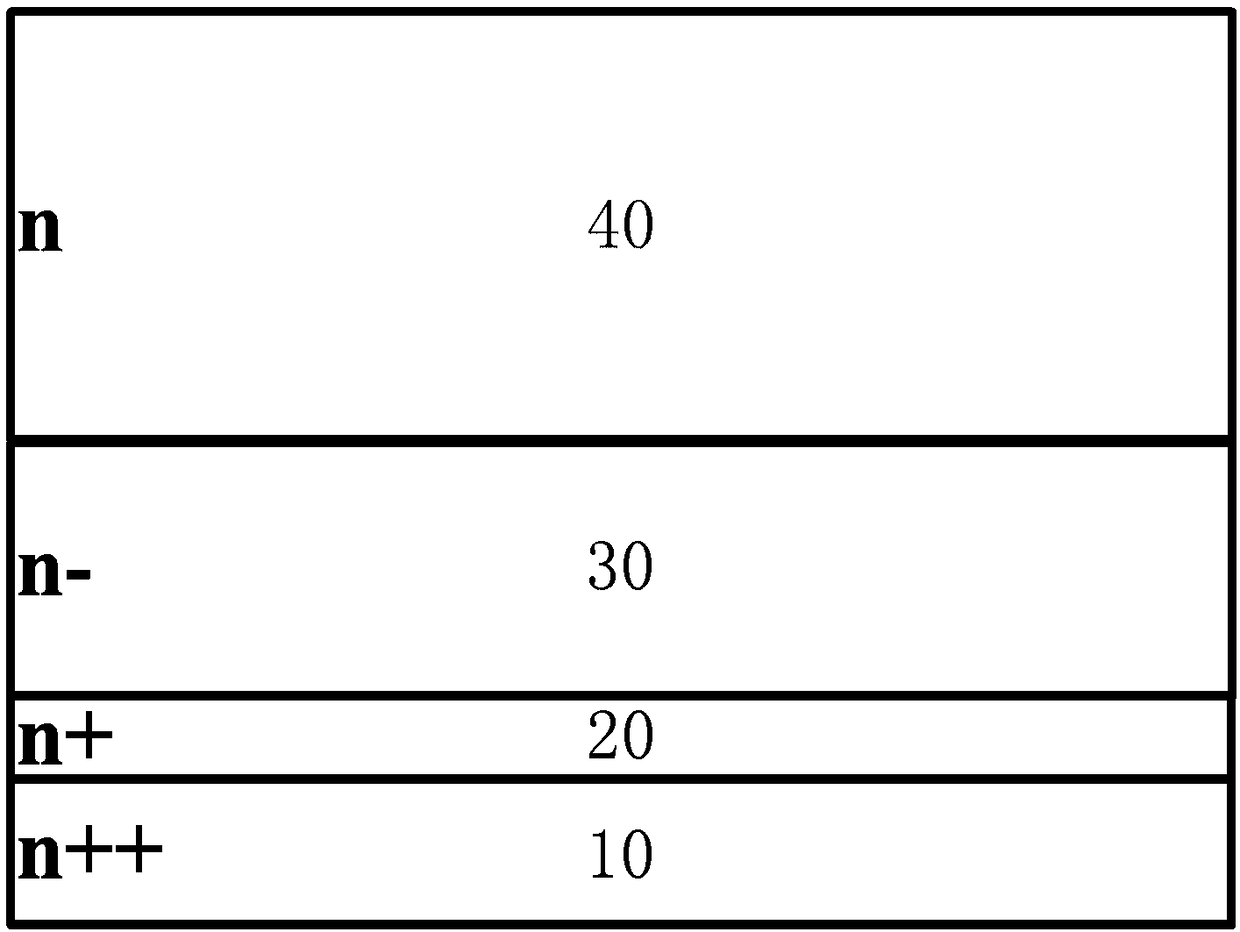

[0091] Step A: making a silicon carbide epitaxial substrate; including, epitaxially growing an n+ type buffer layer 20, an n-drift layer 30, and an n-type current transport layer 40 on the n++ type silicon carbide substrate 10 from bottom to top;

[0092] Step B: Doping the active region in the n-type current transport layer 40, including:

[0093]Sub-step B1: Deposit an implantation mask on the n-type current transport layer 40, pattern it by photolithography, and use doping methods such as ion implantation to form a top-down p-type trench in the n-type current transport layer 40 Road layer 41 and p+ type shielding layer 42;

[0094] In the sub-step B1, the doping concentration range of the p-type channel layer 41 is 1×10 16 cm -3 ~1×10 18 cm -3 , the distance between the upper surface and the upper surface of the n-type ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More