Super junction structure and manufacturing method thereof

A superjunction, N-type technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0055] The super junction structure of the first embodiment of the present invention:

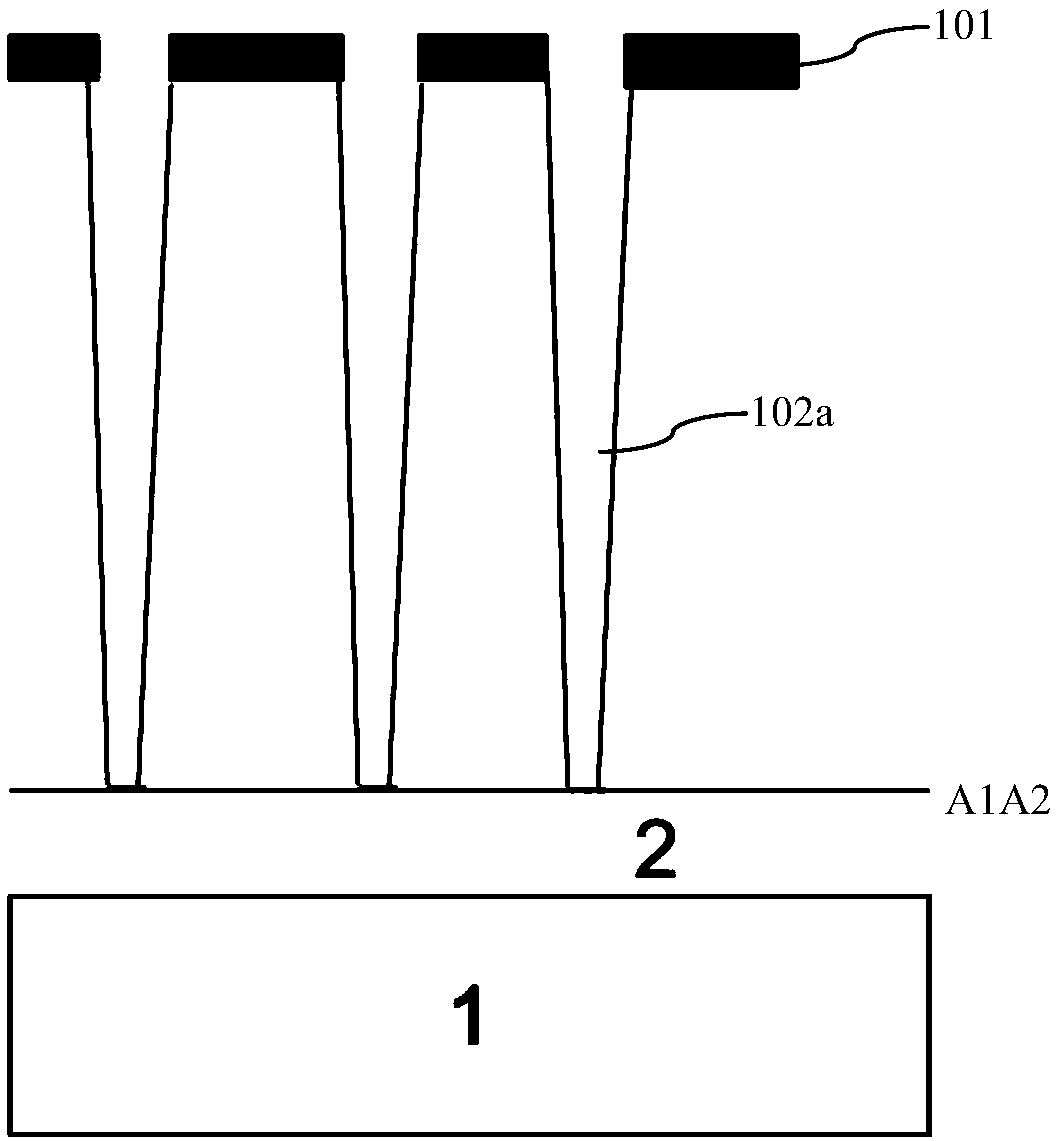

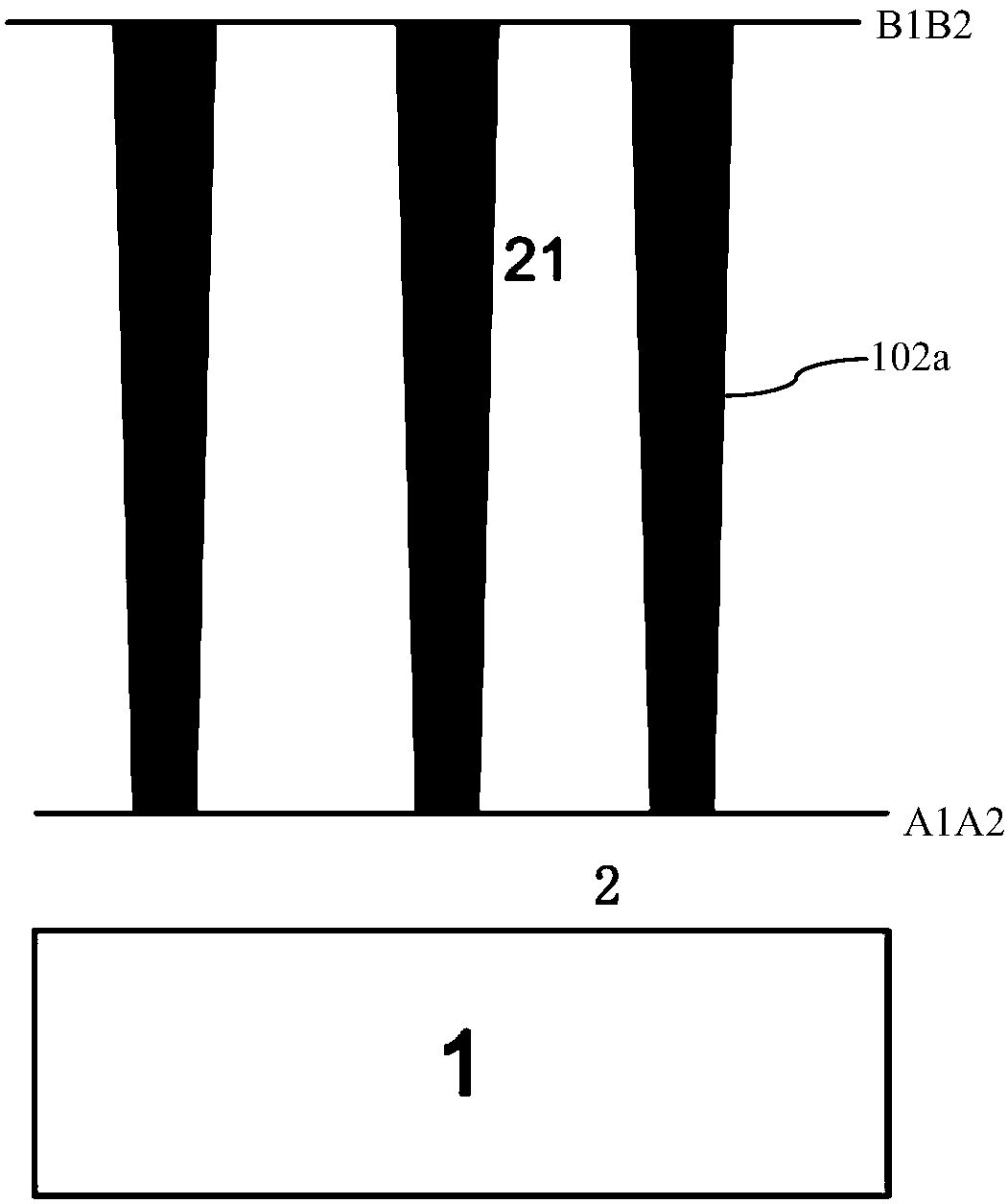

[0056] Such as Figure 1C Shown is the device structure diagram of the super junction structure of the first embodiment of the present invention; figure 2 It is a device structure diagram of a super-junction device formed by adopting the super-junction structure of the first embodiment of the present invention. The super-junction structure of the first embodiment of the present invention includes:

[0057] The first N-type sub-epitaxial layer 2 is formed in the first N-type sub-epitaxial layer 2 with first P-type sub-columns 31 and first N-type sub-columns 21 alternately arranged to form a first super-junction sub-structure.

[0058] The second N-type sub-epitaxial layer is formed on the surface of the first N-type sub-epitaxial layer 2 formed with the first superjunction sub-structure, and the second N-type sub-epitaxial layer is formed in the second N-type sub-epitaxial layer. The seco...

no. 1 example

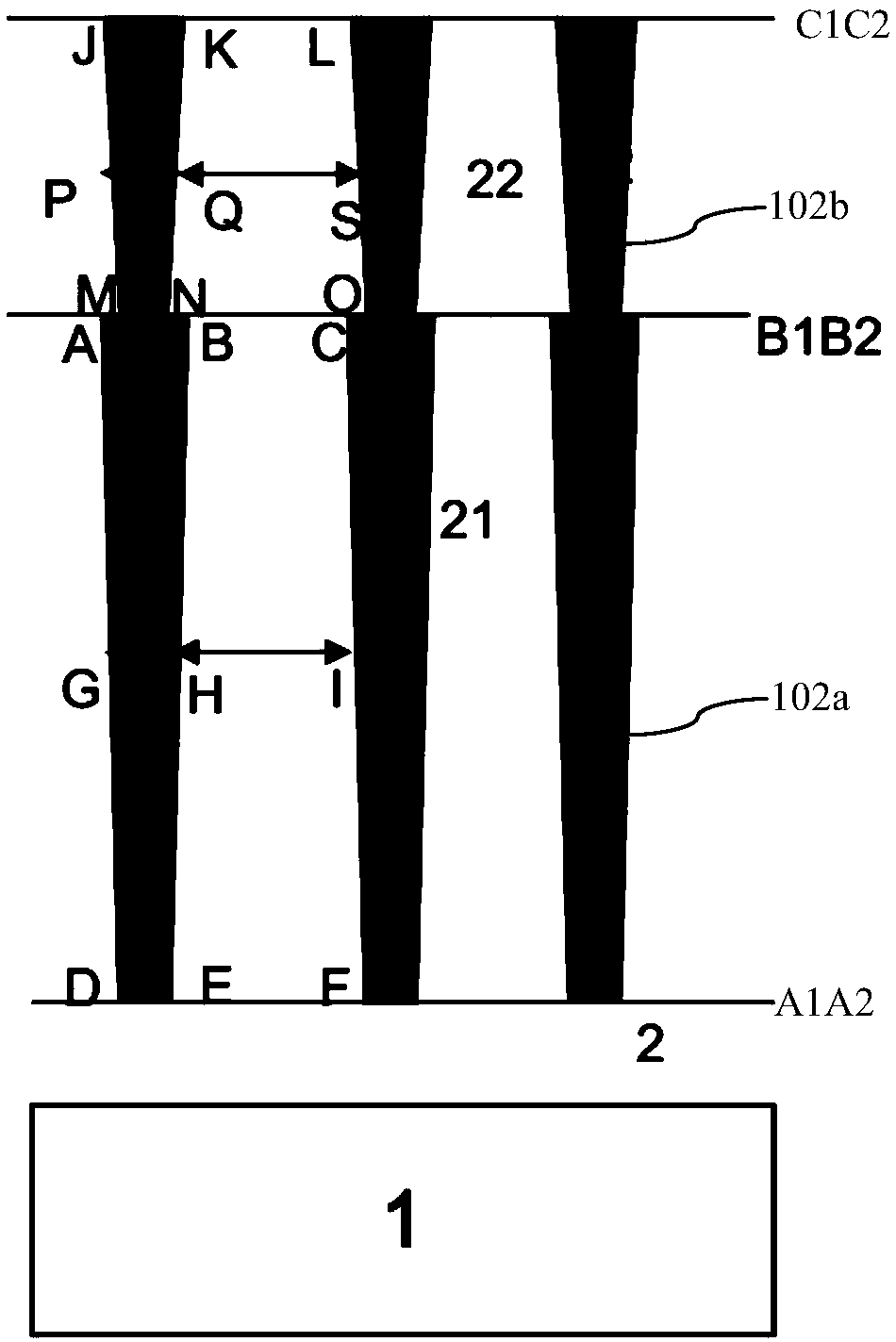

[0084] for more clarity figure 2 The super junction device of the first embodiment of the present invention is shown, and the device structure of the first embodiment of the present invention will be described below with specific parameters:

[0085] The resistivity of the semiconductor substrate 1 is 0.001 ohm·cm to 0.003 ohm·cm, and the thickness is about 725 microns.

[0086] The position of the bottom surface of the first sub-trench 102a is shown by the line A1A2, and the position of the top surface of the first sub-trench 102a is shown by the line B1B2.

[0087] The first N-type sub-epitaxial layer 2 has a thickness of 45 microns to 50 microns, a resistivity of 1.57 ohm·cm, and a doping concentration of 3.0e15cm -3 The side inclination angle of the first sub-groove 102a is 88.6 degrees, the depth is 40 microns between the line A1A2 and B1B2, the top width is 4 microns, the width AB between the points A and B for short, and the bottom The width between points D and E is...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Top width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com