Manufacturing method for gate and semi-conductor device

A manufacturing method and semiconductor technology, applied in the manufacture of semiconductor devices and the field of gate manufacturing, can solve problems affecting the performance of semiconductor devices, affecting the etching of gate layer 14, and reducing production, and achieve strong ability to remove residual defects, The effect of increasing productivity and reducing execution time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

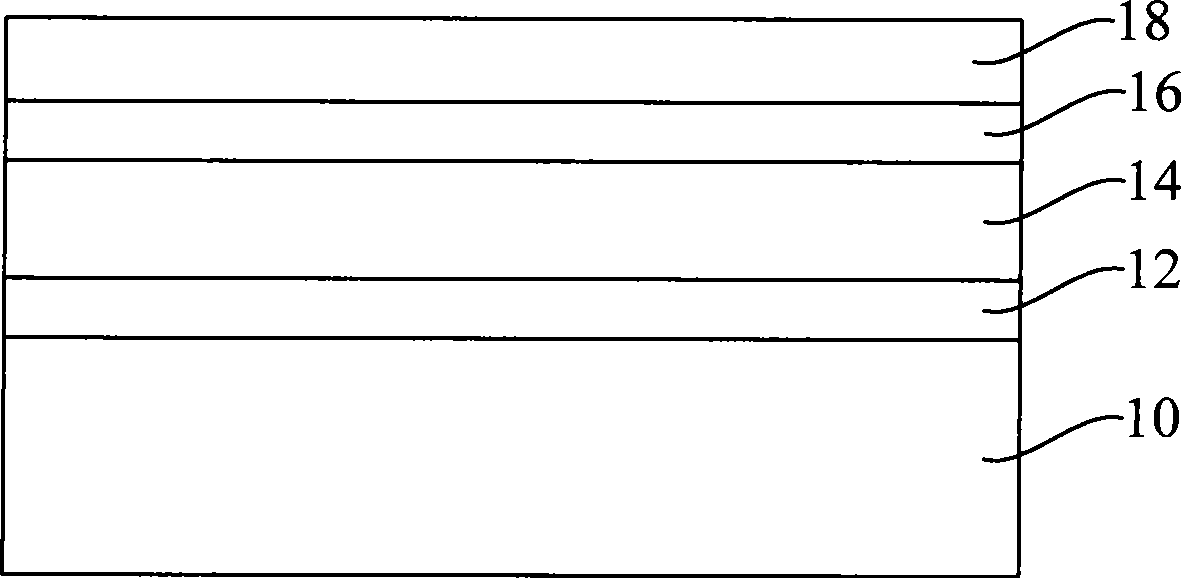

[0057] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0058]In an embodiment of the present invention, a method for manufacturing a gate is provided: first, a semiconductor substrate including a gate layer is provided, an anti-reflection layer is formed on the gate layer, and a photolithography layer is formed on the anti-reflection layer. Adhesive layer;

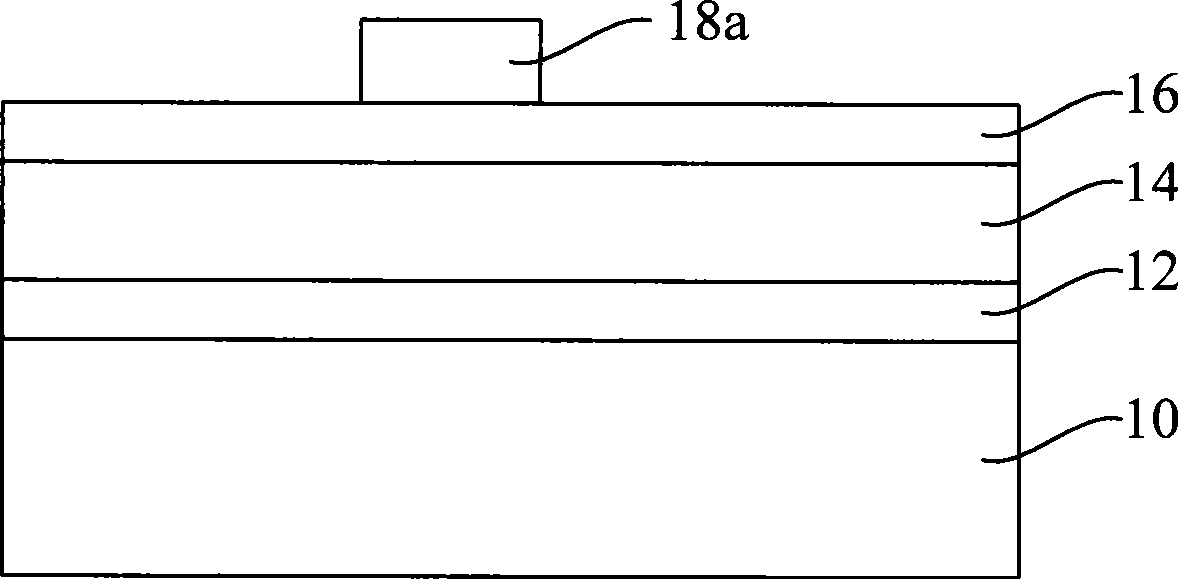

[0059] Next, patterning the photoresist layer to form a photoresist pattern of the gate, the patterning process includes a photolithography process, or a photolithography process and a photoresist reduction process;

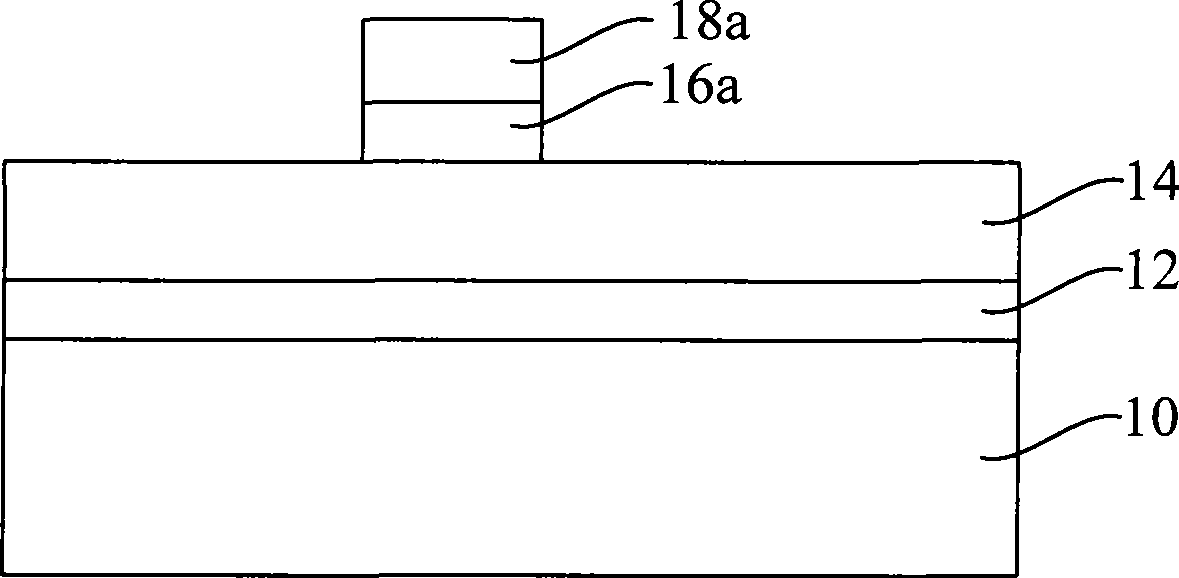

[0060] Then, etching and removing the anti-reflection layer not covered by the photoresist pattern, wherein the etching process includes: performing a main etching process on the anti-reflection layer with plasma; have CF 4 and O 2 performing an over-etching process on the anti-reflection layer with a gas plasma;

[0061]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More