Patents

Literature

160results about How to "Reduce etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

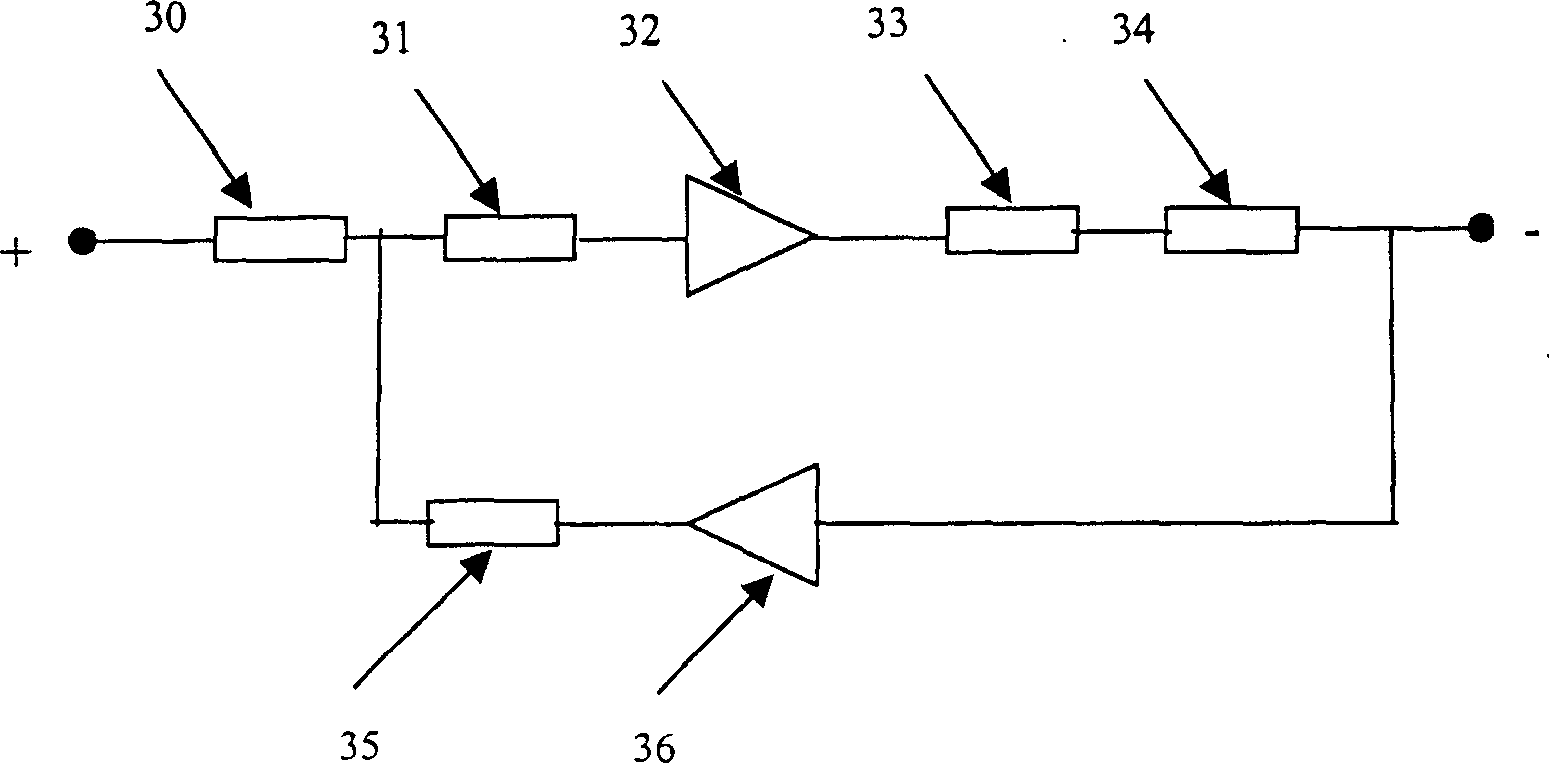

Method and apparatus for forming optical gratings

InactiveUS6172792B1Increase contrastFast response timeDiffraction gratingsNon-linear opticsGratingElectrical field strength

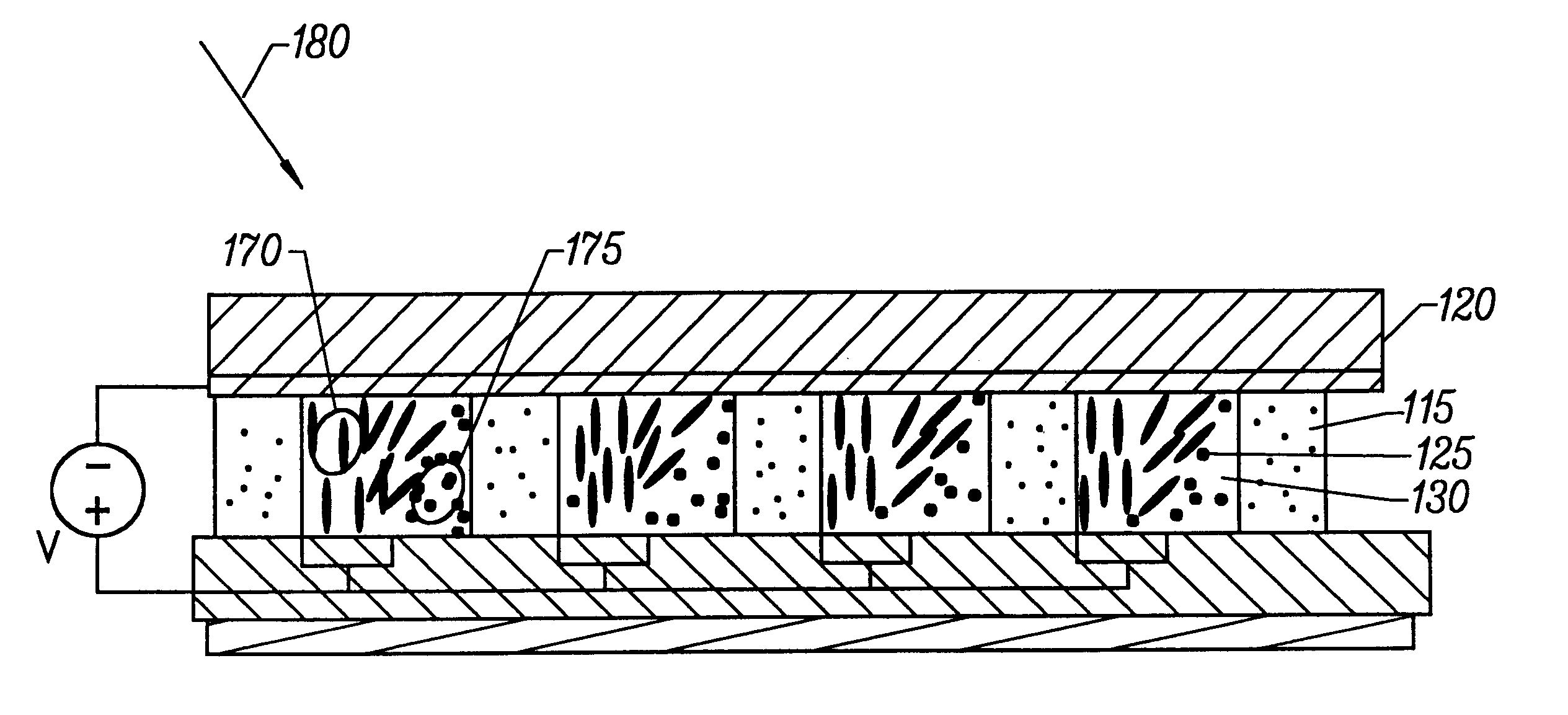

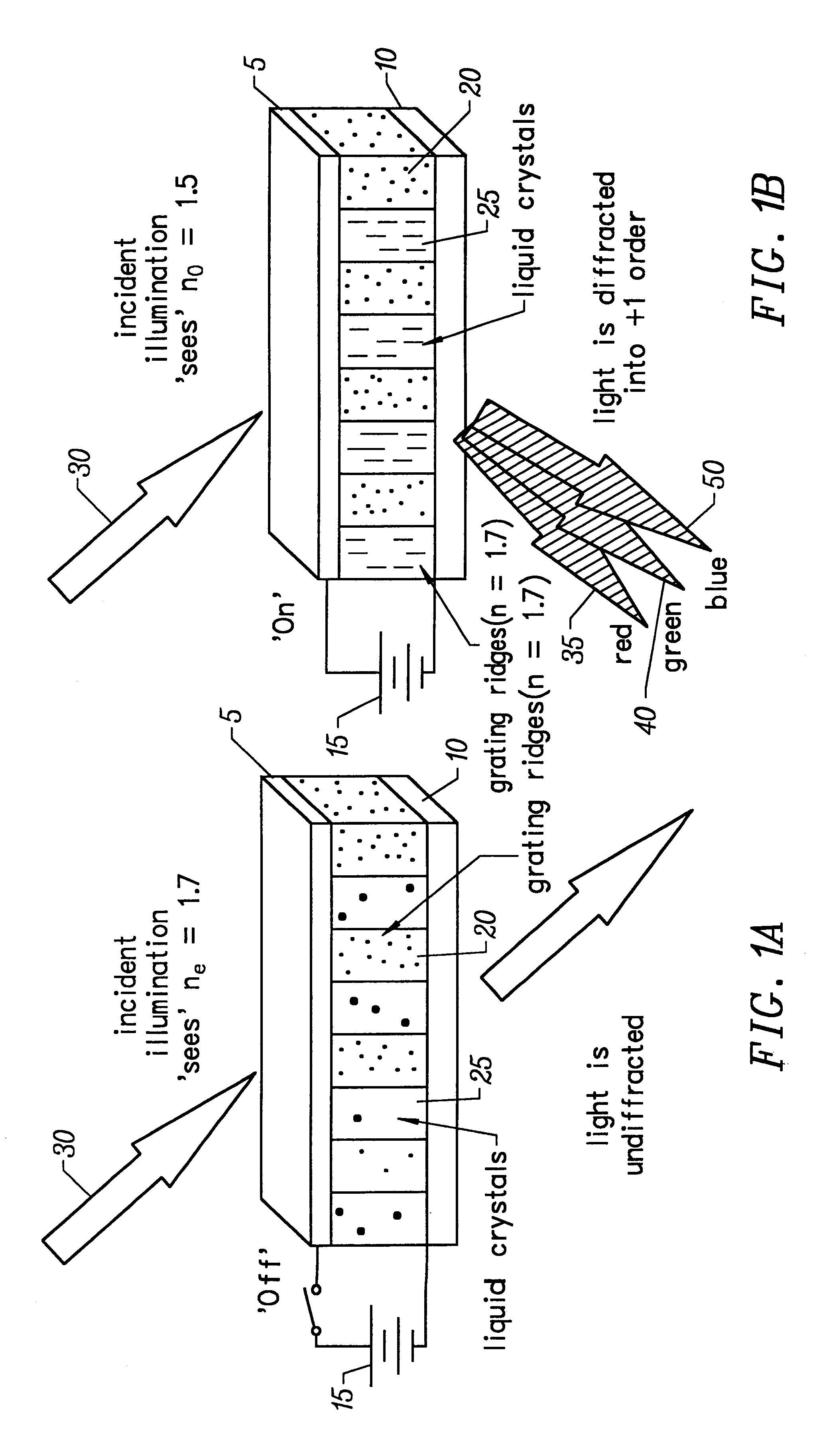

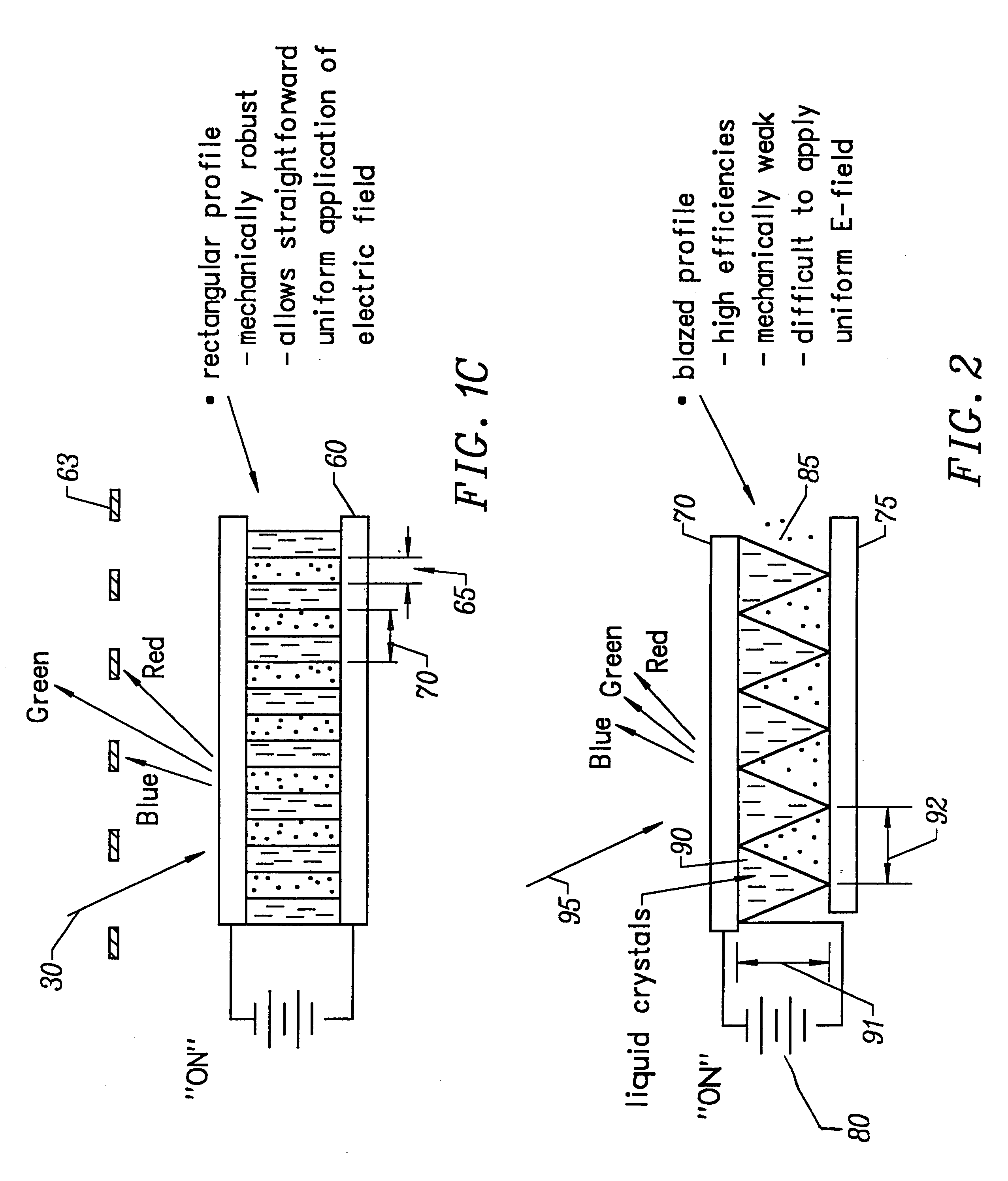

An apparatus for redirecting physical energy includes a substrate defining a first boundary of a region, a first electrode defining a second boundary of the region, the second boundary disposed opposite to the first boundary, a second electrode adjacent to the first boundary for cooperating with the first electrode to apply a non-uniform electric field to the region, the non-uniform electric field having electrical field intensities simultaneously including a first electric field intensity and a second electric field intensity, and a layer of material disposed in the region, the layer having a variable index of refraction responsive to the electric field intensities of the non-uniform electric field, the variable index of refraction including a first index of refraction in response to the first electric field intensity and a second index of refraction in response to the second electric field intensity.

Owner:ROSSELLA

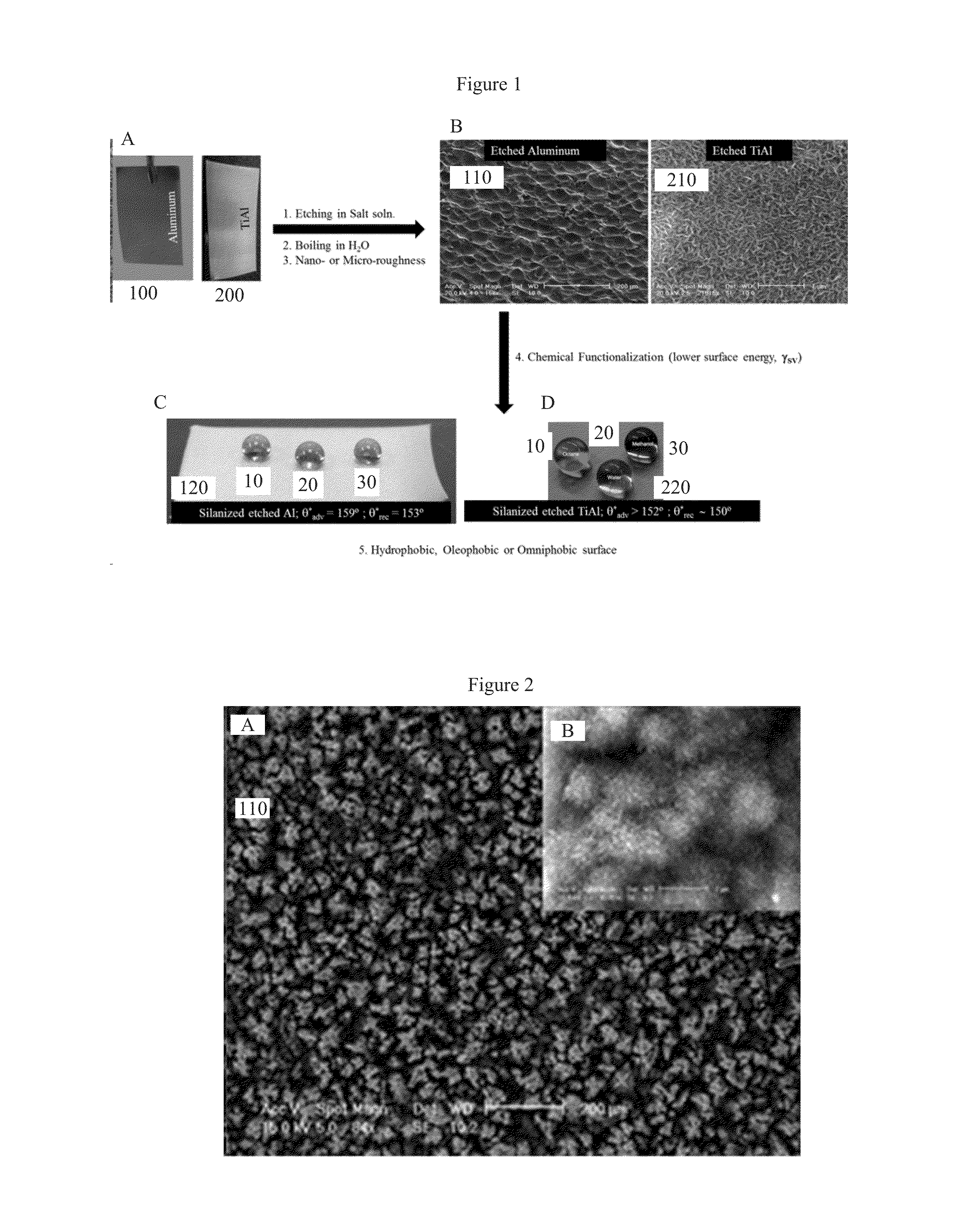

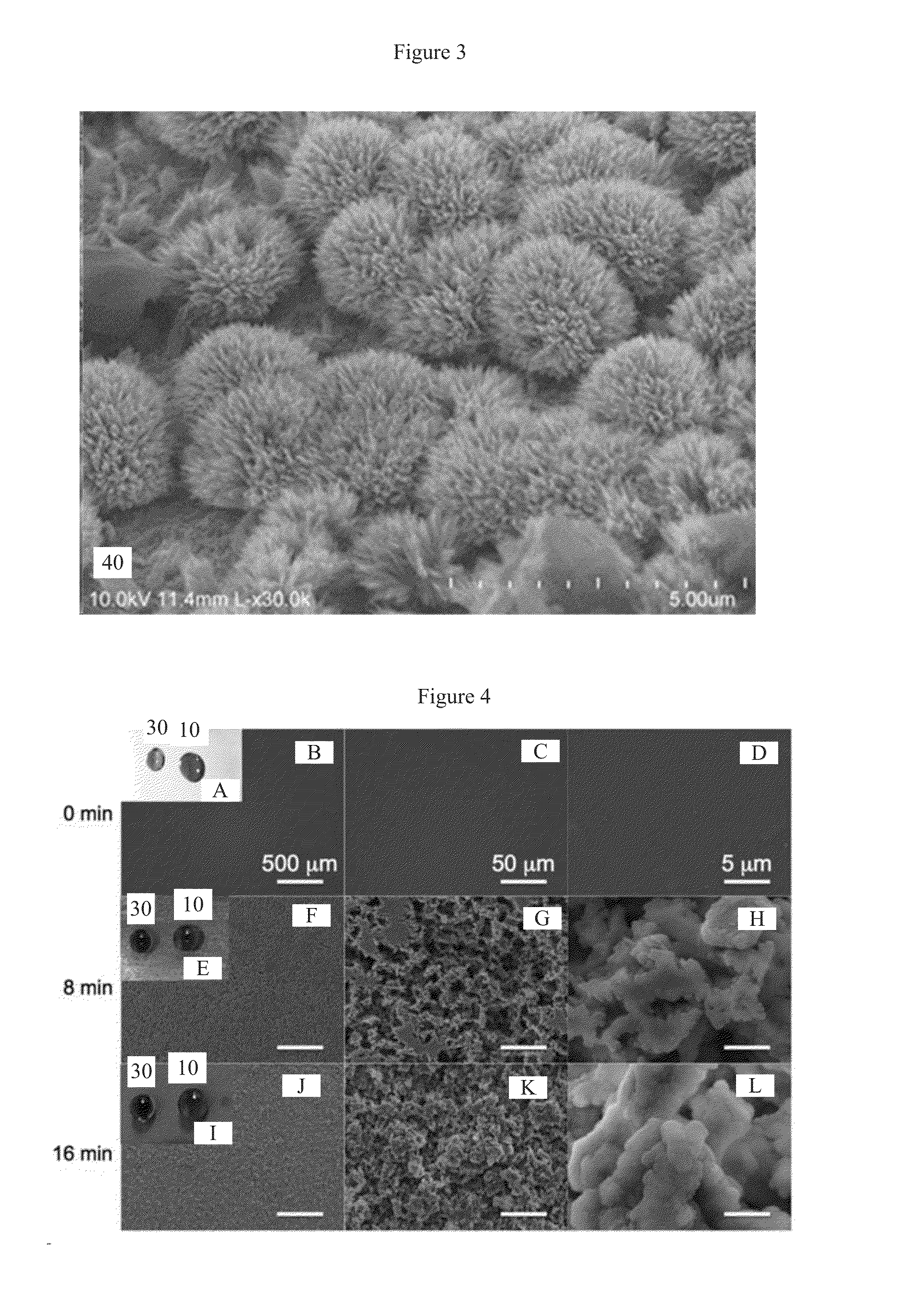

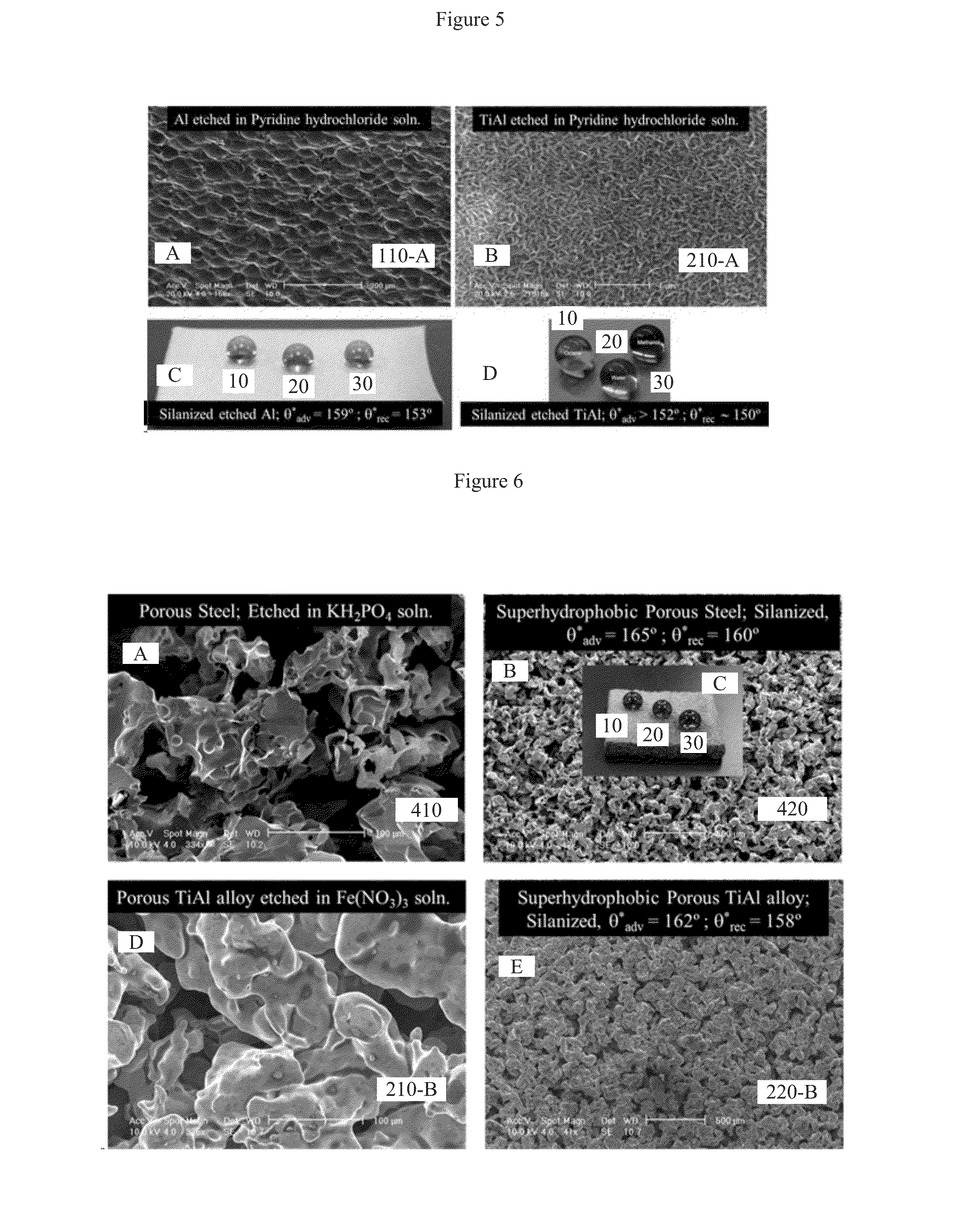

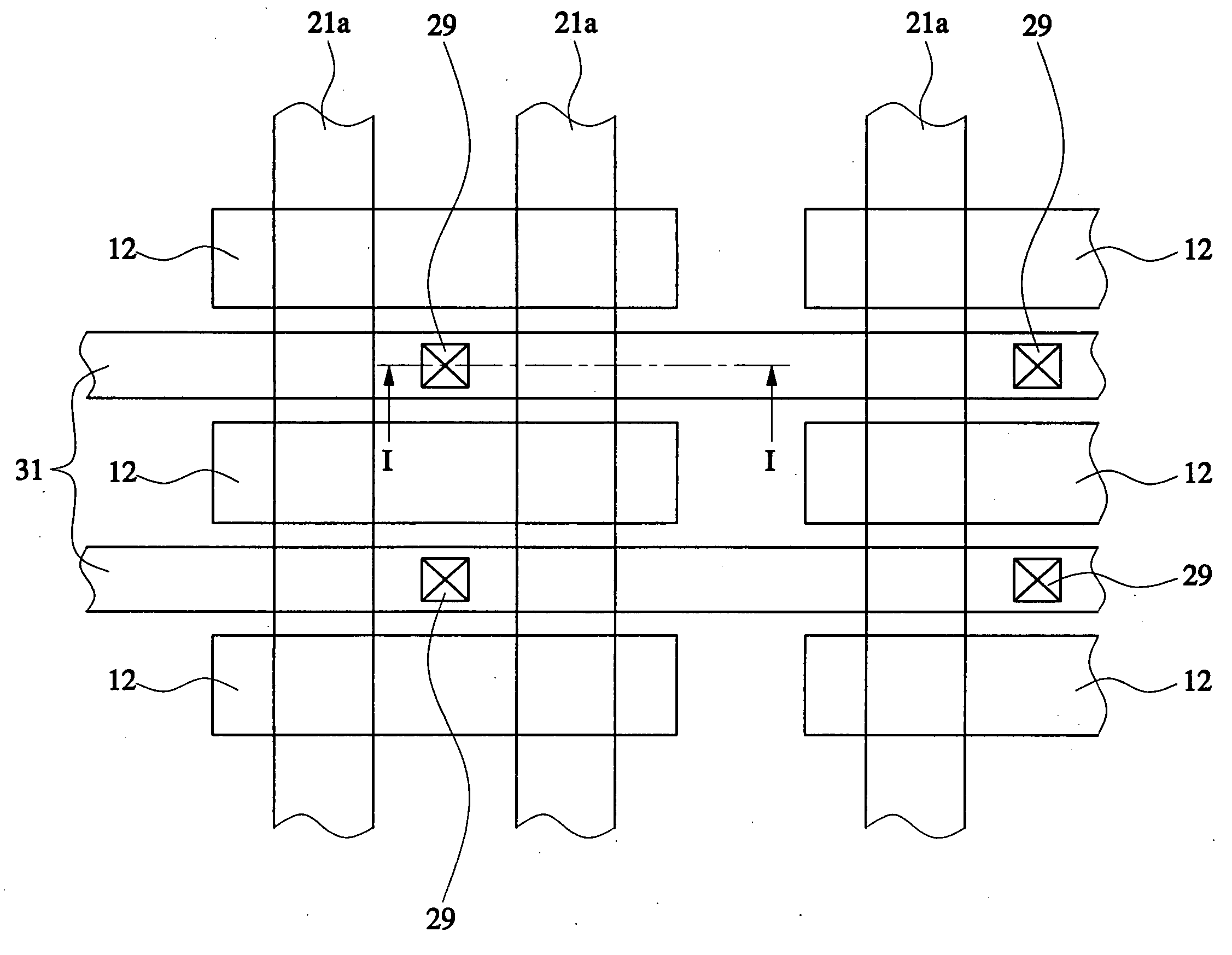

Salt Based Etching of Metals and Alloys for Fabricating Superhydrophobic and Superoleophobic Surfaces

InactiveUS20160153094A1Reduce etchingEasy disposalDecorative surface effectsMetallic material coating processesEtchingRe entrant

A process to etch hierarchical, re-entrant texture into the surface of metals and their alloys using salt-based etching solutions. The process imbues superhydrophobic, oleophobic or superoleophobic, omniphobic or superomniphobic properties by further imparting a low surface energy coating onto the etched surfaces by chemical functionalization by low surface energy hydrophobilizing compounds.

Owner:TUTEJA ANISH +2

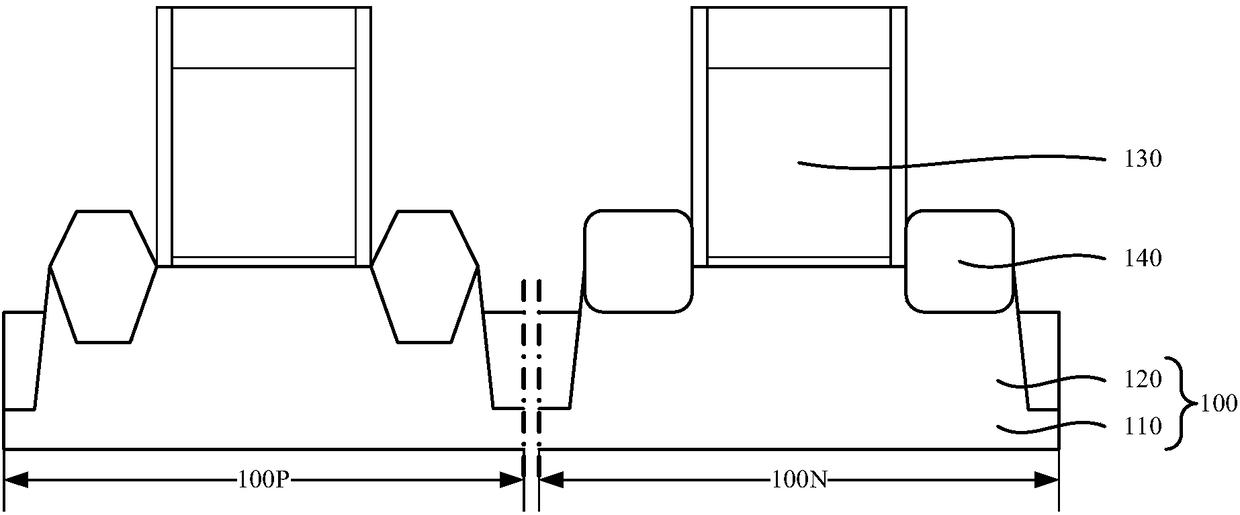

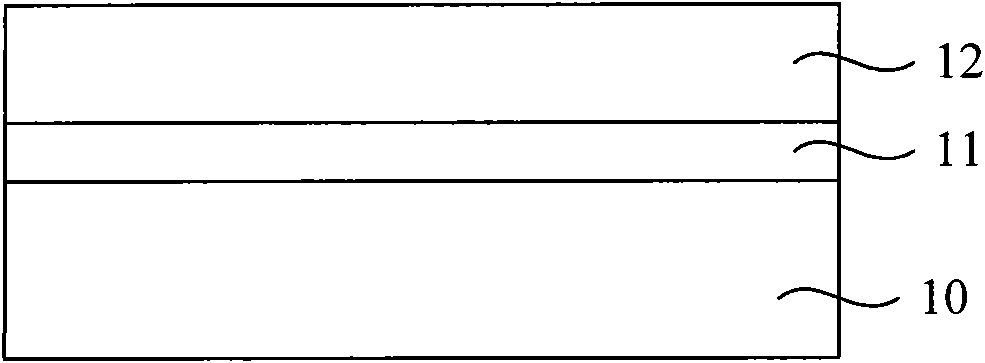

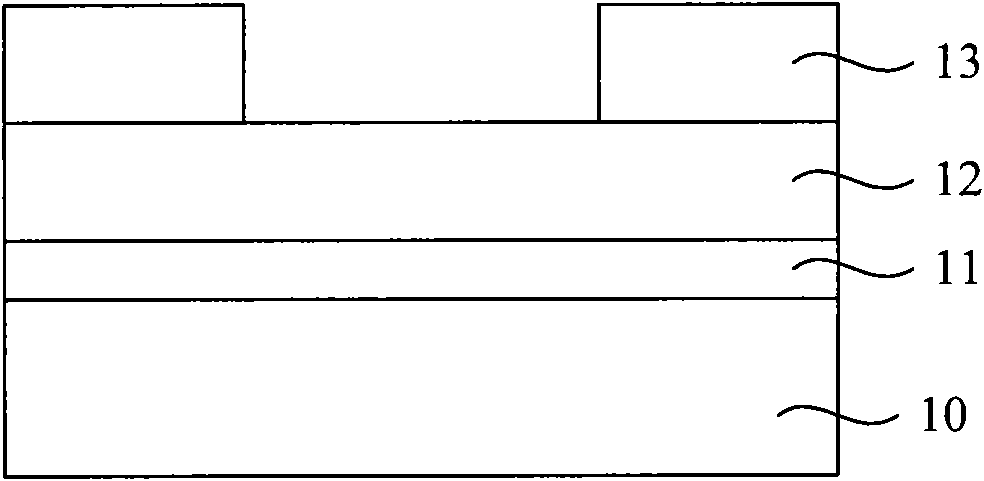

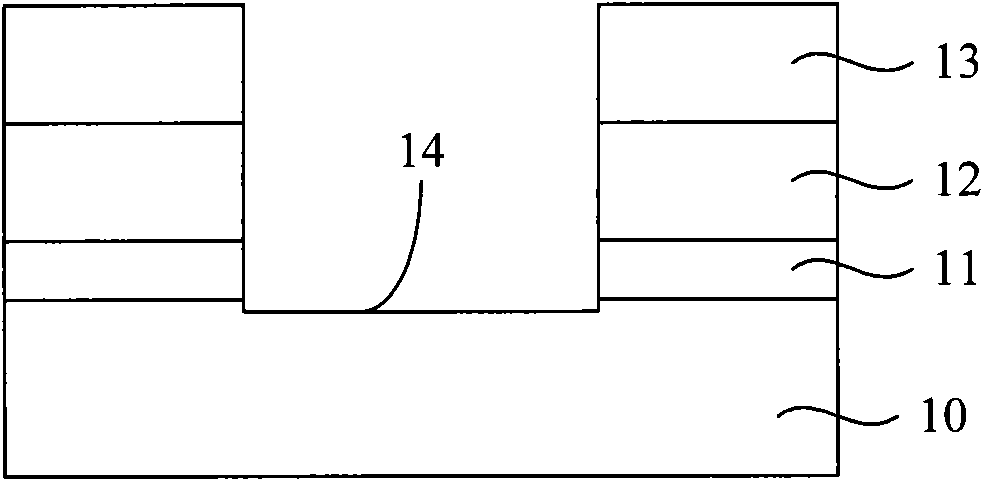

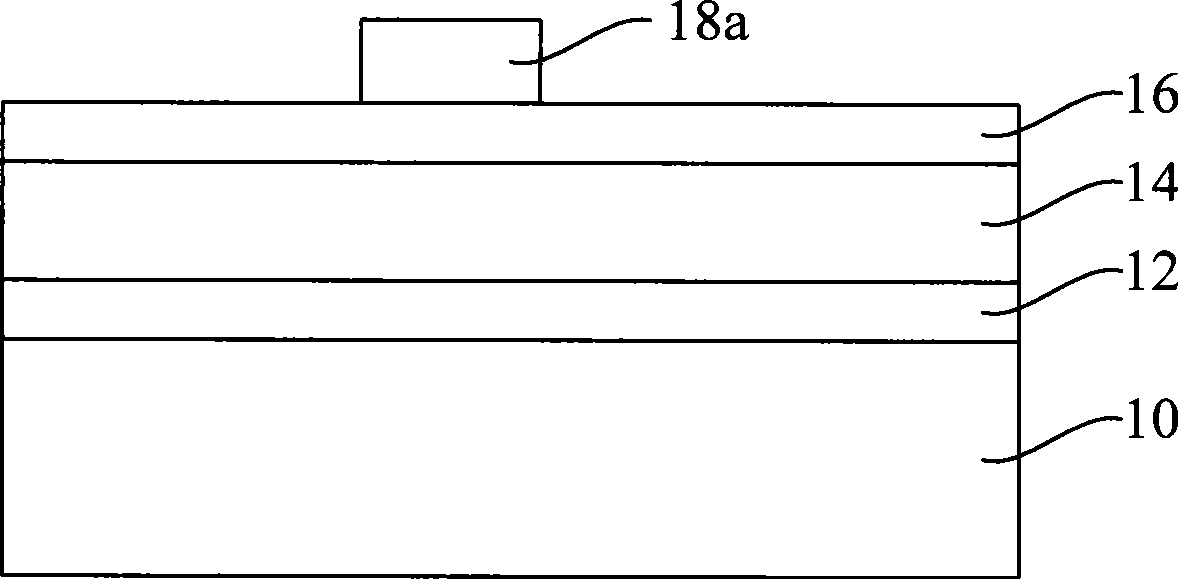

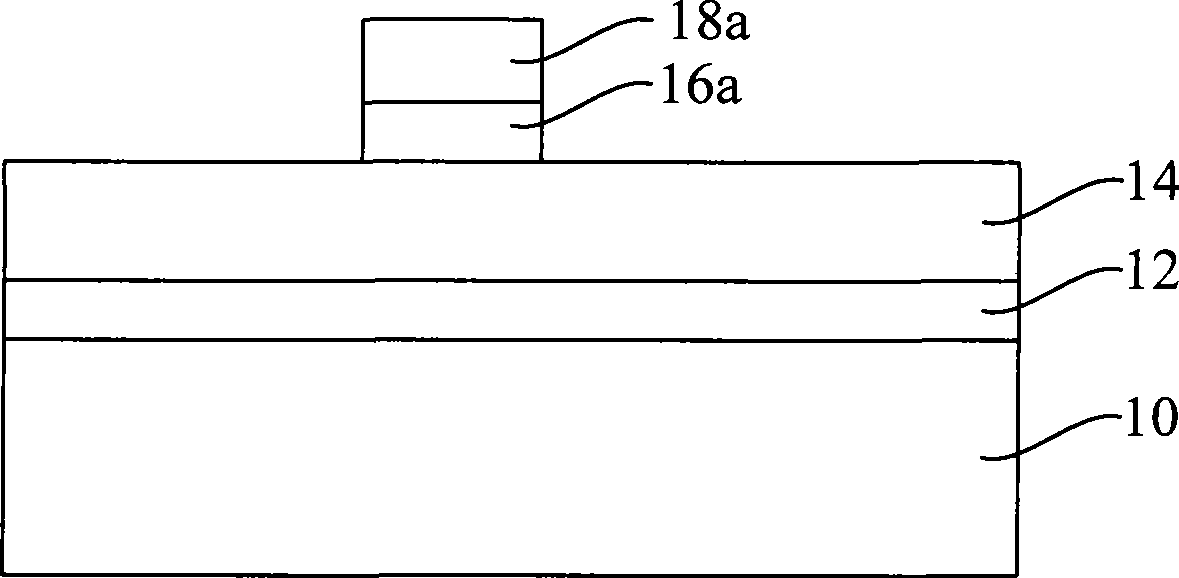

Nonvolatile memory cell employing a plurality of dielectric nanoclusters and method of fabricating the same

InactiveUS20050067651A1Avoid leakage currentMinimizing overeraseNanoinformaticsSolid-state devicesDielectricGate dielectric

A nonvolatile memory cell employing a plurality of dielectric nanoclusters and a method of fabricating the same are disclosed. In one embodiment, the nonvolatile memory cell comprises a semiconductor substrate having a channel region. A control gate is disposed above the channel region. A control gate dielectric layer is disposed between the channel region and the control gate. A plurality of dielectric nanoclusters are disposed between the channel region and the control gate dielectric layer. Each nanocluster may be separated from adjacent nanoclusters by the control gate dielectric layer. A tunnel oxide layer is disposed between the plurality of dielectric nanoclusters and the channel region. Further, a source and a drain are formed in the semiconductor substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

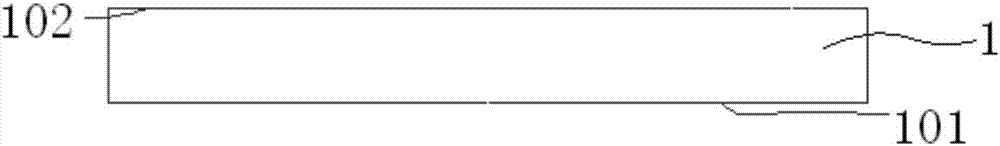

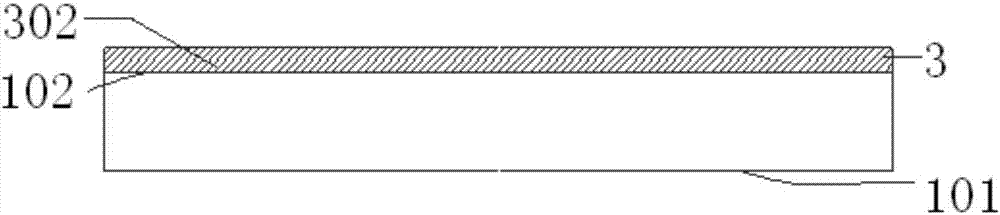

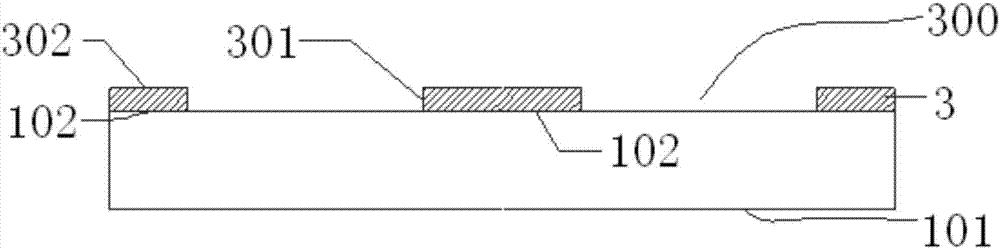

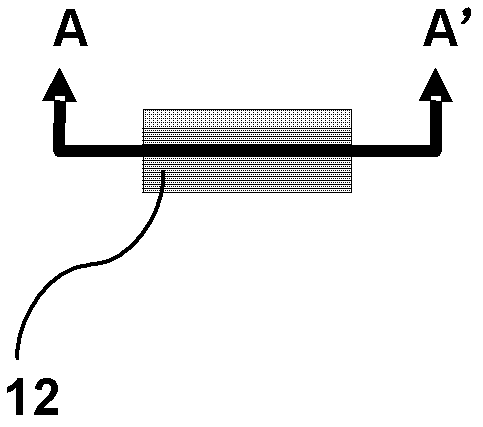

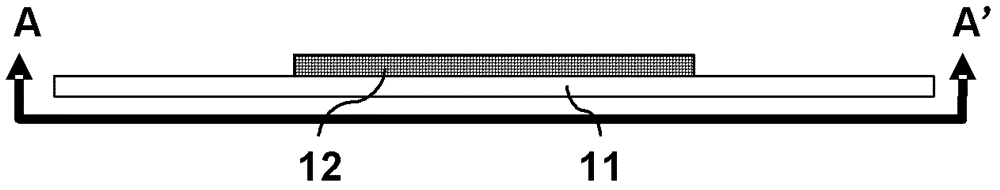

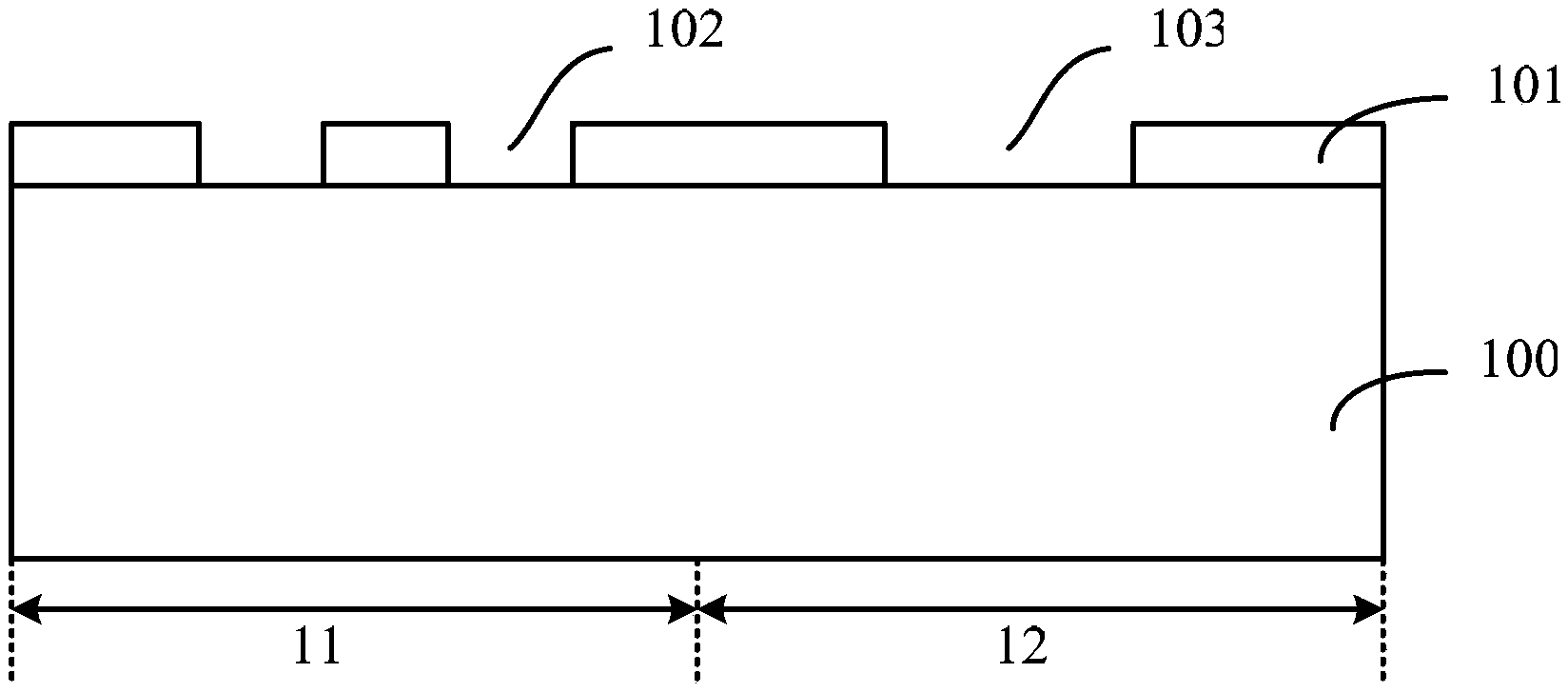

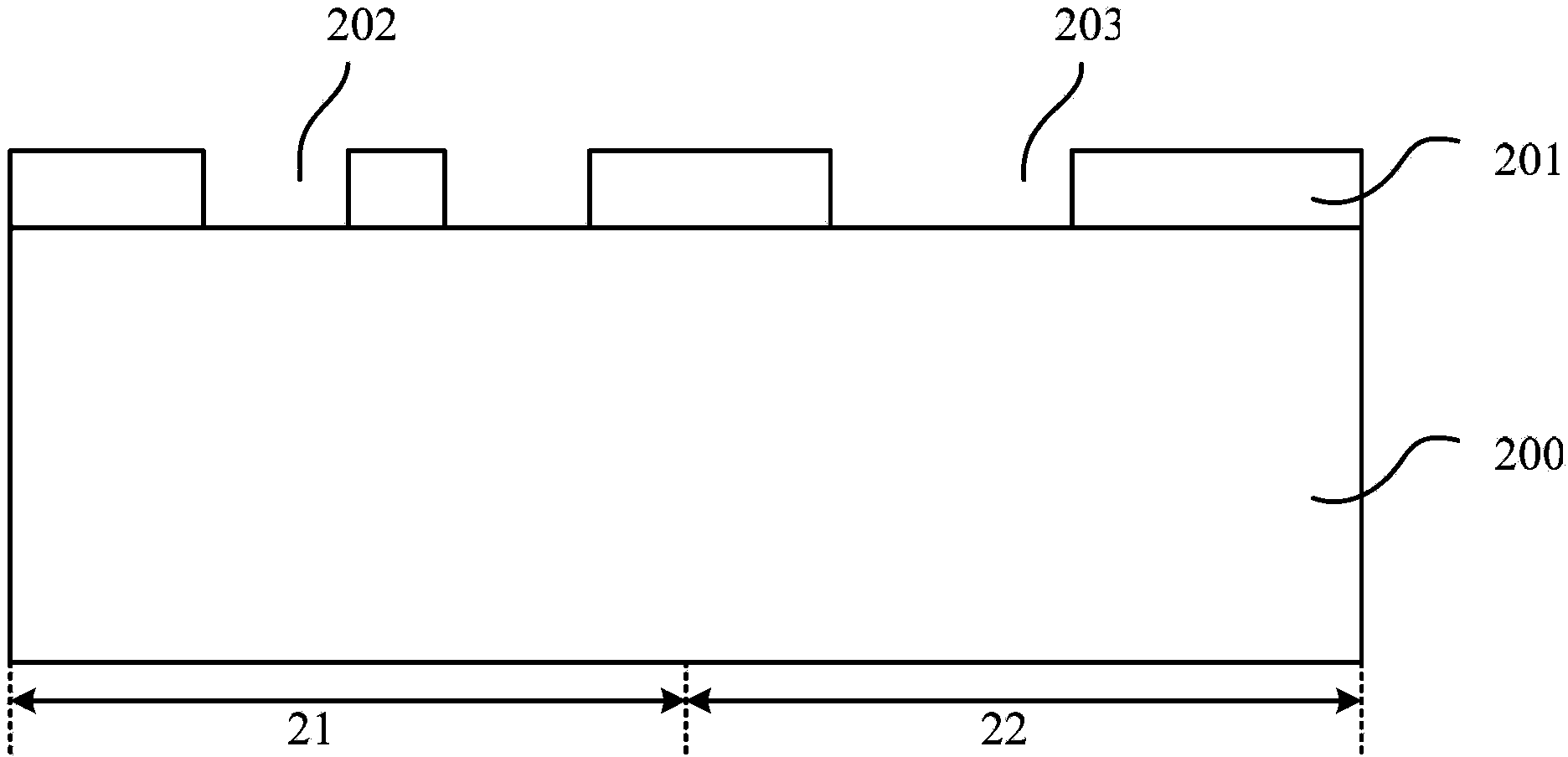

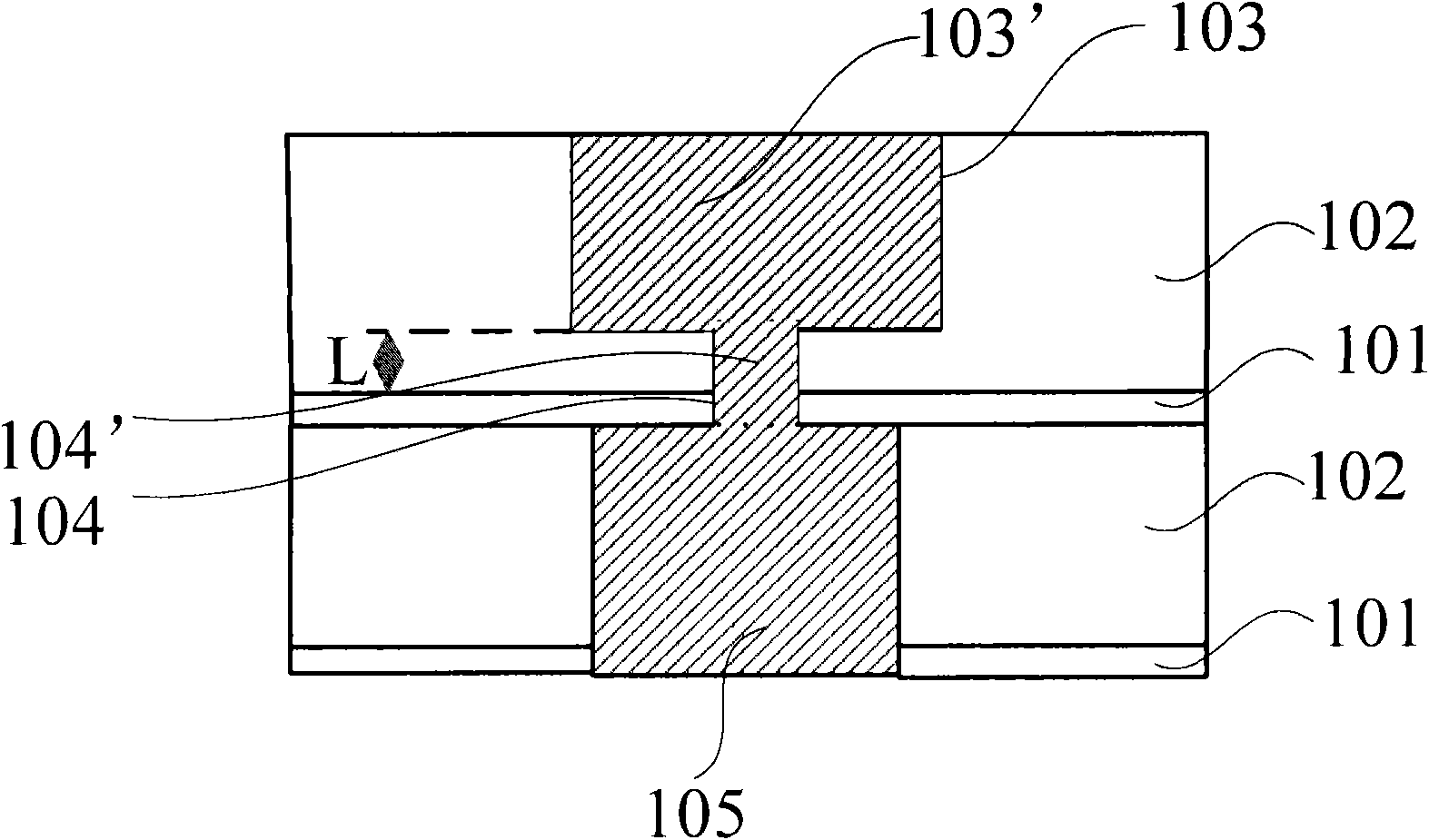

Chip embedded silicon substrate type fan-out type packaging structure and manufacturing method therefor

ActiveCN106876356AReduce warpageImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesSubstrate typeEngineering

The invention discloses a chip embedded silicon substrate type fan-out type packaging structure and a manufacturing method therefor. The packaging structure comprises a silicon substrate, wherein the silicon substrate has a first surface and a second surface; at least one groove A which extends to the second surface is formed in the first surface of the silicon substrate; at least one chip with an upward bonding pad surface is arranged in the groove A; the bonding pad surface of the chip is higher than the first surface of the silicon substrate for a certain distance; a thick adhesive layer which exposes the groove A and the chip is paved on the first surface; the sum of the thickness of the thick adhesive layer and the depth of the groove A is close to or equal to the thickness of the chip; and the electric power of the bonding pad of the chip is fan out to the upward side of the thick adhesive layer through a metal wiring layer. The thick adhesive layer is introduced to the surface of the silicon substrate, and the thick adhesive layer and the silicon substrate are jointly used as a chip fan-out carrier, so that requirement on the groove etching depth and the groove bottom etching uniformity in embedding the chip in the silicon substrate can be lowered, and the purposes of shortening etching process time on the silicon substrate, lowering etching and packaging costs and reducing warping degree are achieved.

Owner:HUATIAN TECH KUNSHAN ELECTRONICS

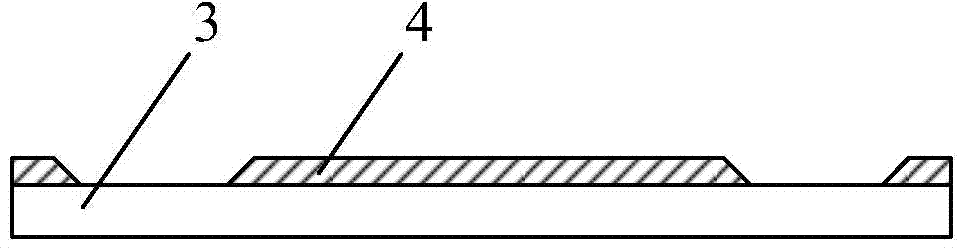

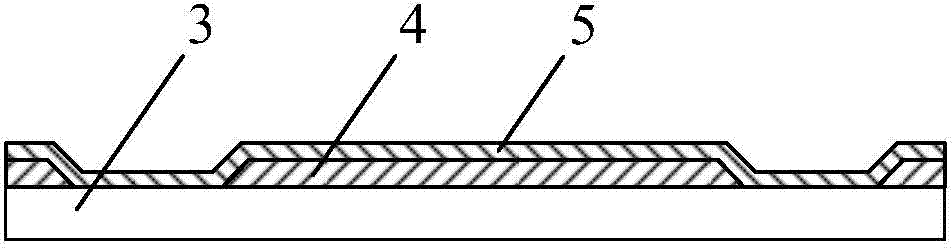

Sandwich structure pre-lithiated negative electrode and lithium ion battery

ActiveCN110828778AImprove lithium ion conductivityReduce etchingCell electrodesSecondary cellsElectrical batteryLithium metal

The invention provides a sandwich structure pre-lithiated negative electrode, which comprises a negative electrode current collector; a negative electrode active layer is arranged above the negative electrode current collector, and a sandwich structure is arranged above the negative electrode active layer; the sandwich structure comprises a first-stage protective layer, a lithium-containing metallayer and a second-stage protective layer; the lithium-containing metal layer is located between the first-stage protective layer and the second-stage protective layer, the second-stage protective layer is located above the first-stage protective layer, and the first-stage protective layer is located on the negative electrode active layer. The sandwich structure pre-lithiation negative electrode can maintain a relatively stable state in the production process and the storage process, the potential safety hazard in the pole piece transfer and battery preparation process is reduced while the electrochemical performance of the battery is improved, the safety performance of the battery is greatly improved, and the negative electrode pre-lithiation effect is greatly improved.

Owner:复阳固态储能科技(溧阳)有限公司

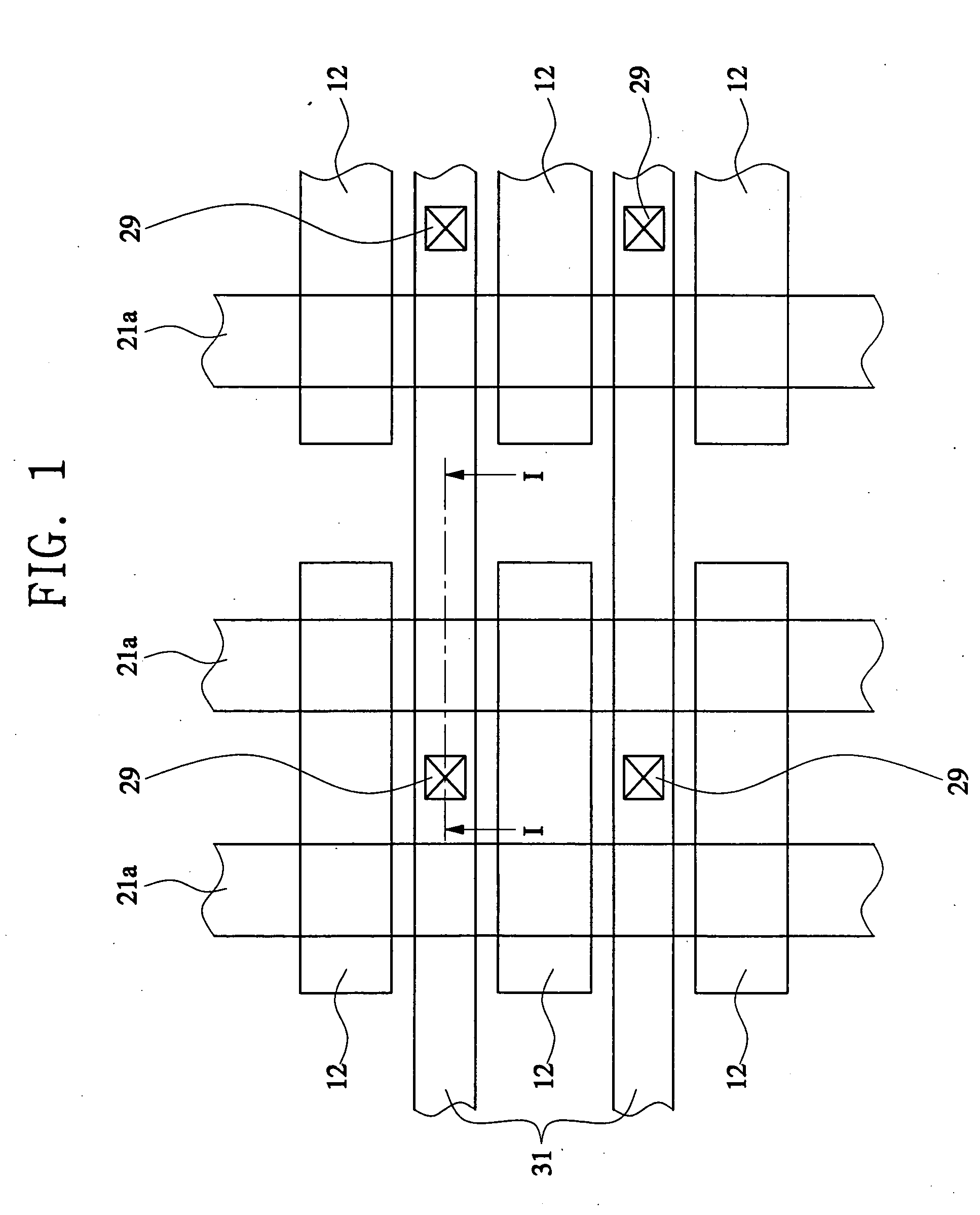

Double-patterned magneto-resistive random access memory (MRAM) for reducing magnetic tunnel junction (MTJ) pitch for increased MRAM bit cell density

ActiveUS20190214554A1Reduce sizeFacilitates MTJsMagnetic-field-controlled resistorsSolid-state devicesStatic random-access memoryRandom access memory

Double-patterned magneto-resistive random access memory (MRAM) for reducing magnetic tunnel junction (MTJ) pitch for increased MRAM bit cell density is disclosed. In one aspect, to fabricate MTJs in an MRAM array with reduced MTJ row pitch, a first patterning process is performed to provide separation areas in an MTJ layer between what will become rows of fabricated MTJs, which facilitates MTJs in a given row sharing a common bottom electrode. This reduces the etch depth and etching time needed to etch the individual MTJs in a subsequent step, can reduce lateral projections of sidewalls of the MTJs, thereby relaxing the pitch between adjacent MTJs, and may allow an initial MTJ hard mask layer to be reduced in height. A subsequent second patterning process is performed to fabricate individual MTJs. Additional separation areas are etched between free layers of adjacent MTJs in a given row to fabricate the individual MTJs.

Owner:QUALCOMM INC

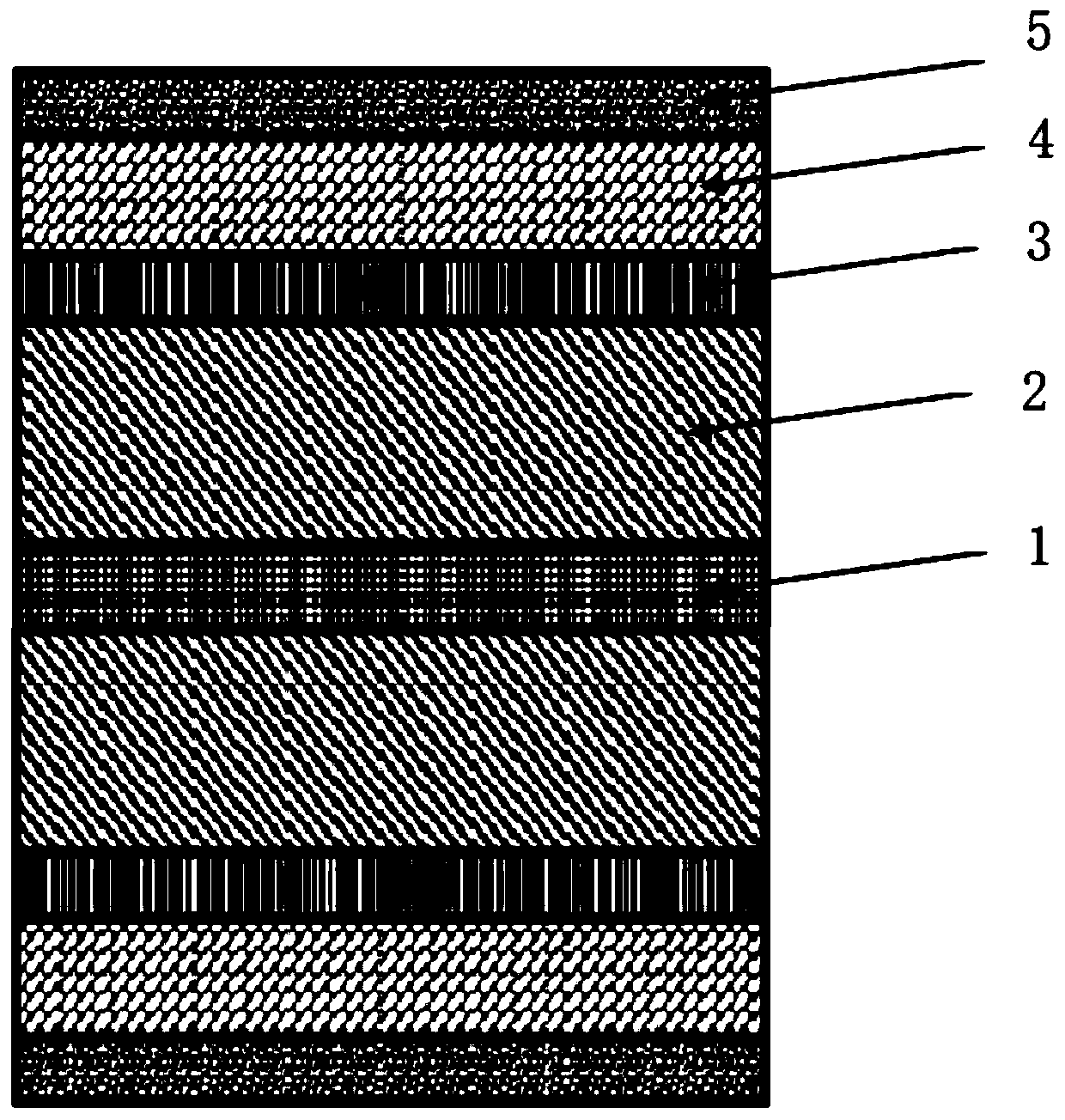

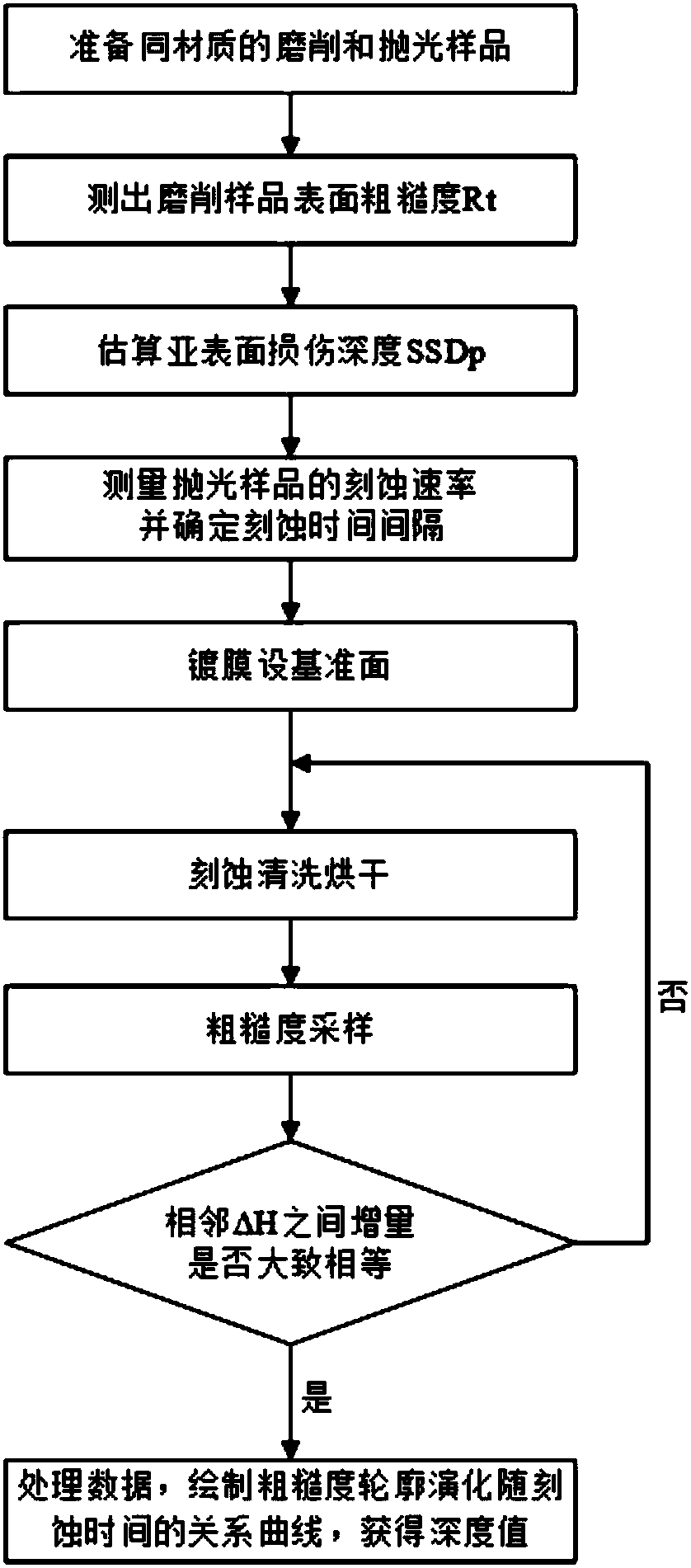

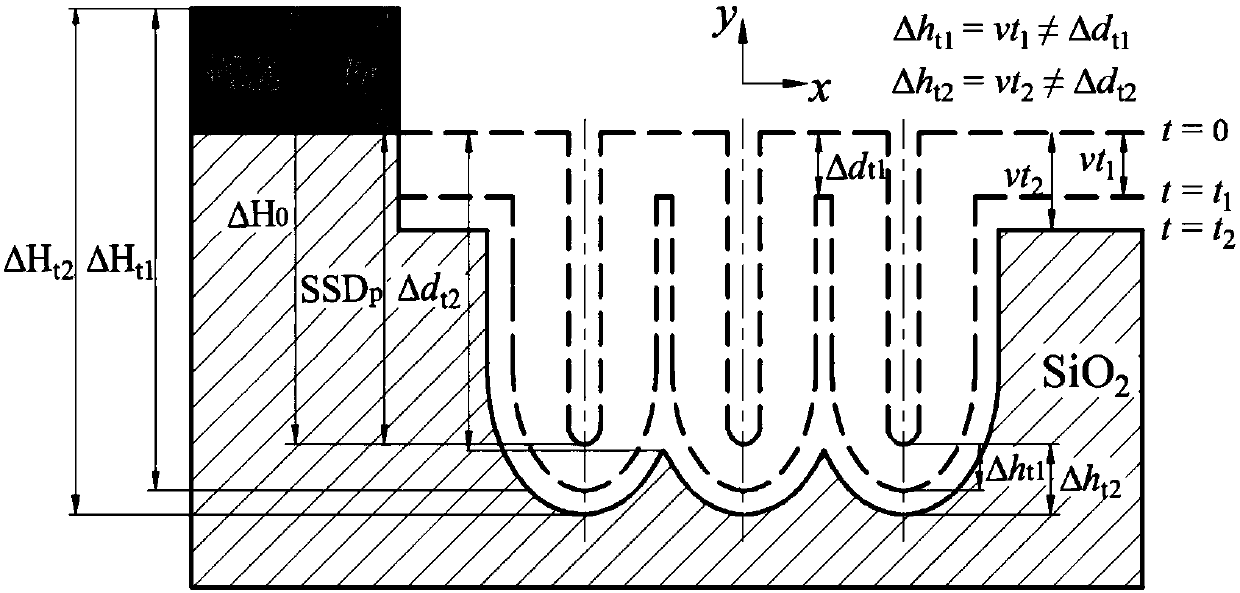

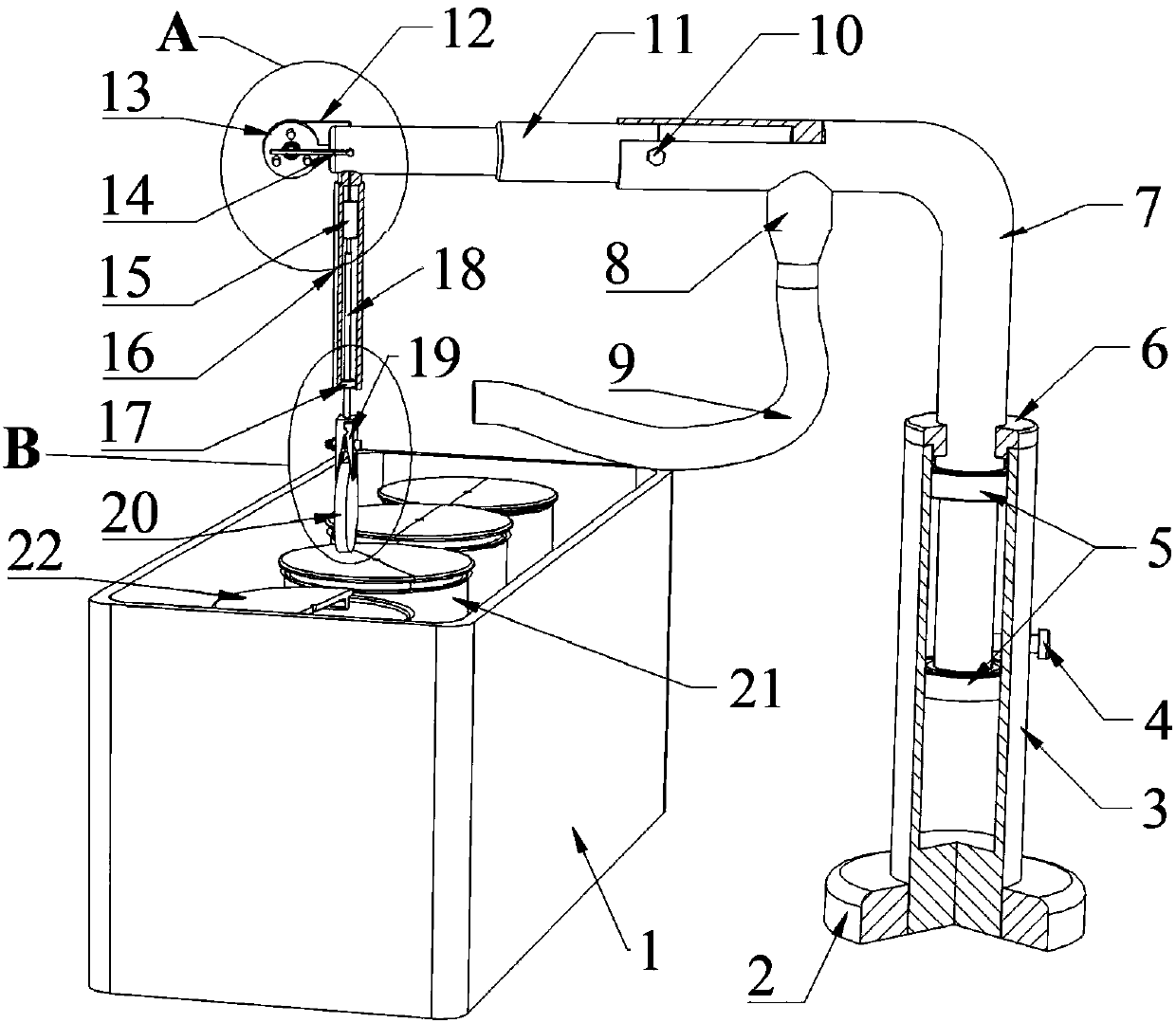

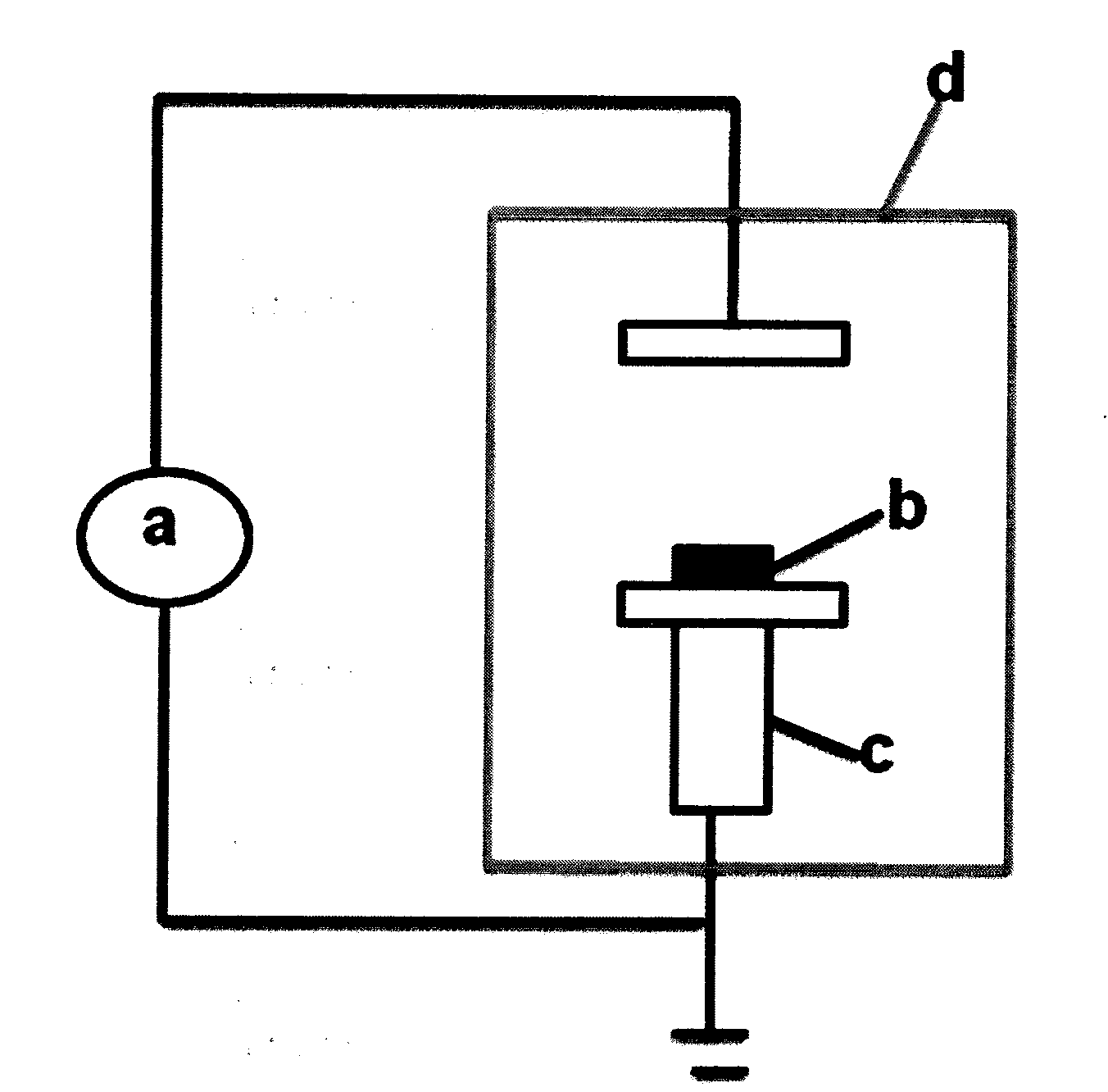

Chemical etching measurement method for optical element sub surface damages, auxiliary experiment device and test method

ActiveCN107907086AThe test result is simpleEasy to measurePreparing sample for investigationEtchingUltrasonic vibration

The invention relates to a chemical etching measurement method for optical element sub surface damages, an auxiliary experiment device and a test method. In the chemical etching measurement method, through measuring the roughness of a sample during the etching process, an evolutional relation curve for roughness outlines along with the etching time is drawn, and a sub surface damage depth value isthus obtained. The chemical etching auxiliary device is used to realize etching, cleaning and drying on the optical element, an ultrasonic vibration instrument is added during the cleaning process toassist cleaning, and a hair drier and a motor are added during the drying process to assist drying. The sub surface damage depth can be quickly and accurately measured; a set of etching auxiliary device is designed, the device is simple in operation, high in efficiency and low in danger, sediments generated during the etching process can be effectively reduced, and influences on etching and measurement are greatly reduced.

Owner:XI AN JIAOTONG UNIV

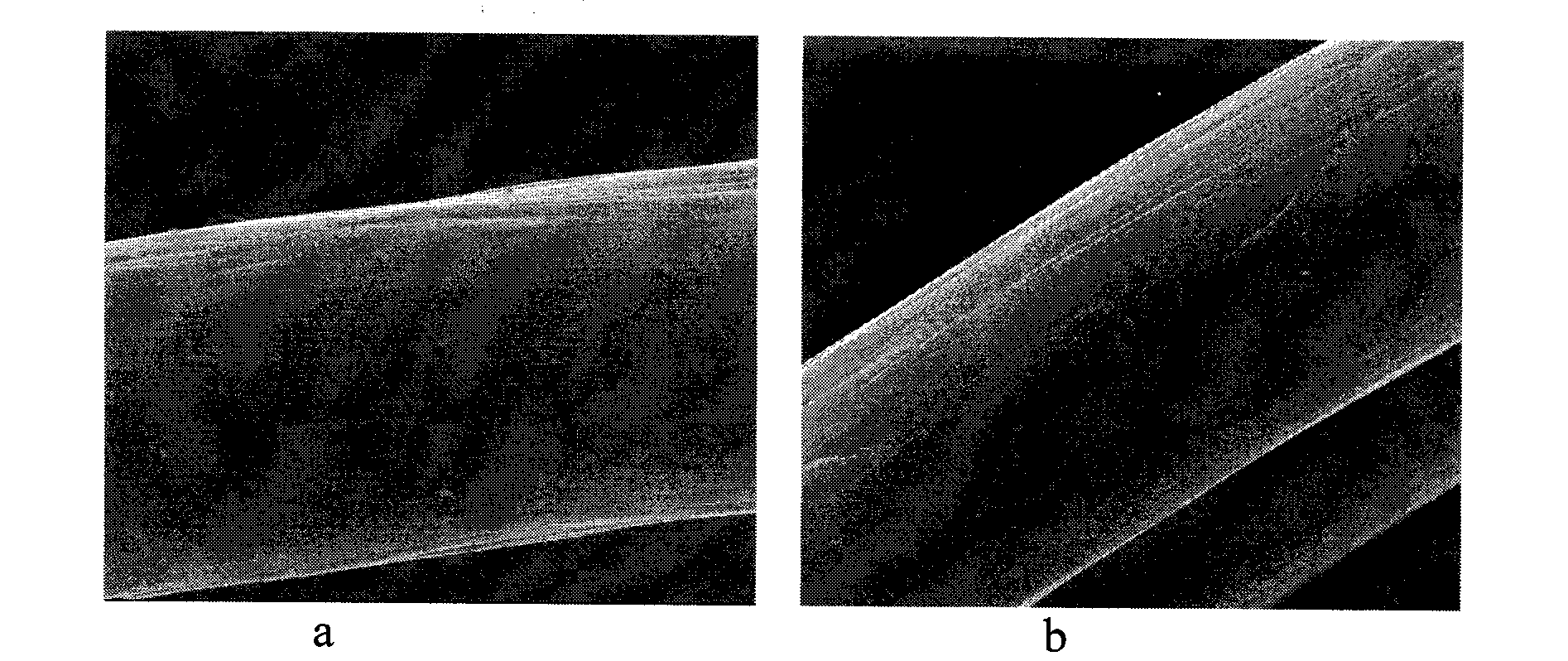

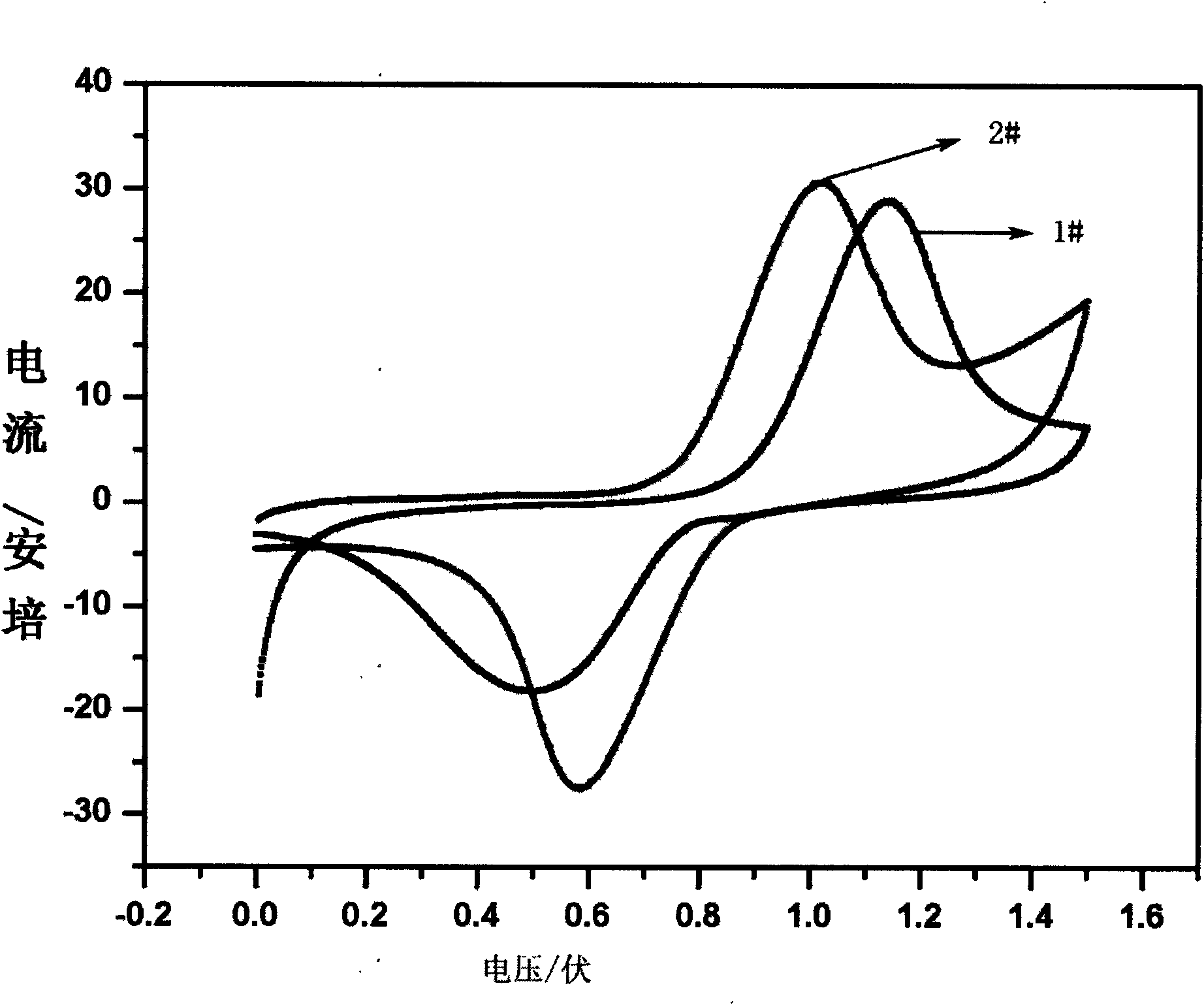

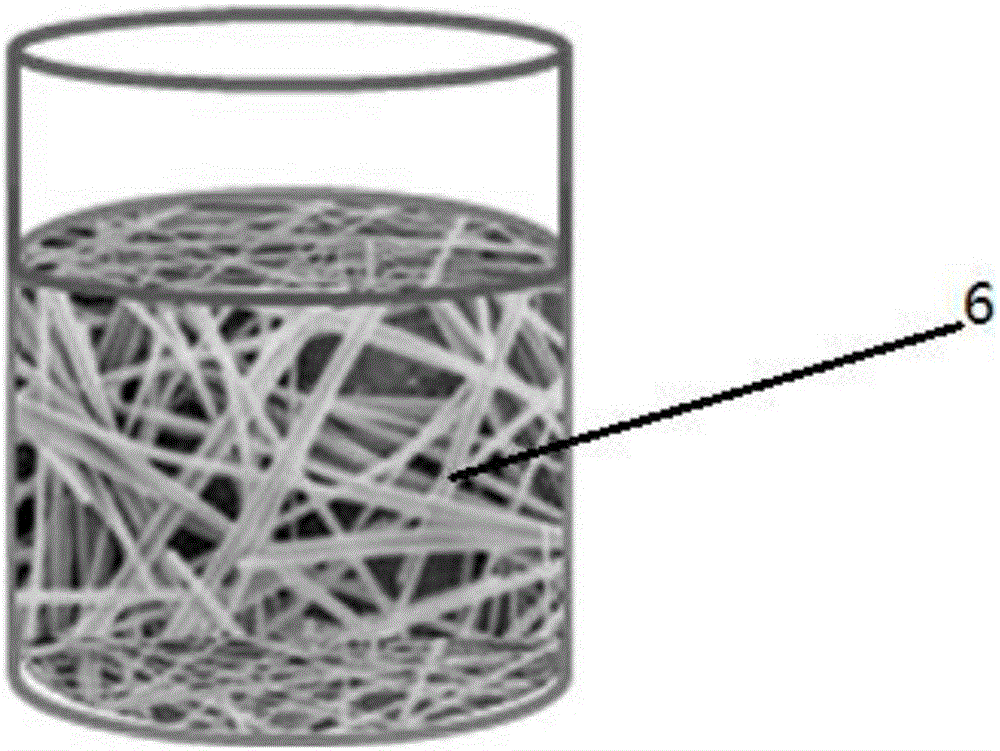

Surface modification method for raising activity of electrode material of vanadium cell

ActiveCN102723502AImprove energy storage efficiencyImprove hydrophilic propertiesCell electrodesCell fabricationElectrical polarity

The invention, relating to the field of cell manufacturing and energy storage, discloses a surface modification method for raising the activity of an electrode material of a vanadium cell, comprising the following steps: firstly cleaning the electrode material of the vanadium cell to remove surface impurities, then carrying out modification treatment of the electrode material by using plasma, reacting the gas which generates plasma with the electrode surface under ionization state to generate polar functional groups; and finally carrying out ultrasonic cleaning on the modified electrode material for 5-30 min and drying at 60-120 DEG C. According to the invention, by using the method of the invention to carry out surface modification on the electrode material of the vanadium cell, the hydrophilcity of the electrode surface is enhanced, partial polar functional groups has good catalytic influence on electrode reaction, and the energy storage efficiency of the cell is expected to increase. The method can be used for processing material surfaces with various morphologies and can keep mechanical properties and the like of material matrixes, the experiment condition are easy to control and the method has no pollution to environment. The method is efficient and environmentally friendly.

Owner:辽宁科京新材料有限公司

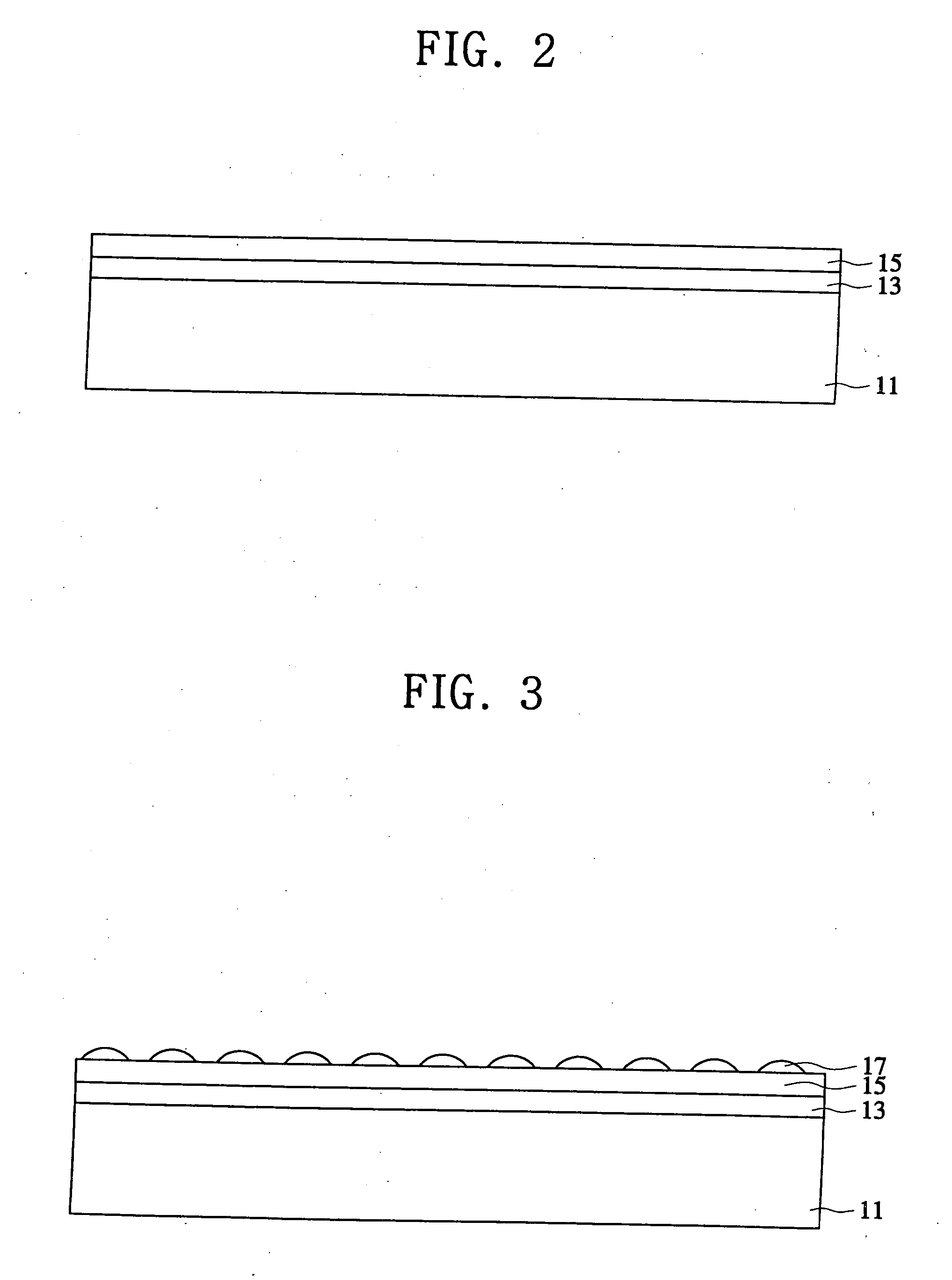

Production of inverted gallium nitride base light emitting diode chip

InactiveCN1780002AImprove antistatic performanceImprove performanceSemiconductor devicesContact layerGallium nitride

A process for preparing the reverse GaN-based LED chip includes such steps as epitaxial growth of N-type GaN contact layer, active luminescent region and P-type GaN layer on substrate, depositing insulating SiO2 or SiN layer on said P-type layer, thinning the substrate from its back, depositing insulating and isolating SiO2 or SiN layer on carrier, preparing P-type solder bosses on P-type electrode and N-type solder boss on N-type electrode, reversely soldering each chip onto carrier, and cutting for separating the LED chip units from each other.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

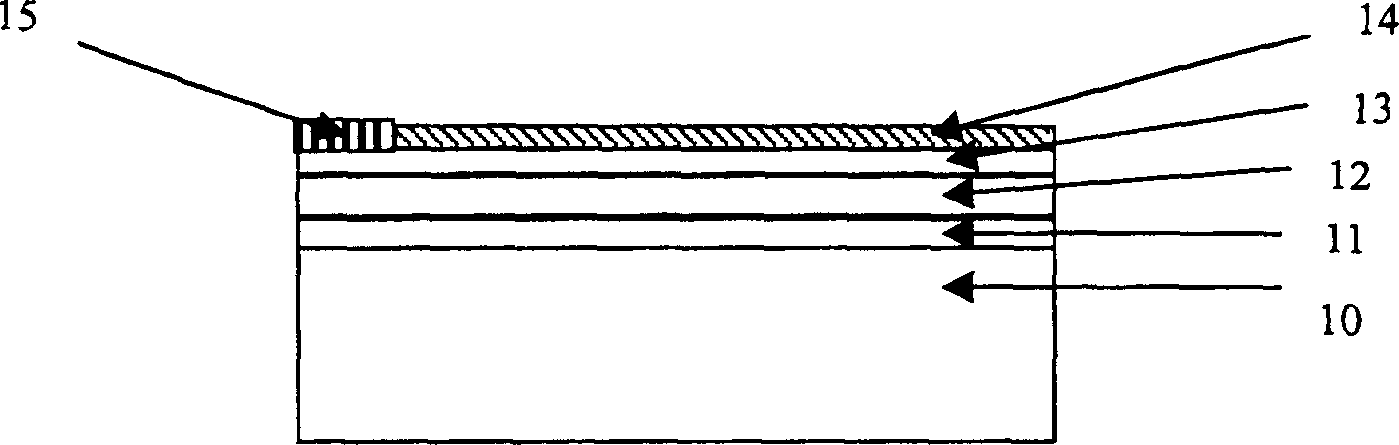

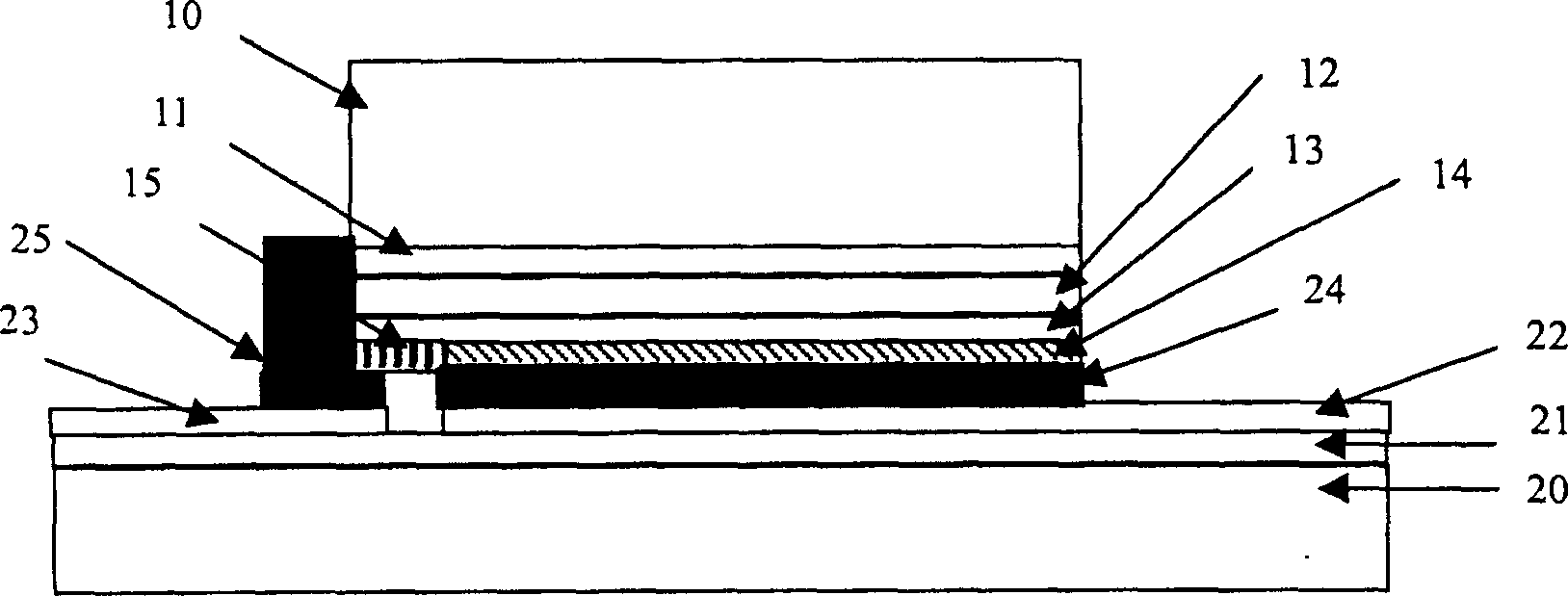

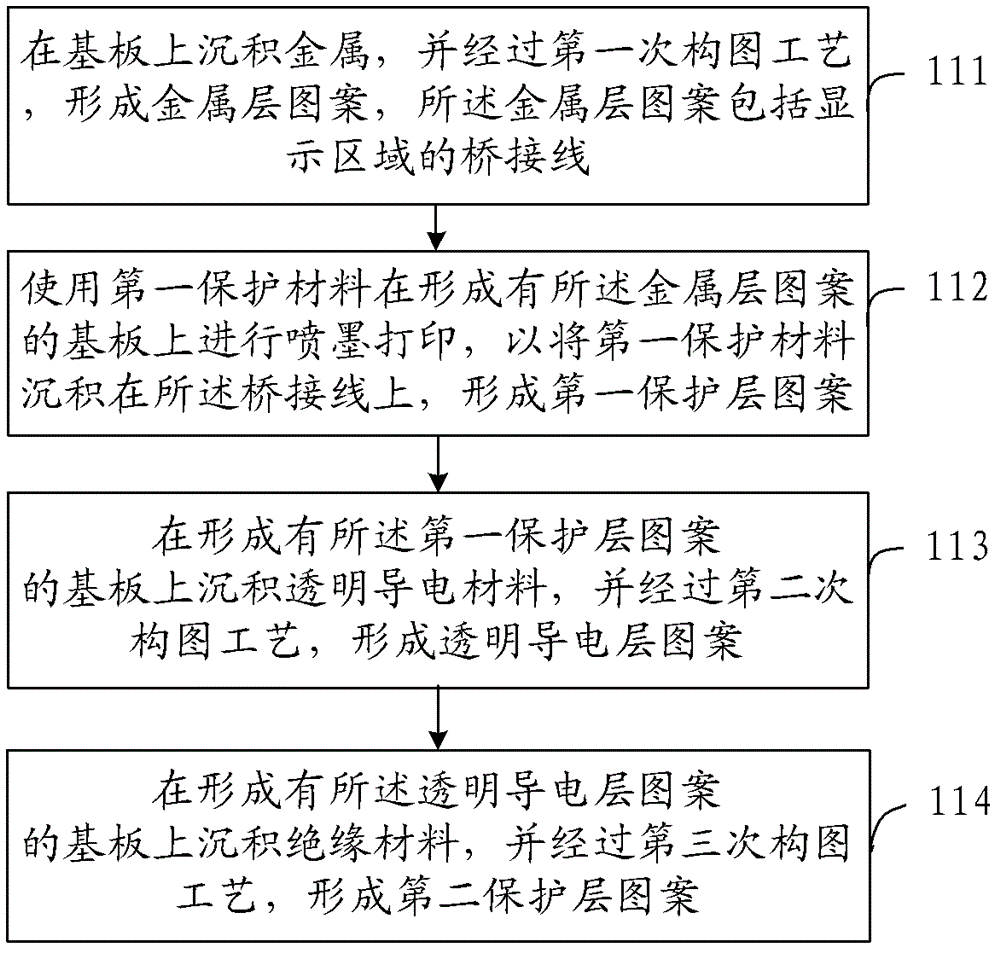

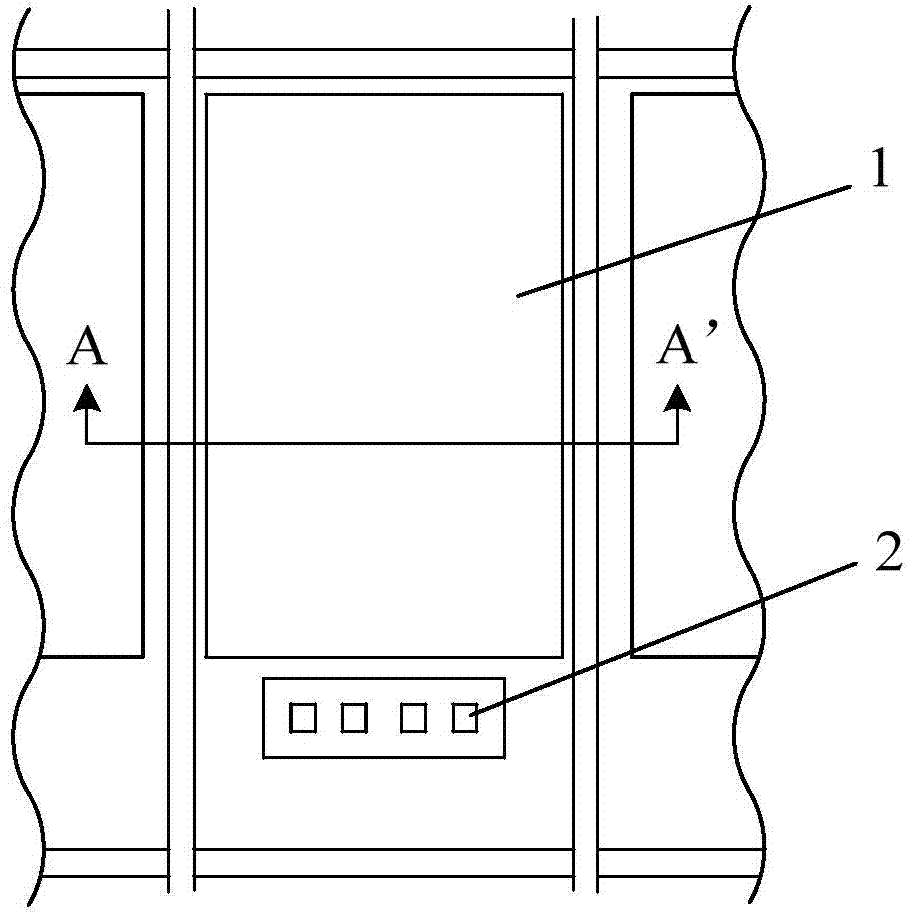

Method for manufacturing touch screen and touch screen

ActiveCN102722277AReduce exposureReduce developmentInput/output processes for data processingComposition processConductive materials

The invention provides a method for manufacturing a touch screen and the touch screen, relates to the field of display, and aims to solve the technical problem that a process for manufacturing the touch screen is complicated in the prior art. The method for manufacturing the touch screen comprises the following steps of: depositing metal on a substrate, and forming a metal layer pattern by a first composition process, wherein the metal layer pattern comprises a bridging line of a display area; performing inkjet printing on the substrate with the metal layer pattern by using a first protection material to deposit the first protection material on the bridging line so as to form a first protection layer pattern; depositing a transparent conducting material on the substrate with the first protection layer pattern, and forming a transparent conducting layer pattern by a second composition process; and depositing an insulating material on the substrate with the transparent conducting layer pattern, and forming a second protection layer pattern by a third composition process. By the method, the process of manufacturing the touch screen can be simplified.

Owner:BOE TECH GRP CO LTD +1

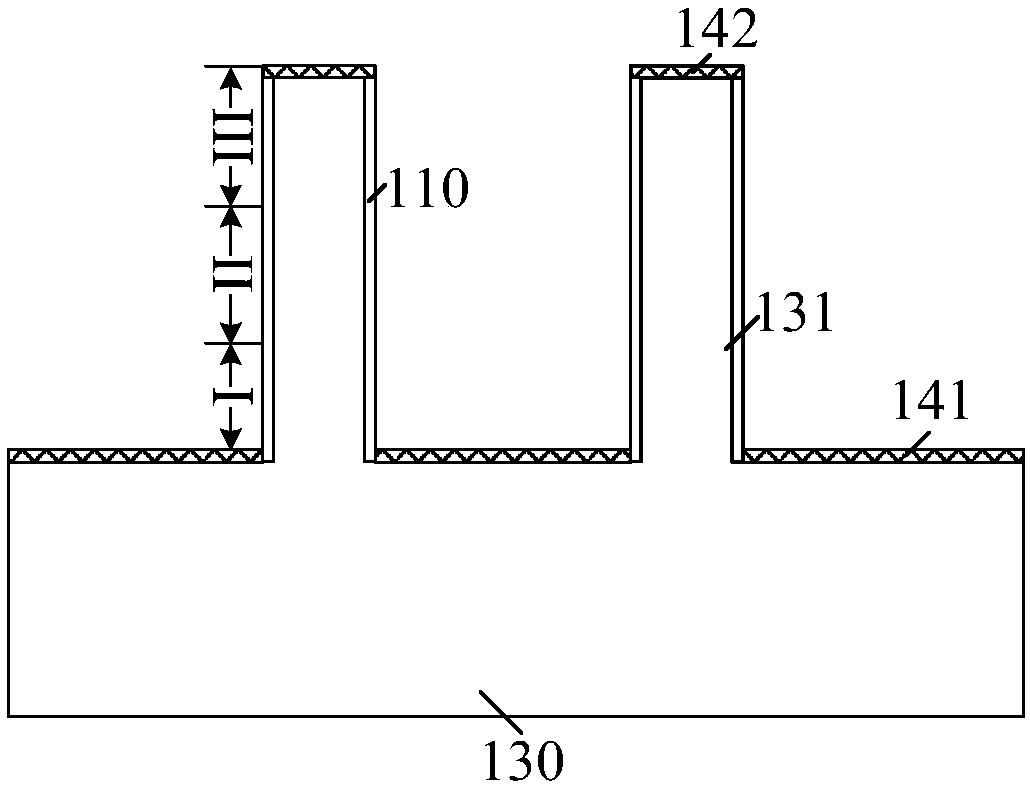

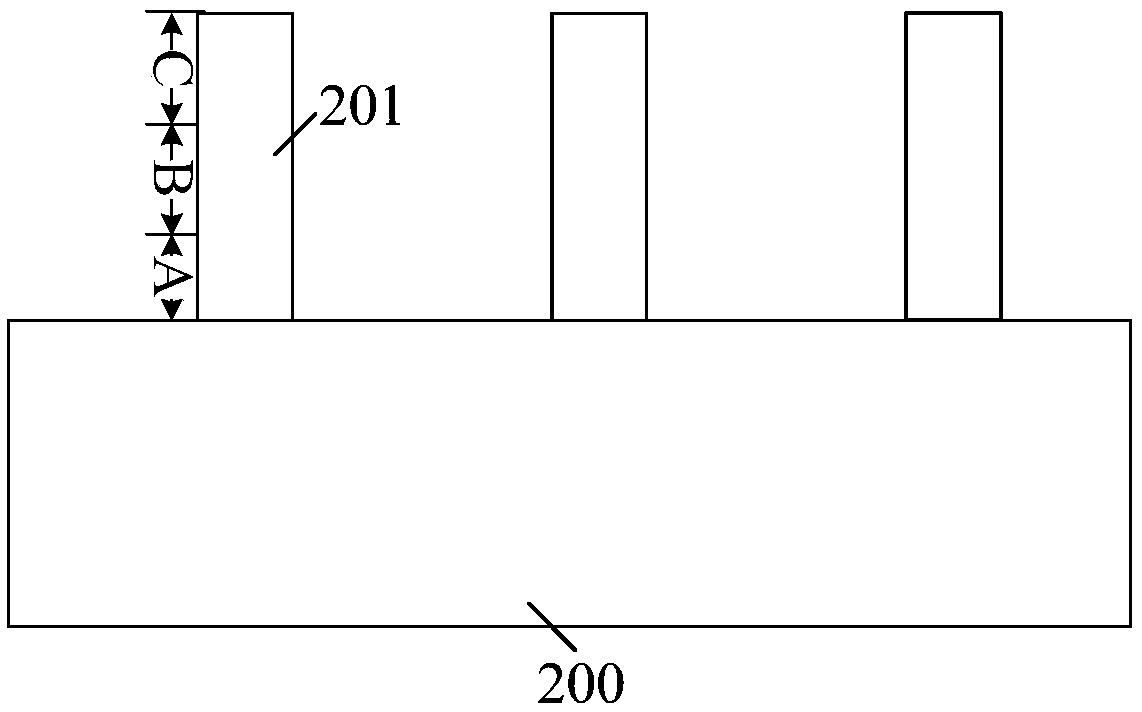

Groove forming method

ActiveCN104124194AReduce depth differenceEliminate the effects of etch loading effectsSemiconductor/solid-state device manufacturingPartial thicknessSilicon

A groove forming method comprises the steps of providing a silicon substrate which comprises a first area and a second area; performing plasma etching on the silicon substrate, wherein the plasma etching comprises the steps of performing etching of a first stage, forming a first opening and a second opening in the silicon substrate, and enabling the width of the first opening to be smaller than that of the second opening; performing oxidation of a second stage, forming a first oxidation layer at the bottom and a side wall of the first opening, forming a second oxidation layer at the bottom and a side wall of the second opening; performing etching of a third stage, etching and removing the first oxidation layer and the second oxidation layer of a partial thickness; performing etching of a fourth stage, forming a third opening and a fourth opening; and repeating the steps of oxidation of the second stage, etching of the third stage and etching of the fourth stage until a plurality of first grooves are formed in the first area of the silicon substrate and a plurality of second grooves are formed in the second area of the substrate. The influence on the etching process caused by the etching load effect is effectively eliminated.

Owner:SEMICON MFG INT (SHANGHAI) CORP

OLED (organic light-emitting diode) backboard and manufacturing method for same

ActiveCN103500731AReduce depositionReduce etchingSolid-state devicesSemiconductor/solid-state device manufacturingColor filmLight-emitting diode

The invention discloses an OLED (organic light-emitting diode) backboard and a manufacturing method for the same, and relates to the technical field of display. The OLED backboard can be more simply manufactured. The manufacturing method for the OLED backboard comprises the following steps of forming a pattern comprising TFTs (thin film transistors) on a substrate; forming a passivation layer on the substrate with the pattern comprising the TFTs; forming a color film on the substrate comprising the passivation layer; forming a resin layer on the substrate comprising the color film; heavily doping the resin layer in a first area in each sub-pixel on the substrate comprising the resin layer to endow electrical conductivity to the resin layer in the first areas, wherein each first area comprises a passivation layer through hole area, a pixel electrode area and a communicating area between the passivation layer through hole area and the pixel electrode area, and the drains of the TFTs are in the passivation layer through hole areas; sequentially forming an organic luminous layer and an anode on the substrate of which the resin layer in the first areas is heavily doped.

Owner:BOE TECH GRP CO LTD

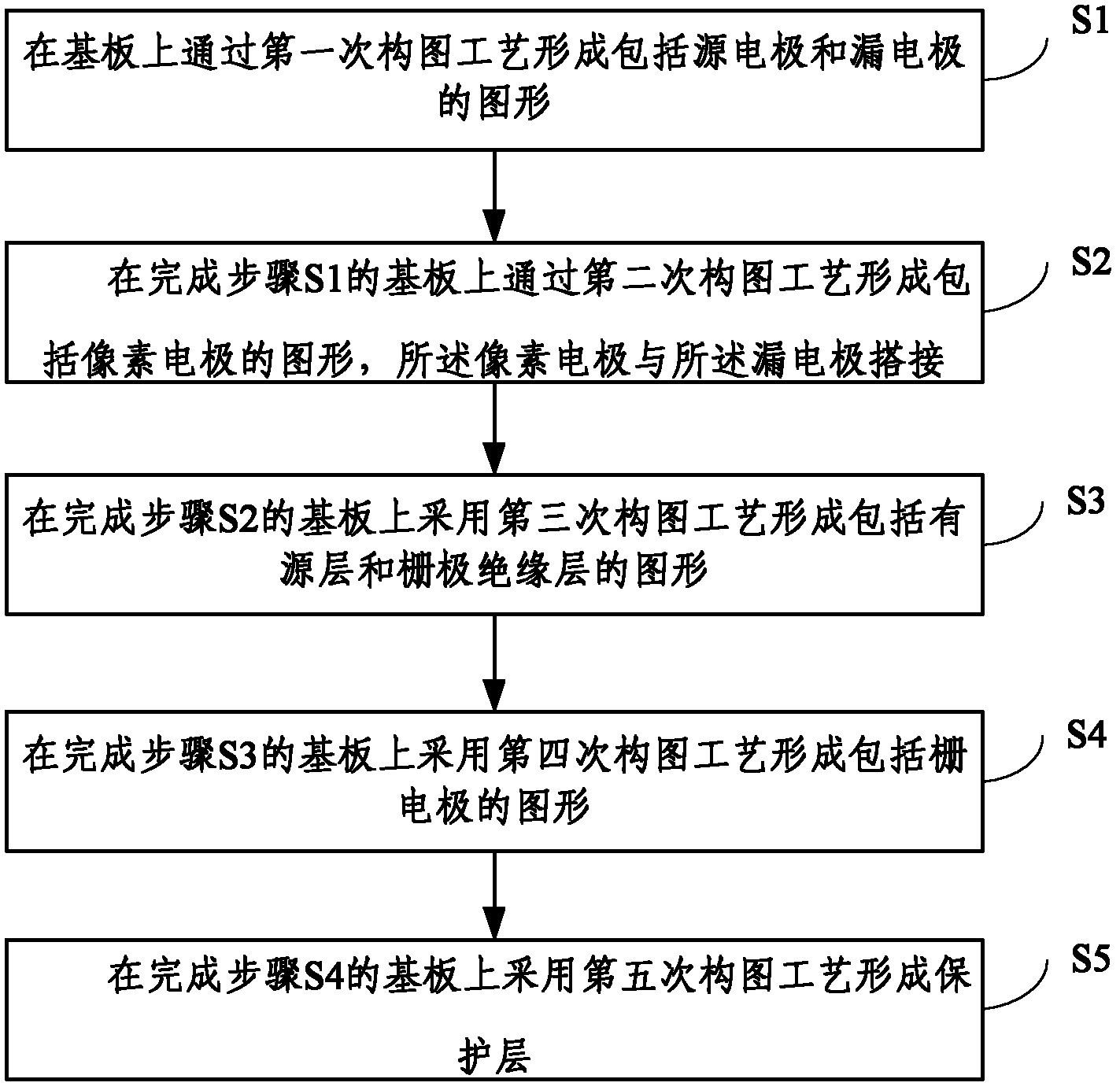

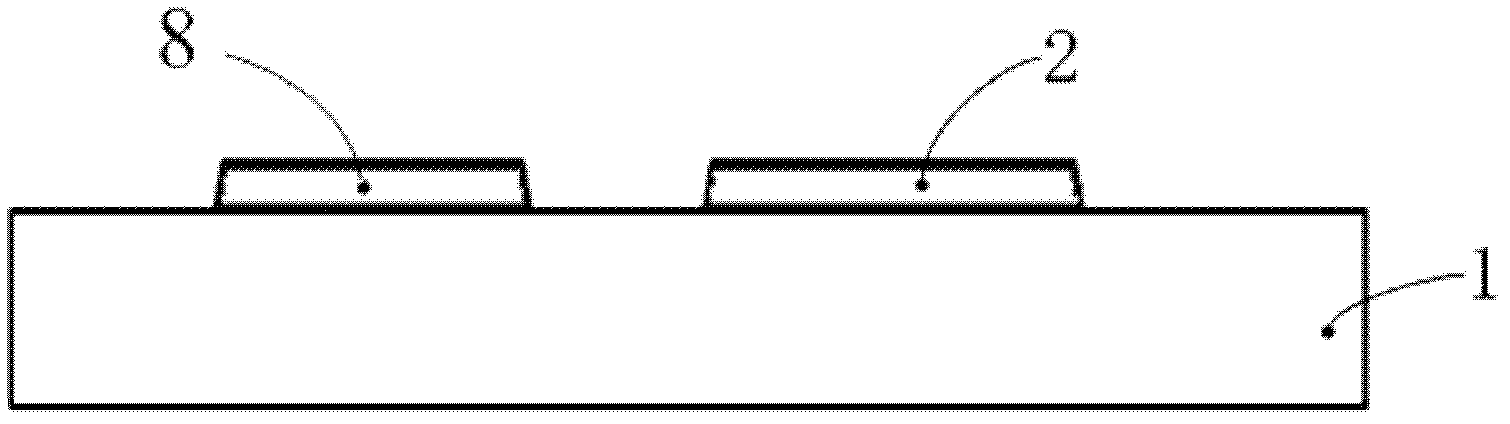

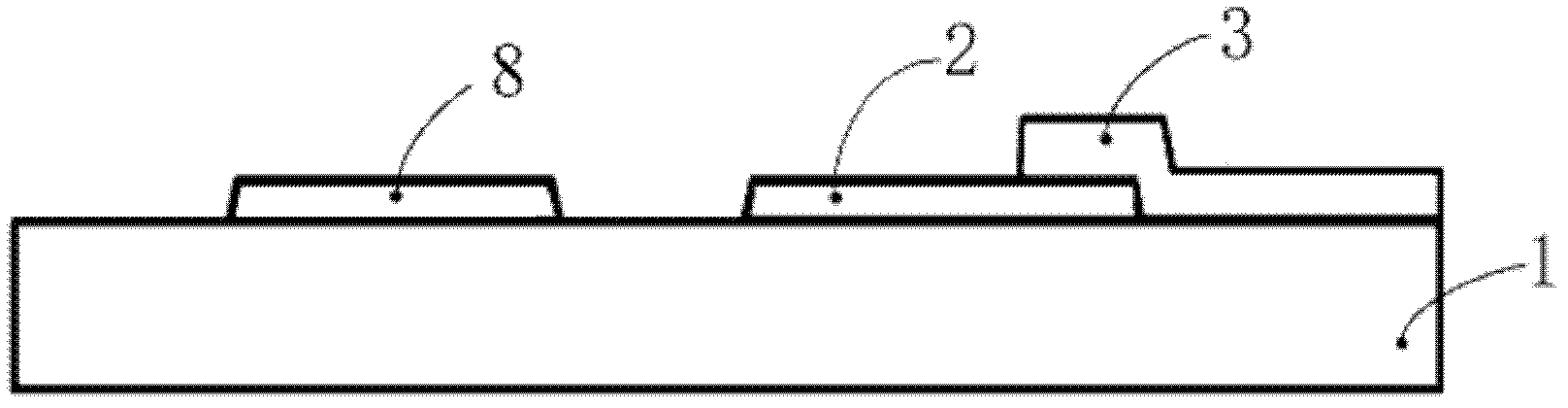

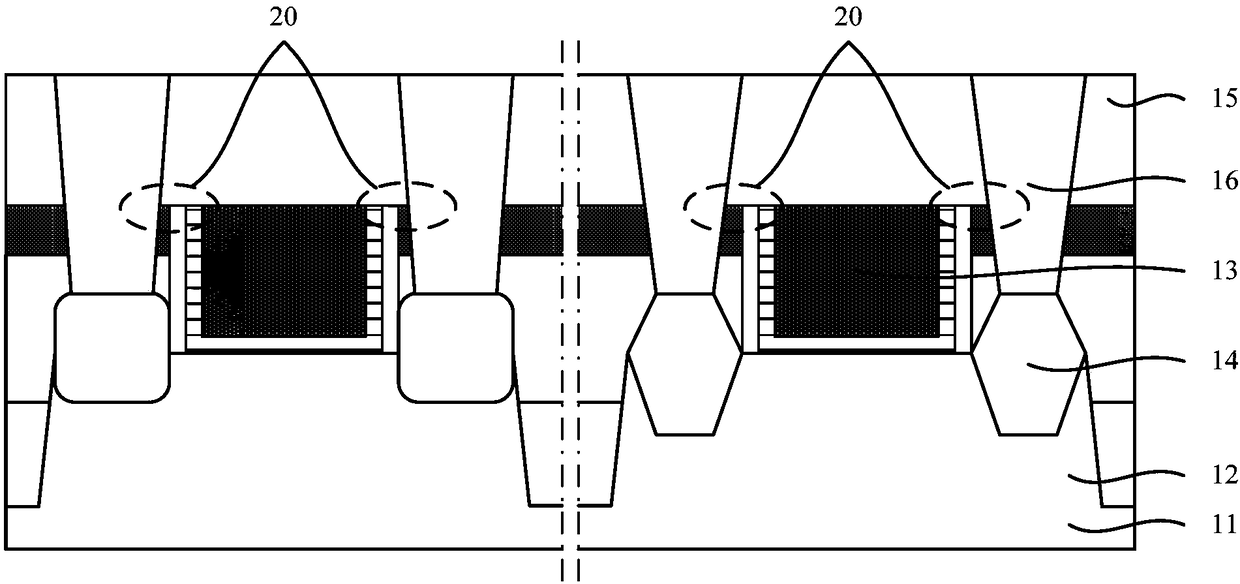

Display device, array substrate and manufacturing method thereof

ActiveCN102629611AAvoid destructionReduce etchingSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOptoelectronics

The invention relates to the technical field of display, in particular to a display device, an array substrate and a manufacturing method thereof. The array substrate comprises a substrate and a plurality of pixel units; each pixel unit comprises a thin film transistor and a pixel electrode; the thin film transistor comprises a source electrode, a drain electrode, an active layer, a grid electrode insulating layer and a grid electrode, wherein the source electrode and the drain electrode are oppositely arranged on the substrate and forms a channel of the thin film transistor; the active layer is positioned above the source / drain electrode and the channel; the grid electrode insulating layer and the grid electrode are arranged above the active layer in sequence; and the pixel electrode is positioned in an area outside the thin film transistor in the pixel unit and extends to the upper part of the drain electrode and is overlapped with the drain electrode. Through the array substrate provided by the invention, as the active layer is positioned above the source / drain electrode, the active layer can be prevented from being damaged in the forming process of the source / drain electrode. Moreover, when the active layer is made of metallic oxide, a blocking layer can be omitted, and further, the process flow is simplified, the production efficiency is improved, and the production cost is reduced.

Owner:BOE TECH GRP CO LTD

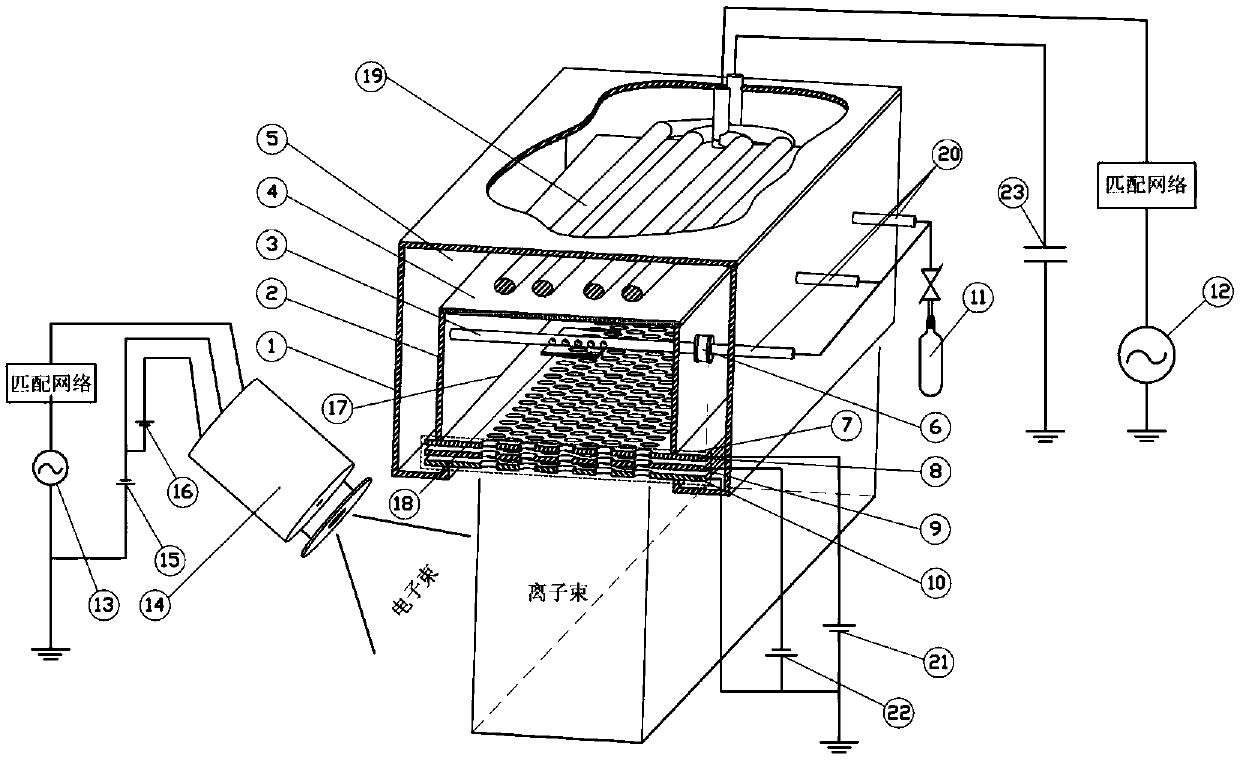

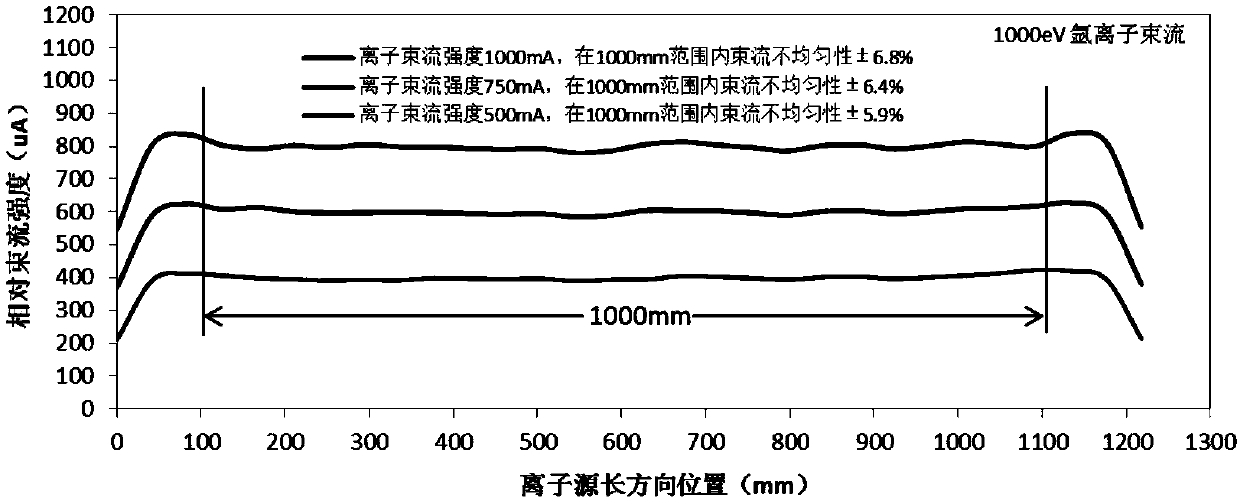

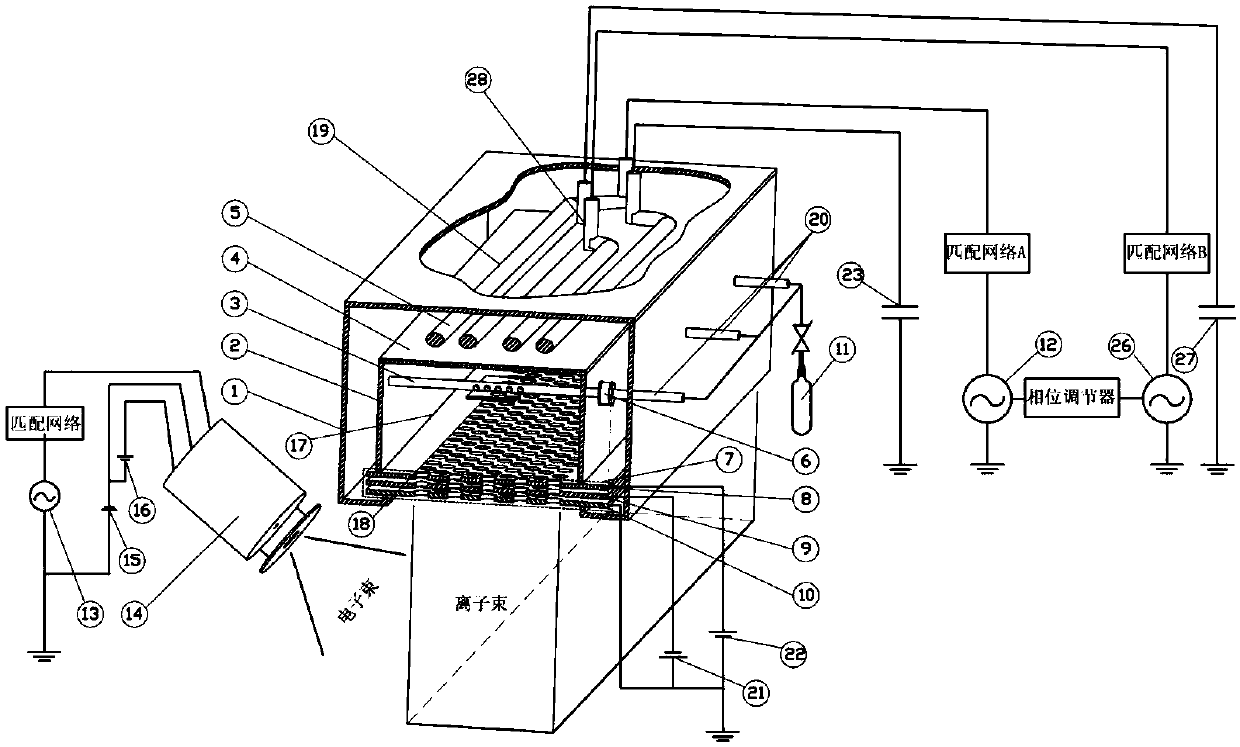

Radio-frequency inductive coupling linear ion source

PendingCN111385953AReduce thicknessReduce processing difficultyPlasma techniqueIon beamParticle physics

The invention belongs to the technical field of ion beam control, and particularly relates to a radio-frequency inductive coupling linear ion source. The radio-frequency inductive coupling linear ionsource comprises an ion source shielding shell, a radio frequency coupling antenna, a dielectric coupling window used for transmitting radio-frequency power and isolating a discharge chamber from an antenna chamber, a plasma discharge chamber side wall used for accommodating discharge plasmas, a multi-grid ion beam extraction system used for extracting ion beams from the plasma discharge chamber,and a radio-frequency neutralizer used for providing initial electrons into the discharge chamber and providing neutralized electrons into the ion beams and a base material. The radio-frequency inductive coupling linear ion source can generate high-uniformity large-area narrow and long linear ion beams in a large size range, and is suitable for processes of ion beam cleaning, etching, thin film deposition and the like of large-area base materials.

Owner:中核同创(成都)科技有限公司

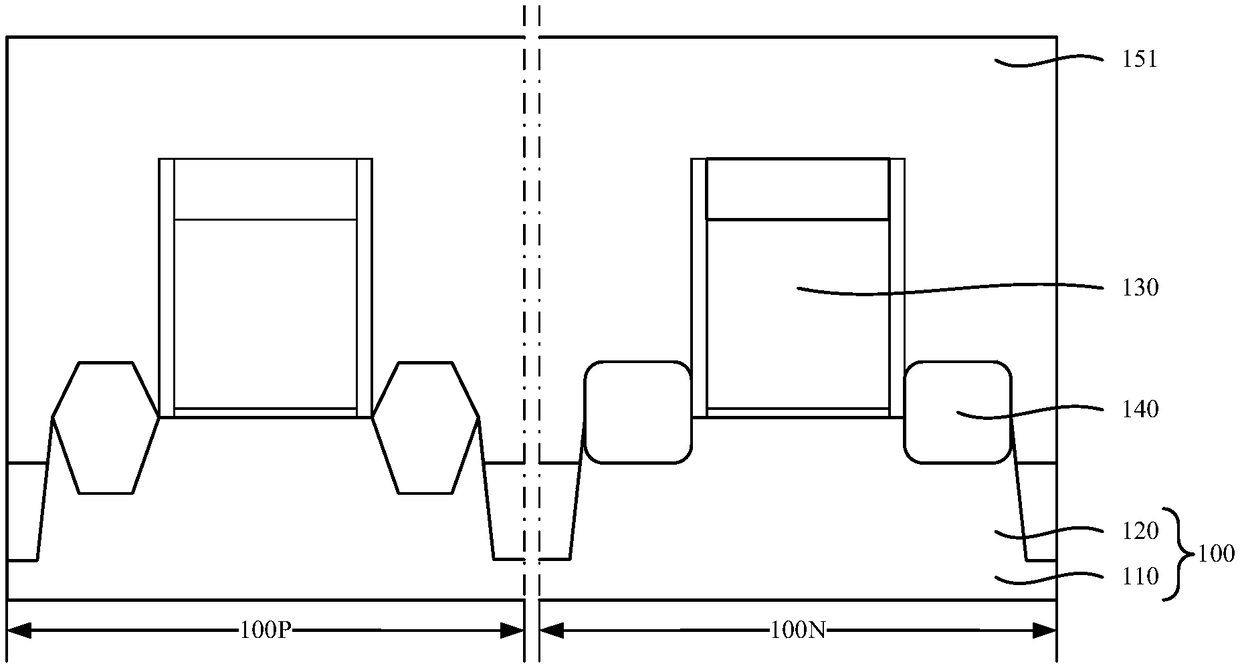

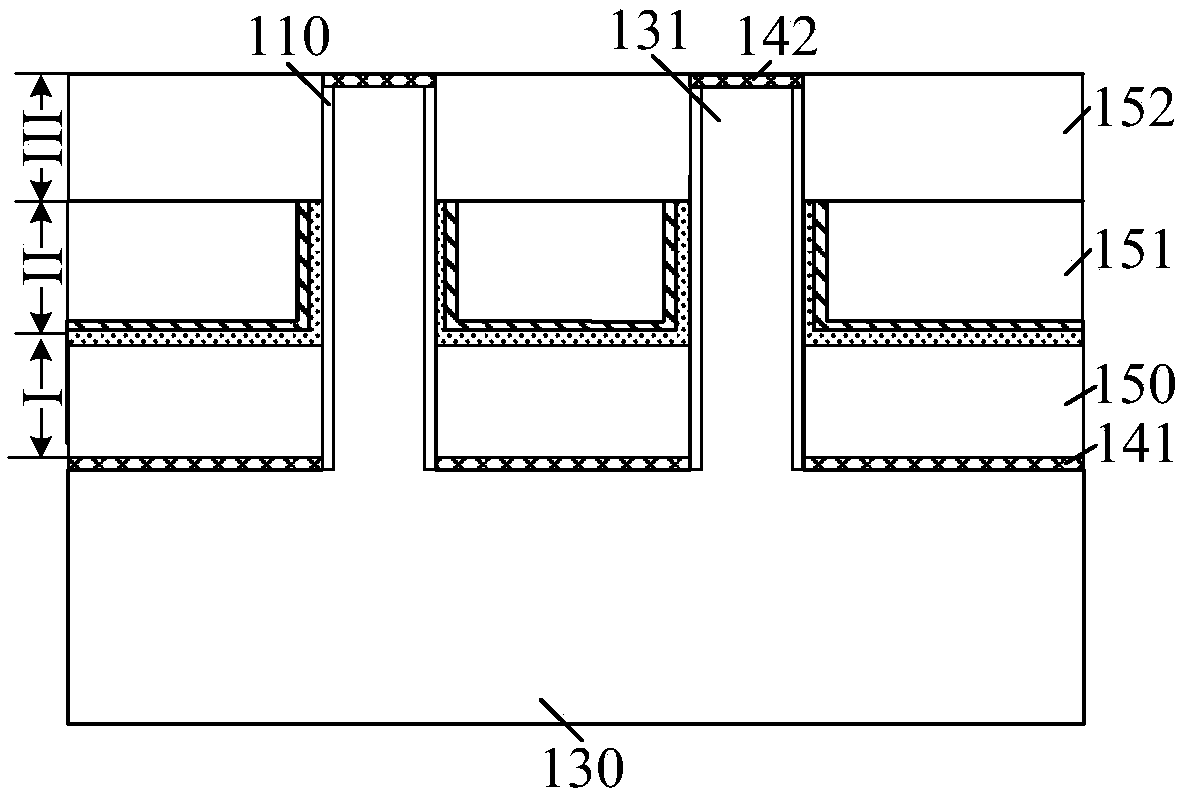

Semiconductor structure and forming method thereof

ActiveCN109148278AImprove electrical isolationImprove reliabilityTransistorSemiconductor/solid-state device detailsSemiconductor structureDielectric layer

A semiconductor structure and a forming method thereof are provided, wherein the forming method includes forming a substrate having a gate structure thereon; forming a first dielectric layer on the substrate; removing a portion of thickness of the first dielectric layer such that the top of the remaining first dielectric layer is lower than the top of the gate structure; and forming an isolation side wall is formed on the exposed side wall of the gate structure. The isolation side wall can effectively improve the electrical isolation performance between the gate structure and a plug formed subsequently, which is conducive to reducing the problem of breakdown between the gate structure and the plug, and is conducive to improving the reliability of the formed semiconductor structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

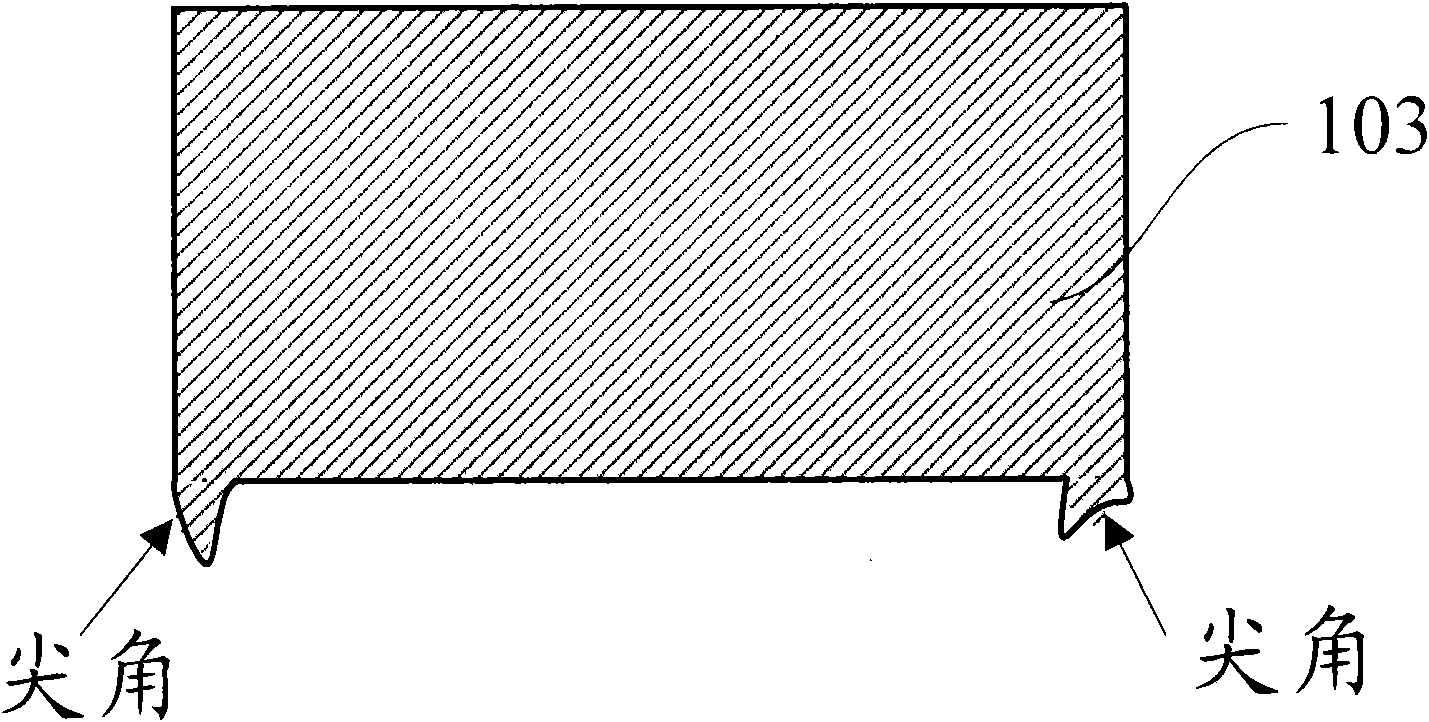

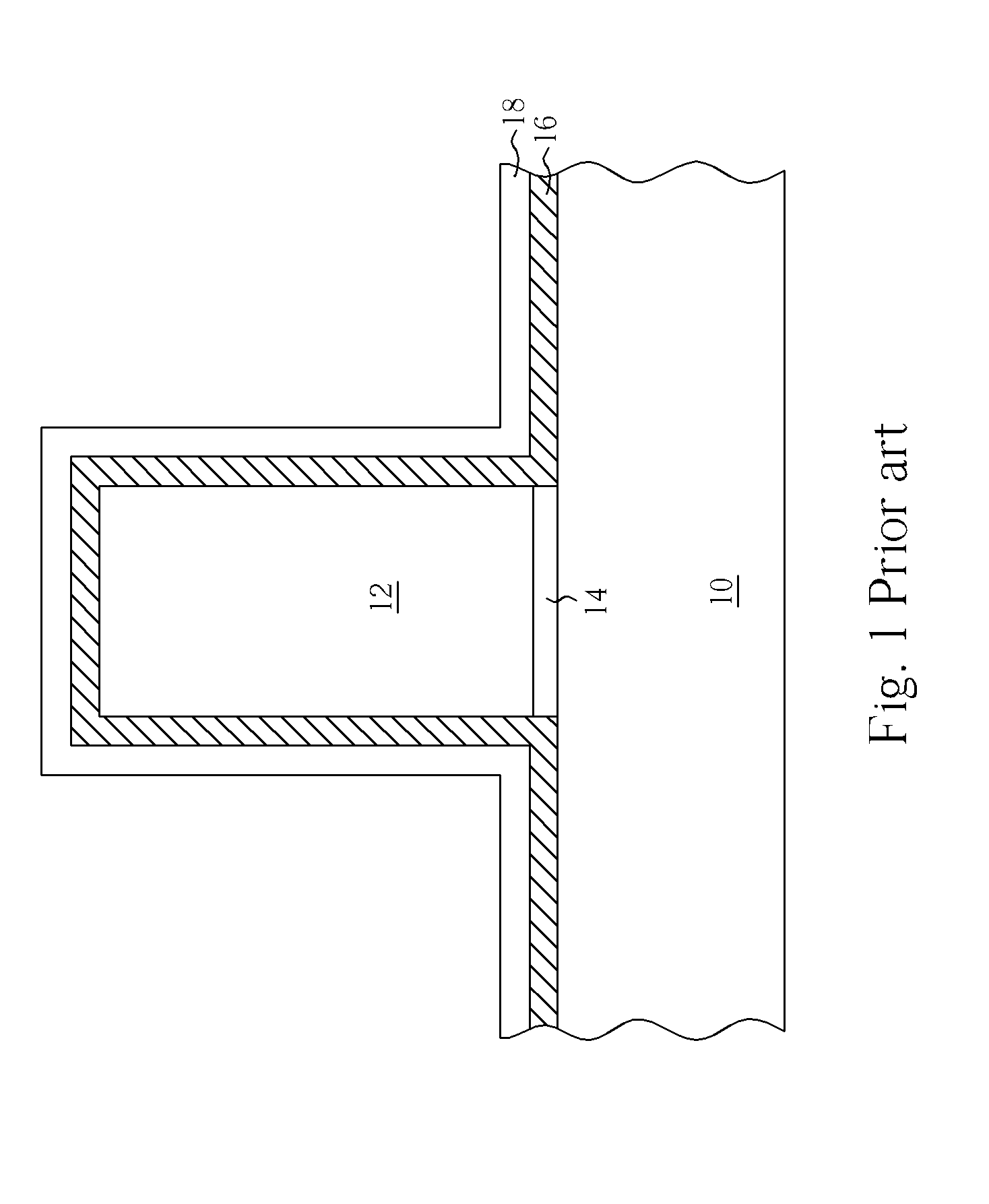

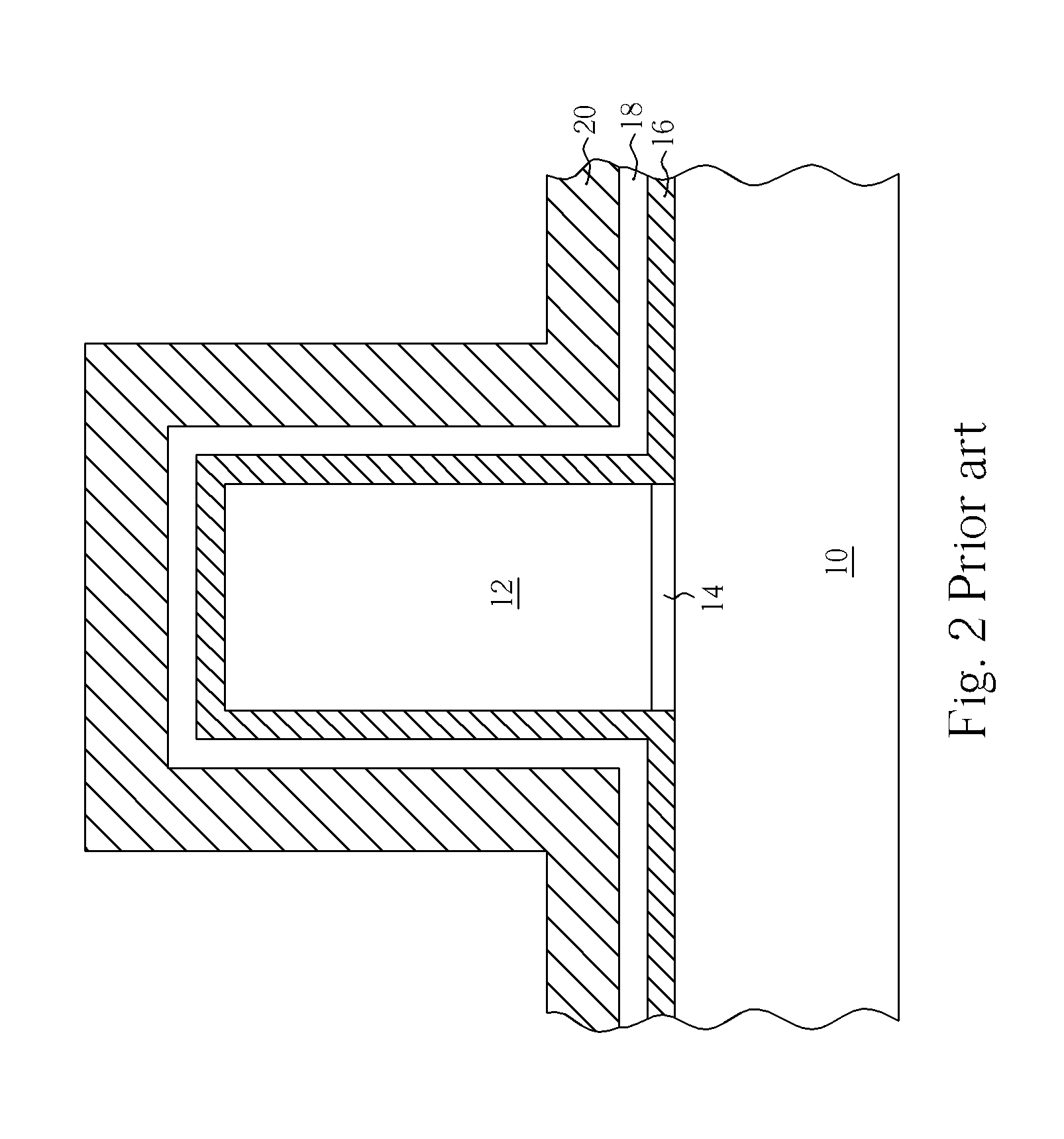

Method for manufacturing shallow groove isolation structure

InactiveCN102087989AReduce etchingSmooth chamferSemiconductor/solid-state device manufacturingEngineeringDry etching

The invention discloses a method for manufacturing a shallow groove isolation structure, which comprises: forming a hard mask of which an opening exposes from a substrate, and oxidizing the substrate in an oxygen atmosphere; and forming a shallow groove on the substrate at the position of the opening by a dry etching method after the oxidation treatment. The method for manufacturing the shallow groove isolation structure can form a relatively round shallow groove top chamber and reduce the probability of process defects.

Owner:CSMC TECH FAB1 +1

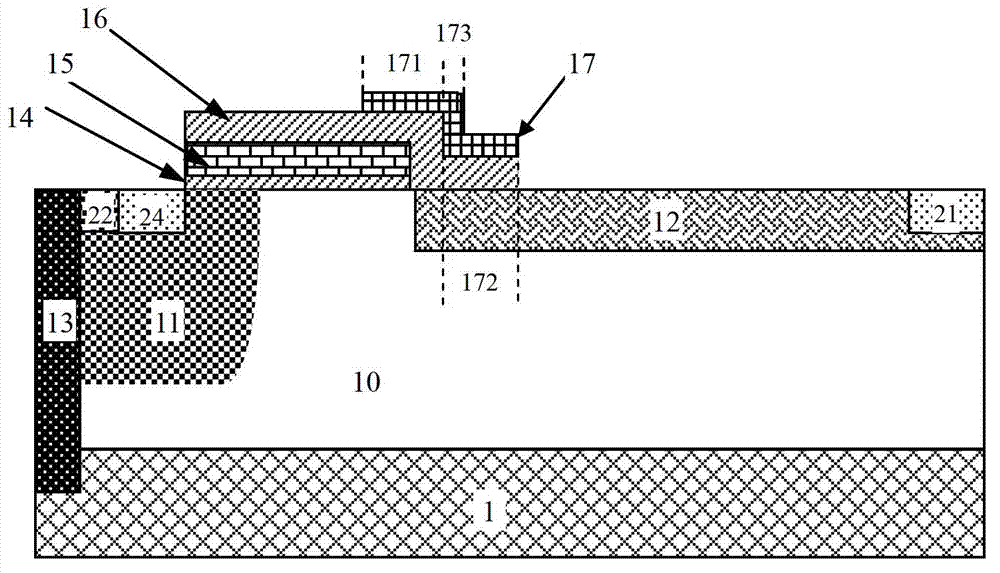

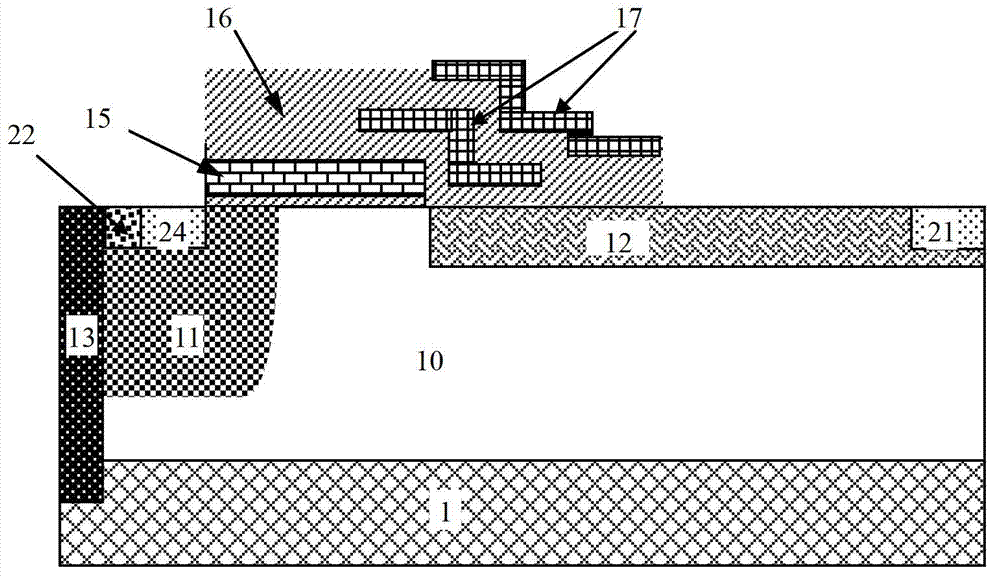

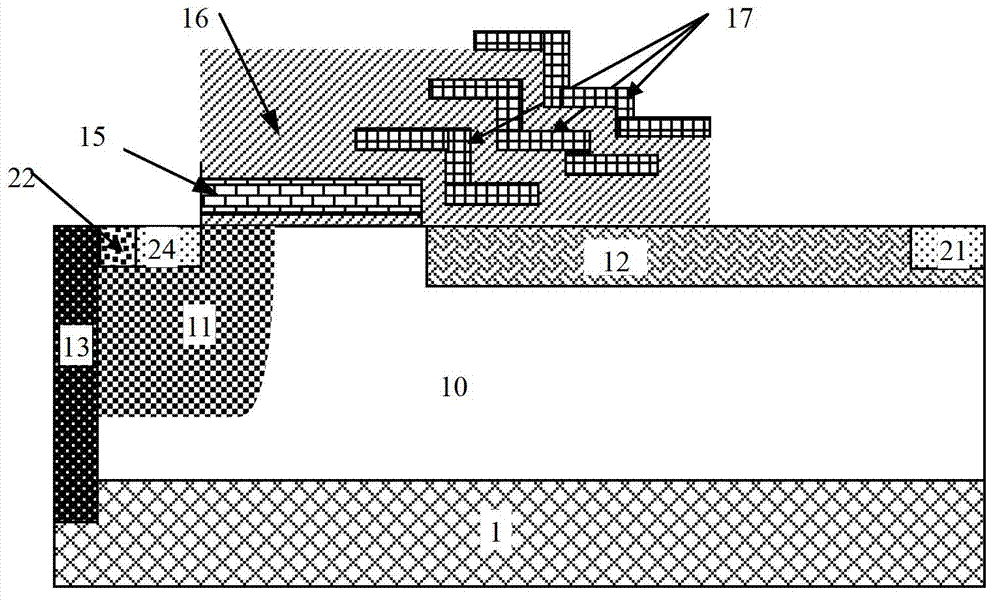

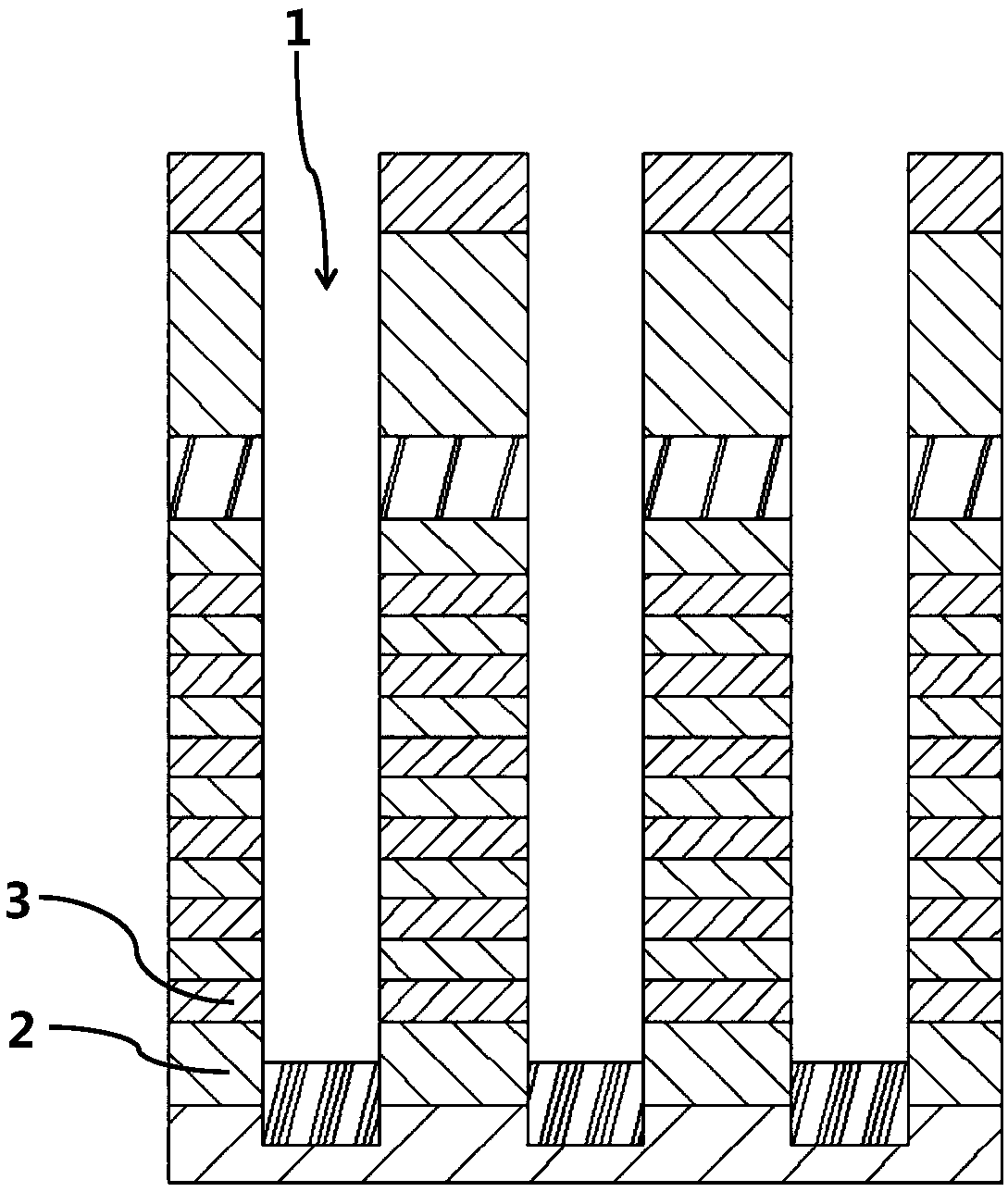

Radio frequency laterally diffused metal oxide semiconductor (LDMOS) component and manufacturing method thereof

ActiveCN103035722AImprove breakdown voltageIncrease BVSemiconductor/solid-state device manufacturingSemiconductor devicesRadio frequencyOxide semiconductor

The invention discloses a radio frequency laterally diffused metal oxide semiconductor (LDMOS) component. A faraday shield is a single metal layer. A part, above a drain terminal drift region, of the faraday shield comprises more than three vertical structures, wherein the depths of the vertical structures decrease in sequence. Arrangement of the vertical structures can play a role in lifting an electric field. Due to difference combination of the lengths of the vertical structures and difference of distances of drain terminals, the electric field below the faraday shield can be distributed more evenly, and breakdown voltage of the component is improved. Without deposition of multi-layer metal, the radio frequency LDMOS component can achieve a high breakdown voltage, a metal deposition and corrosion process during a manufacturing process of the component can be reduced, manufacturing technology of the component is simple, and technology cost of the component is lowered. The invention further discloses a manufacturing method of the radio frequency LDMOS component.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Novel inorganic environment-friendly film-stripping liquid

InactiveCN107908084AFast peeling speedReduce etchingPhotosensitive material processingChemical compoundEtching rate

The invention discloses a novel inorganic environment-friendly film-stripping liquid, which comprises the following materials in percentages by weight: 1-10% of an inorganic alkali compound, 0.01-5% of an azole compound, 1-5% of a tin-protecting deoxidizer, 0.05-1% of a film-stripping accelerator and the balance of water. Through the ratios of the materials, the novel inorganic environment-friendly film-stripping liquid is capable of quickly stripping a dry film of an anti-corrosion layer on a circuit board subjected to pattern plating, the etching rate on copper and tin is extremely low, anda waste liquid generated after film stripping through the novel inorganic environment-friendly film-stripping liquid is low in COD value and complexing capability, so that the treatment difficulty ofthe waste liquid can be effectively reduced and the easy-to-treat and easy-to-discharge standards are achieved.

Owner:DONGGUAN GUANGHUA CHEM

Process of improving the plugging of oxide recess through a contact hole

ActiveCN107731741AReduce etchingImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingAtomic layer depositionSilicon

The invention provides a process of improving the plugging of oxide recess through a contact hole. The wet etching (DHF+SCI) is replaced by plasma dry etching in the pre-cleaning process, and therebythe situation that the worsening of the bowing profile morphology of a channel hole caused by the excessively-fast etching of oxide layers deposed by atomic layer deposition technology (ALD) due to the fact that the wet etching rate of the ALD oxide and that of the PECVD oxide are different can be prevented. With the anisotropy characteristics of the plasma dry etching, the situation that the pre-cleaning process mainly aims at the surface of the bottom part of the silicon groove and the etching of the side wall of the contact hole is little can be controlled, and the worsening of the bowing profile morphology of the channel hole can be prevented. Accordingly, the integral performance of the 3D NAND flash memory can be improved.

Owner:YANGTZE MEMORY TECH CO LTD

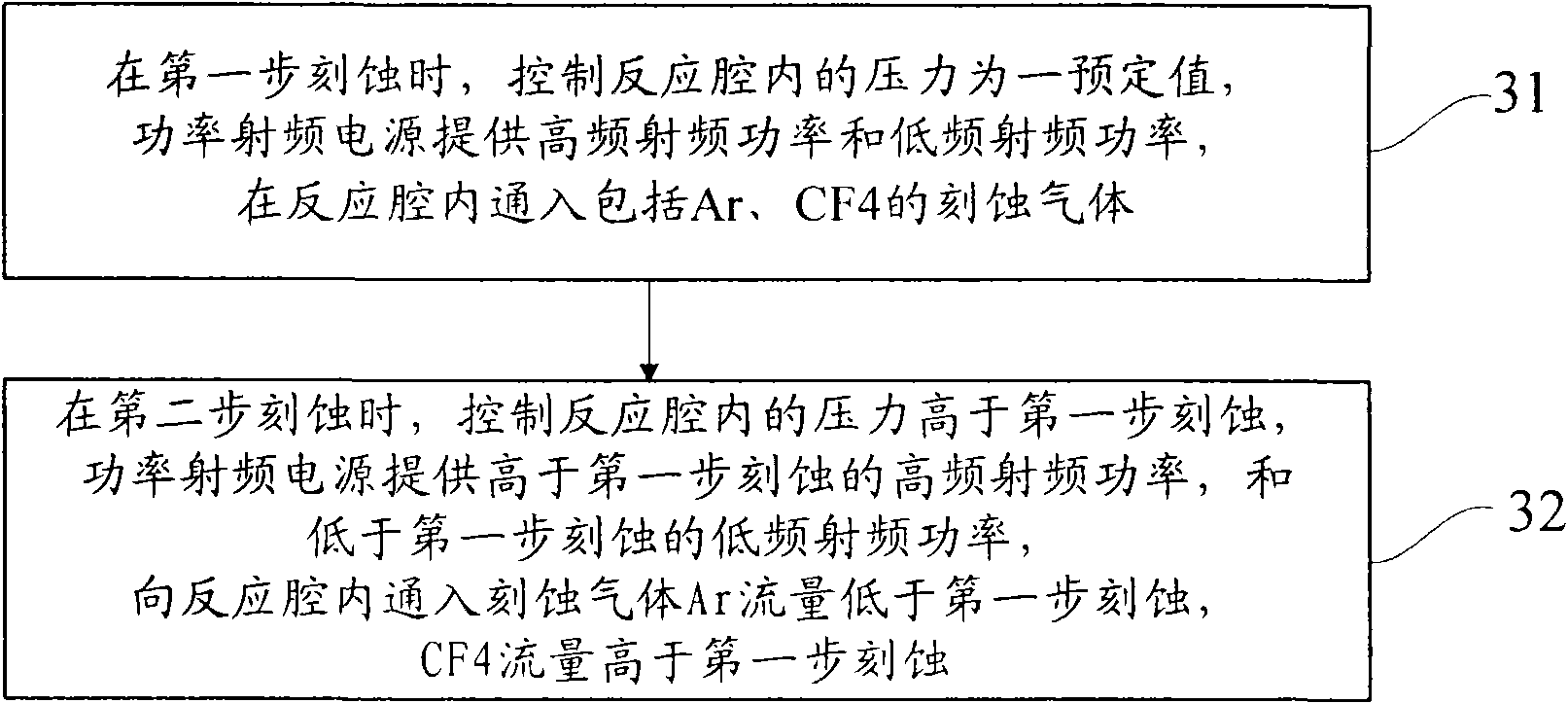

Method for etching groove

InactiveCN101866846ALower latencyIncrease pressureSemiconductor/solid-state device manufacturingEtchingTwo step

The method discloses a method for etching a groove. In the invention, the etching is carried out in a reaction chamber, and the method comprises the a following main etching step implemented by two steps: 1, etching on the basis of the original process parameters; and 2, etching on the basis of the regulated process parameters. By adopting the method, micro grooves can be effectively eliminated to further reduce the RC delay.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

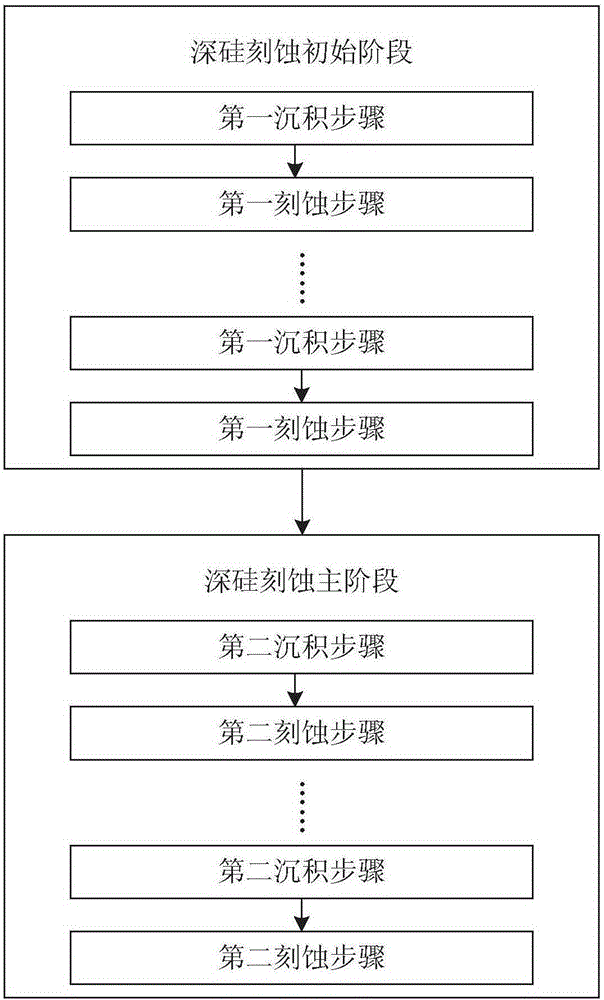

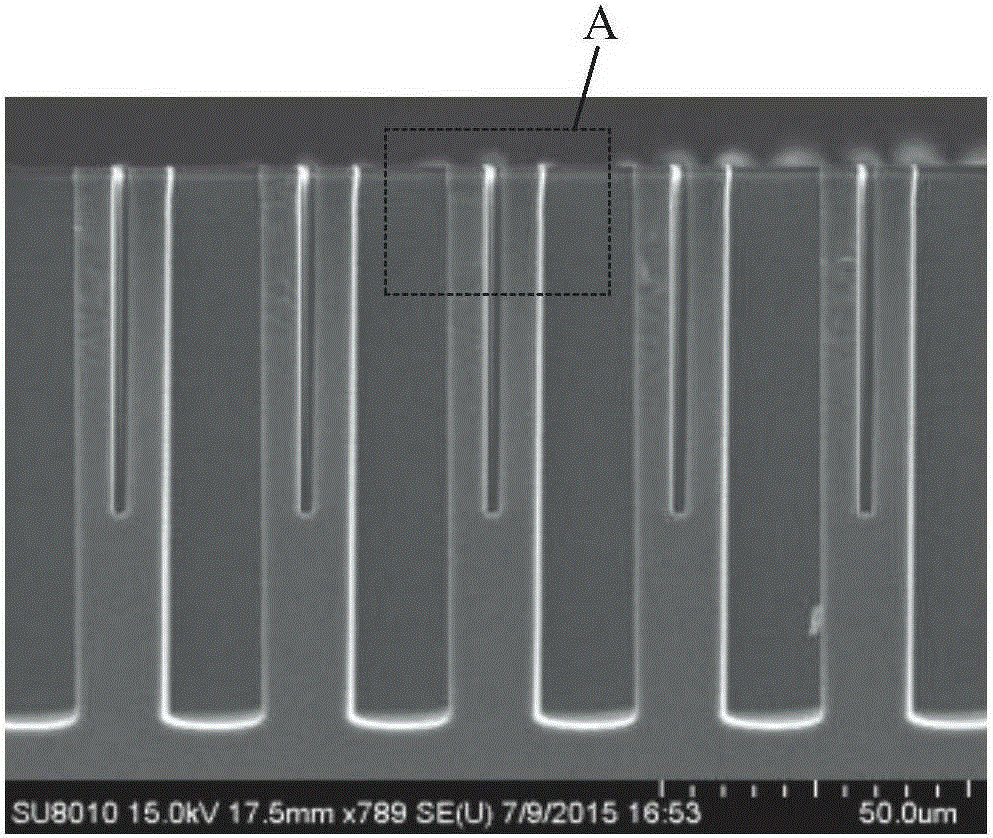

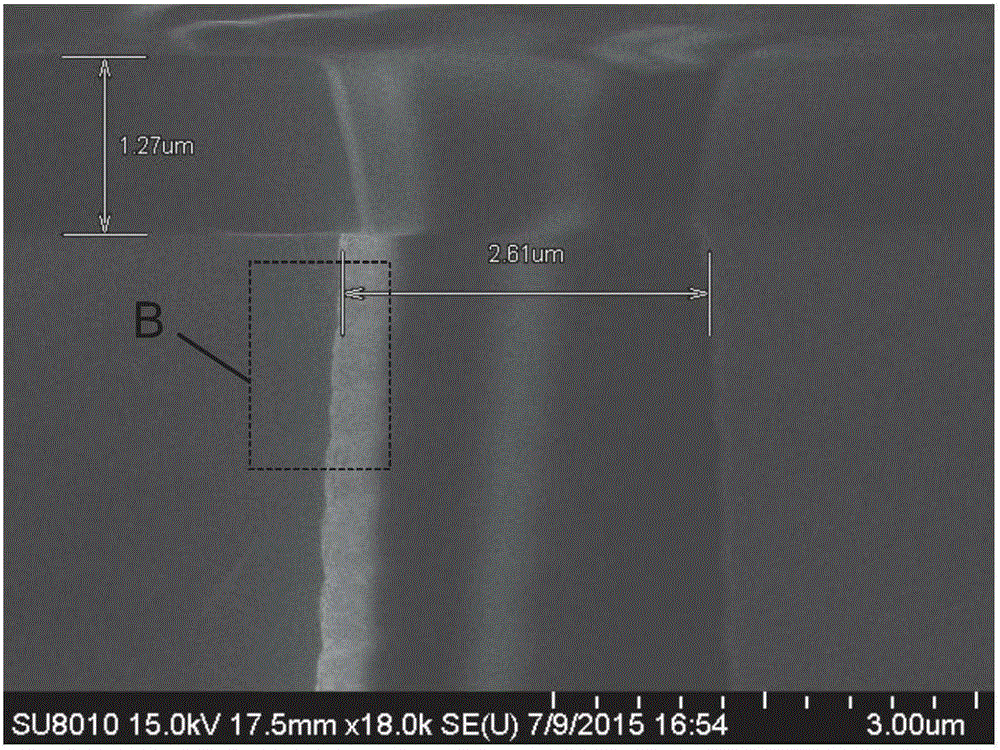

Deep silicon etching method

ActiveCN106564855AImprove protectionReduce etchingDecorative surface effectsChemical vapor deposition coatingSilicon etchingSemiconductor

The invention discloses a deep silicon etching method, and relates to the technical field of semiconductors. The method can improve the morphology of a sidewall. The deep silicon etching method comprises an initial deep silicon etching stage, the initial deep silicon etching stage comprises a plurality of primary deposition steps and a plurality of primary etching steps, the plurality of primary deposition steps and the plurality of primary etching steps are alternately carried out, the deposition time duration of the plurality of primary deposition steps successively decreases, and the etching time duration of the plurality of primary etching steps successively increases. The method is used for deep silicon etching.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

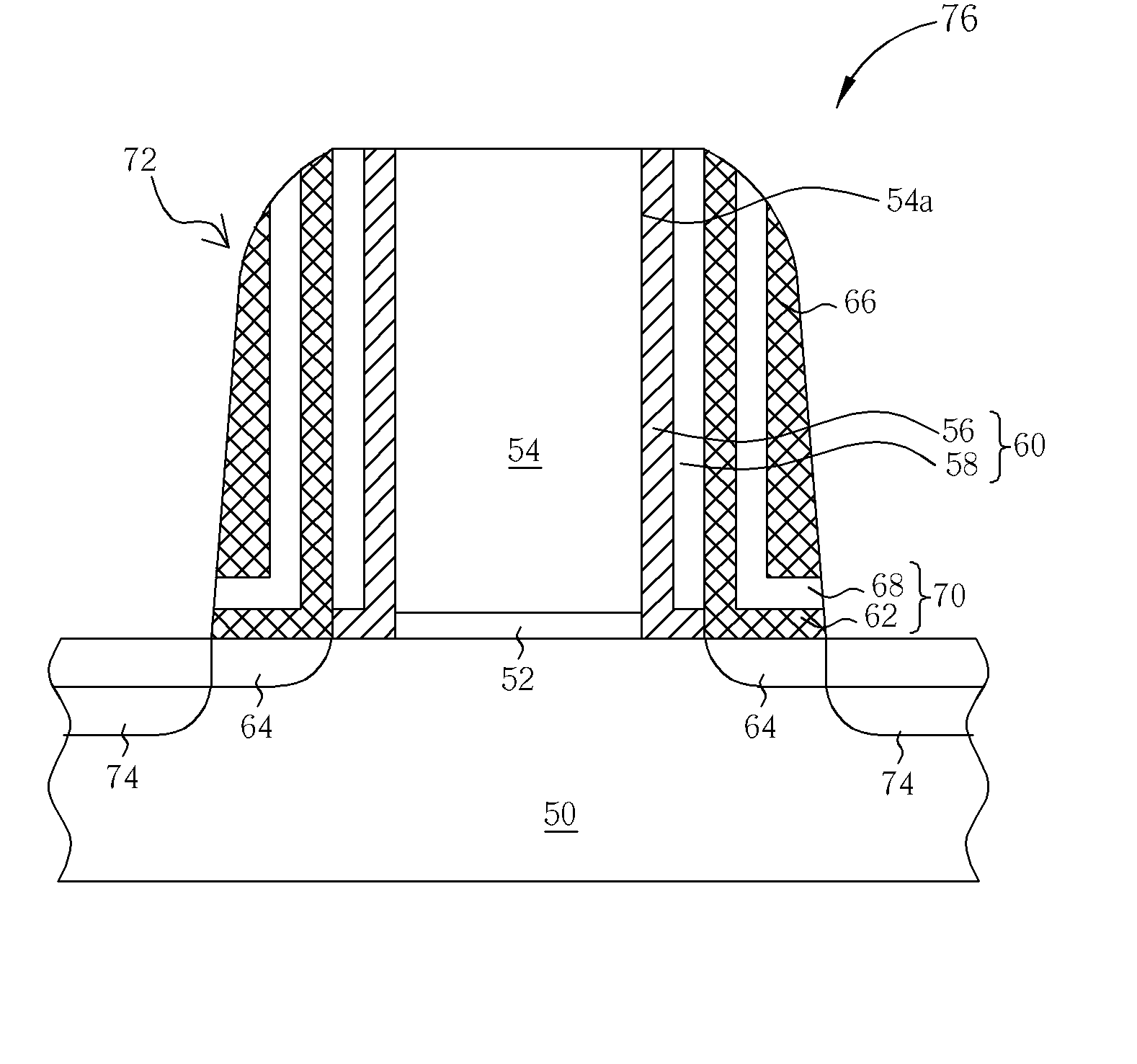

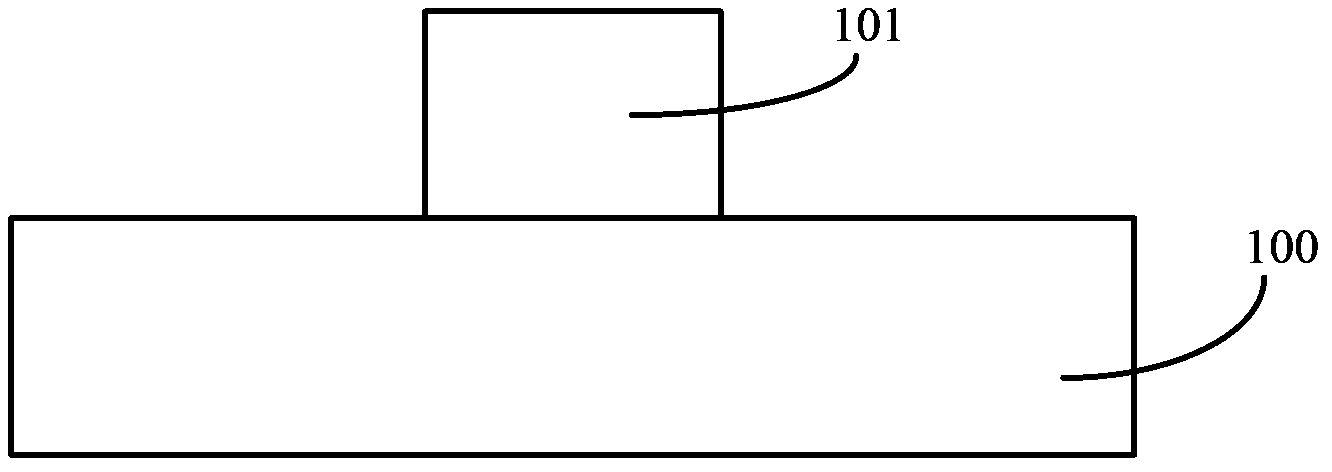

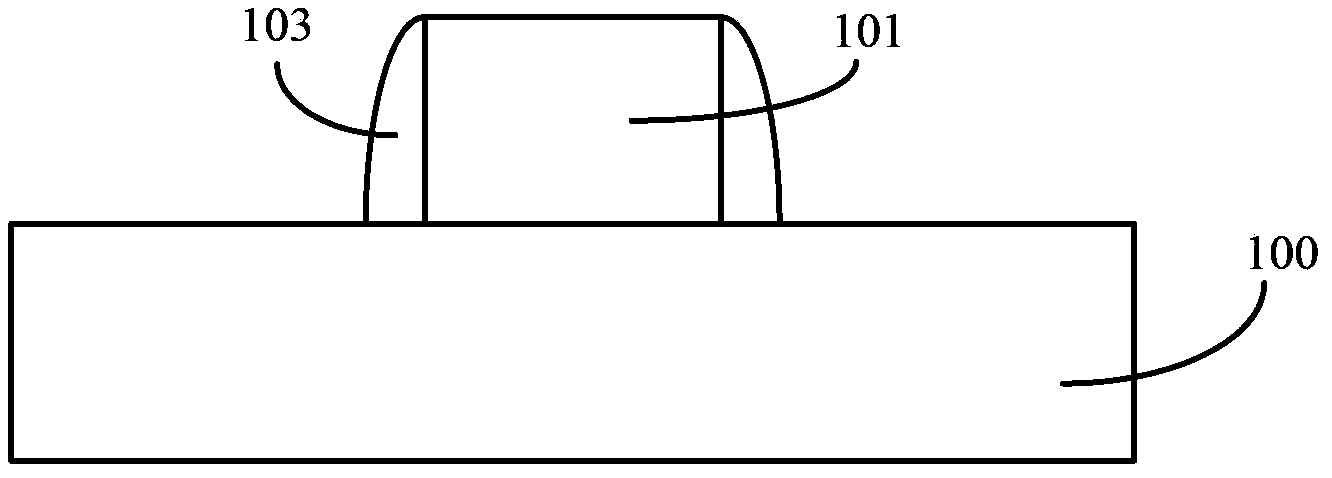

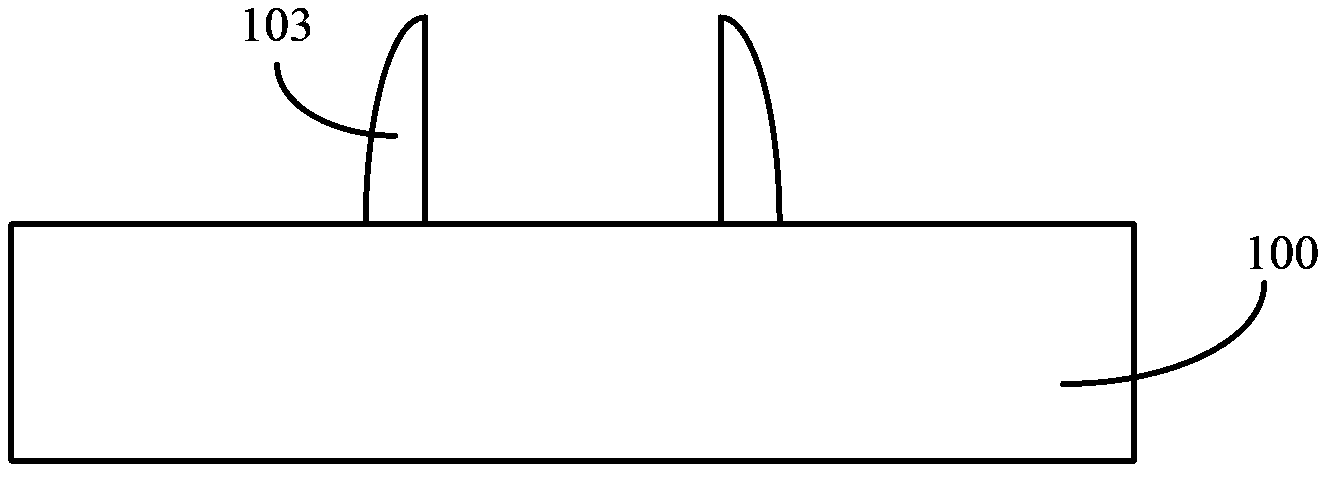

Spacer structure and fabrication method thereof

ActiveUS20070246751A1Etch selectivityLow first rateSemiconductor/solid-state device manufacturingSemiconductor devicesCarbon nitrideOxygen

A spacer structure contains a carbon-containing oxynitride film positioned on a gate sidewall and a nitride film covering the carbon-containing oxide film. The carbon-containing oxynitride film has low etch rate so that the spacer structure can have a good profile during etching the carbon-containing oxynitride film.

Owner:MARLIN SEMICON LTD

Semiconductor structure and formation method thereof

ActiveCN109979880AHighly integratedIt is not easy to increase the threshold voltageTransistorSolid-state devicesEngineeringSemiconductor structure

The present invention provides a semiconductor structure and a formation method thereof. The formation method of the semiconductor structure comprises the steps of: providing a substrate, wherein thesubstrate comprises fin columns, and each fin column comprises a bottom portion region, a channel region located on the bottom portion region and a top portion region located on the channel region; forming first isolation layers on the substrate, wherein the first isolation layers cover the bottom portion regions of the fin columns; forming first gate oxide layers and second gate oxide layers at the surfaces of the side walls of the channel regions of the fin columns, wherein the second gate oxide layers are located at the surfaces of the top portions of the first gate oxide layers, and the thicknesses of the first gate oxide layers and the second gate oxide layers are different; forming gate structures at the surfaces of the top portions of the first isolation layers, wherein the gate structures cover the first gate oxide layers and the second gate oxide layers; and forming second isolation layers at the surfaces of the top portions of the gate structures, wherein the second isolationlayers cover the side walls of the top portion regions of the fin columns. The formation method provided by the invention can improve the performances of the semiconductor structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

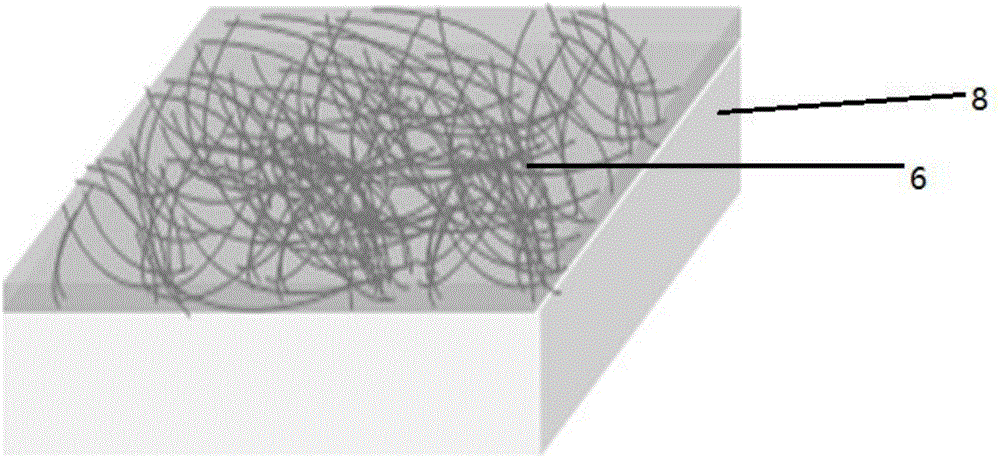

Conductive nanowire layer and graphical method and application thereof

ActiveCN106784393AImprove adhesionReduce etchingSolid-state devicesSemiconductor/solid-state device manufacturingNanowireConductive materials

The invention provides a graphical method of a conductive nanowire layer. The method comprises the steps that a conductive nanowire material and graphical glue are mixed to form a mixed solution, a substrate is coated with the mixed solution, and then the conductive nanowire layer is obtained through curing molding. The conductive nanowire layer can be obtained just through one step of curing. Compared with a traditional method, etching and stripping technologies are omitted, and the adhesive force between the nanometer conductive material and the substrate is enhanced; when the conductive nanowire layer is used as an electrode layer of an organic electroluminescence device, light rays of the device are uniform, and the problem of visual light ray non-uniformity or other optical defects cannot be generated.

Owner:CHENGDU VISTAR OPTEOLECTRONICS CO LTD

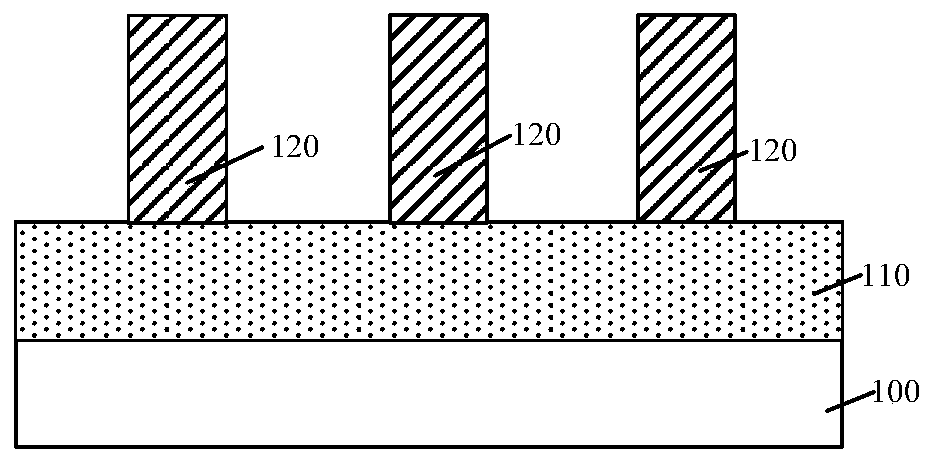

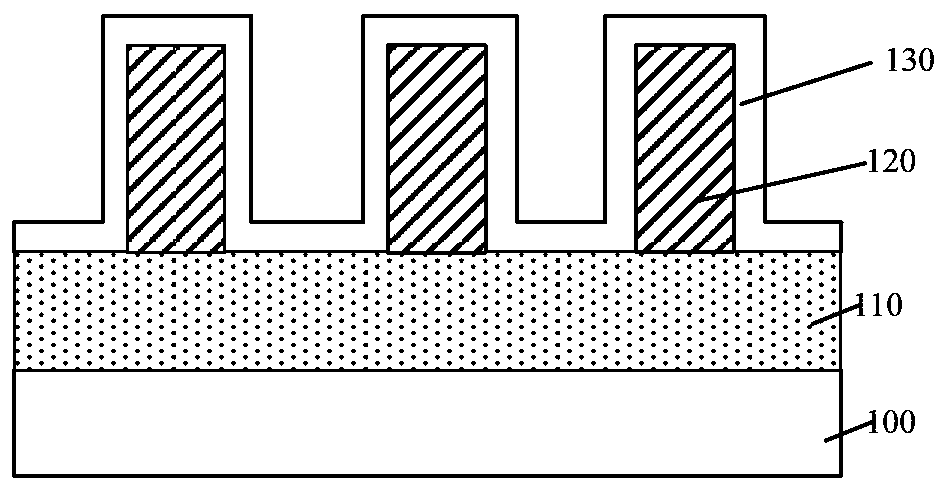

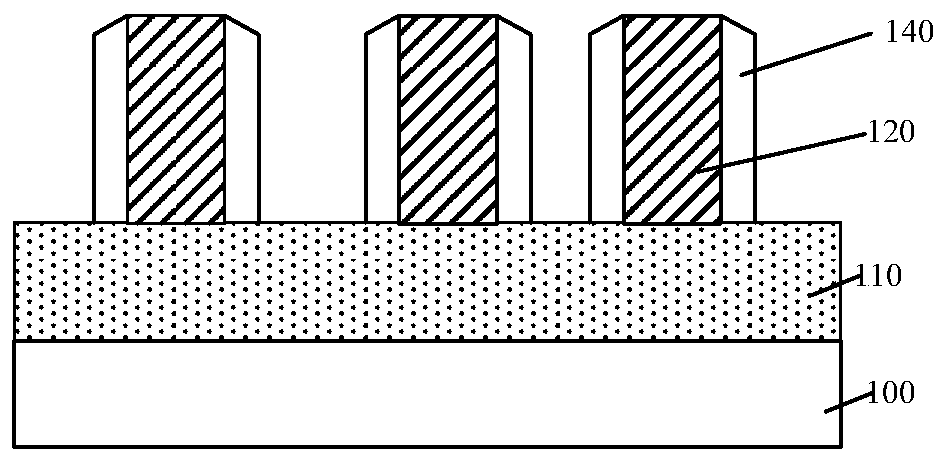

Method for forming self-aligned triple graphs

ActiveCN104078330ASmall sizeInconsistent sizeSemiconductor/solid-state device manufacturingBiomedical engineering

A method for forming self-aligned triple graphs comprises the steps of providing a to-be-etched layer, wherein part of the surface of the to-be-etched layer is provided with a plurality of split first sacrificial layers, the surface of the to-be-etched layer is exposed between the adjacent first sacrificial layers, and the surfaces of the first sacrificial layers are provided with second sacrificial layers; forming mask films on the surface of the to-be-etched layer, the surfaces of the first sacrificial layers and the surfaces of the second sacrificial layers; removing the mask films on side walls and top surfaces of the second sacrificial layers and forming first masks on two sides of the first sacrificial layers; after the first masks are formed, removing part of the second sacrificial layers along side wall surfaces of the second sacrificial layers to reduce the dimensions of the second sacrificial layers and expose part of the surfaces of the first sacrificial layers, and reducing the dimensions until the second sacrificial layers form second masks. The method is simple, and the formed triple graphs are applied more widely.

Owner:SEMICON MFG INT (SHANGHAI) CORP

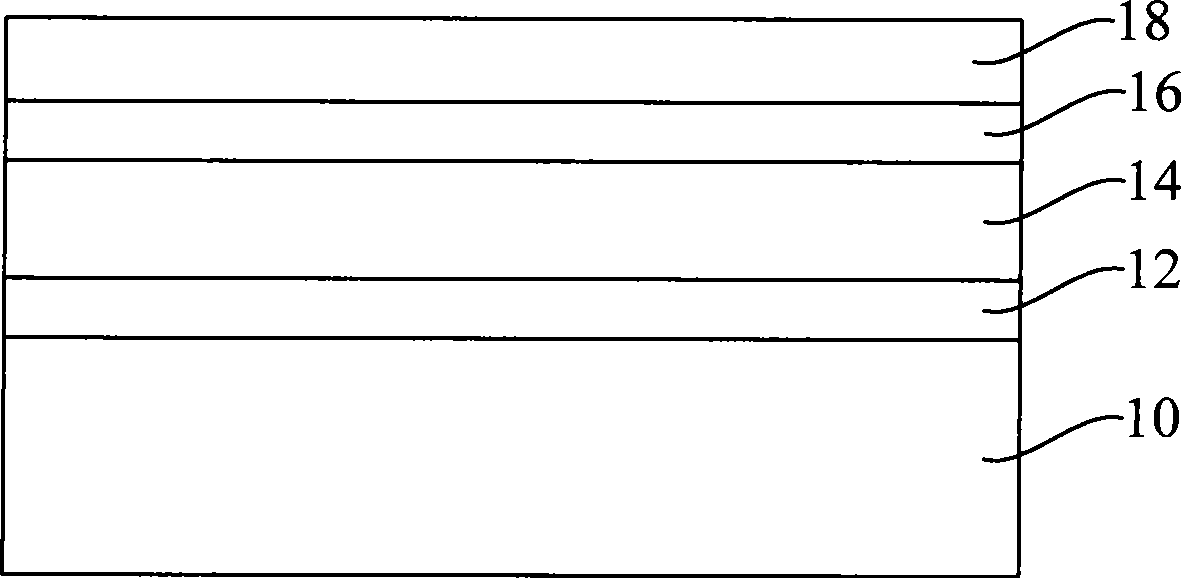

Self-aligned double patterning method and semiconductor structure formed by same

PendingCN111524795AImprove reliabilityStable supportSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

The invention relates to a self-aligned double patterning method and a semiconductor structure formed by the same. The method comprises steps of providing a substrate, and enabling a surface of the substrate to be provided with a to-be-etched material layer and a plurality of mutually-separated sacrificial layers located on a surface of the to-be-etched material layer; forming a first mask layer on a surface of a side wall of the sacrificial layer; after the first mask layer is formed, forming a second mask layer on a surface of a side wall of the first mask layer, and the second mask layer and the first mask layer being made of different materials; after the second mask layer is formed, removing the sacrificial layers. The method is advantaged in that reliability of the self-alignment double patterning method is high.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Manufacturing method for gate and semi-conductor device

InactiveCN101459069AReduced execution timeStrong ability to remove residues and defectsSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing gridPhotoresist

A method of manufacturing grids includes steps of sequentially forming a grid layer, an anti-reflection layer and grid photoresist patterns on a semiconductor substrate, etching for removing the anti-reflection layer uncovered by the grid photoresist patterns, etching the grid layer uncovered by the anti-reflection layer, and forming grids, wherein a process of etching the anti-reflection layer includes steps of primarily etching the anti-reflection layer with plasma and over-etching the anti-reflection layer with plasma containing CF4 and O2. The invention further provides a method of manufacturing semiconductor devices. The method of manufacturing grids is capable of reducing residue defects of the anti-reflection layer materials or does not have any residue defects.

Owner:SEMICON MFG INT (SHANGHAI) CORP

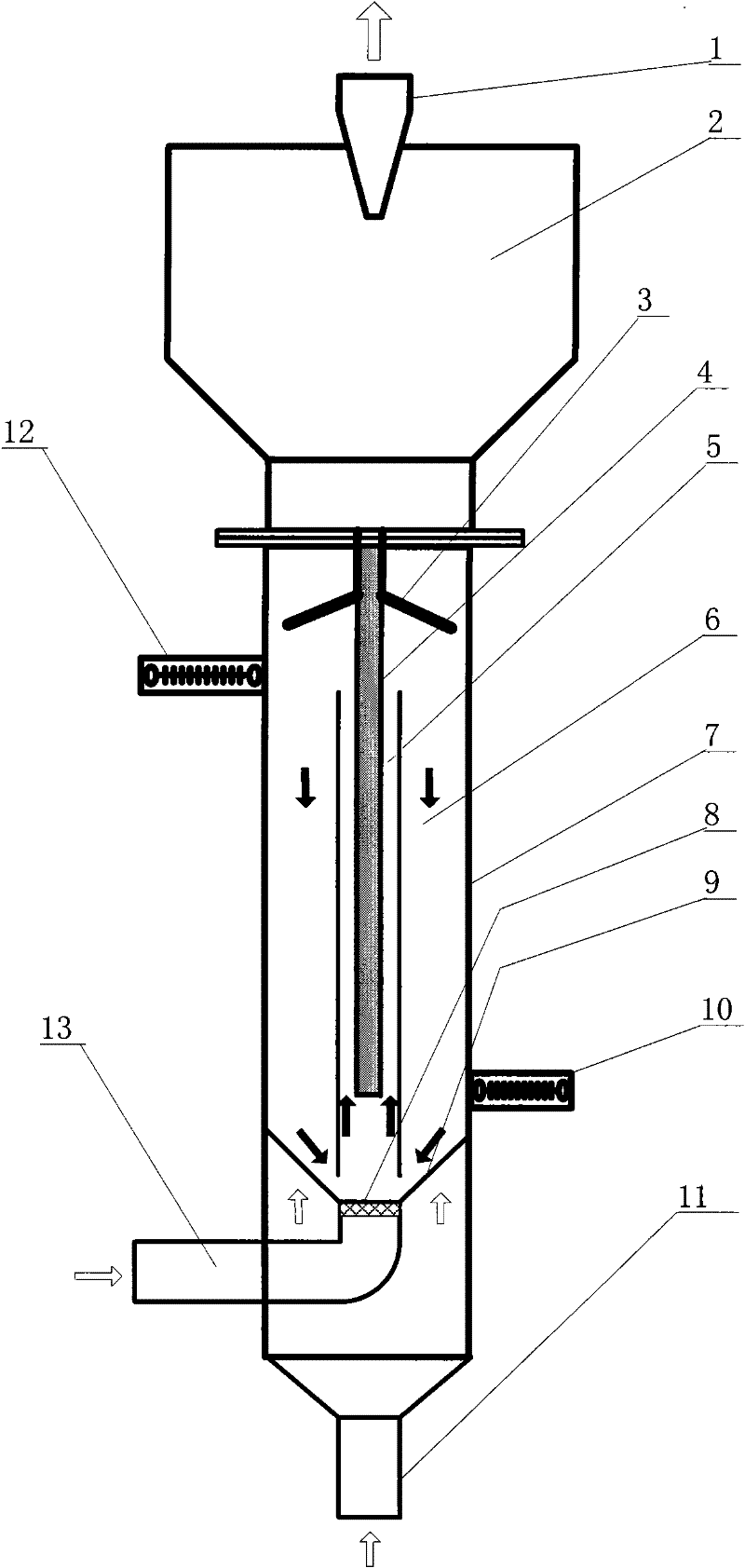

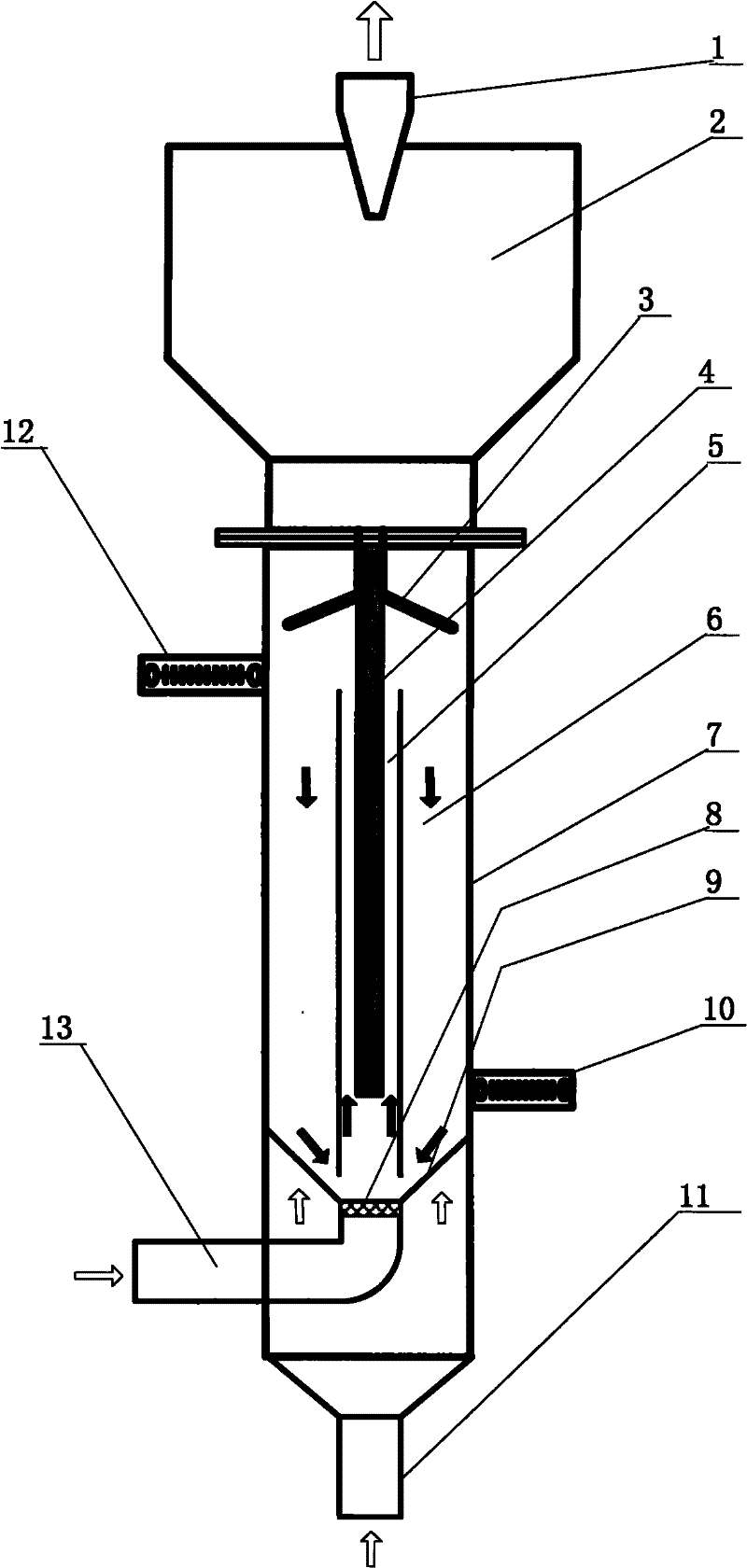

Spouted bed reactor and method thereof for synthesizing chlorinated polyvinyl chloride by using low-temperature plasmas

ActiveCN101649010BIncrease the scaleLittle affected by electric fieldChlorinated polyvinyl chlorideReaction zone

The invention relates to a spouted bed reactor and a method for synthesizing chlorinated polyvinyl chloride by using low-temperature plasmas. The reactor mainly comprises a reactor main body, a gas and solid separating zone, a gas and solid separating device and the like, wherein the gas and solid separating zone and the gas and solid separating device are arranged at the top of the reactor body.A low-temperature plasma generating device is arranged in the reactor main body and divides the interior of the reactor main body into a low-temperature plasma reaction zone and a granule descending chlorine migration zone. The method of the spouted bed reactor synthesizing chlorinated polyvinyl chloride is characterized in that the polyvinyl chloride is induced to be quickly chloridized by usingthe low-temperature plasmas, and the polyvinyl chloride granules are spouted in a low-temperature plasma discharging zone to generate chloridizing reaction; and the granules carried out of the low-temperature plasma reaction zone by air flow are deposited in the granule descending chlorine migration zone to realize circulation chloridizing of the granules. The invention utilizes the low-temperature plasma method to simultaneously activate chlorine gas and polyvinyl chloride granules at low temperature; and the product efficiency and the product quality are preferably enhanced.

Owner:TSINGHUA UNIV

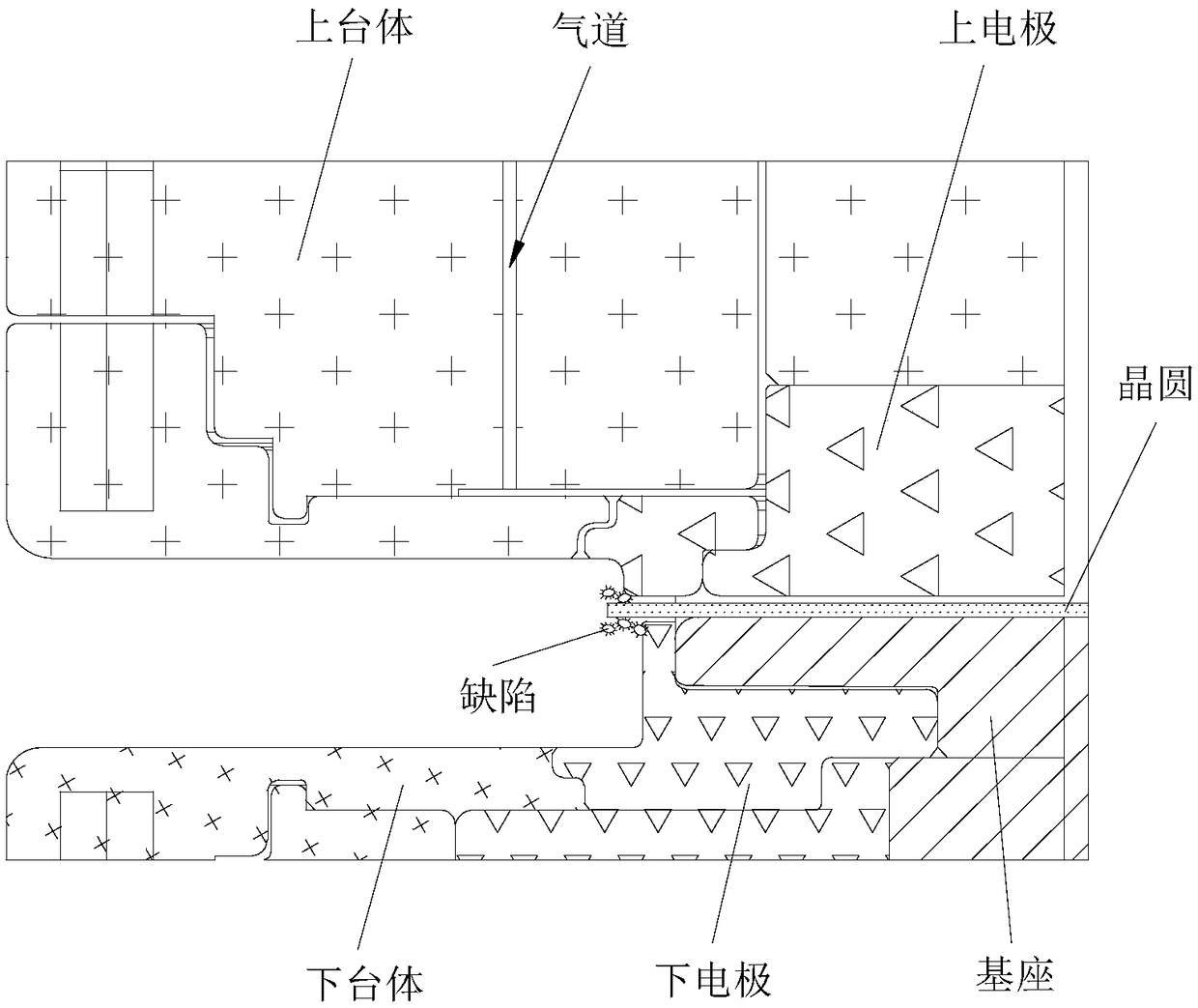

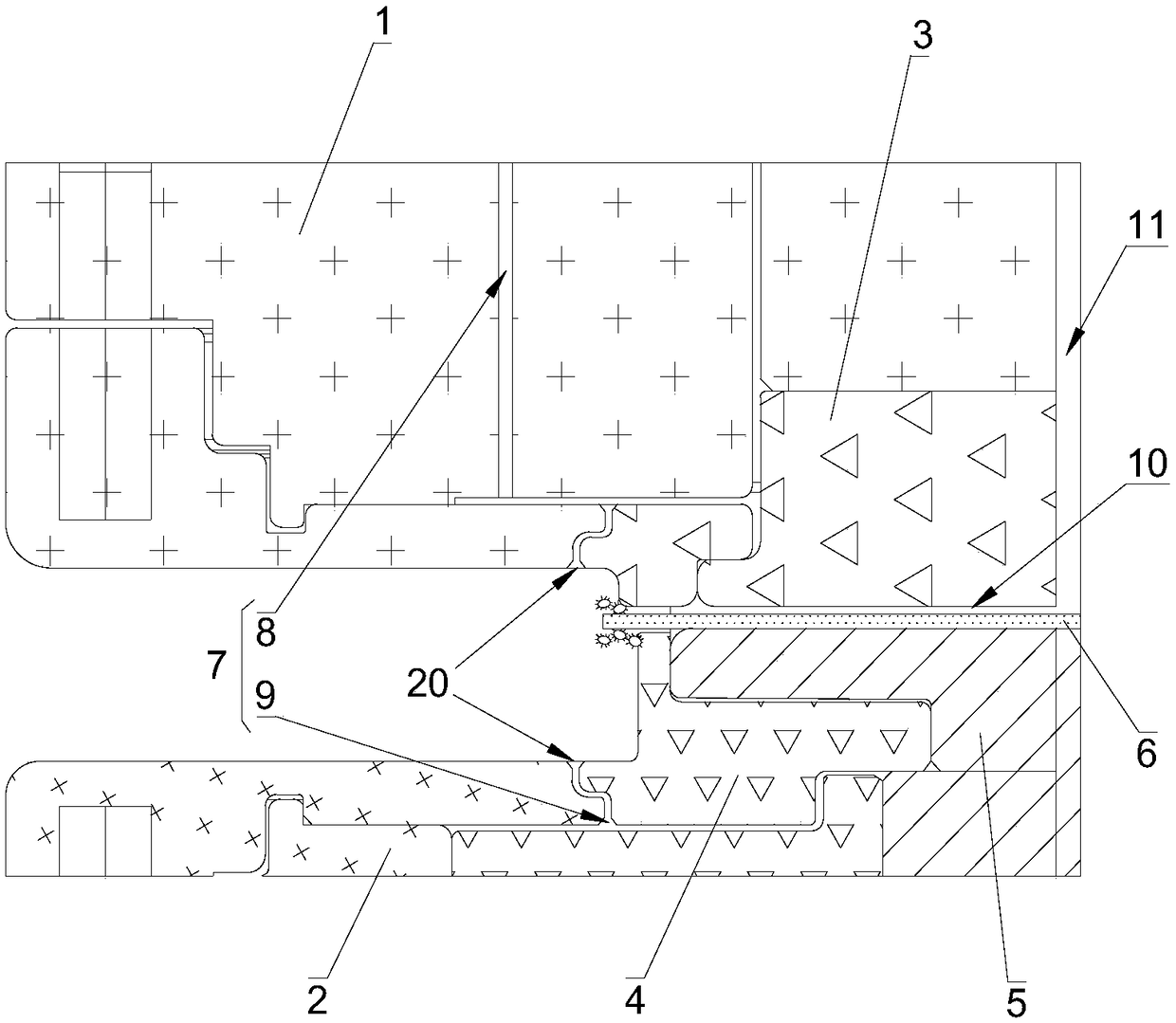

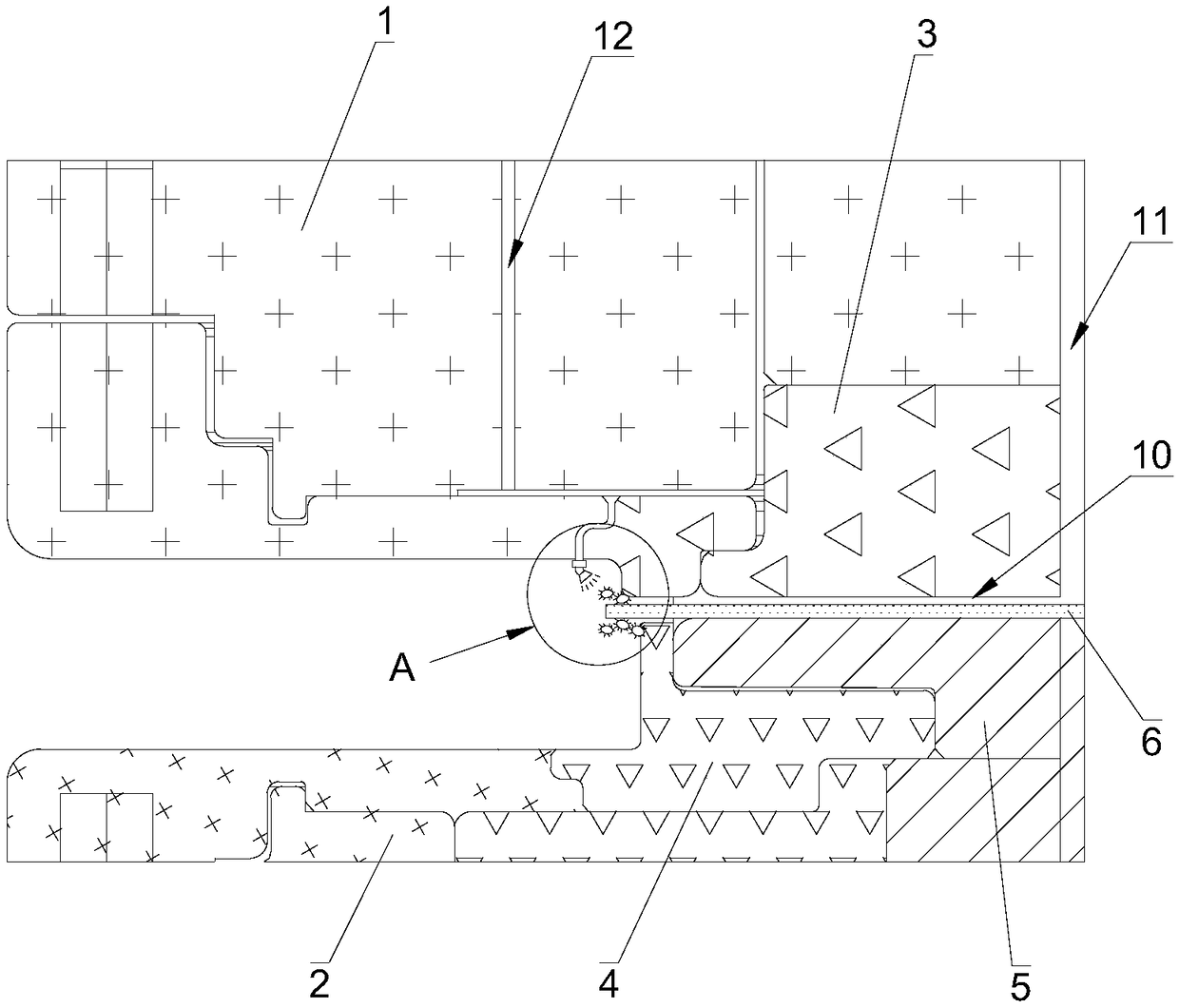

Etching equipment and crystal edge etching method

InactiveCN109148252AClean up comprehensivelyReduce cleanupSemiconductor/solid-state device testing/measurementElectric discharge tubesEngineeringGas supply

The invention relates to the technical field of semiconductor processing equipment, and discloses etching equipment for removing defects on the back surface of a wafer and a crystal edge etching method. The specific etching equipment includes an upper table body and a lower table body, wherein upper and lower electrodes are respectively arranged on opposite sides of the upper table body and the lower table body, a base for supporting the wafer is arranged on the lower electrode, and the equipment also includes an etching gas supply assembly for etching the upper and lower edges of the wafer. When crystal edge etching is carried out, the wafer is placed on the base, the upper table body drives the upper electrode to move downward, presses and covers the center of the wafer, the etching gassupply assembly introduces gas to the upper and lower edges of the wafer, the defects of the upper and lower edges of the wafer are etched and removed at the same time, and the yield of the product isimproved.

Owner:HUAIAN IMAGING DEVICE MFGR CORP

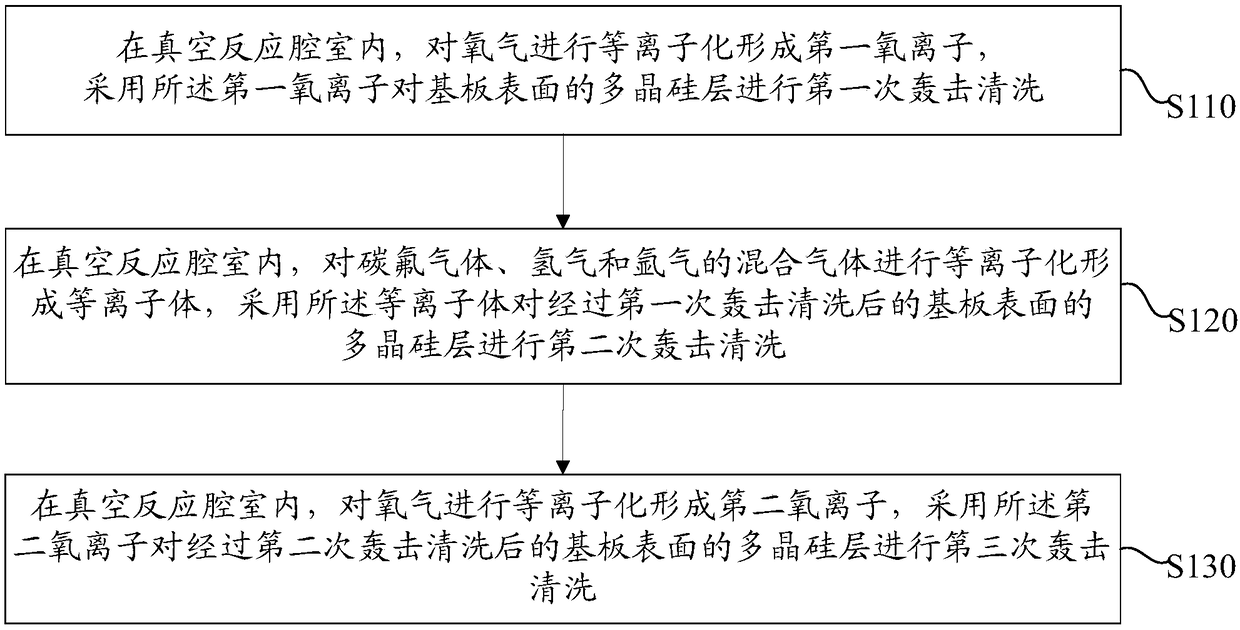

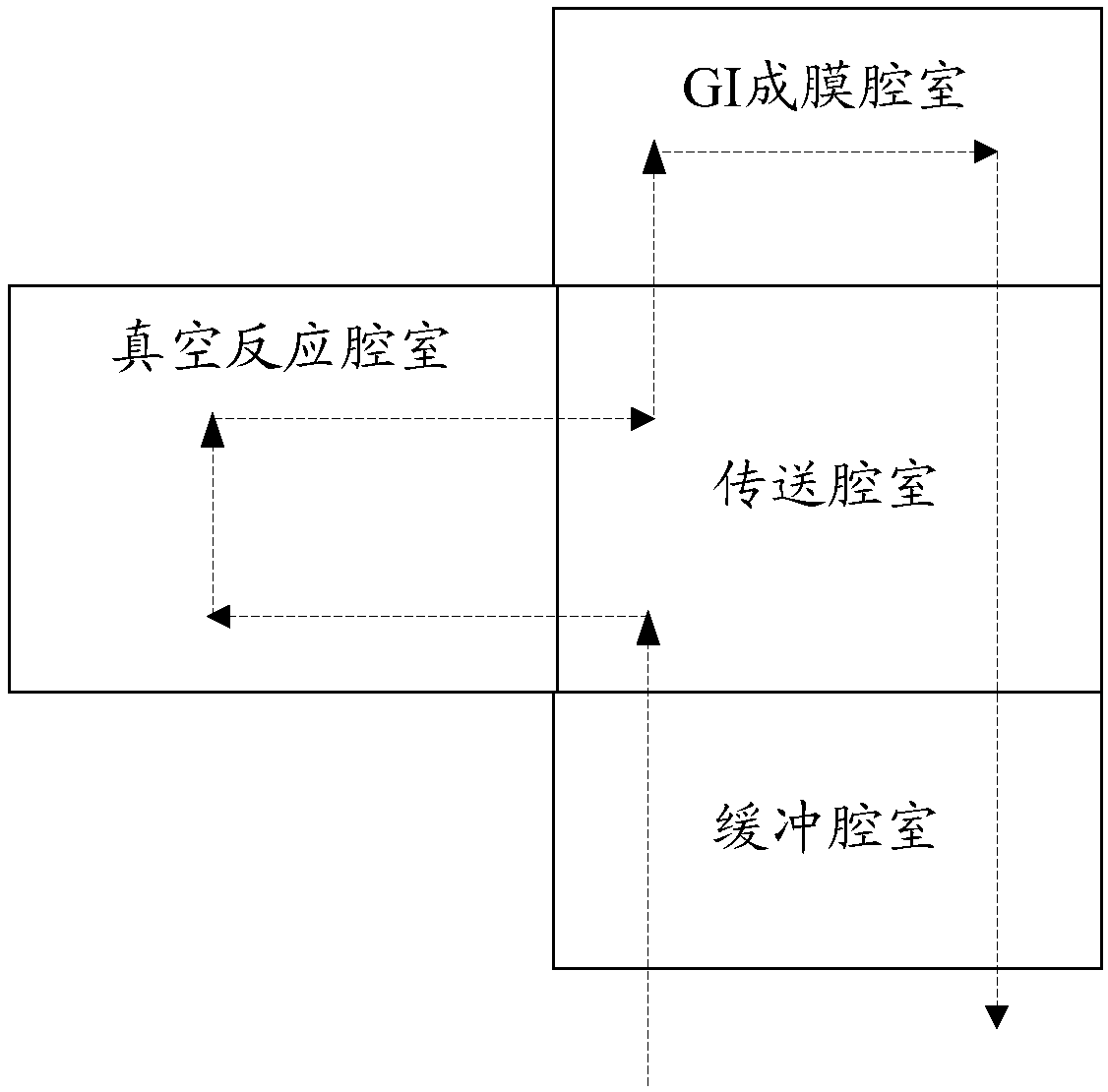

Method and system for processing polycrystalline silicon layer before forming of gate insulation layer

ActiveCN108346561AGood removal effectReduce etchingSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerOxygen ions

The invention discloses a method and system for processing a polycrystalline silicon layer before the forming of a gate insulation layer, and the method comprises the following steps: carrying out theplasma processing of oxygen in a vacuum reaction cavity to form first oxygen ions, and carrying out the first bombardment cleaning of the polycrystalline silicon layer on the surface of a substrate through the first oxygen; carrying out the plasma processing of the mixed gas of fluorocarbon gas, hydrogen gas and argon gas in the vacuum reaction cavity to form plasmas, and carrying out the secondbombardment cleaning of the polycrystalline silicon layer on the surface of the substrate through the plasmas after the first bombardment cleaning; carrying out the plasma processing of the mixed gasof oxygen gas in the vacuum reaction cavity to form second oxygen ions, and carrying out the third bombardment cleaning of the polycrystalline silicon layer on the surface of the substrate through thesecond oxygen ions after the second bombardment cleaning. The method provided by the invention can achieve the removal of the oxides (mainly comprising silicon oxide) on the surface of the polycrystalline silicon layer in a better way, and can reduce mura on a P-Si surface.

Owner:TRULY HUIZHOU SMART DISPLAY