Self-aligned double patterning method and semiconductor structure formed by same

A double patterning and self-alignment technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as poor reliability and achieve the effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] As mentioned in the background, the existing self-aligned double patterning method has poor reliability.

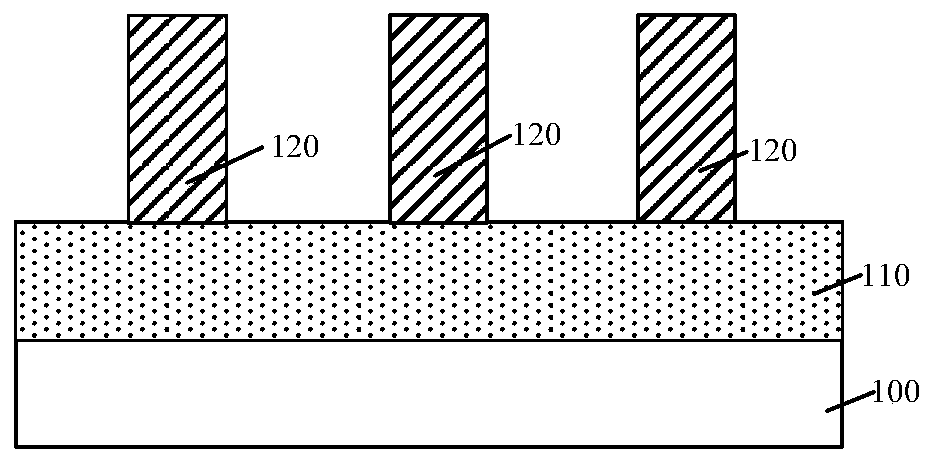

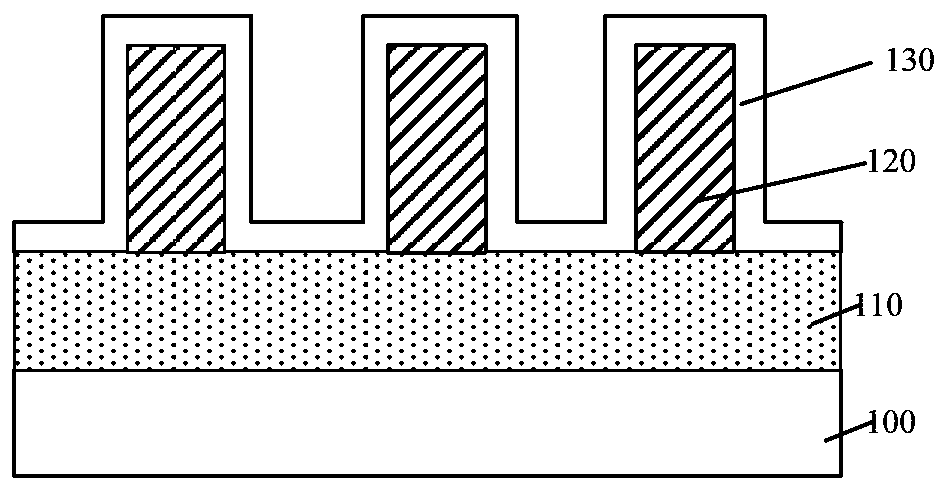

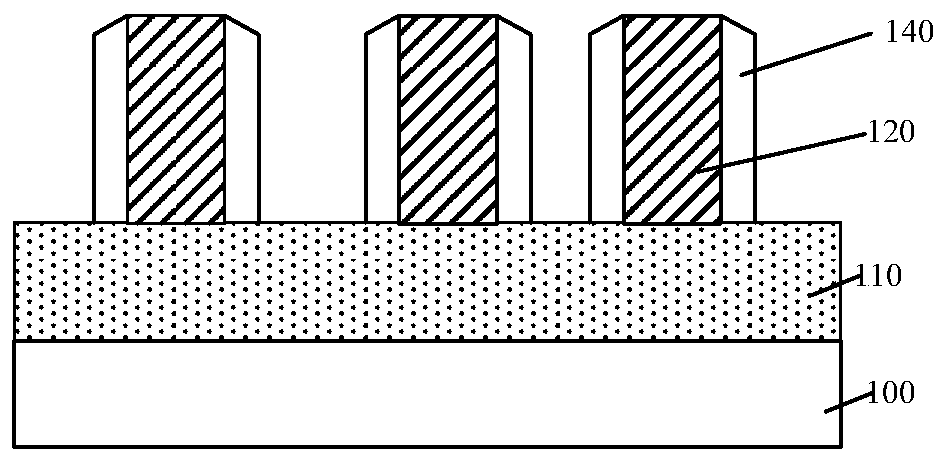

[0034] Figure 1 to Figure 5 It is a structural schematic diagram of each step of a self-aligned double patterning method.

[0035] Please refer to figure 1 A substrate 100 is provided, the surface of the substrate 100 has a material layer 110 to be etched, and several (three are shown in the figure) mutually separated sacrificial layers 120 located on the surface of the material layer 110 to be etched.

[0036] Please refer to figure 2 , forming a mask material layer 130 on the surface of the material layer 120 to be etched, and the mask material layer 130 covers the top surface and the sidewall surface of the sacrificial layer 120 .

[0037] Please refer to image 3 After the mask material layer 130 is formed, the mask material layer 130 is etched back until the top surface of the sacrificial layer 120 and the top surface of the material layer 110 to be etch...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More