Shield gate groove type field effect transistor and preparation method thereof

A field effect transistor and shielded gate technology, applied in the field of shielded gate trench type field effect transistor and its preparation, can solve problems such as transistor avalanche failure, and achieve the effects of inhibiting turn-on and improving avalanche tolerance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

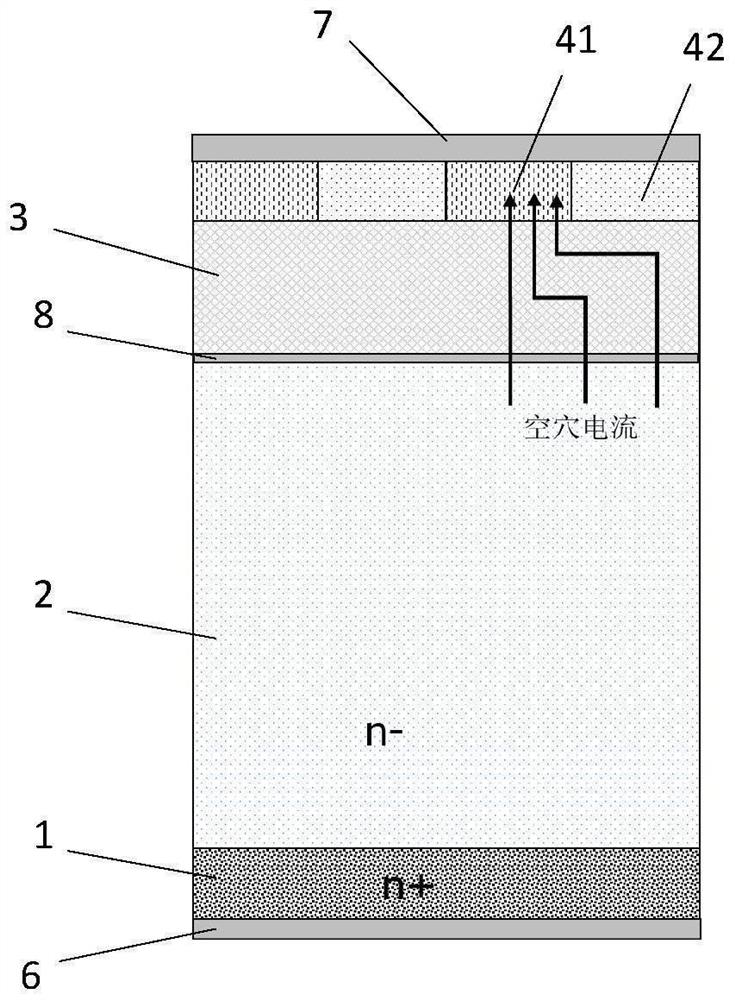

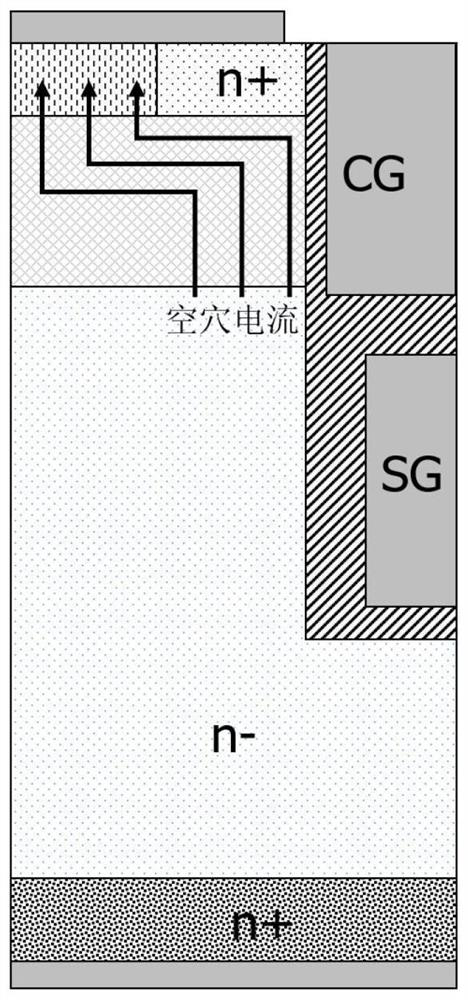

[0052] When the traditional SGT forward high voltage is blocked or forward high voltage is turned on, the SGT is prone to generate hole current due to the avalanche effect, and the hole current flowing through the channel of the substrate region will cause the parasitic transistor to turn on. The turn-on of the parasitic triode will lead to avalanche failure of the transistor.

[0053] In view of the above problems, the embodiment of the present application provides a shielded gate trench type field effect transistor, which can suppress the turn-on of the parasitic transistor in the SGT before the avalanche failure of the SGT occurs.

[0054] The technical solutions of the embodiments of the present application are described in detail below with reference to the accompanying drawings.

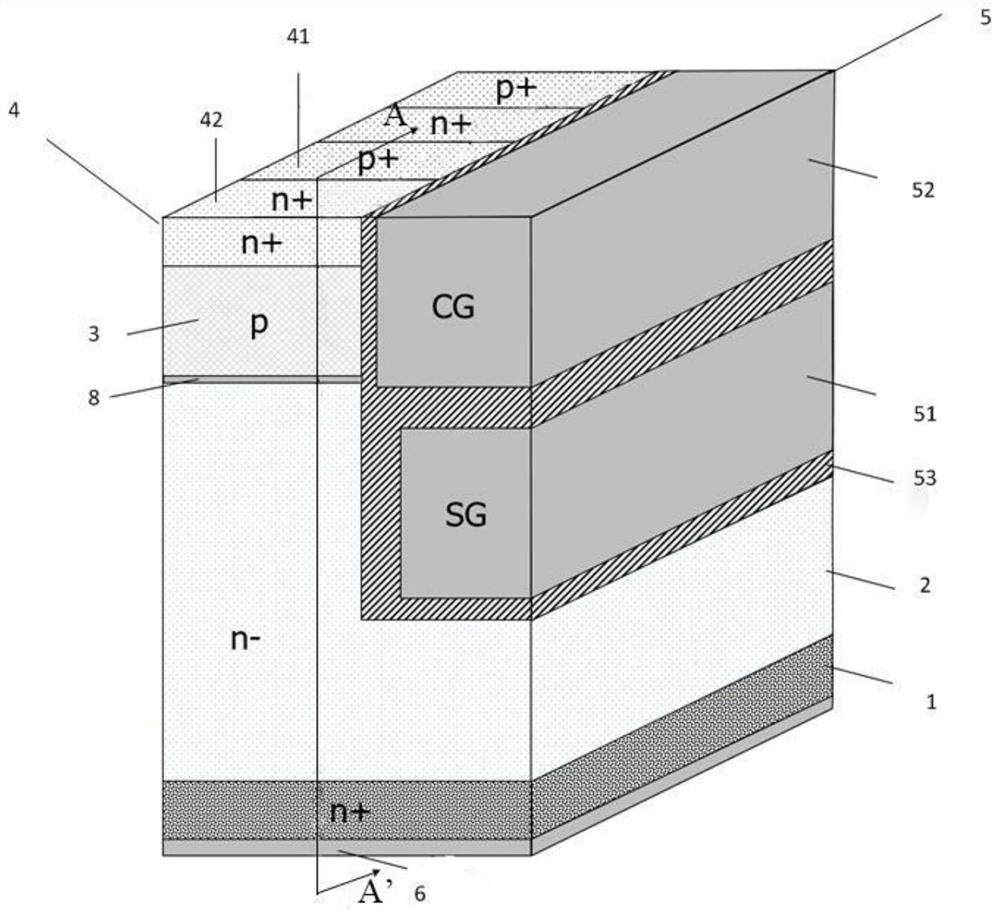

[0055] figure 1 It is a schematic structural diagram of a shielded gate trench type field effect transistor shown in an embodiment of the present application;

[0056] figure 2Yes figure 1...

Embodiment 2

[0076] Based on the first embodiment above, the embodiment of the present application provides another shielded gate trench field effect transistor, which can effectively guide the hole current into the base region and flow into the P-type source region 41 more uniformly when an avalanche occurs.

[0077] The technical solutions of the embodiments of the present application are described in detail below with reference to the accompanying drawings.

[0078] see figure 1 and figure 2 , the shielded gate trench field effect transistor, comprising:

[0079] Substrate region 1, drift region 2, base region 3, source region 4, trench region 5, source 7 and drain 6;

[0080] The drift region 2 is in contact with the substrate region 1, and the direction in which the substrate region 1 points to the drift region 2 is upward,

[0081] The base region 3 and the source region 4 are sequentially arranged above the drift region 2;

[0082] The trench region 5 is disposed on the side of...

Embodiment 3

[0093] Corresponding to the aforementioned shielded gate trench field effect transistor and its embodiments, the present application also provides a method for manufacturing a shielded gate trench field effect transistor and corresponding embodiments.

[0094] Figure 4 It is a schematic flow chart of the manufacturing method of the shielded gate trench field effect transistor shown in the embodiment of the present application.

[0095] see Figure 4 , the preparation method of the shielded gate trench type field effect transistor, comprising:

[0096] 401. Prepare a substrate region with a semiconductor material;

[0097] In the embodiment of the present application, the substrate region is prepared with an N-type heavily doped semiconductor material, that is, the doping type of the substrate region is N-type doping, and the doping concentration of the substrate region is a heavily doped concentration.

[0098] In the embodiment of the present application, the semiconducto...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More