Method for preparing FinFET on germanium and III-V semiconductor material substrate

A technology of the third and fifth groups and semiconductors, which is applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, electrical components, etc., and can solve the problems of adjusting threshold voltage, small on-state current, and high process cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041]The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments, and a process scheme for manufacturing FinFETs on germanium and III-V semiconductor material substrates proposed in the present invention will be specifically given, but the scope of the present invention is not limited in any way.

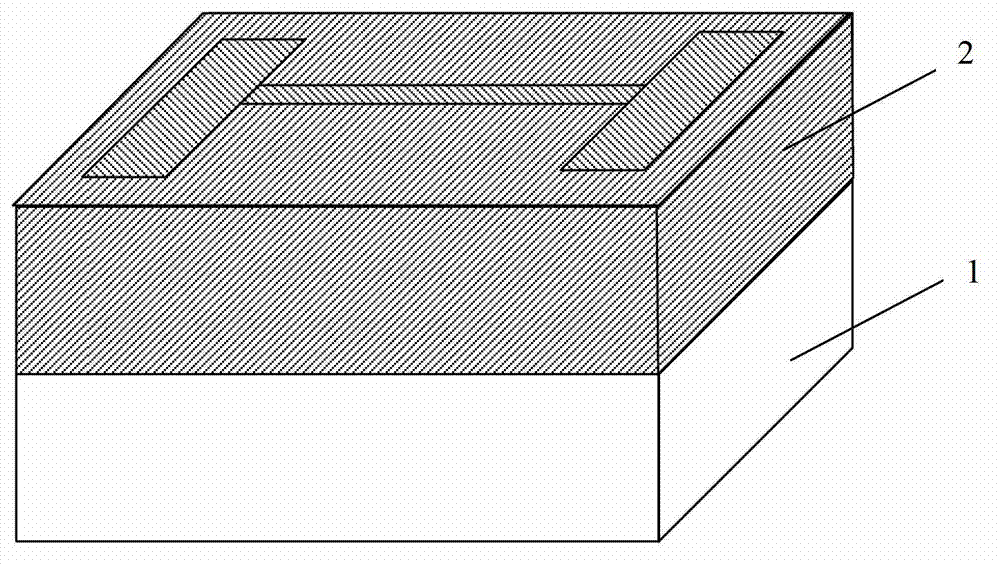

[0042] According to the following steps, plan 1 for n-type germanium and Group III and V FinFETs with a Fin strip thickness of about 20 nanometers and a channel length of about 32 nanometers:

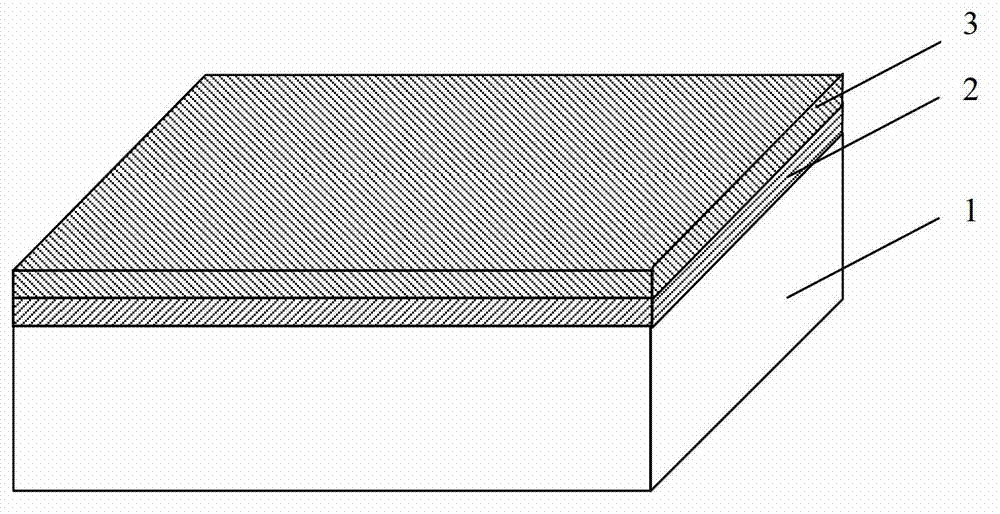

[0043] 1. Ion-enhanced chemical vapor deposition of silicon oxide 300 on a silicon substrate

[0044] 2. Ion-enhanced chemical vapor deposition of silicon nitride 1000 on silicon oxide Such as figure 1 shown;

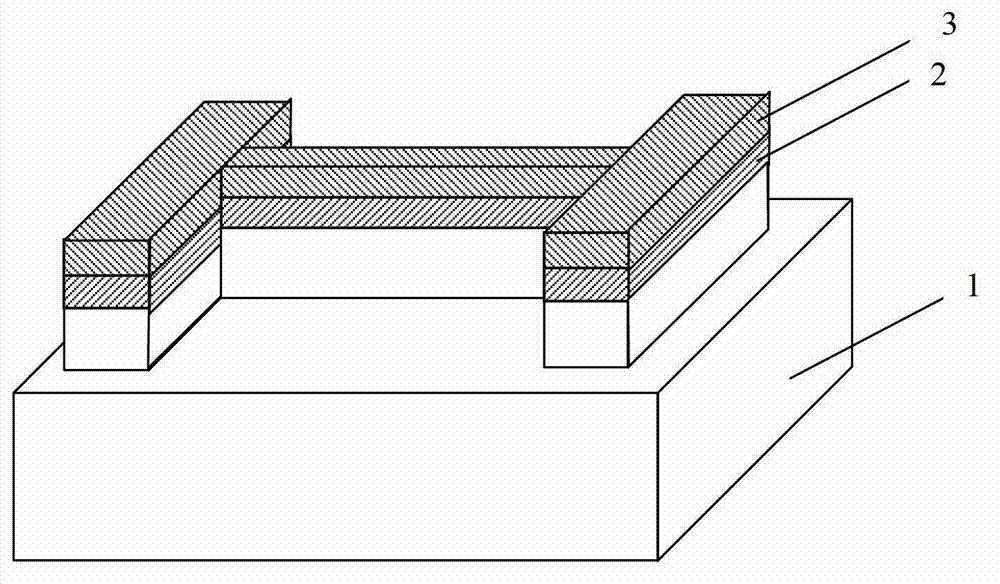

[0045] 3. Electron beam lithography defines the source and drain and the thin strip pattern structure connecting the source and drain, wherein the width of the thin strip pattern structure is 20 nanometers;

[0...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More