IGBT device with carrier storage layer using diode clamping

A carrier storage and diode clamping technology, applied in the field of IGBT devices, can solve the problems of high saturation voltage, reduced saturation current of new IGBTs, and small short-circuit safe working area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

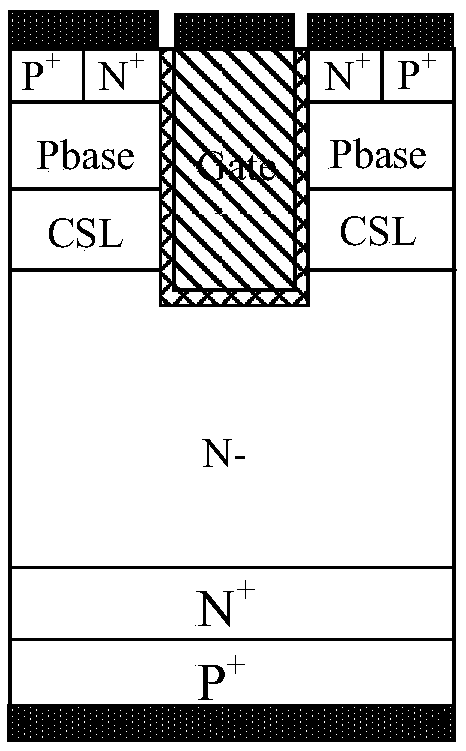

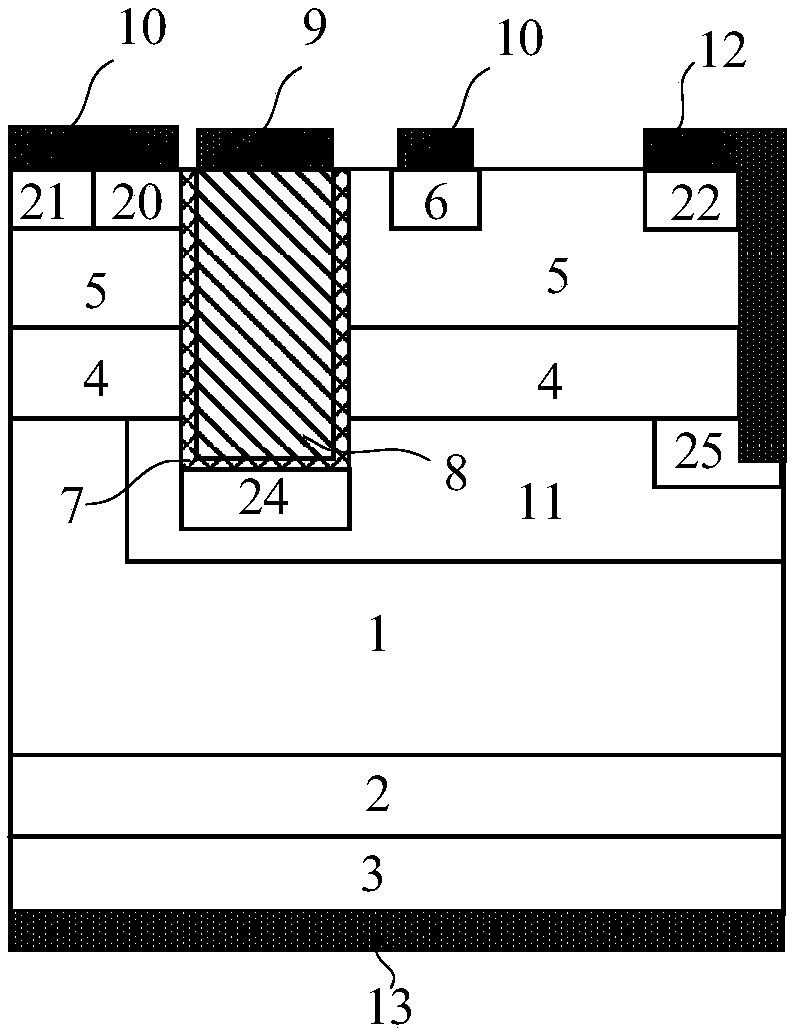

[0034] This embodiment provides an IGBT device with a carrier storage layer clamped by a diode, and its cell structure is as follows image 3 shown, including:

[0035] The voltage-resistant region 1, the N-type buffer layer 2 disposed at the bottom of the voltage-resistant region 1, the P-type collector semiconductor region 3 disposed on the lower surface of the N-type buffer layer 2, and the P-type collector semiconductor region 3 disposed on the lower surface collector metal 13;

[0036] The P-type electric field shielding layer 11 arranged on the upper surface of the withstand voltage region 1, the N-type carrier storage layer 4 covering the upper surface of the withstand voltage region 1 and the P-type electric field shielding layer 11, and the N-type carrier layer 4 covering the upper surface of the N-type electric field shielding layer 11. P-type base region 5 on the upper surface of sub-storage layer 4;

[0037] The surface of the cell is provided with a first deep g...

Embodiment 2

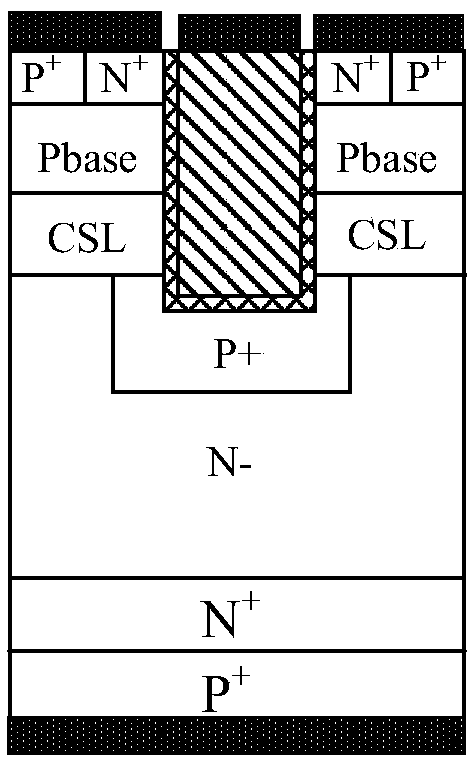

[0046] This embodiment provides a diode-clamped IGBT device with a carrier storage layer, the cell structure of which is as follows Figure 4 As shown, the difference between its cellular structure and Embodiment 1 is that: the short-circuit mode is different from Embodiment 1; in this embodiment, the P-type electric field shielding layer 11 on the other side of the first deep groove, the N-type The carrier storage layer 4 is connected to the semiconductor surface through a deep diffused P-type semiconductor region 27 and an N-type semiconductor region 28 respectively, and then the deep-diffused P-type semiconductor region 27, N-type semiconductor region 28 and the side P-type base region 5 The surface of the first P-type heavily doped semiconductor region 22 in the interior covers the metal 12; the N-type semiconductor region 28 is connected to the metal 12 through a second N-type heavily doped region 6 to form an ohmic contact; the deep diffusion P Type semiconductor region ...

Embodiment 3

[0048] This embodiment provides an IGBT device with a carrier storage layer clamped by a diode, and its cell structure is as follows Figure 5 As shown, the difference between its cell structure and that of Embodiment 1 is that n-1 N-type semiconductor isolation regions 19 are arranged in the P-type base region 5 located on the other side of the first deep groove, n≥2, and the following The surface is in contact with the N-type carrier storage layer 4, and the N-type semiconductor isolation region 19 separates the P-type base region on this side into n P-type sub-regions, and an N-type heavily doped sub-region is arranged in each P-type sub-region. The miscellaneous semiconductor region 6, the N-type heavily doped semiconductor region 6 and the respective P-type subregions form a PN junction diode, and a P-type heavily doped semiconductor region is also provided in the P-type subregion of each PN junction diode. Region 22 is used as the anode ohmic contact region of the diode,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More