Silicon carbide MOSFET device integrated with SBD and preparation method thereof

A silicon carbide and device technology, applied in the field of silicon carbide MOSFET devices and their preparation, can solve the problems of high turn-on voltage drop and reverse recovery loss, unfavorable to the reliability of silicon carbide devices, increased reverse bias leakage current, etc. , to increase reliability, reduce impact, and improve power density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] The implementation of the present invention will be described in detail below in conjunction with the accompanying drawings and examples, so as to fully understand and implement the process of how to apply technical means to solve technical problems and achieve technical effects in the present invention. It should be noted that, as long as there is no conflict, each embodiment and each feature in each embodiment of the present invention can be combined with each other, and the formed technical solutions are all within the protection scope of the present invention.

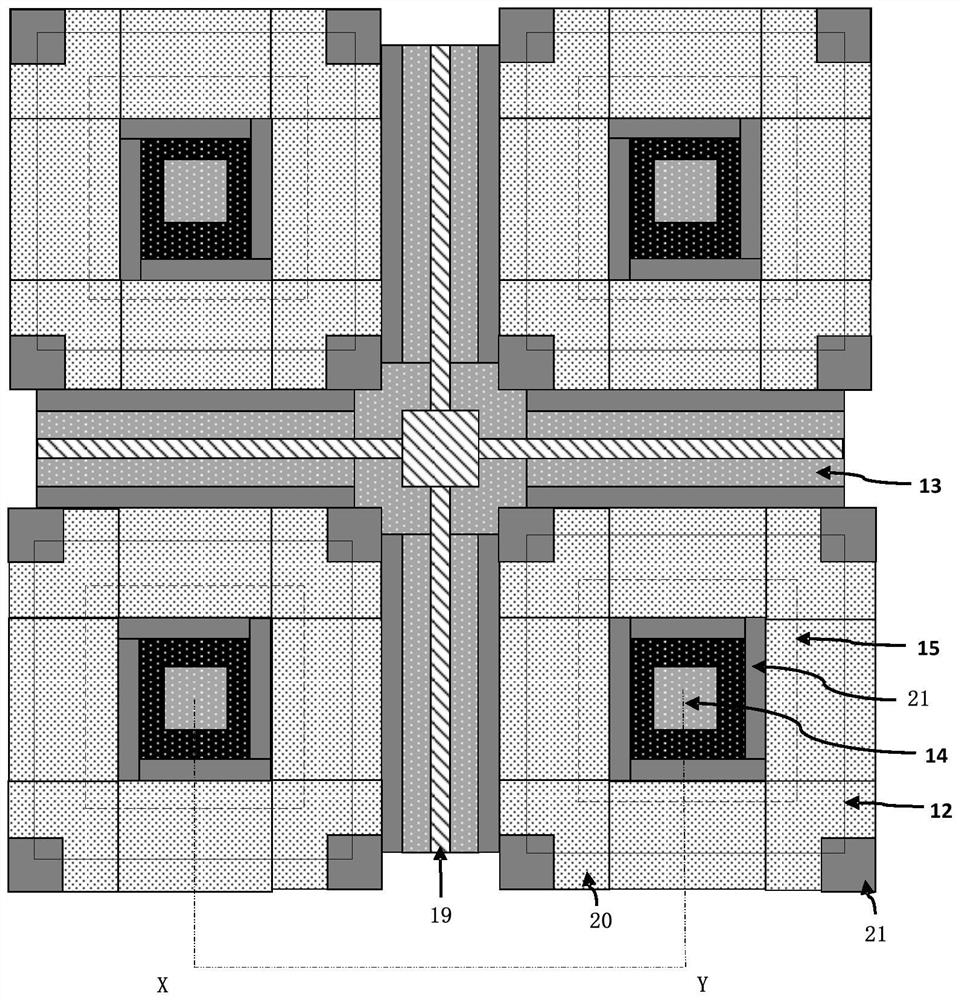

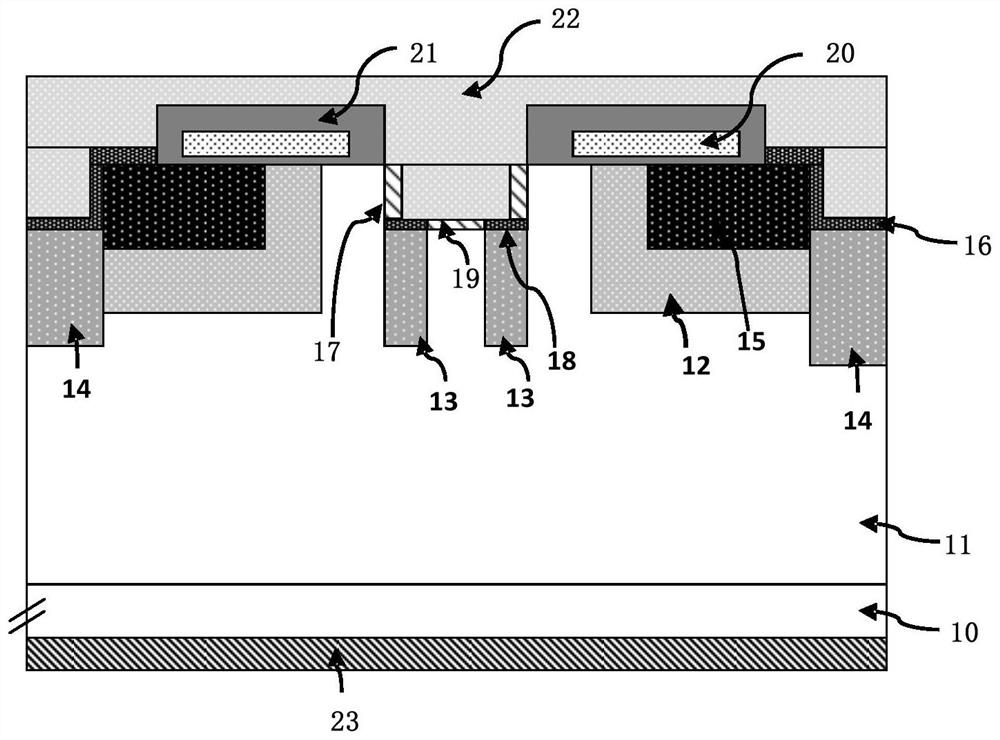

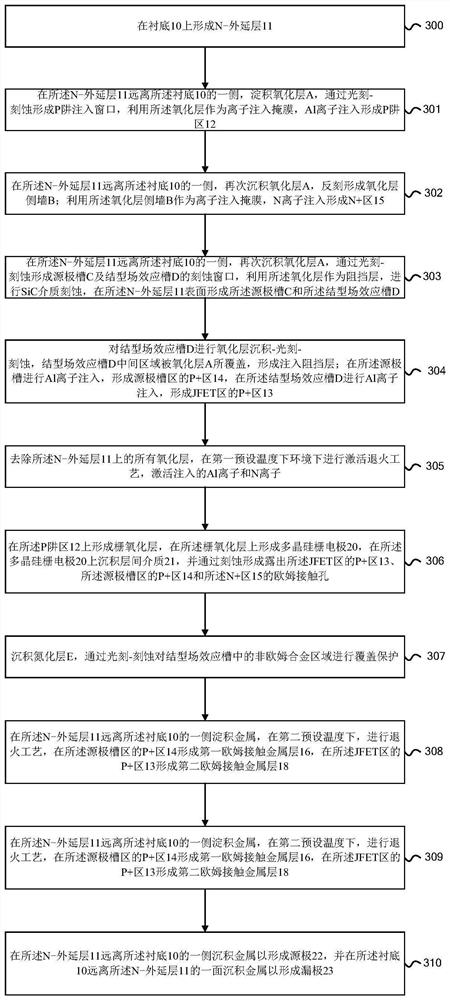

[0053] figure 1 It is a top view of the silicon carbide MOSFET device integrating SBD of the present invention, figure 2 for figure 1 Cross-sectional view in the X-Y direction. Such as Figure 1-Figure 2 As shown, the SBD-integrated silicon carbide MOSFET device of this embodiment may include several cell structures. The cellular structure includes a substrate 10, an N-epitaxial layer 11 formed on the s...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More