Small-area high-linearity shaping circuit

A technology for forming circuits and high linearity, applied in electrical components, power oscillators, etc., can solve problems such as poor linearity, achieve the effect of reducing chip area, ensuring constant gain, and improving linearity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

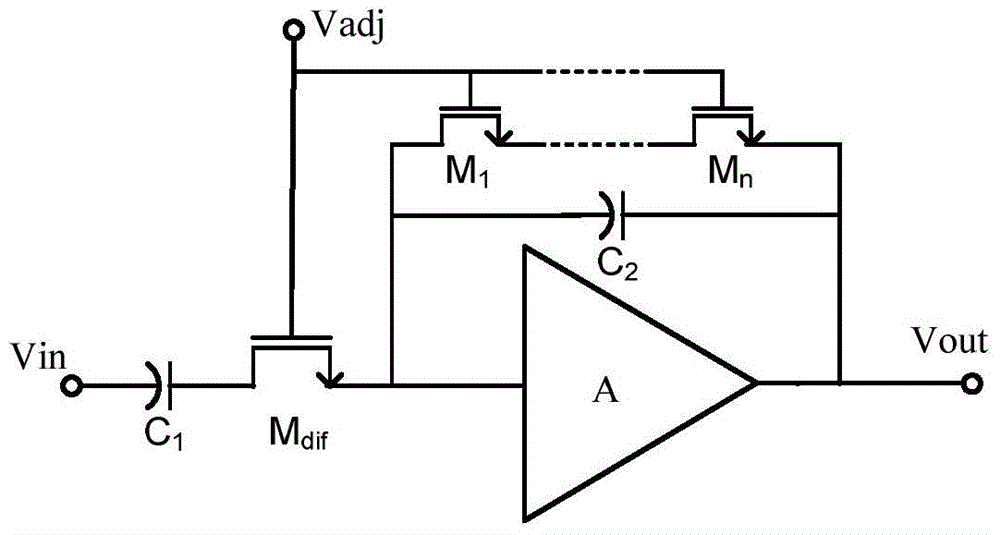

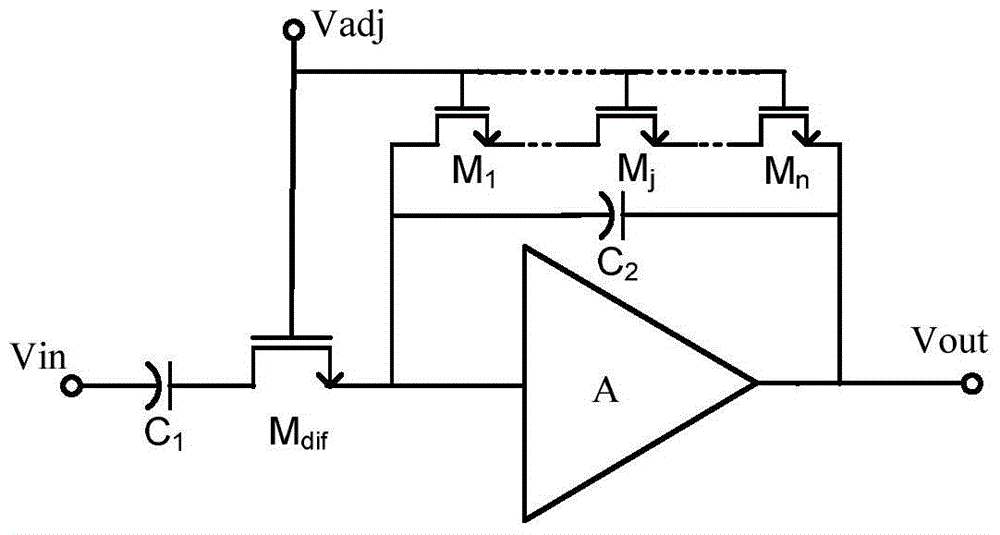

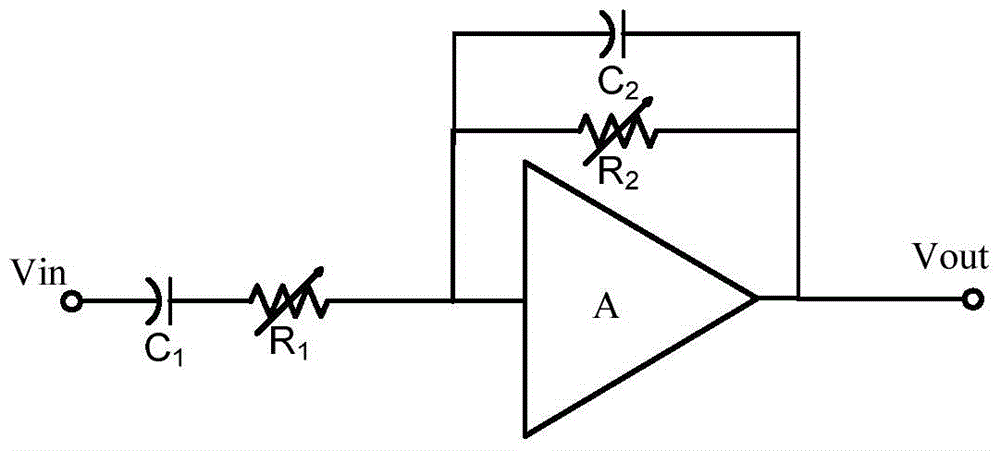

[0018] The following examples refer to Figure 1-2 .

[0019] The small-area high-linearity forming circuit of the present invention includes a capacitor C 1 , capacitance C 2 and operational amplifier A, also includes an NMOS transistor M dif and n NMOS transistors M 1 ~ M n . Capacitance C 1 One end of the forming circuit is connected to the input terminal Vin, and the capacitor C 1 The other end of the NMOS transistor M dif The drain of the NMOS transistor M dif The sources of are respectively connected to the input terminal of the operational amplifier A, n NMOS transistors M 1 ~ M n Drain and capacitance C after series connection 2 one end. The output terminal of the operational amplifier A, n NMOS transistors M 1 ~ M n The source and capacitor C after series connection 2 The other end is connected to the output end Vout of the shaping circuit. NMOS transistor M dif and NMOS transistor M 1 ~ M n The gates of are connected to the time adjustment control ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More