A Current Enhanced Lateral Insulated Gate Bipolar Transistor

A bipolar transistor and current enhancement technology, applied in circuits, electrical components, semiconductor devices, etc., can solve problems such as drop in withstand voltage, drop in latch-up suppression capability, increase in device turn-off time, etc., to improve the on-current capability , Improve the latch-up suppression ability, improve the effect of on-current density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

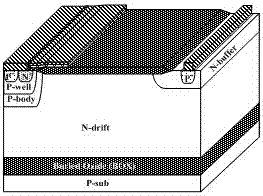

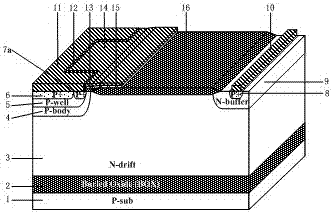

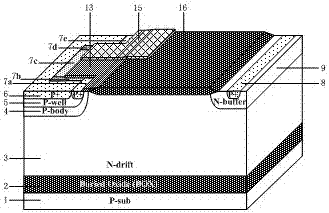

[0030] Combine below figure 2 , image 3 , to describe the present invention in detail, a current-enhanced lateral insulated gate bipolar transistor, comprising: a P-type substrate 1, a buried oxygen 2 is arranged on the P-type substrate 1, and an N-type substrate is arranged on the buried oxygen 2 The drift region 3 is provided with a P-type body region 4 and an N-type buffer region 9 on both sides of the N-type drift region 3, and a heavily doped P-type collector region 8 is arranged in the N-type buffer region 9. Anode metal 10 is connected to the miscellaneous P-type collector region 8, and a field oxide layer 16 is arranged above the N-type drift region 3. One side of the boundary of the field oxide layer 16 is above the N-type buffer zone 9, and the other side is above the N-type buffer zone 9. One side boundary is in contact with the P-type body region 4 and is a straight boundary, a P-type well region 5 is arranged in the P-type body region 4, and a heavily doped P-t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More