Discrete power mos field effect transistor and manufacturing method thereof

A technology of field effect tube and manufacturing method, which is applied in the field of discrete power mos field effect tube and its manufacturing, can solve the problems that P+ contact area cannot be formed, P+ injection cannot be formed, and is not easy to form, so as to improve the avalanche breakdown tolerance, The effect of reducing parasitic P+ resistance and simplifying the manufacturing process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

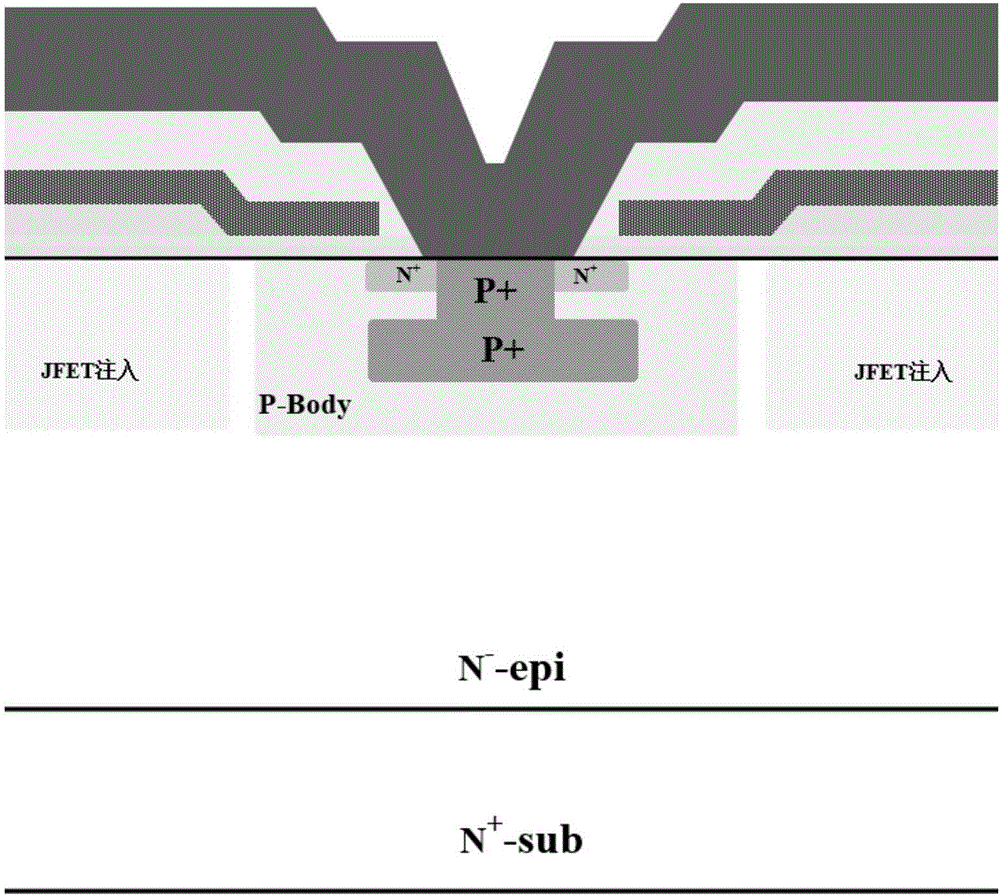

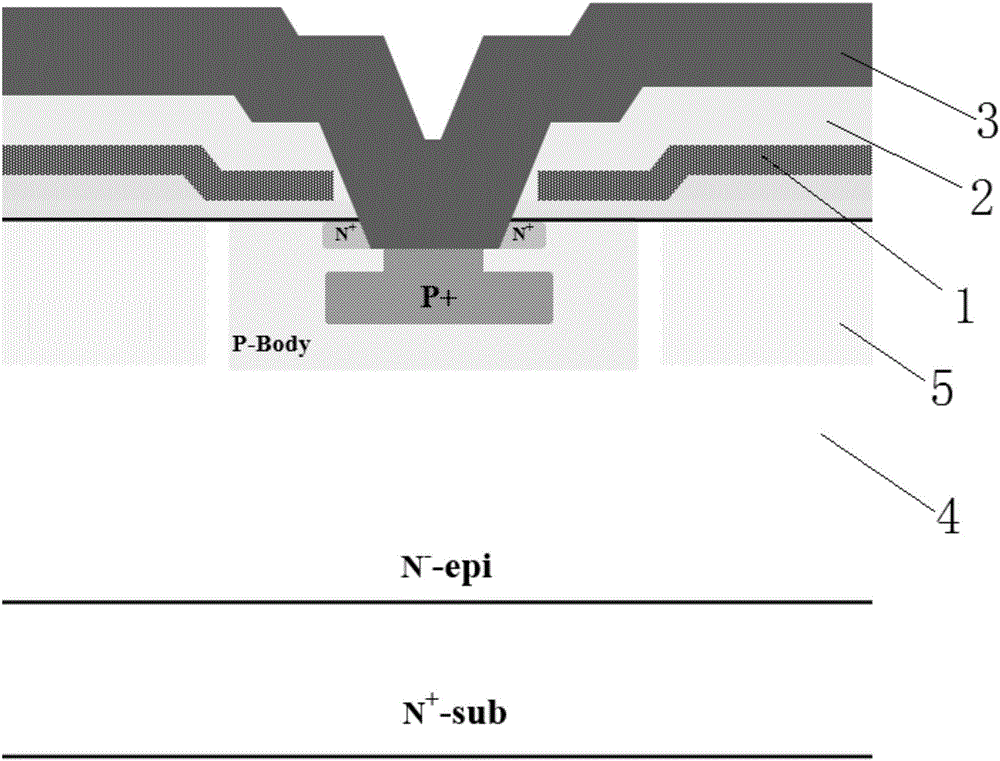

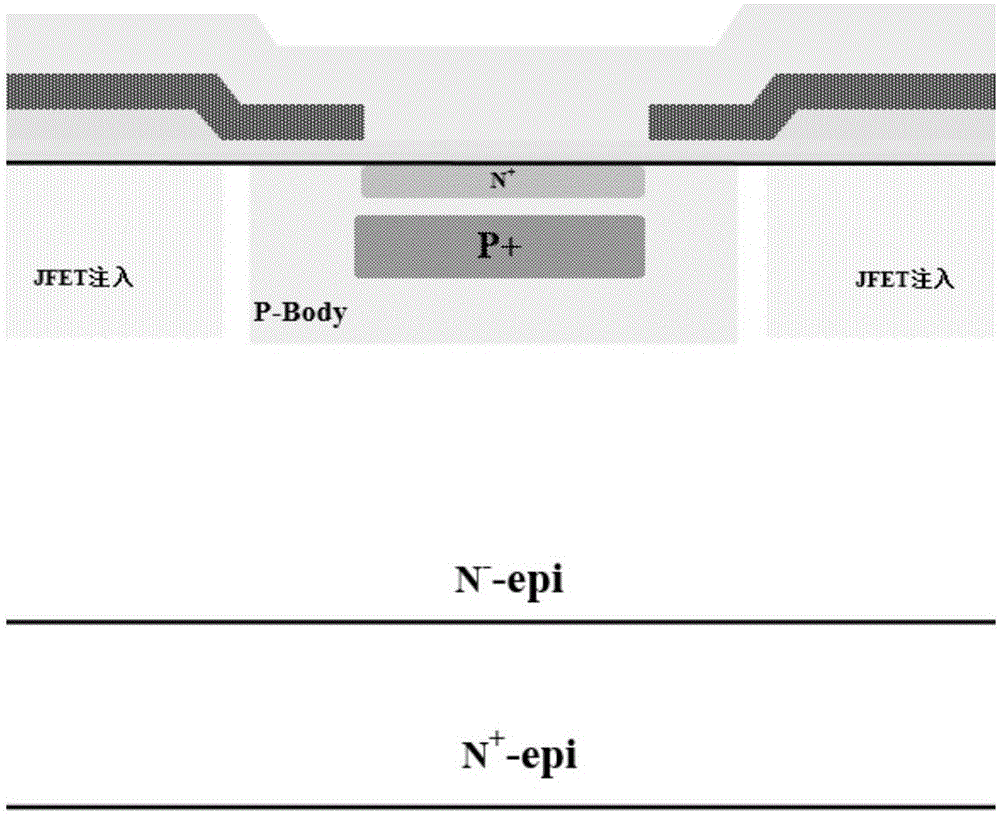

[0027] The present invention is described in further detail below in conjunction with accompanying drawing:

[0028] A method for manufacturing a discrete power MOS field effect transistor, specifically comprising the following steps:

[0029] Step 1), first oxidizing the outer side of the epitaxial layer of the substrate, and then performing a terminal process to form a terminal;

[0030] Specifically, the outer side of the epitaxial layer of the substrate is oxidized, and then the terminal ring is sequentially subjected to photolithography, terminal ring implantation, terminal ring advancement, and field oxidation to form a terminal;

[0031] Wherein the substrate is an N-type substrate;

[0032] Step 2), then forming a source region in the epitaxial layer;

[0033] In the epitaxial layer where the source region needs to be formed, the photolithography of the active region is performed, and then the active region is etched, and then JFET implantation and gate oxide growth ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More