Collector back side structure of insulated gate type bipolar transistor

A bipolar transistor and insulated gate technology, applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of reducing the effective injection of back collector holes, unfavorable device conduction voltage drop, and reducing the efficiency of back injection, etc., to achieve The effect of reducing the risk of debris, reducing injection efficiency, and improving switching performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

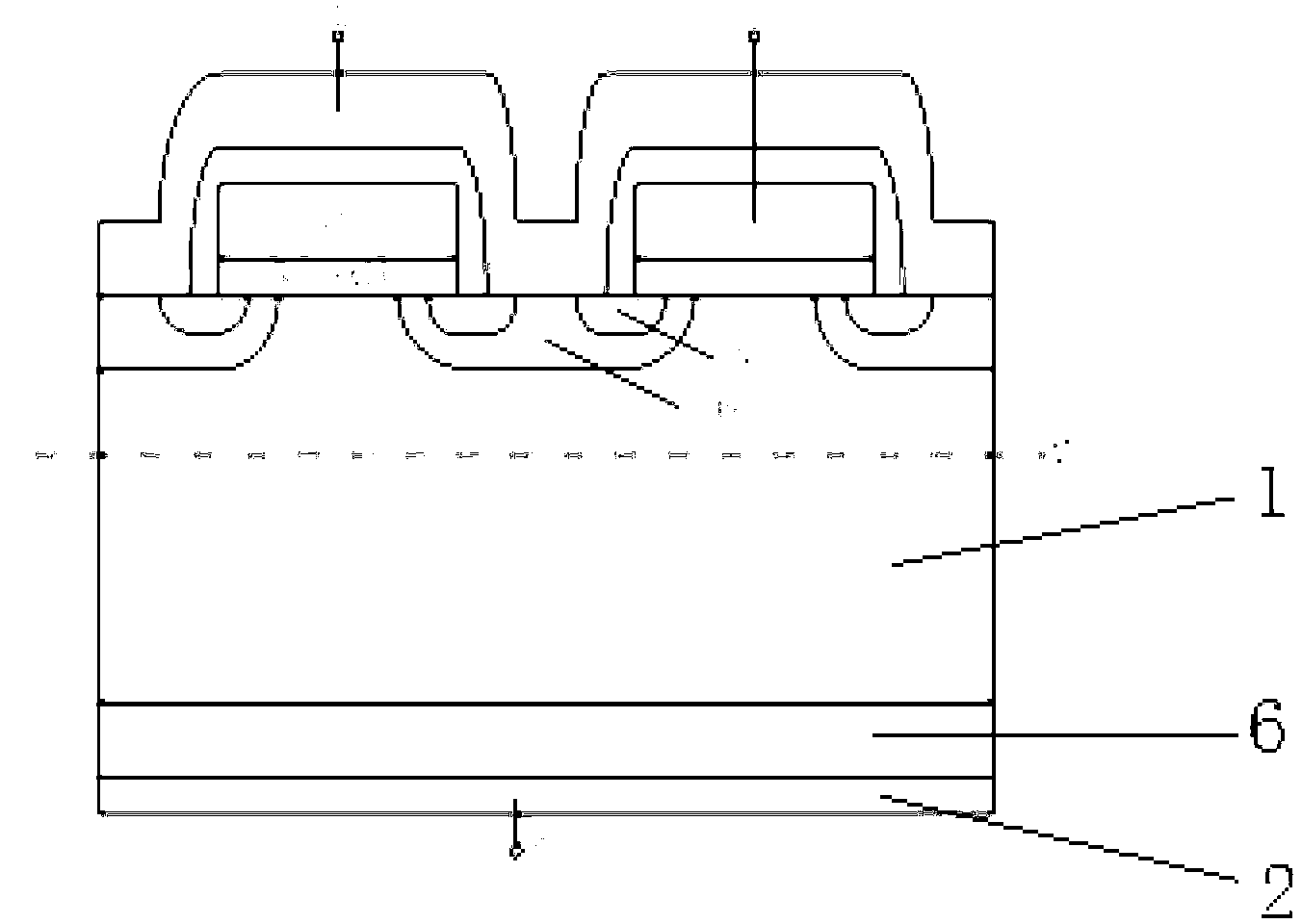

[0020] A collector back structure of an insulated gate bipolar transistor, which includes a silicon substrate layer 1 and a collector metal layer 2, and has high-concentration implantation regions 3 and low-concentration implantation regions 4 distributed at intervals on the backside of the silicon substrate layer 1 , and the thickness of the silicon substrate layer 1 corresponding to the high-concentration implantation region 3 is smaller than the thickness of the silicon substrate layer 1 corresponding to the low-concentration implantation region 4 .

[0021] Such as figure 2 As shown, depending on the structure of the front side, the back side is etched and forms different implant distributions. For the right under the implantation of the front P+ region, it is slightly thinner than other places by etching, and the thickness is determined according to the actual situation. For the lower part of the JFET area, no treatment is performed or the epitaxy method is used to make...

Embodiment 2

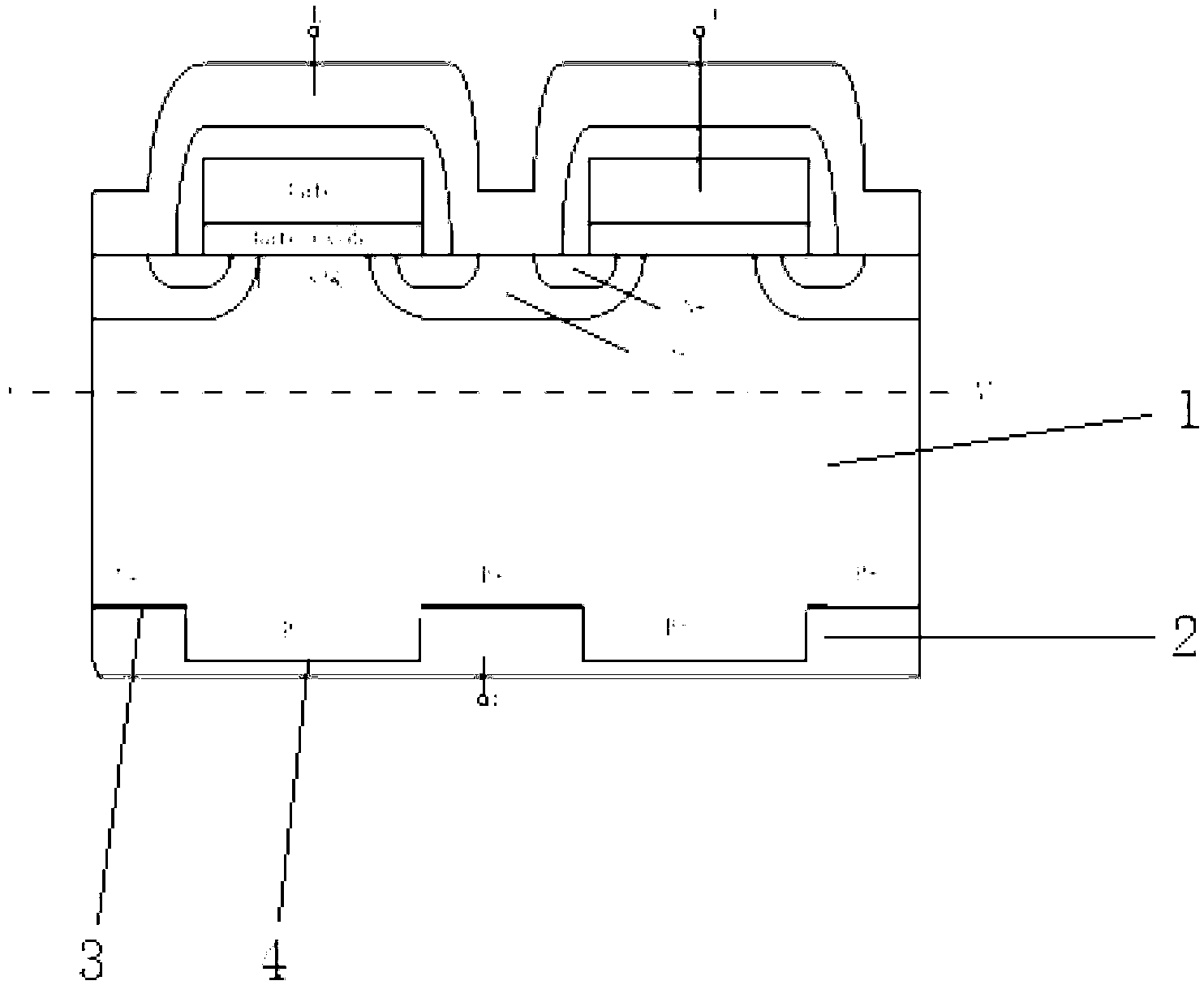

[0023] A collector back structure of an insulated gate bipolar transistor, which includes a silicon substrate layer 1 and a collector metal layer 2, and has high-concentration implantation regions 3 and low-concentration implantation regions 4 distributed at intervals on the backside of the silicon substrate layer 1 , and the thickness of the silicon substrate layer 1 corresponding to the high-concentration implantation region 3 is smaller than the thickness of the silicon substrate layer 1 corresponding to the low-concentration implantation region 4, and a buffer layer 5 is provided between the silicon substrate layer 1 and the collector metal layer 2 .

[0024] For the collector back structure of PT-type IGBT and the collector back structure of FS-type IGBT, such as image 3 shown.

Embodiment 3

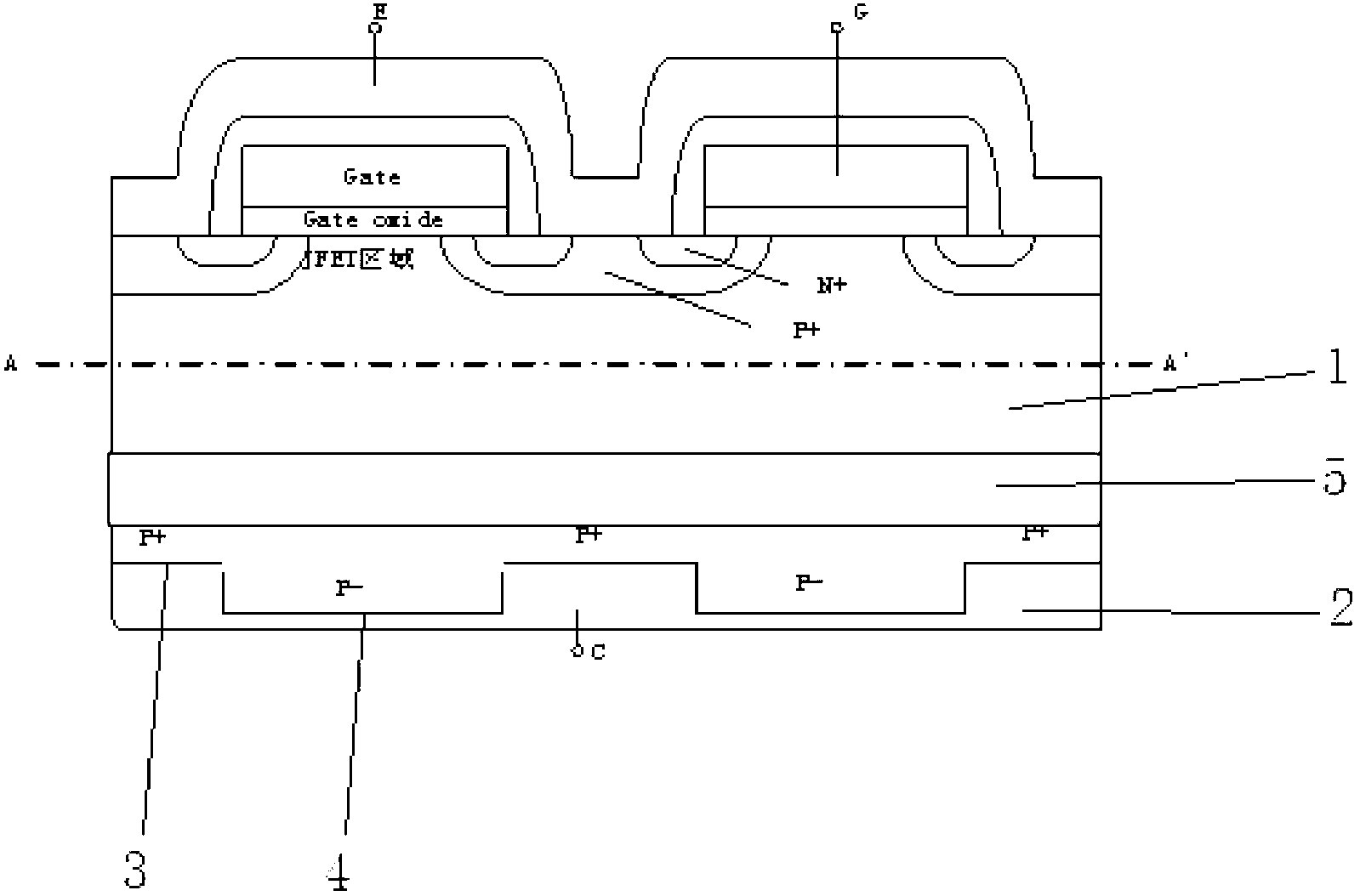

[0026] A collector back structure of an insulated gate bipolar transistor, which includes a silicon substrate layer 1 and a collector metal layer 2, and has high-concentration implantation regions 3 and low-concentration implantation regions 4 distributed at intervals on the backside of the silicon substrate layer 1 , and the thickness of the silicon substrate layer 1 corresponding to the high-concentration implantation region 3 is smaller than the thickness of the silicon substrate layer 1 corresponding to the low-concentration implantation region 4 .

[0027] For the back structure of the collector of the IGBT whose front is a trench type structure, such as Figure 4 shown.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More