Silicon-on-insulator transverse insulated gate bipolar transistor with low saturation current

A technology of bipolar transistors and silicon-on-insulators, applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of reduced injection efficiency, complex drive circuits, and increased conduction voltage drop, and achieve increased base drive current. The effect of large, increased number of holes, and large linear current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

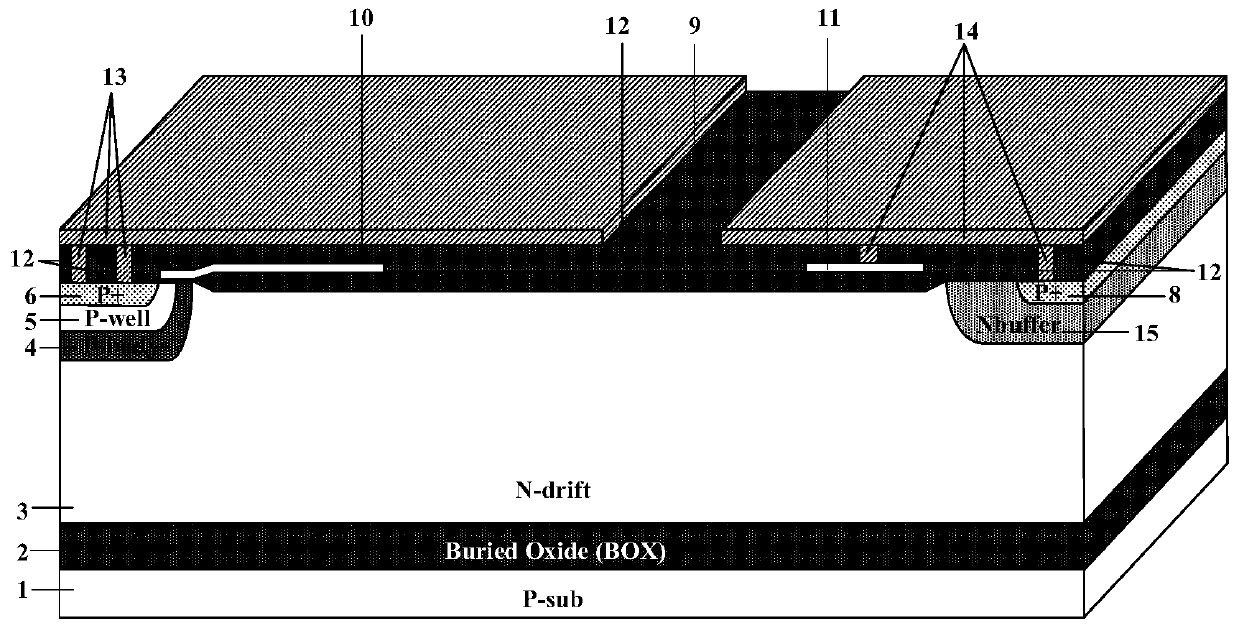

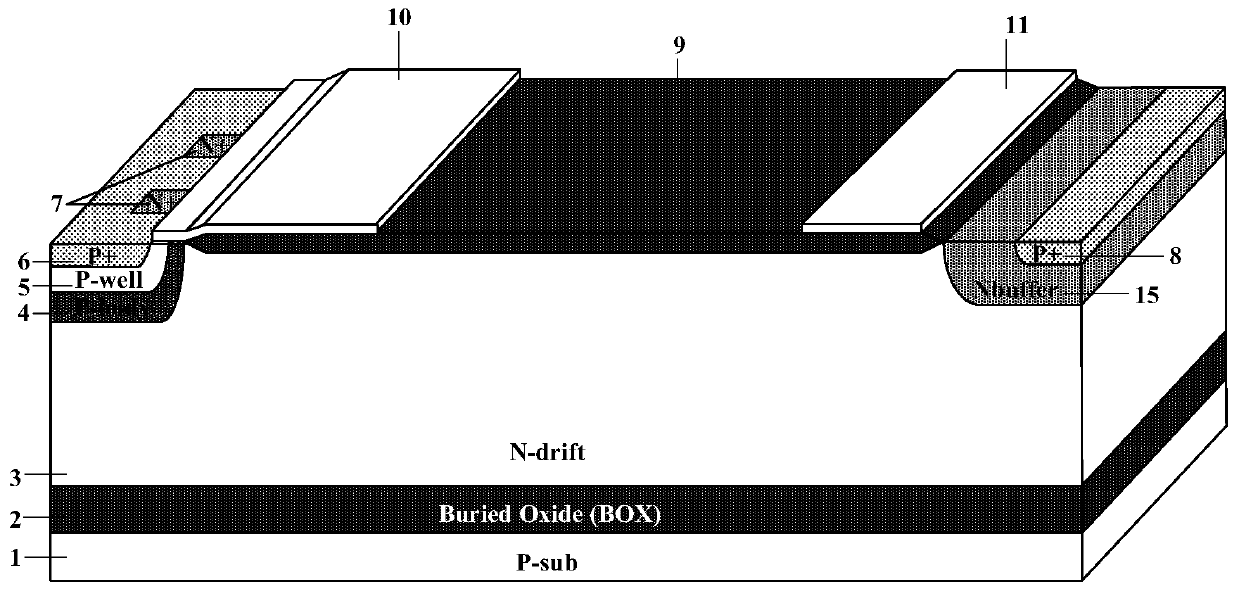

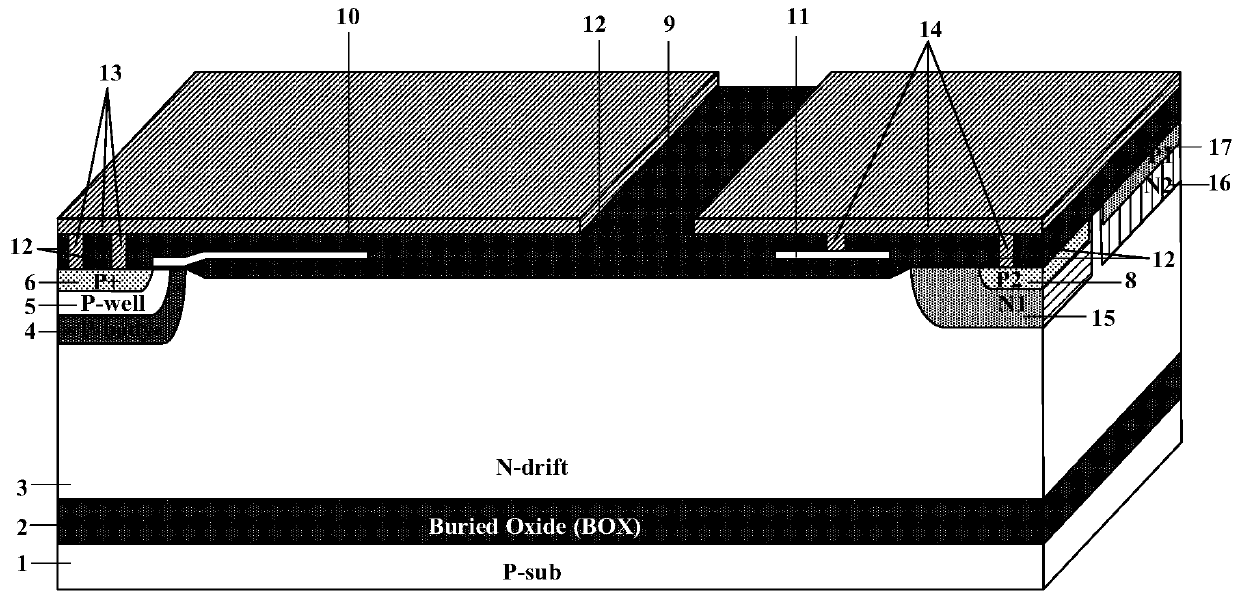

[0022] Combine below image 3 and Figure 4 , the present invention is described in detail, a silicon-on-insulator lateral insulated gate bipolar transistor with low saturation current, comprising: a P-type substrate 1, a buried oxide layer 2 is arranged above the P-type substrate 1, and a buried oxide layer is formed on the buried oxide layer An N-type drift region 3 is provided above 2, and a P-type body region 4, a field oxygen layer 9 and a collector region are arranged below the emitter side of the upper surface in the N-type drift region 3, and the field oxygen layer 9 is located in the P-type body Between the region 4 and the collector region, a connected P well 5 is provided in the P-type body region 4, a P-type emitter region 6 is arranged in the P-type body region 5, and an N-type emitter region is arranged on the P-type emitter region 6. The emitter region 7 is provided with an oxide layer 12 above the P-type body region 4, the P well 5, the P-type emitter region 6...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More