Method for implementing well division construction in super-high density slot type power device design

A high-density, well-splitting technology, used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of difficult to control R&D costs and R&D risks, long development cycles, and difficult to control thermal processes, so as to shorten the development cycle. , the effect of reducing R&D costs and easy process integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention proposes an ultra-high density (>5×10 7 Cell / cm 2 ) A new method for realizing the sub-well structure 21 in the design of trench-type power devices effectively solves the contradiction between the realization of the sub-well structure 21 and the ultra-high density design, and is fully compatible with traditional trench-type semiconductor processes and is easy to integrate.

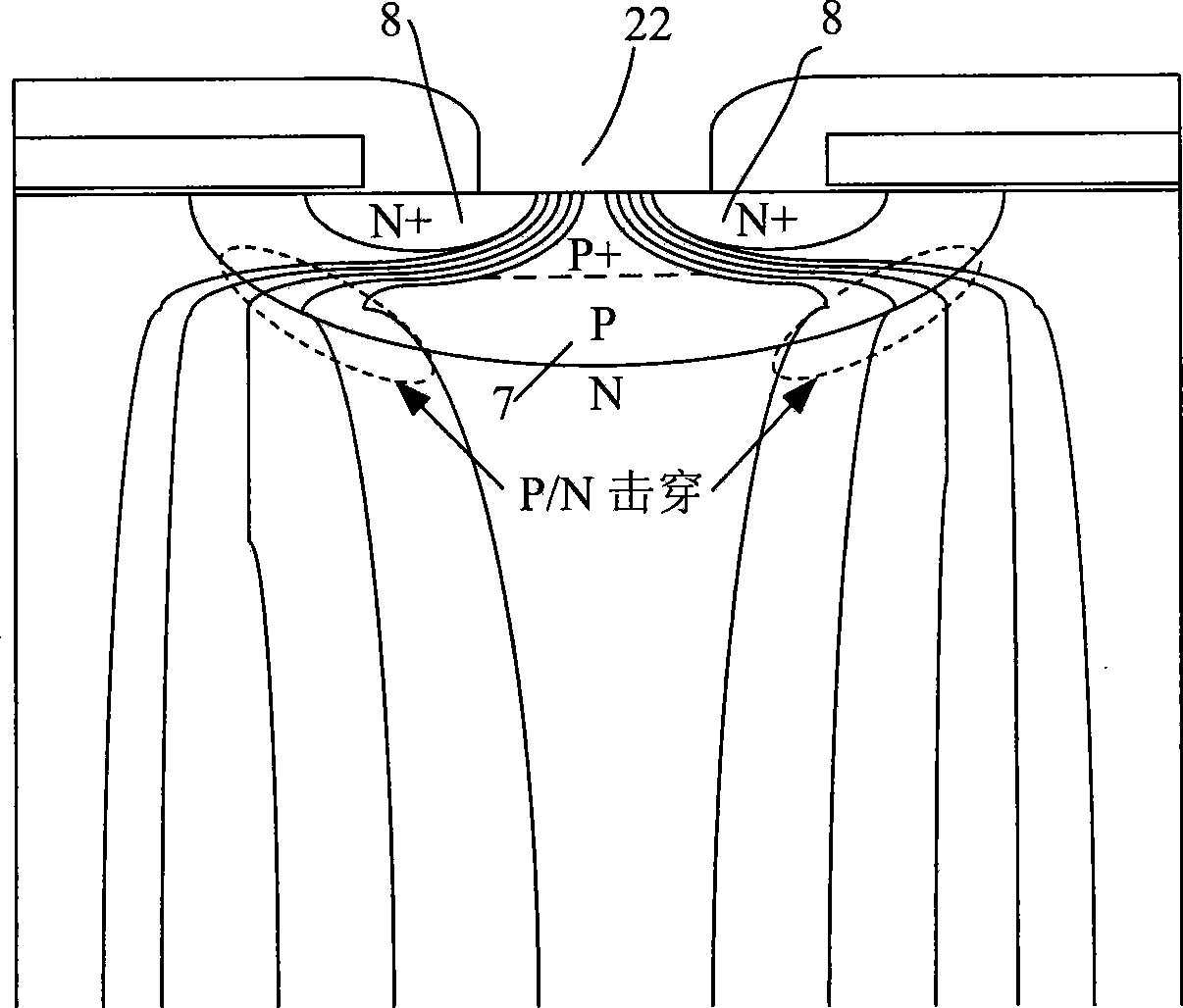

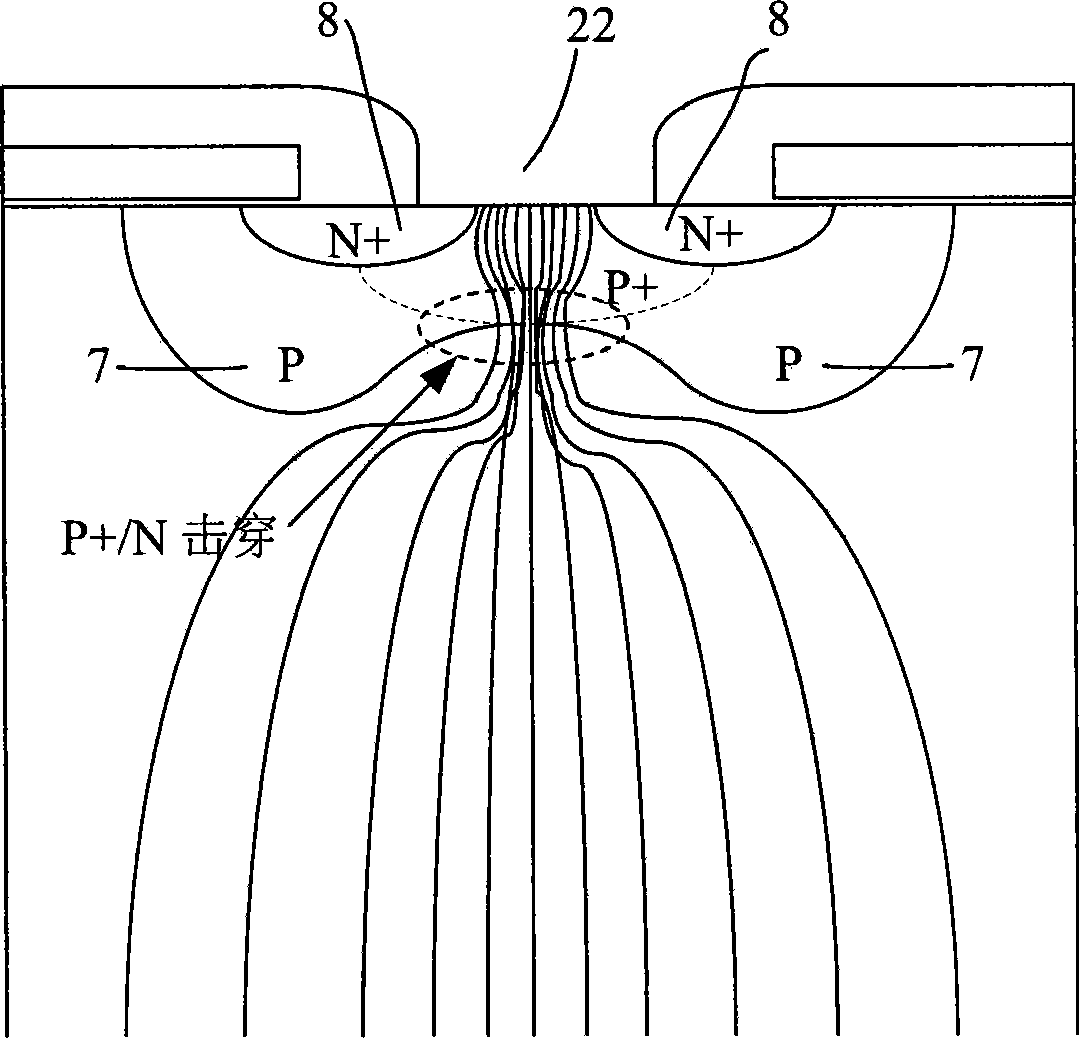

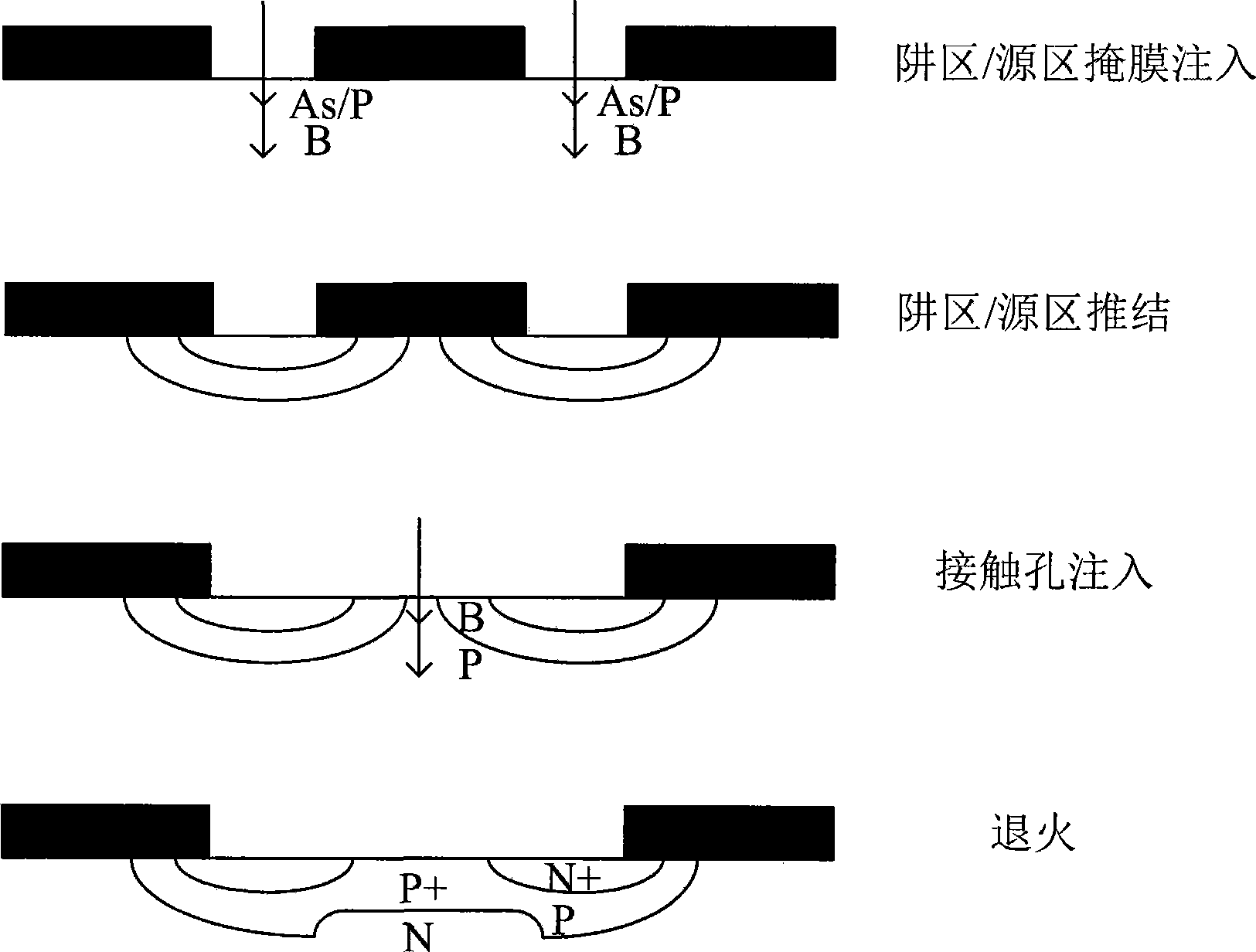

[0024] FIG. 4 describes the key process of implementing the sub-well structure 21 in the design of ultra-high-density trench power devices. Figure 4(a) is trench photolithography, and the photolithographic pattern is transferred to the silicon dioxide 3 / silicon nitride 4 stack as a strong mask for subsequent trench etching; in Figure 4(b), sequentially Trench etching, sacrificial oxide layer, gate oxide layer 5, polycrystalline 6 deposition, and polycrystalline etch-back (Poly Etch-back); in Figure 4(c), well region ion implantation 12, diffusion push junction and Ion implant...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More