Patents

Literature

66results about How to "Easy process integration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

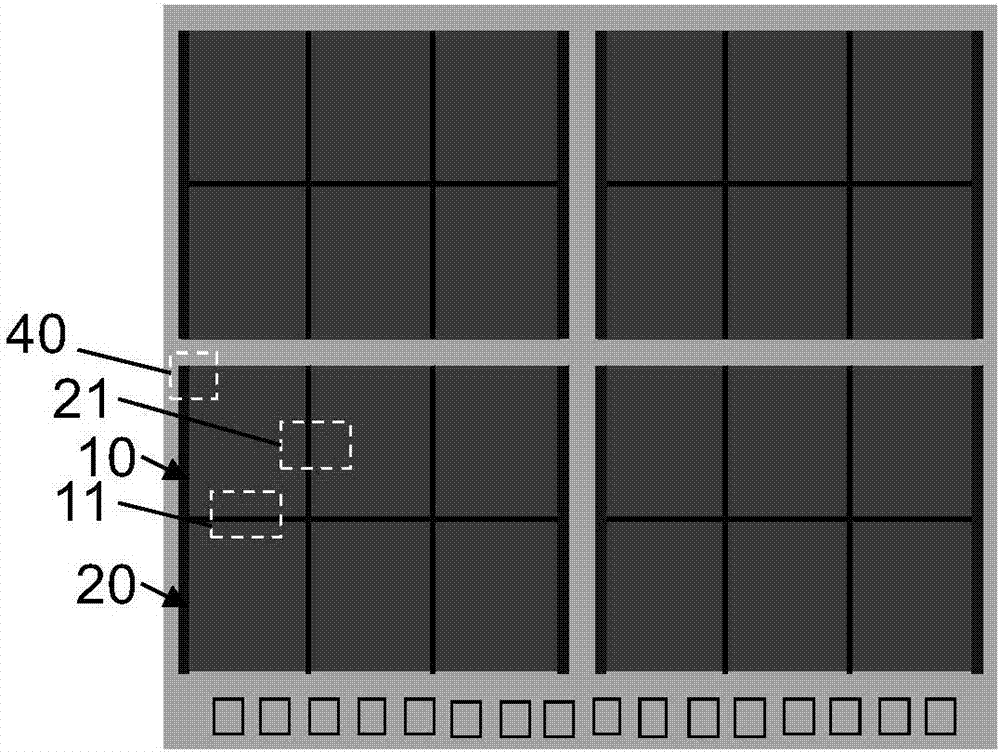

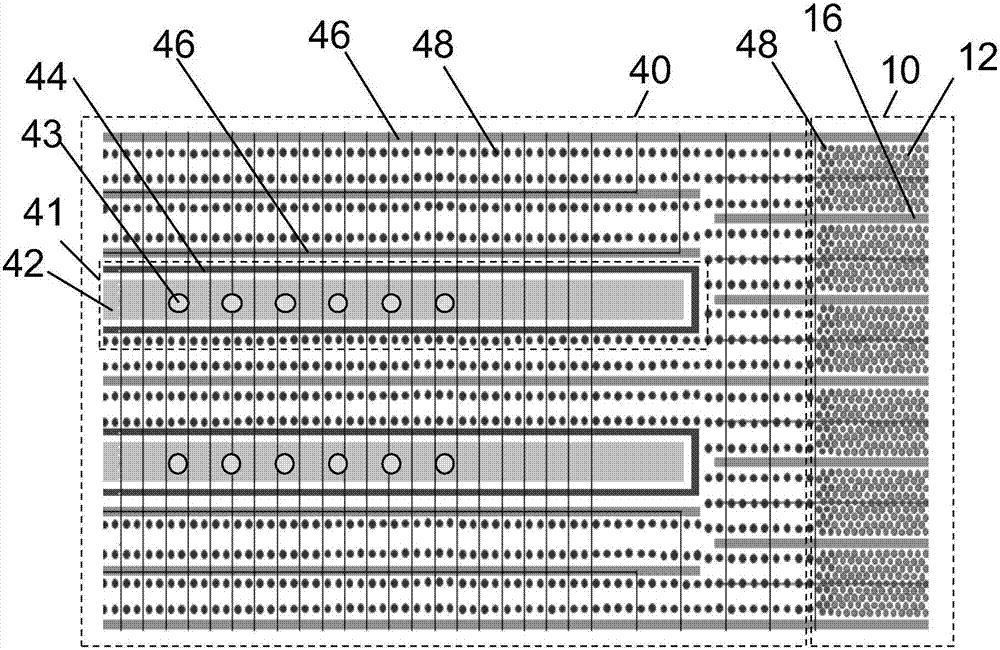

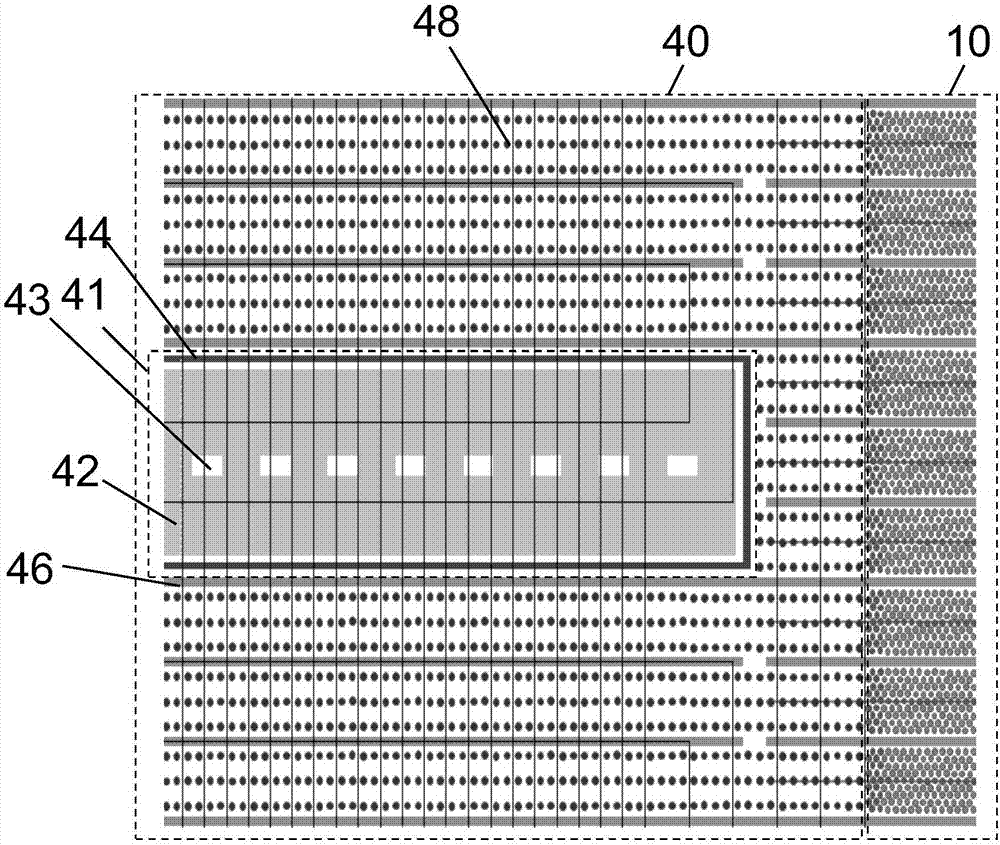

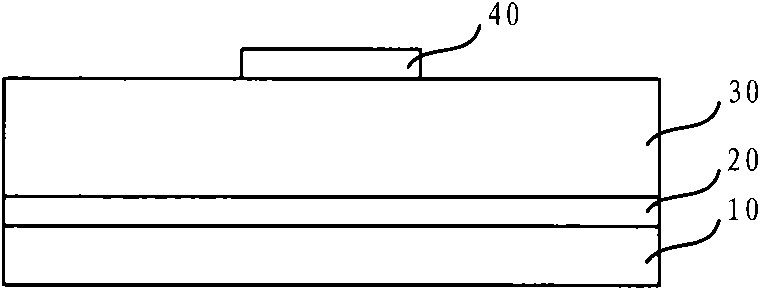

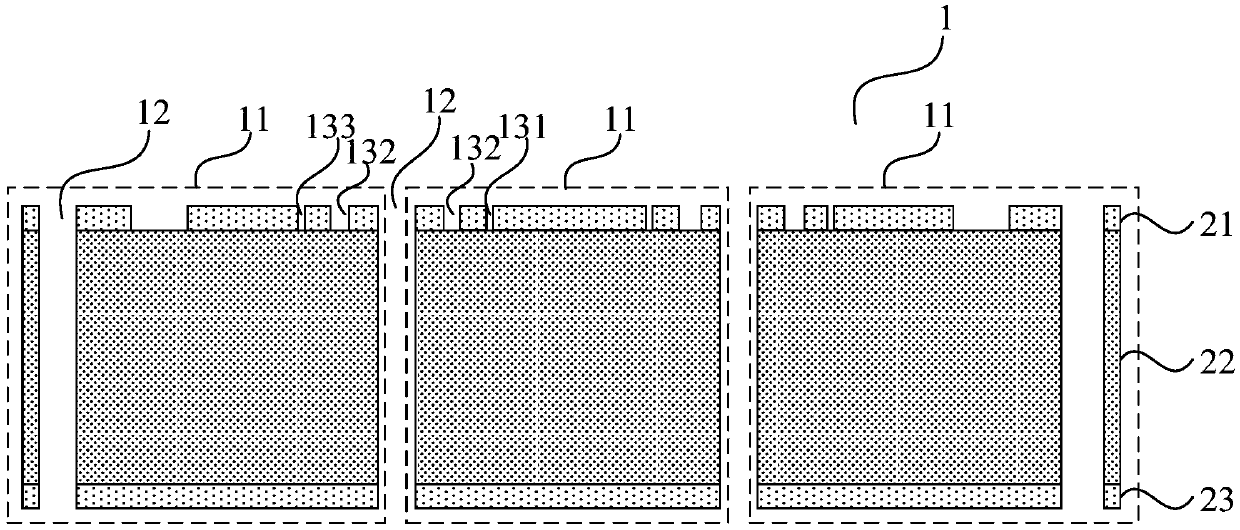

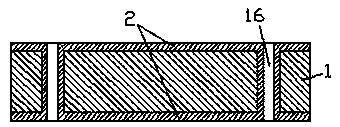

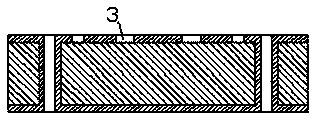

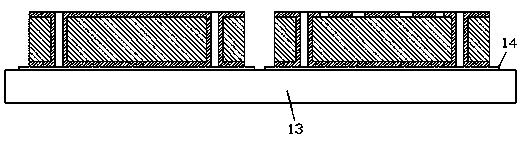

3D NAND memory device and manufacturing method therefor

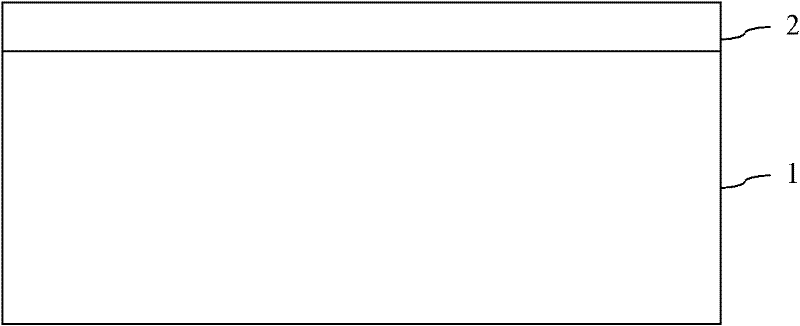

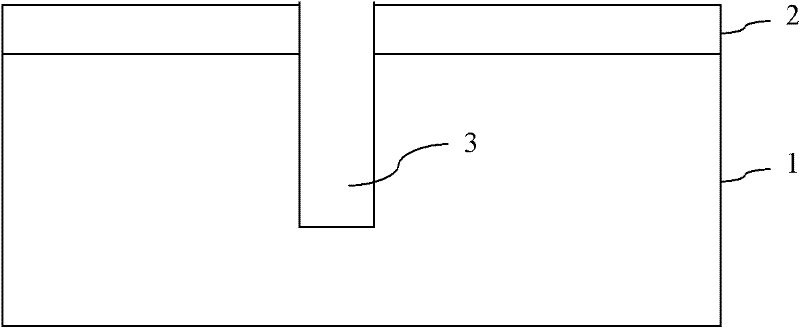

ActiveCN106920794AEasy process integrationFirmly connectedSolid-state devicesSemiconductor devicesOxideContact hole

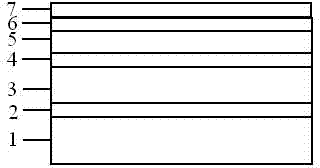

The invention provides a 3D NAND memory device. The memory device comprises a substrate, a first memory region, a sub step region, run-through contact holes, and grid line gaps, wherein the first memory region is arranged on the substrate; the first memory region comprises a word line stacking layer and channel holes in the word line stacking layer; the side wall of the word line stacking layer adopts a step structure; the sub step region is arranged in the step structure; the sub step region is a stacked layer of an oxide layer and a nitride layer; the sub step region extends to the edge of the step structure in a word line direction; an insulating layer is arranged on the side wall, connected with the step structure, of the sub step region; the run-through contact holes are formed in the sub step region; and the grid line gaps are formed in the step structure outside the sub step region. By virtue of the run-through contact holes with the structure, connection between the memory device and a CMOS chip can be realized conveniently, and the memory device can be integrated with the existing process easily; particularly, when the thickness of the stacking layer is constantly increased, a step of etching metal stacking to form the run-through contact holes is not needed, so that realization of the process and constant improvement of the integration degree can be facilitated.

Owner:YANGTZE MEMORY TECH CO LTD

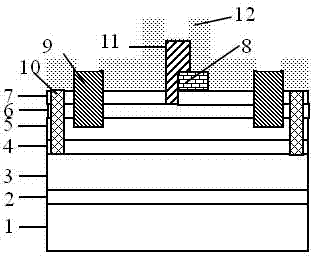

Preparation method of low noise GaN HEMT device

ActiveCN103779208AImprove pressure resistanceImprove stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionLow noise

The invention provides a preparation method of a low noise GaN HEMT device. The preparation method comprises the steps that 1) an AlGaN / GaN heterojunction material with a component gradient back barrier grows; 2) a medium field plate is prepared; 3) ohmic contact is prepared; 4) an isolation region of the device is formed; 5) a gamma type gate of a TaN radical is formed through a positive photoresist stripping method; 6) by using a plasma deposition method, a Si3N4 / SiO2 / Si3N4 multilayer surface passivation medium is deposited on the surface of a sample; and 7) through a plasma etching method, dielectric materials on a source drain and a gate electrode are removed, so as to form a test window. The preparation method has the advantages that 1) a structure is compatible with power GaN HEMT, which is conductive to process integration; 2) voltage resistance of the device is effectively improved, and the degradation of frequency characteristics is prevented; 3) the device's ability to bear high input power is improved; and 4) the effect of a passivation process on the device frequency is reduced, and at the same time the gate stability is improved.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

Germanium nanopoint/silicon nanowire array structure thin film and preparation thereof

ActiveCN101486439AFirmly connectedImprove lighting efficiencyIndividual molecule manipulationGermananeSilicon nanowires

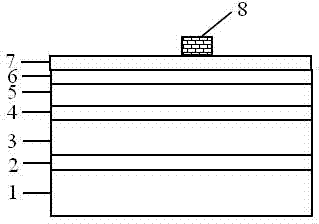

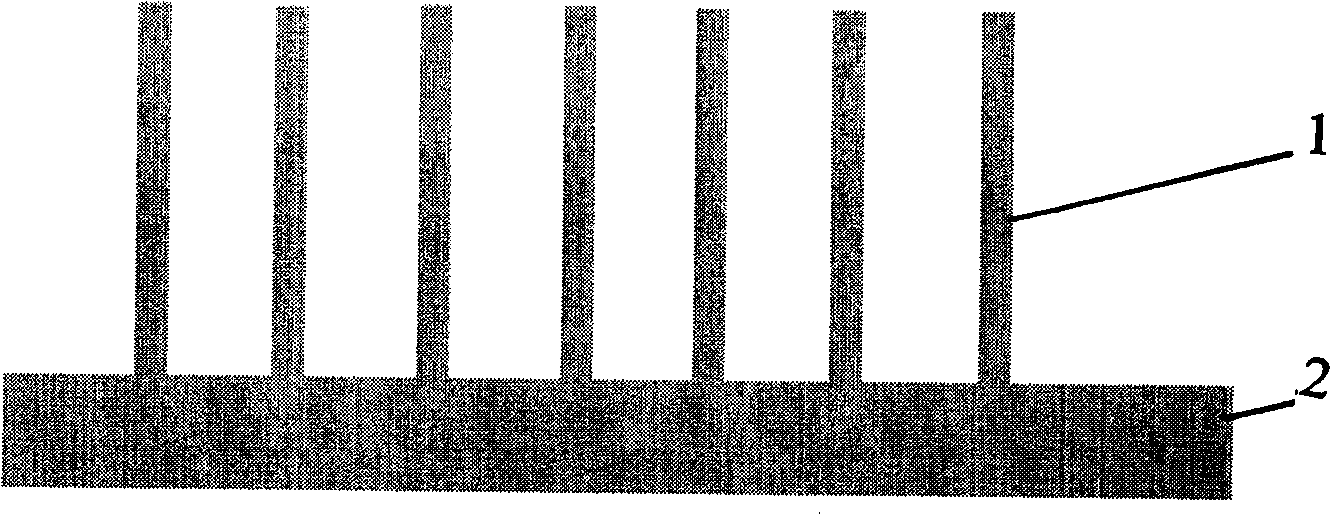

The invention provides a germanium nanometer point / silicon nanometer line array structural film, mainly consisting of silicon nanometer lines and germanium nanometer points distributed on the silicon nanometer lines of the silicon nanometer line array. The preparing method thereof mainly comprises steps as follows: with P or N type single crystal silicon and poly-silicon as raw materials, preparing large silicon nanometer line arrays by utilizing an etching method; and then applying low-pressure chemical vapor deposition technique and using germane as the gas source to prepare germanium points on substrates of the large silicon nanometer line arrays. With more layers of germanium nanometer points and high optical efficiency, the large-scale germanium nanometer point / silicon nanometer line array structural film brings great benefits to the further production of high-efficiency optoelectronic devices. With the advantages of low cost of manufacturing equipment, high production efficiency and greatly reduced cost and the like, the production method thereof is easy to be combined with the existing techniques of silicon film devices, and is considered as an optimized method for producing germanium nanometer point / silicon nanometer line array structural films.

Owner:施毅

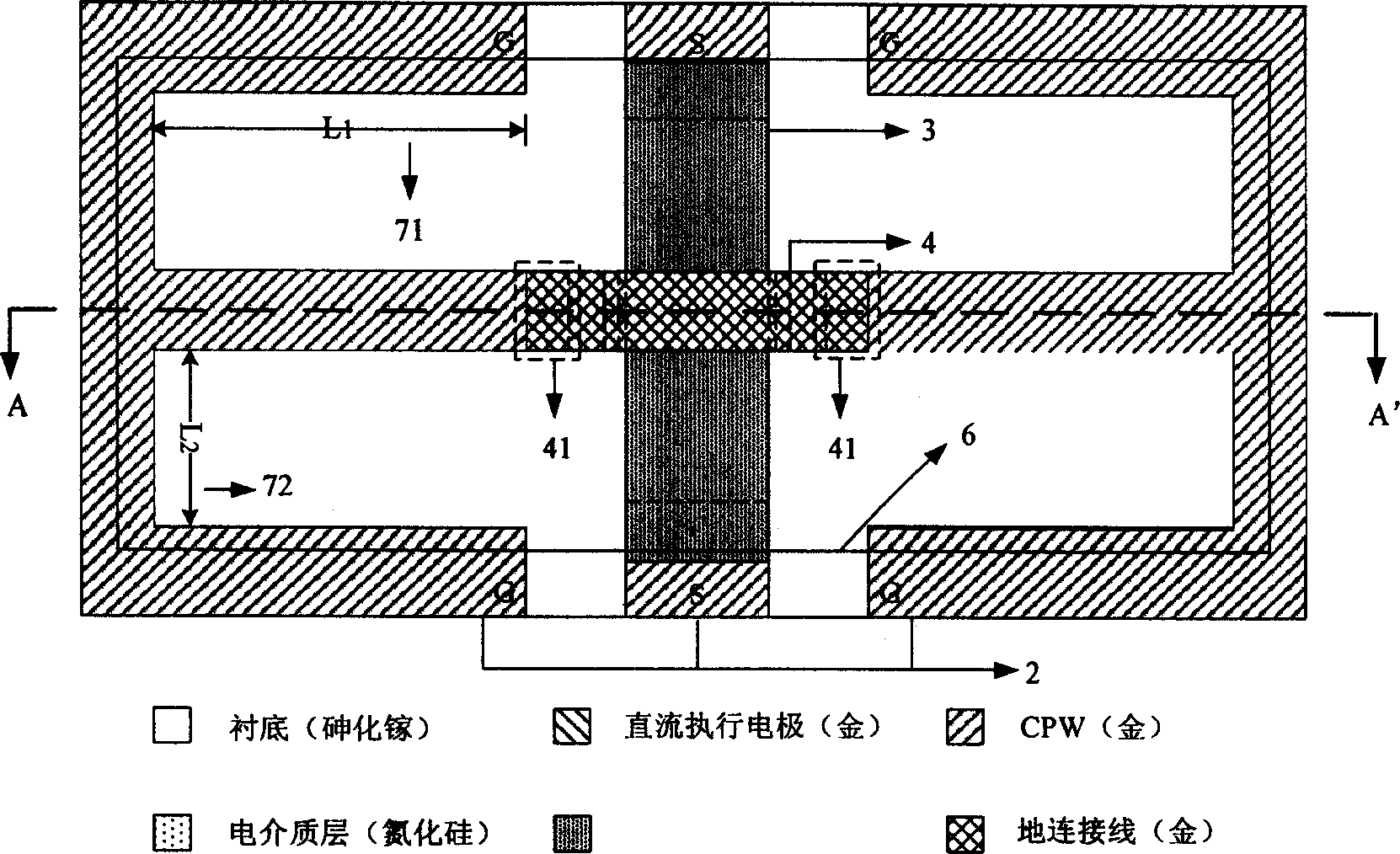

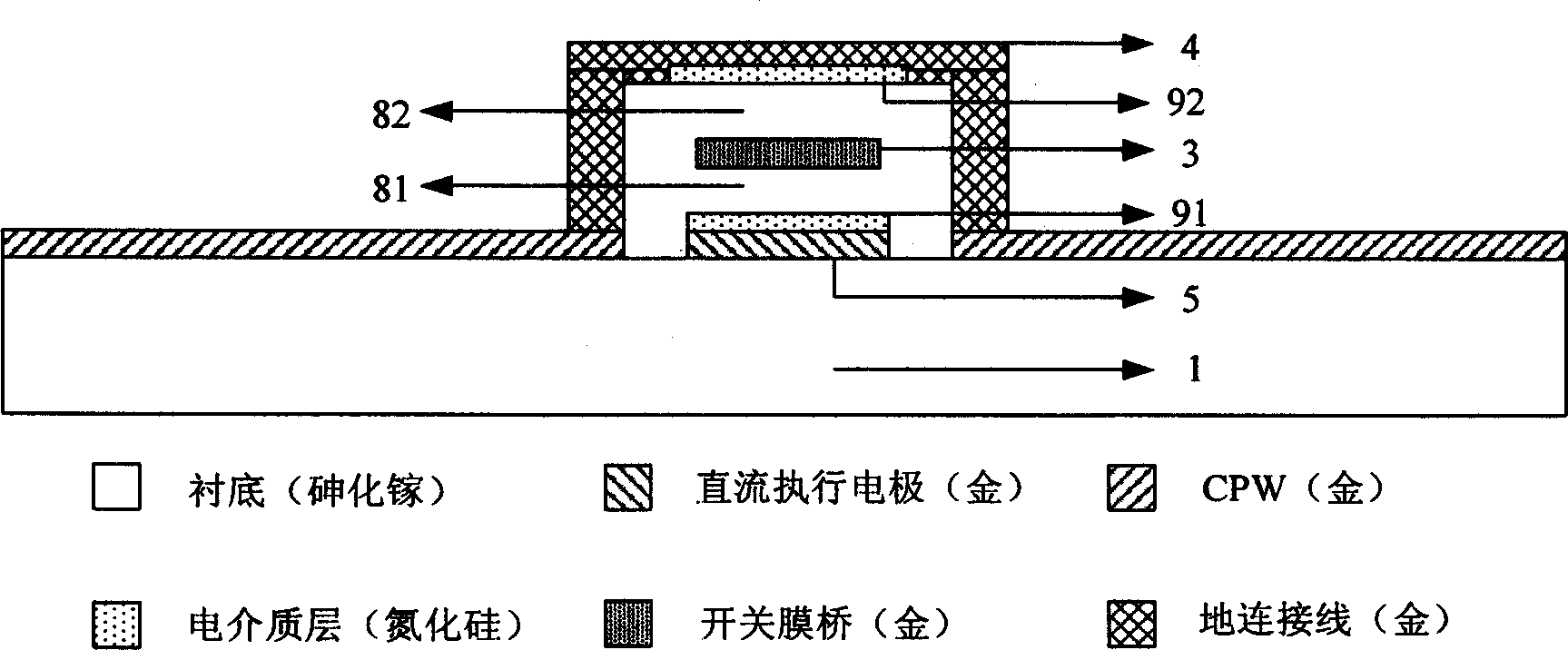

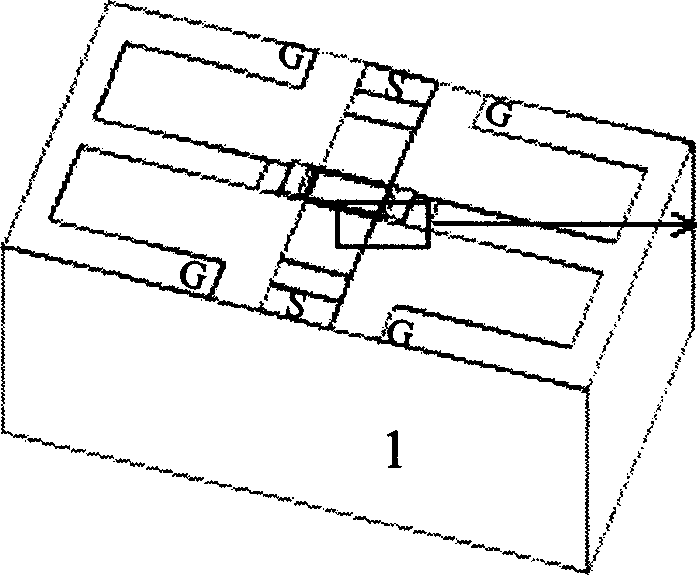

Radio-frequency micro-electronic mechanical double-film parallel capacitive type switch and preparation method thereof

InactiveCN1832081AReduce static power consumptionImprove isolationElectrostatic/electro-adhesion relaysCoplanar waveguideEngineering

A RF micro-electronic mechanical double-layer membrane bridge parallel condenser switch is used in RF microwave circuit, said structure uses a double end fixing strut beam as the switch membrane bridge and applies a double membrane structure to resolve the self-execution and self locking effect caused by RF high power including: a switch is installed on a GaAs substrate, a coplanar-waveguide is taken as a port of a switch, the switch bridge is part of a signal line realized by a fixed double end beam, the connection line of the coplanar-waveguide earth line is set above the signal line switch bridge, which is also the earth coupled line of the switch, a DC control electrode is below the signal line switch bridge and a SiN medium layer grows on the opposite faces of the DC electrode, earth connection line and the switch bridge, MMIC technological process is applied and polyimide is used as a sacrifice layer.

Owner:SOUTHEAST UNIV

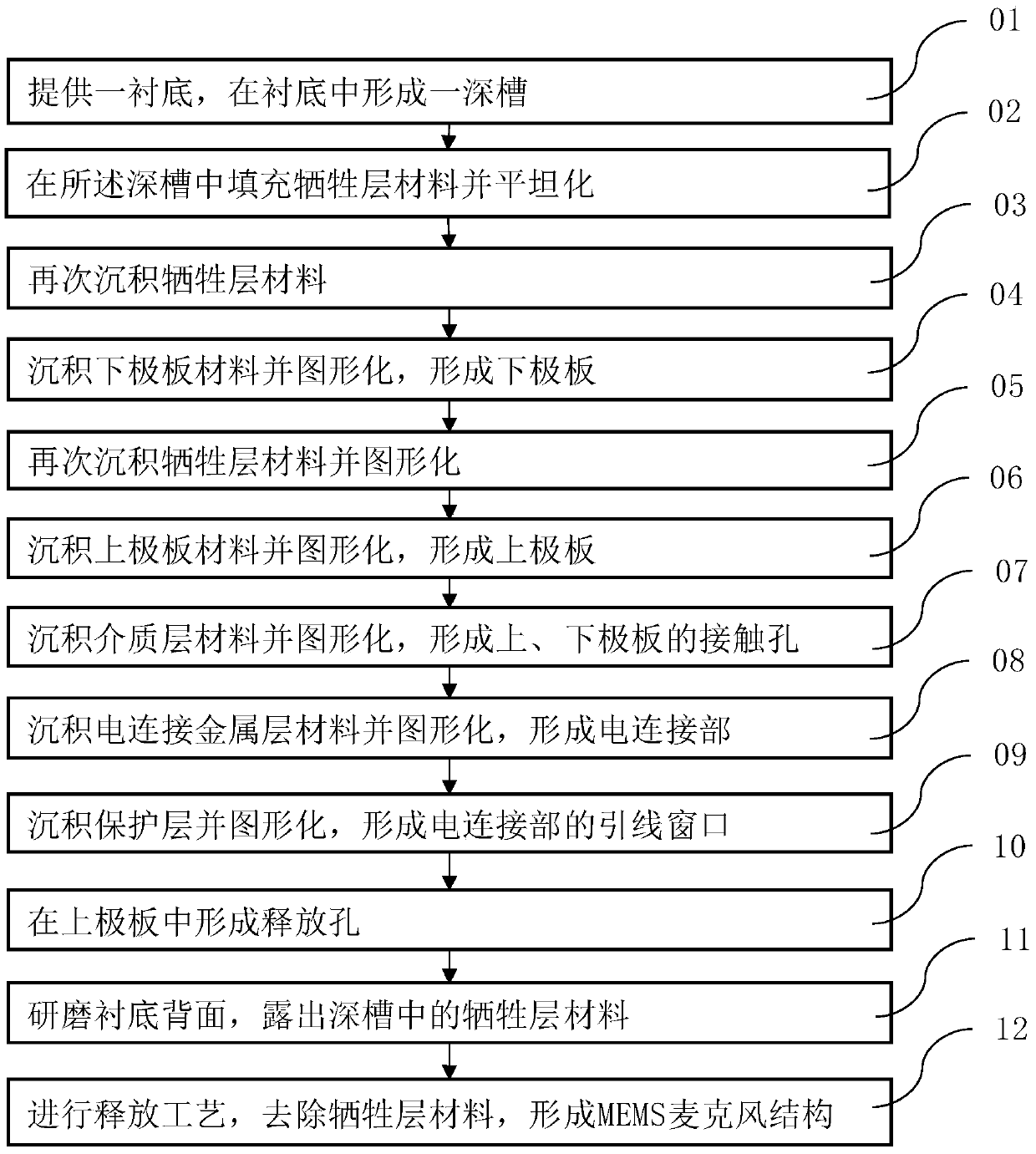

MEMS microphone manufacturing method

ActiveCN105516879AReduce process complexityEasy process integrationElectrostatic transducer microphonesEngineeringMems microphone

The invention discloses an MEMS microphone manufacturing method. The MEMS microphone manufacturing method comprises the following steps: forming a deep groove in a substrate, filling the deep groove with a sacrificial layer material and flattening the sacrificial layer material, forming a lower electrode plate and an upper electrode plate, forming contact holes of the upper and lower electrode plates, forming a lead window, forming release holes in the upper plate electrode, grinding the back surface of the substrate, exposing the sacrificial layer material in the deep groove, carrying out a release process, and removing the sacrificial layer material, so an MEMS microphone structure can be formed without carrying out a back surface process, the complexity of the process can be greatly reduced, the process is integrated with a CMOS process more easily, and the yield is improved.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

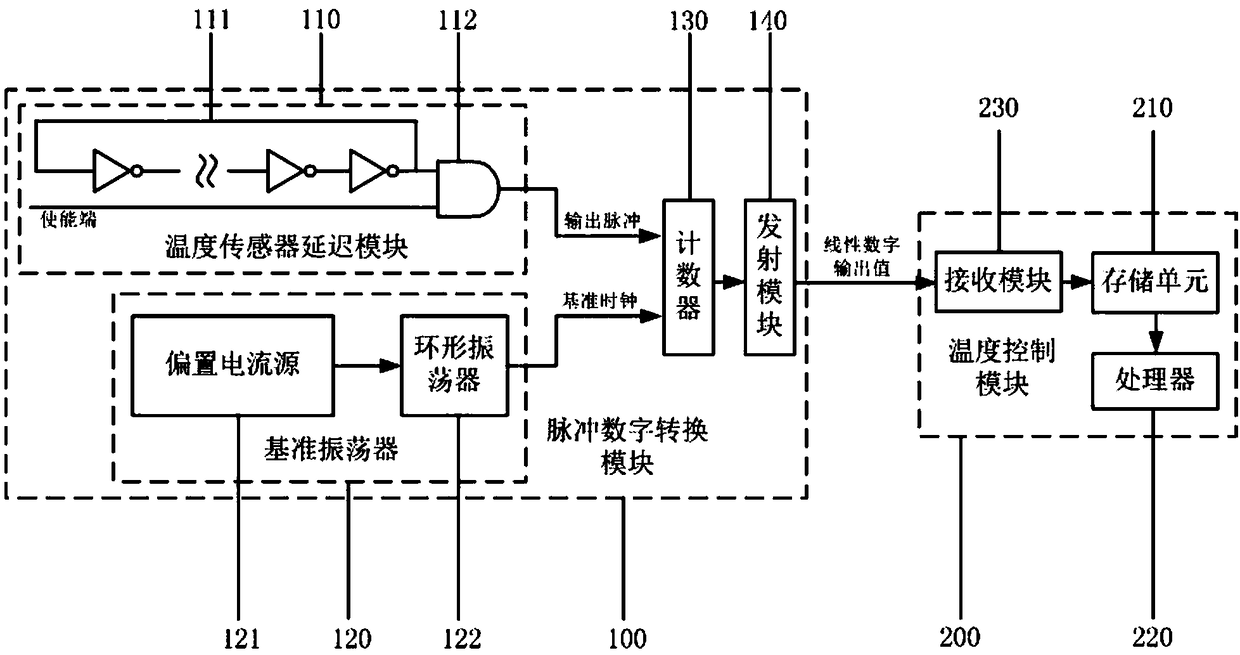

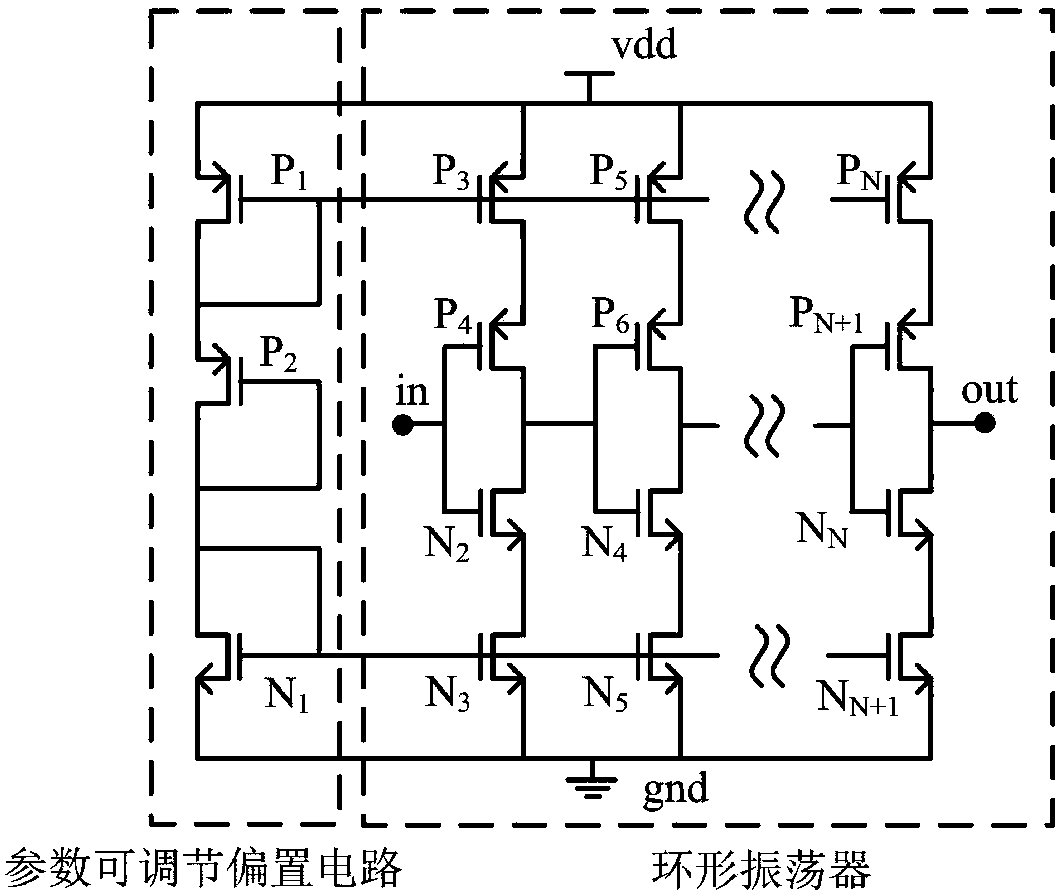

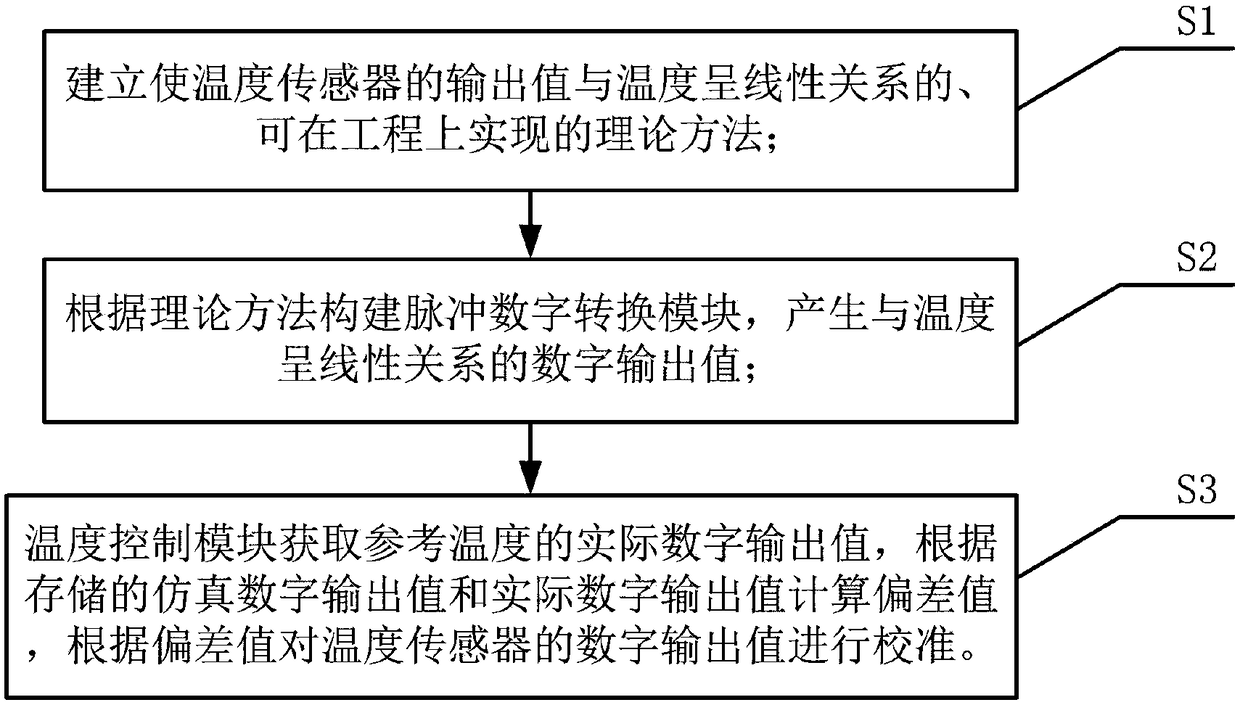

Pulse modulation temperature sensor calibration system and calibration method

ActiveCN108344527AHigh measurement accuracyAchieve calibrationThermometer testing/calibrationTemperature controlTheoretical methods

The invention provides a pulse modulation temperature sensor calibration system and calibration method, and belongs to the technical field of integrated circuit design. The system comprises a pulse digital conversion module and a temperature control module. The method comprises the steps that a theoretical method which enables the digital output value of the temperature sensor to have a linear relation with the temperature and can be implemented in engineering is established; the pulse digital conversion module is constructed according to the theoretical method so as to generate the digital output value having the linear relation with the temperature; and the temperature control module acquires the actual digital output value of the reference temperature, calculates the deviation value according to the stored simulation digital output value and the actual digital output value and calibrates the digital output value of the temperature sensor according to the deviation value. According to the system and the method, the measurement accuracy of the sensor can be enhanced, the calibration process can be simplified, real-time automatic calibration can be performed and the circuit structure can be simplified.

Owner:LIAONING TECHNICAL UNIVERSITY

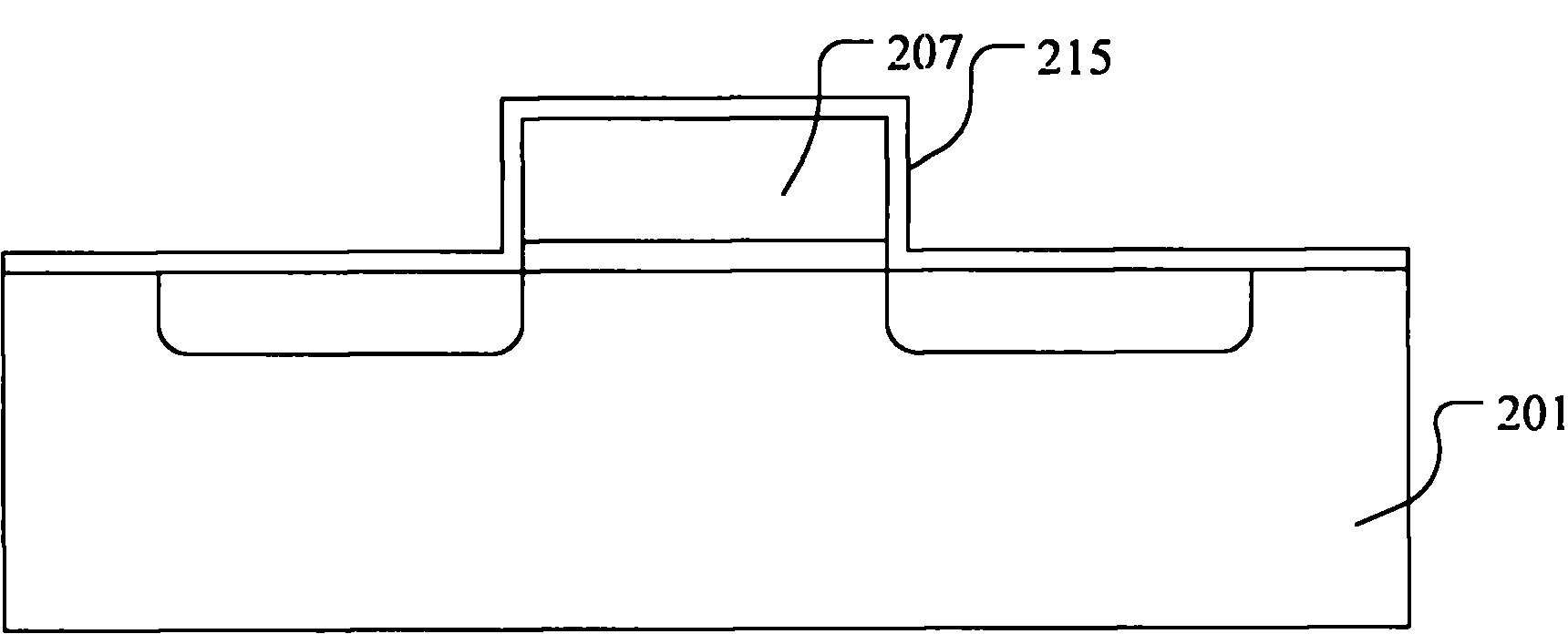

Method for manufacturing DRAM capacitor structure and formed structure

ActiveCN101211853AImprove device yieldEasy process integrationTransistorSolid-state devicesSemiconductorMask layer

The invention relates to a method for forming a capacitor structure used for a dynamic random access memory. The method comprises the steps as follows: a cover semiconductor substrate is formed; a first dielectric layer of a cover device is formed; a via hole in the first dielectric layer is formed; a first oxide layer covering the first dielectric layer is formed; a barrier layer covering the first oxide layer is formed; a second oxide layer covering the barrier layer is formed; a groove region which passes through a part of the second oxide layer, a part of the barrier layer and a part of the first oxide layer is formed; a bottom electrode structure is formed to sketch out the groove region; a mask layer is used for protecting the bottom electrode structure and selectively removing the second oxide layer and up to the barrier layer which has etching and resisting effect to expose the external region of the bottom electrode structure; dielectric layers of the capacitor which cover the external region of the bottom electrode structure and the internal region of the bottom electrode structure are formed; a plate of the upper capacitor which covers the dielectric layers of the capacitor is formed to form the capacitor structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

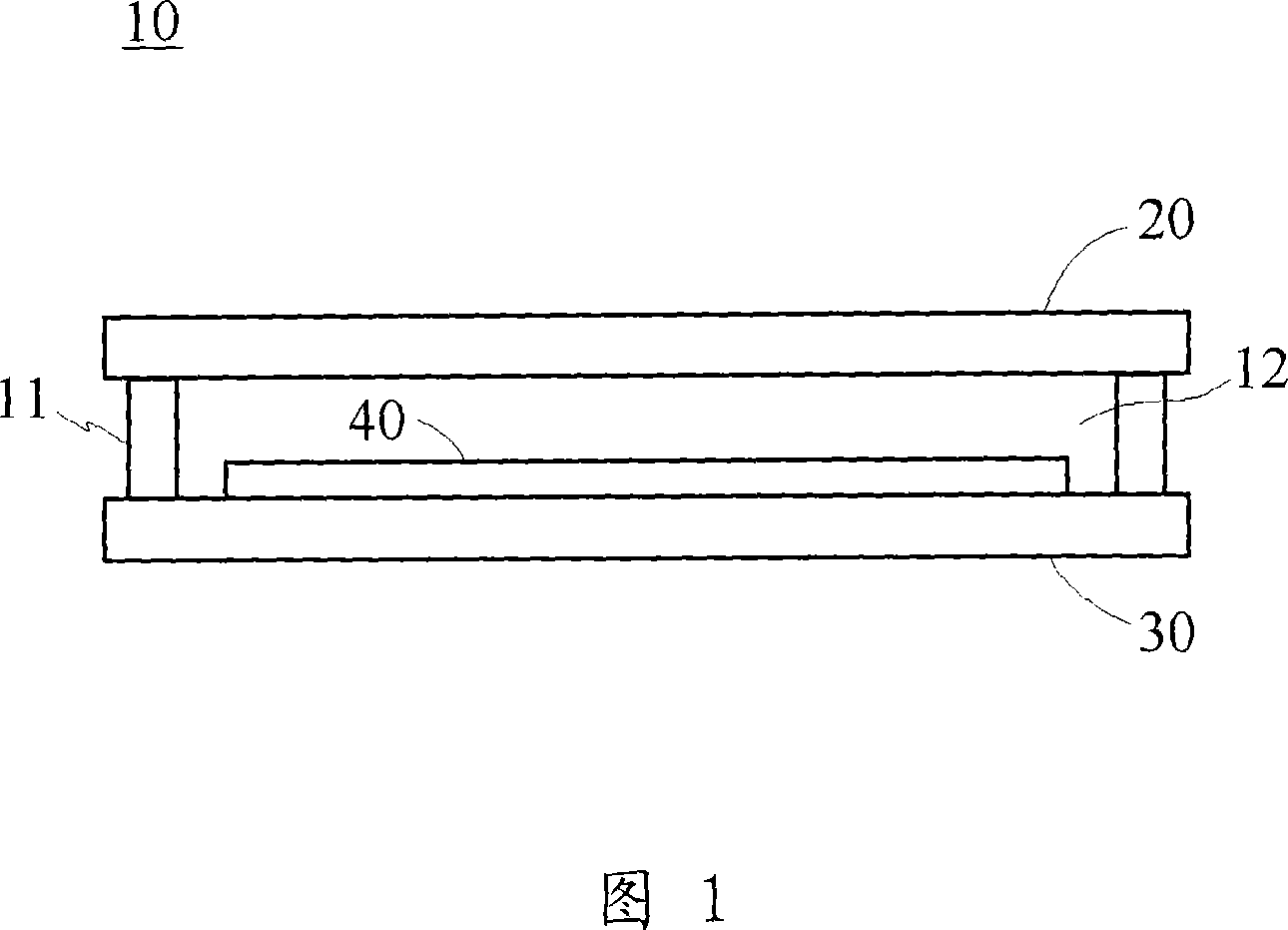

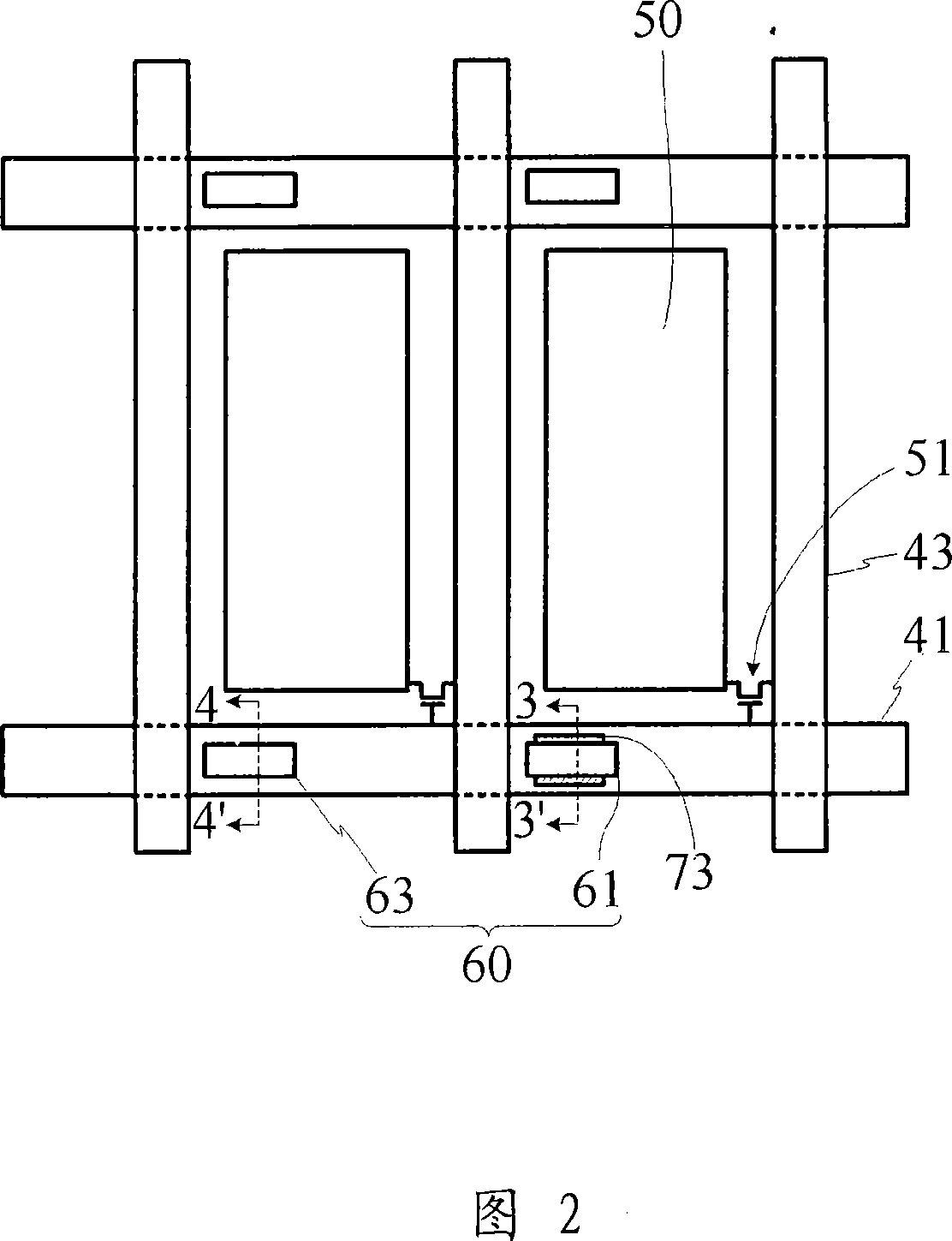

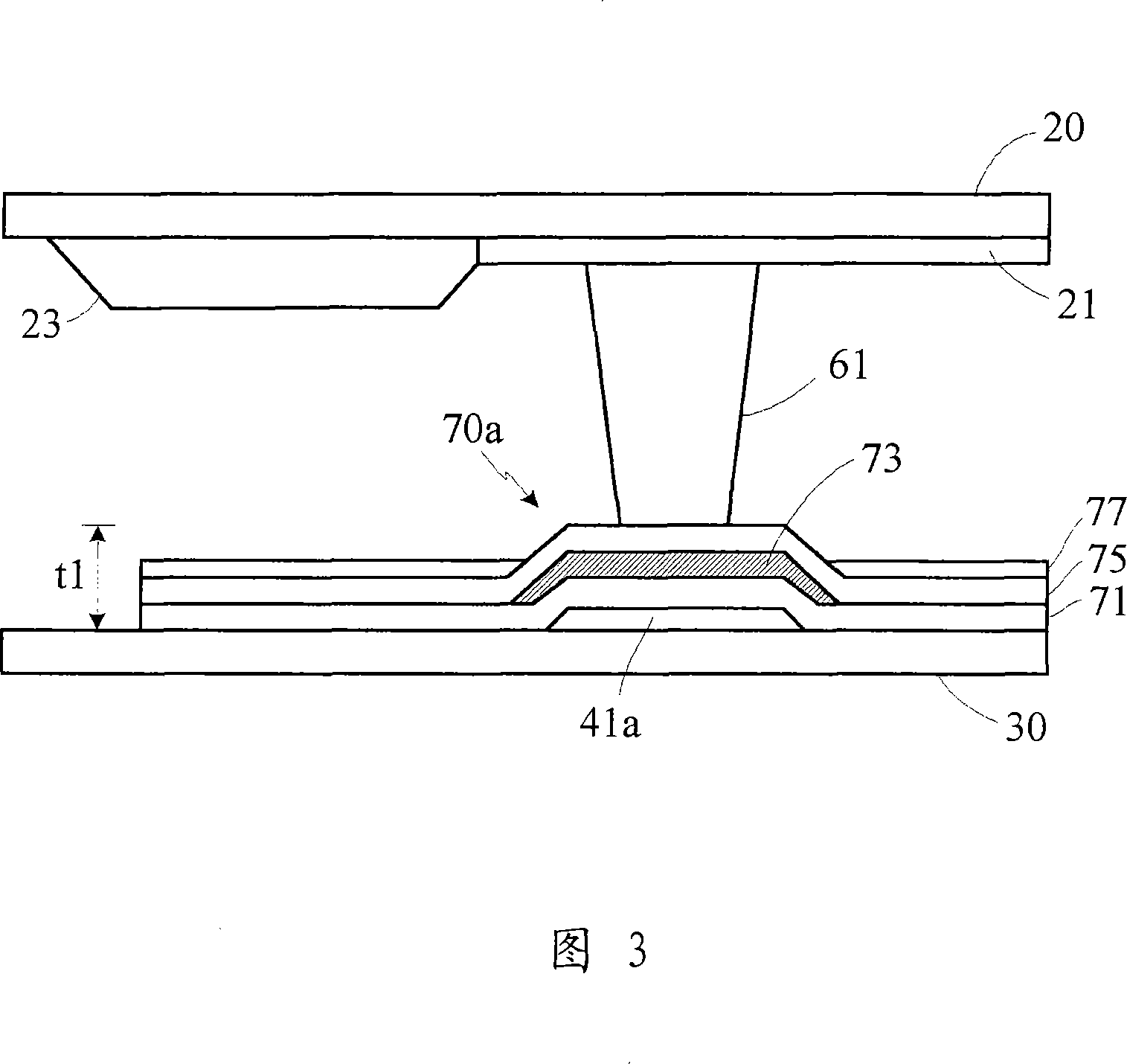

Liquid crystal display and support structure

ActiveCN101055353ADoes not affect alignment rotationDoes not affect aperture ratioStatic indicating devicesNon-linear opticsLiquid-crystal displayScan line

The invention discloses a liquid crystal display device and a structural support thereof. The liquid crystal display device comprises a first cardinal plate and a second cardinal plate mounting a plurality of scan lines and data wires to limit a plurality of display unit. The structural support comprises control module component and a plurality of distance pieces arranged on the first cardinal plate and respectively arranged at the location where each display unit correspond to the scan line. Moreover, the middle distance pieces is straight against the control module component on the second cardinal plate, and the other distance pieces are kept a interval to the control module component.

Owner:AU OPTRONICS (SUZHOU) CORP LTD

Resistive random access memory with high uniformity and manufacturing method thereof

InactiveCN103515534AImprove consistencyThe process steps are simpleElectrical apparatusDigital storageStatic random-access memoryProcess integration

The invention discloses a resistive random access memory with high uniformity and a manufacturing method thereof. A method that a graphical area of substrate silicon is used as a bottom electrode to be combined with selective heavy doping is adopted, and a proper ion injection direction is selected, so that an electric field can be controllably concentrated within a partial peak range, operation in every time and resistive random action of each element occur in the same position, and uniformity of the elements is effectively improved. According to the resistive random access memory and the method, a simple process method is used, the resistive random access memory with high uniformity can be manufactured, and meanwhile the electrode is avoided from being made of precious metal Pt, and process integration is facilitated.

Owner:PEKING UNIV

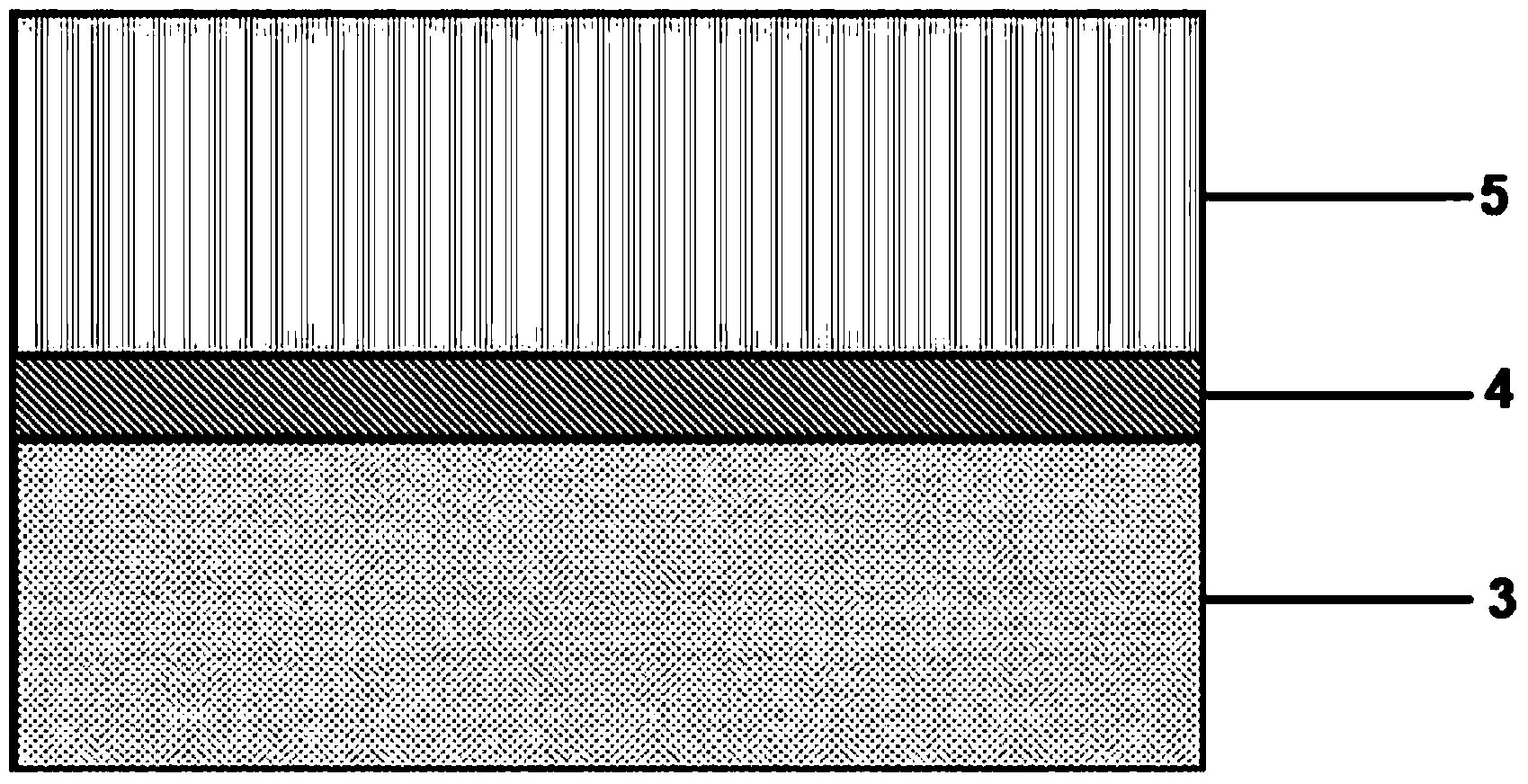

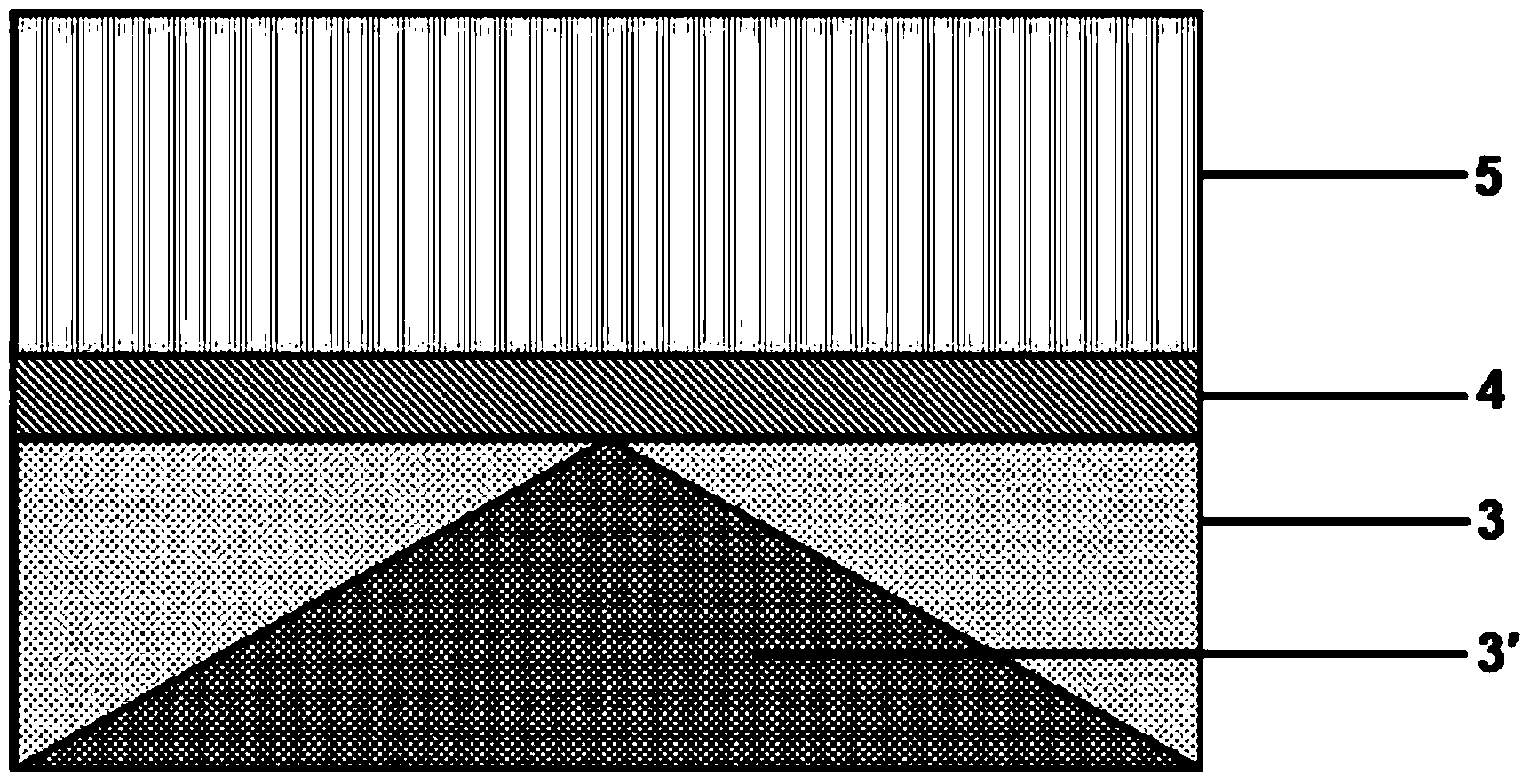

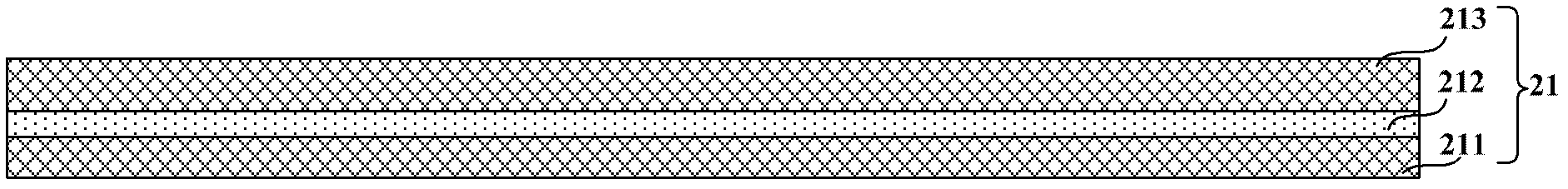

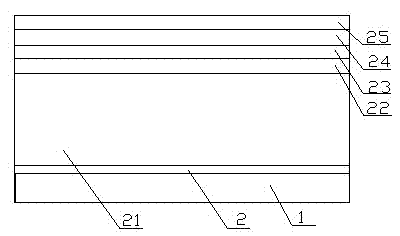

Absorbing layer structure for non-refrigeration long-wave infrared detector

ActiveCN103852171AFirmly attachedStrong corrosion resistanceRadiation pyrometryPhysicsSilicon nitride

The invention discloses an absorbing layer structure for a non-refrigeration long-wave infrared detector. The absorbing layer is arranged on a heat reactive film of the detector and sequentially composed of a first medium layer, a second metal layer and a third insulating layer from top to bottom. The absorbing layer is characterized in that the first medium layer is a silicon nitride film which is good in thermal-conductivity and high in corrosion resistance, the silicon nitride film is used as an anti-reflecting layer and a component protecting layer, the thickness of the film is 1000-1200nm, the second metal layer is a nickel chrome layer with the thickness being 8-12nm, the second metal layer is used as an absorbing layer of an infrared band, the third insulating layer is a silicon dioxide film with the thickness being 50-100nm, and the silicon dioxide film is used as the insulating layer between the heat reactive film and the metal layer. The absorbing layer is simple in preparation process, compatible with the existing microelectronic process and suitable for unit, alignment and area array infrared detectors. The infrared absorbing layer has the advantages of being firm in adherence, high in resistance to corrosion, good in repeatability, low in specific heat capacity and excellent in heat transfer performance, and has the absorption rate of larger than 85% on the infrared band of 8-14 micrometers.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

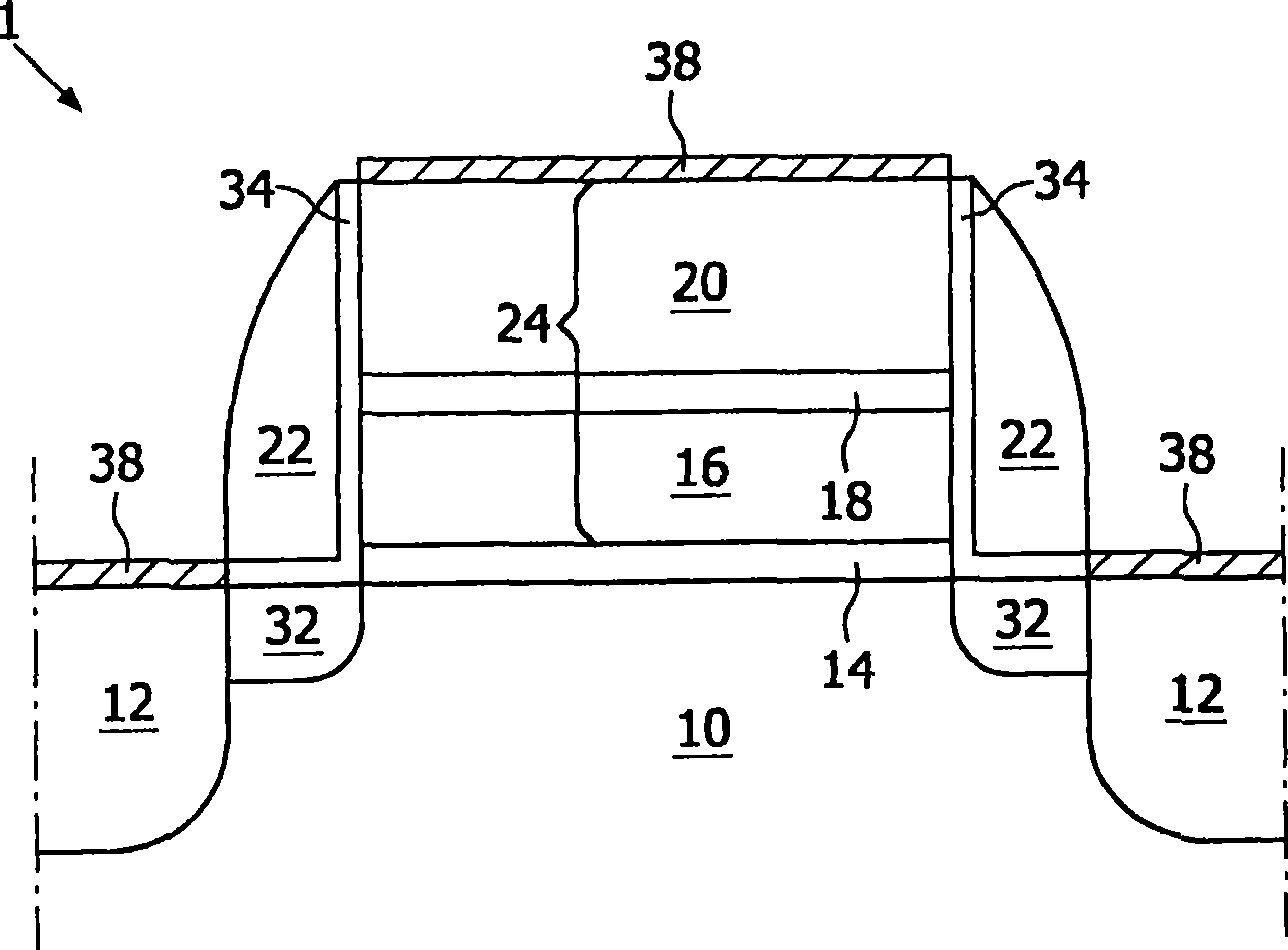

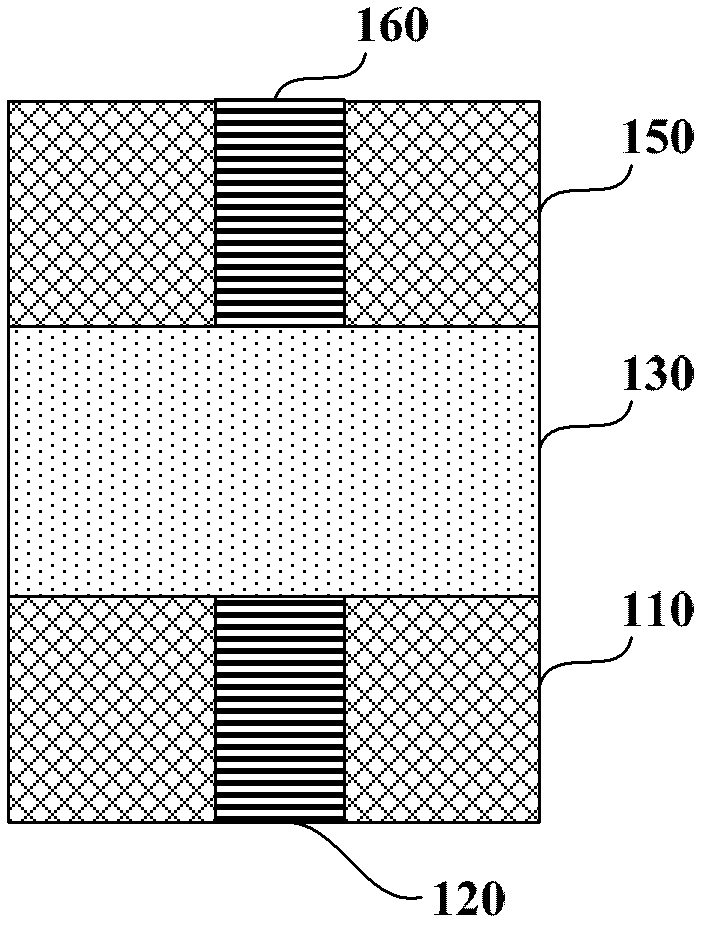

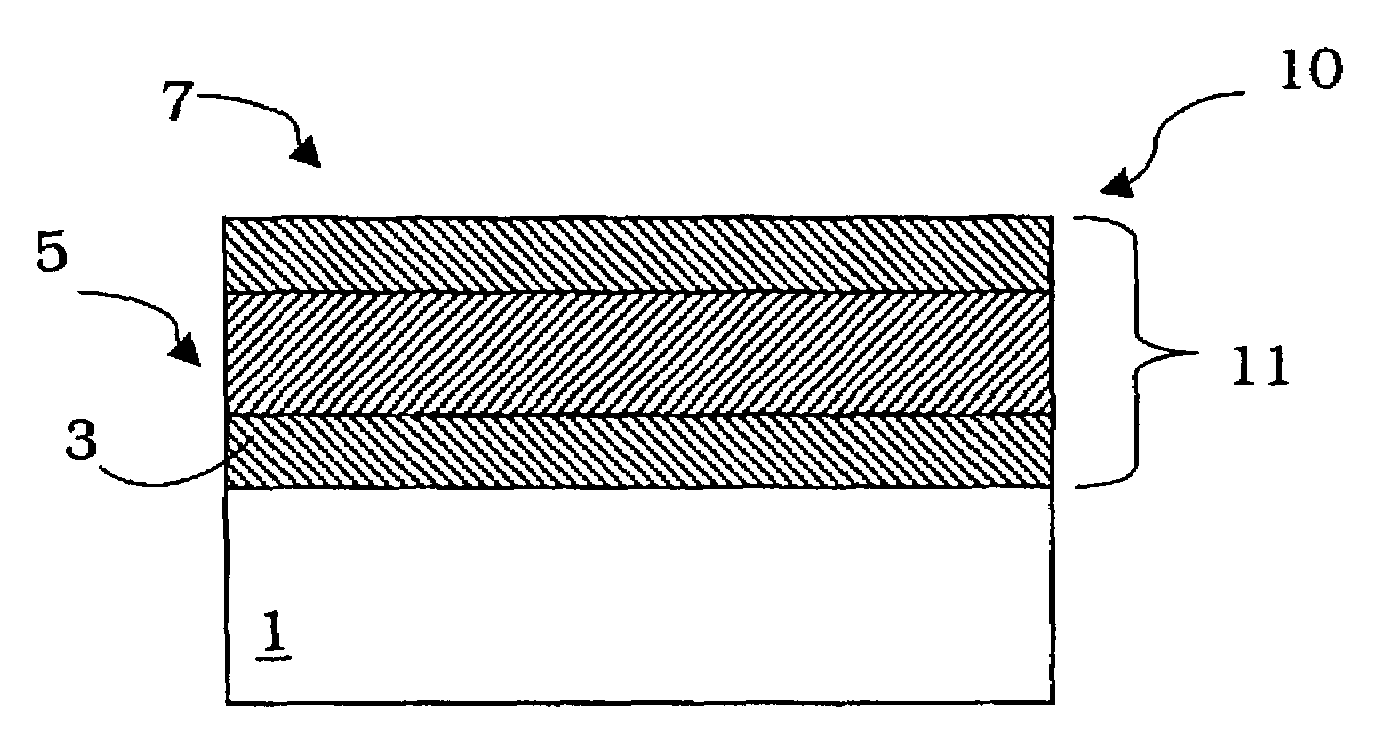

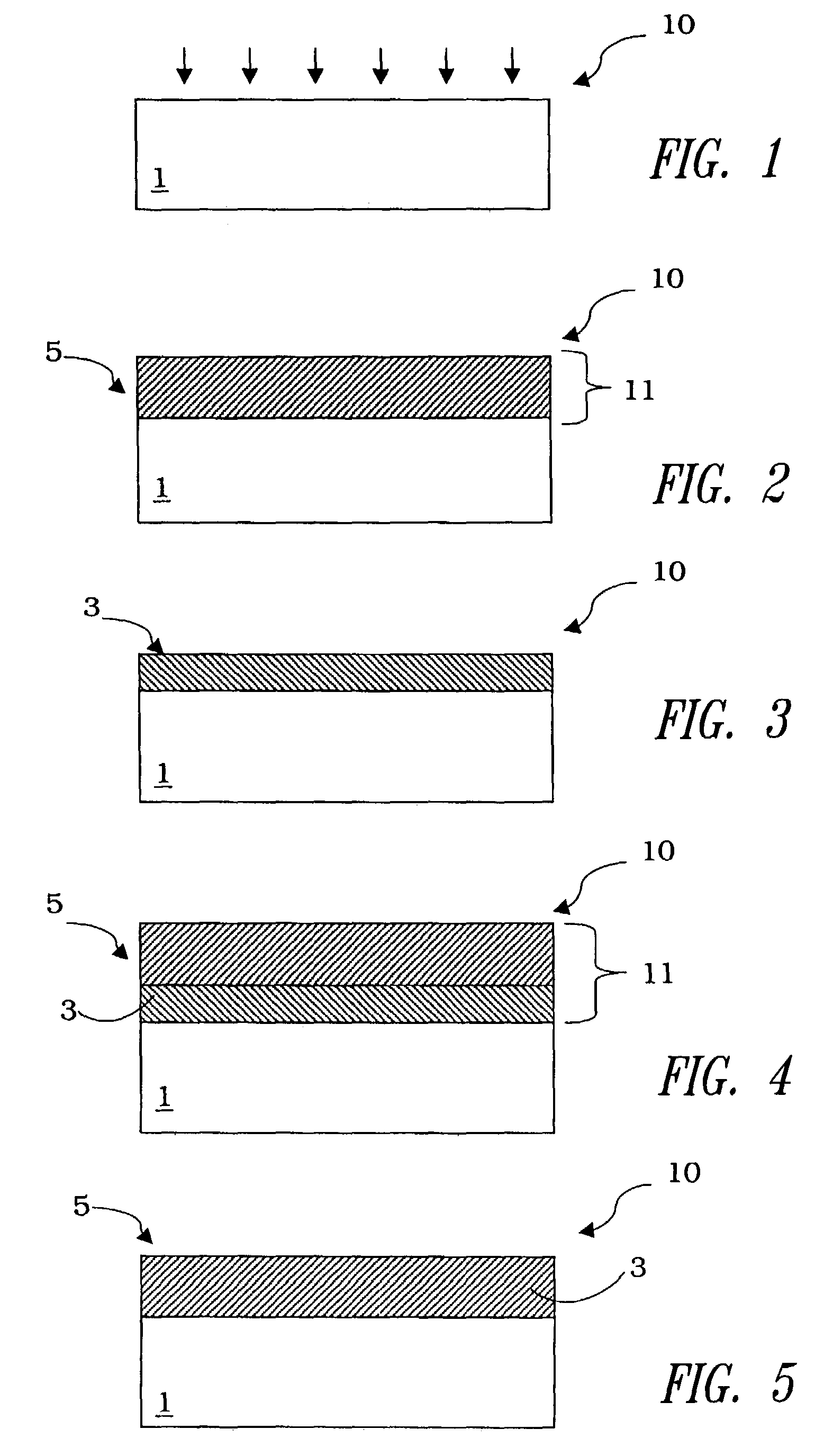

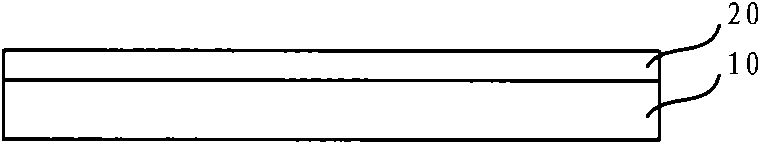

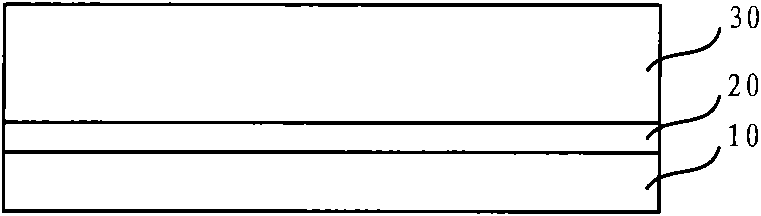

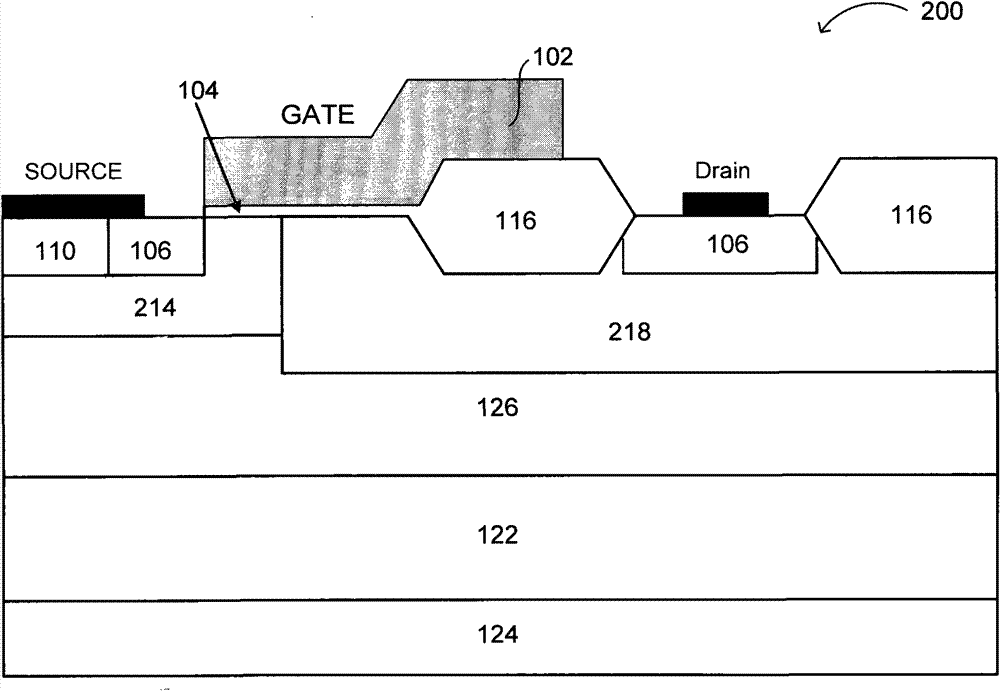

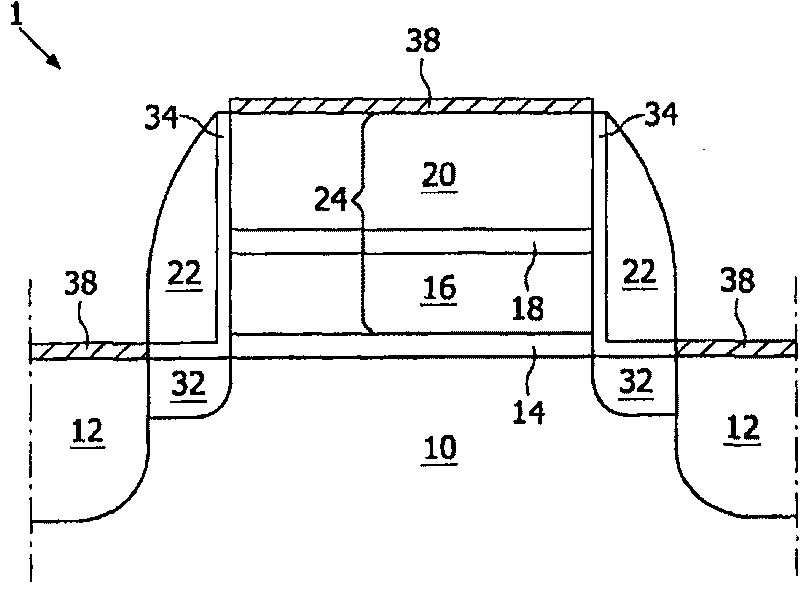

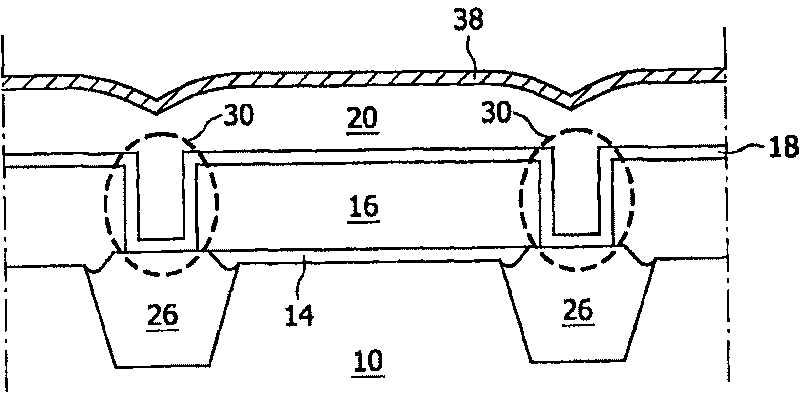

Non-volatile memory device having a gap in the tunnuel insulating layer and method of manufacturing the same

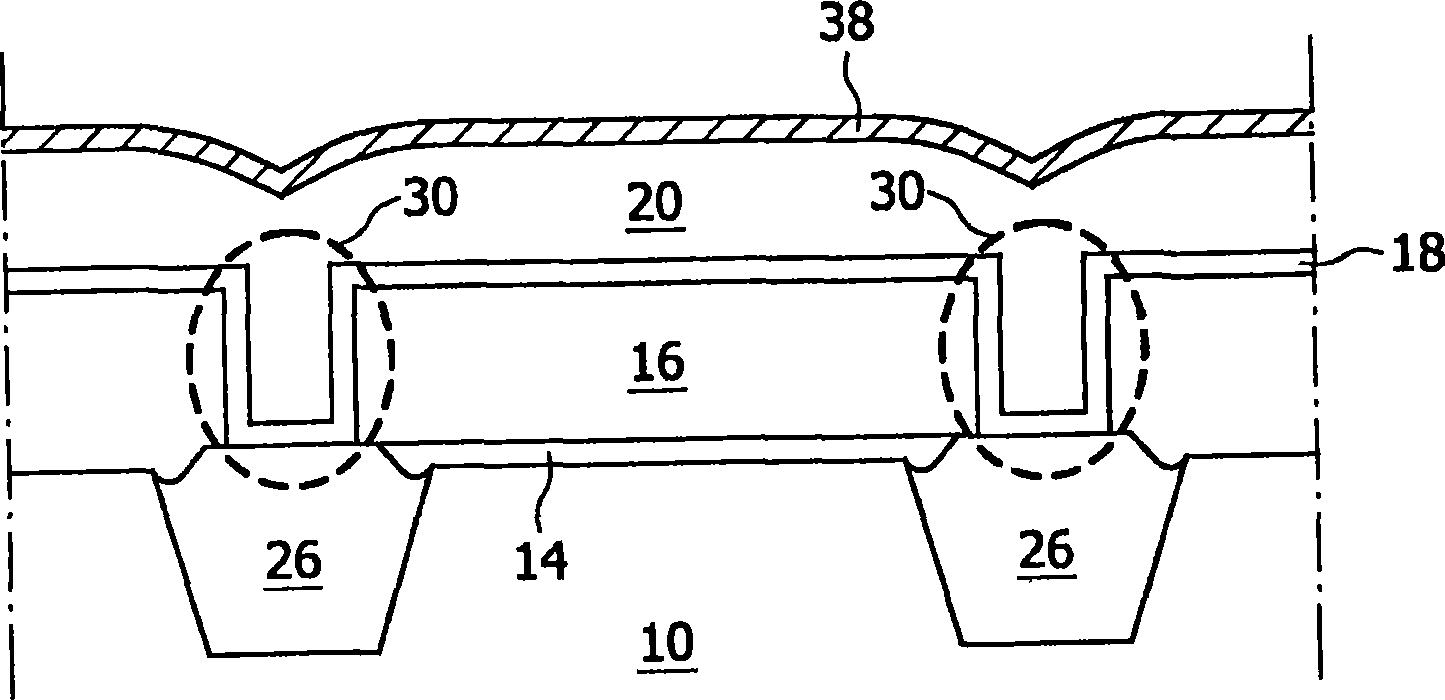

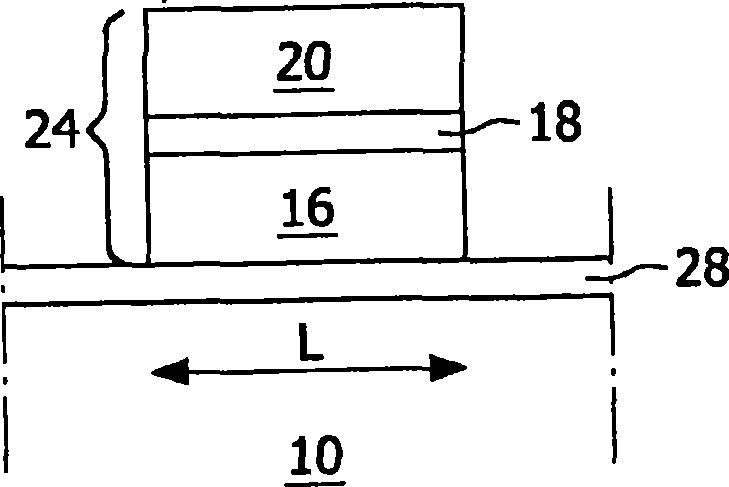

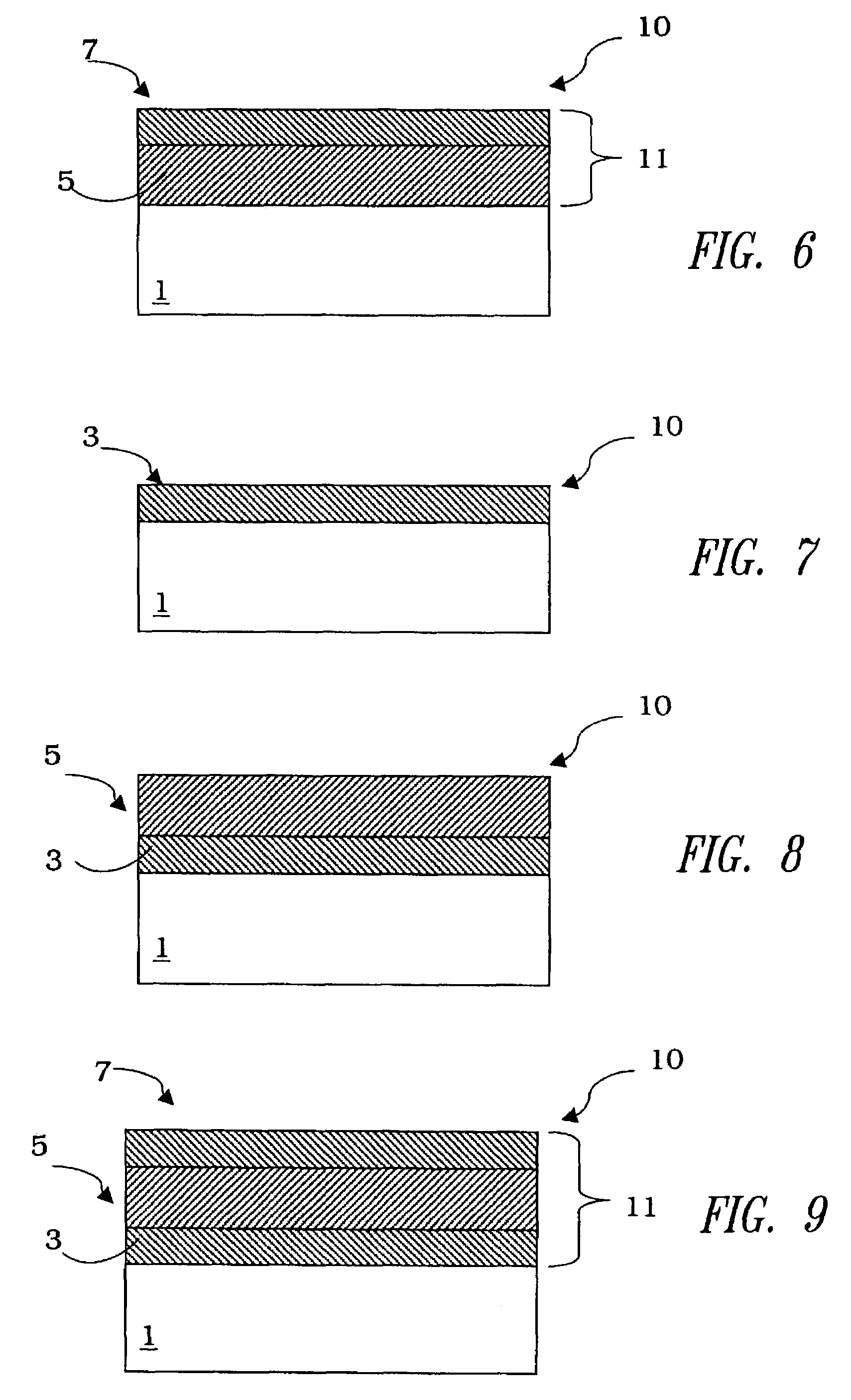

InactiveCN101375373AReduce thicknessReduce voltageTransistorSolid-state devicesDielectric layerSemiconductor

A non- volatile memory device (1, 101, 201, 301) having a gap within a tunnel dielectric layer (14, 114, 214, 314) and a method of manufacturing the same is provided. The devices have a stack of layers on top of a substrate (10, 110, 210, 310) including, a charge tunneling layer with a gap (14, 114, 214, 314), a charge storage layer (16, 116, 216, 316), a control gate layer (20, 120, 220, 320) and an insulating layer (18, 118, 218 220) in between the charge storage layer and the control gate. Manufacturing proceeds through deposition of a sacrificial layer (28, 128,228,328) on parts of a substrate, whereupon a stack of layers (24, 124,224,324) including a charge-storage layer, an insulating layer and a control gate layer are formed. Subsequently, selected parts of the sacrificial layer are removed, thereby forming a gap in between the charge storage region and the substrate. The gap is protected from future processing by deposition of a sealing layer (34, 134, 234, 334). Such a device has a reduced operating voltage and its manufacture can be easily implemented in existing semiconductor processes.

Owner:NXP BV

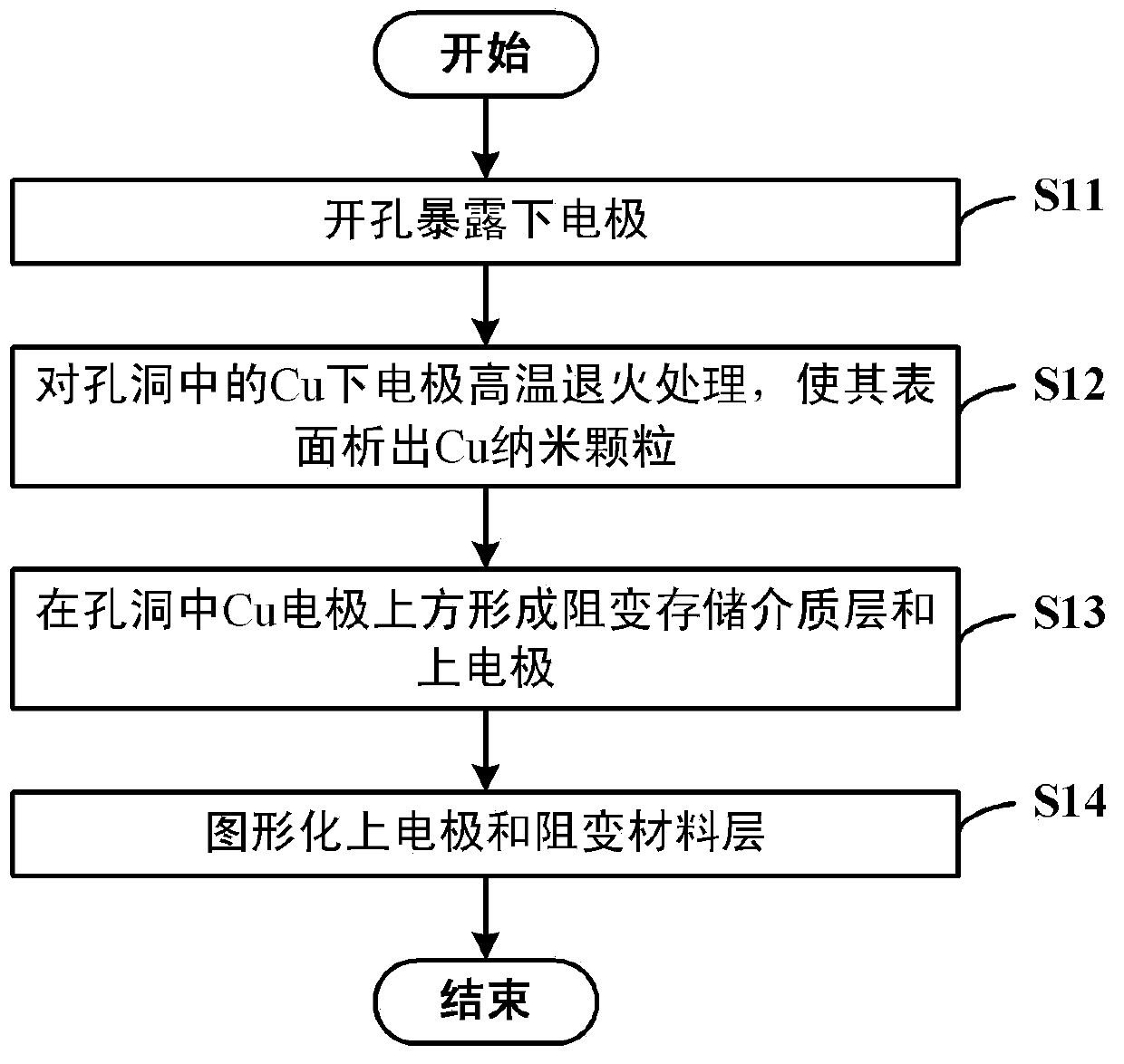

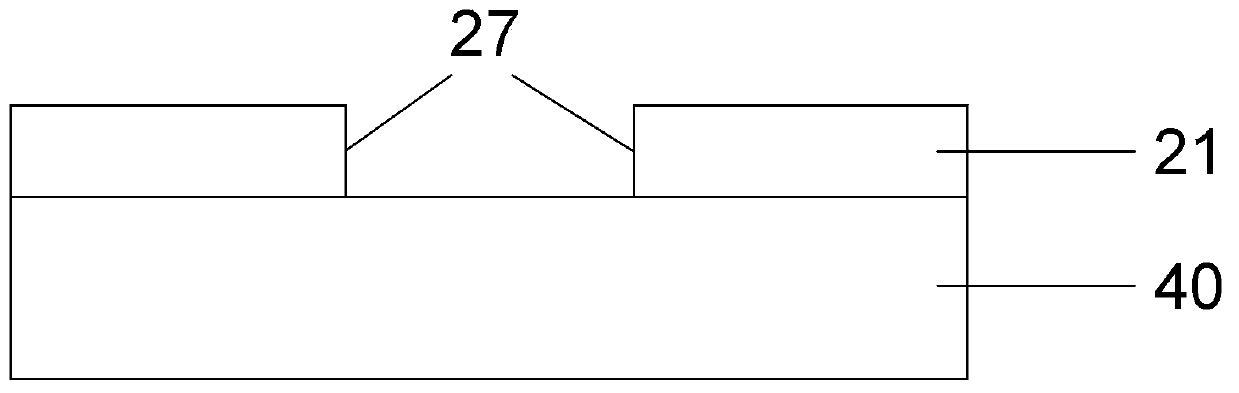

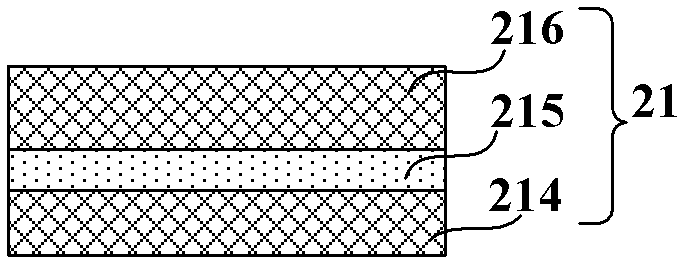

Preparation method of resistor type memory

The invention discloses a preparation method of a resistor type memory; the method comprises the following steps: carrying out high temperature annealing to an exposed lower electrode with an opening so as to precipitate nanometer particles on the surface of the electrode; forming a resistance change storage medium layer and an upper electrode above the lower electrode in a hole; schematizing the upper electrode and a resistance change material layer. The preparation method of the resistor type memory is provided; synapse particles are formed on the surface of the electrode under Cu, because local electric field enhancement effect is presented, when resistance changes in the storage medium, a conductive path can be formed in priority above the synapse particles, thereby effectively eliminating activation voltage of an element, improving element yield, and reducing discreteness of element parameters. The CuxO base resistor type memory prepared by the method is low in making cost, good in effect, and can be easily integrated with CMOS technology.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Semiconductor device and manufacturing method thereof

ActiveCN103187523AReduce contact areaAvoid Lithography Capacity LimitationsSolid-state devicesDigital storageDriving currentEngineering

The invention discloses a semiconductor device and a manufacturing method thereof. The semiconductor device comprises a phase change unit and two side wall electrodes, wherein the side wall electrodes are respectively located on two opposite side walls of the phase change unit. The phase change unit comprises three structures, wherein a phase change material layer is clamped between an upper insulation material layer and a lower insulation material layer. The first side wall electrode and the second side wall electrode contact the end face of the phase change material layer. By arranging the side wall electrodes, the connection method of the electrodes and phase change material is changed, the contact area of the electrodes and the phase change material can be reduced by utilizing existing preparation technique, therefore small driving current can be obtained, and the continually-improving demands of semiconductor device integration can be met.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

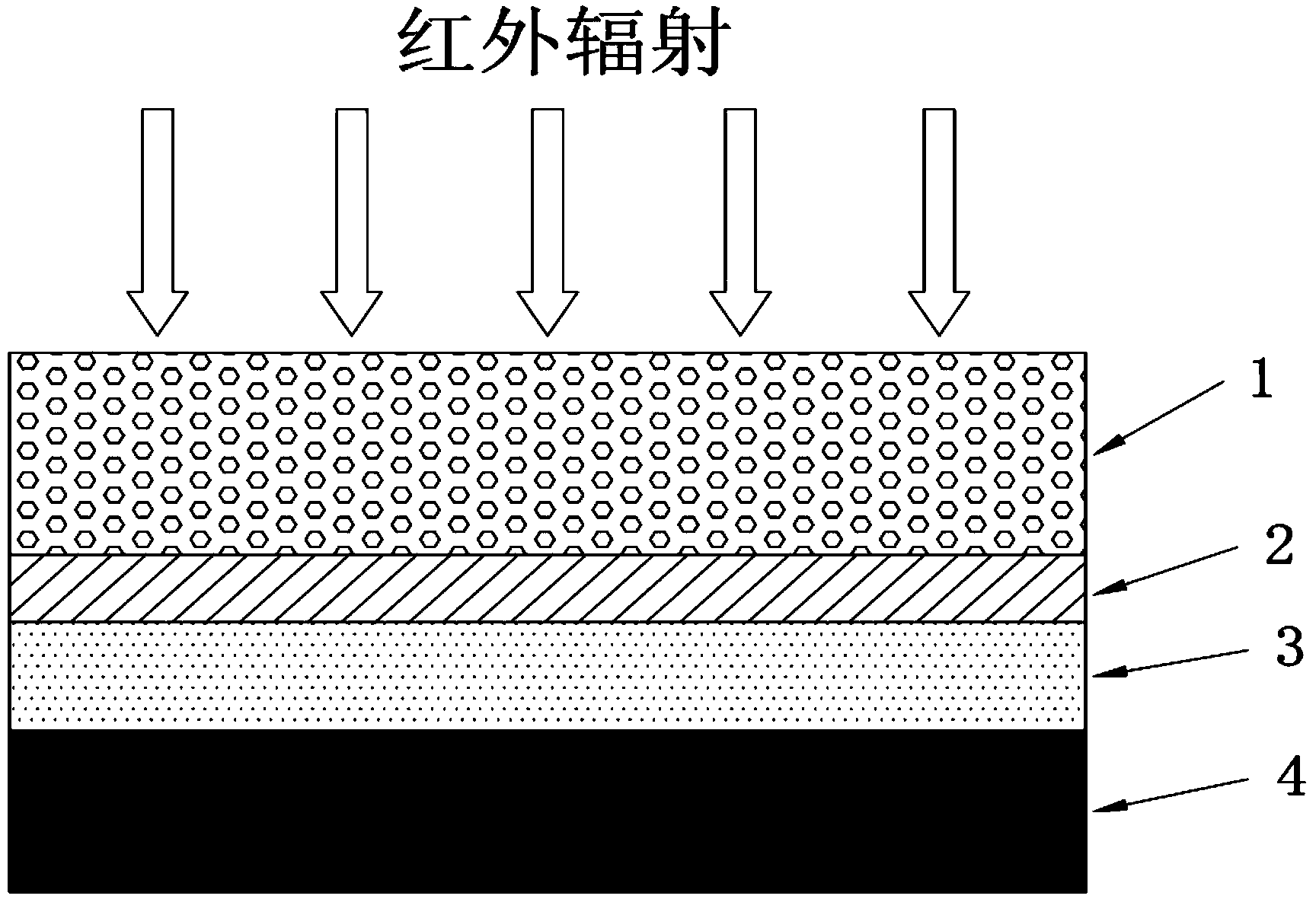

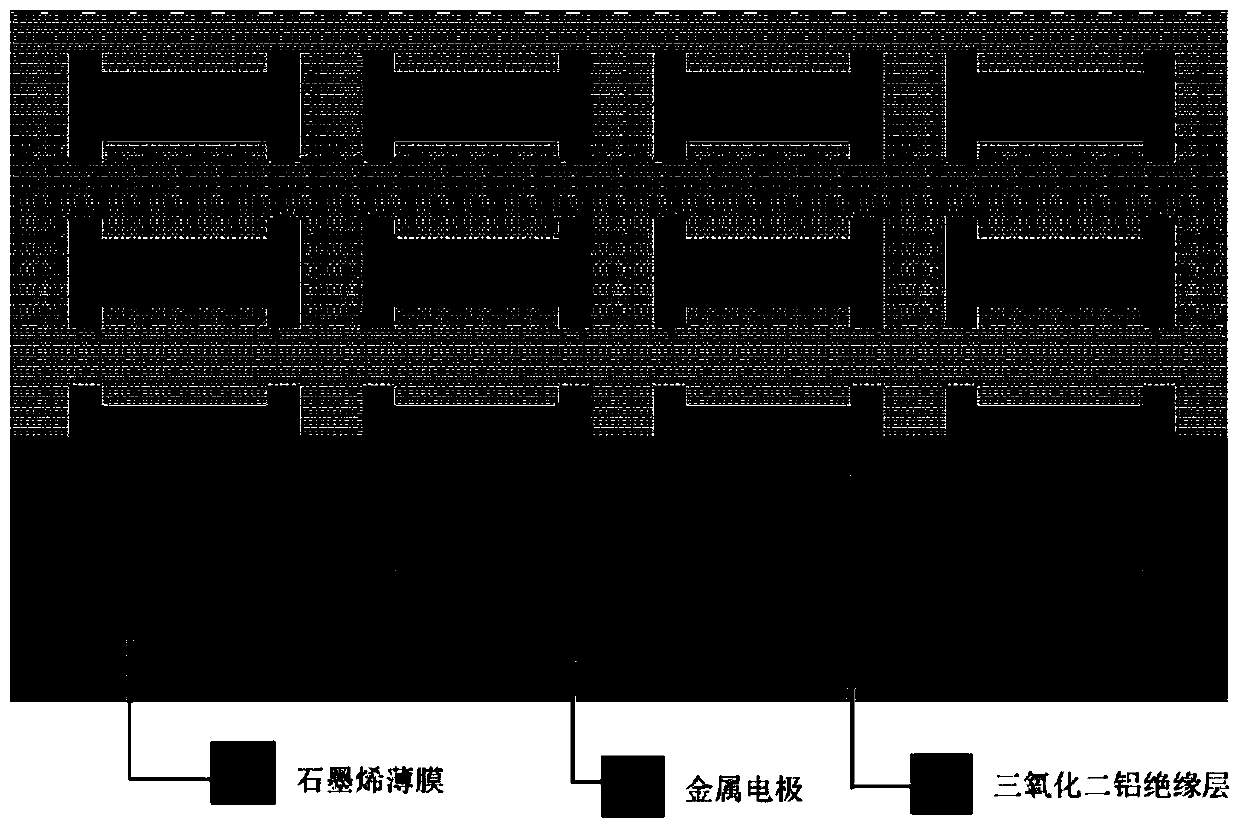

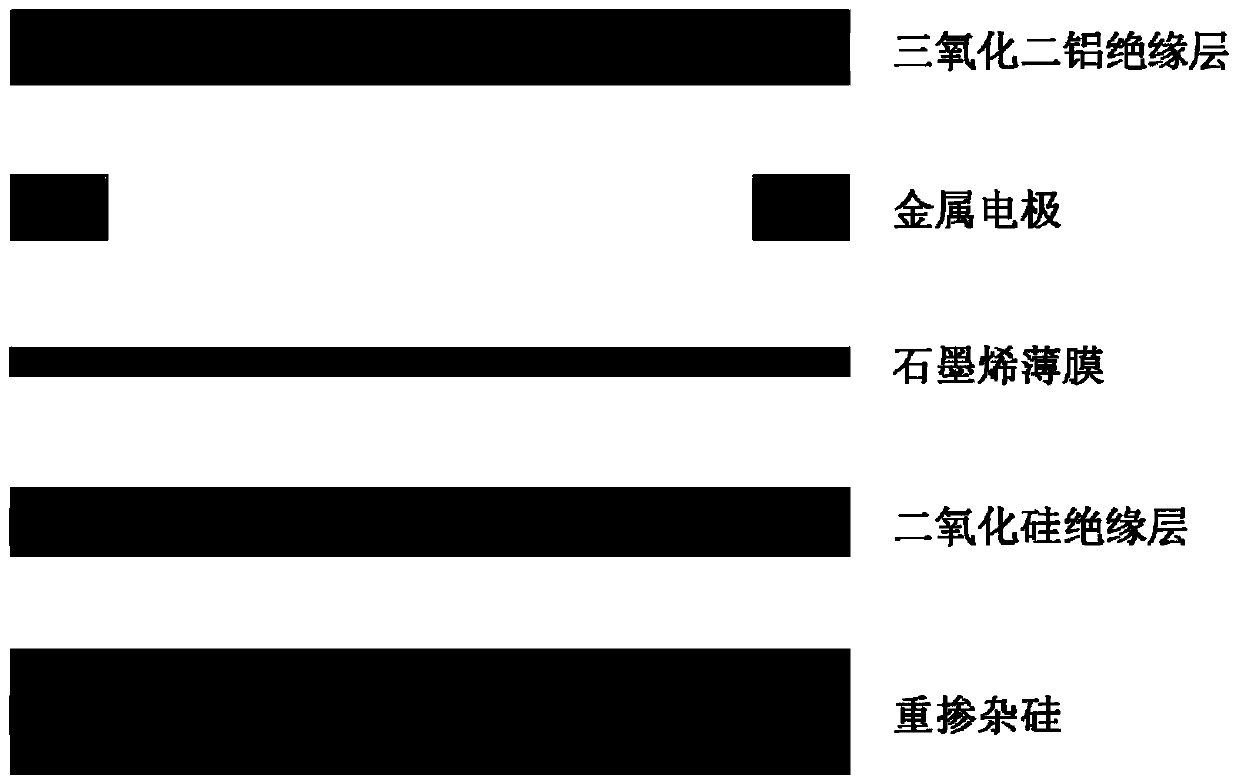

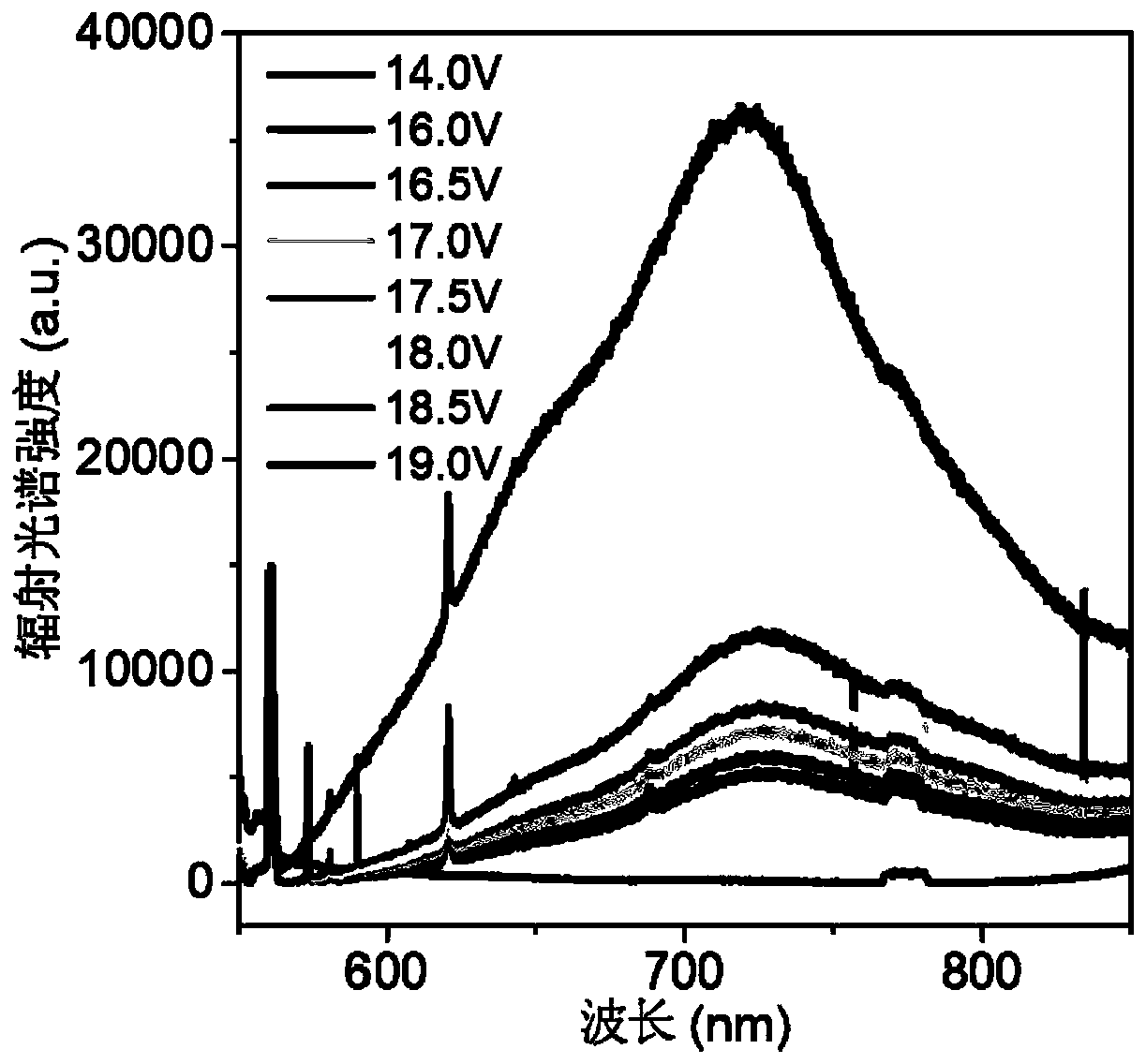

Electro-thermal radiation light emitting array device and preparation method and application thereof

InactiveCN110300475AHigh resolutionHigh frame rate characteristicsElectrical apparatusElectroluminescent light sourcesOptical communicationLength wave

The invention provides an electro-thermal radiation light emitting array device, which comprises a silicon wafer, a graphene film array on the silicon wafer, metal electrodes vapor-plated at the two ends of each graphene film in the graphene film array, and an aluminum oxide insulating layer at the top. The aluminum oxide insulating layer is deposited on the outermost layer of the whole silicon wafer to cover the graphene film array, the metal electrodes and the surface of the silicon wafer outside the area of the graphene film array and the metal electrodes, and are used to isolate the graphene films on the silicon wafer from the air and avoid the oxidation of the graphene films. A preparation method of the device and an application of the device prepared by the method in the field of optical communication are also provided. The electro-thermal radiation light emitting array device of the invention has the advantages of small volume, high resolution, fast switching, adjustable radiation wavelength, large-scale production and easy integration with a silicon-based process, and has a good application prospect in on-chip integrated high-speed optical communication.

Owner:NAT UNIV OF DEFENSE TECH

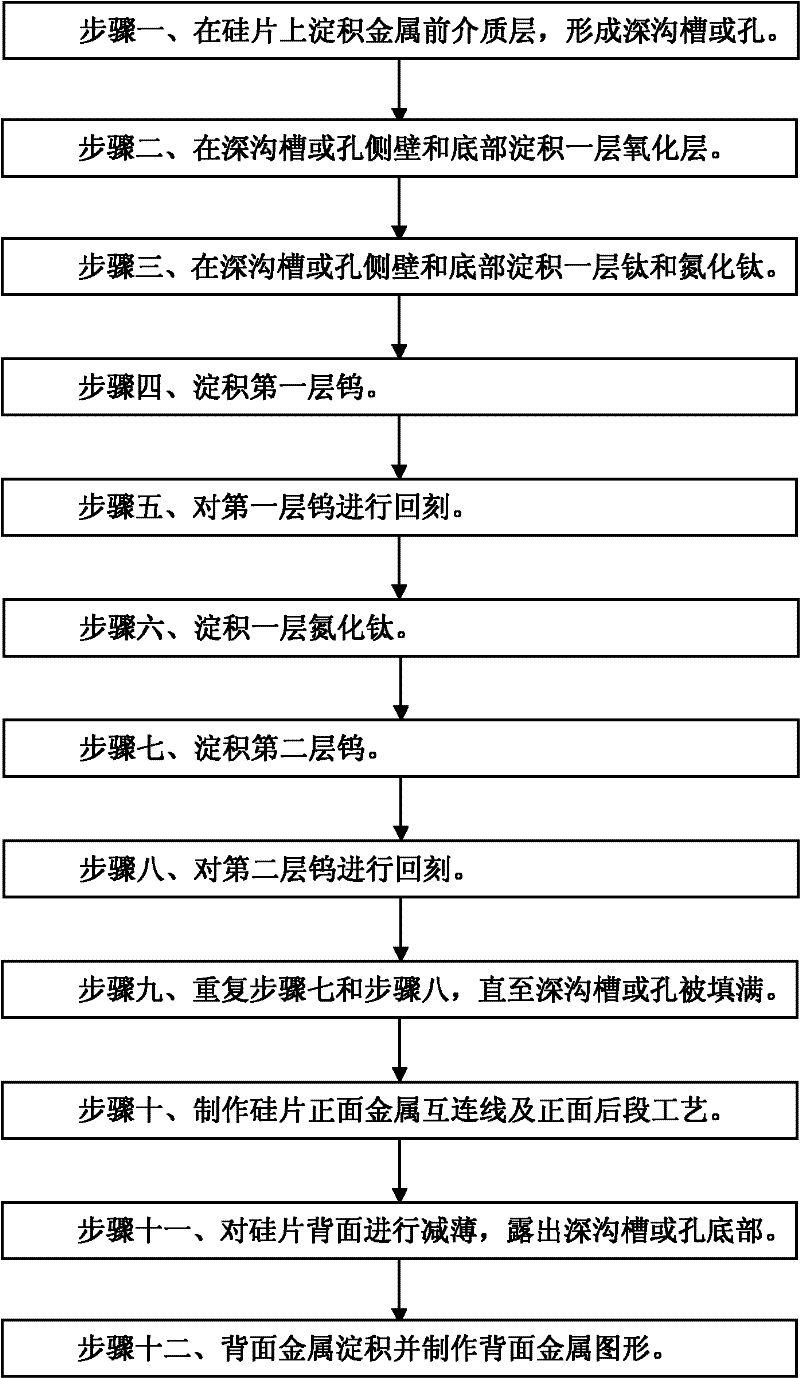

Through silicon via (TSV) filling method

InactiveCN102412195AReduce process difficulty and costEasy process integrationSemiconductor/solid-state device manufacturingMetal interconnectEtching

The invention discloses a through silicon via (TSV) filling method. The method comprises the following steps: forming a deep groove or hole; depositing an oxide layer on the side walls and bottom of the deep groove or hole; depositing titanium and titanium nitride; depositing a first layer of tungsten; carrying out back etching on the first layer of tungsten to remove the first layer of tungsten outside the deep groove or hole; depositing a layer of titanium nitride; depositing the second layer of tungsten; carrying out back etching on the second layer of tungsten to remove the second layer of tungsten outside the deep groove or hole; if the deep groove or hole is not filled up, repeating deposition and back etching of the second layer of tungsten until the deep groove or hole is filled up; manufacturing front metal interconnects and a front backend process; thinning the back of a silicon wafer; and forming back metal and manufacturing back metal patterns. The method has the following beneficial effects: through combination of a tungsten filling process and a tungsten etching process, the method can be used for realizing the filling of the TSV with high aspect ratio, can be conveniently integrated with the existing integrated circuit process and can be used for processing by utilizing the existing production equipment; and the process difficulty and cost can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Method for reducing free ammonia in anchovy protein hydrolysate

InactiveCN102406047AReduce free ammoniaReduce autolysisProtein composition from fishProtein foodstuffs working-upYeastFlavor

The invention relates to a method for reducing free ammonia in anchovy protein hydrolysate. Currently, a method for effectively removing free ammonia is not presented in the production process of enzymolysis of seawater anchovy protein. The method comprises the following steps: firstly, regulating the temperature of hydrolysate to 25-35 DEG C; then adding active dried yeast in a proportion that 0.01-0.1g of active dried yeast is added in per L of hydrolysate, or adding yeast culture in a proportion that 10-100 ml of yeast culture is added in per L of hydrolysate; and after evenly stirring, standing for 1-4 hours at the temperature of 25-35 DEG C, heating to 55-70 DEG C, insulating for 2-6 hours; and then raising temperature to 80-90 DEG C and maintaining for 10-20 minutes to inactivate the yeast. The method in the invention has the effect of obviously reducing free ammonia in protein hydrolysate, and can be used for effectively controlling the pH value of a product, effectively releasing the endogenesis soluble protein of the yeast and increasing the flavor of the product. The method provided by the invention is simple and practicable, and has good effect.

Owner:OCEAN RES CENT OF ZHOUSHAN ZHEJIANG UNIV

Method for copper dual damascene structure having ultralow dielectric constant layer

InactiveCN102820258AImprove mechanical propertiesLow dielectric constantSemiconductor/solid-state device detailsSolid-state devicesProcess integrationCopper

The invention discloses a method for a copper dual damascene structure having an ultralow dielectric constant layer. The method comprises the steps of providing a substrate; depositing an etching blocking layer, a first interlayer dielectric layer having a low dielectric constant, a first oxidation layer, a metal protection layer, a second oxidation layer and a first bottom anti-reflection layer sequentially on the substrate; etching a first groove and a first through-hole on the etching blocking layer, filling the first groove and the first through-hole with copper, conducting planarization treatment till the first interlayer dielectric layer, and forming a first metal layer; producing a second groove and a third groove on the first interlayer dielectric layer; and filling and depositing an ultralow dielectric constant material on the first groove, the second groove, the first interlayer dielectric layer and the first metal layer, forming a second interlayer dielectric layer, removing the ultralow dielectric constant material which covers the first dielectric layer and the first metal layer, and forming the first layer copper damascene structure. By the aid of the method, the mechanical performance of interlayer dielectric substances is good, and process integration is facilitated.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

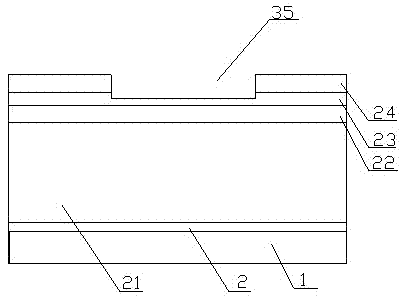

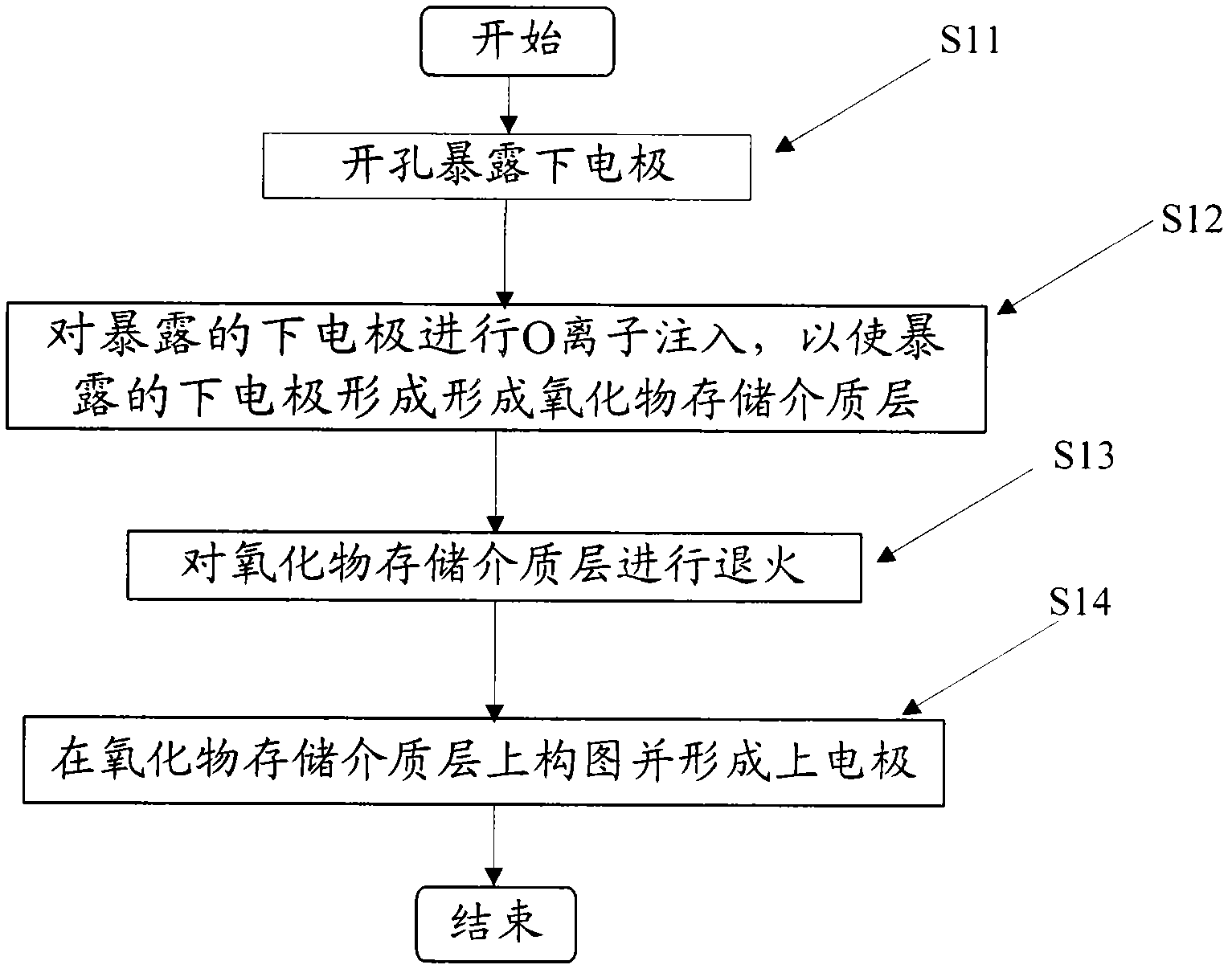

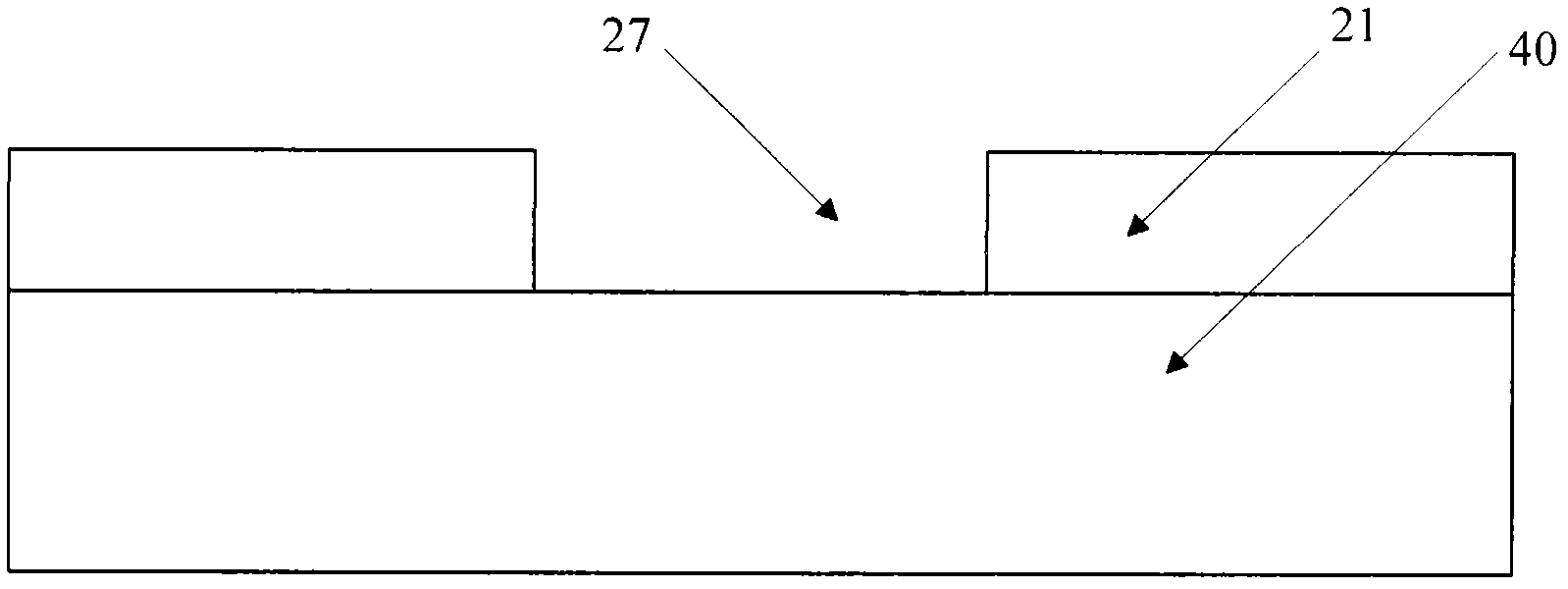

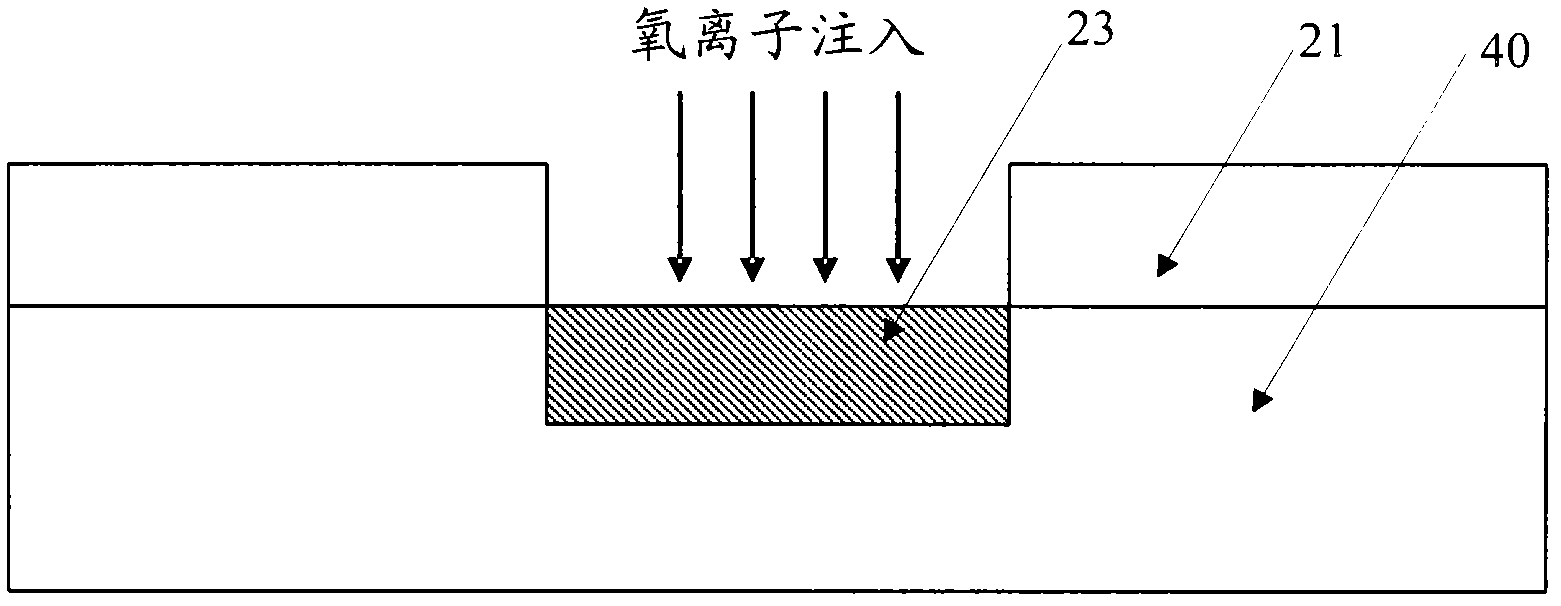

Method for manufacturing resistive type memory

ActiveCN102254803ATo avoidDistribution Precise ControlSemiconductor/solid-state device manufacturingCMOSOxygen ions

The invention provides a method for manufacturing a resistive type memory, comprising the following steps: constructing a picture for a lower electrode and carrying out oxygen ion implantation on the lower electrode to form an oxide storage medium layer on the lower electrode; annealing the oxide storage medium layer; and constructing a picture on the oxide storage medium layer and forming an upper electrode. By using the method, an empty hole is not generated between the storage medium layer and the lower electrode; and the oxygen storage medium layer is even, and O elements are distributed evenly in the oxygen storage medium layer. The resistive type memory manufactured by the method has the advantages of low manufacturing cost and good effect and is easy to integrate with a CMOS (complementary metal oxide semiconductor) technology.

Owner:江苏畅微电子科技有限公司

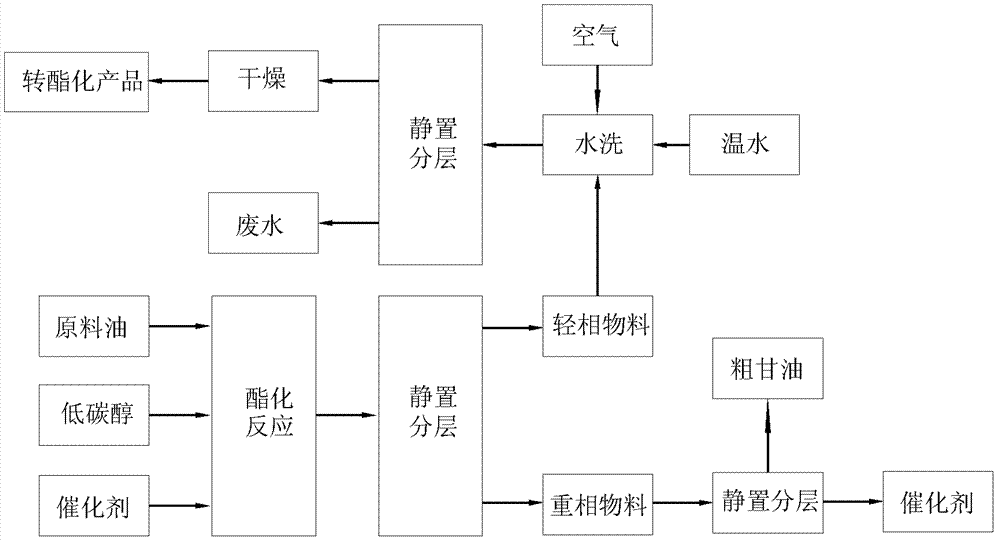

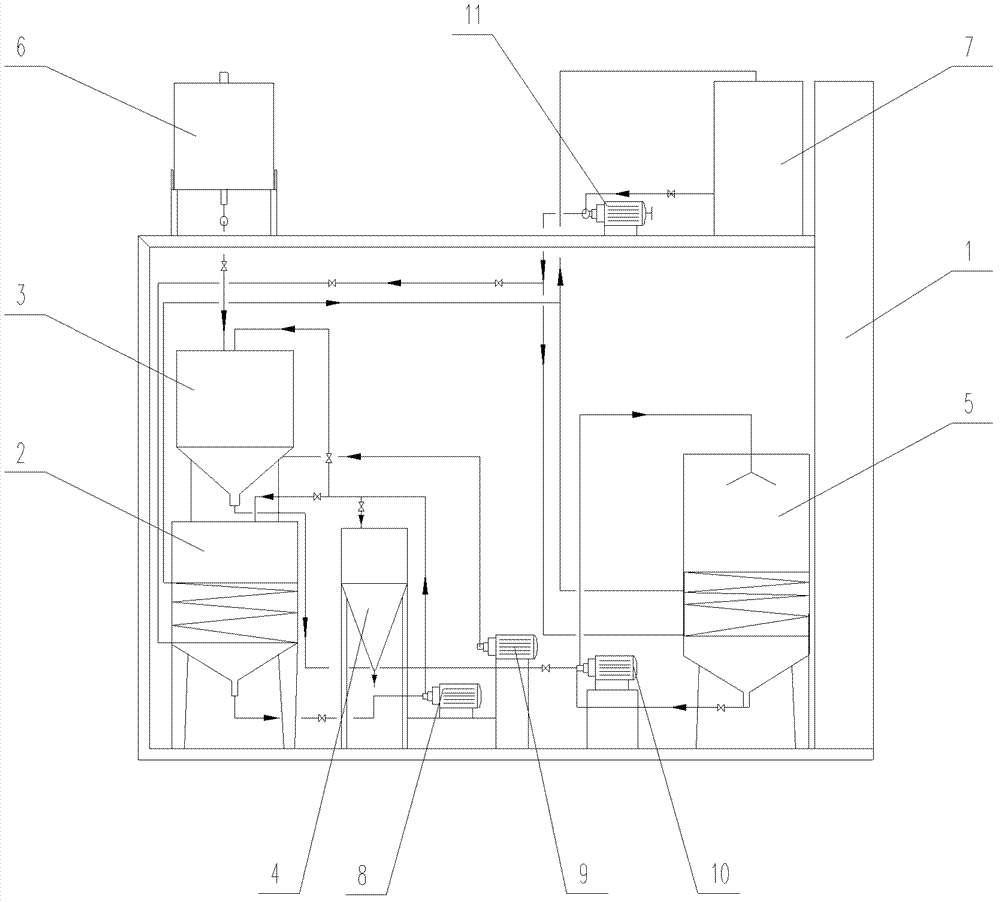

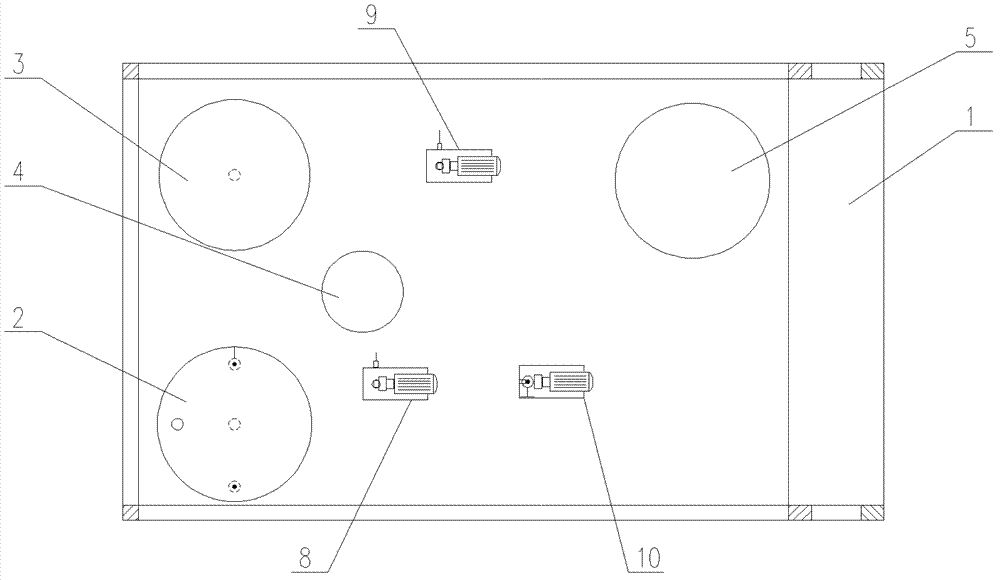

Production device and production method for distribution type plant oil transesterification

InactiveCN102492560BEasy to recycleShort process routeFatty acid esterificationFatty-oils/fats refiningHeat conductingWarm water

The invention discloses a production device and a production method for distribution type plant oil transesterification. The production device comprises an equipment frame, a reaction kettle, a washing tank, a catalyst recovering tank, a drier, a warm water storage tank, a heat conducting oil heating tank, a reaction circulating pump, an air pump, a material pump and a heat conducting oil pump. The production method comprises the following steps of: heating and stirring a mixture of plant fat raw material oil, low-carbon alcohol and a pyridyl trifluoromethanesulfonate ion liquid catalyst to react for 3-5 hours; standing so that reaction materials are divided into a light phase and a heavy phase, and separating the light phase from the heavy phase; standing the heavy-phase material and naturally cooling, so that the catalyst is precipitated to the bottom, and the rest is crude glycerol containing alcohol; adding warm water to the light-phase material for washing, and then standing so that the light phase and the heavy phase are formed again; and pumping the light-phase material into the drier for drying, so as to obtain the plant oil. The production method disclosed by the invention can achieve homogeneous catalysis and different-phase separation through process integration, and the yield of the plant oil is improved; and the production device disclosed by the invention is handy and simple, and is convenient for real-time processing of a dispersed raw material.

Owner:SOUTH CHINA UNIV OF TECH

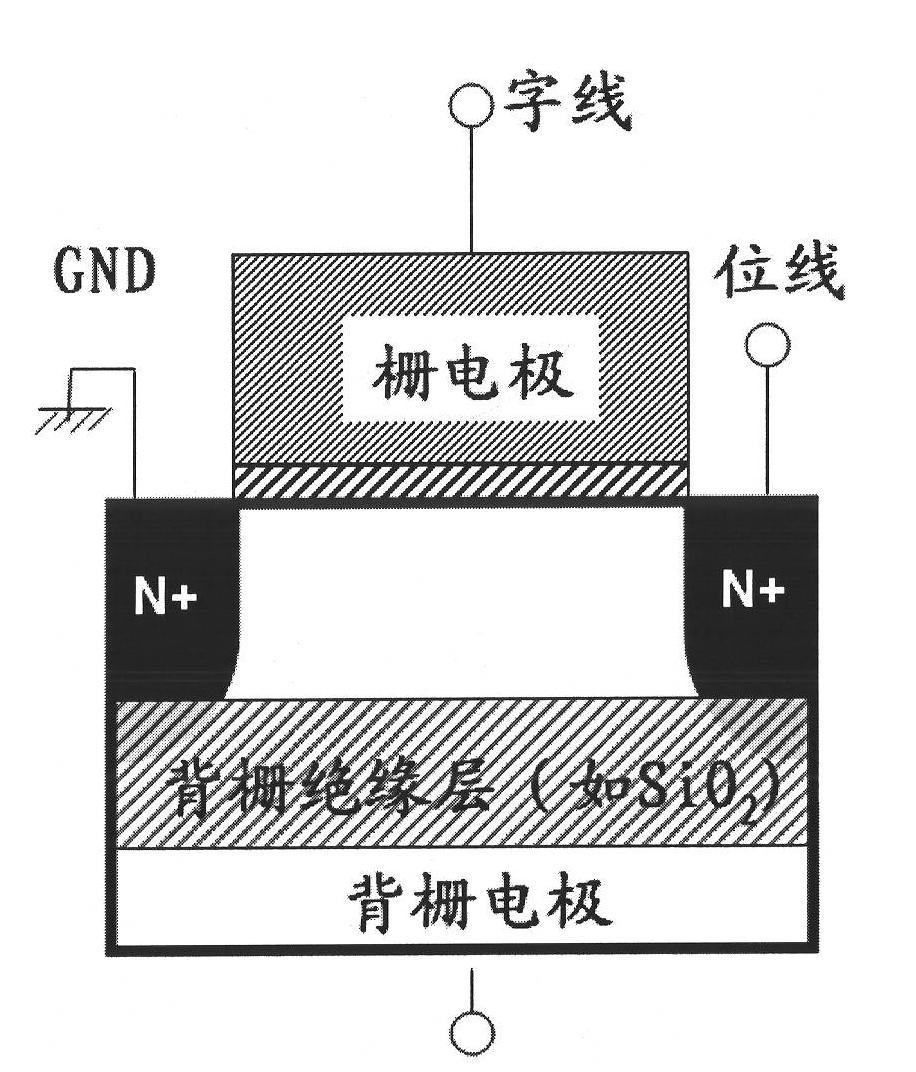

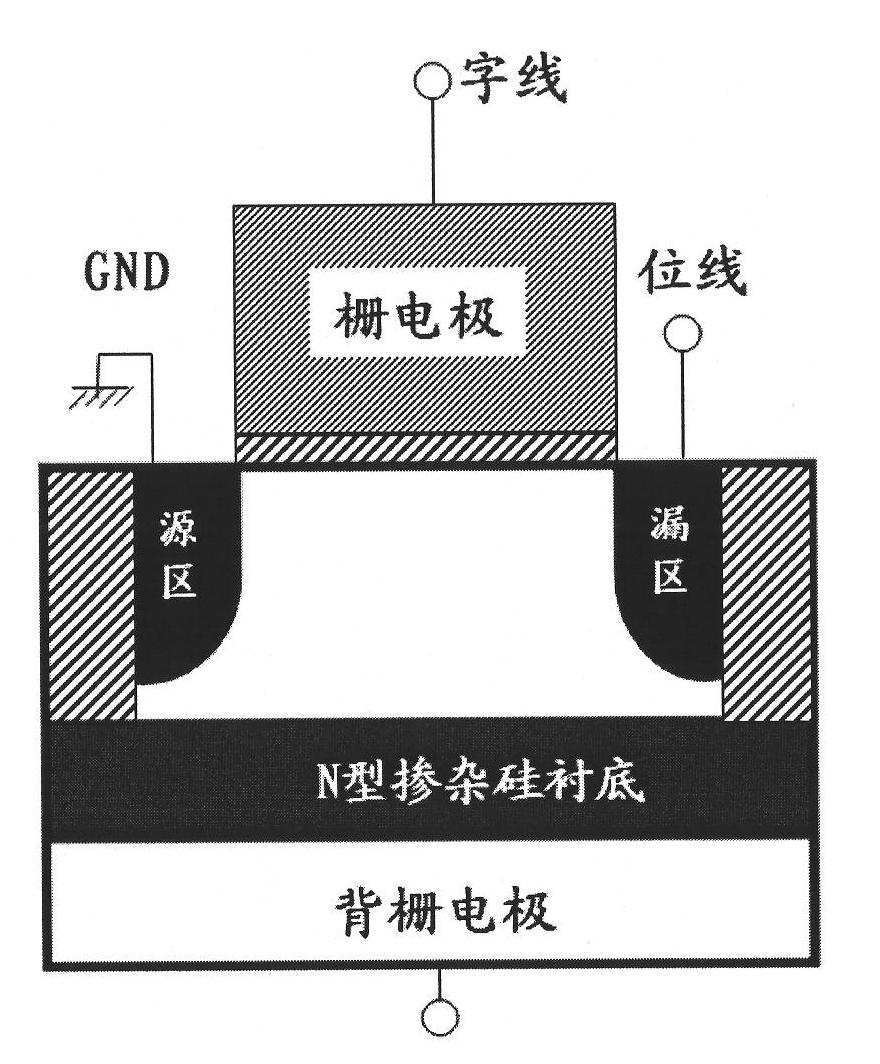

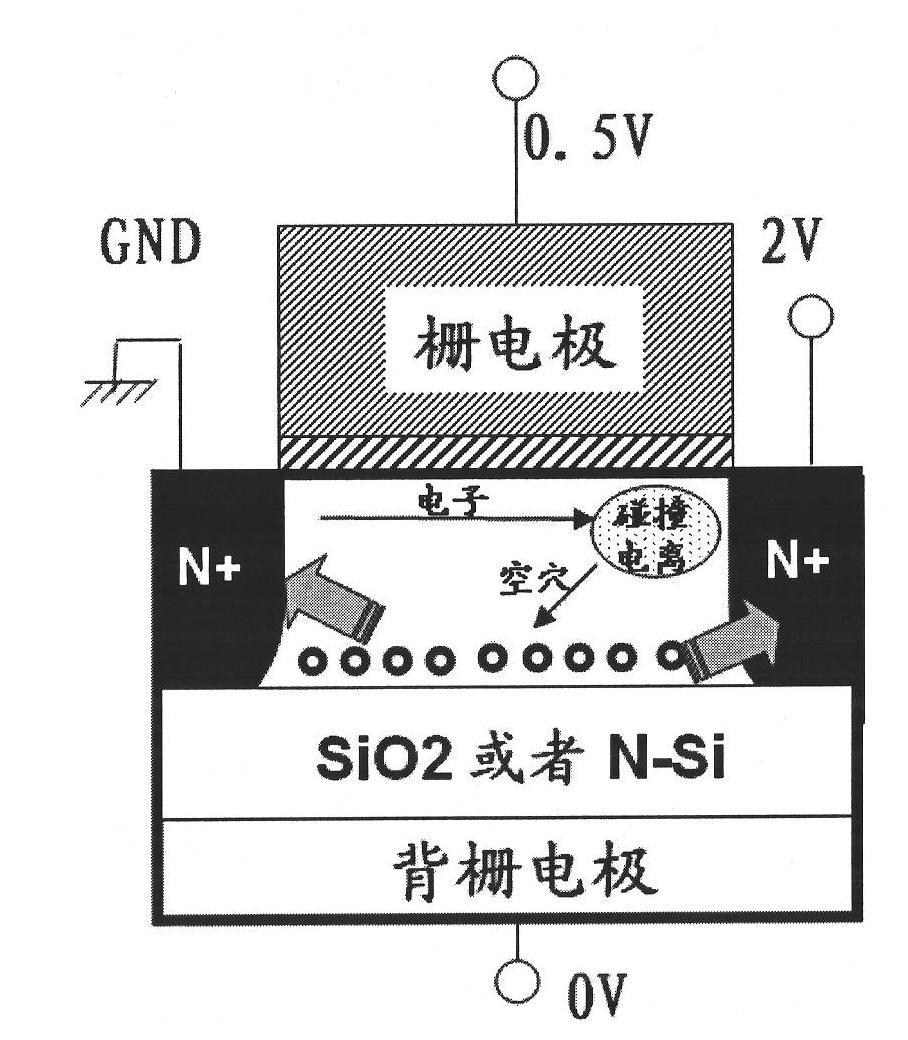

Semiconductor memory cell, device and preparation method thereof

ActiveCN102468303AReduce movement speedExtended hold timeTransistorSemiconductor/solid-state device manufacturingFloating body effectSource area

The invention discloses a semiconductor memory cell, a device and a preparation method thereof. The semiconductor memory cell comprises: a substrate, a channel region located above the substrate, a grid region located above the channel region, a source area and leakage area located above the substrate and on two sides of the channel region, a buried layer located between the substrate and the channel region and is made by a material whose forbidden bandwidth is narrower than the forbidden bandwidth of the channel region material. Because the forbidden bandwidth of the buried layer is narrower than the forbidden bandwidth of the channel region material, a hole barrier is formed in the buried layer so that the hole stored in the buried layer is difficult to be leaked out facing the barrier. By using the method of the invention, information maintaining time of the memory cell using a floating body effect can be increased.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

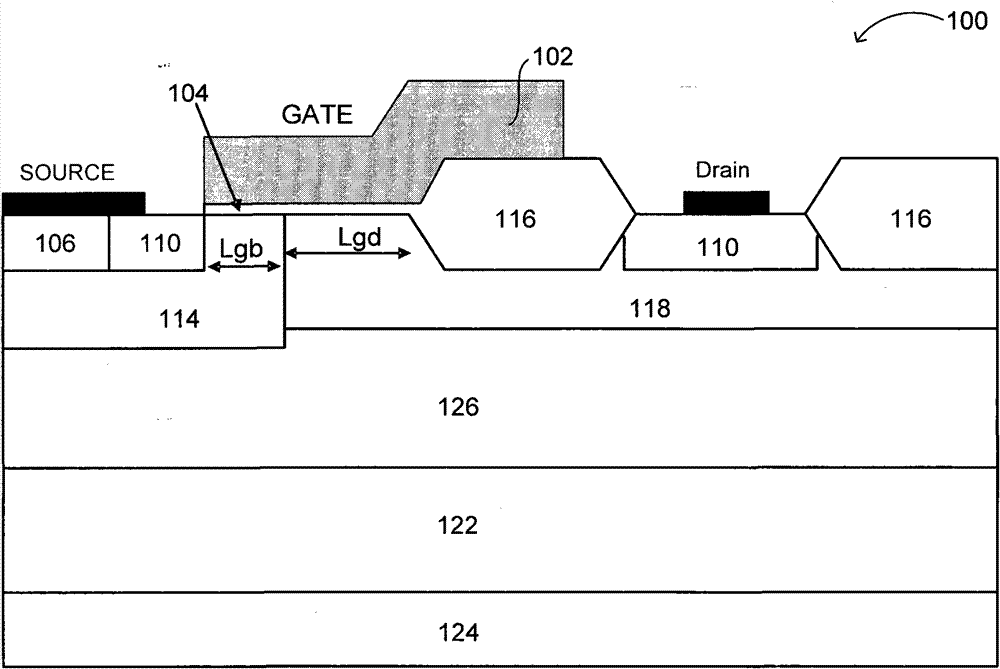

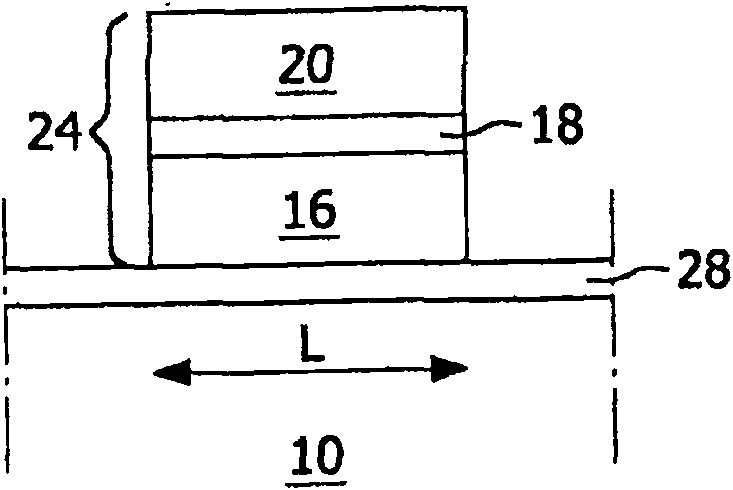

Manufacturing process of a semiconductor non-volatile memory cell

ActiveUS7262098B2Easy process integrationImprove electrical performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerSemiconductor

A process for manufacturing a non-volatile memory cell having at least one gate region, the process including the steps of depositing a first dielectric layer onto a semiconductor substrate; depositing a first semiconductor layer onto the first dielectric layer to form a floating gate region of the memory cell; and defining the floating gate region of the memory cell in the first semiconductor layer. The process further includes the step of depositing a second dielectric layer onto the first conductive layer, the second dielectric layer having a higher dielectric constant than 10. Also disclosed is a memory cell integrated in a semiconductor substrate and having a gate region that has a dielectric layer formed over a first conductive layer and having a dielectric constant higher than 10.

Owner:MICRON TECH INC

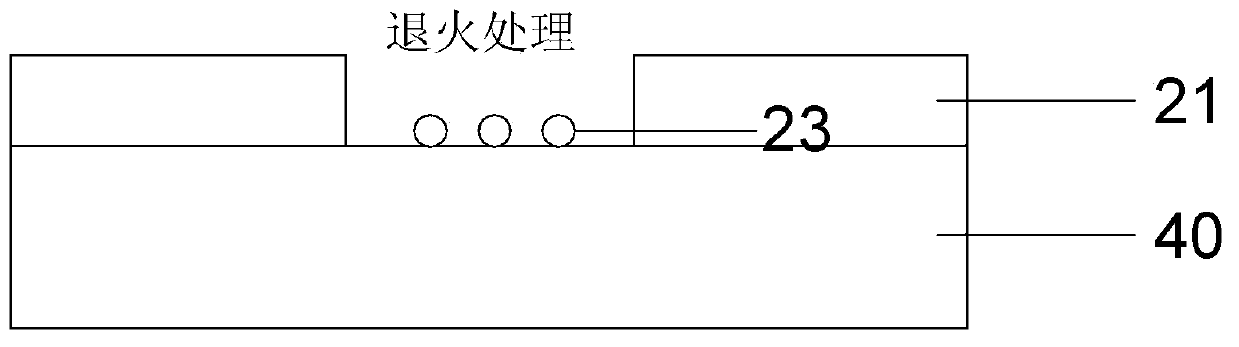

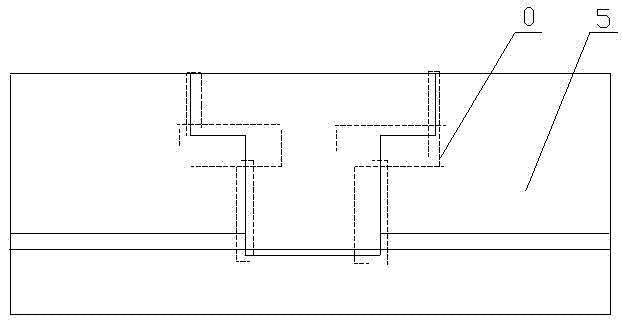

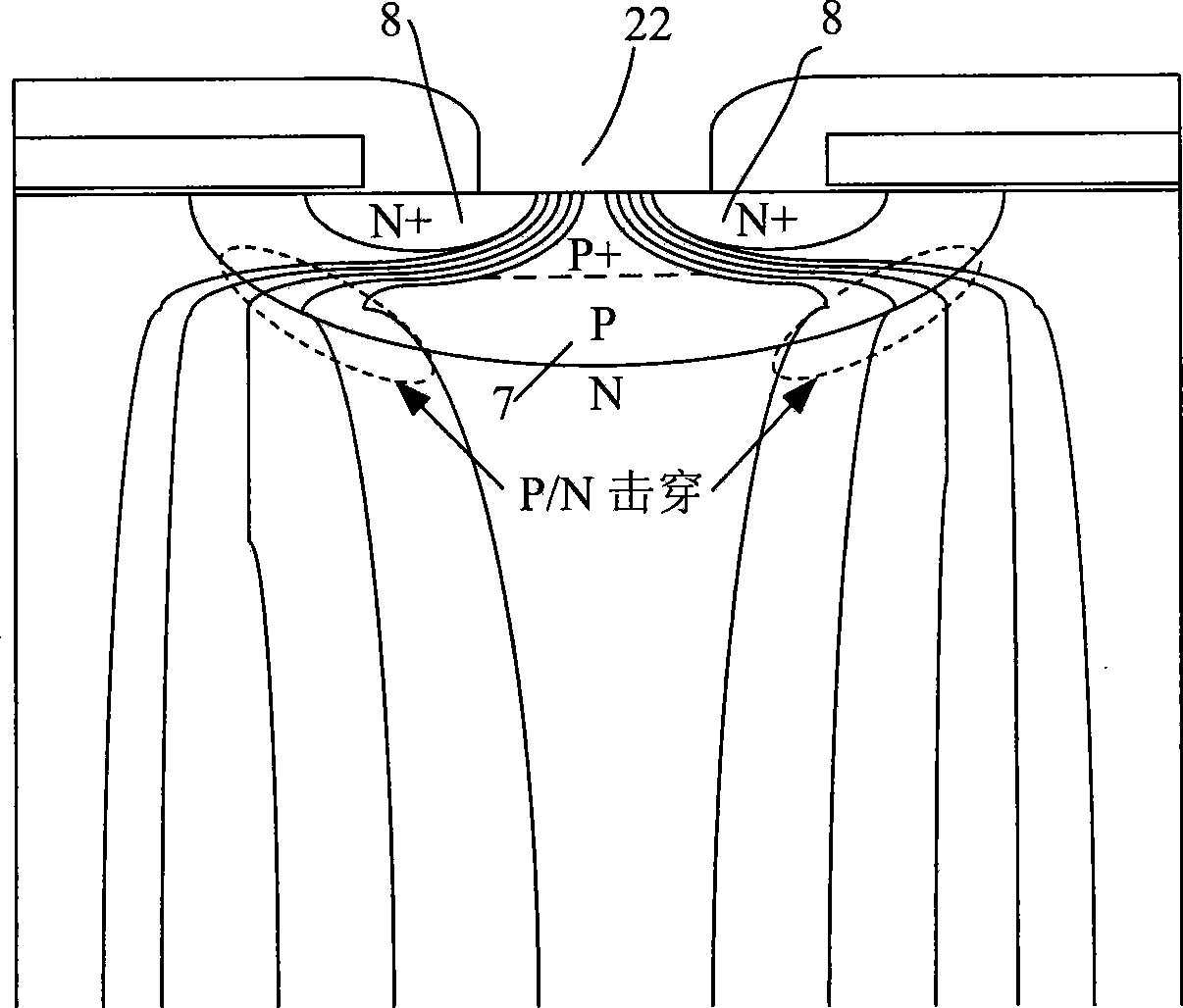

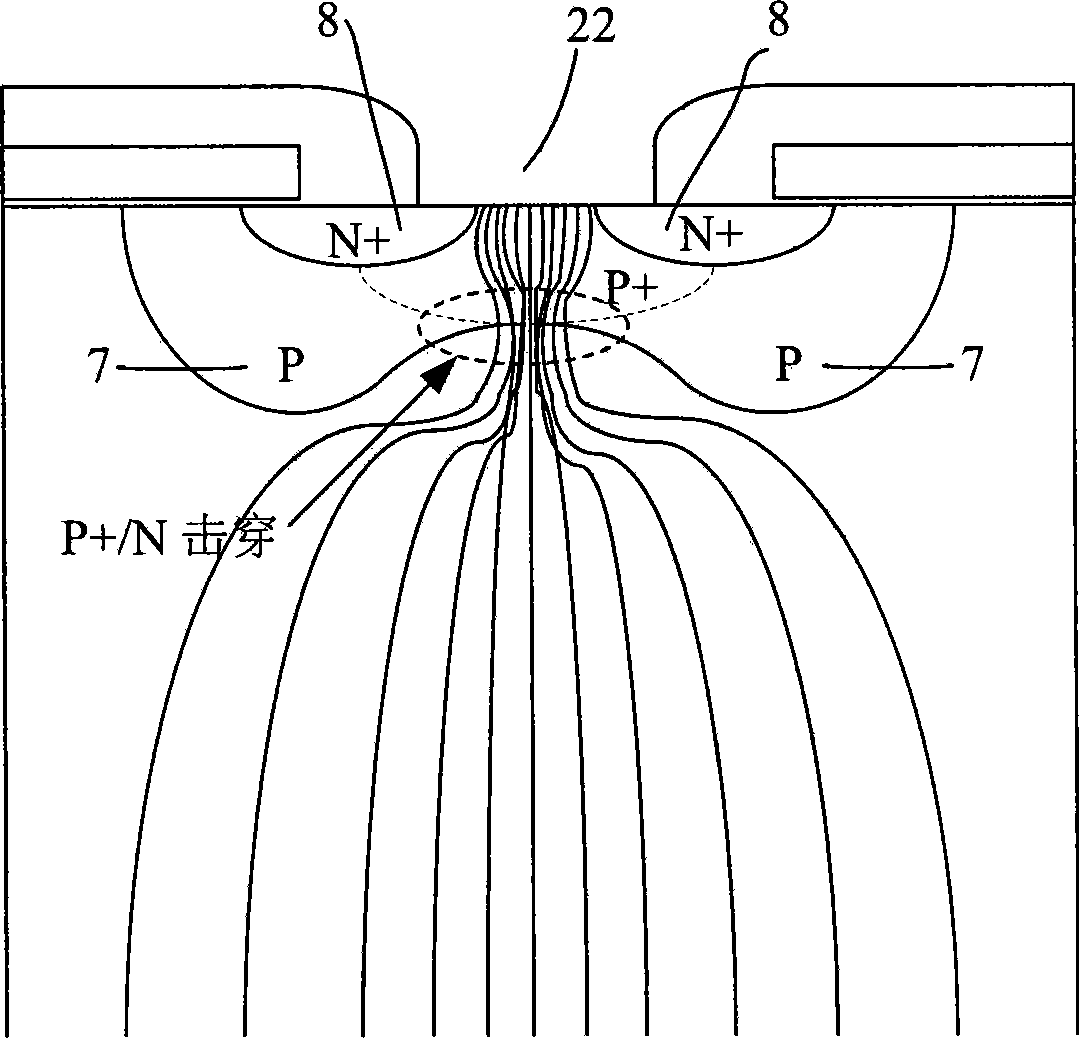

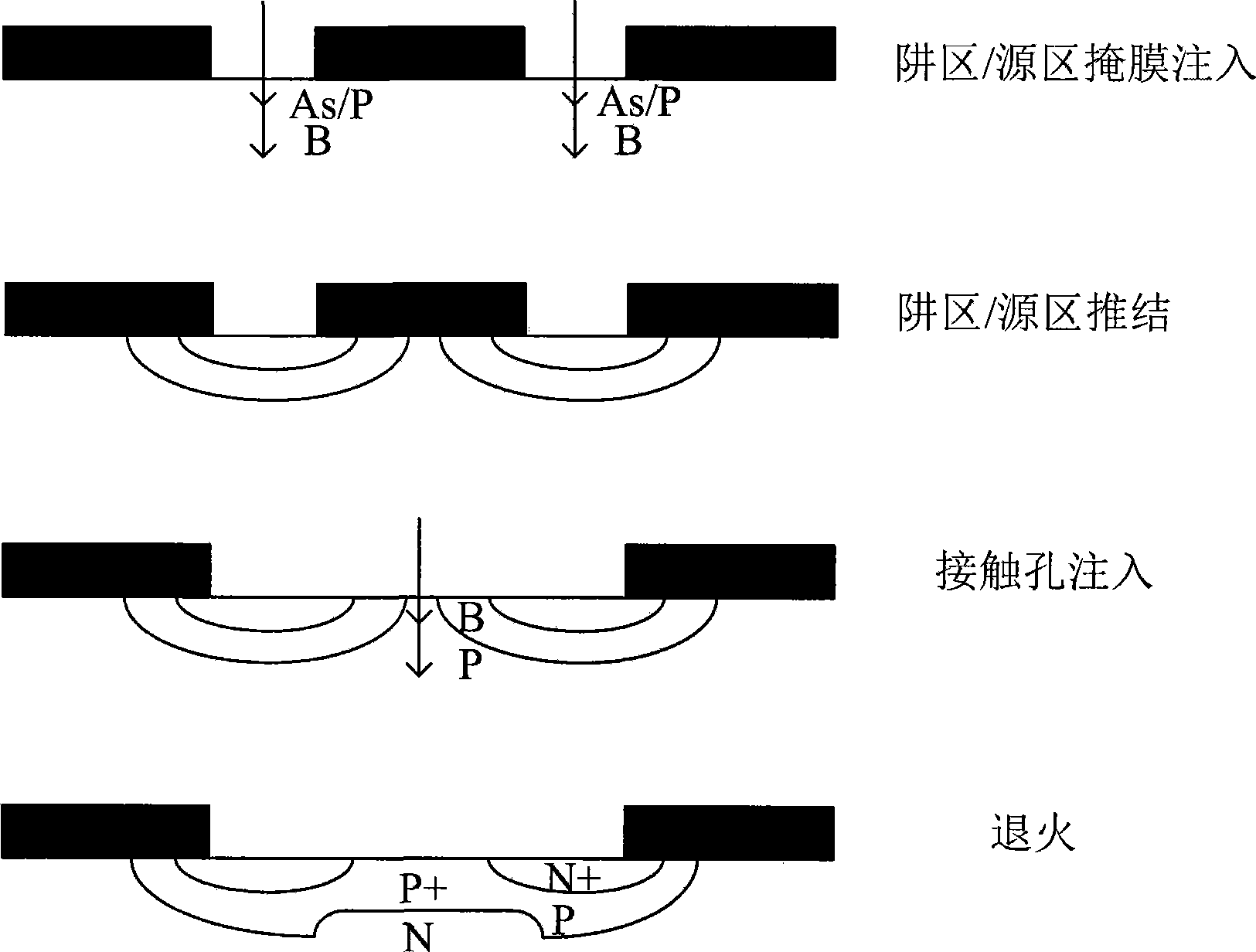

Method for implementing well division construction in super-high density slot type power device design

InactiveCN101393857AShorten the development cycleReduce R&D costsSemiconductor/solid-state device manufacturingHigh densityHigh energy

The invention relates to a novel method for achieving a Split Well structure in the design of an ultrahigh-density groove-type power device, and is effective in solving the problem that the Split Well structure (21) is incompatible with the ultrahigh-density design. Based on the impurity compensation theory, the method is characterized in that the high-energy N-type ion injection (18) and the quick annealing are carried out through a contact hole (22) so as to ensure that the Split Well structure (21) is formed at the bottom part in the middle of a well area (7). With the contact hole (22) over-etched below a silicon surface (23), the process ensures that the energy demand for sequential N-type ion injections is effectively reduced, thereby reducing the probability of injection damage to the well area (7) with less leakage sources that cause current to leak out from the device. Moreover, a higher integrated level can be attained with the Split Well structure 21 achieved in Z direction. The novel Split Well technology leads to a substantial improvement on the design of the device which ensures the long-standing reliability of the device as well as the workability of the on-resistance of the device, the firmness of the device and the reverse recovery characteristic of the body diode of the device.

Owner:成都方舟微电子有限公司

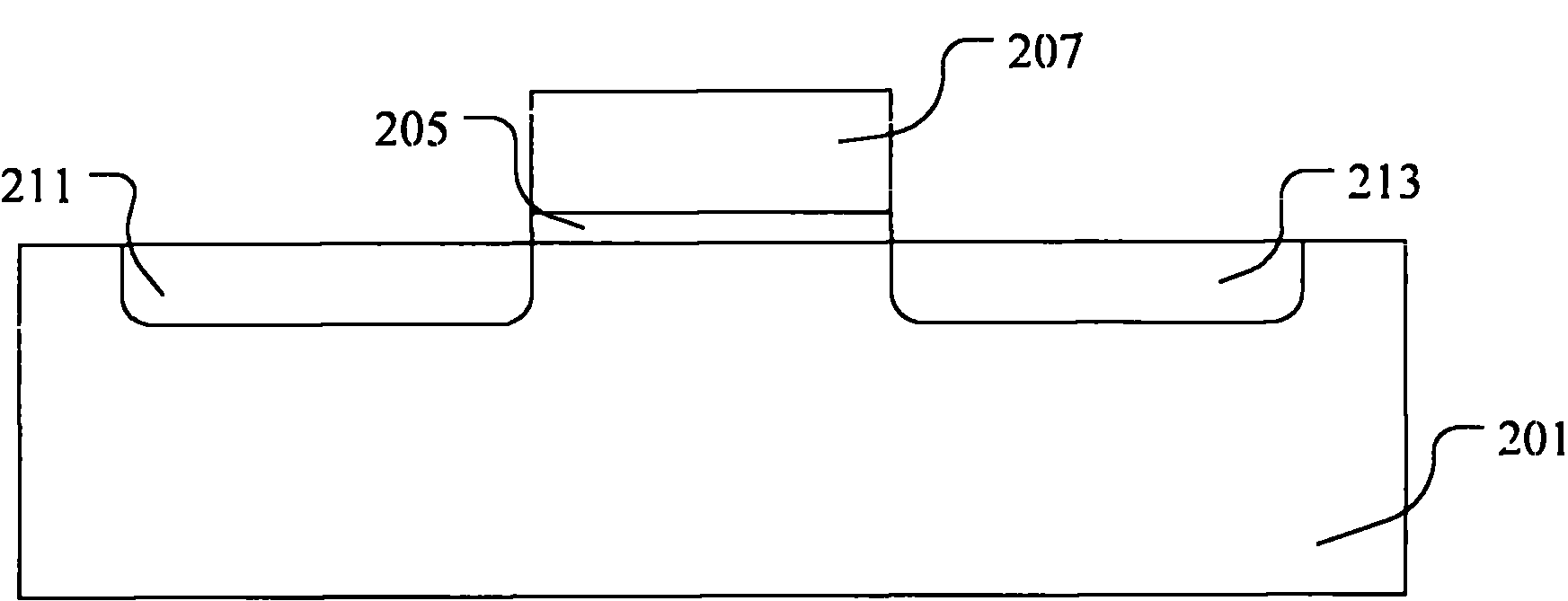

Polysilicon gate, semiconductor device and formation method thereof

ActiveCN101593684AImprovement of root defectsLess root defectsSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPolysilicon gate

A polysilicon gate formation method comprises the steps as follows: forming a sacrifice layer on a substrate; forming a groove in the sacrifice layer and exposing the substrate by the groove; forming a stratum layer covering the sacrifice layer as well as the side wall and the bottom wall of the groove; forming a polysilicon layer covering the stratum layer and filling the groove; executing planarization operation and removing the stratum layer covering the sacrifice layer; and removing the sacrifice layer. The invention also provides a polysilicon gate, so that the root defects of the formed polysilicon gate can be improved. The invention further provides a semiconductor device formation method and a semiconductor device, thus having fewer polysilicon gate root defects after being formed.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Filter and manufacturing method thereof

PendingCN109616726AThe number of stages in the passband increasesSmall sizeWaveguide type devicesHigh resistanceCavity resonance

The invention discloses a filter and a manufacturing method thereof, the filter comprises at least one silicon cavity resonance unit, and the silicon cavity resonance unit comprises a bottom metal layer, a high-resistance silicon dielectric layer and a top metal layer which are sequentially arranged. The edge of each silicon cavity resonance unit is provided with a plurality of through structures.The through structure penetrates through the bottom metal layer, the high-resistance silicon dielectric layer and the top metal layer. A metal deposition layer is formed on the surface of the inner side of the through structure. The penetrating structure is a through hole and / or a through groove. A slot line type stepped impedance resonator is also included and is composed of a plurality of slotlines which are formed on the top metal layer and communicate with one another. The depth of the slot line is equal to the thickness of the top metal layer. According to the filter and the manufacturing method thereof, the problems that an existing filter is large in size and multi-chip integration is not easy to achieve are solved.

Owner:GUANGDONG DAPU TELECOM TECH CO LTD

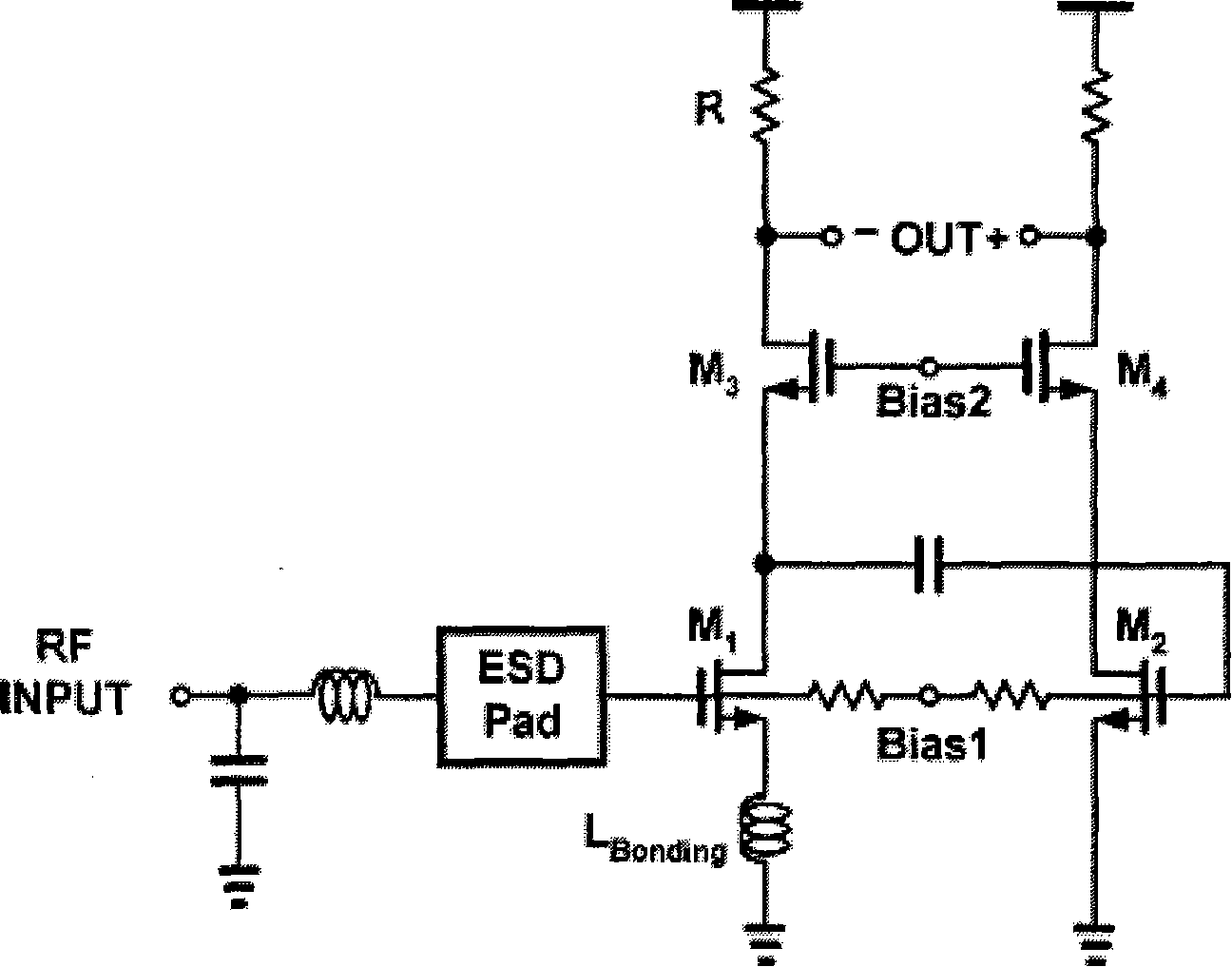

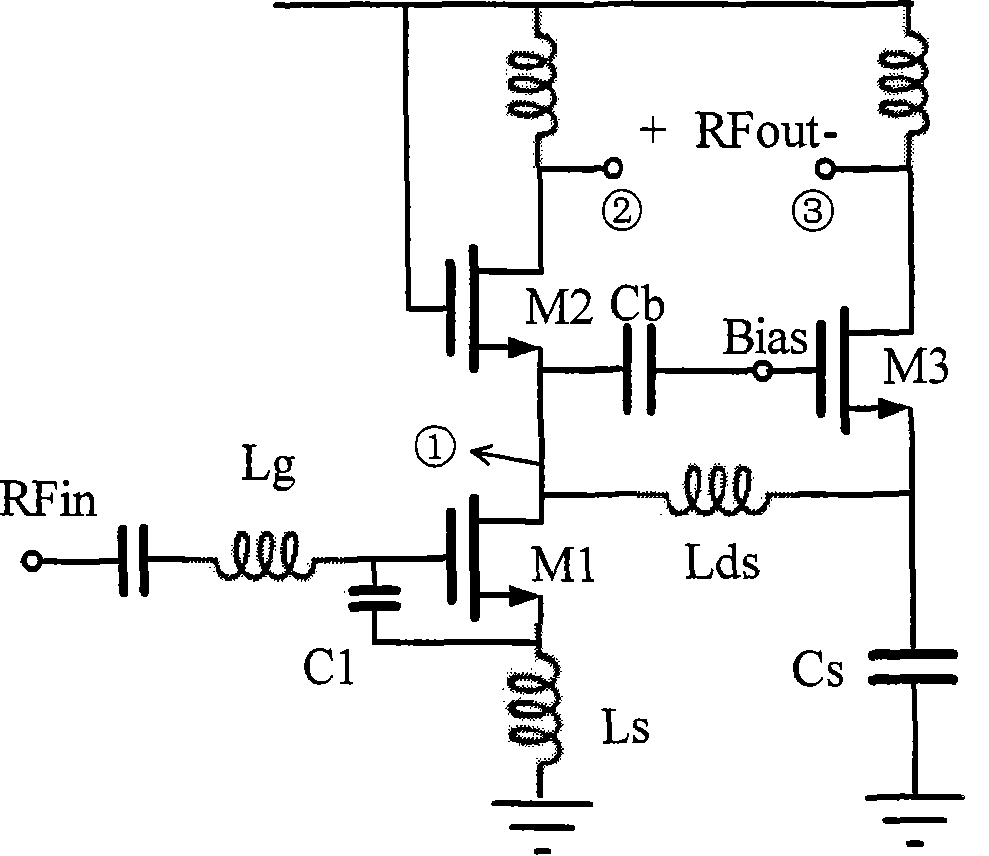

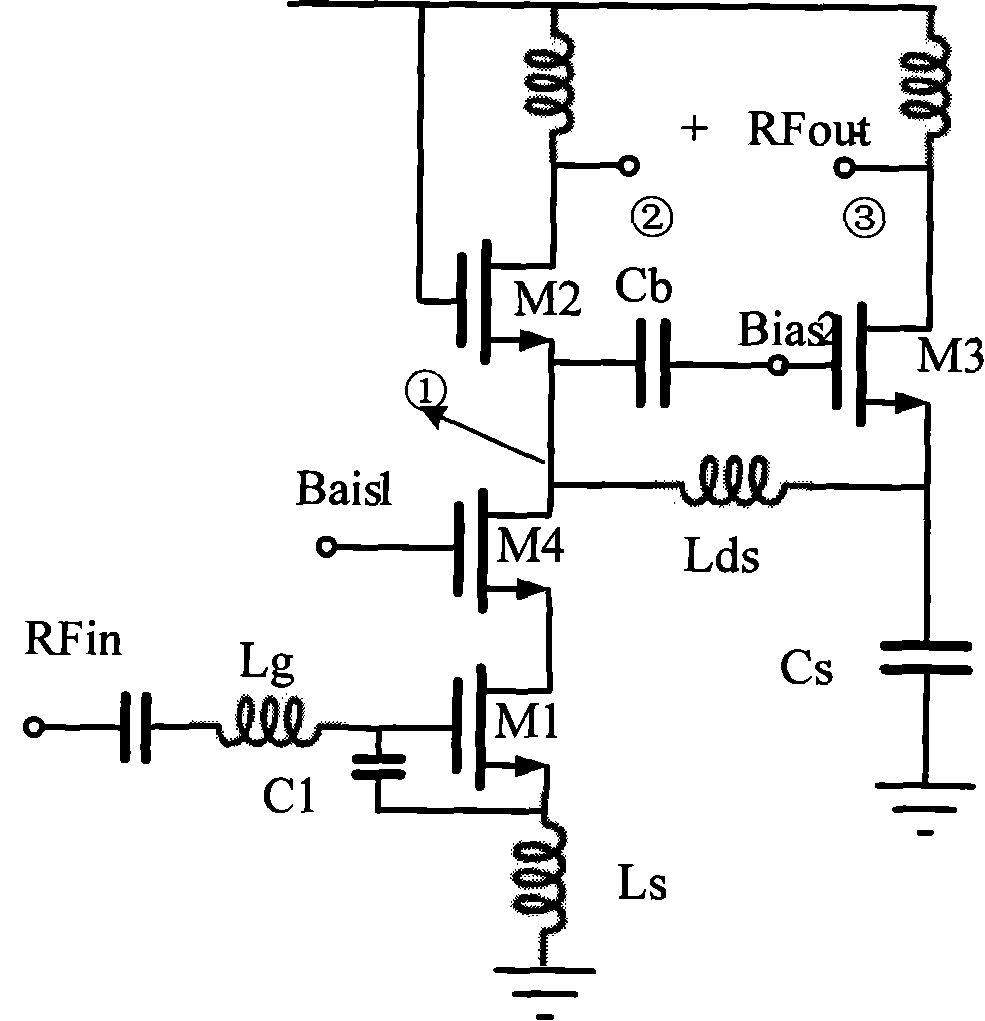

Low-power consumption single-ended input difference output low-noise amplifier

InactiveCN101282110BReduce power consumptionImprove Noise PerformanceAmplifier modifications to reduce noise influenceDifferential amplifiersAudio power amplifierDc current

The invention discloses a low power dissipation single end input difference output low noise amplifier, belonging to radio frequency communication technical field. The amplifier comprises an input matching circuit, a first stage amplifying circuit, a second stage common grid amplifying circuit and a second stage comon source amplifying circuit which are connected with each other, and an output load matching circuit, the input matching circuit is connected with the first stage amplifying circuit, a control circuit is provided between the first stage amplifying circuit and the second stage comon source amplifying circuit, the control circuit is used for controlling direct current flowing to the second stage common grid amplifying circuit to flow to the first stage amplifying circuit, meanwhile, stops the radio frequency signal outputted by the first stage amplifying circuit to flow to the source end of the second stage comon source amplifying circuit, the second stage comon source amplifying circuit and the second stage common grid amplifying circuit are respectively connected with one output load matching circuit. The invention can resuce half of the system power consumption, and the second amplifying circuits are symmetrical, thereby ensuring output noise, phase and gain of the differential signal more symmetrical.

Owner:PEKING UNIV

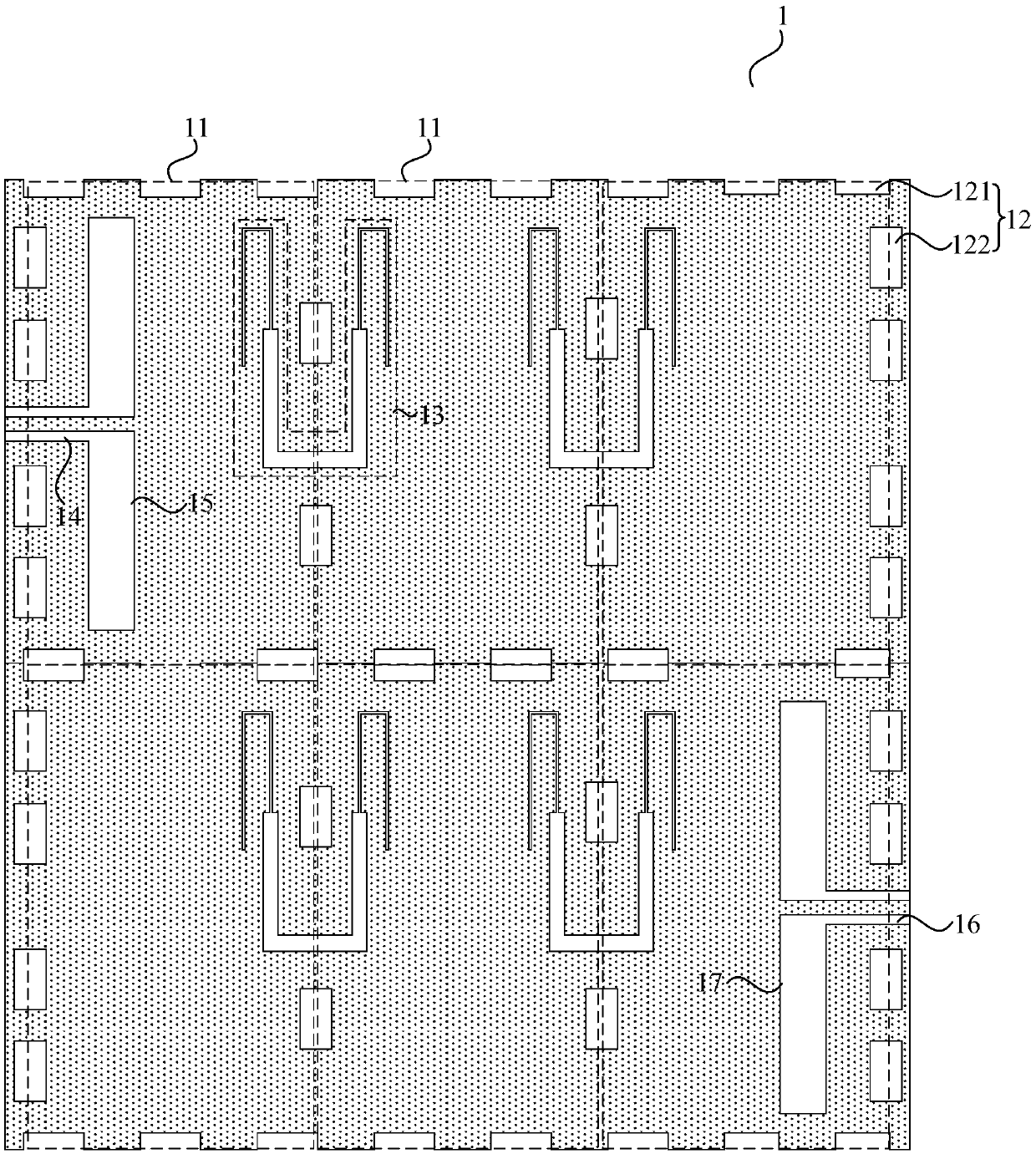

Low-loss silicon-based filter chip capable of improving reuse rate and manufacturing method thereof

ActiveCN111430318AHigh out-of-band rejectionReduced adhesion areaImpedence networksSemiconductor/solid-state device detailsEtchingMicromachinery

The invention discloses a low-loss silicon-based filter chip capable of improving reuse rate and a manufacturing method thereof. The silicon-based filter chip comprises a high-resistance silicon dielectric layer, a first metal layer, a second metal layer, a third metal layer and a fourth metal layer, the first metal layer is arranged on the top surface of the high-resistance silicon dielectric layer; a silicon cavity is formed in the bottom surface of the high-resistance silicon dielectric layer in a concave manner; the second metal layer is arranged in the silicon cavity; the third metal layer is arranged on the bottom surface of the high-resistance silicon dielectric layer and keeps away from the silicon cavity, the fourth metal layer is arranged on the bottom surface of the third metallayer, a through hole penetrating through the first metal layer upwards is formed in the high-resistance silicon dielectric layer, a metal deposition layer is arranged on the inner wall of the throughhole, and production is carried out through etching and micromachining processes. With application of the mode, the low-loss silicon-based filter chip capable of improving the reuse rate and the manufacturing method thereof are convenient to produce, the out-of-band rejection degree of the silicon-based filter chip is improved, loss is reduced and the reuse rate is high.

Owner:昆山鸿永微波科技有限公司

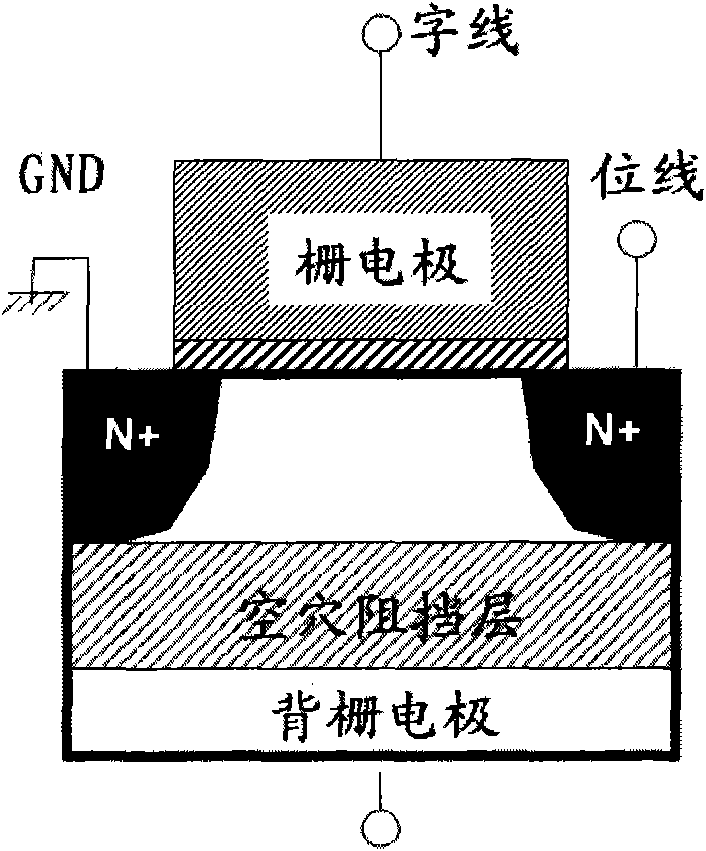

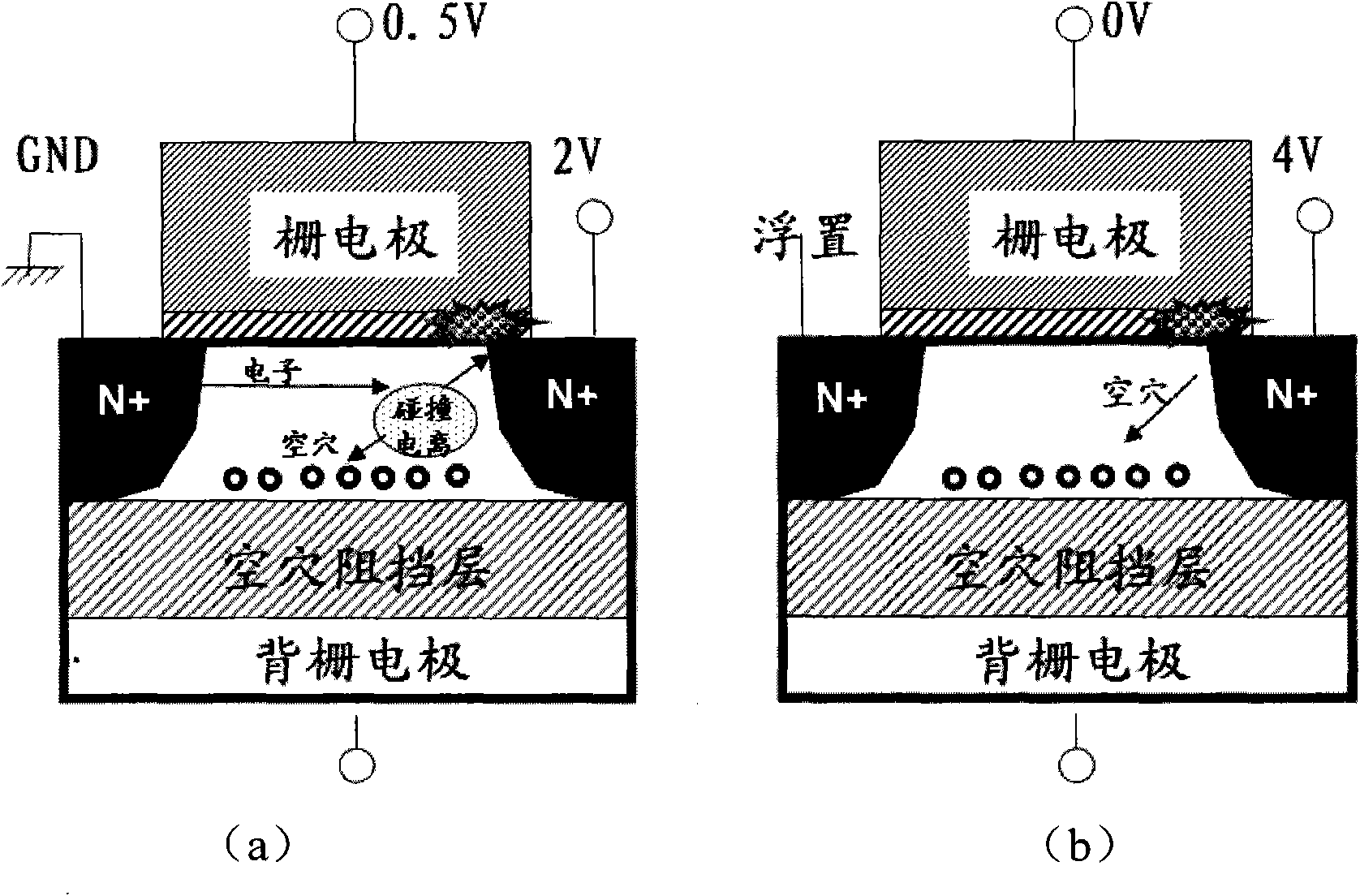

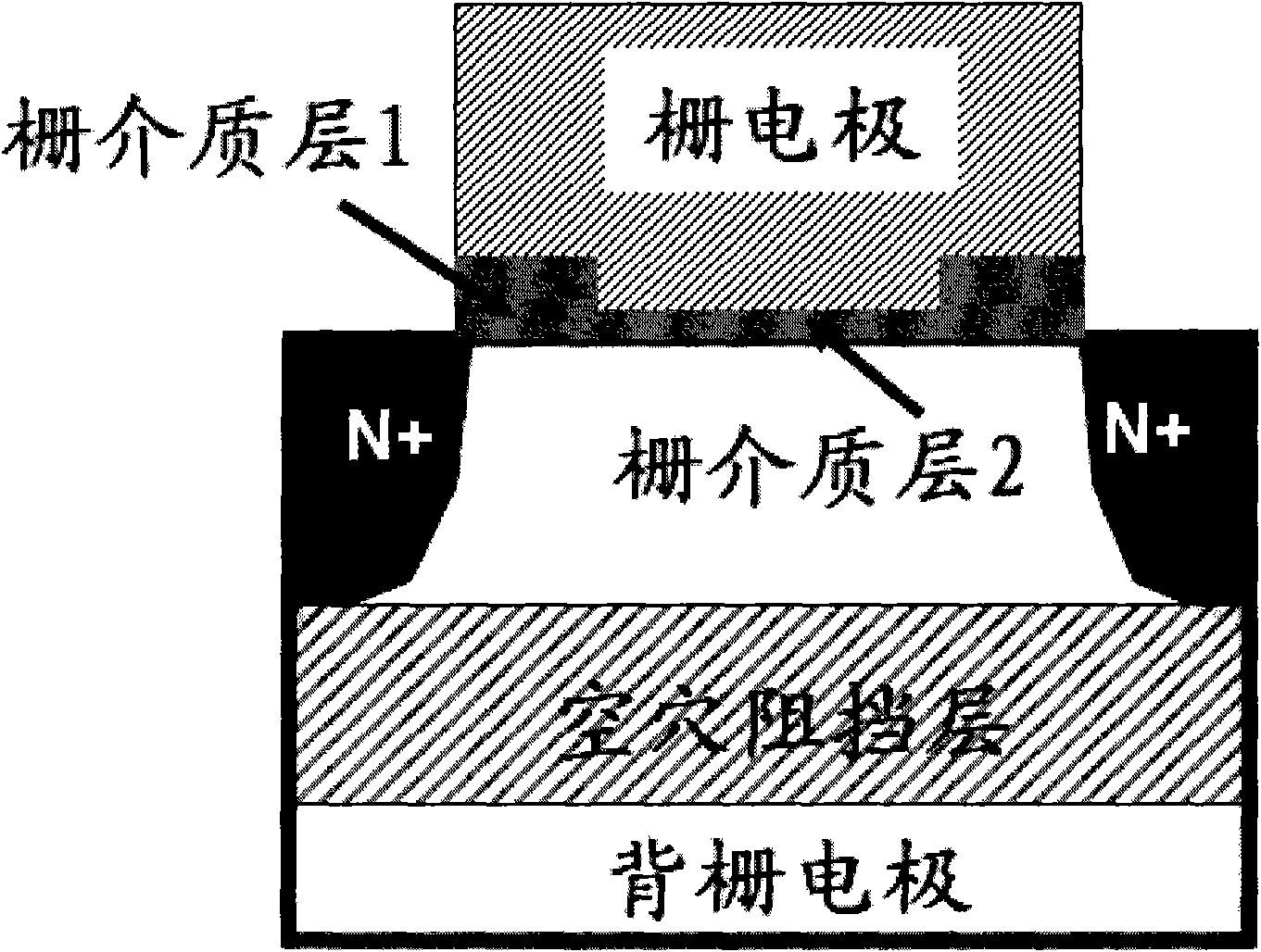

Capacitance-free dynamic random access memory structure and preparation method thereof

ActiveCN102376715BIncrease electrical thicknessPrevent degradationTransistorSemiconductor/solid-state device manufacturingCapacitanceHigh density

The invention discloses a capacitance-free dynamic random access memory structure and a preparation method thereof. Under the premise that the capacitance-free dynamic random access memory structure meets high voltage leakage requirements for a high impact ionization rate, the electrical thickness of a gate medium in a source drain junction area is increased via adoption of different gate medium materials or gate medium thicknesses near the area, an electric field in the vertical direction is reduced effectively. Meanwhile, a thin oxidation layer or a high K material is adopted in the central area of a channel, the gate control capability is improved, and the short channel effect is inhibited. By adopting the structure, the degradation of the gate medium can be inhibited effectively, the reliability (durability) of a storage unit can be improved, the scaling-down of a device can be facilitated, and the complex process for the capacitance structure in the conventional 1T1C structure can be avoided completely in the capacitance-free structure. The adopted manufacturing process is completely compatible with the conventional logic process, and the high-density three-dimensional process integration can also be facilitated.

Owner:宁夏储芯科技有限公司

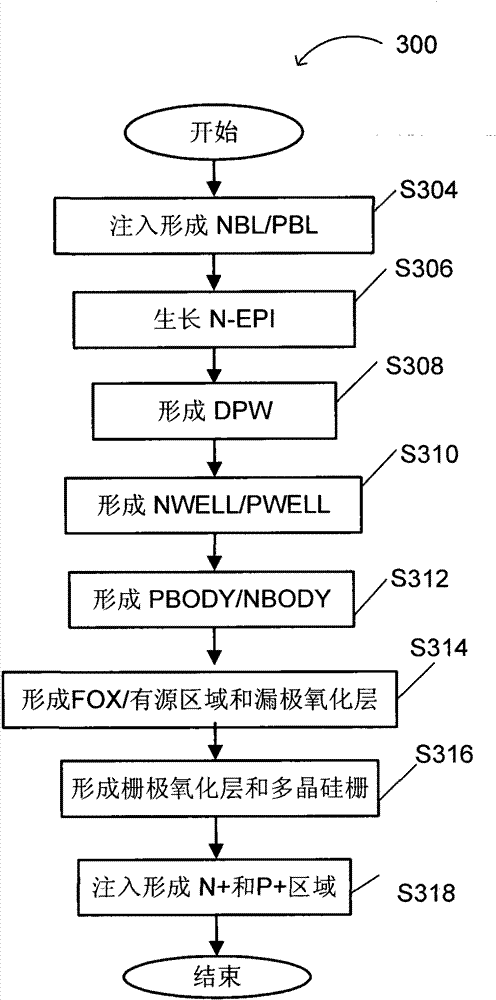

Method for manufacturing lateral double-diffused metal oxide semiconductor transistor

ActiveCN101819937BOptimize push timeDoes not affect process stepsSolid-state devicesSemiconductor/solid-state device manufacturingLDMOSEngineering

The invention relates to a lateral double-diffused metal oxide semiconductor transistor, namely an LDMOS transistor, and a structure, a manufacturing method and application. According to one embodiment of the invention, the method for manufacturing the LDMOS transistor with a source electrode region, a drain electrode region and a grid region on a substrate, includes: generating a P-typed bury layer region and a n-typed bury layer region, growing an external layer on the NBL / PBL region, forming a p-doped deep p-well region on the PBL region, forming a well region on the external layer, forming a doped body region, then forming a active region and a field oxidation region and forming a drain oxidation layer between the LDMOS transistor source region and the drain region, after the form of the doped body region, forming a grid oxidation layer approaching the source and drain region and forming a grid on the grid oxidation layer and one part of drain oxidation layer, then forming a dopeddrain region, and a first doped source region and a second doped source region.

Owner:SILERGY SEMICON TECH (HANGZHOU) CO LTD

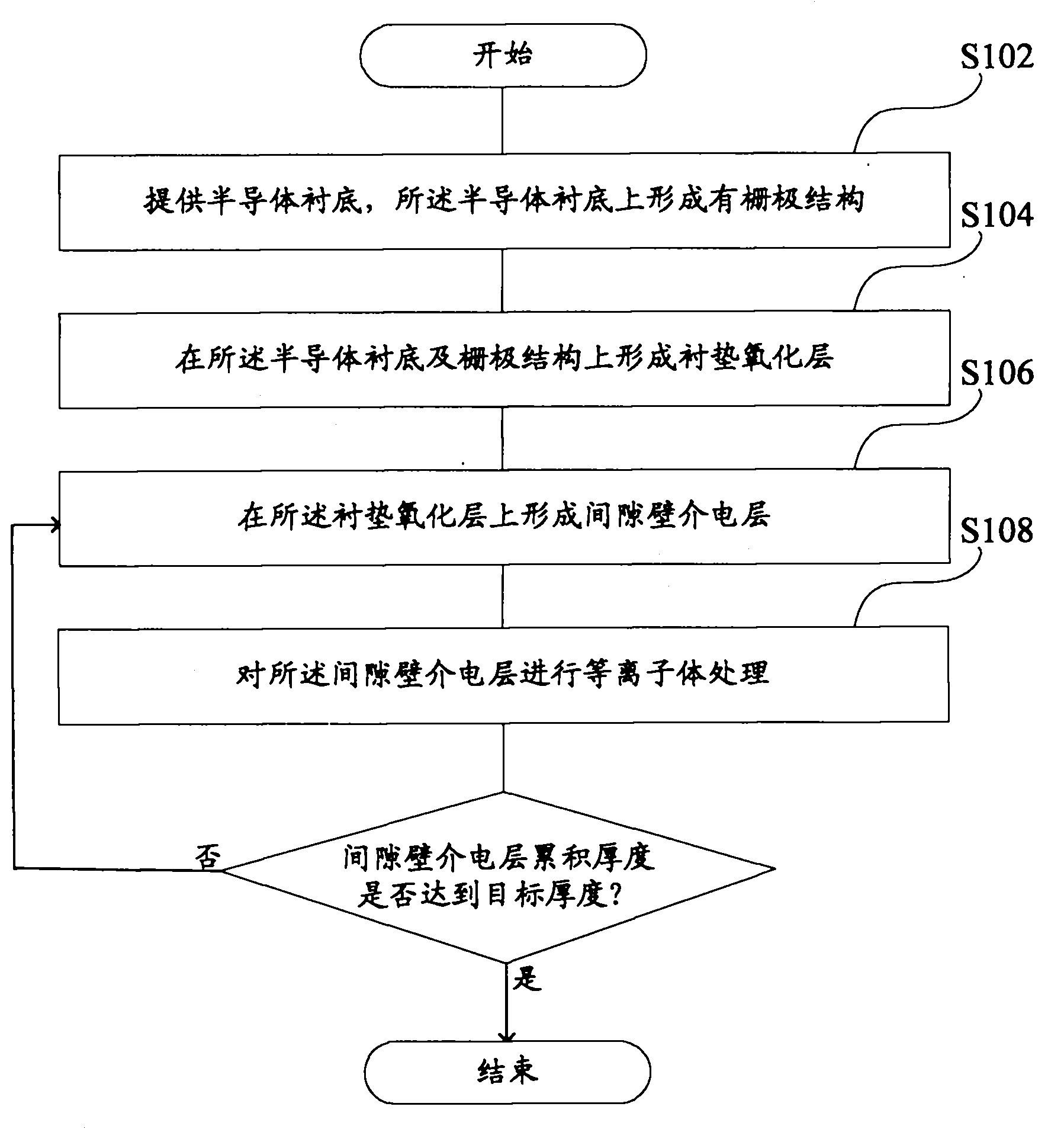

Making method for MOS (Metal Oxide Semiconductor) transistor

InactiveCN102214575ASmall thickness deviationImprove consistencySemiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerSemiconductor

The invention provides a making method for a MOS (Metal Oxide Semiconductor) transistor. The making method comprises the following steps: providing a semiconductor substrate on which a gate structure is formed; forming a liner oxidation layer on the semiconductor substrate and the gate structure; forming a clearance wall dielectric layer on the liner oxidation layer; performing plasma treatment on the clearance wall dielectric layer; and repeating the formation process of the clearance wall dielectric layer and the formation process of the plasma treatment for at least one time until the accumulated thickness of the clearance wall dielectric layer reaches the target thickness. The making method for the MOS transistor provided by the invention reduces the thickness deviation of the MOS transistor clearance walls in different areas of the thickness of the devices on the semiconductor substrate, thus consistency in effective trench lengths of the MOS transistors can be improved and consistency in the performances of the MOS transistors can be further improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Non-volatile memory device having a gap in the tunnuel insulating layer and method of manufacturing the same

InactiveCN101375373BImprove reliabilityExtended storage timeTransistorSolid-state devicesDielectric layerSemiconductor

A non- volatile memory device (1, 101, 201, 301) having a gap within a tunnel dielectric layer (14, 114, 214, 314) and a method of manufacturing the same is provided. The devices have a stack of layers on top of a substrate (10, 110, 210, 310) including, a charge tunneling layer with a gap (14, 114, 214, 314), a charge storage layer (16, 116, 216, 316), a control gate layer (20, 120, 220, 320) andan insulating layer (18, 118, 218 220) in between the charge storage layer and the control gate. Manufacturing proceeds through deposition of a sacrificial layer (28, 128,228,328) on parts of a substrate, whereupon a stack of layers (24, 124,224,324) including a charge-storage layer, an insulating layer and a control gate layer are formed. Subsequently, selected parts of the sacrificial layer areremoved, thereby forming a gap in between the charge storage region and the substrate. The gap is protected from future processing by deposition of a sealing layer (34, 134, 234, 334). Such a devicehas a reduced operating voltage and its manufacture can be easily implemented in existing semiconductor processes.

Owner:NXP BV