Making method for MOS (Metal Oxide Semiconductor) transistor

A technology of MOS transistors and manufacturing methods, which is applied in the field of MOS transistor manufacturing, can solve problems such as performance deviations of MOS transistor devices, and achieve the effects of improving consistency, facilitating process integration, and reducing thickness deviations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

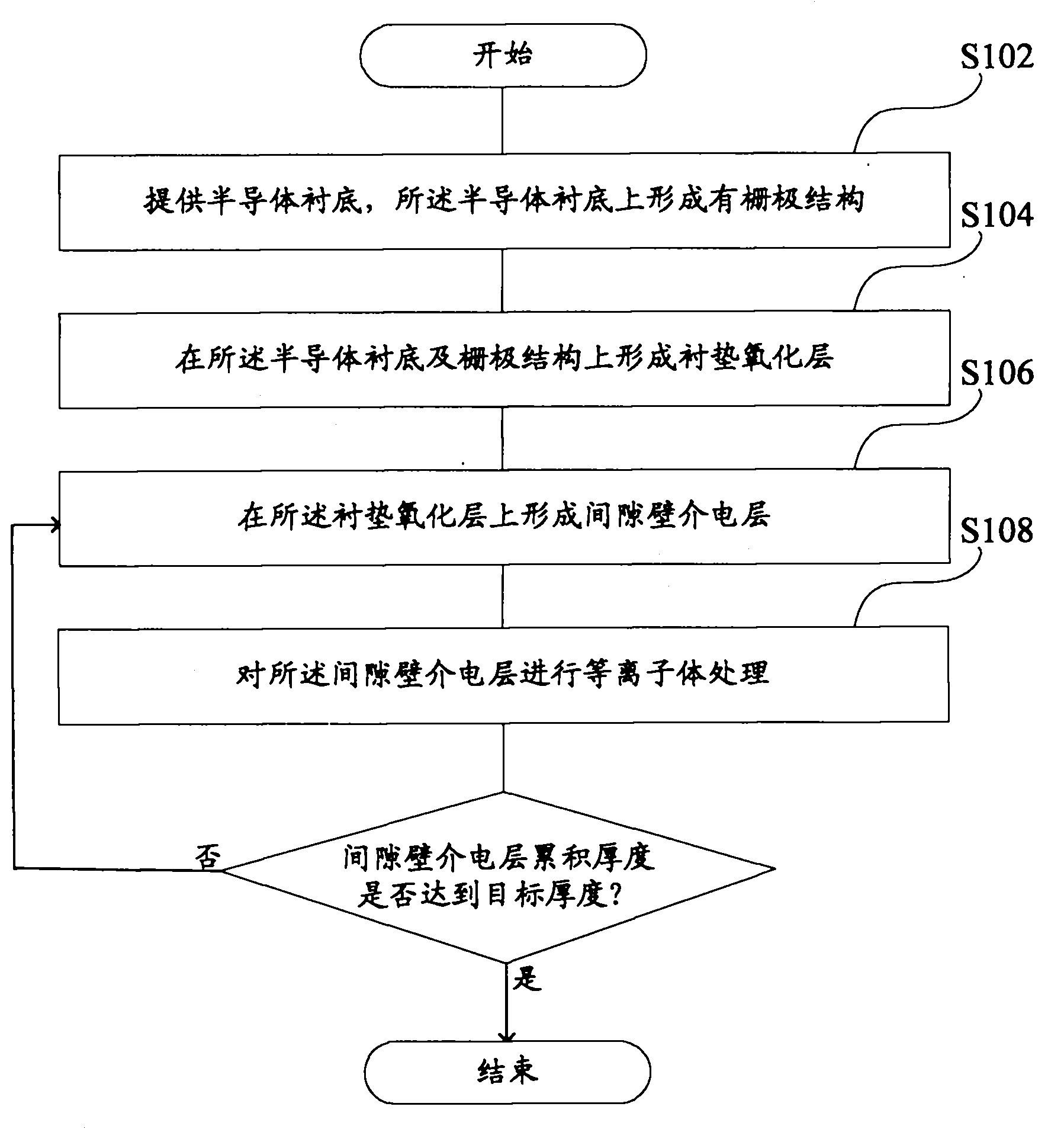

[0021] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0022] In the following description, many specific details are set forth in order to fully understand the present invention, but the present invention can also be implemented in other ways than those described here, so the present invention is not limited by the specific embodiments disclosed below.

[0023] As described in the background technology section, when forming a spacer dielectric layer in the prior art MOS transistor manufacturing method, due to the loading effect of plasma enhanced chemical vapor deposition, the thickness of the spacer dielectric layer varies with the thickness of the semiconductor substrate. The variation of device density will have large process deviation, and the thickness deviation of the spacer dielectr...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More