Semiconductor memory cell, device and preparation method thereof

A storage unit and semiconductor technology, applied in the field of microelectronics, can solve the problems of short data retention time of FBC, and achieve the effects of high-density three-dimensional process integration, improvement of retention characteristics, and reduction of refresh times

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

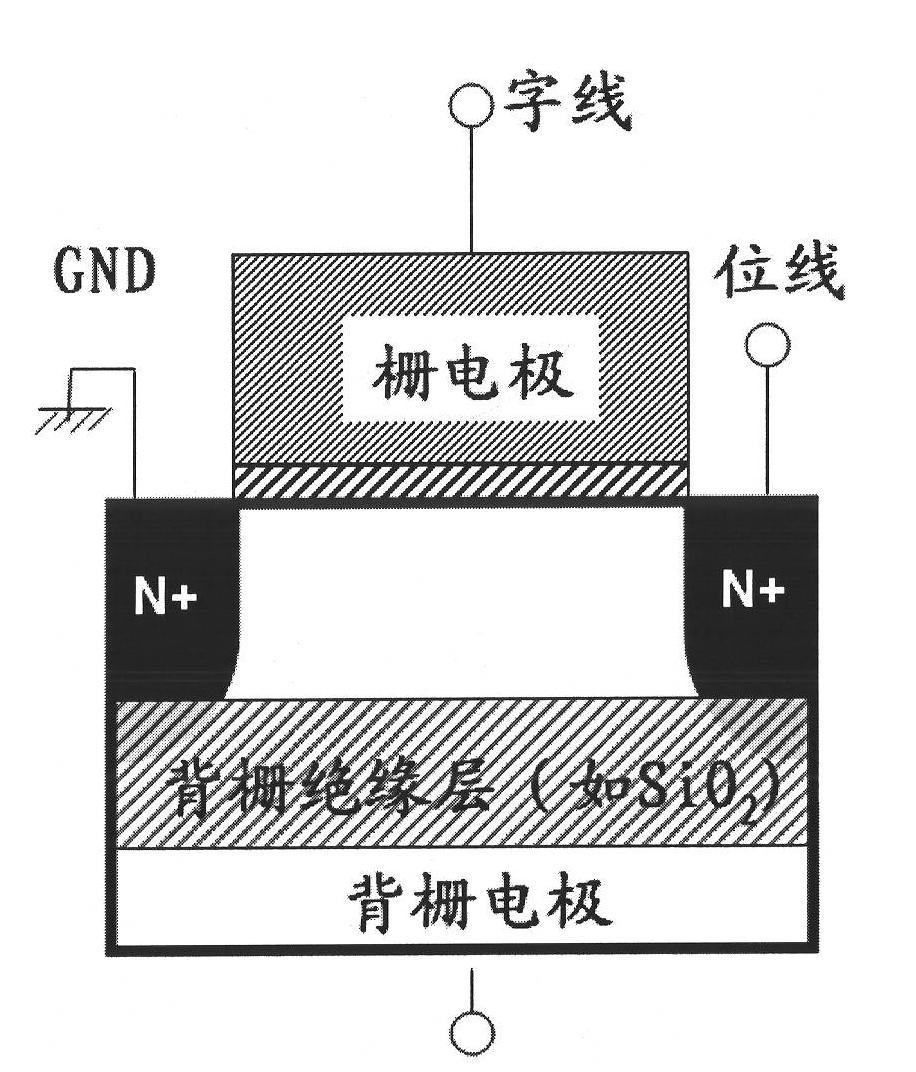

[0024] image 3 It is a schematic diagram of a semiconductor memory unit according to an embodiment of the present invention. Such as image 3 As shown, the semiconductor memory unit includes: a substrate; a channel region above the substrate; a gate region above the channel region; above the substrate, gate regions on both sides of the channel region a source region and a drain region; a buried layer located between the substrate and the channel region and made of a material whose forbidden band width is narrower than that of the channel region material.

[0025] In this embodiment, the material of the channel region is Si or stressed silicon, and the material of the buried layer is a group IV material or a III-V group material, such as Si x Ge 1-x , Ge, GaN, or InP; or the material of the channel region is Si x Ge 1-x , the material of the buried layer is Ge.

[0026] Since the forbidden band width of the buried layer is narrower than that of the material of the channe...

Embodiment 2

[0028] This embodiment will further optimize the technical solution on the basis of the first embodiment.

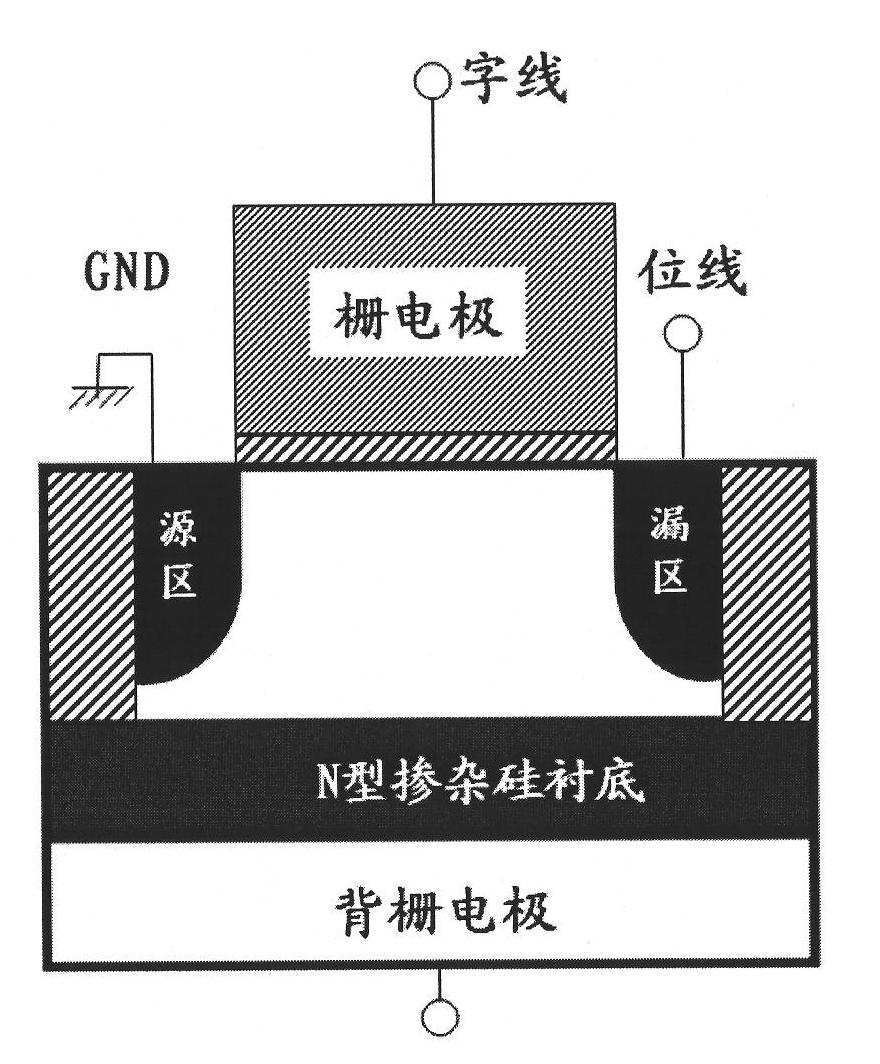

[0029] Figure 4 It is a schematic diagram of a semiconductor memory unit according to Embodiment 2 of the present invention. Such as Figure 4 In the shown semiconductor memory unit, an insulating layer is further included between the source / drain region and the substrate, on both sides of the buried layer. Preferably, the insulating layer is partially located between the channel region and the substrate. The material of the insulating layer is one of the following materials: Ge x o y , SiO 2 , SiC, Si x N y . The insulating layer can effectively reduce the area of the PN junction, thereby effectively reducing the leakage current of the PN junction from the substrate to the source region and from the substrate to the drain region.

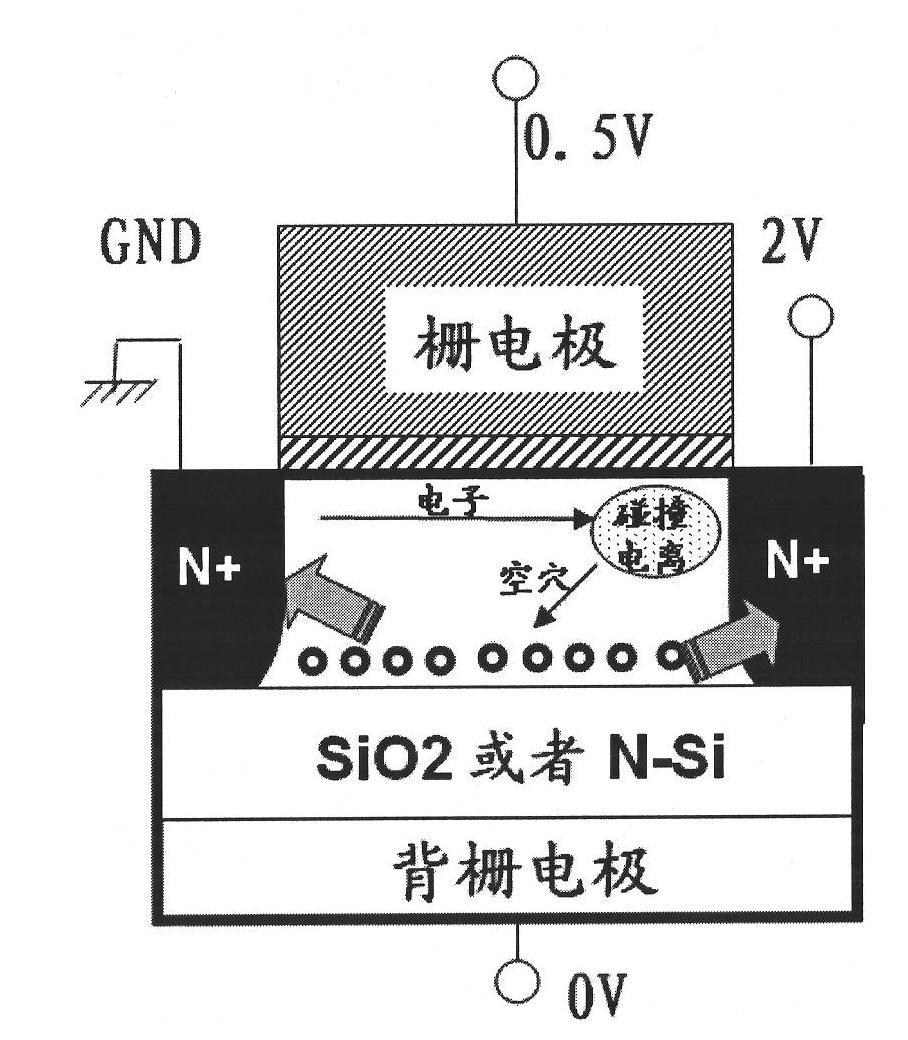

[0030] Figure 5 For the second embodiment of the present invention, the semiconductor storage unit is Figure 4 Schematic dia...

Embodiment 3

[0034] This embodiment provides a semiconductor storage device, which may include one or more semiconductor storage units disclosed in Embodiment 2 or Embodiment 2, and obtain corresponding technical effects.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More