Pressure sensor encapsulation structure containing silicon through holes

A technology of pressure sensor and packaging structure, which is applied in the direction of microstructure technology, measuring fluid pressure, microstructure device, etc., can solve the problems of expensive welding equipment, difficult production, and affecting the accuracy of pressure measurement, so as to reduce the packaging volume and weight, The effect of increasing test sensitivity and realizing local airtightness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

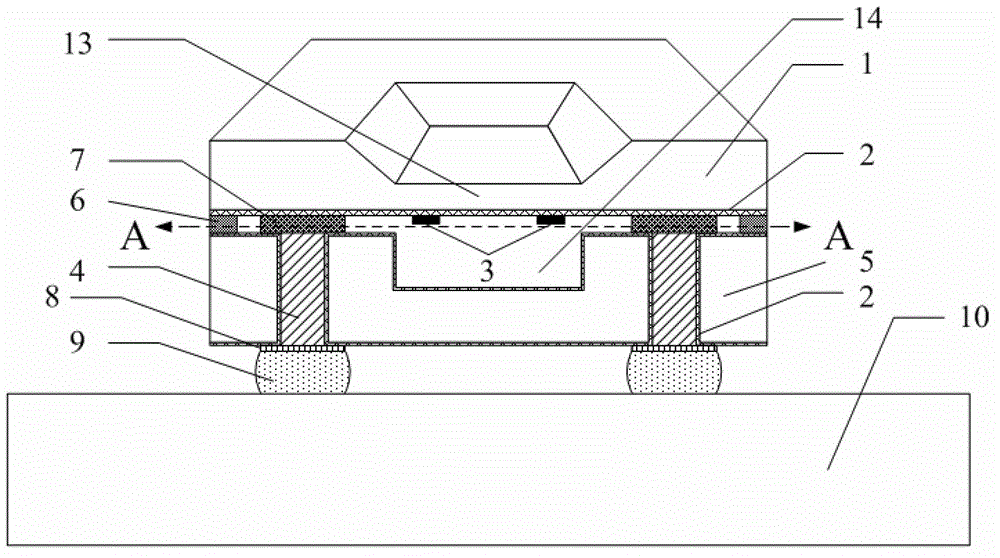

[0033] like image 3 As shown, the present invention uses the DRIE process to etch blind silicon vias with a depth of about 100-200 μm on the silicon base 5 from the back to the front at the position corresponding to the data signal port of the SOI pressure sensor chip 1 (wherein the DRIE process parameters are: SF 6 Gas flow 130sccm, C 4 F 8 The gas flow rate is 100sccm, the stage power is 600W, the automatic pressure control APC is selected as 60, the passivation is 7s after every 9s of etching, and the etching rate is about 2μm / min (the specific parameters are closely related to the etching area)); the thermal oxygen forms a thickness of 2μm SiO 2 Insulating sidewalls or depositing SiNx, magnetron sputtering deposition adhesive layer The barrier layer W forms an insulating barrier layer 2, and at the same time sputters a 1-2 μm seed layer on the sidewall of the blind hole, wherein the material of the seed layer is the same as the conductive material filled in the sili...

Embodiment 2

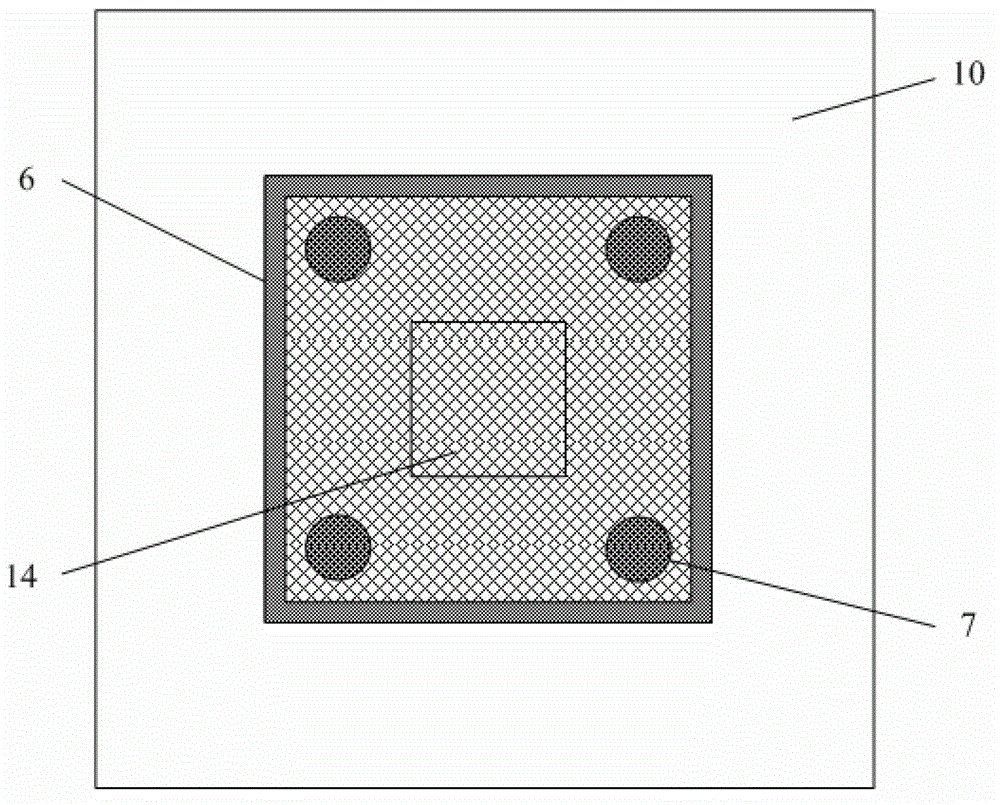

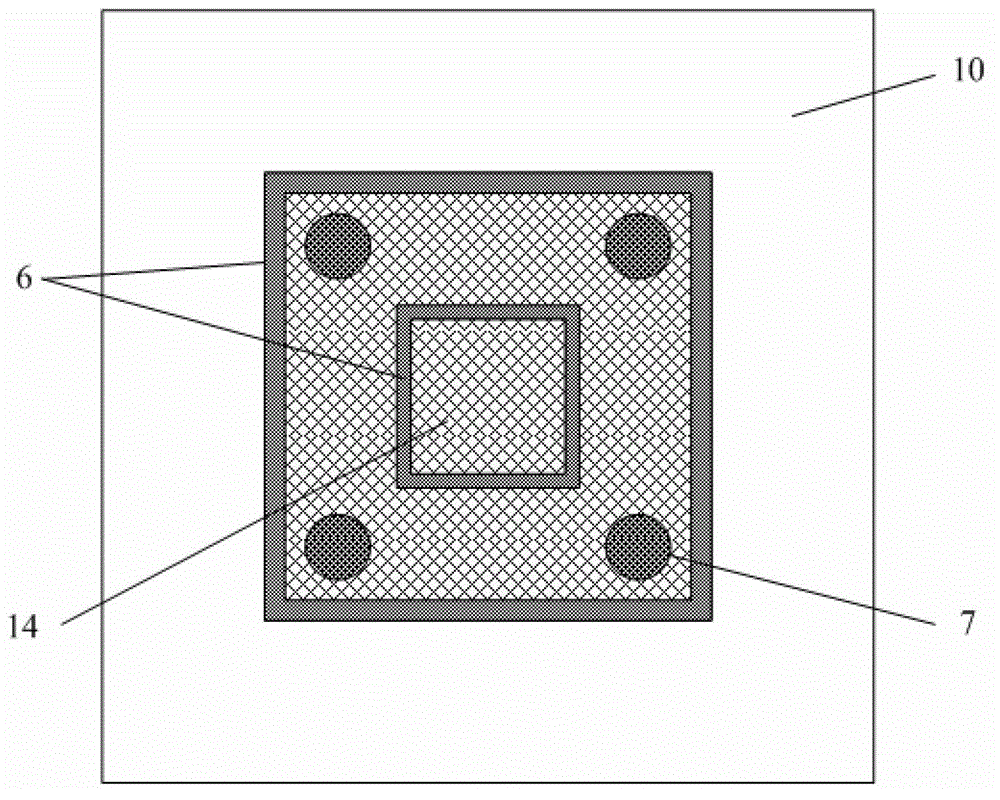

[0035] like Figure 4 As shown, the second embodiment of the present invention is similar to the first embodiment, the main difference is that the front side of the silicon base 5 is thinned and polished by CMP, and after the through hole 4 is formed through the substrate, electroplating or chemical plating is performed at the position of the through hole 4 to form conductive micro-convex. At point 7, a ring-shaped bonded metal ring structure is electroplated or electrolessly plated on both sides of the inner and outer periphery at the same time, wherein the material of the bonded metal ring 6 is an airtight material. The remaining process steps are the same and will not be repeated here. The silicon piezoresistive strips 3 are distributed at a horizontal distance of 100-200 μm from the edge of the silicon film 13 close to the pressure sensor, and are placed in the concave groove 14 of the silicon base 5 after packaging.

Embodiment 3

[0037] like Figure 5 As shown, the third embodiment of the present invention is as follows:

[0038] The process steps of flip-chip bonding the pressure sensor chip 1 on the silicon base 5 are as follows: the silicon base 5 is etched with a depth of about 100-200 μm from the back to the front at the position corresponding to the data signal port of the SOI pressure sensor chip 1 using a DRIE process. Silicon blind vias followed by deposition of 2 μm thick SiO 2 or SiNx insulating layer, adhesive layer The barrier layer W forms an insulating barrier layer 2, and sputters a 1-2 μm seed layer at the same time, wherein the material of the seed layer is the same as the conductive material filled with the silicon blind hole; the silicon blind hole is electroplated to form a conductive column, and the UBM8 structure is prepared by electroplating or electroless plating process. , and then etch to remove the surface adhesion layer Ti / barrier layer W / seed layer; the back side of t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More