Patents

Literature

59results about How to "Improve interconnect reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

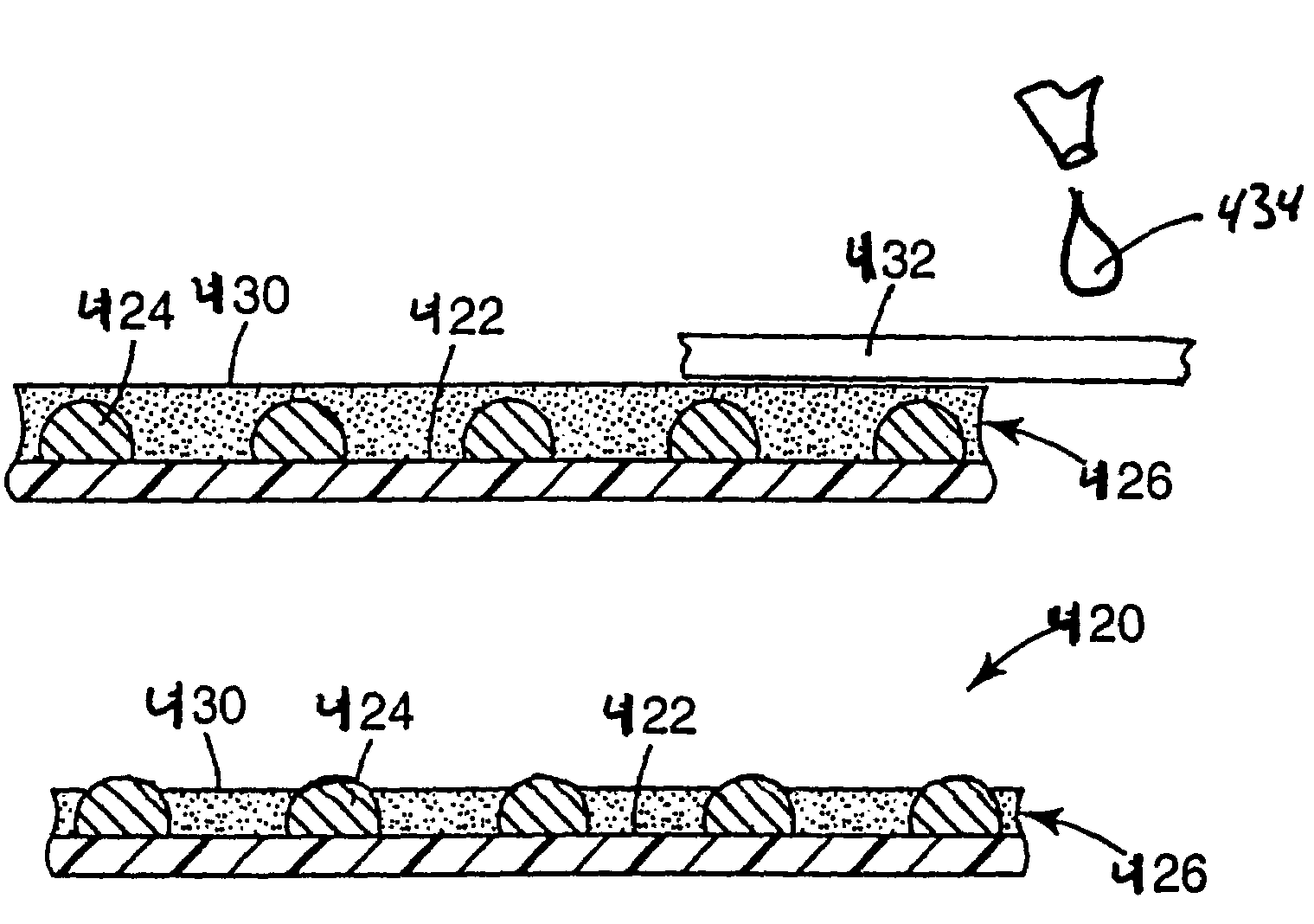

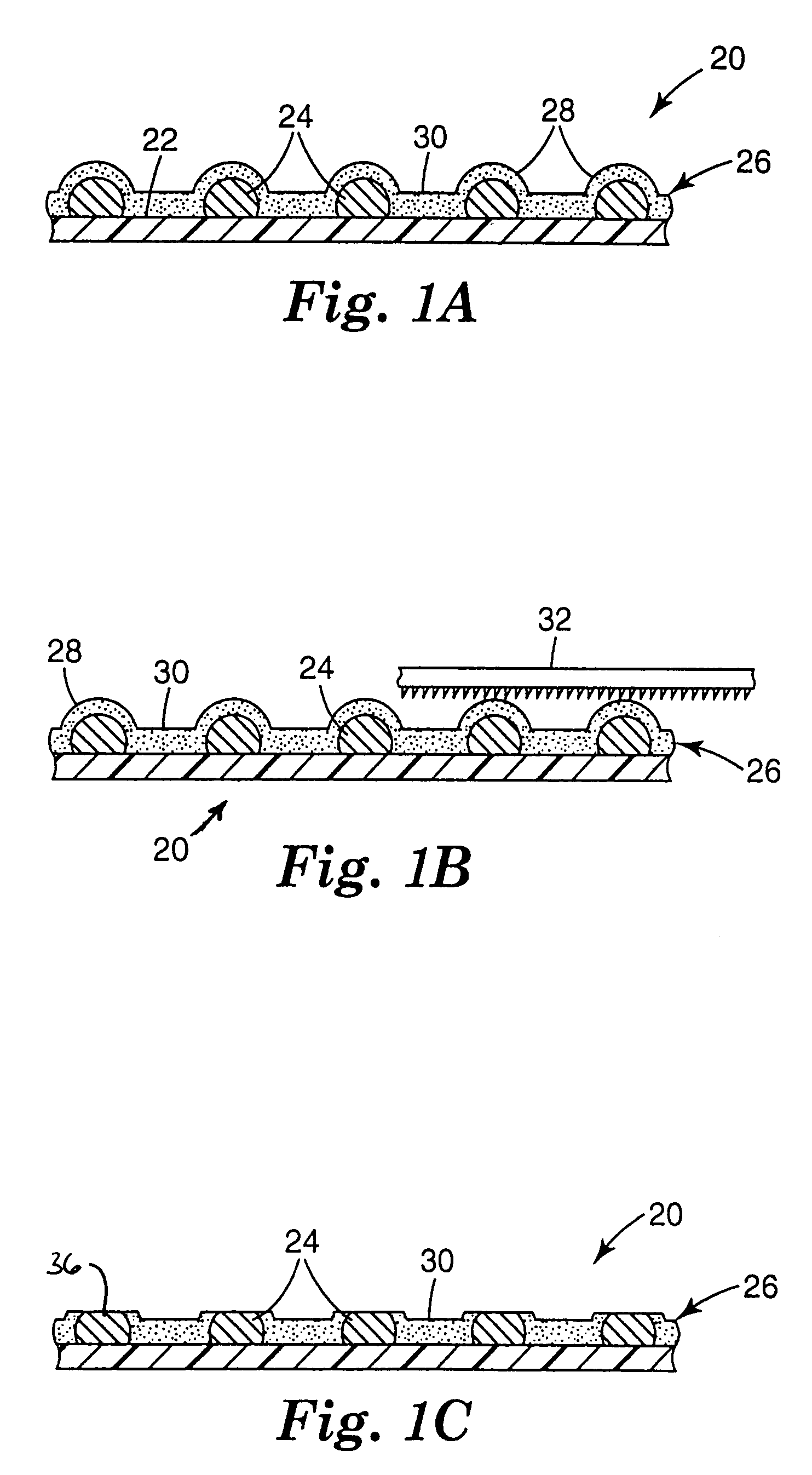

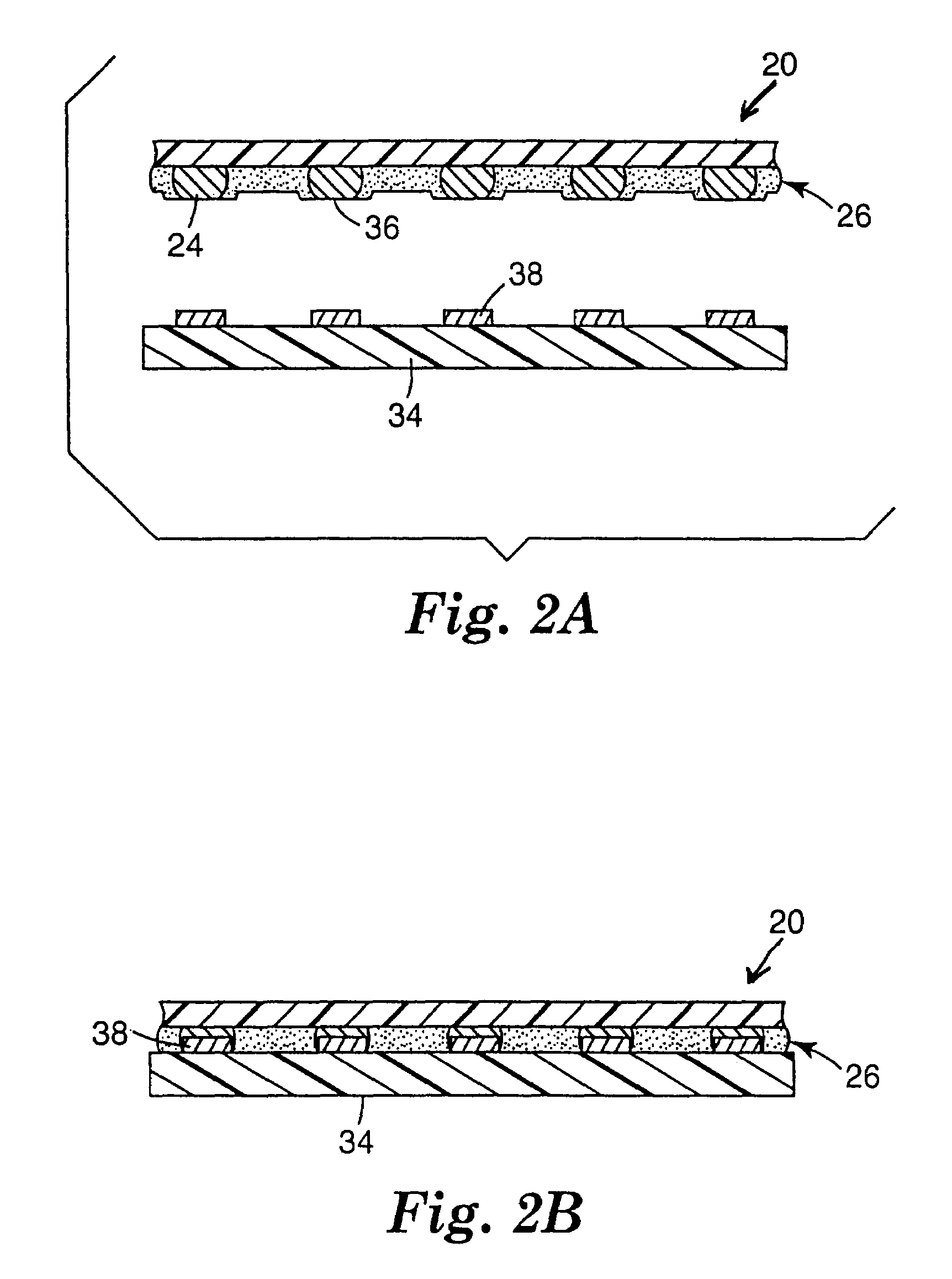

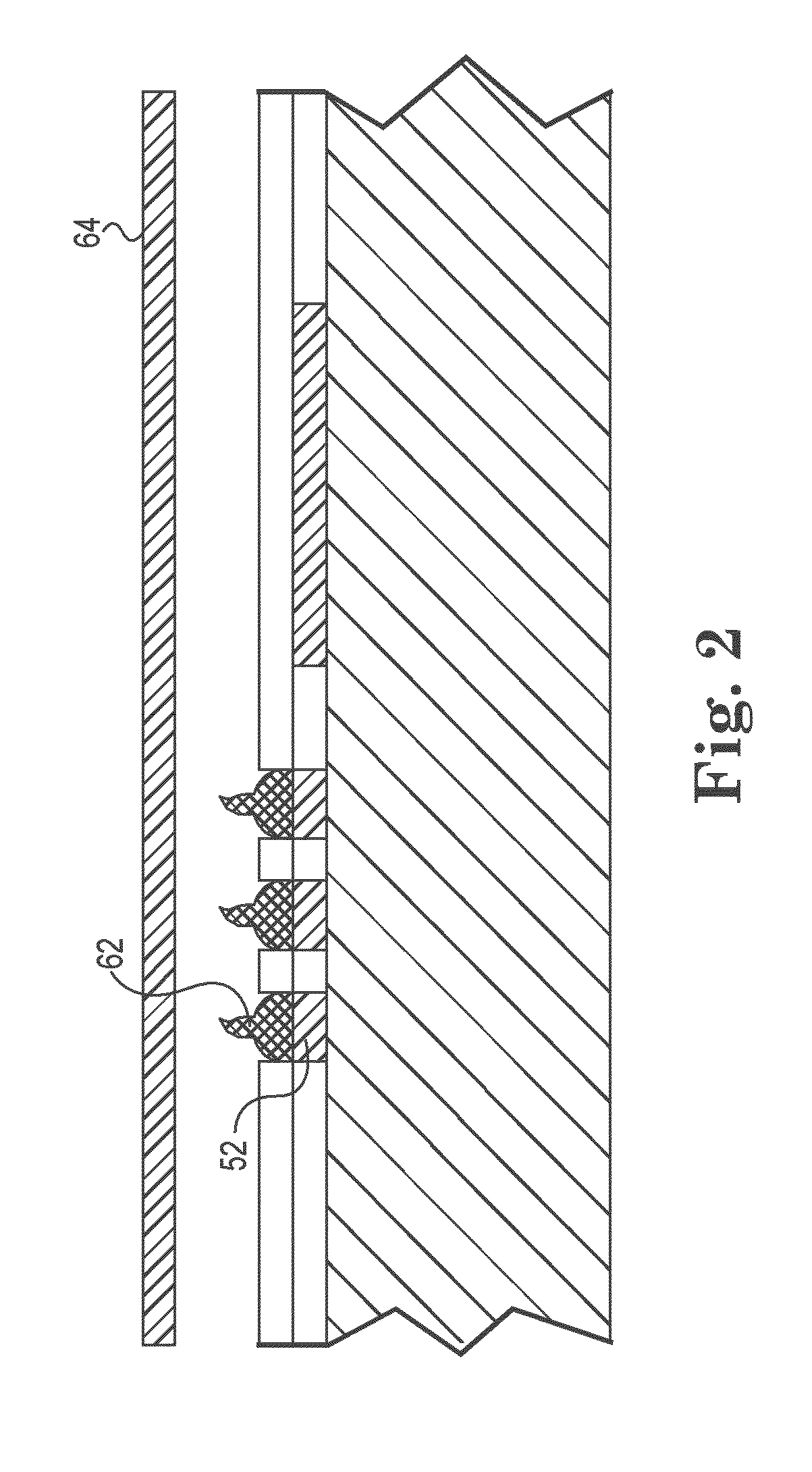

Solvent assisted burnishing of pre-underfilled solder bumped wafers for flipchip bonding

InactiveUS7170185B1Simplify flip-chip assembly processLower assembly costsSemiconductor/solid-state device detailsSolid-state devicesAdhesiveElectrical connection

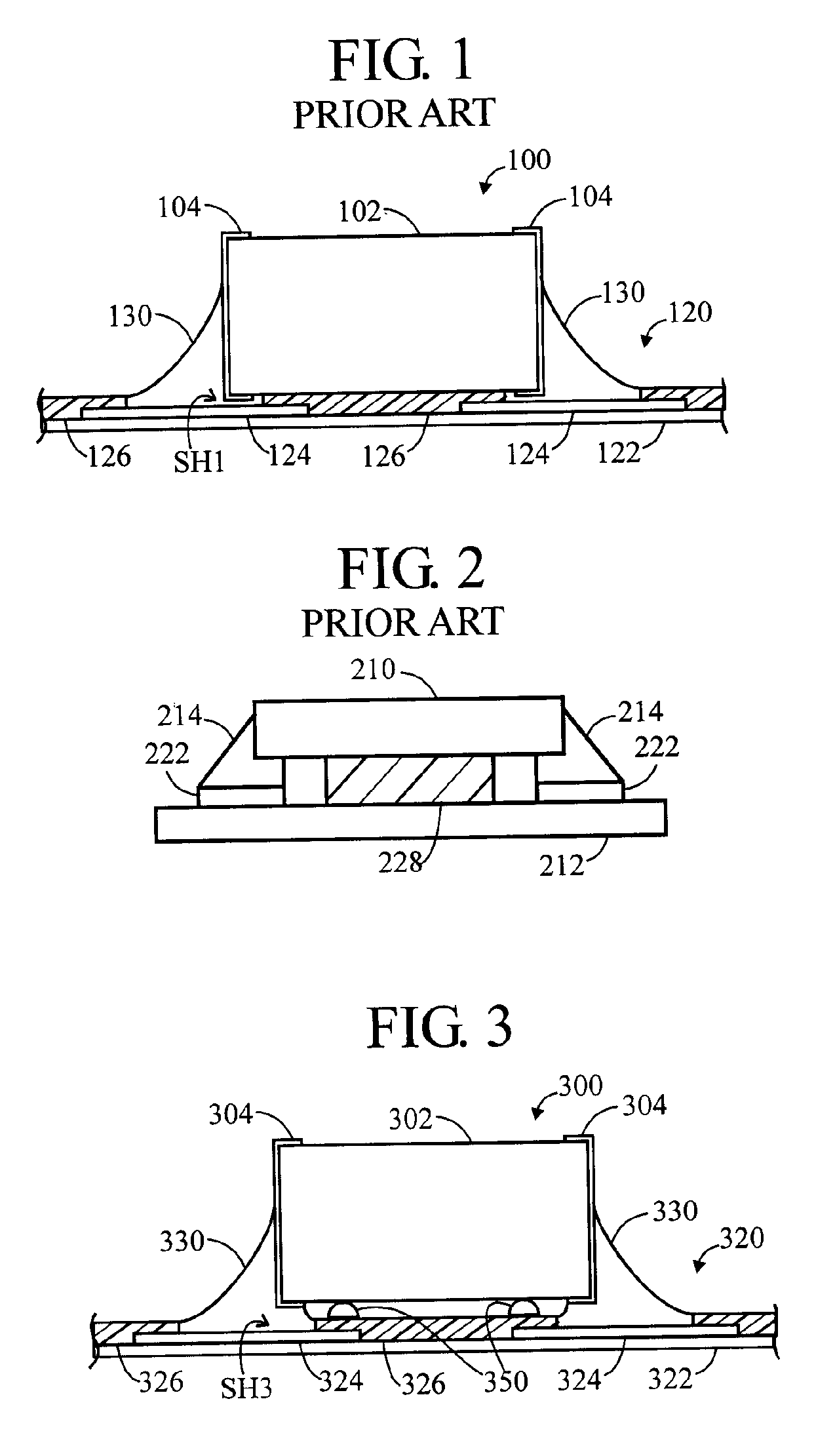

The present invention relates to a method for connecting an integrated circuit chip to a circuit substrate. The method includes the step of pre-applying adhesive directly to a bumped side of an integrated circuit chip. The method also includes the steps of removing portions of the adhesive from the tips of the solder bumps to expose a contact surface, and pressing the bumped side of the integrated circuit chip, which has previously been coated with adhesive, against the circuit substrate such that the bumps provide an electrical connection between the integrated circuit chip and the circuit substrate. The adhesive is removed from the tips of the solder bumps using a solvent assisted wiping action. The pre-applied adhesive on the chip forms a bond between the integrated circuit chip and the circuit substrate.

Owner:3M INNOVATIVE PROPERTIES CO

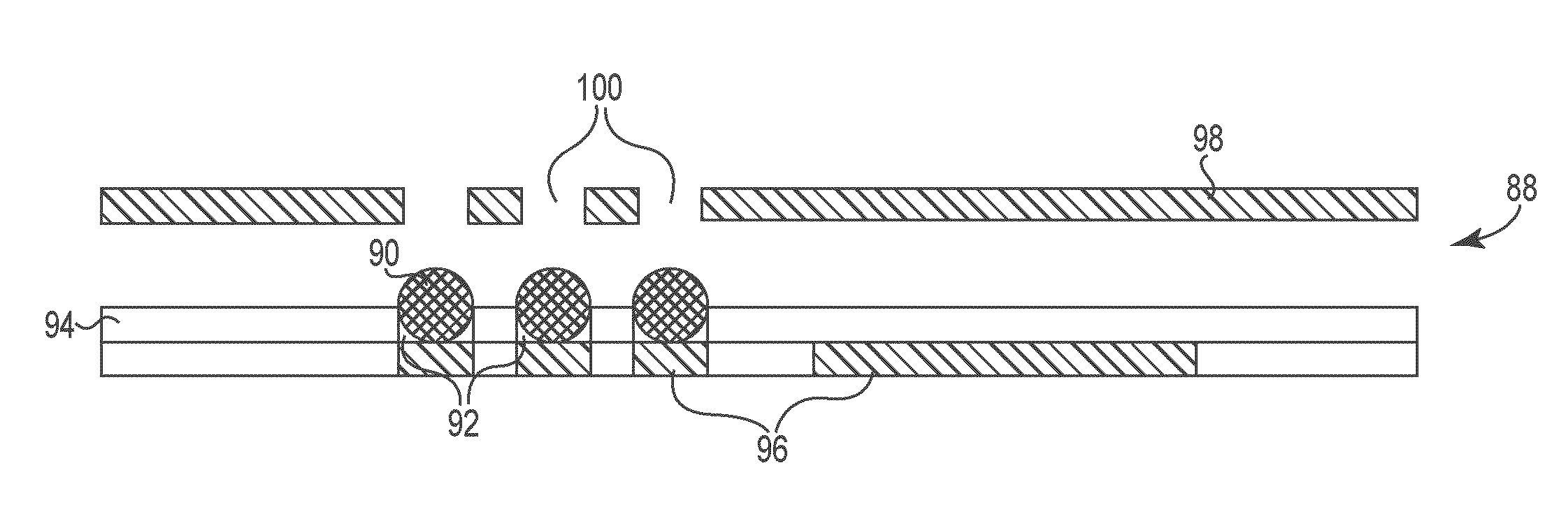

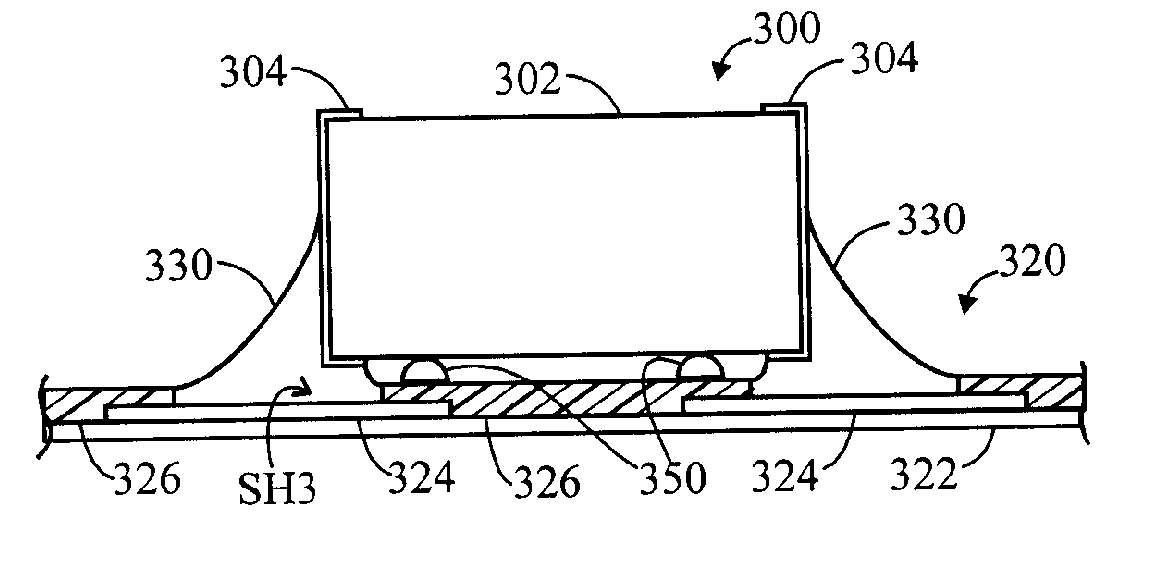

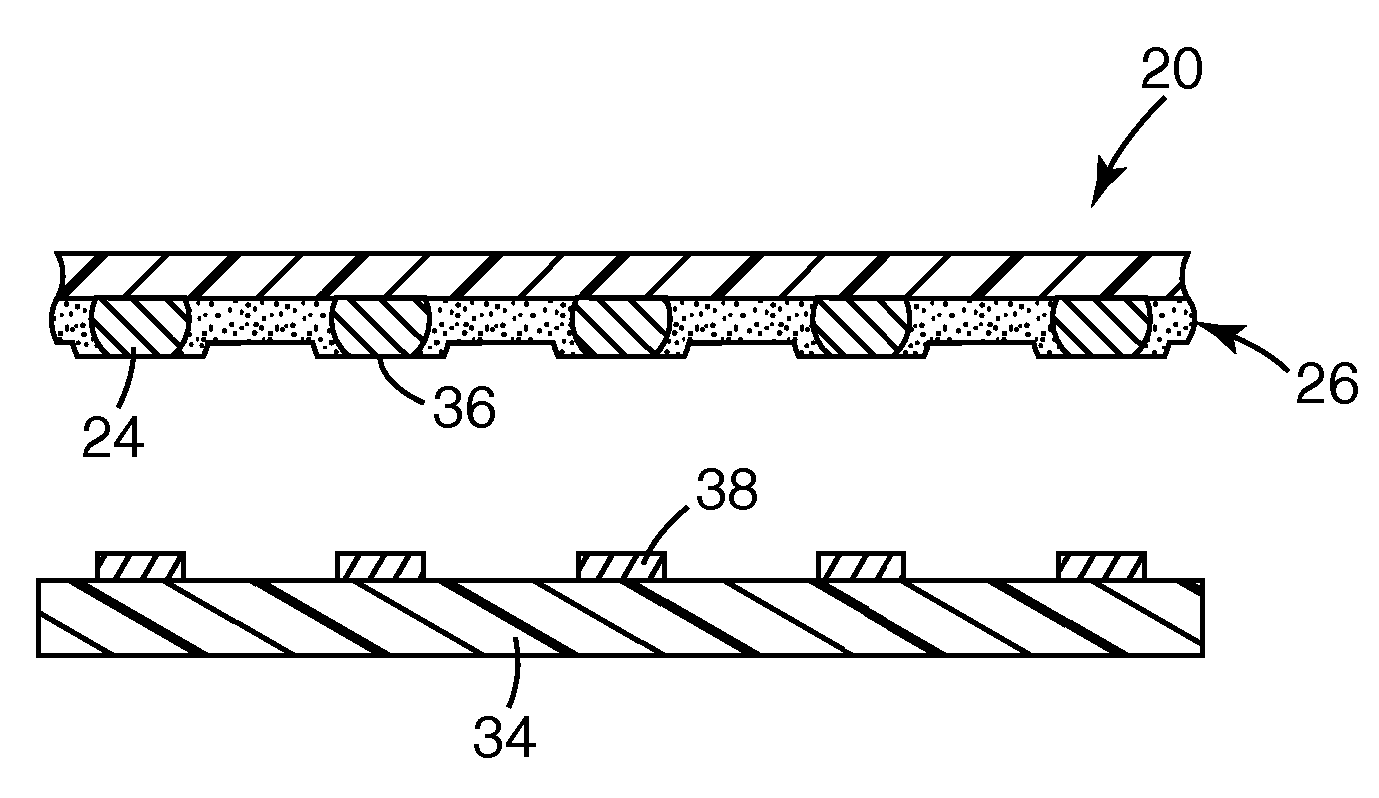

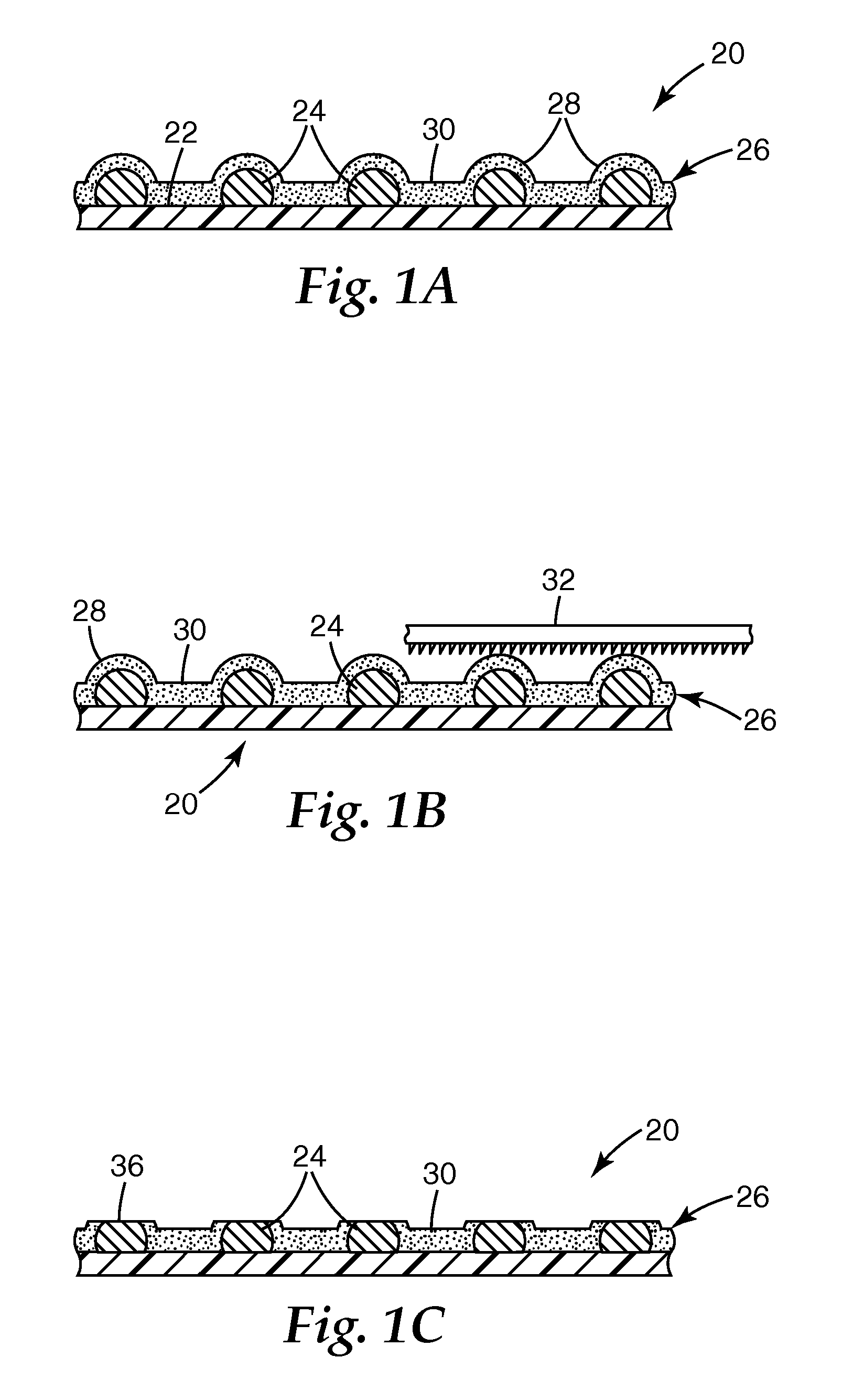

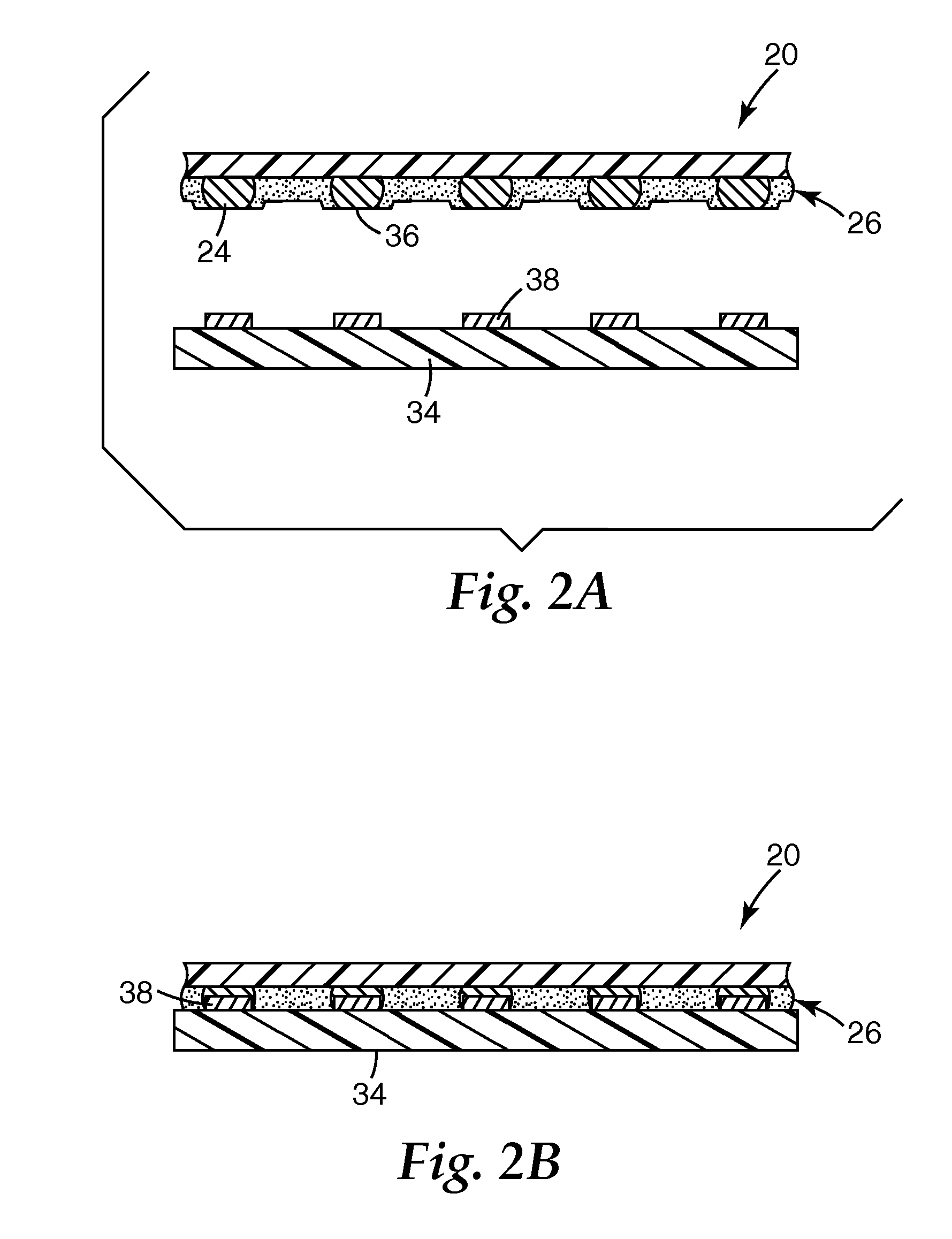

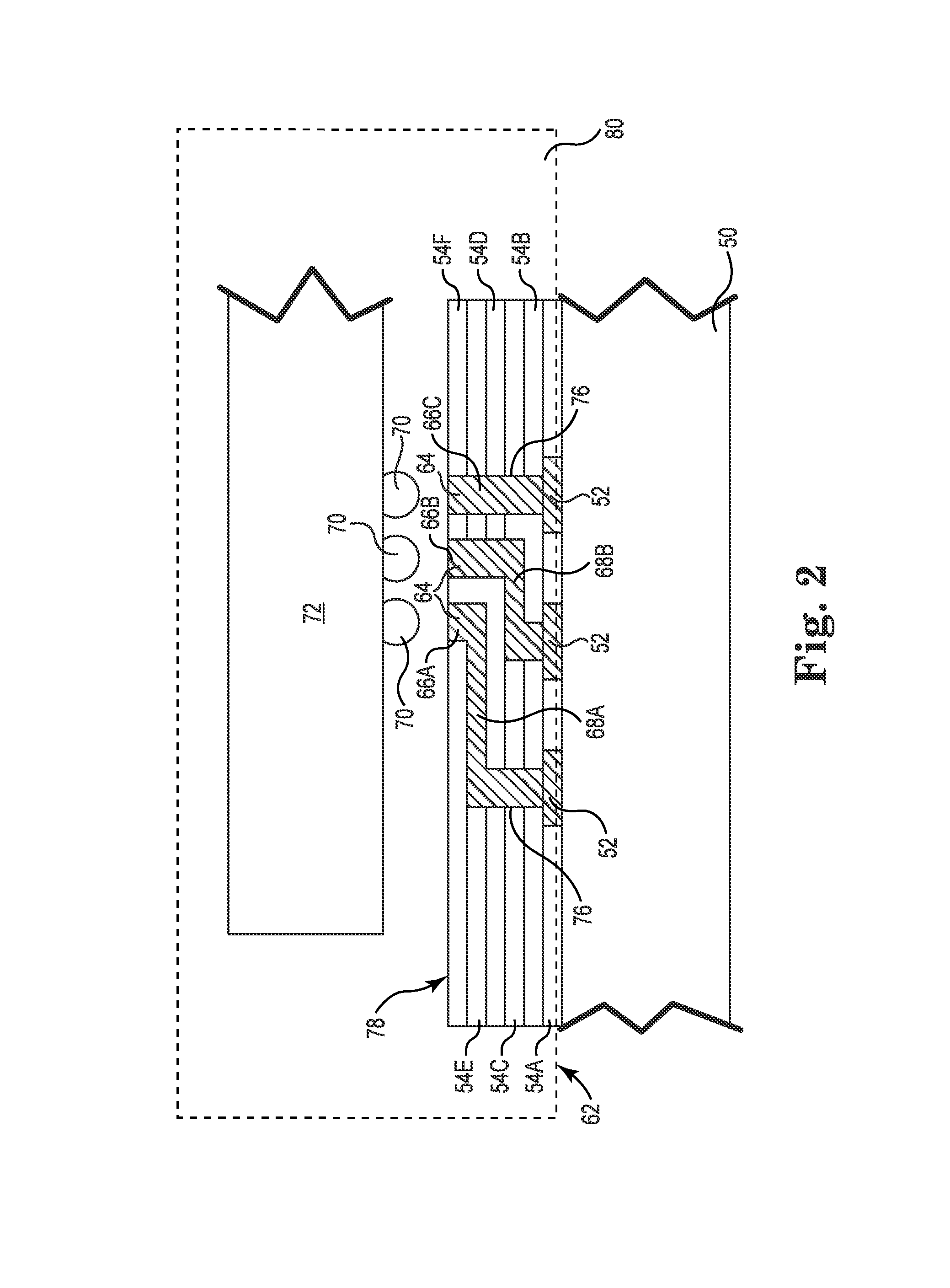

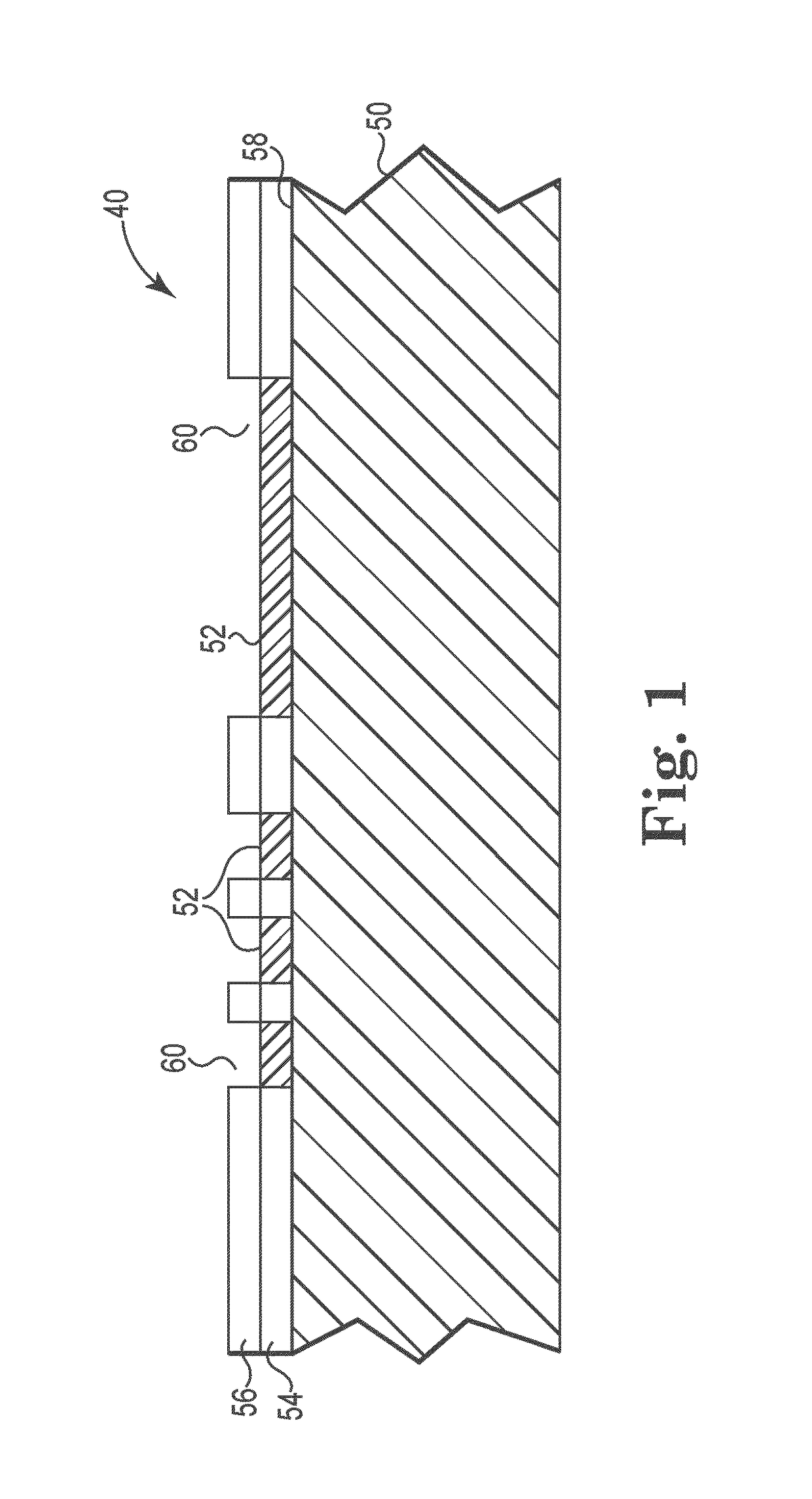

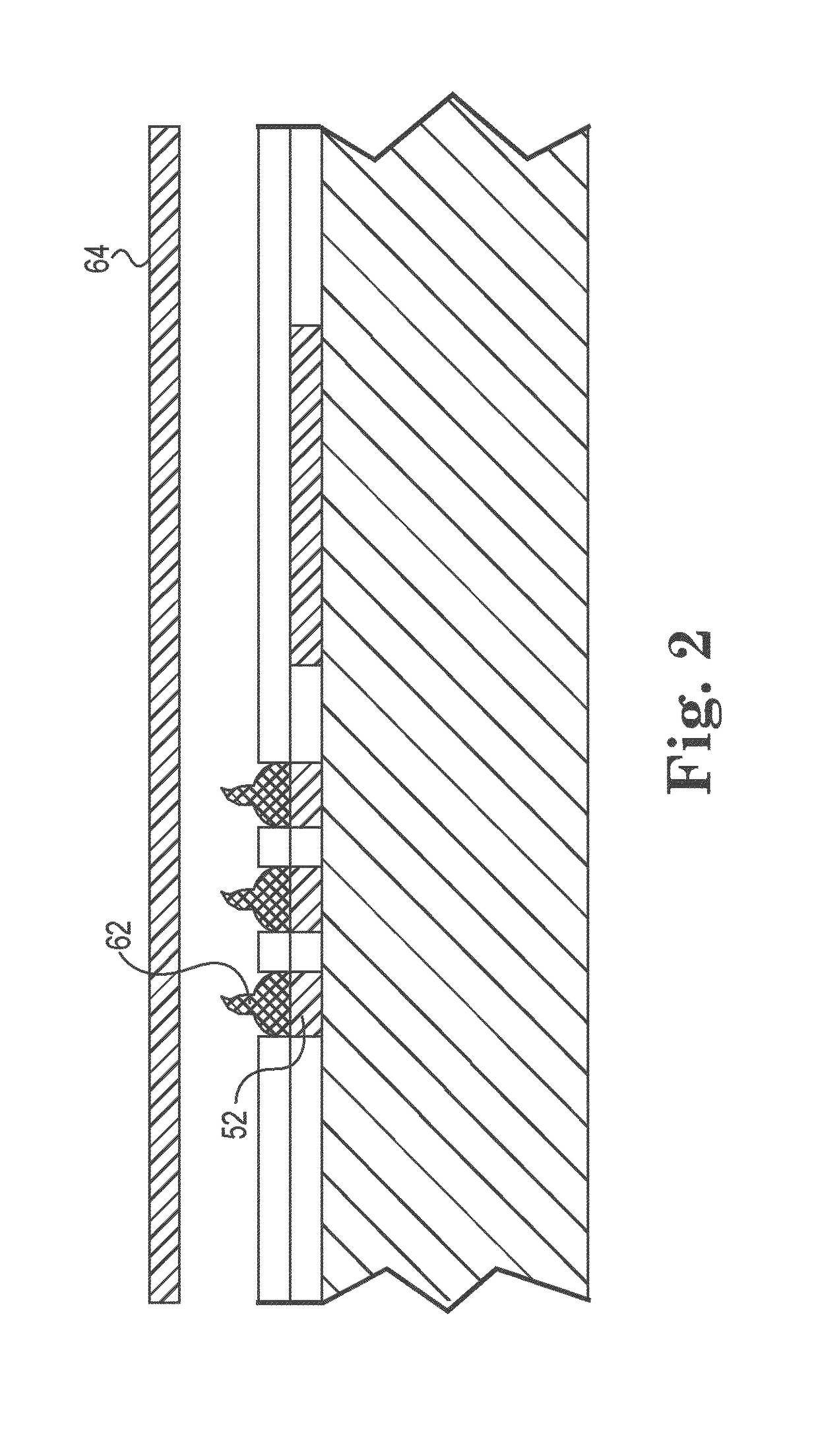

Compliant printed circuit area array semiconductor device package

ActiveUS20120061846A1Low production costImprove electrical performanceSemiconductor/solid-state device detailsSolid-state devicesRoad surfaceIc devices

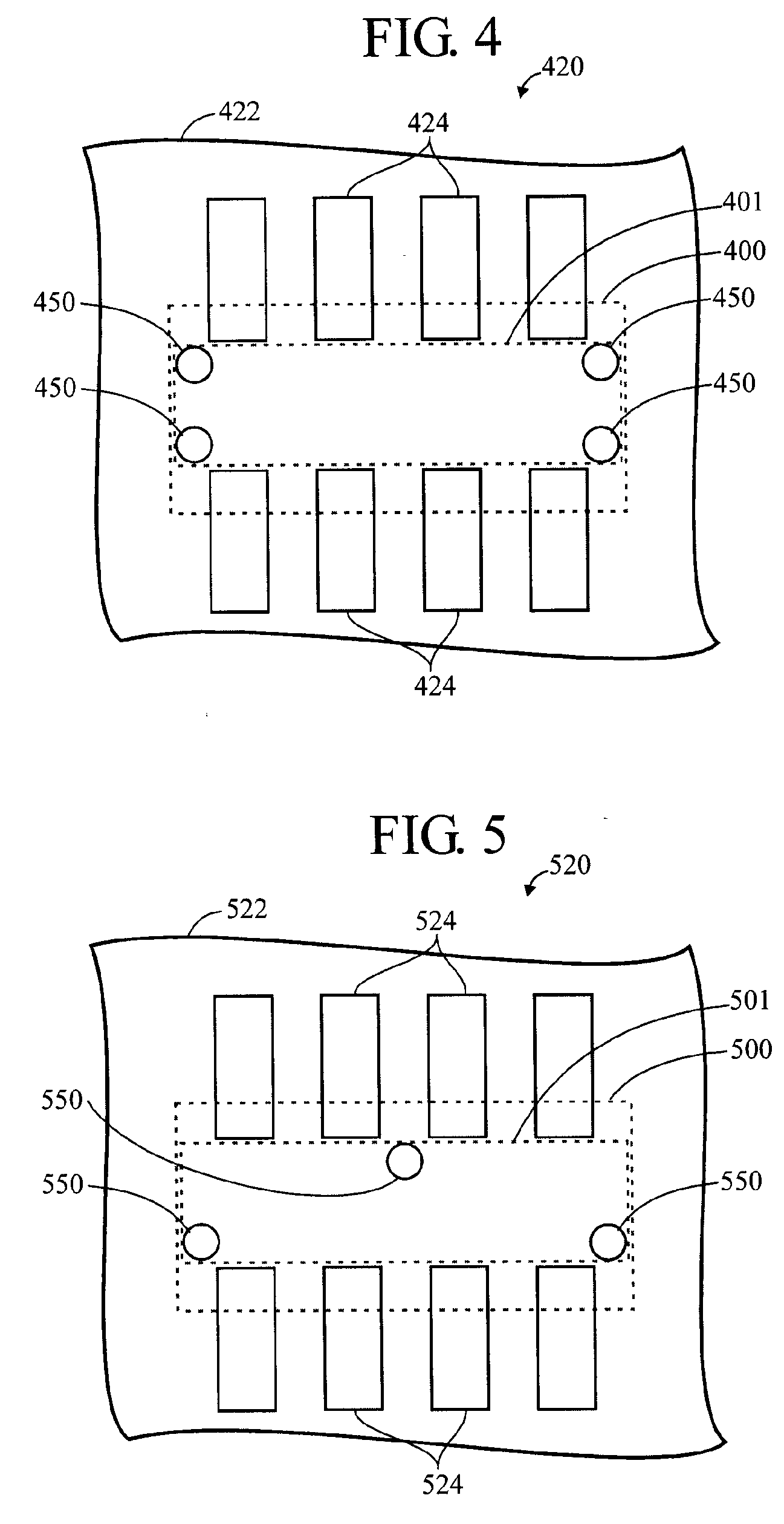

An integrated circuit (IC) package for an IC device, and a method of making the same. The IC package includes an interconnect assembly with at least one printed compliant layer, a plurality of first contact members located along a first major surface, a plurality of second contact members located along a second major surface, and a plurality of printed conductive traces electrically coupling a plurality of the first and second contact members. The compliant layer is positioned to bias at least the first contact members against terminals on the IC device. Packaging substantially surrounds the IC device and the interconnect assembly. The second contact members are accessible from outside the packaging.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV +1

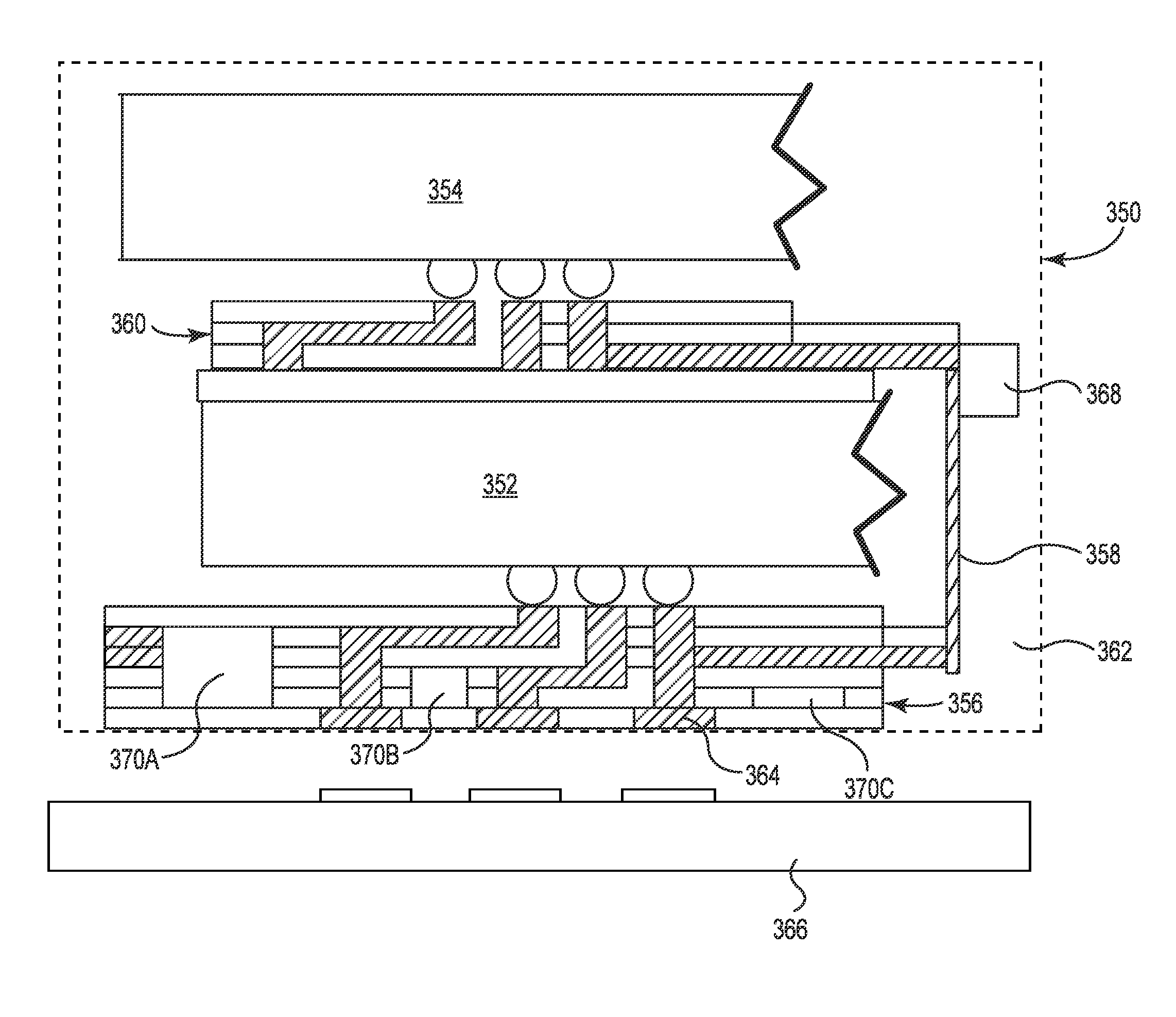

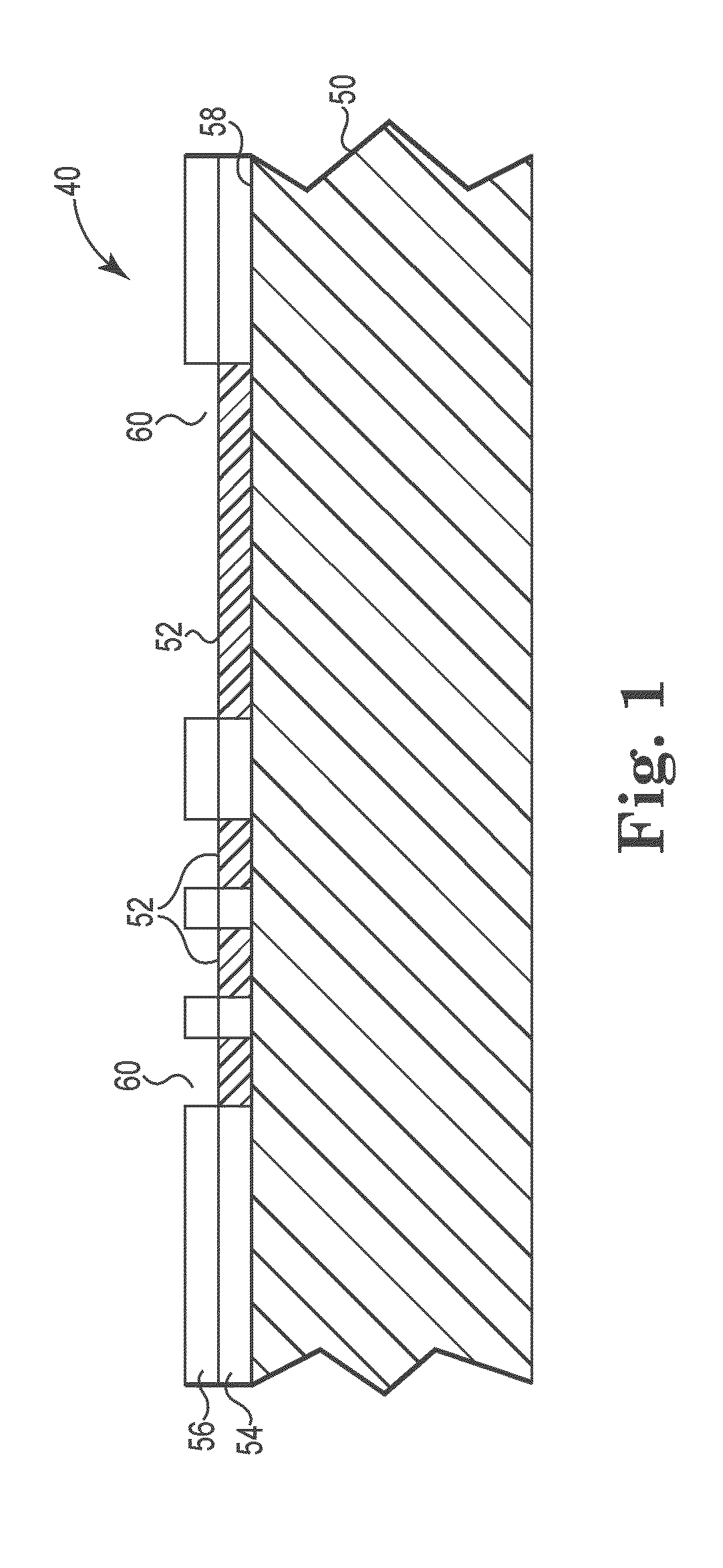

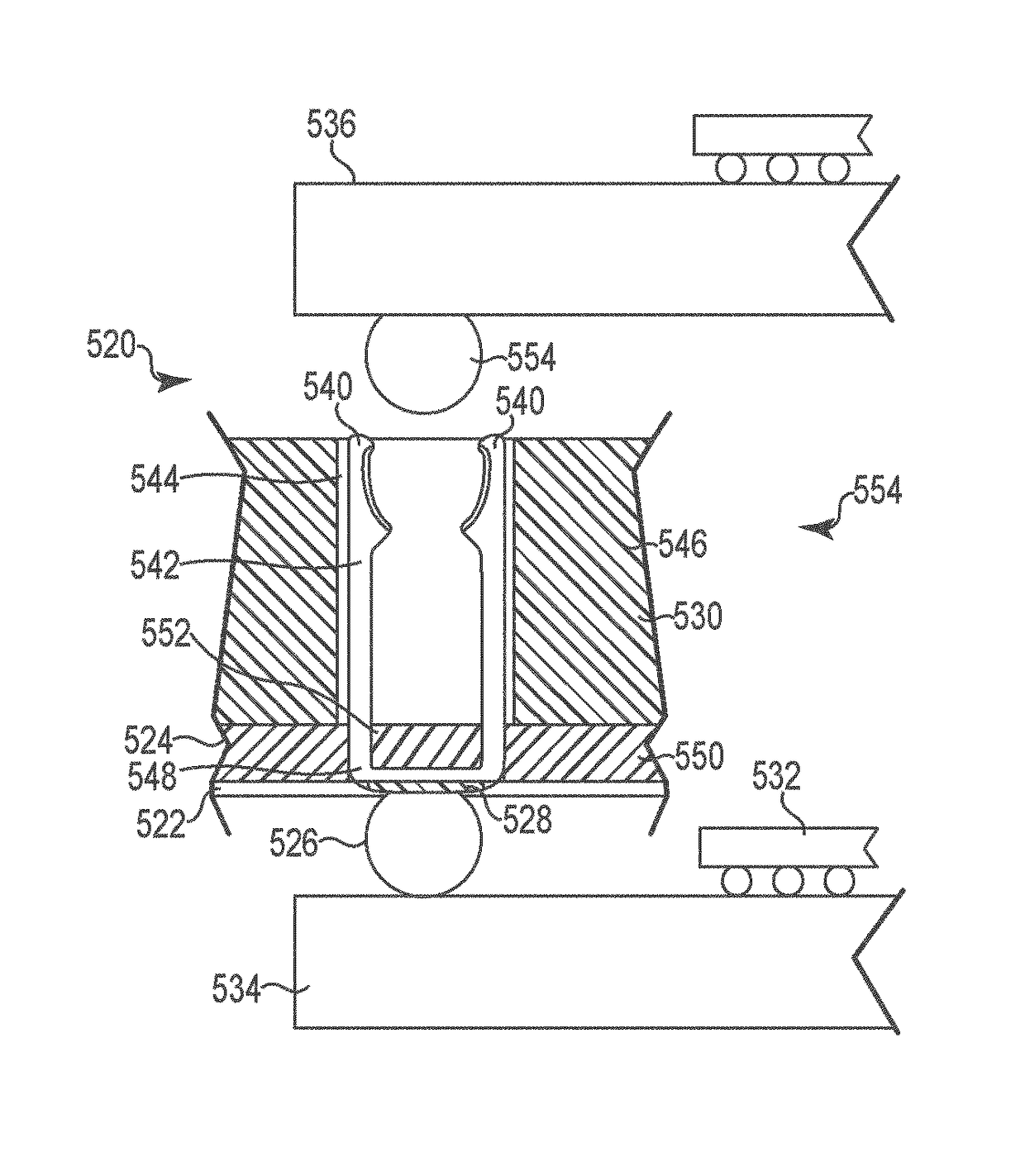

Area array semiconductor device package interconnect structure with optional package-to-package or flexible circuit to package connection

ActiveUS20120161317A1Alleviate environmental issuesImprove electrical performanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

An area array integrated circuit (IC) package for an IC device. The IC package includes a first substrate with conductive traces electrically coupled to the IC device. An interconnect assembly having a first surface is mechanically coupled to the first substrate. The interconnect assembly includes a plurality of contact members electrically coupled to the conductive traces on the first substrate. A second substrate is mechanically coupled to a second surface of the interconnect assembly so that the first substrate, the interconnect assembly, and the second substrate substantially surround the IC device. The second substrate includes conductive traces that are electrically coupled to the contact members in the interconnect assembly.

Owner:HSIO TECH

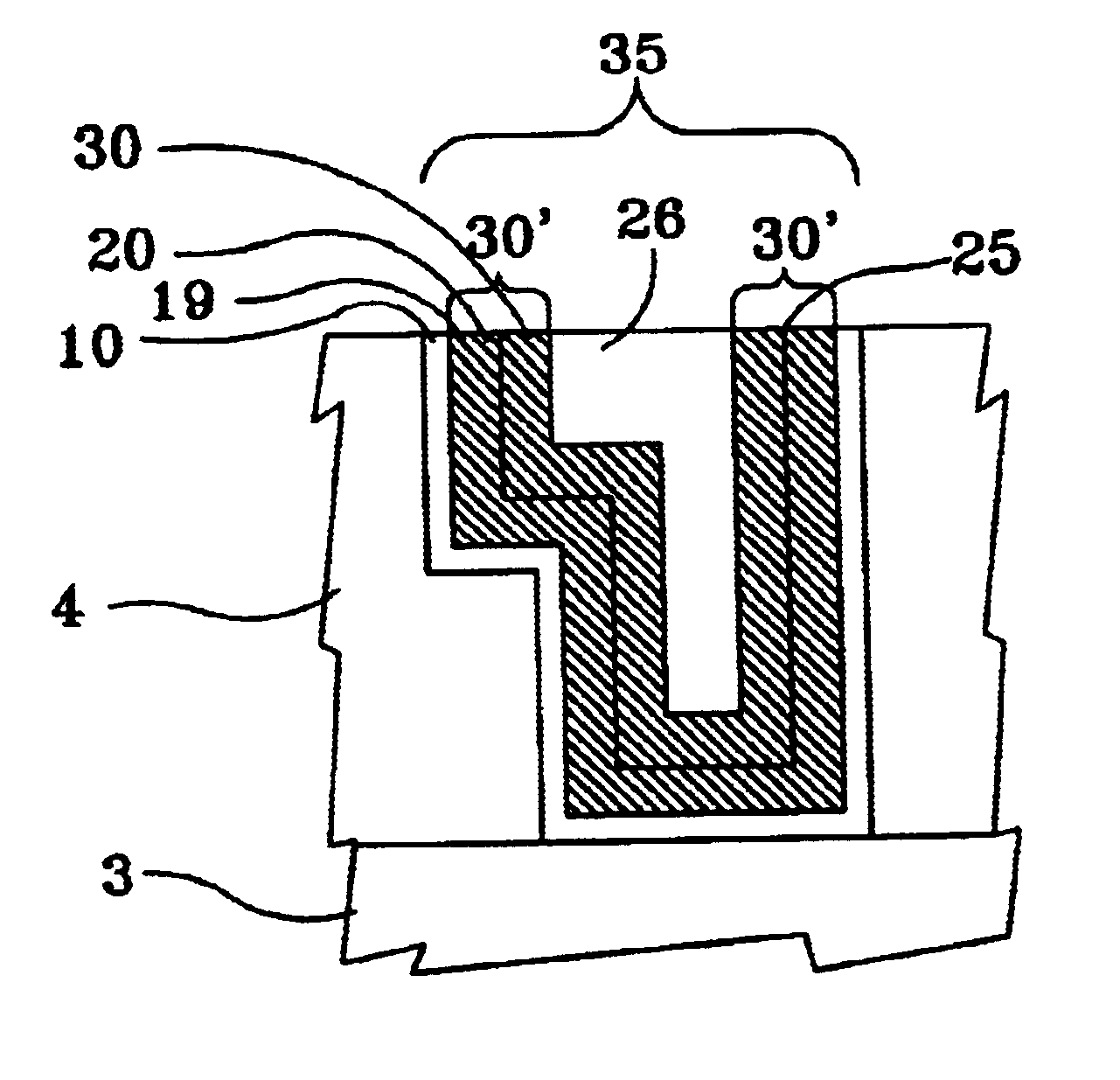

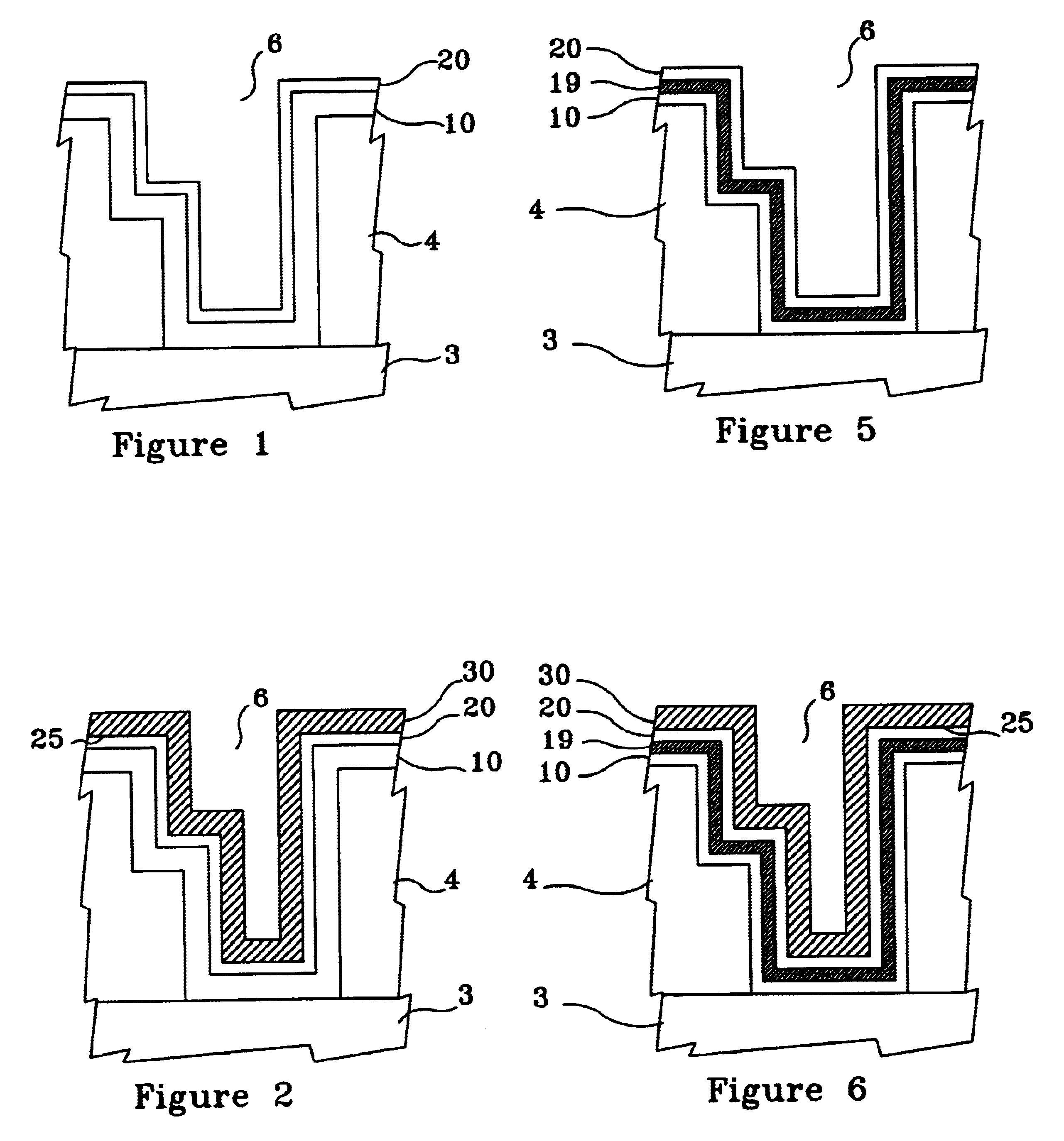

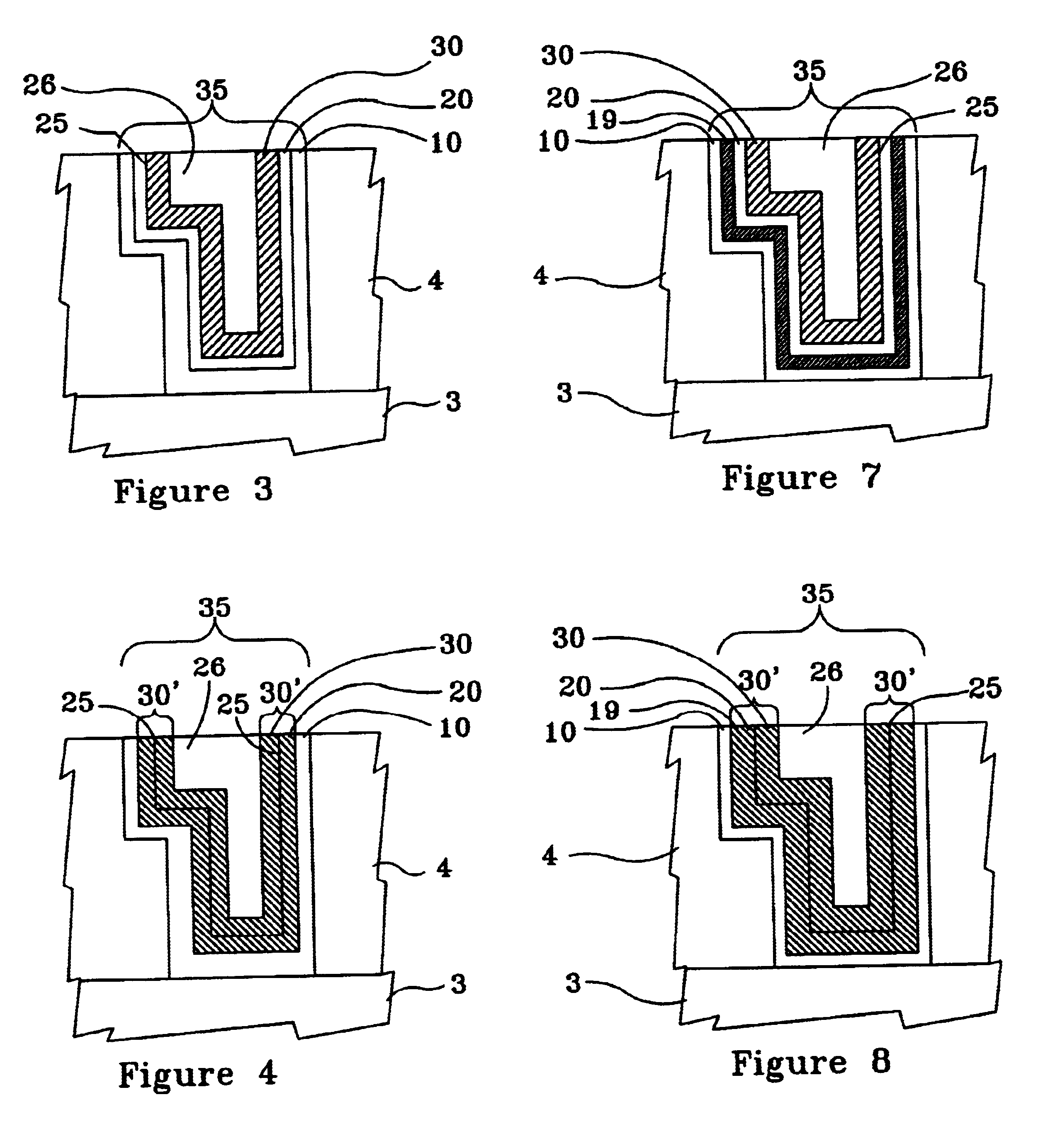

Method of reducing electromigration in a copper line by electroplating an interim copper-zinc alloy thin film on a copper surface and a semiconductor device thereby formed

InactiveUS6660633B1Improves Cu interconnect reliabilityReduce manufacturing costElectrolysis componentsSolid-state devicesCopper interconnectChemical solution

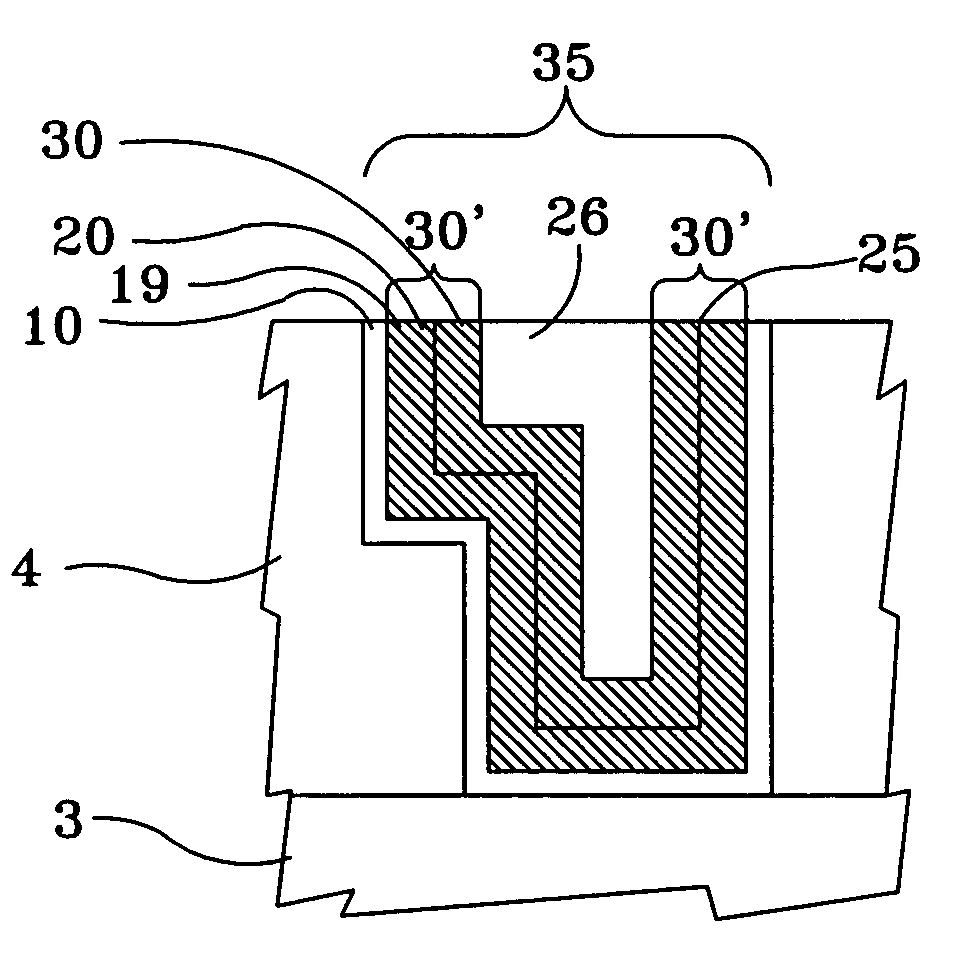

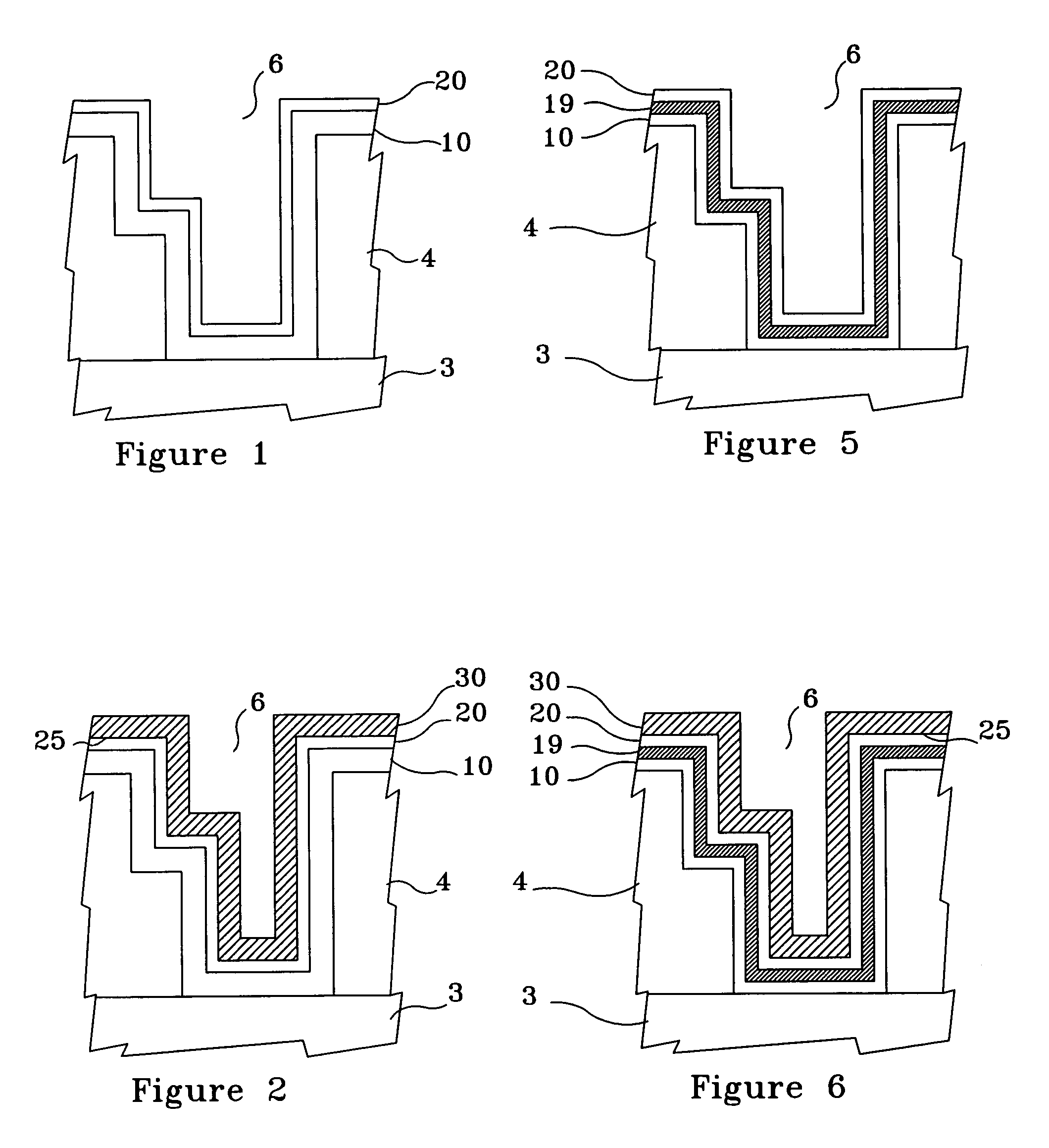

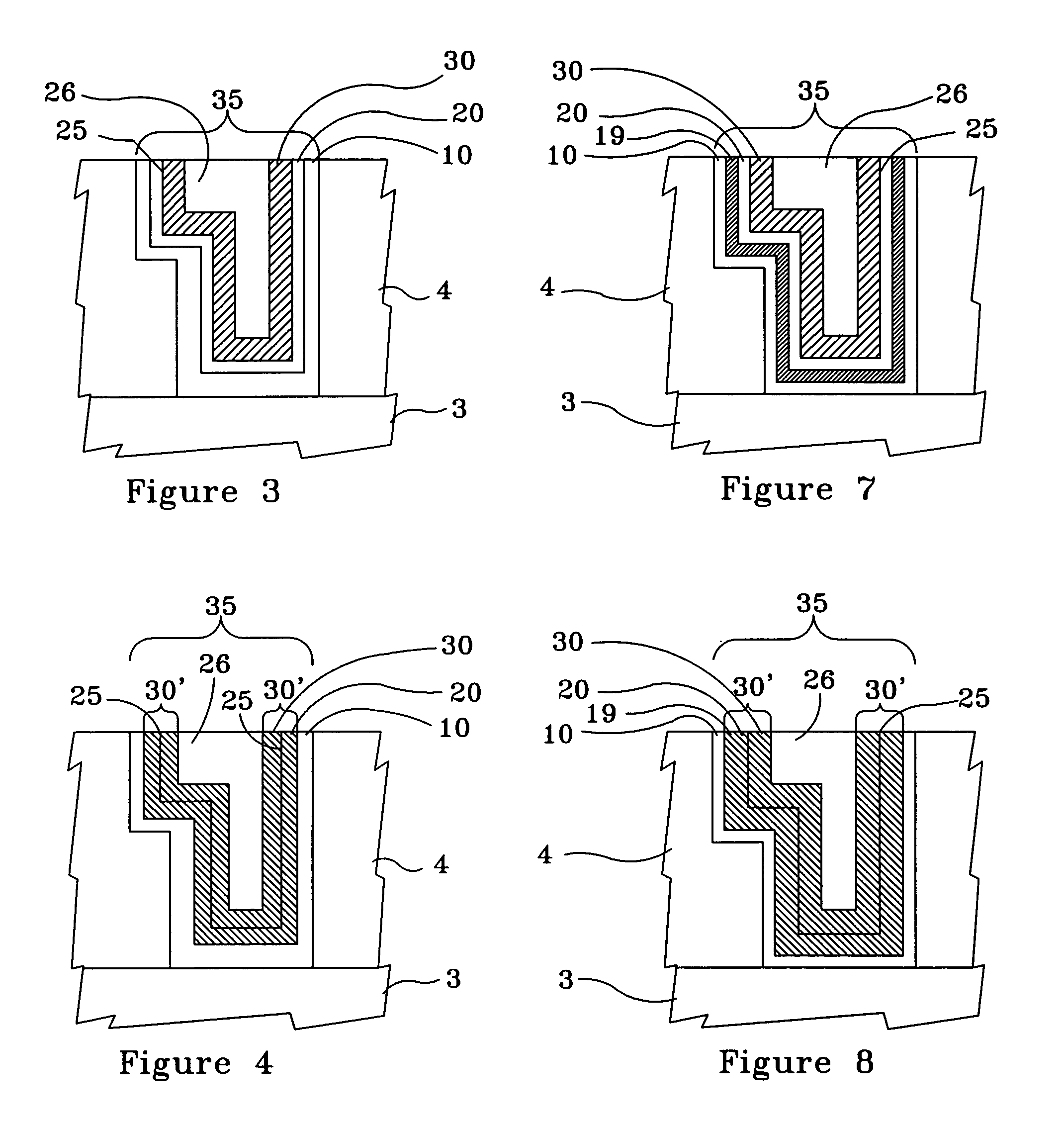

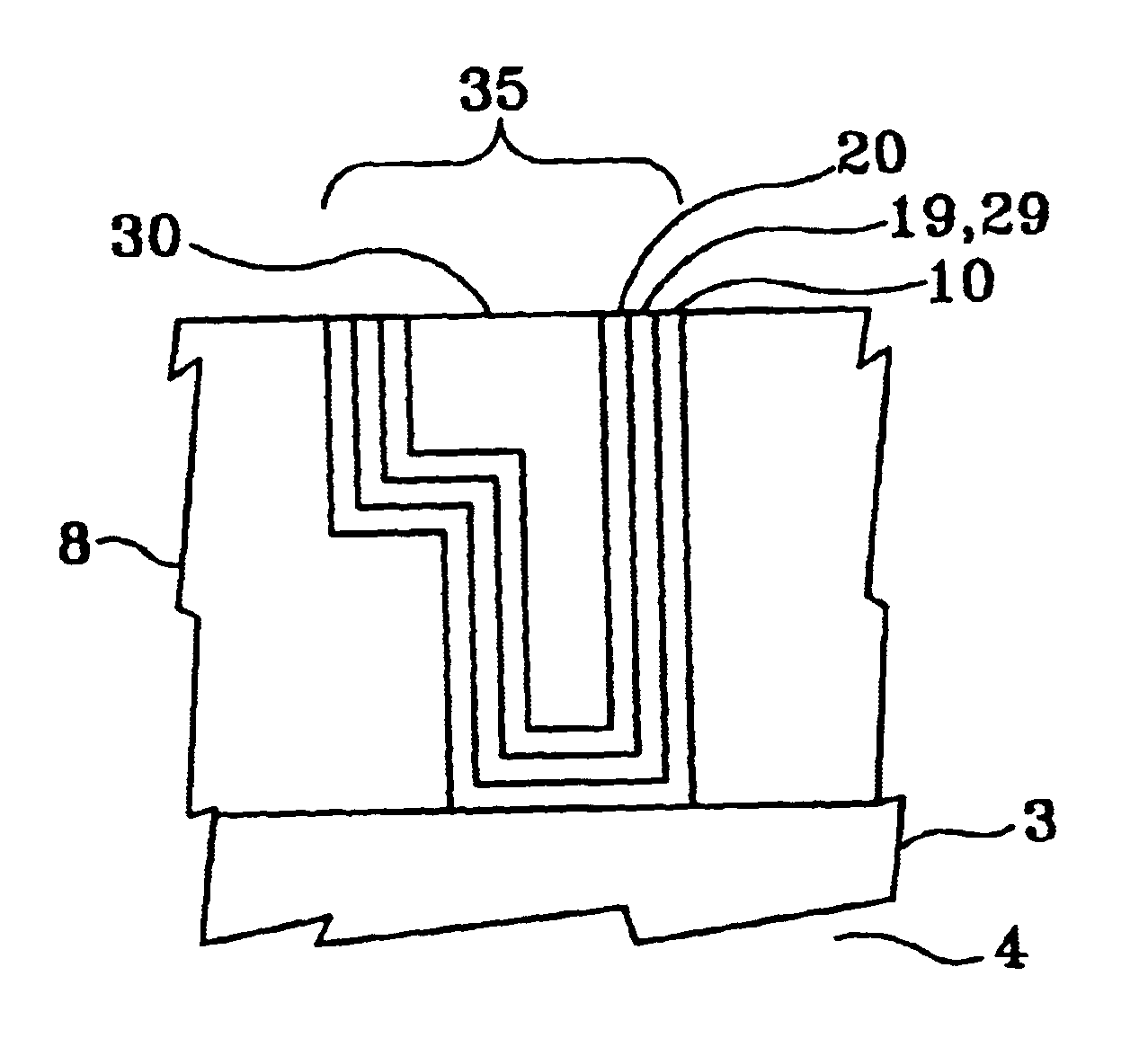

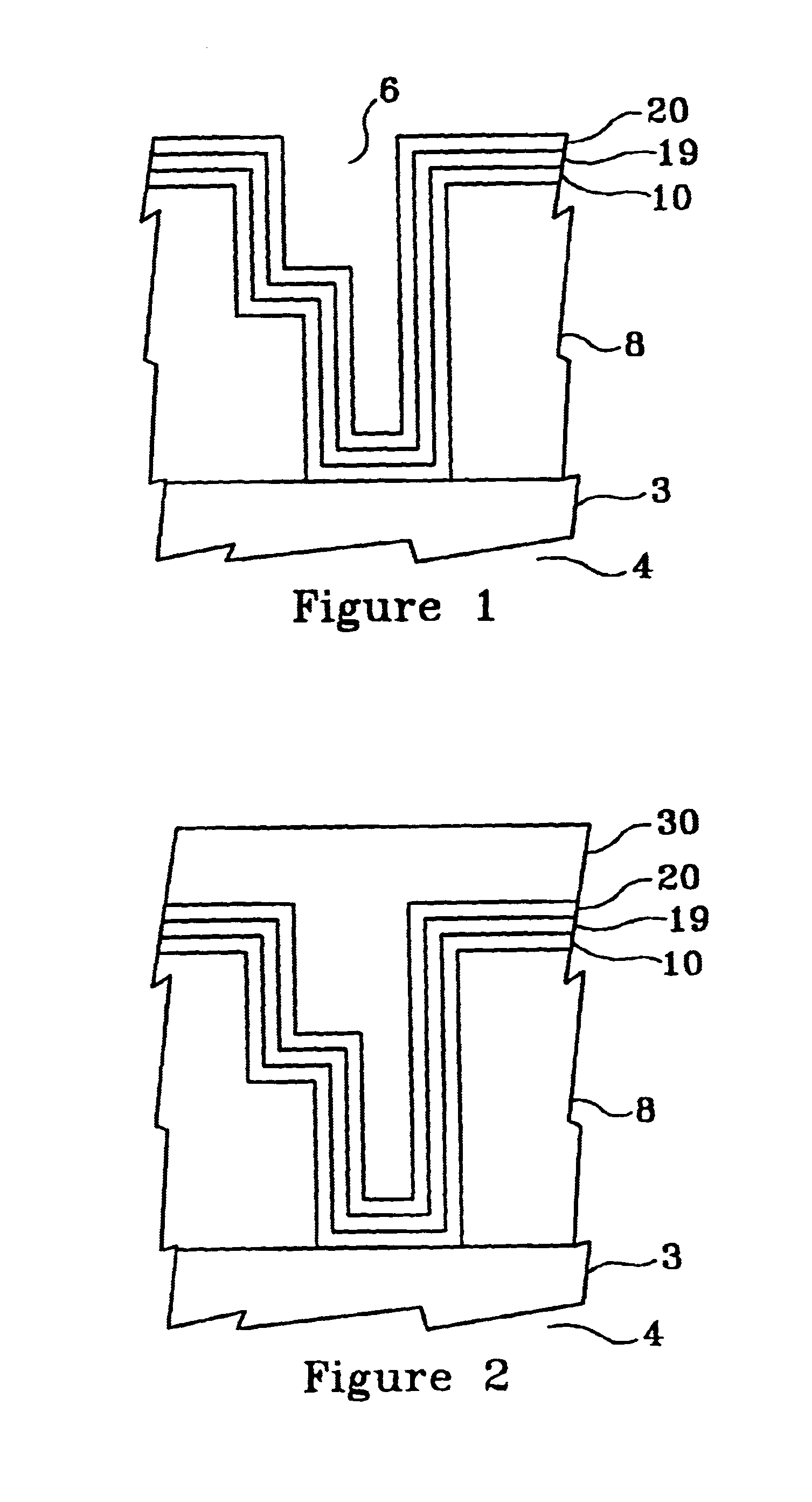

A method of fabricating a semiconductor device, having an interim reduced-oxygen Cu-Zn alloy thin film (30) electroplated on a blanket Cu surface (20) disposed in a via (6) by electroplating, using an electroplating apparatus, the Cu surface (20) in a unique chemical solution containing salts of Zn and Cu, their complexing agents, a pH adjuster, and surfactants; and annealing the interim electroplated Cu-Zn alloy thin film (30); filling the via (6) with further Cu (26); annealing and planarizing the interconnect structure (35); and a semiconductor device thereby formed. The reduction of electromigration in copper interconnect lines (35) is achieved by decreasing the drift velocity in the copper line (35) / via (6), thereby decreasing the copper migration rate as well as the void formation rate, by using an interim conformal Cu-rich Cu-Zn alloy thin film (30) electroplated on a Cu surface (20) from a stable chemical solution, and by controlling the Zn-doping thereof, which improves also interconnect reliability and corrosion resistance.

Owner:GLOBALFOUNDRIES US INC

Superconducting quantum bit chip

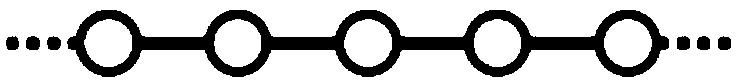

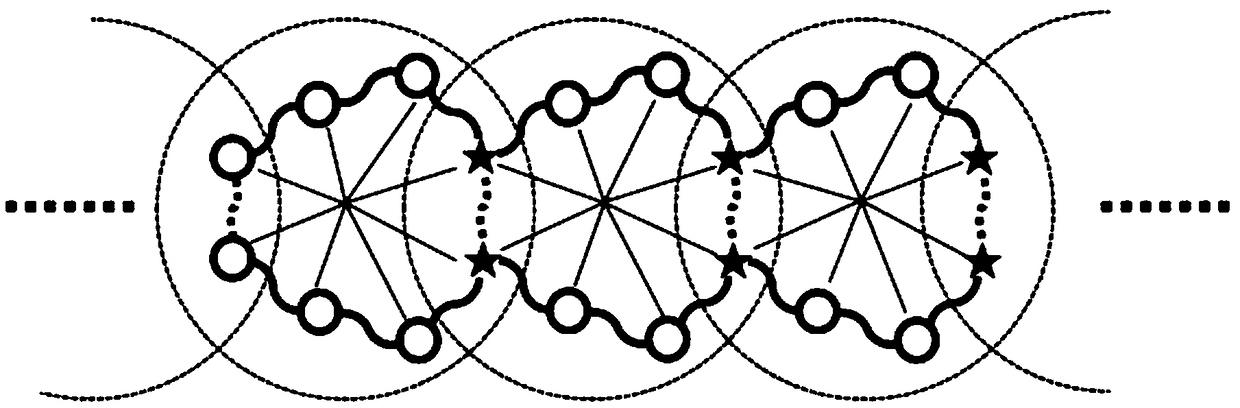

ActiveCN109376870APrevent Interconnect BreakpointsIncrease flexibilityQuantum computersMicrowave cavityChain structure

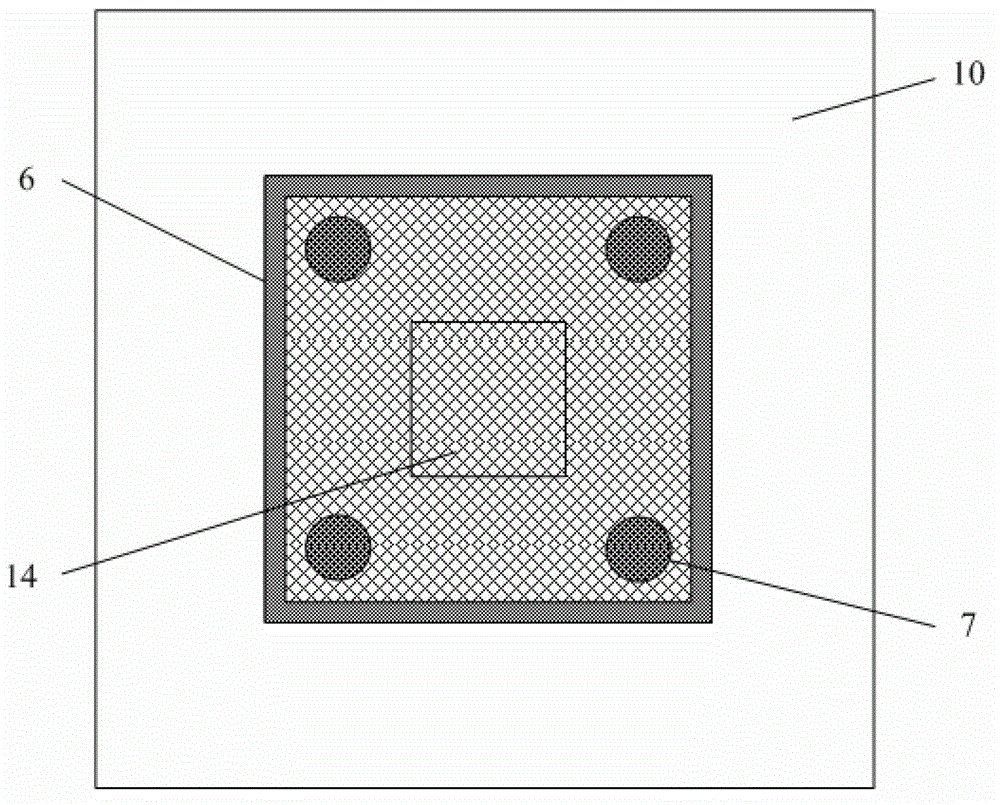

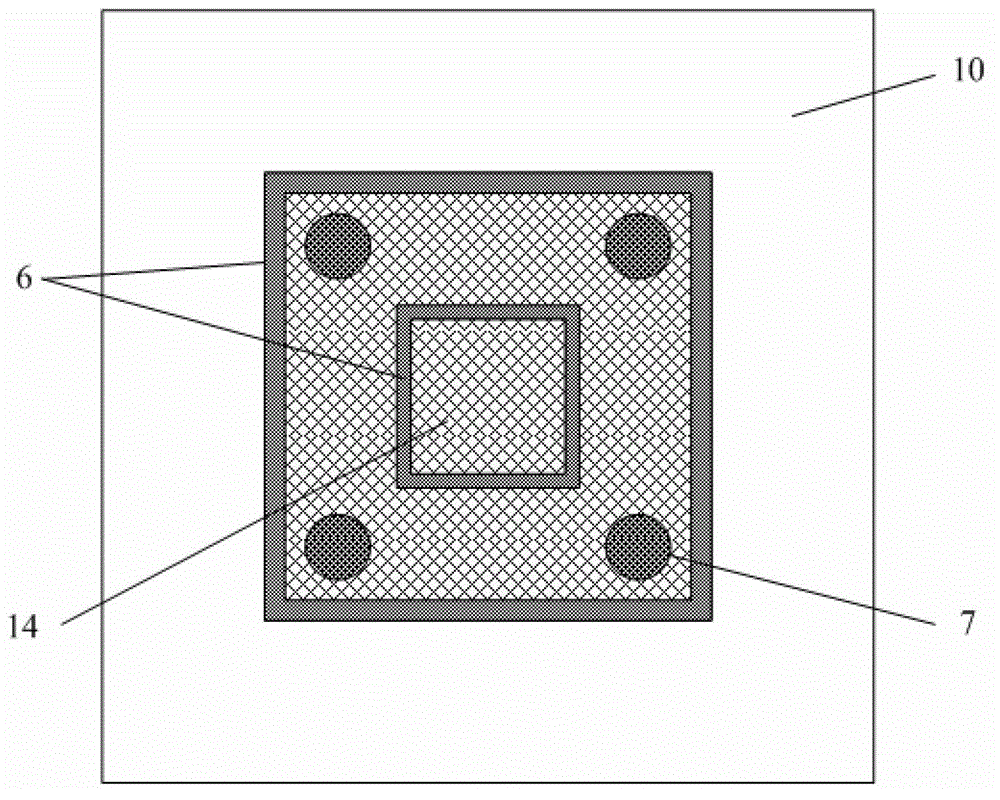

The invention discloses a superconducting quantum bit chip, comprising a quasi-one-dimensional network chain structure layout superconducting quantum bit array and a manipulating and reading microwavecircuit, wherein each mesh unit comprises n qubits, and m (m and n are natural numbers, n>m>=2) shared qubits between adjacent networks are used for interconnection between mesh units; Each superconducting qubit in the mesh unit is coupled to the same coplanar superconducting microwave cavity for interconnection of qubits in the network. Each qubit is coupled to a coplanar superconducting microwave cavity and further coupled to a coplanar microwave transmission line, and is connected to an external circuit for qubit state reading. The present application can effectively prevent the possibility of qubit interconnection breakpoints, greatly improve interconnection reliability, increase the flexibility of error correction coding design, effectively reduce the complexity of qubit manipulationand reading circuits, and has an important scientific research and industrial application prospect.

Owner:TSINGHUA UNIV

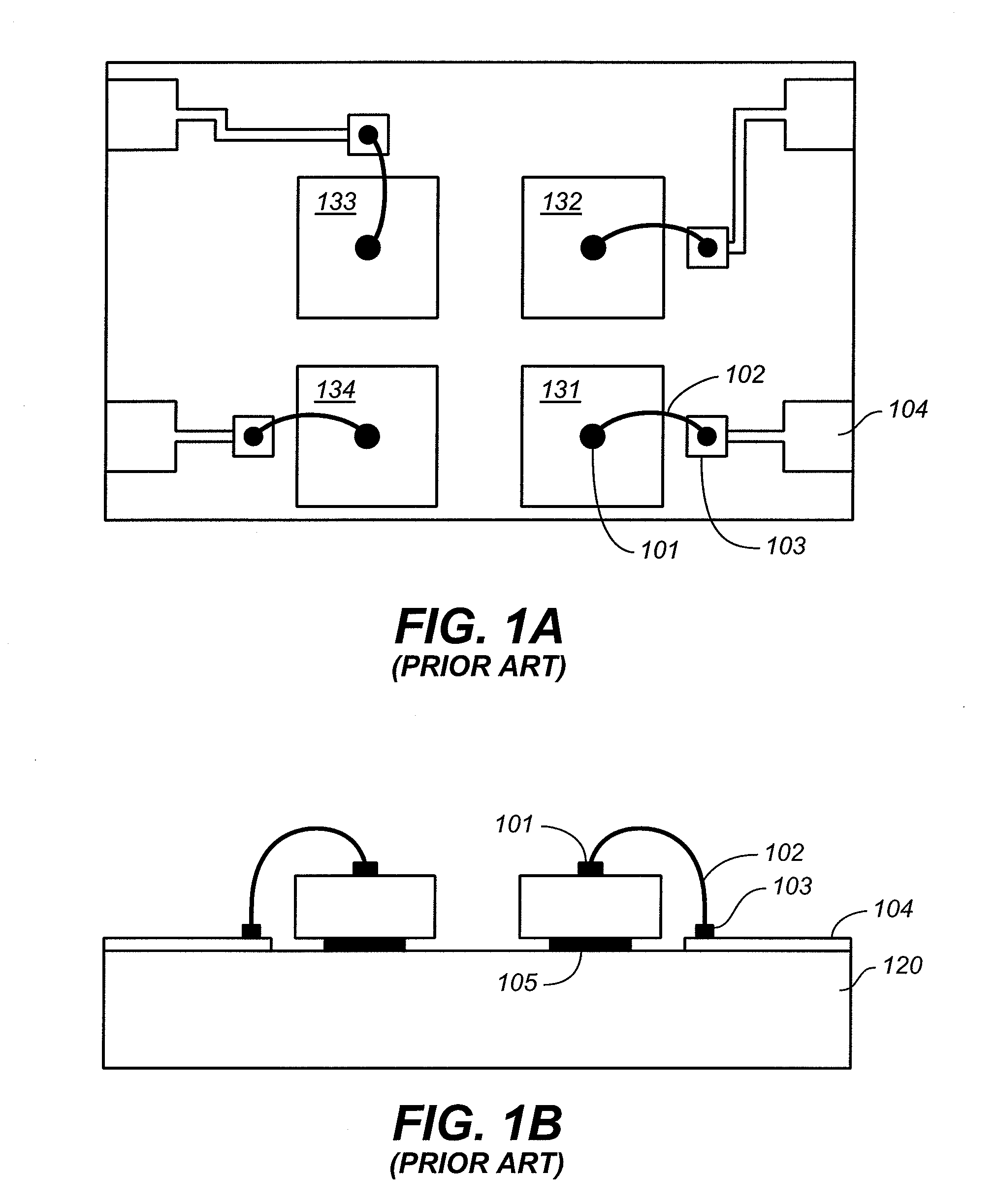

LED chip array module

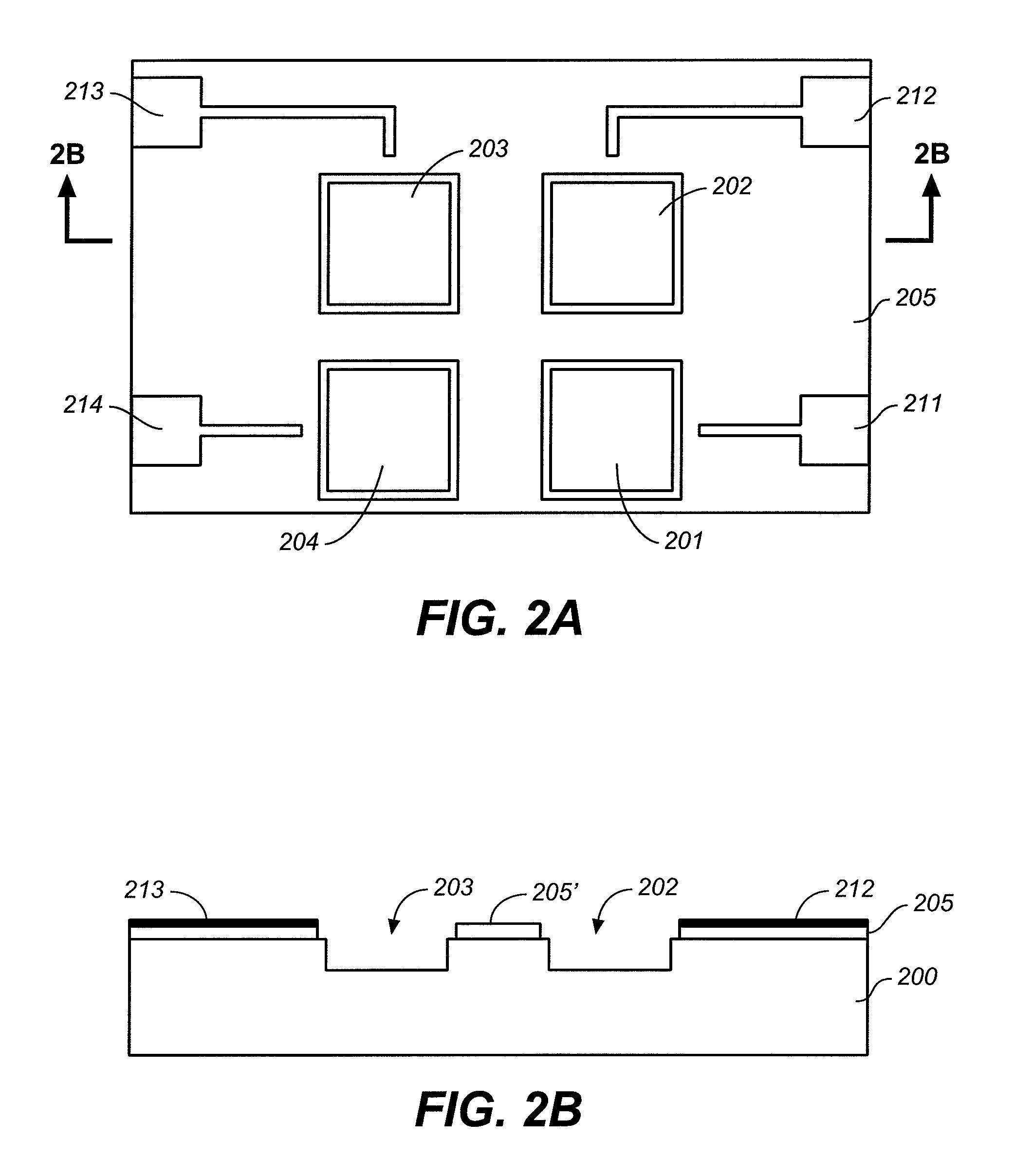

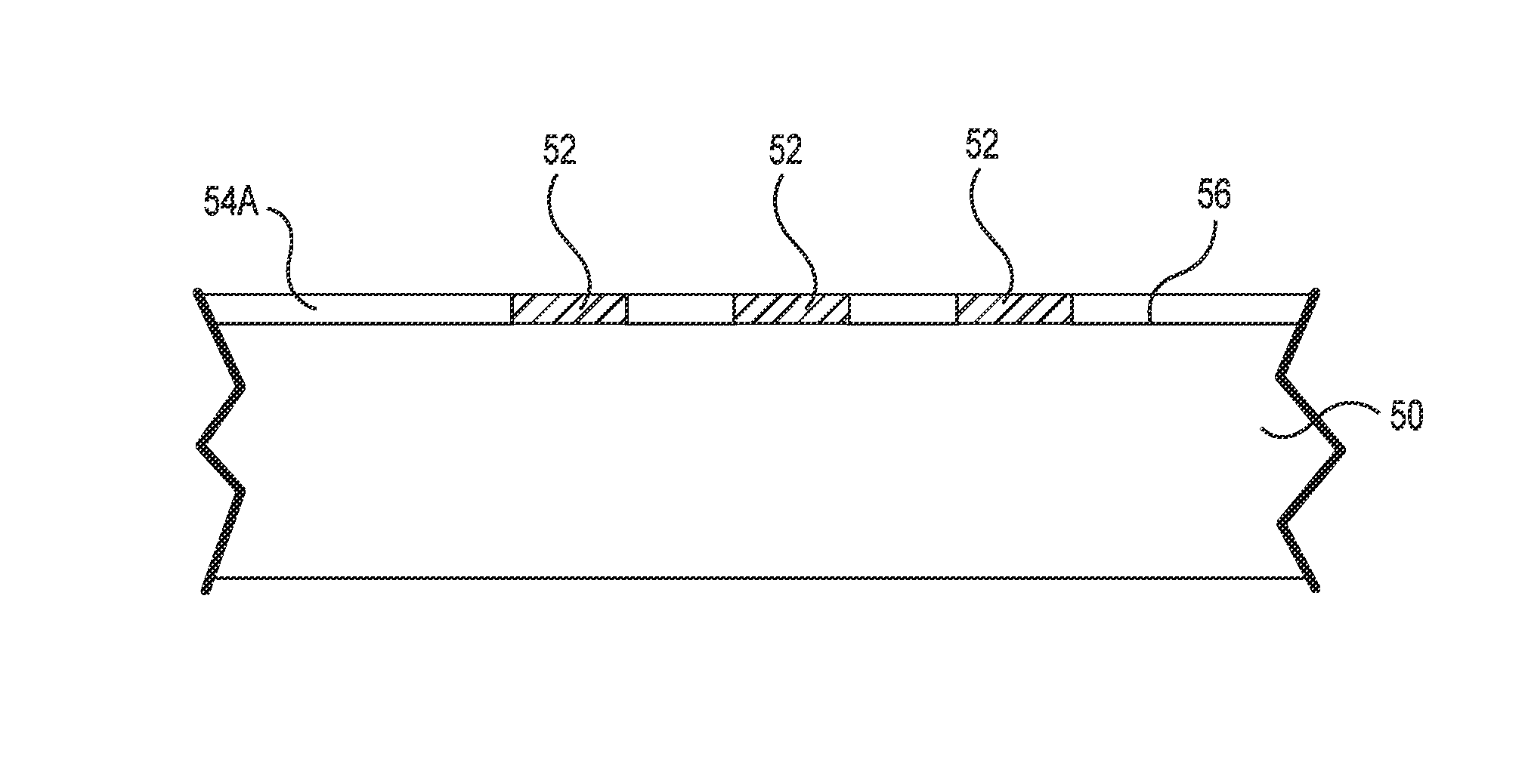

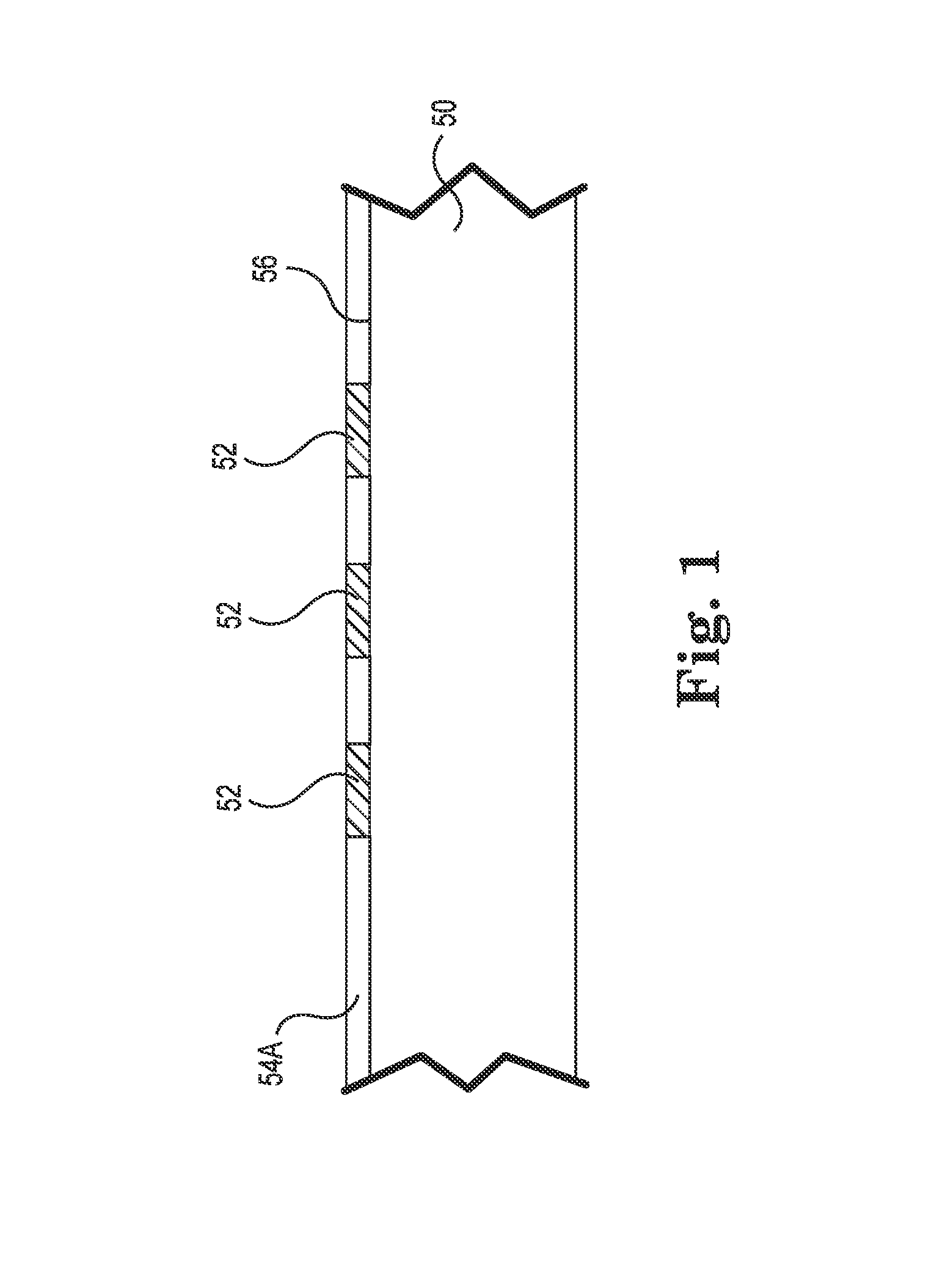

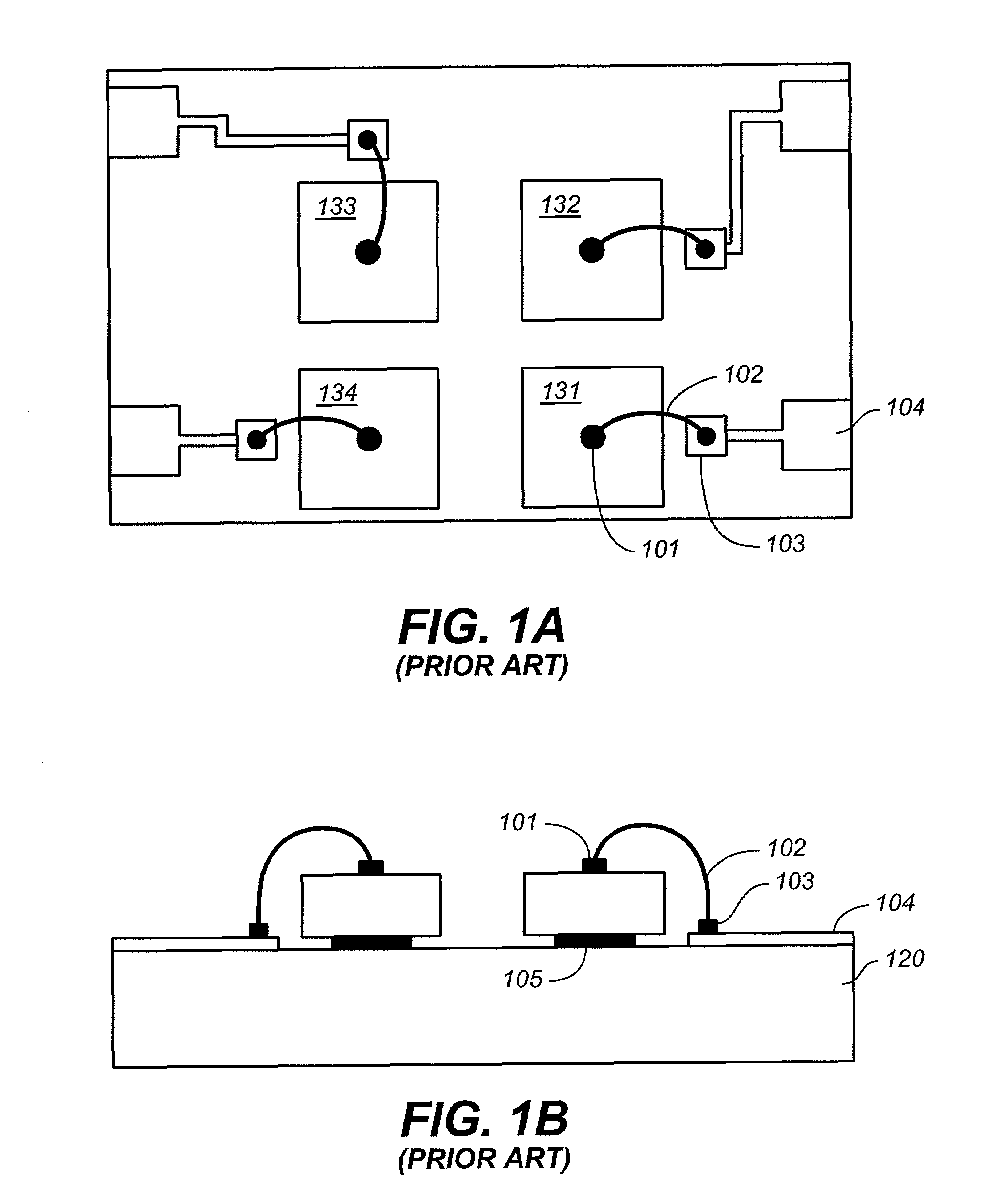

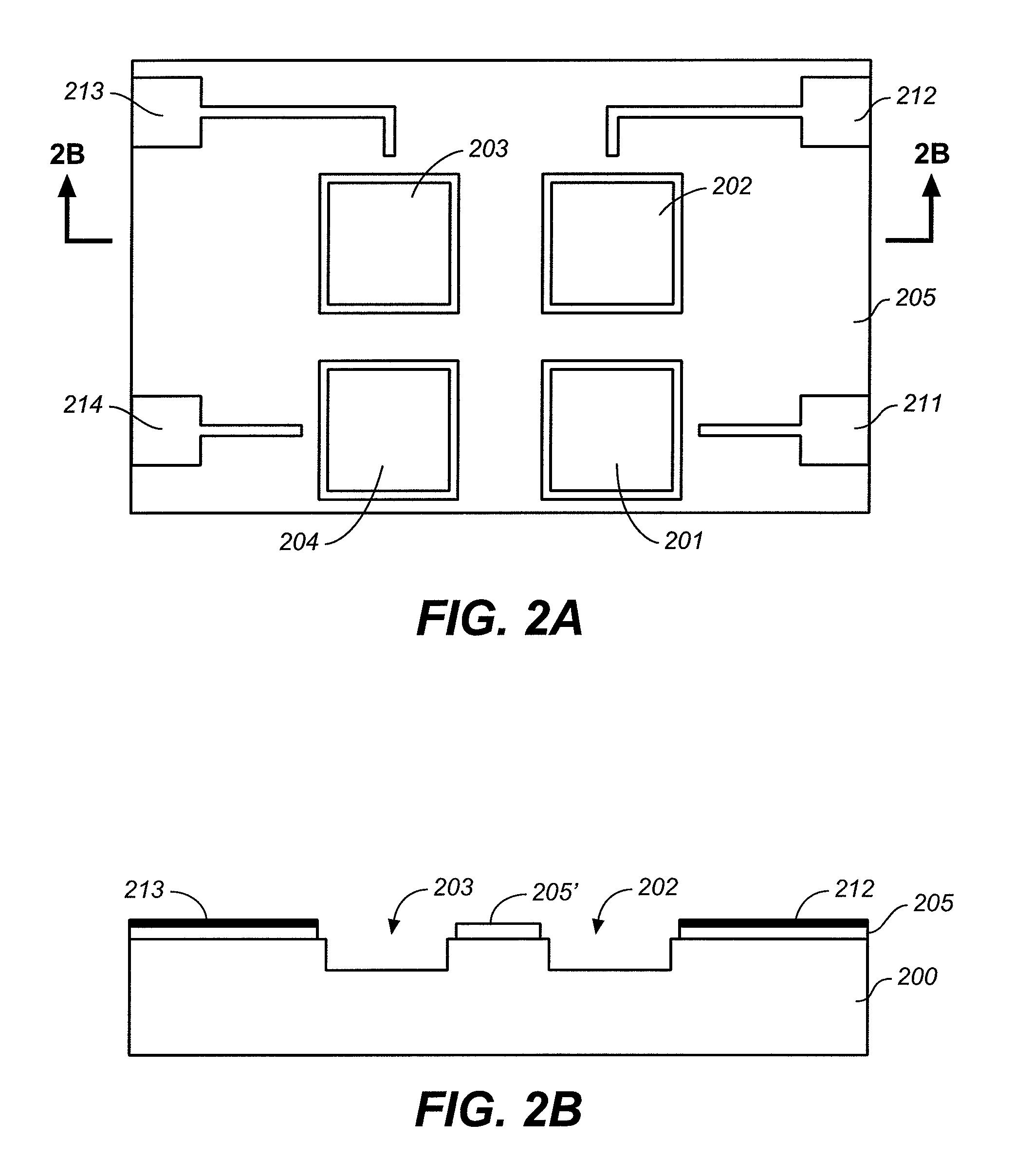

ActiveUS20070235863A1Simple processEnsure electrical connection reliabilitySemiconductor/solid-state device detailsSolid-state devicesWire bondingElectrical and Electronics engineering

The difficulties encountered in conventional LED multiple chip modules where wire bonding is used to connect the chips to electrodes can be overcome by using an interconnect to connect the chip to electrodes in a module where the interconnect is supported at points along its length other than at endpoints thereof, by a carrier either directly or indirectly. This improves reliability of the interconnect over conventional designs. Preferably, the contacts of the chips, and the electrodes are all within, or do not extend beyond, two parallel planes that are 400 microns apart for a compact design.

Owner:DICON FIBEROPTICS

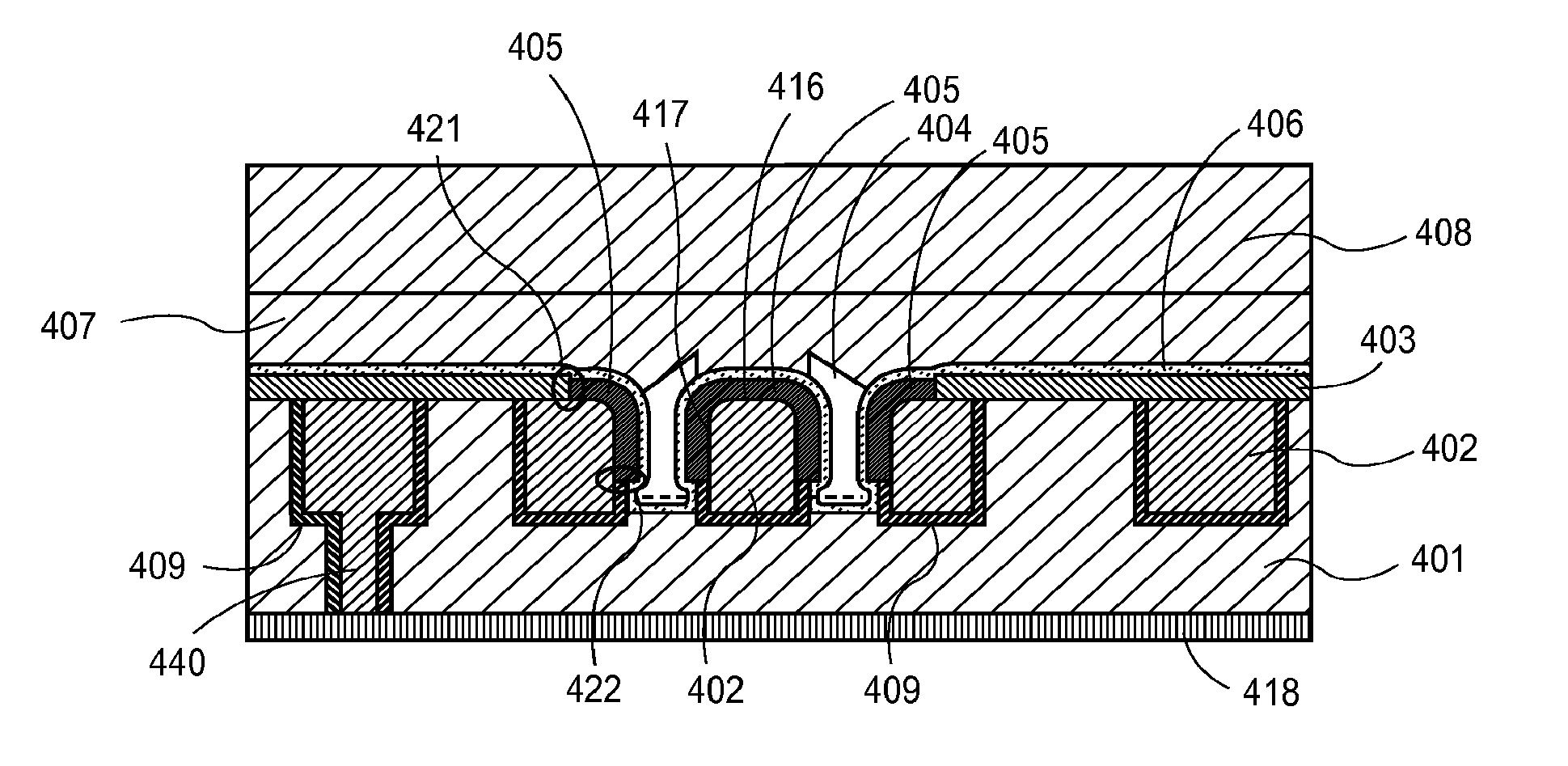

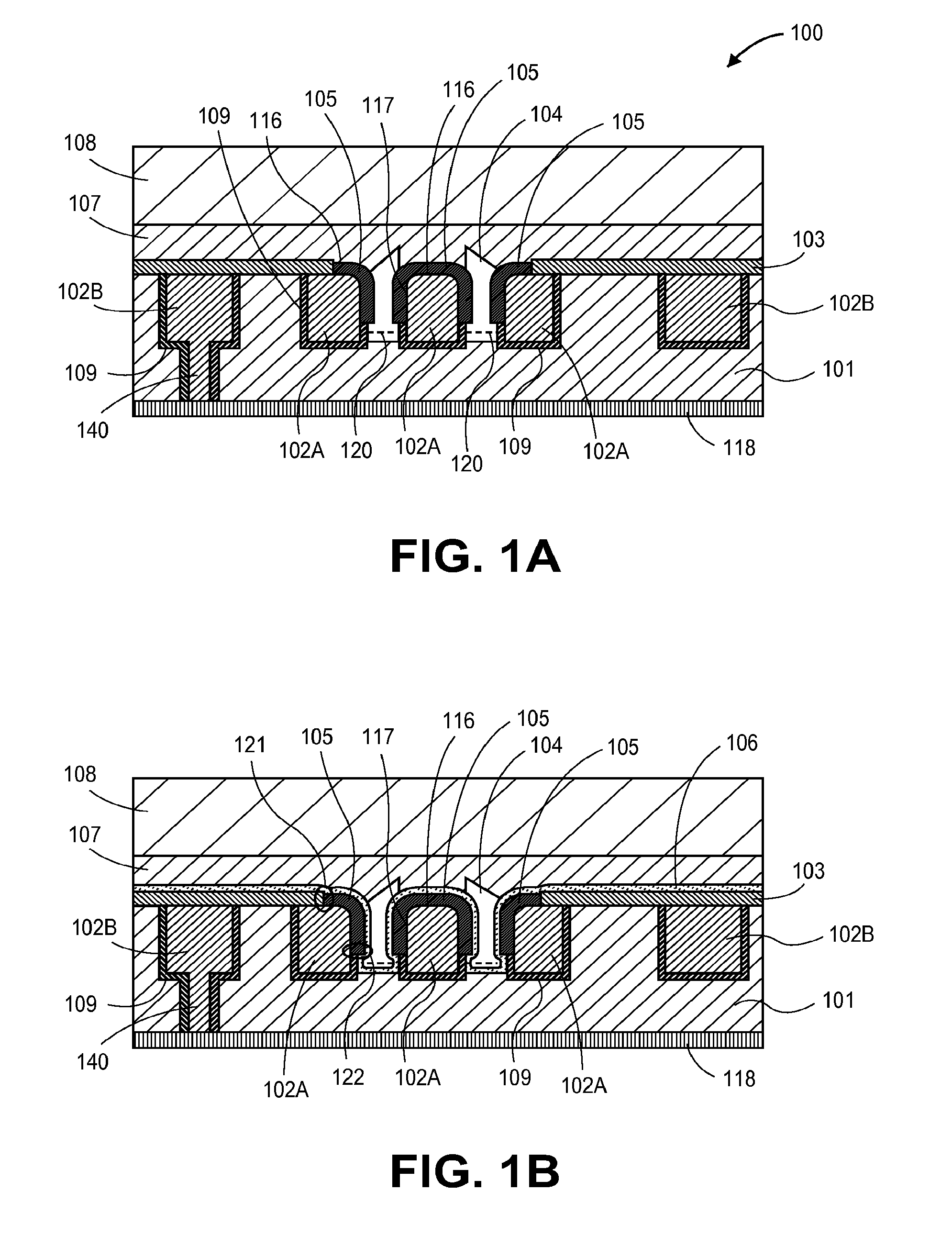

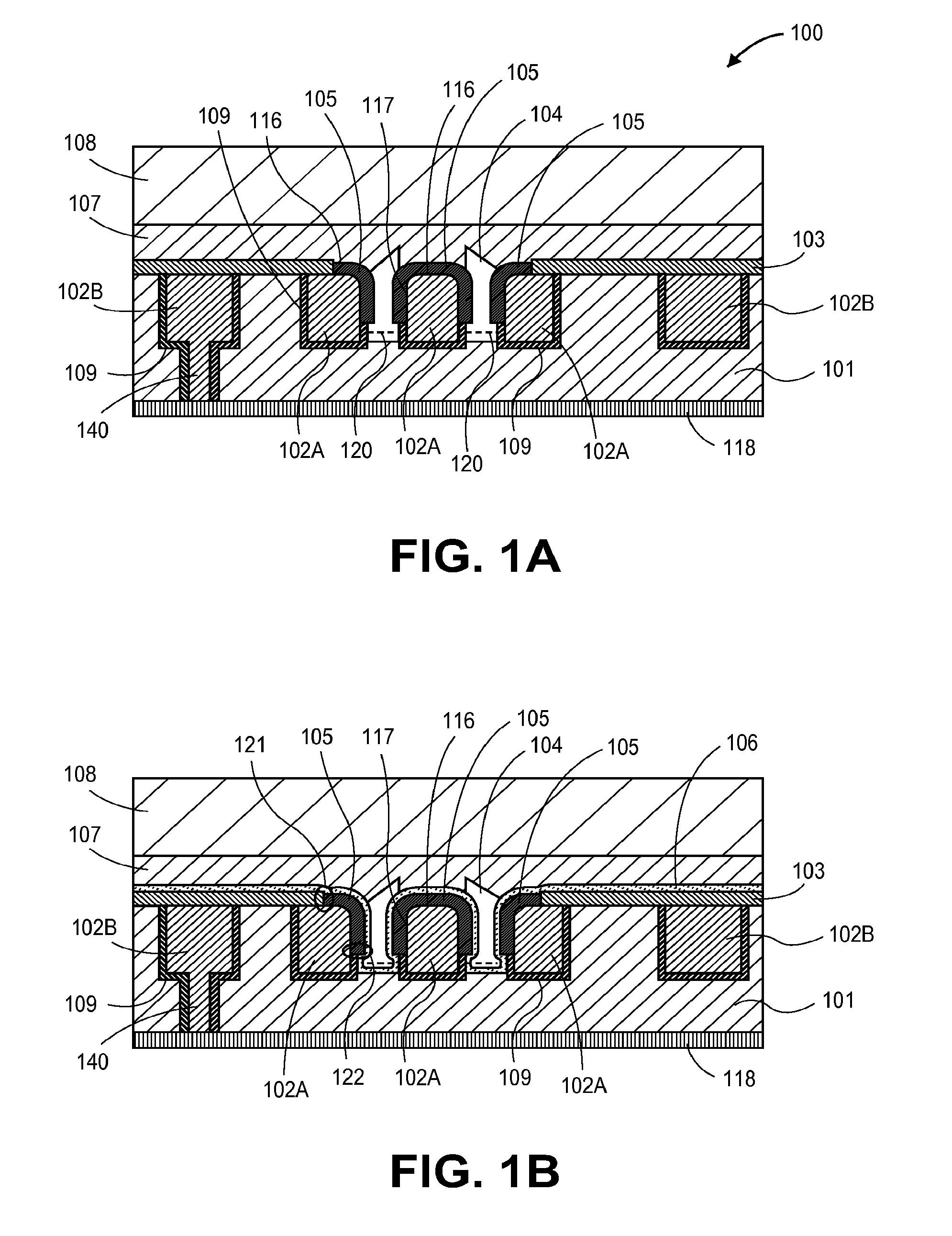

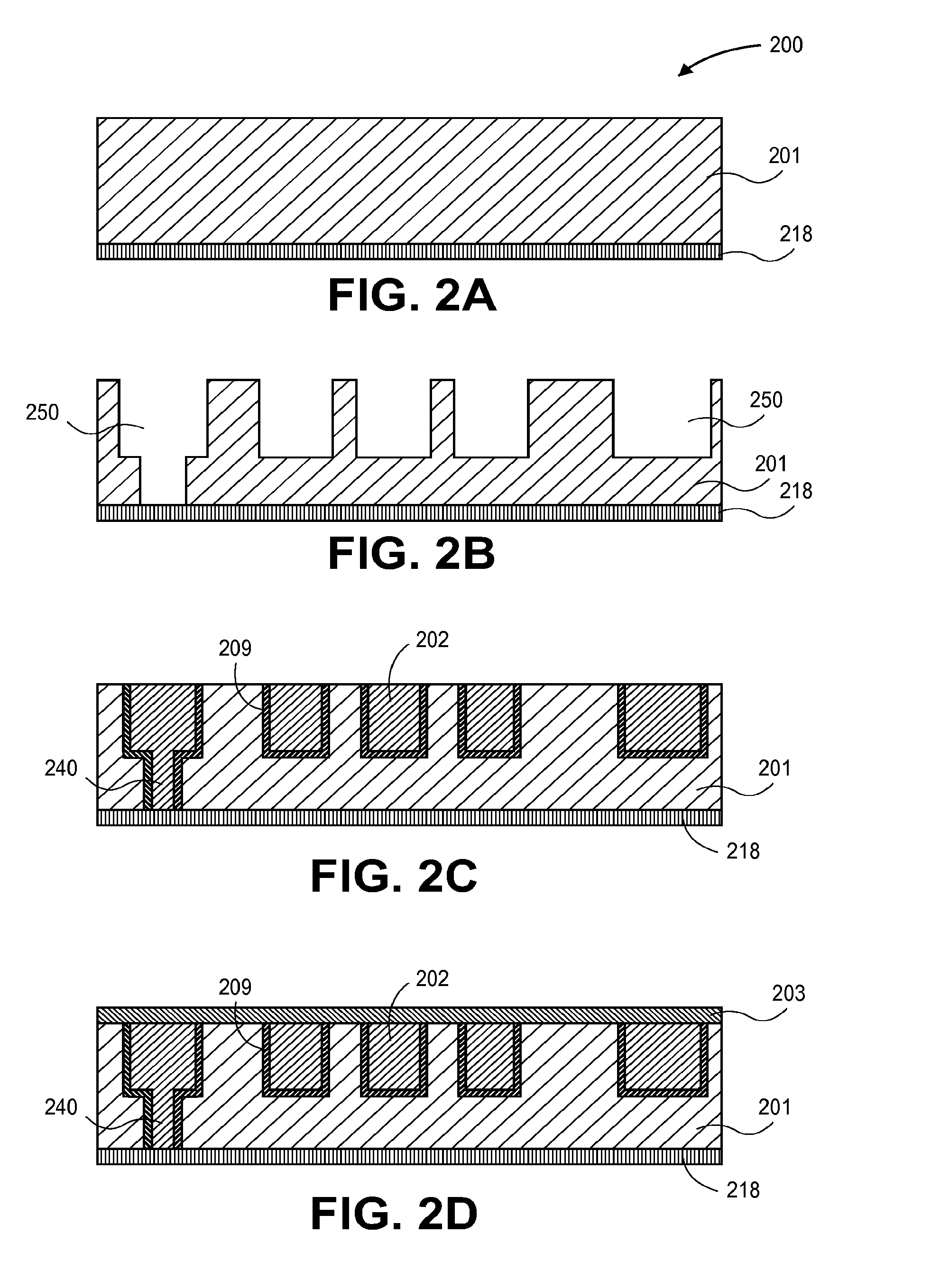

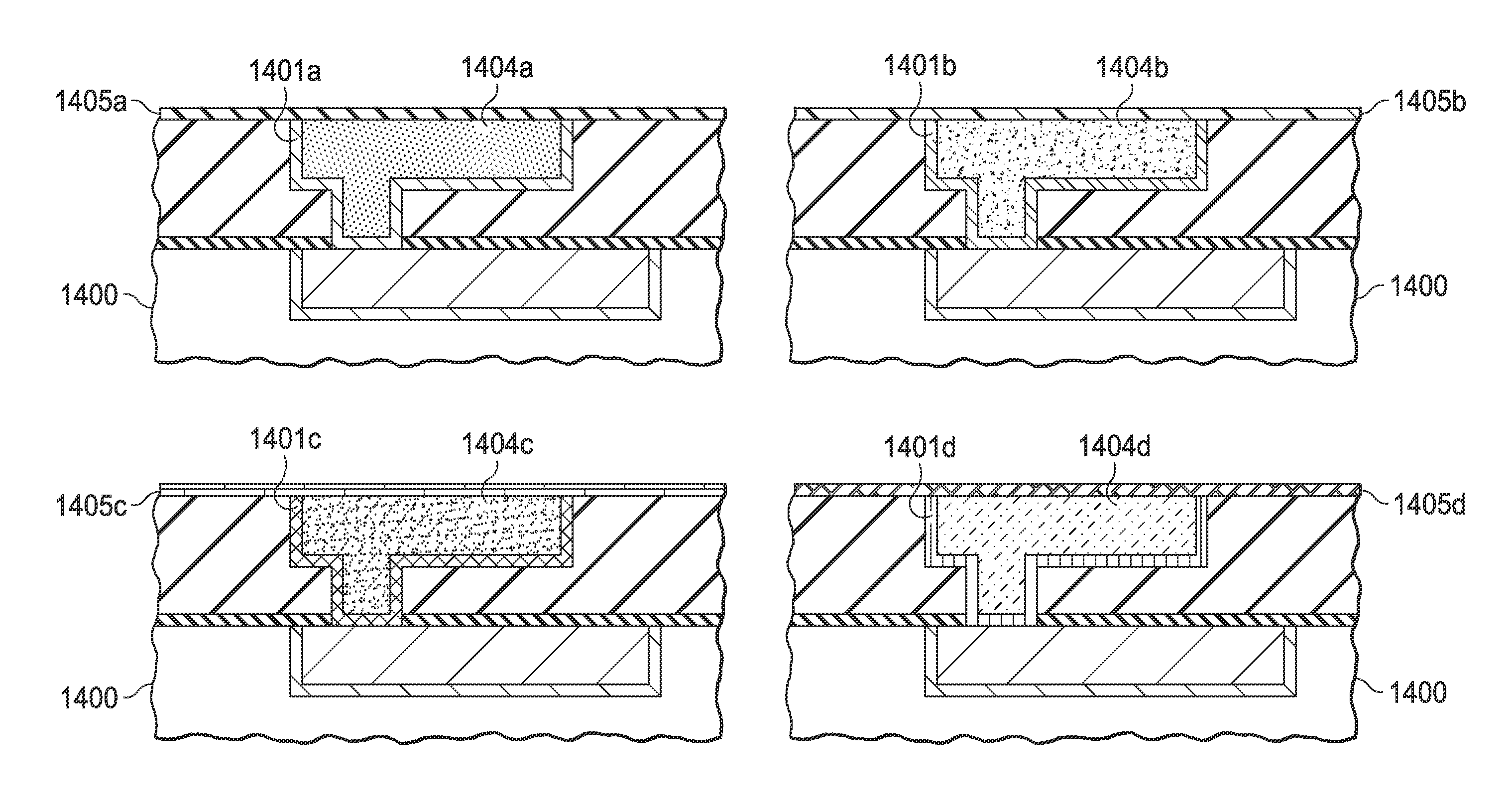

Airgap interconnect with hood layer and method of formiing

ActiveUS20140191401A1Improve interconnect reliabilitySemiconductor/solid-state device detailsSolid-state devicesCopper interconnectOptoelectronics

An airgap interconnect structure with hood layer and methods for forming such an airgap interconnect structure are disclosed. A substrate having a dielectric layer with a plurality of interconnects formed therein is provided. Each interconnect is encapsulated by a barrier layer. A hardmask is formed on the dielectric layer and patterned to expose the dielectric layer between adjacent interconnects where an airgap is desired. The dielectric layer is etched to form a trench, wherein the etching process additionally etches at least a portion of the barrier layer to expose a portion of the side surface of each adjacent copper interconnect. A hood layer is electrolessly plated onto an exposed portion of the top surface and the exposed portion of the side surface to reseal the interconnect. A gap-sealing dielectric layer is formed over the device, sealing the trench to form an airgap.

Owner:TAHOE RES LTD

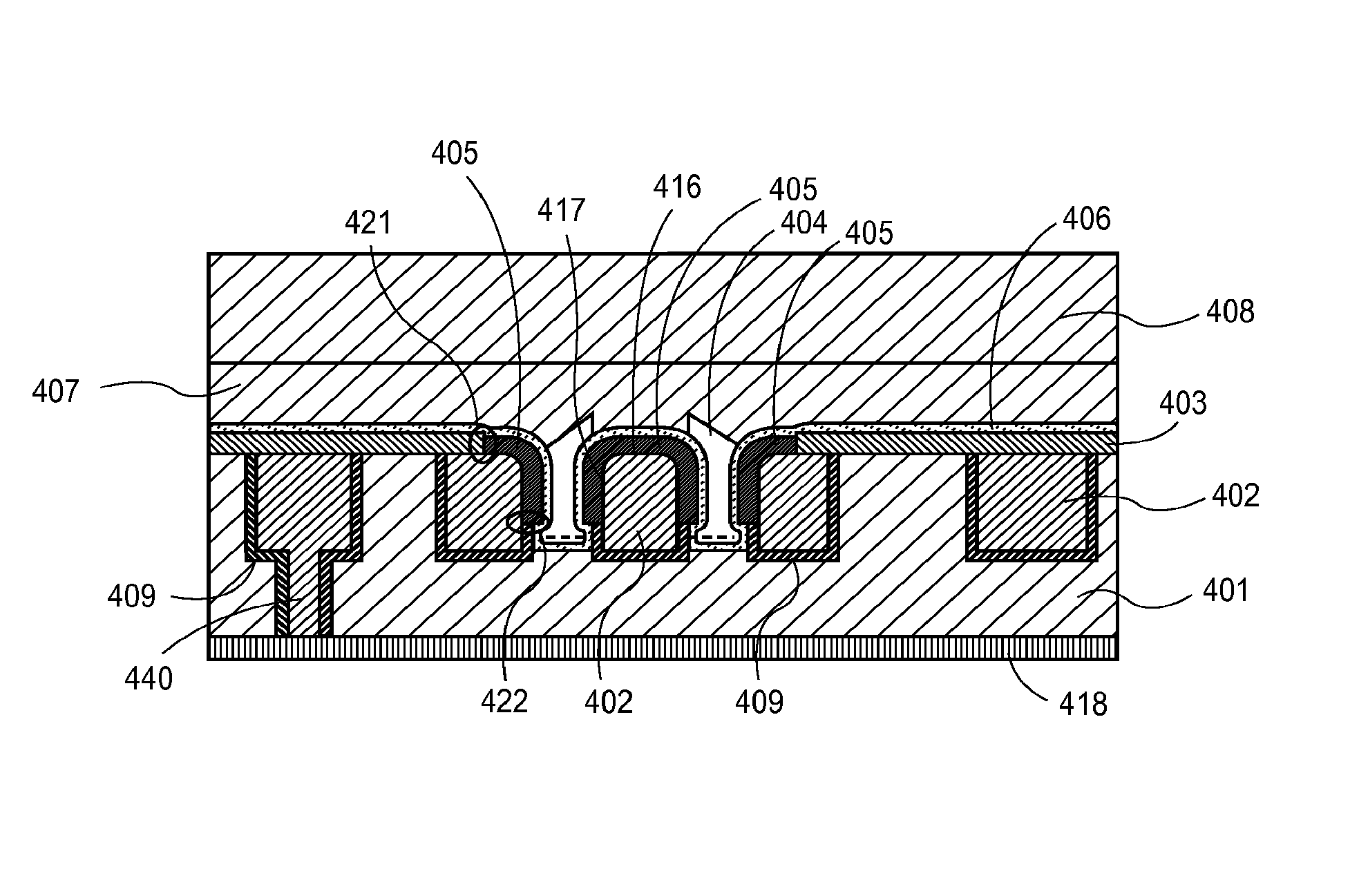

Airgap interconnect with hood layer and method of forming

ActiveUS9123727B2Improve interconnect reliabilitySemiconductor/solid-state device detailsSolid-state devicesCopper interconnectOptoelectronics

An airgap interconnect structure with hood layer and methods for forming such an airgap interconnect structure are disclosed. A substrate having a dielectric layer with a plurality of interconnects formed therein is provided. Each interconnect is encapsulated by a barrier layer. A hardmask is formed on the dielectric layer and patterned to expose the dielectric layer between adjacent interconnects where an airgap is desired. The dielectric layer is etched to form a trench, wherein the etching process additionally etches at least a portion of the barrier layer to expose a portion of the side surface of each adjacent copper interconnect. A hood layer is electrolessly plated onto an exposed portion of the top surface and the exposed portion of the side surface to reseal the interconnect. A gap-sealing dielectric layer is formed over the device, sealing the trench to form an airgap.

Owner:TAHOE RES LTD

Standoff structures for surface mount components

InactiveUS20070007323A1Improve surface mount interconnect reliabilityIncrease the amount of solderSecond resist patternFinal product manufactureEpoxySurface mounting

Increasing standoff height for surface mount components mounted to a laminate by image screening at least one standoff structure in a footprint area on the laminate surface. The standoff structure may comprise a filled epoxy and curing agents and may be cured by thermal treatment or by exposure to actinic radiation. The use of legend ink as a standoff structure offers a method and a structure for improving component standoff height without additional processing operations or cost.

Owner:IBM CORP

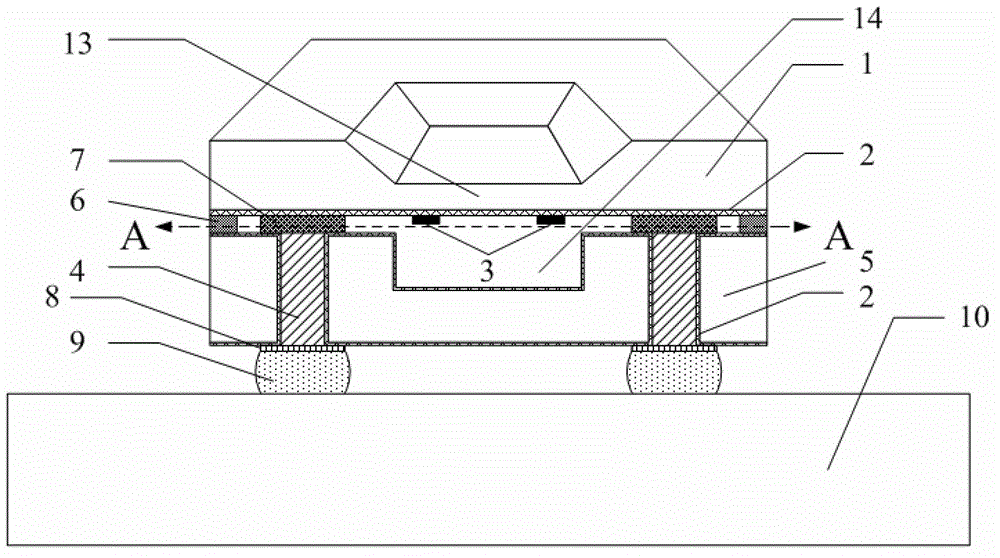

Pressure sensor encapsulation structure containing silicon through holes

InactiveCN102749167APackage structure is simpleReduce package sizeSolid-state devicesFluid pressure measurementMembrane technologyAir tightness

The invention provides a pressure sensor encapsulation structure containing silicon through holes, which uses a silicon base to substitute a traditional boron-phosphorosilicate glass base, and adopts a flip chip bonding technology and a bonding technology (such as CuSn bonding, AuSn eutectic bonding, Cu-Cu bonding and Au-Au bonding) to realize the airtight vacuum encapsulation of pressure sensors; a monocycle or bi-cycle bonding metal ring is adopted for encapsulation, and plays the role of reducing the bonding stress on the encapsulation of the pressure sensors with different piezoresistance strip distribution under the condition of ensuring the measurement sensitivity; and conductive columns are adopted for replacing metal wires to be used as signal lead wires, so the mutual connection reliability is increased. Compared with encapsulation structures of the silicon glass electrostatic bonding technology, the metal wire bonding technology, the metal isolating membrane technology and the airtight cavity silicone oil filling technology which are adopted traditionally, the pressure sensor encapsulation structure cancelled silicone oil filling and the metal isolating membrane, contributes to the improvement in the pressure sensor sensitivity, can also be used for dynamic pressure detection, and has the advantages of small size and high integration level.

Owner:PEKING UNIV

Solvent Assisted Burnishing of Pre-Underfilled Solder-Bumped Wafers for Flipchip Bonding

InactiveUS20070102827A1Simplify flip-chip assembly processLower assembly costsSemiconductor/solid-state device detailsSolid-state devicesAdhesiveElectrical connection

The present invention relates to a method for connecting an integrated circuit chip to a circuit substrate. The method includes the step of pre-applying adhesive directly to a bumped side of an integrated circuit chip. The method also includes the steps of removing portions of the adhesive from the tips of the solder bumps to expose a contact surface, and pressing the bumped side of the integrated circuit chip, which has previously been coated with adhesive, against the circuit substrate such that the bumps provide an electrical connection between the integrated circuit chip and the circuit substrate. The adhesive is removed from the tips of the solder bumps using a solvent assisted wiping action. The pre-applied adhesive on the chip forms a bond between the integrated circuit chip and the circuit substrate.

Owner:3M INNOVATIVE PROPERTIES CO

Semiconductor device having copper lines with reduced electromigration using an electroplated interim copper-zinc alloy film on a copper surface

InactiveUS6936925B1Reduce electromigrationLow mobilityElectrolysis componentsSemiconductor/solid-state device detailsCopper interconnectChemical solution

The present invention relates to the semiconductor device fabrication industry. More particularly a semiconductor device, having an interim reduced-oxygen Cu—Zn alloy thin film (30) electroplated on a blanket Cu surface (20) disposed in a via (6) by electroplating, using an electroplating apparatus, the Cu surface (20) in a unique chemical solution containing salts of Zn and Cu, their complexing agents, a pH adjuster, and surfactants; and annealing the interim electroplated Cu—Zn alloy thin film (30); filling the via (6) with further Cu (26); annealing and planarizing the interconnect structure (35). The reduction of electromigration in copper interconnect lines (35) is achieved by decreasing the drift velocity in the copper line (35) / via (6), thereby decreasing the copper migration rate as well as the void formation rate, by using an interim conformal Cu-rich Cu—Zn alloy thin film (30) electroplated on a Cu surface (20) from a stable chemical solution, and by controlling the Zn-doping thereof, which improves also interconnect reliability and corrosion resistance.

Owner:GLOBALFOUNDRIES INC

Method of reducing electromigration by forming an electroplated copper-zinc interconnect and a semiconductor device thereby formed

InactiveUS6717236B1Reduce electromigrationImprove corrosion resistanceTransistorElectrolysis componentsCopper interconnectChemical solution

A method of reducing electromigration in a dual-inlaid copper interconnect line (3) by filling a via (6) with a Cu-rich Cu-Zn alloy (30) electroplated on a Cu surface (200 from a stable chemical solution, and by controlling the Zn-doping thereof, which also improves interconnect reliability and corrosion resistance, and a semiconductor device thereby formed. The method involves using a reduced-oxygen Cu-Zn alloy as fill (30) for the via (6) in forming the dual-inlaid interconnect structure (35). The alloy fill (30) is formed by electroplating the Cu surface (20) in a unique chemical solution containing salts of Zn and Cu, their complexing agents, a pH adjuster, and surfactants, thereby electroplating the fill (30) on the Cu surface (20); and annealing the electroplated Cu-Zn alloy fill (30); and planarizing the Cu-Zn alloy fill (30), thereby forming the dual-inlaid copper interconnect line (35).

Owner:GLOBALFOUNDRIES US INC

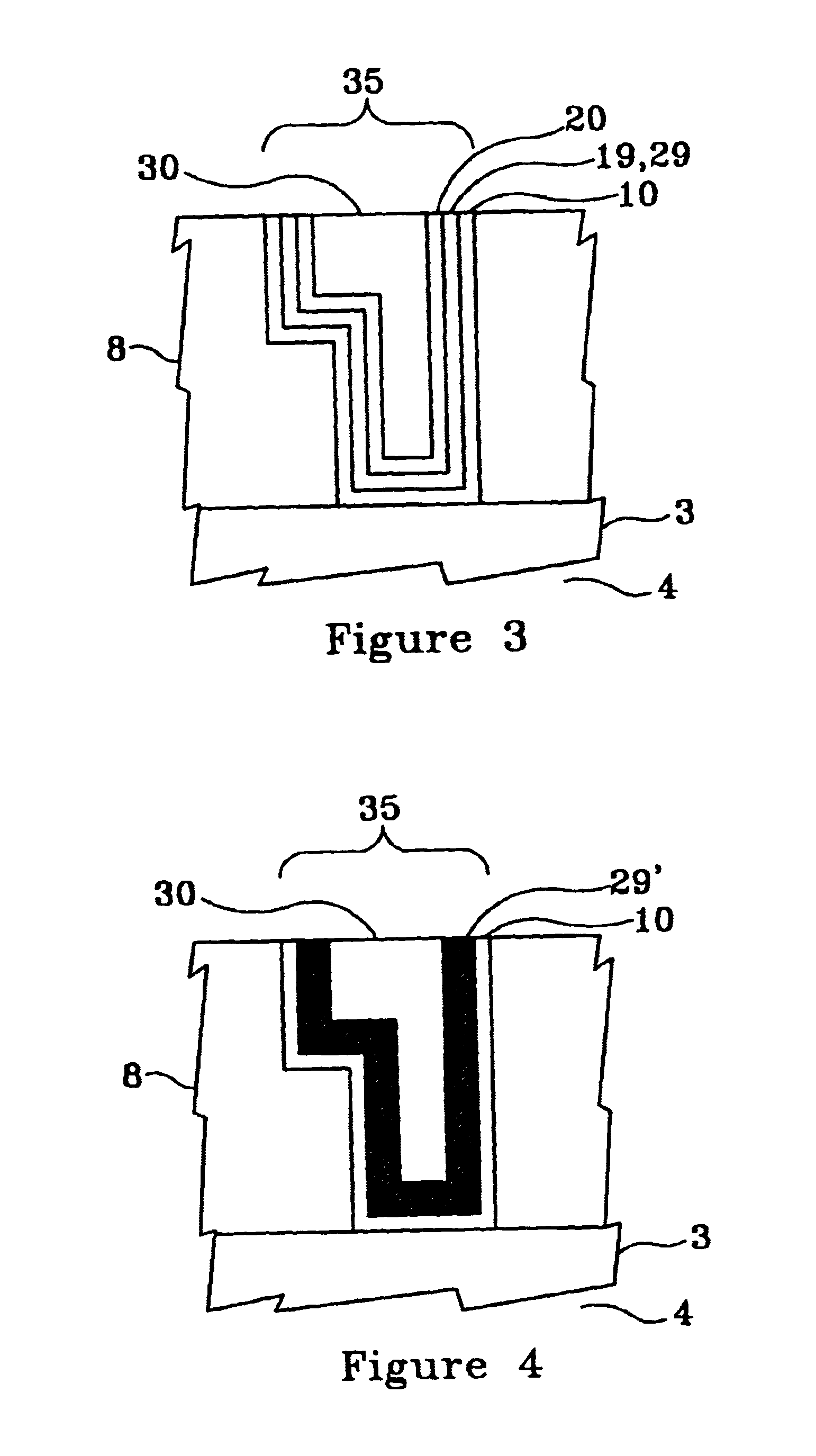

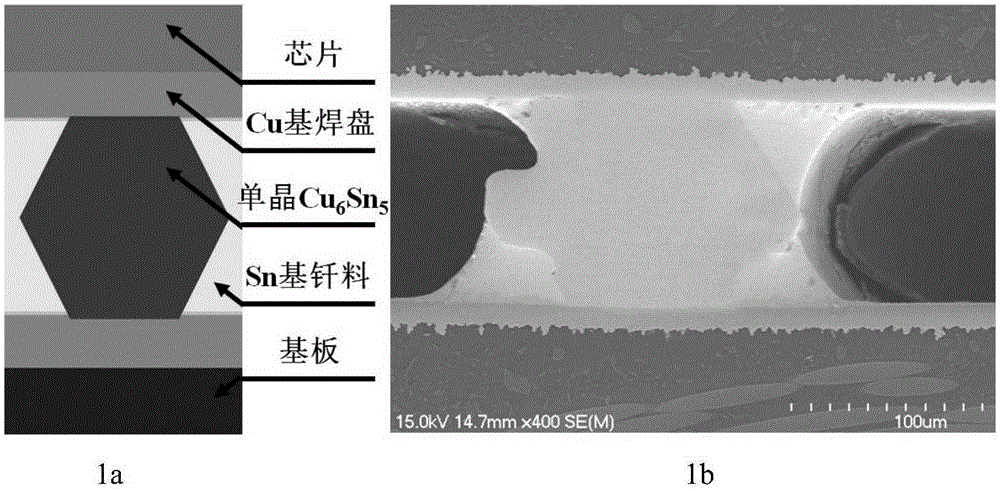

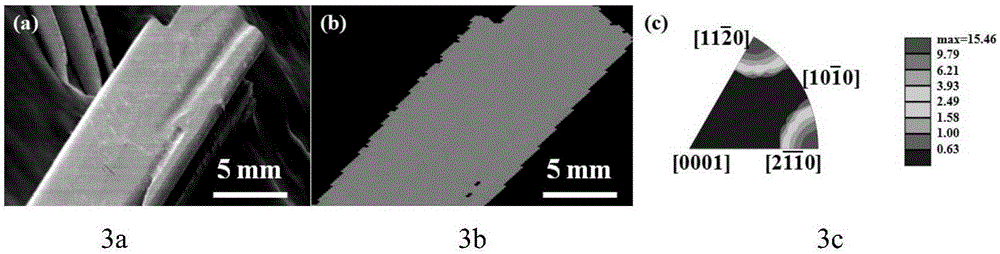

Directional interconnection method for Cu6Sn5-base single-crystal lead-free solder joints for high-temperature packaging

InactiveCN105171168ALow costStrong creep resistanceSolid-state devicesSemiconductor/solid-state device manufacturingInterconnectionFiller metal

The invention belongs to the technical field of materials, and provides a directional interconnection method for Cu6Sn5-base single-crystal lead-free solder joints for high-temperature packaging. The method comprises the steps of firstly, preparation of a Cu6Sn5-base single-crystal block body, secondly, cutting of the Cu6Sn5-base single-crystal block body, thirdly, surface pretreatment of a Cu-base welding disc, and fourthly, interconnection of Cu6Sn5-base single-crystal welding blocks. The elasticity modulus of the Cu6Sn5-base single-crystal lead-free interconnected solder joints prepared with the method is 235% of that of common Sn-base brazing filler metal, the conductivity of the Cu6Sn5-base single-crystal lead-free interconnected solder joints is 52.4% that of the Sn-base brazing filler metal, and the heat conductivity of the Cu6Sn5-base single-crystal lead-free interconnected solder joints is 57.8% that of the Sn-base brazing filler metal. The method has the beneficial effects of being low in cost, resistant to high temperature, high in reliability of interconnection of the solder joints and a Cu-base welding disc, high in creep-resistance, and capable of being used for a long time under the severe condition. The method has the beneficial effects of being simple in working principle, low in cost, rapid in single-crystal preparation and high in quality.

Owner:HARBIN INST OF TECH SHENZHEN GRADUATE SCHOOL

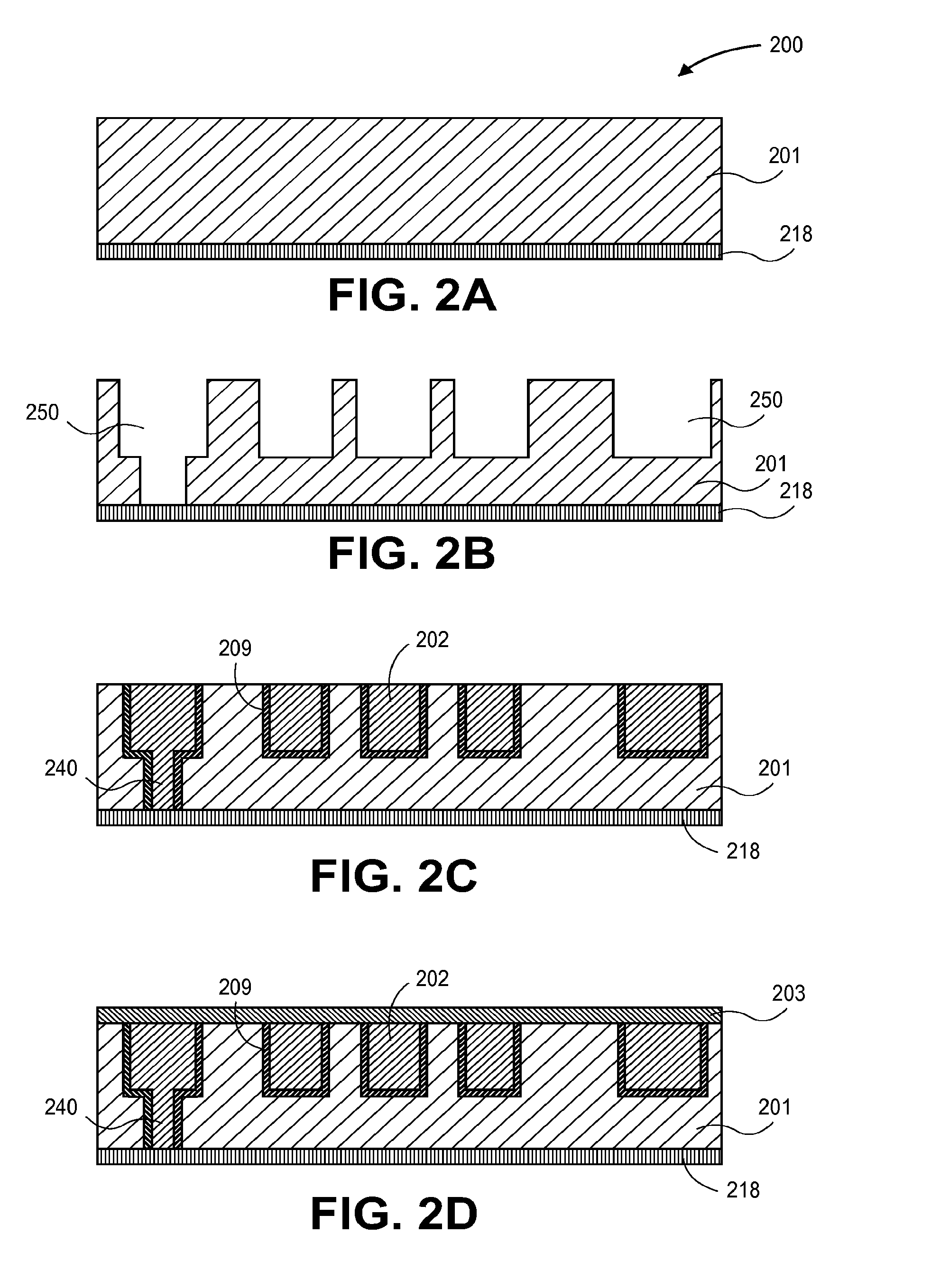

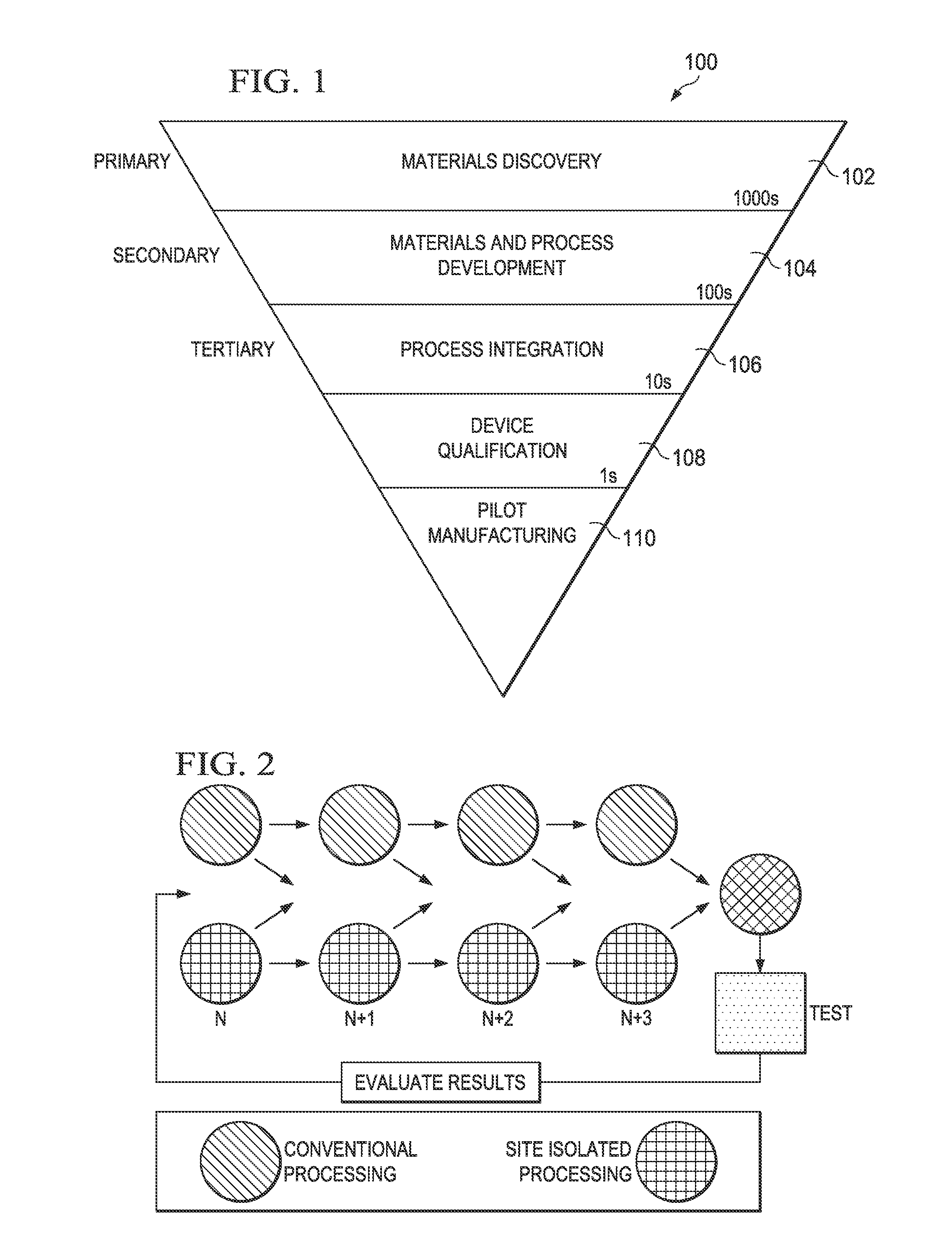

Method to Increase Interconnect Reliability

InactiveUS20140264871A1Increase metal interconnect reliabilityImprove interconnect reliabilitySemiconductor/solid-state device detailsSolid-state devicesMetal interconnectGrain growth

Methods to increase metal interconnect reliability are provided. Methods include forming a conformal barrier layer within an opening in a semiconductor device structure and forming a copper alloy material above the conformal barrier layer. Next, removing the copper alloy material that extends beyond the opening. Removing native oxide from a top surface of the copper alloy material. Further, annealing or applying a plasma treatment to the copper alloy material. Finally, forming a capping layer above the copper alloy material. Notably, near the top of the copper alloy material, smaller copper grain growth may be present. Furthermore, more non-copper alloy atoms are present near the top of the copper alloy material than the bulk of the copper alloy material.

Owner:INTERMOLECULAR

Millimeter-wave air slot differential integrated antenna

InactiveCN107591618AReduce processing difficultyReduced precision requirementsRadiating elements structural formsAntennas earthing switches associationCapacitanceAntenna bandwidth

The invention discloses a millimeter-wave air slot differential integrated antenna. The millimeter-wave air slot differential integrated antenna comprises five parts, namely, a differential feeding network, a radiation module, a directed radiation module, a bond wire compensation network and a back cavity air slot; each of the radiation module and the directed radiation module is composed of an even number of radiating patch units which are in bilateral symmetry; signals are divided and transmitted to each radiating patch unit through a differential line and a one-to-many T-shaped structure; the back surface ground part of the antenna is partially etched; an air cavity is formed in a base, so that the bandwidth of the antenna can be extended; the antenna is connected with a chip through bond wires; in order to compensate the inductive effect of the bond wires, a capacitive patch is arranged between the bond wires, so that an L(inductor)-C(capacitor)-L(inductor) network can be formed, and therefore, interconnection loss of the antenna and the chip can be reduced; and in order to extend the bandwidth of the antenna, parasitic patches are arranged beside the radiating patch units. According to the millimeter-wave air slot differential integrated antenna of the invention, a dielectric material of which the height is consistent with the height of the chip is adopted to design the antenna, and therefore, the sticking, bonding and packaging of the antenna and the chip can be benefitted.

Owner:SOUTHEAST UNIV

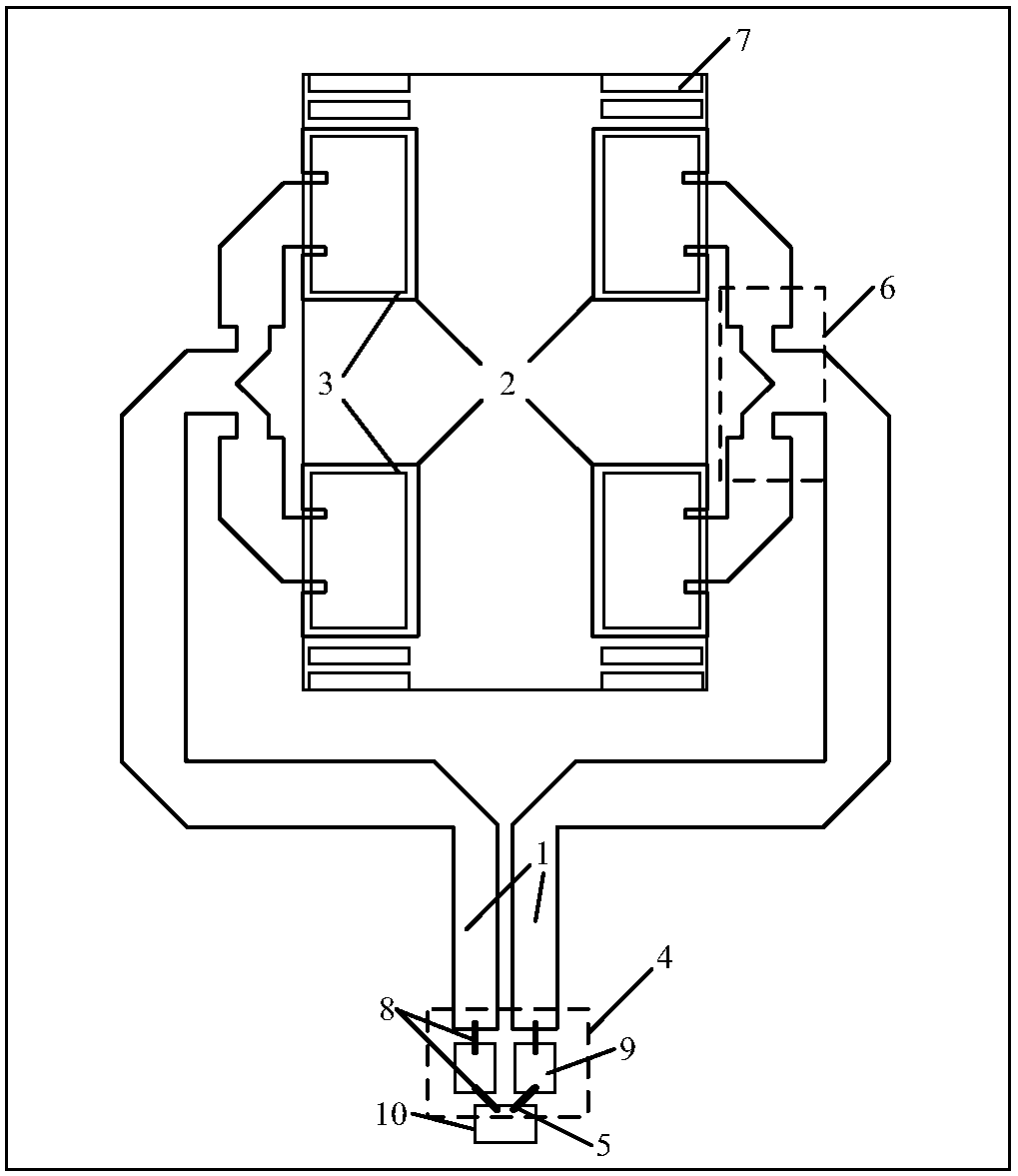

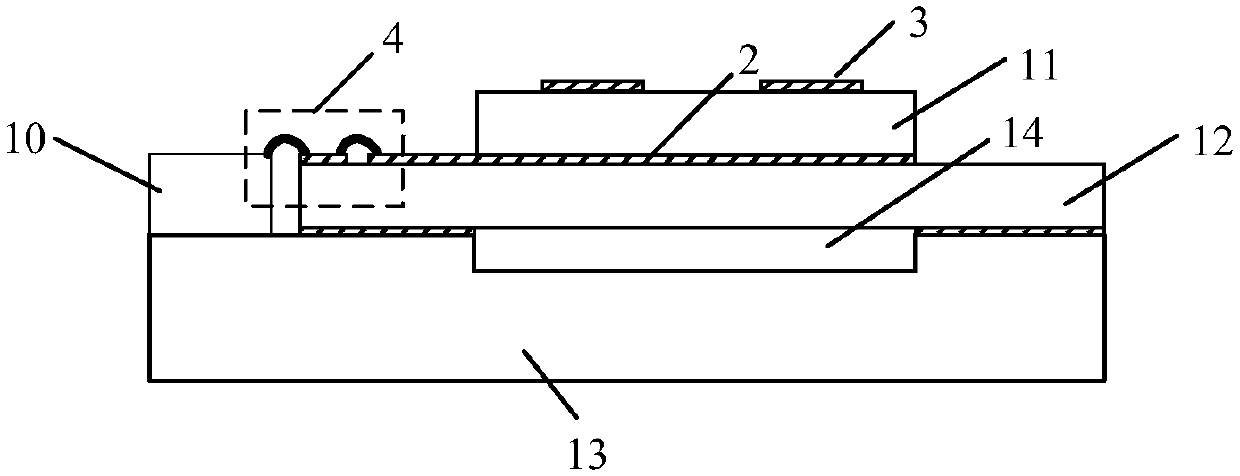

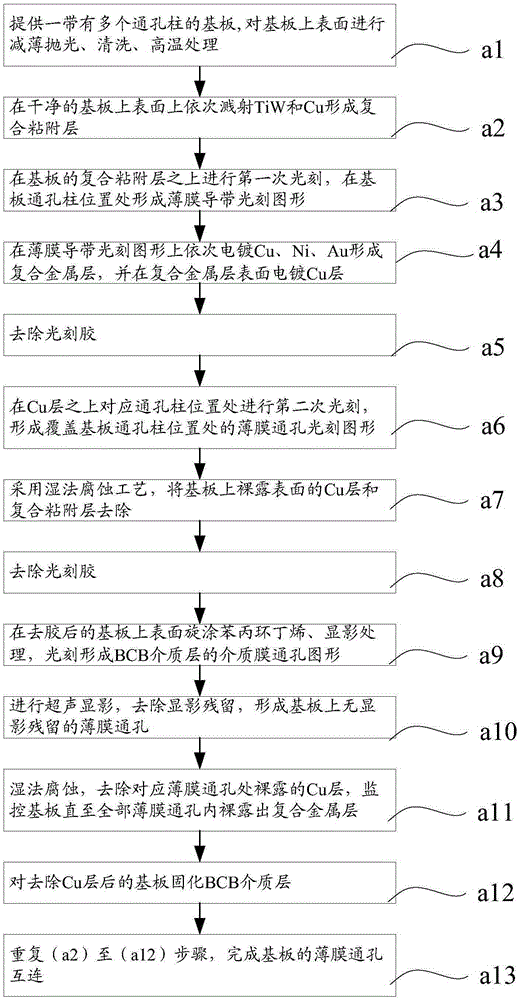

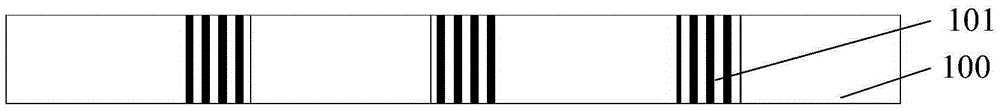

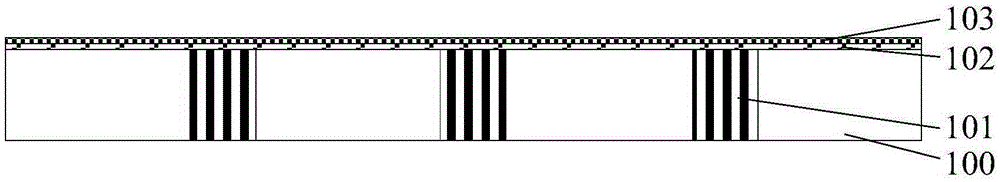

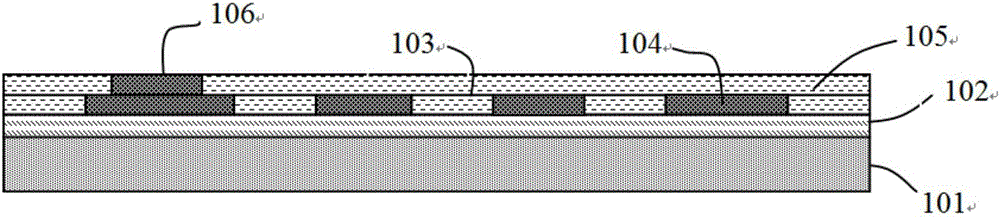

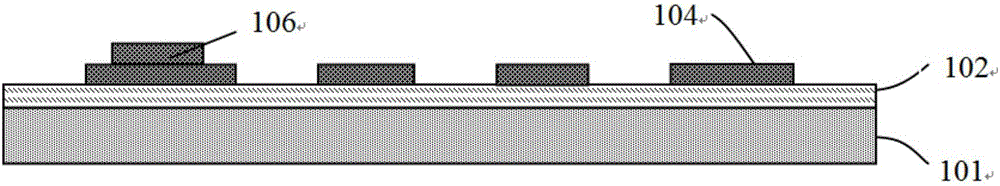

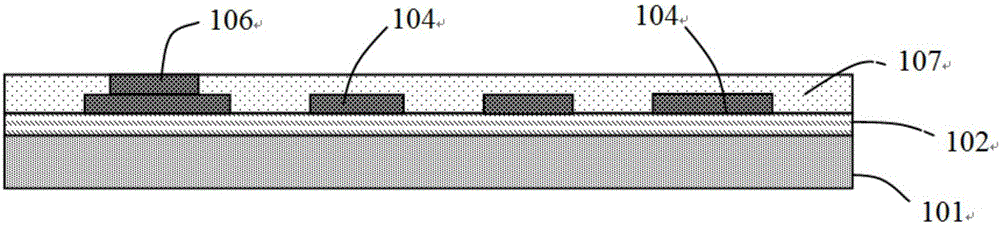

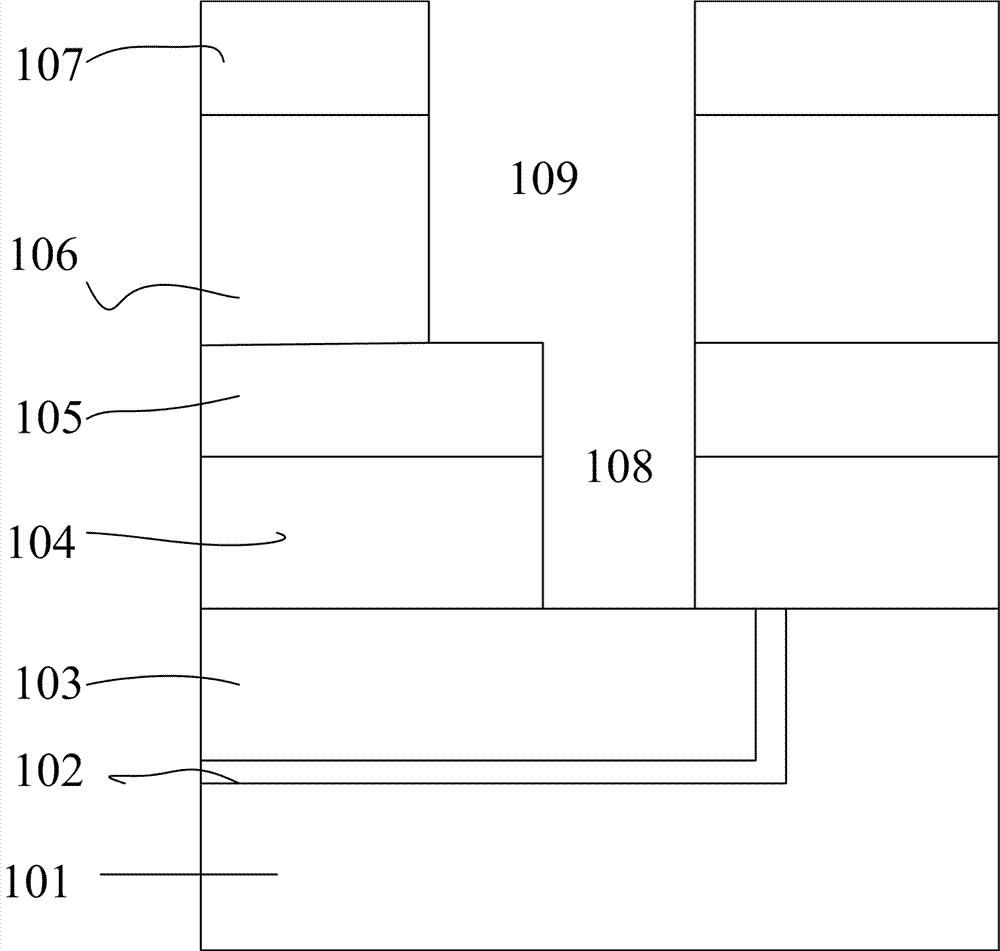

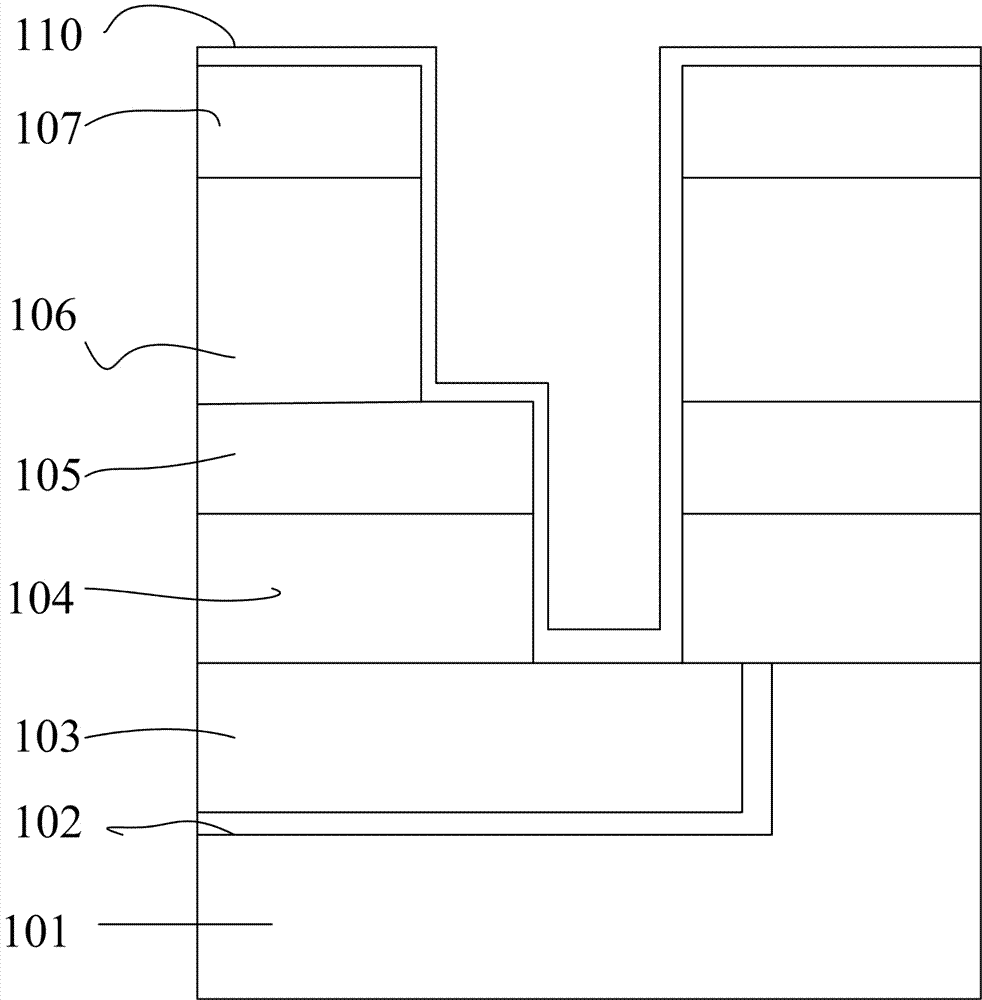

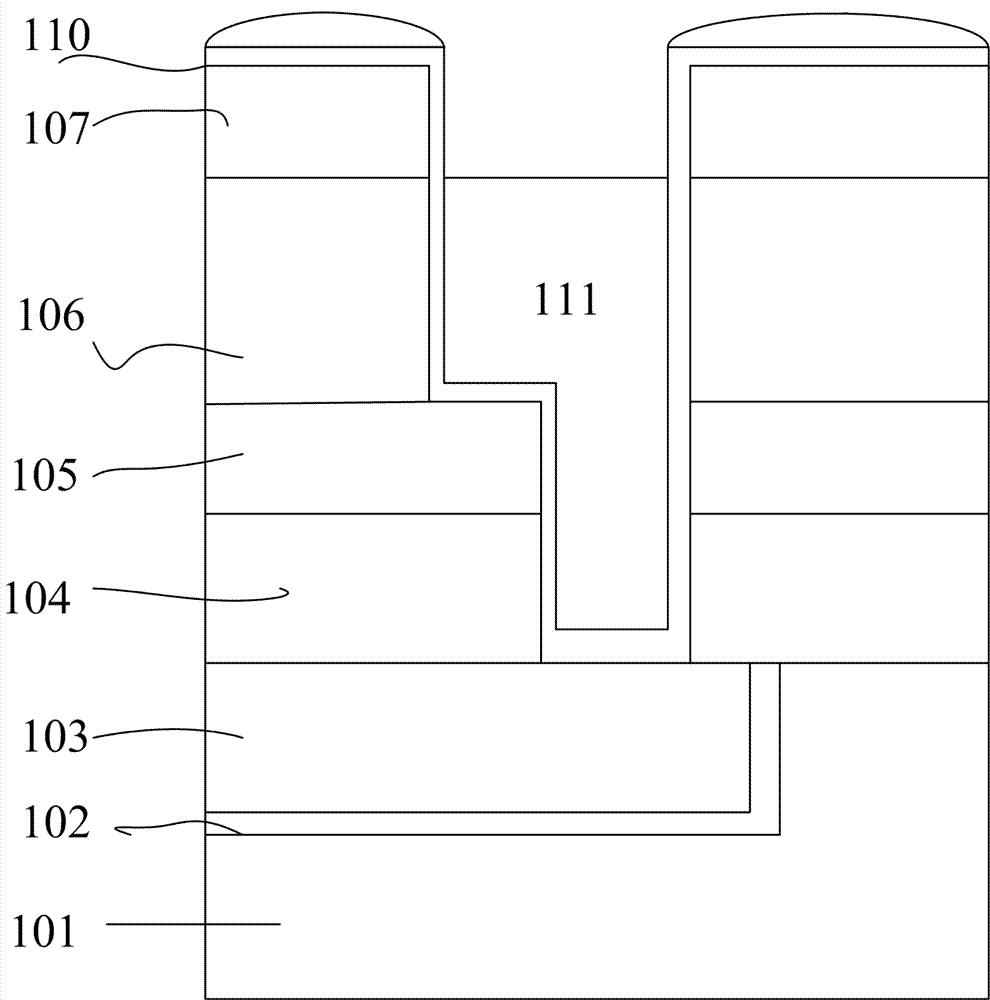

Interconnection manufacturing method for film through holes in substrate

ActiveCN105244313AImprove interconnect reliabilitySimple processSemiconductor/solid-state device manufacturingState of artEtching

The invention provides an interconnection manufacturing method for film through holes in a substrate. A composite adhesive layer is sputtered on the upper surface of the clean substrate; photoetching is carried out on the composite adhesive layer to form a film conduction band photoetching graph; a composite metal layer is electroplated, and a Cu layer is electroplated on the surface; removing of photoresist is carried out; photoetching is carried out at a corresponding through hole column above the Cu layer, and a film through hole photoetching graph is formed; wet etching is carried out, and the Cu layer exposed on the surface and the composite adhesive layer are removed; removing of photoresist is carried out; spin coating of benzocyclobutene (BCB) is carried out, development processing is carried out, and a dielectric film through hole graph is formed through photoetching; an ultrasonic development method is used, and development residues are removed; wet etching is carried out, the exposed Cu layer at the corresponding film through hole is removed, and the substrate is monitored online until the composite metal layer is exposed in all film through holes; the BCB dielectric layer is cured, and interconnection of film through holes in the substrate is completed. Problems that the process in the prior art is complicated, the contact resistance is large, reliability is low, through hole connection and disconnection detection can not be realized online, and the like are overcome, and interconnection of high-density through holes of multi-layer wiring of the film can be realized.

Owner:SHANGHAI SPACEFLIGHT ELECTRONICS & COMM EQUIP RES INST

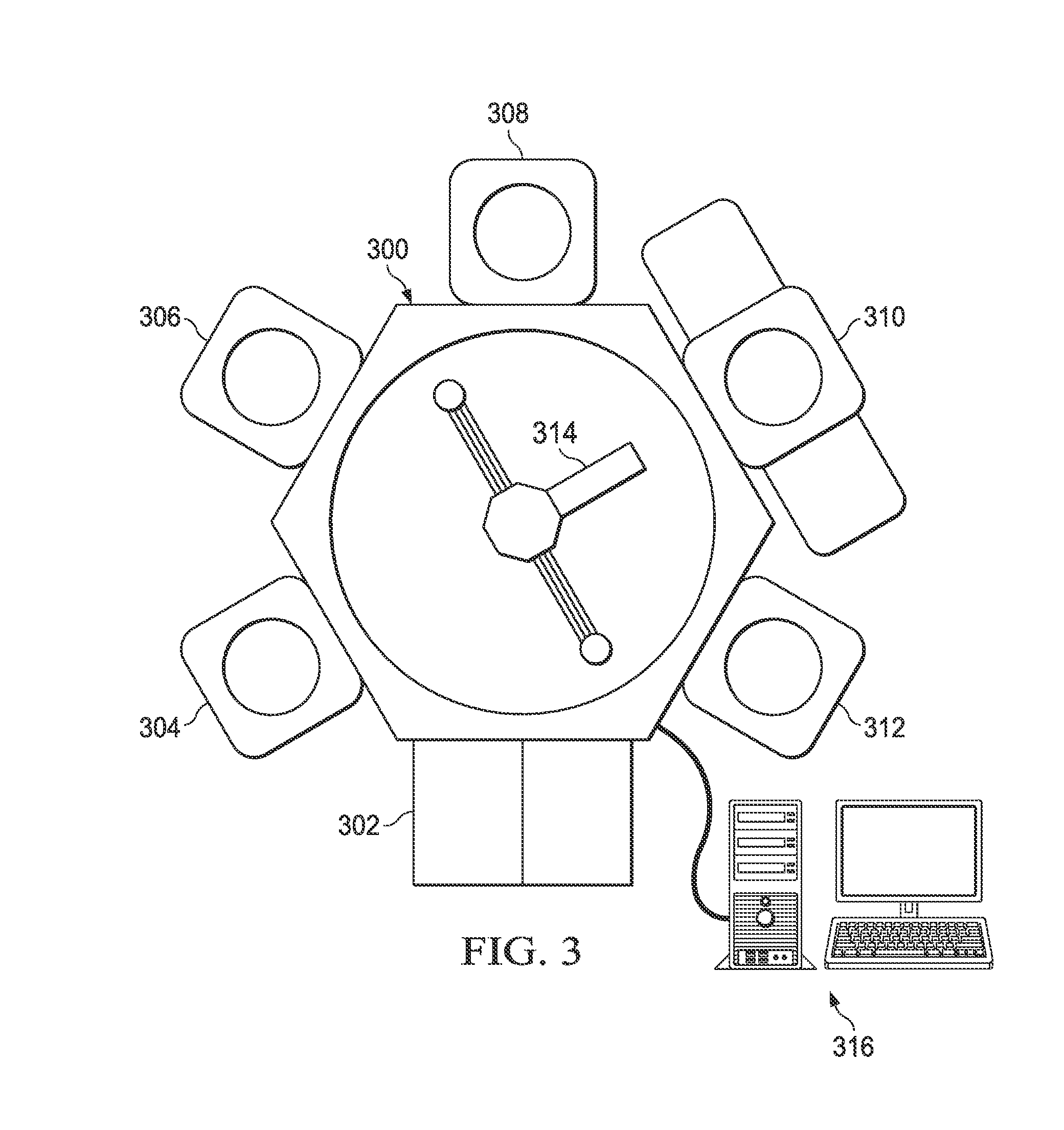

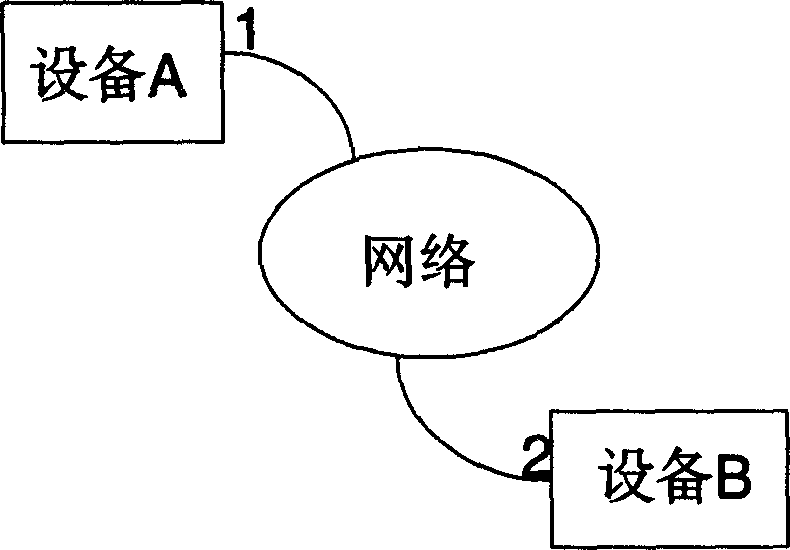

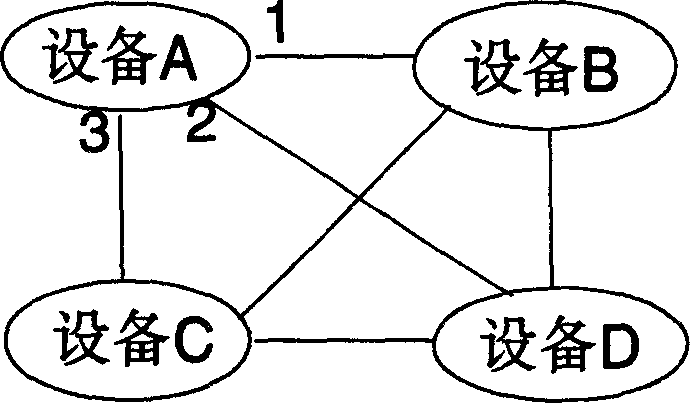

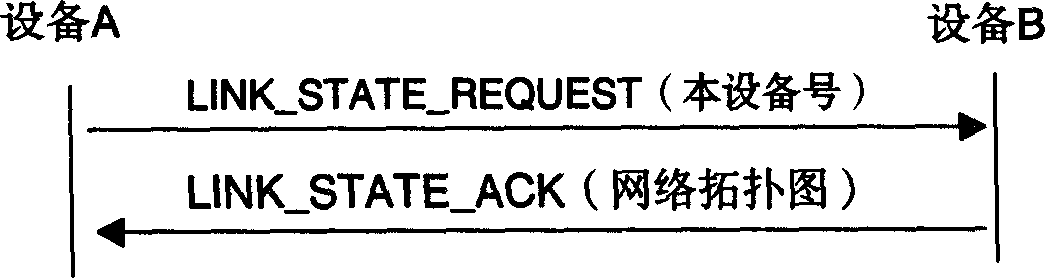

Method for implementing network interconnection management based on asynchronous transmission mode

InactiveCN1486020AEasy to manageLow costNetworks interconnectionAsynchronous Transfer ModeNetwork management

The invention refers to a kind of network interconnecting management method based on asynchronous transfer mode. The method includes: at first, sets up the interconnecting path of ATM net appliances;then, ATM net appliance carries on the setup of network topological diagram through the finding process of adjoining net appliance; at the same time, it also includes the update and maintenance of topological diagram; finally, carries on the ATM interconnection management according to the network topological diagram. The invention provides user of convenience to the ATM network management.

Owner:HUAWEI TECH CO LTD

Printed circuit board and fully-additive manufacturing method therefor

ActiveCN105934084ACause corrosionMeet the requirements of impedance characteristicsPrinted circuit aspectsElectrical connection printed elementsState of artDielectric plate

The invention discloses a printed circuit board. The printed circuit board mainly comprises multiple first structures and second structures which are overlapped in a lamination manner, wherein the first structures and the second structures are arranged at intervals; the first structures and the second structures are formed in a hot-pressing manner; the first structures mainly consist of circuit carriers; conductive convex blocks and circuit layers are embedded in the circuit carriers; the conductive convex blocks are electroplated on the circuit layers; the second structures mainly consist of insulating dielectric plates; conductive blocks are embedded in the insulating dielectric plates; and the circuit layers on the adjacent two first structures are connected through the conductive blocks. Compared with the prior art, the printed circuit board provide by the invention enables fine circuits to satisfy special impendence characteristic requirement; meanwhile, the prepared circuit is high in conductivity and low in cost; the first structures and the second structures are overlapped in a crossed manner in sequence, so that the printed circuit at any layer can be formed by one-time lamination; and therefore, the printed circuit board is high in production efficiency and capable of reducing the production time and the production cost.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Compliant printed circuit area array semiconductor device package

ActiveUS9054097B2Low production costImprove electrical performanceSemiconductor/solid-state device detailsSolid-state devicesRoad surfaceEngineering

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV +1

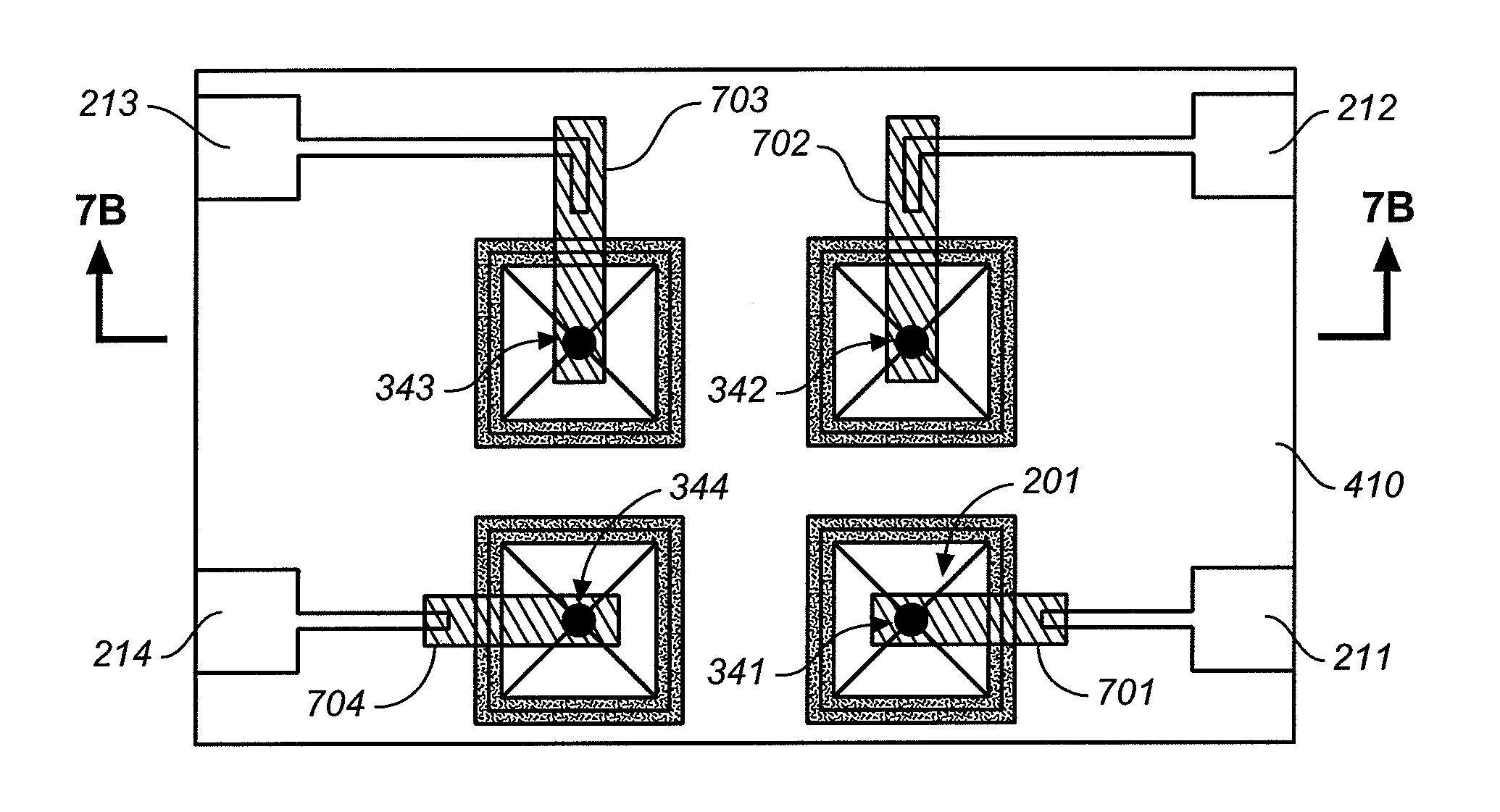

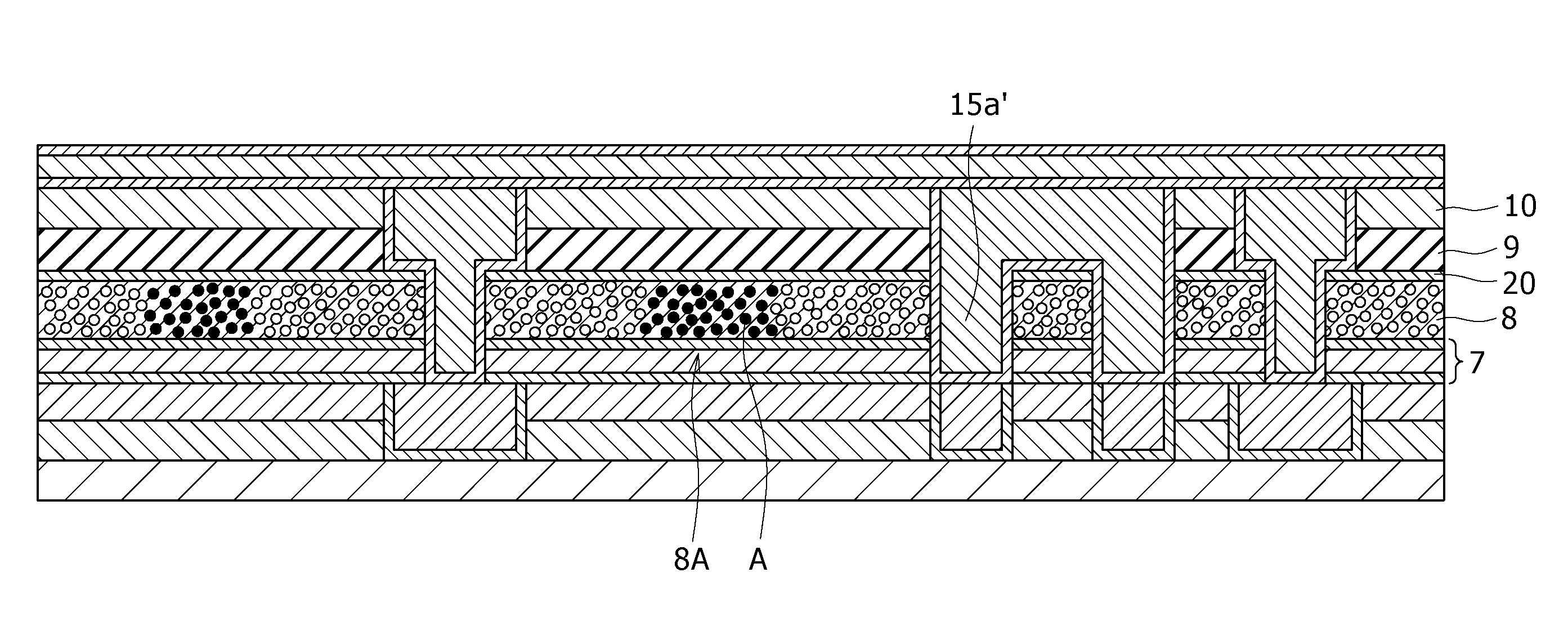

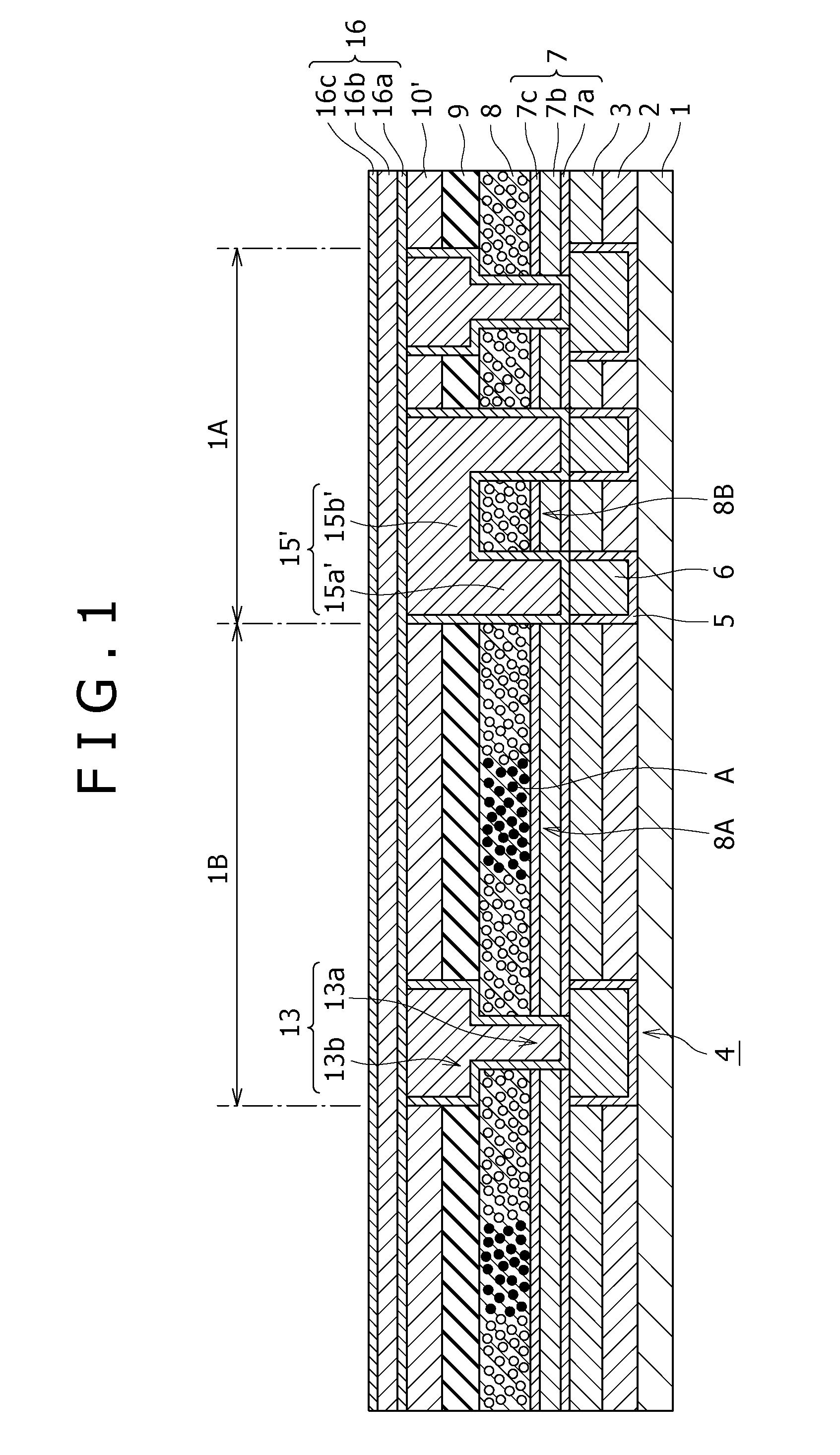

LED chip array module

ActiveUS7683475B2Improve interconnect reliabilityReliability of the electrical connections will be much improvedSemiconductor/solid-state device detailsSolid-state devicesWire bondingElectrical and Electronics engineering

The difficulties encountered in conventional LED multiple chip modules where wire bonding is used to connect the chips to electrodes can be overcome by using an interconnect to connect the chip to electrodes in a module where the interconnect is supported at points along its length other than at endpoints thereof, by a carrier either directly or indirectly. This improves reliability of the interconnect over conventional designs. Preferably, the contacts of the chips, and the electrodes are all within, or do not extend beyond, two parallel planes that are 400 microns apart for a compact design.

Owner:DICON FIBEROPTICS

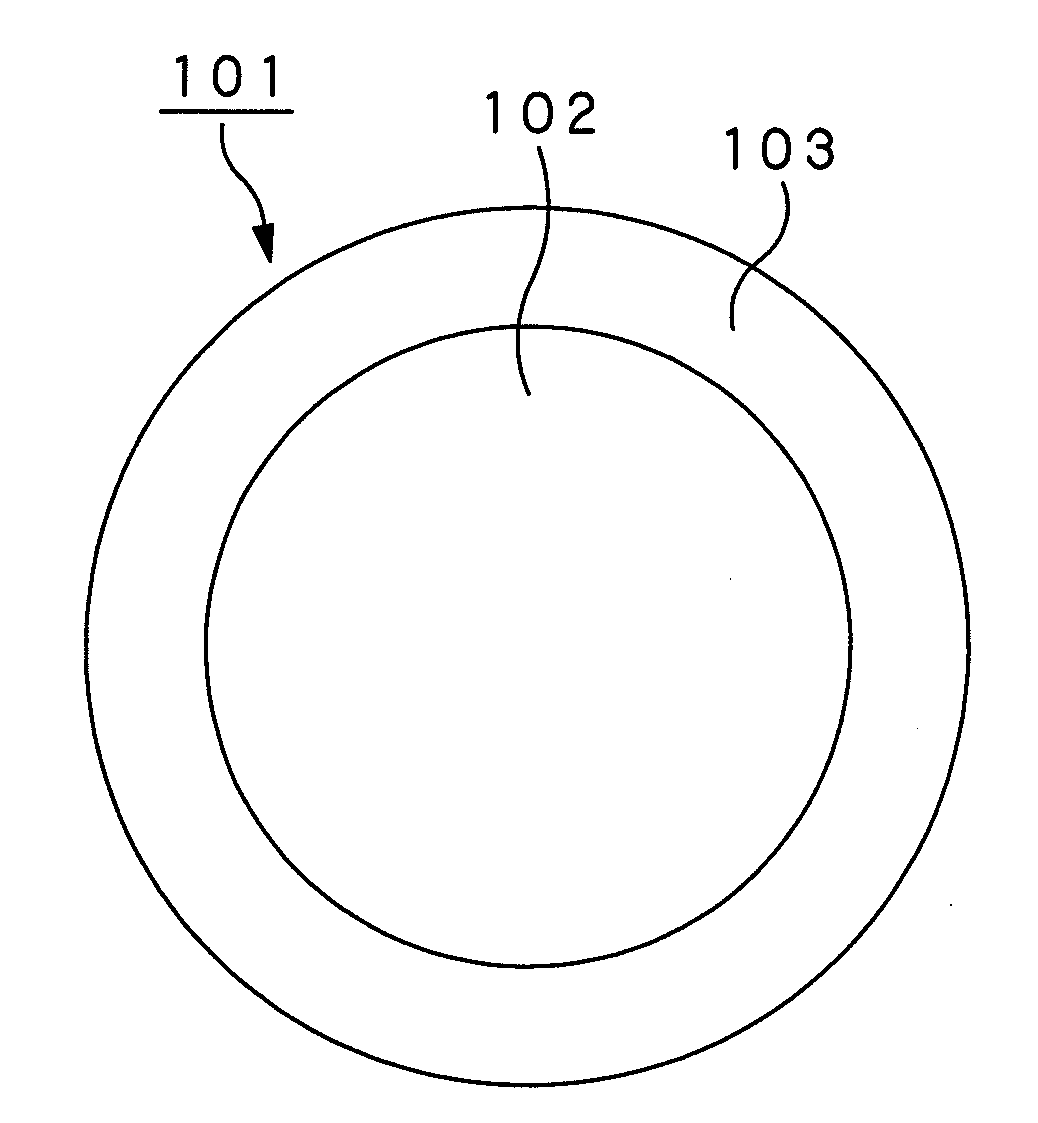

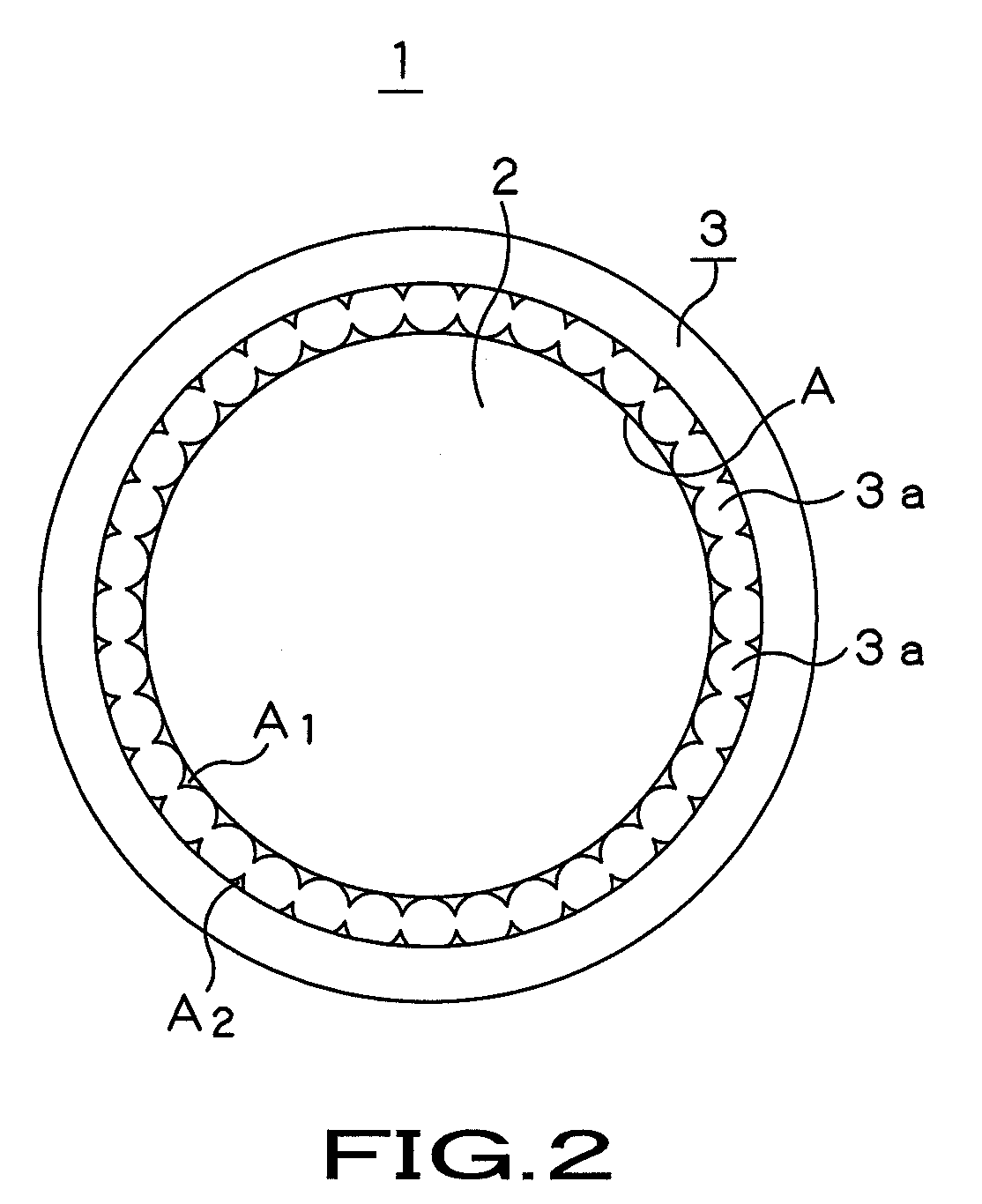

Conductive particle, anisotropic conductive interconnection material that uses the conductive particle, and method for producing the conductive particle

ActiveUS20100051878A1Improve interconnect reliabilityImprove reliabilityNon-insulated conductorsConductive materialInterconnectionOptoelectronics

There is disclosed a conductive particle used for an anisotropic conductive connection material for establishing conductive interconnection between e.g. a substrate and an electrical component. The conductive particle includes a base particle (2) exhibiting electrical conductivity at least on its surface and a continuous insulating resin film (3) formed by welding of fine particles (3a) of an insulating resin that composes the resin film. The surface of the base particle is coated with the continuous insulating resin film. There are formed voids at least between neighboring fine particles.

Owner:DEXERIALS CORP

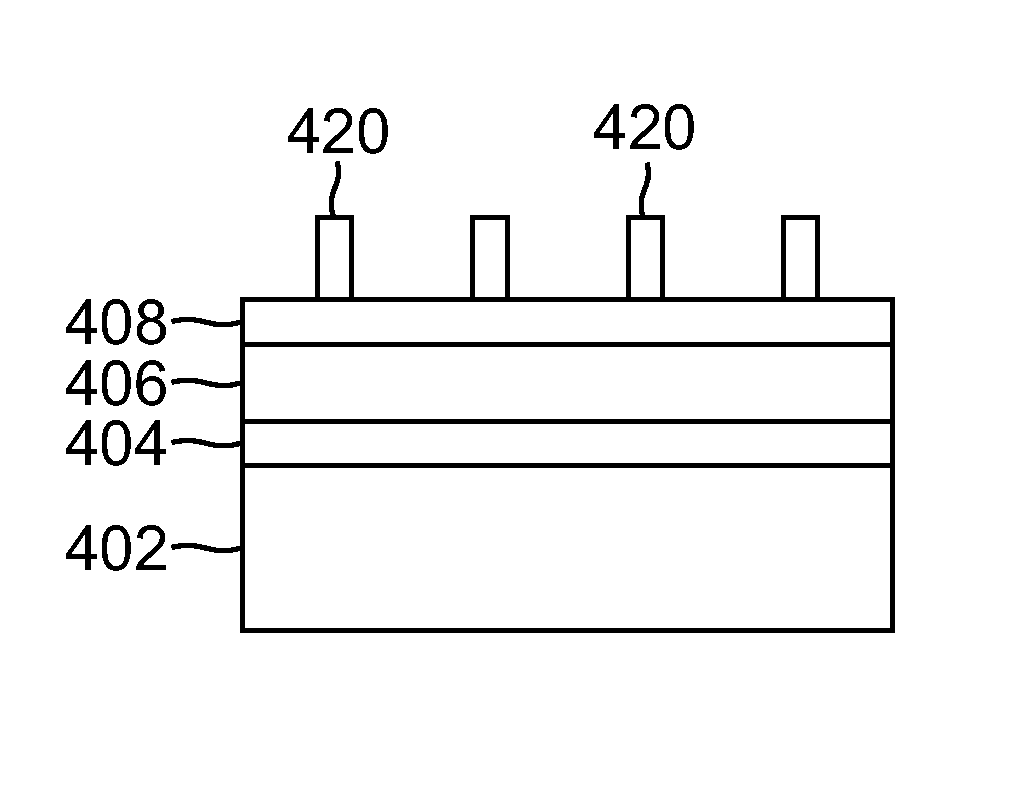

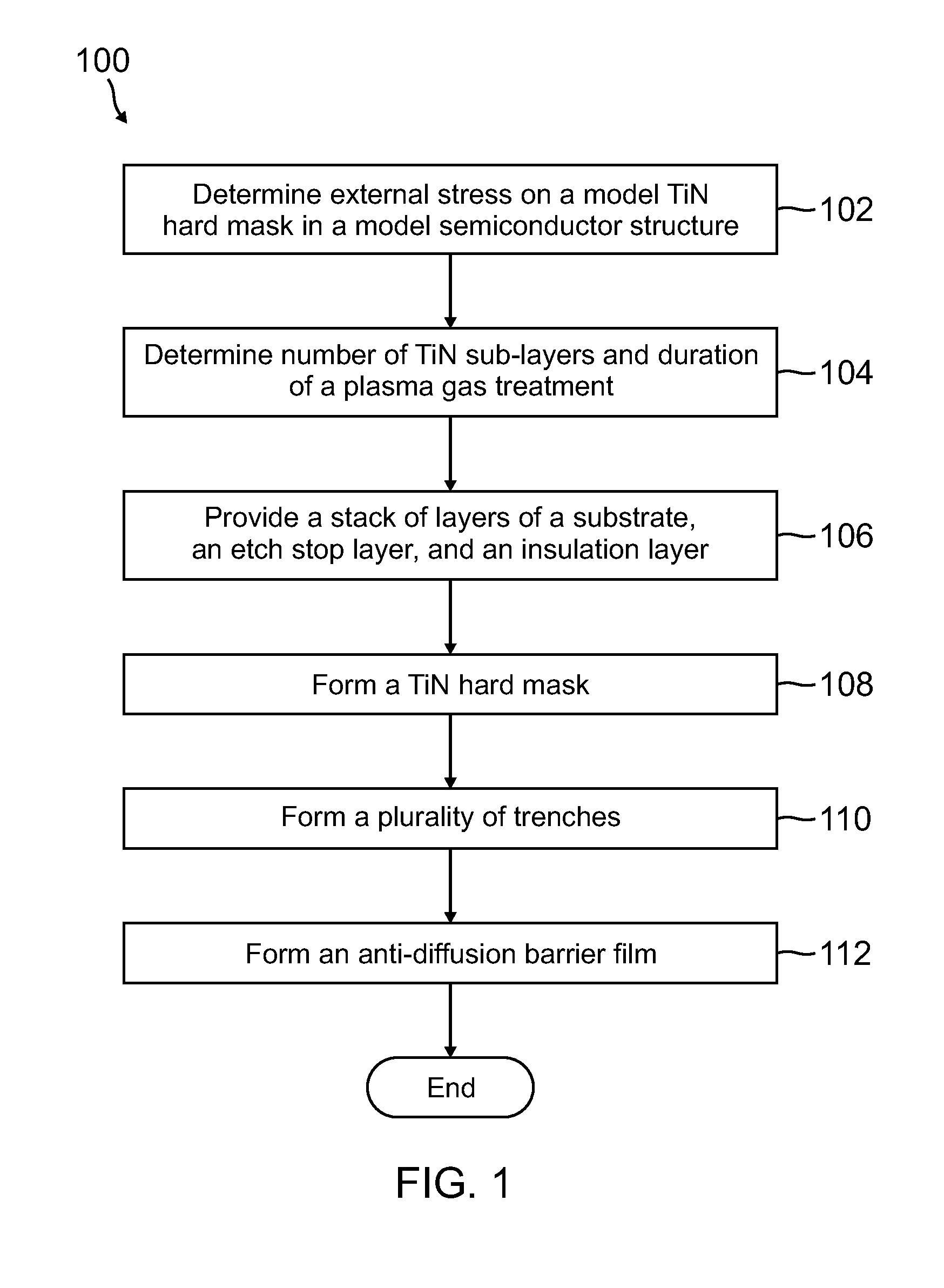

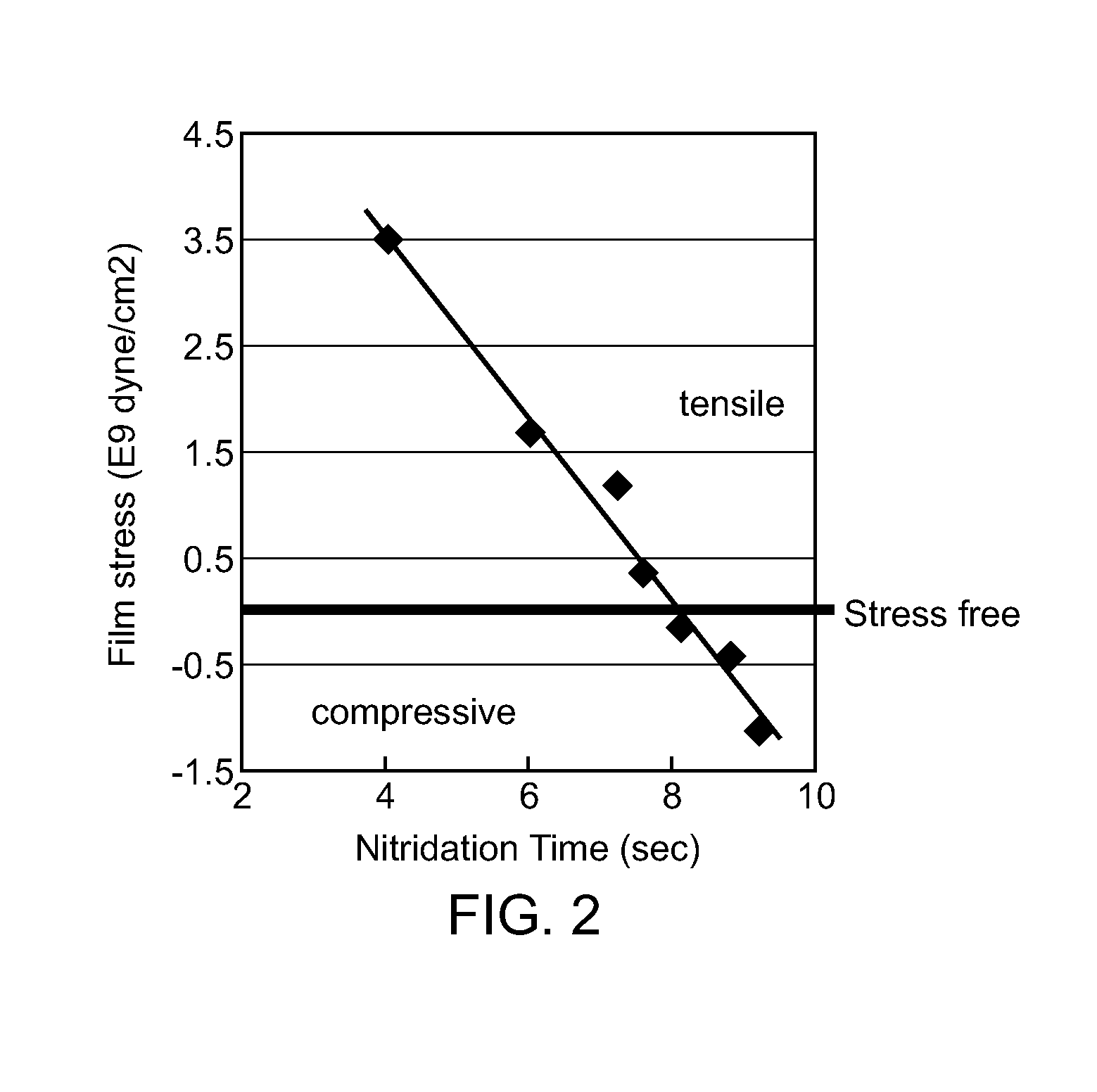

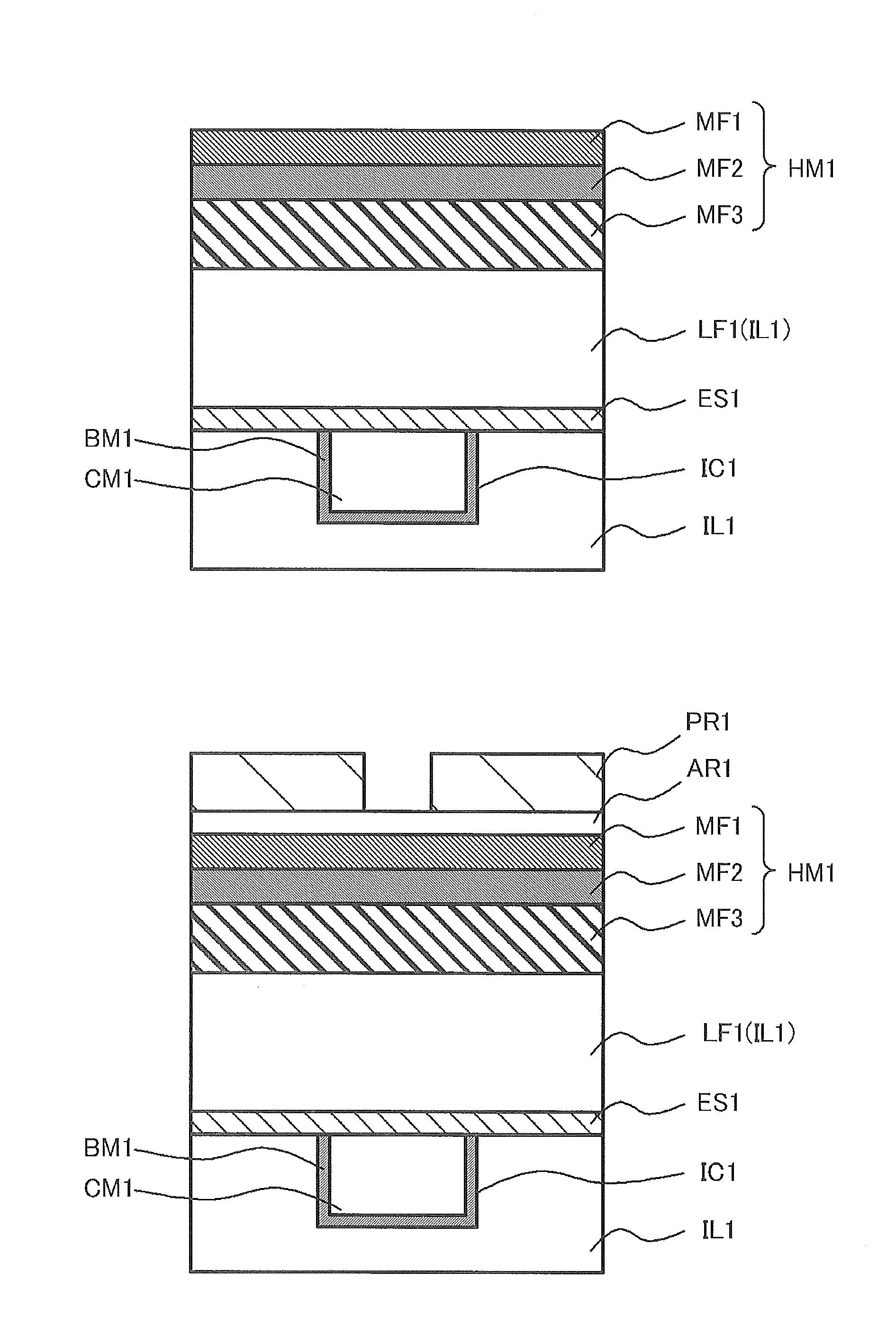

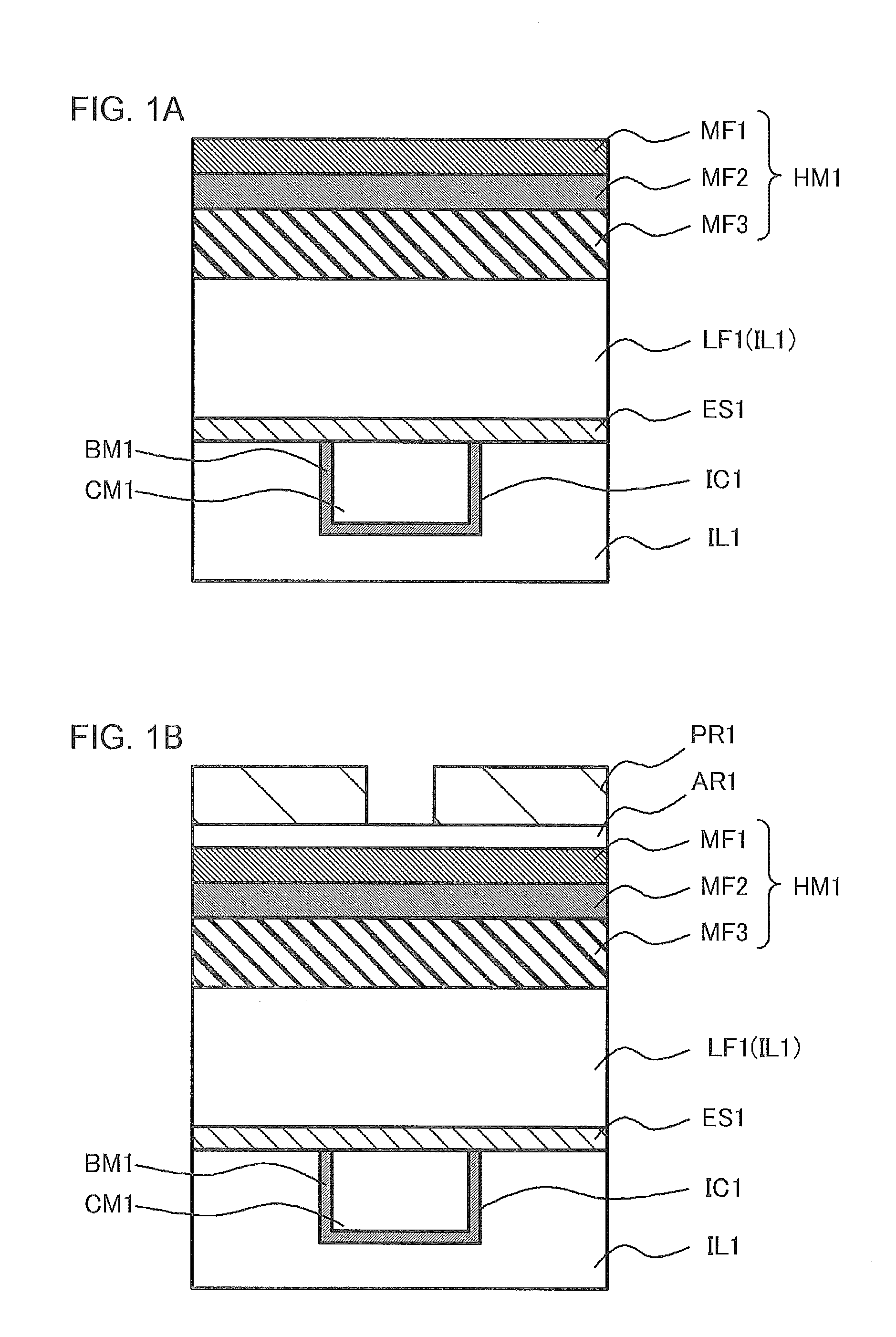

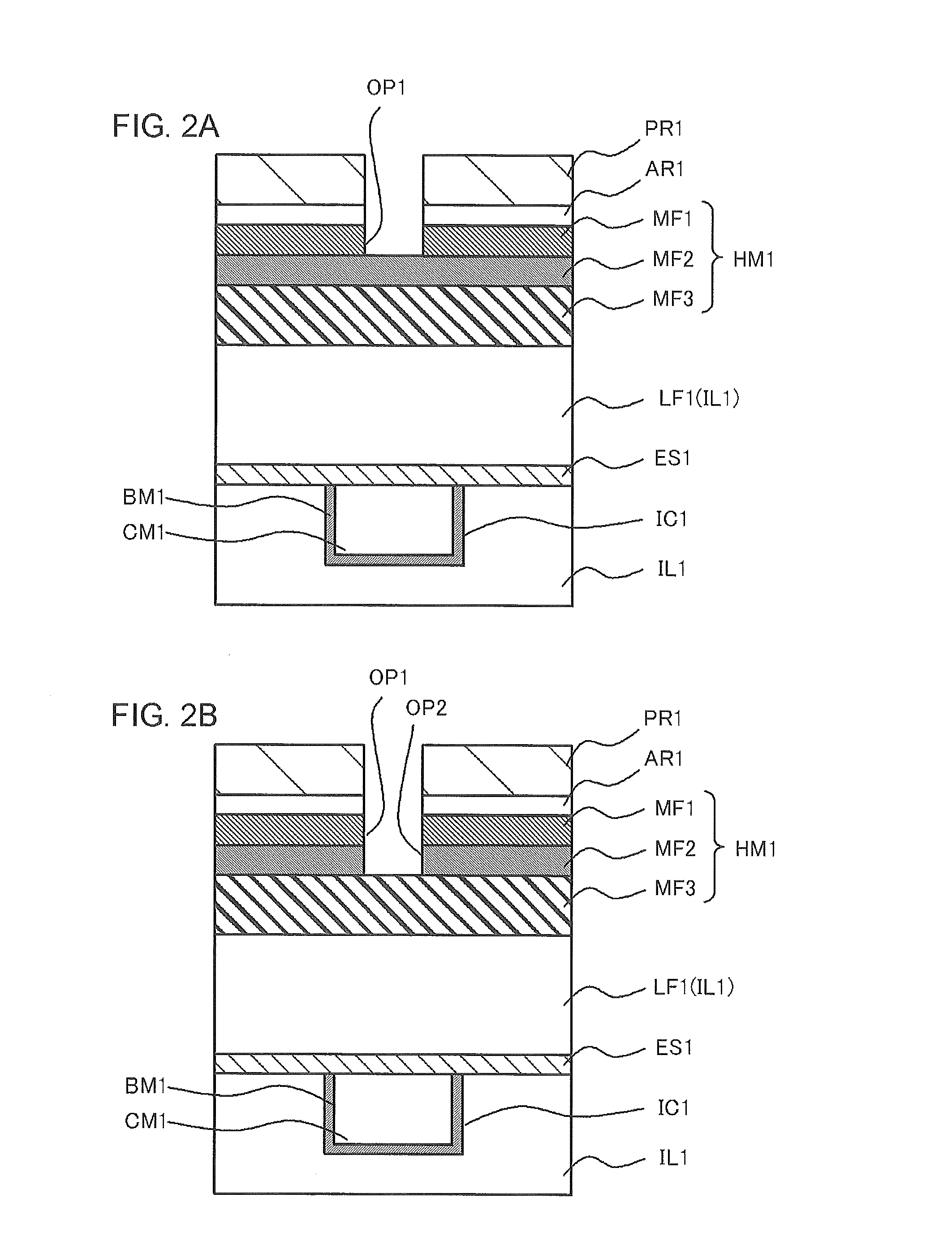

STRESS-CONTROLLED FORMATION OF TiN HARD MASK

ActiveUS20150187579A1Improve interconnect reliabilitySemiconductor/solid-state device manufacturingForming microstructural systemsLayered structureTin

A method to form a titanium nitride (TiN) hard mask in the Damascene process of forming interconnects during the fabrication of a semiconductor device, while the type and magnitude of stress carried by the TiN hard mask is controlled. The TiN hard mask is formed in a multi-layered structure where each sub-layer is formed successively by repeating a cycle of processes comprising TiN and chlorine PECVD deposition, and N2 / H2 plasma gas treatment. During its formation, the stress to be carried by the TiN hard mask is controlled by controlling the number of TiN sub-layers and the plasma gas treatment duration such that the stress may counter-balance predetermined external stress anticipated on a conventionally made TiN hard mask, which causes trench sidewall distortion, trench opening shrinkage, and gap filling problem.

Owner:TAIWAN SEMICON MFG CO LTD

Area array semiconductor device package interconnect structure with optional package-to-package or flexible circuit to package connection

ActiveUS9613841B2Improve interconnect reliabilityHigh-frequency performancePrinted circuit assemblingSemiconductor/solid-state device detailsFlexible circuitsIc devices

Owner:HSIO TECH

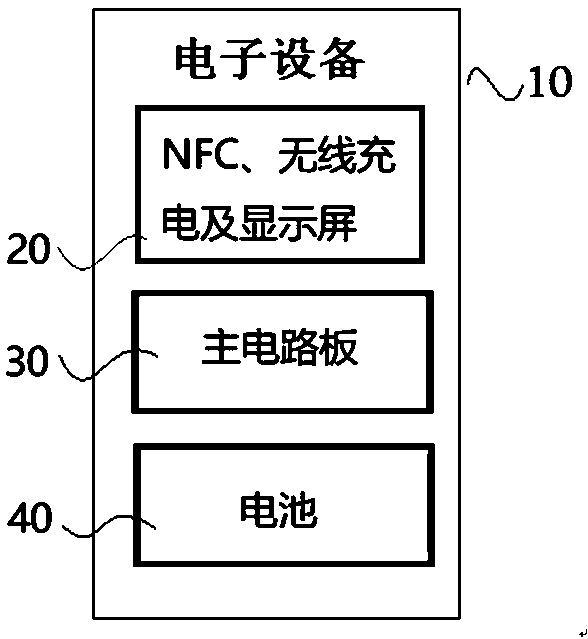

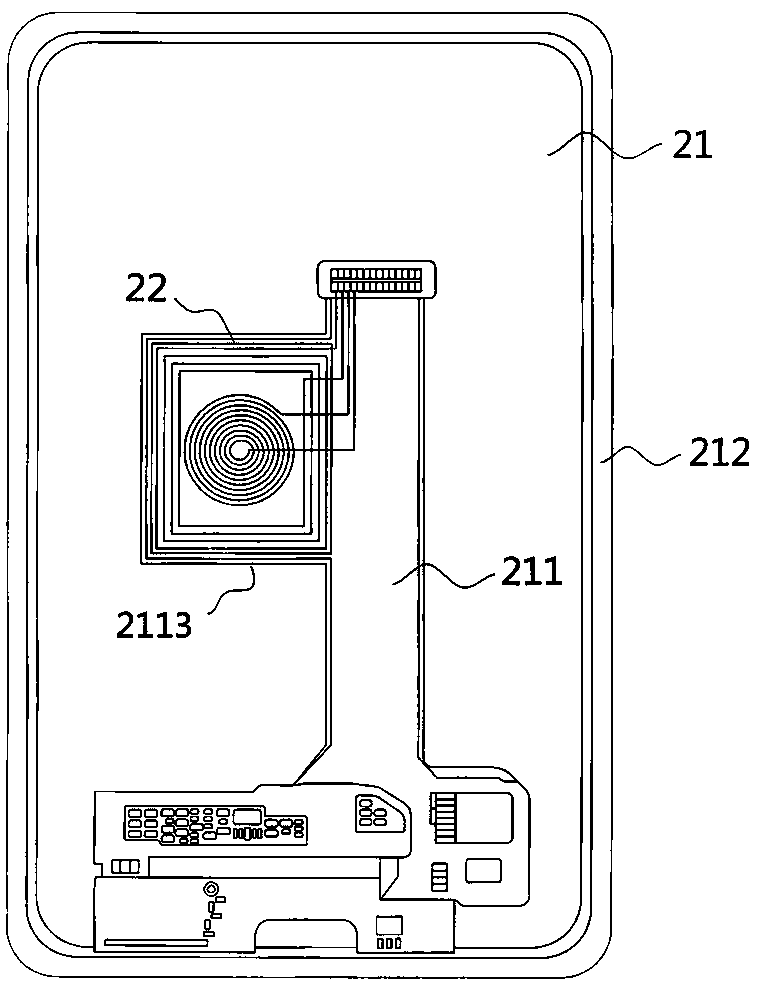

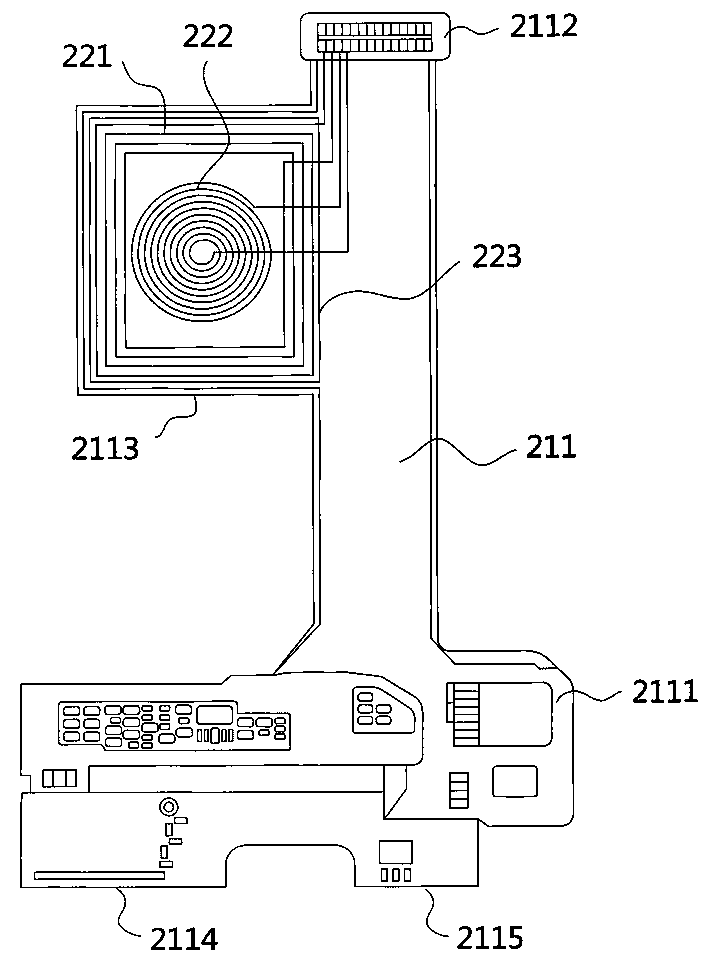

Electronic device integrating near-field communication NFC antenna, wireless charging and display screen

ActiveCN110336114ALow costReduce the impactLoop antennas with ferromagnetic coreParticular array feeding systemsFlexible circuitsEngineering

The invention discloses an electronic device integrating a near-field communication NFC antenna, wireless charging and a display screen. The electronic device comprises a near-field communication NFCantenna and / or wireless charging antenna and display screen integrated assembly, a main printed circuit board PCB and a battery. The near-field communication NFC antenna and / or wireless charging antenna and display screen integrated assembly comprises a display screen assembly and a near-field communication NFC antenna and / or wireless charging antenna assembly. The display screen assembly comprises a flexible printed circuit board FPC and a display module. The flexible printed circuit board FPC comprises an area for providing a driving IC or a touch control IC, a connector for interconnectingwith the main printed circuit board PCB and a protruding portion area. The near-field communication NFC antenna and / or wireless charging antenna assembly is arranged on the protruding portion area ofthe flexible printed circuit board FPC. The electronic device can effectively utilize the space of the device, improves integration level, reduces metal spring assemblies, reduces assembly link and saves cost.

Owner:天通瑞宏科技有限公司

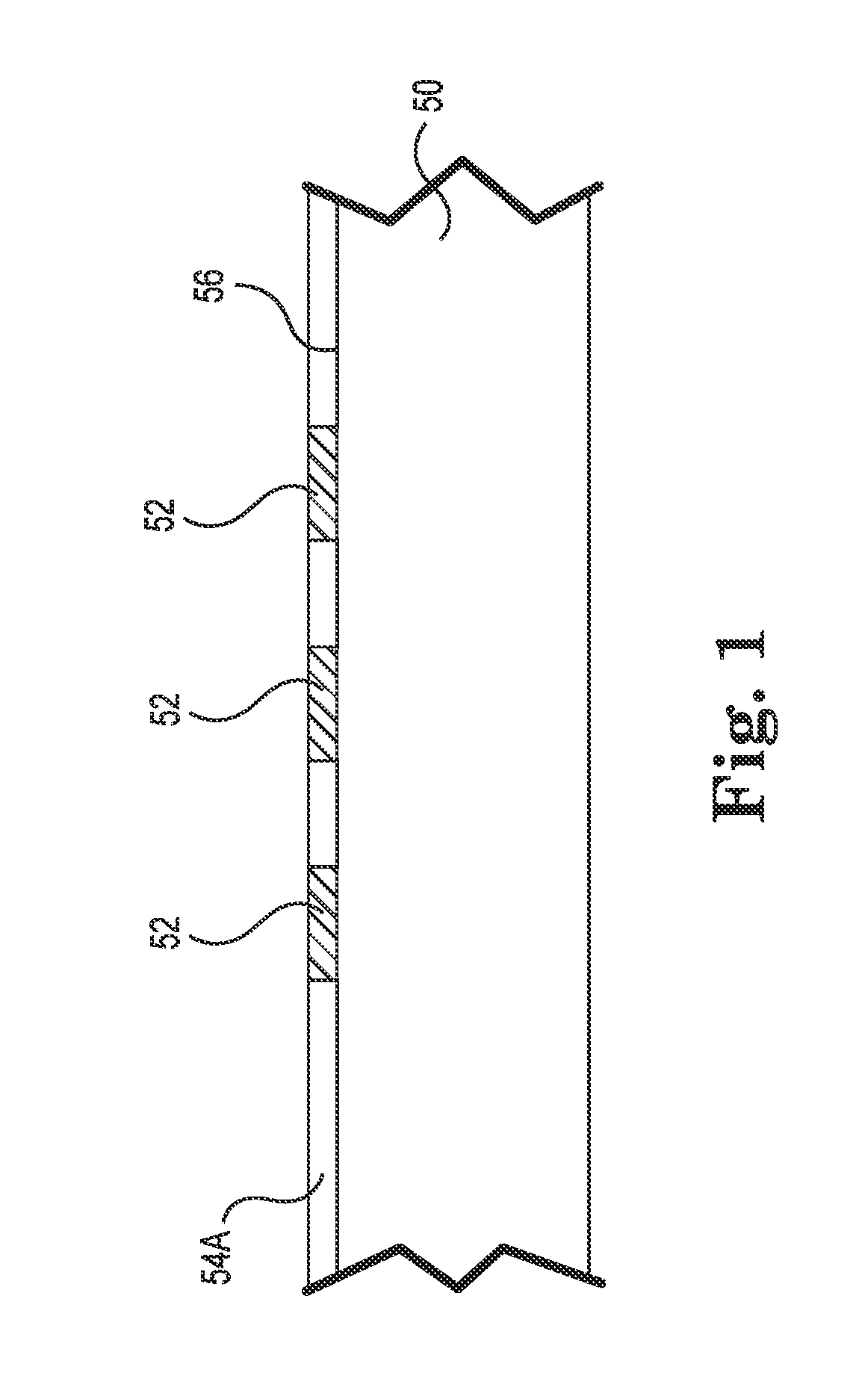

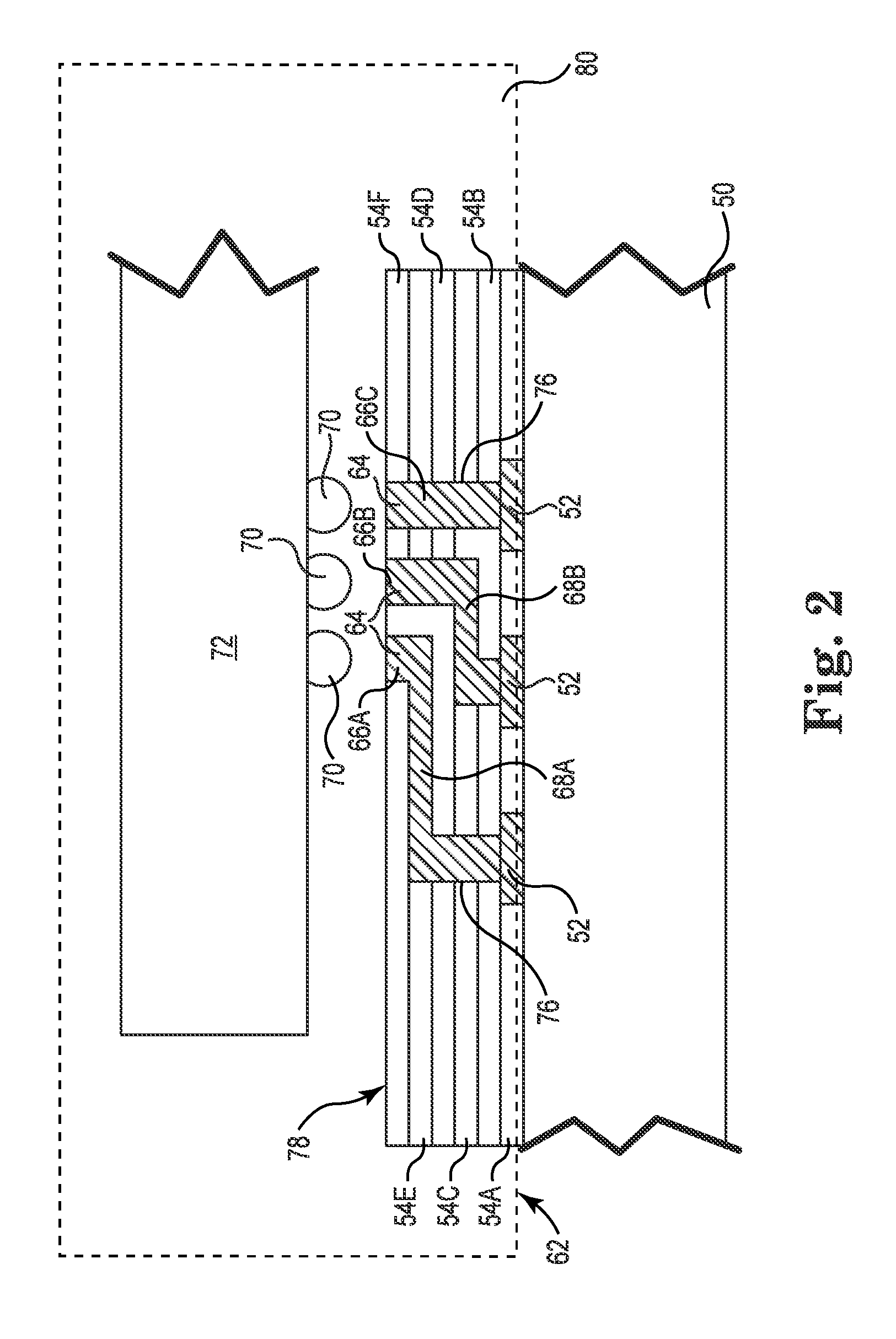

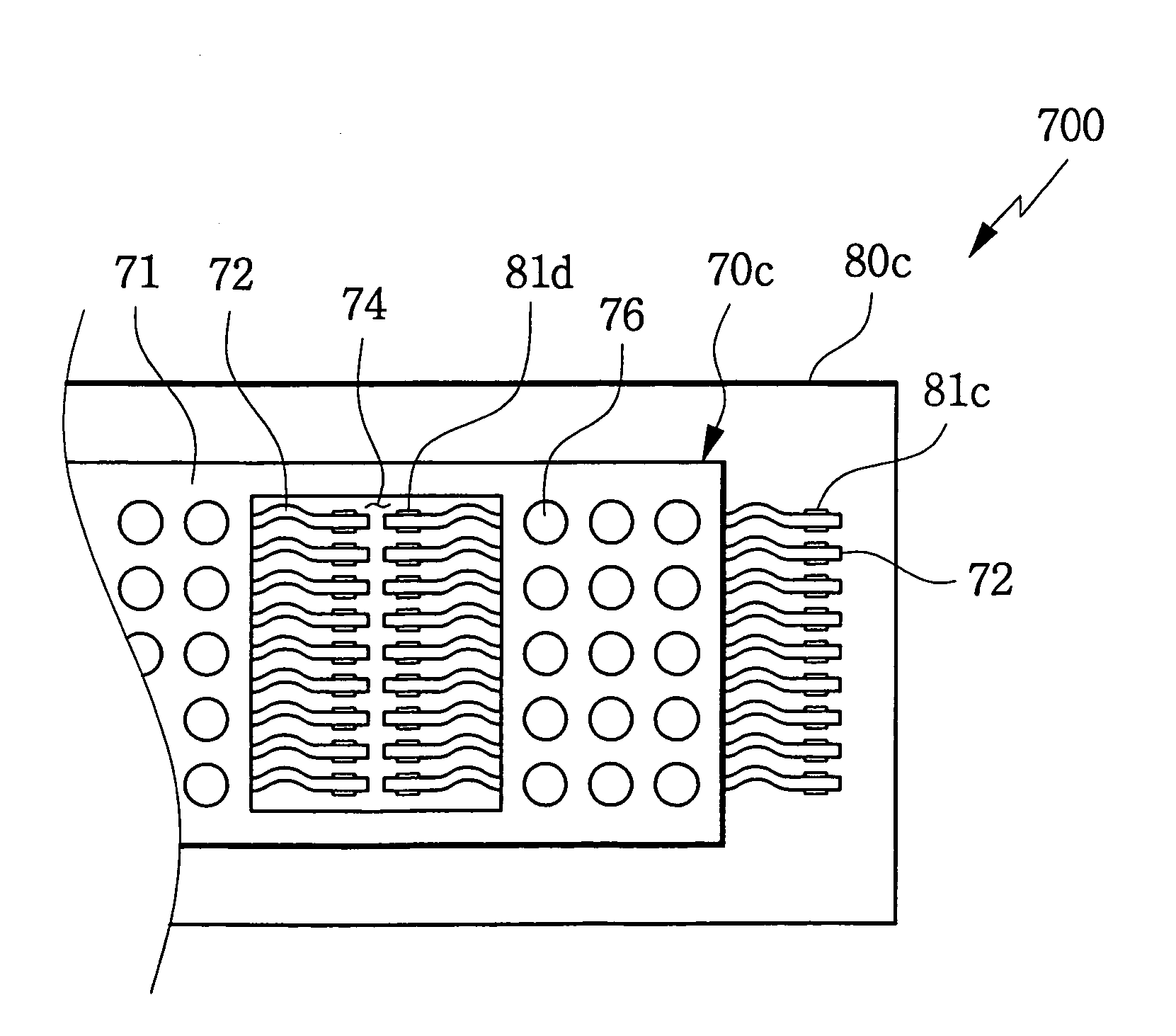

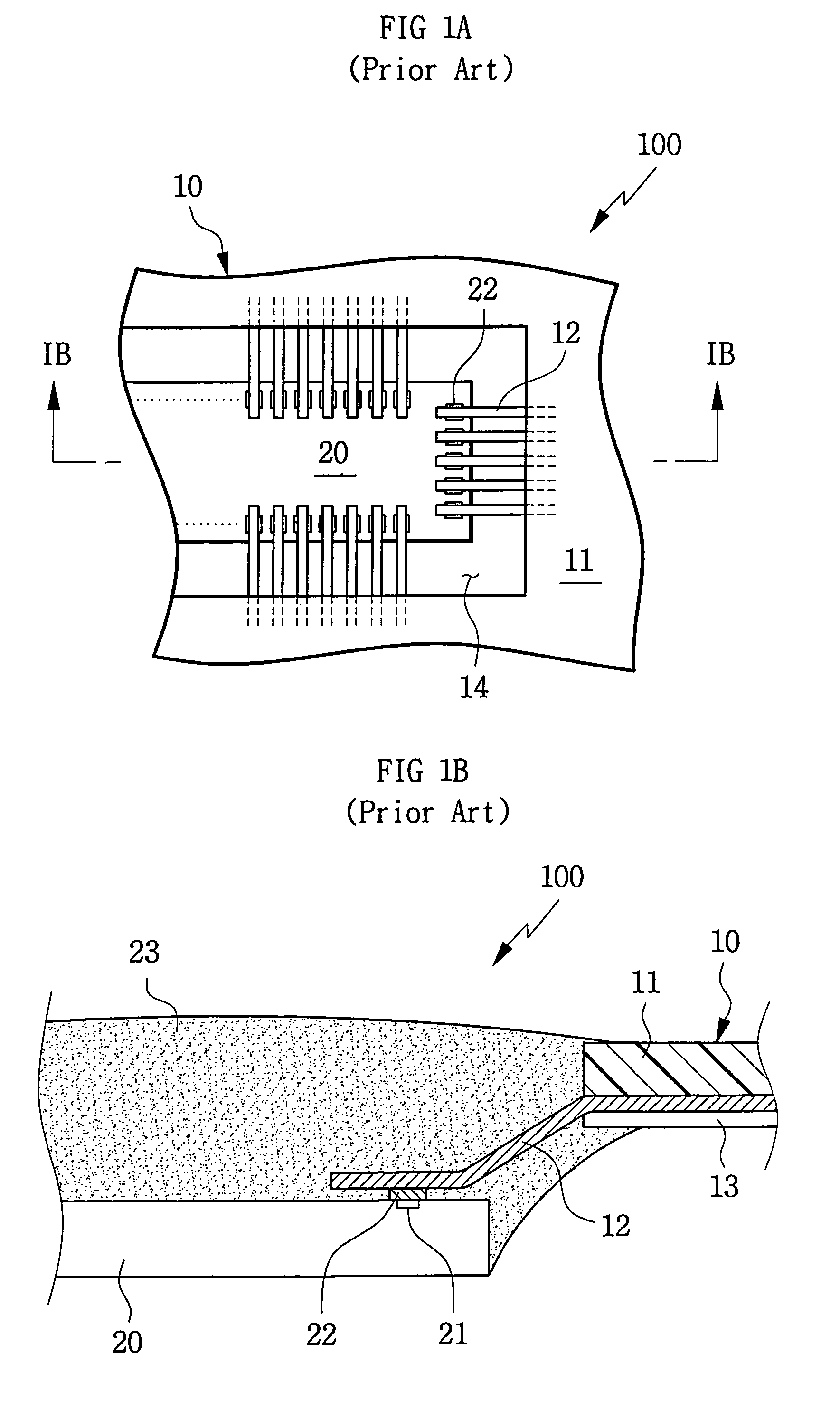

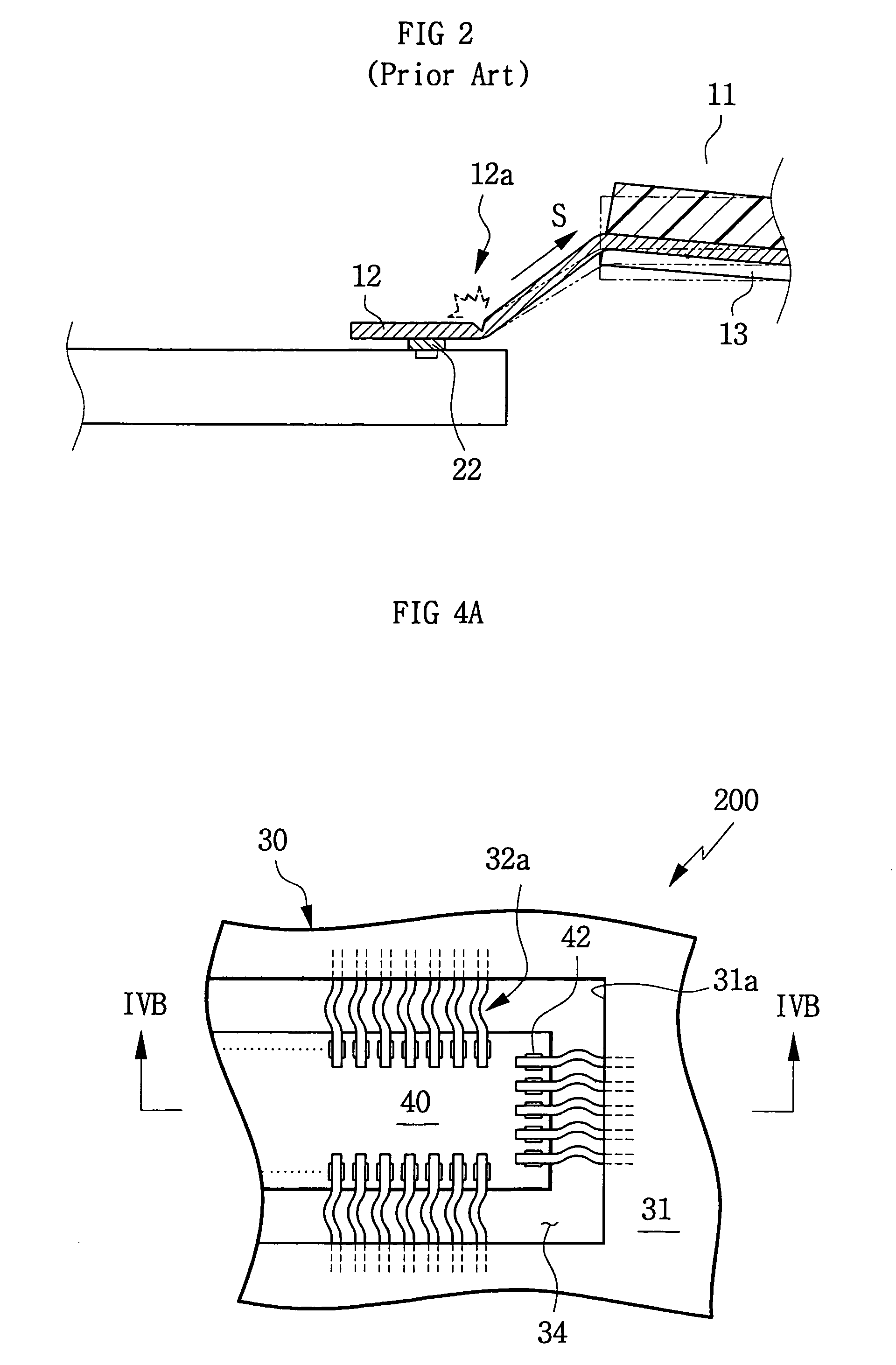

Tape circuit substrate having wavy beam leads and semiconductor chip package using the same

InactiveUS7247936B2Avoid crackingImprove interconnect reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A semiconductor chip package includes an IC chip and a tape circuit substrate. The tape circuit substrate has a base film and a plurality of beam leads formed on the base film. One end portion of each beam lead extends from the base film, and the extended portion has a widthwise wavy portion. The widthwise wavy portion may be, for example, semicircular shaped, S-shaped or zig-zag shaped. The IC chip has chip pads formed on a top surface thereof.

Owner:SAMSUNG ELECTRONICS CO LTD

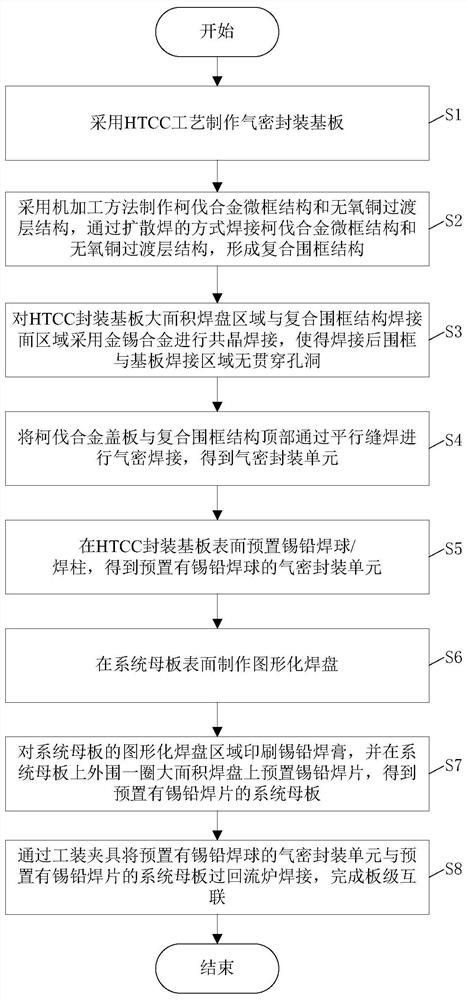

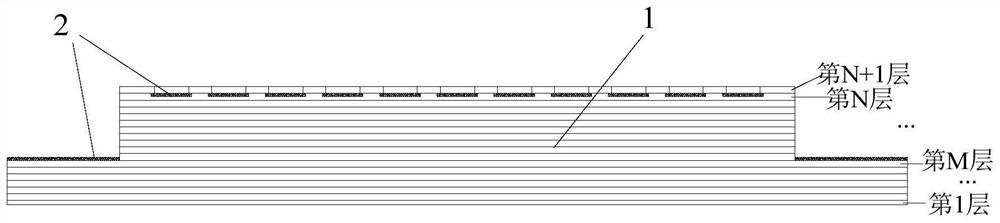

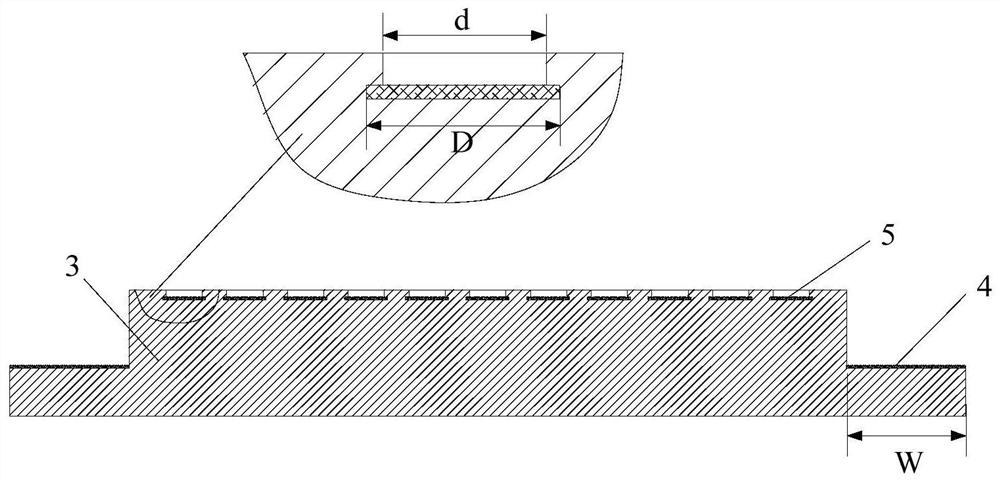

Local large-area welding plate-level interconnection integration method for airtight packaging unit

ActiveCN111933577AImprove pad tensile and shear strengthLess shedding or tearingSemiconductor/solid-state device manufacturingSolder ballStructural engineering

The invention discloses a local large-area welding plate-level interconnection integration method for an airtight packaging unit, in particular to a local large-area welding plate level interconnection integration method for a bonding pad enhanced airtight packaging unit. Manufacturing of an enhanced bonding pad on a substrate is completed through an HTCC process; airtight packaging is realized through multi-temperature gradient welding of the packaging substrate, the composite enclosure frame and the cover plate; high-reliability plate-level interconnection of the airtight packaging unit andthe system mother board is completed through a tin-lead solder ball / solder column and composite enclosure frame structure combined welding method.

Owner:SOUTHWEST CHINA RES INST OF ELECTRONICS EQUIP

Copper interconnection forming method

ActiveCN102956541AImprove interconnect reliabilityReduce processing costsSemiconductor/solid-state device manufacturingInterconnectionDiffusion barrier

The invention relates to a copper interconnection forming method. The method includes: forming low dielectric material layers on a semiconductor substrate; etching a through hole and a groove on the low dielectric material layers respectively; forming a diffusion barrier layer in the through and the groove; forming a Cu layer and a Cu alloy layer on the diffusion barrier layer; and reflowing and annealing the Cu alloy layer to enable alloy elements in the Cu alloy layer to be diffused into the lower Cu layer, so that electromigration reliability of copper interconnection is improved effectively.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method of manufacturing semiconductor device including forming trench pattern in a mask film

InactiveUS9123537B2Improve interconnect reliabilityDamage suppressionSemiconductor/solid-state device manufacturingMetallic materialsAmorphous silicon

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and method for manufacturing semiconductor device

InactiveUS7602061B2Low mechanical strengthHigh densitySemiconductor/solid-state device detailsSolid-state devicesDecompositionSemiconductor

Disclosed herein is a semiconductor device including: an insulating film configured to be provided on a substrate and be porosified through decomposition and removal of a pore-forming material; a covering insulating film configured to be provided on the insulating film; and conductive layer patterns configured to be provided in the covering insulating film and the insulating film and reach the substrate, wherein the insulating film includes a non-porous region in which the pore-forming material remains.

Owner:SONY CORP