Method for Fabricating Array-Molded Package-on-Package

a technology of array-molded packages and integrated circuits, applied in semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of increasing product warpage problems, reducing product thickness, and no longer being acceptable in recent applications, so as to improve testability and thus yield, and reduce cost and simplify the effect of approach

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

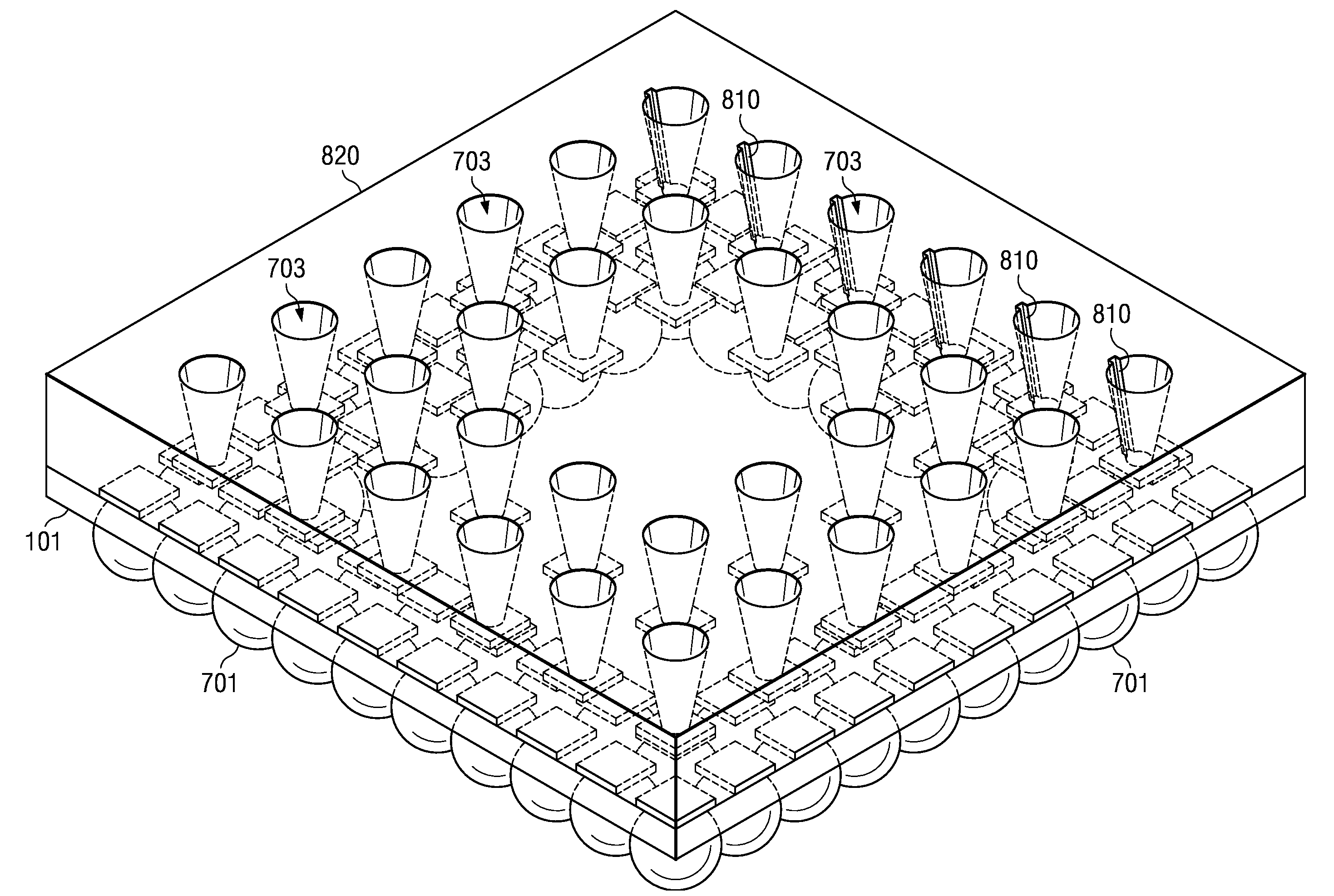

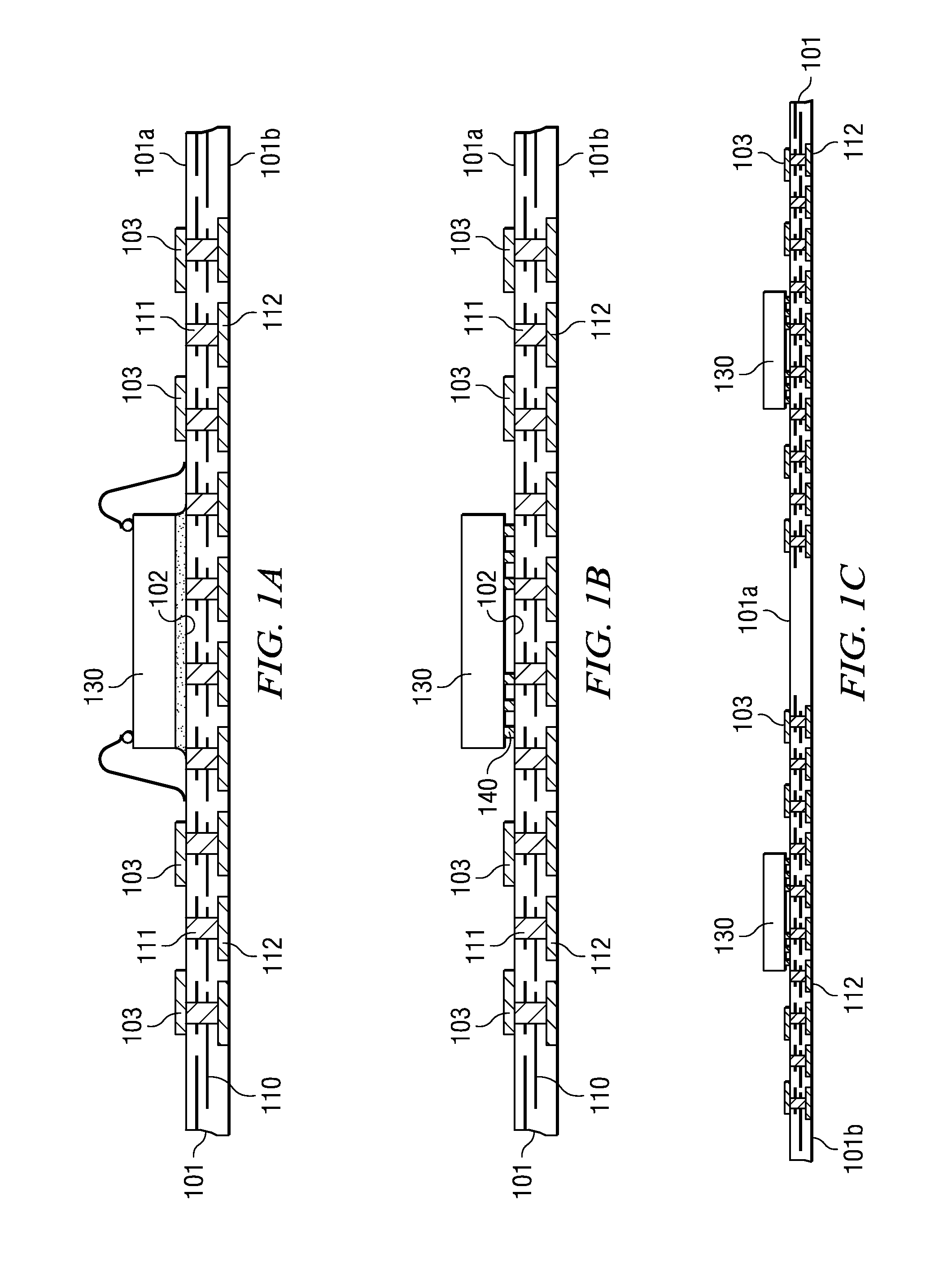

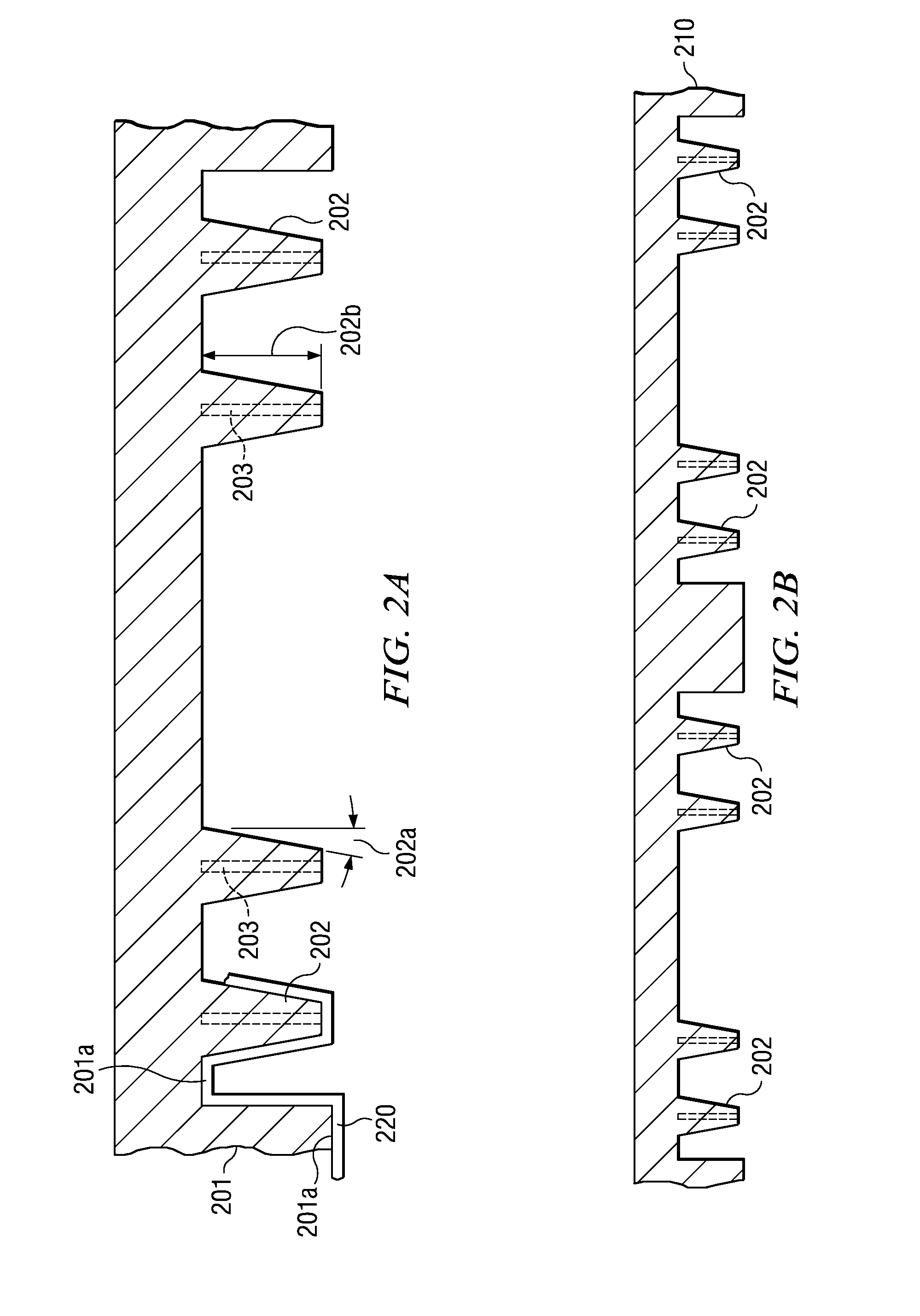

[0033]FIGS. 1A through 7 illustrate schematically the steps of one embodiment of the present invention, a method for array-molding semiconductor devices. The steps shown in FIGS. 1A and 1B show the assembly of a semiconductor chip on a substrate by wire bonding (FIG. 1A) and by flip-chip technology (FIG. 1B); FIG. 1C exemplifies a portion of an array of chips assembled by flip-chip. A sheet-like substrate 101 with insulating core (for example, plastic, glass-fiber reinforced, ceramic) is integral with two or more patterned layers of conductive lines and conductive vias 111 (preferably copper) and contact pads in pad locations. Lines 110 do not reach beyond the boundaries of substrate 101. Substrate 101 has a first surface 101a and a second surface 101b, and a preferred thickness range from 0.2 to 0.5 mm. The first surface 101a includes chip assembly sites 102 and contact pads 103 in pad locations. The metal of the contact pads is preferably copper with a solderable surface (for exam...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More