Patents

Literature

473 results about "Package on package" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

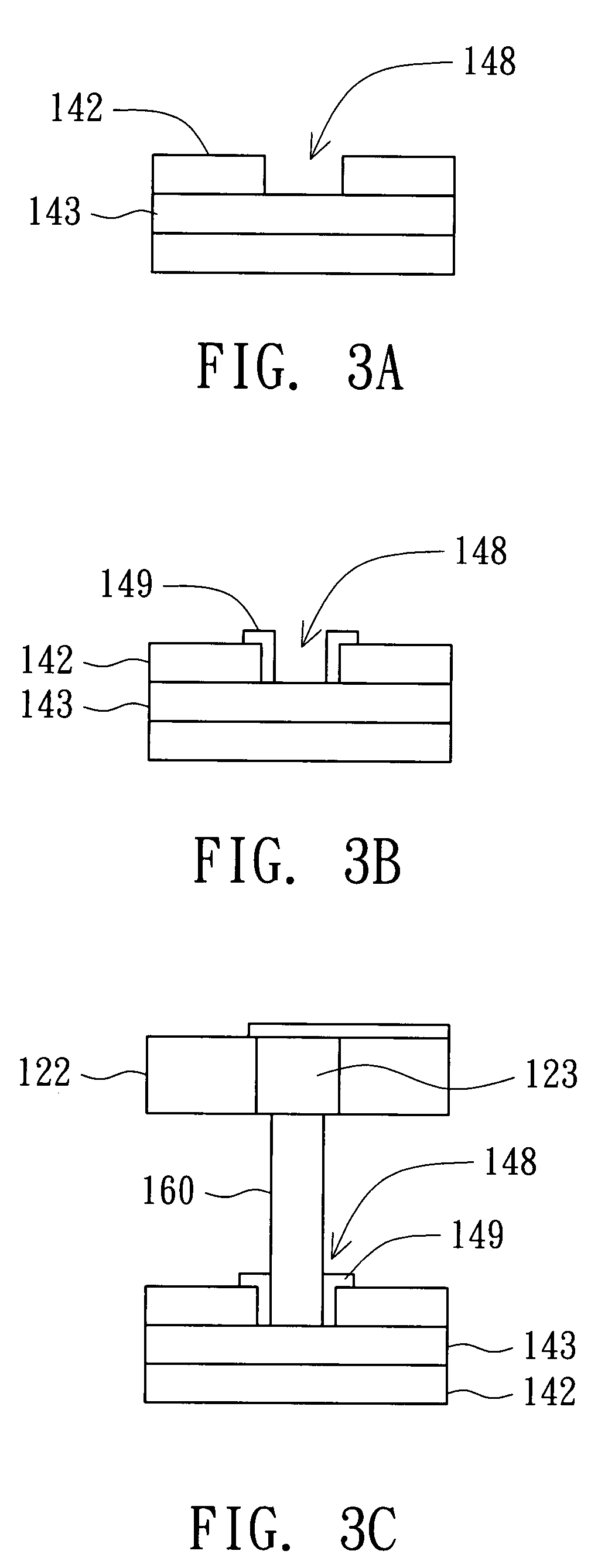

Package on package (PoP) is an integrated circuit packaging method to combine vertically discrete logic and memory ball grid array (BGA) packages. Two or more packages are installed atop each other, i.e. stacked, with a standard interface to route signals between them. This allows higher component density in devices, such as mobile phones, personal digital assistants (PDA), and digital cameras.

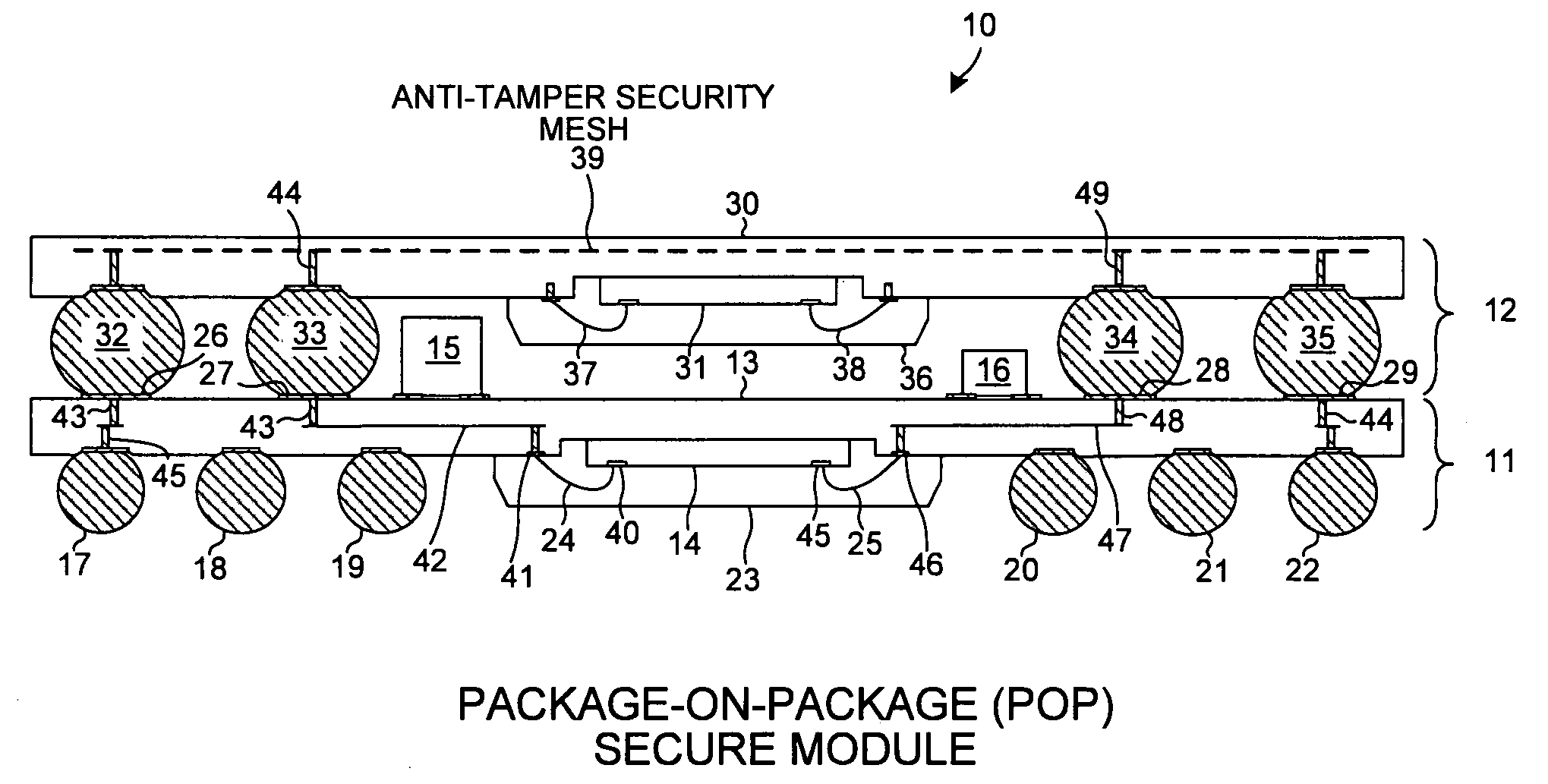

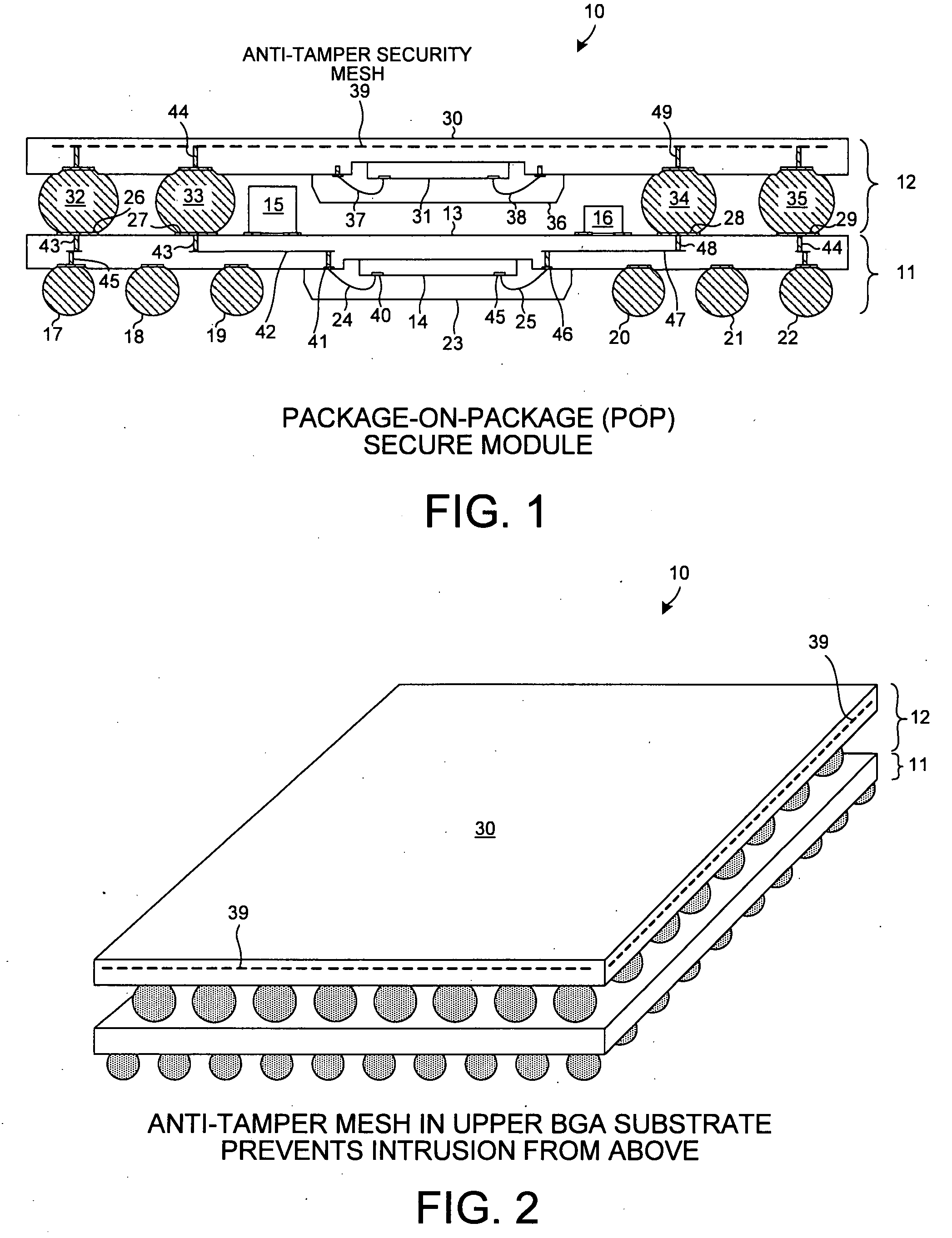

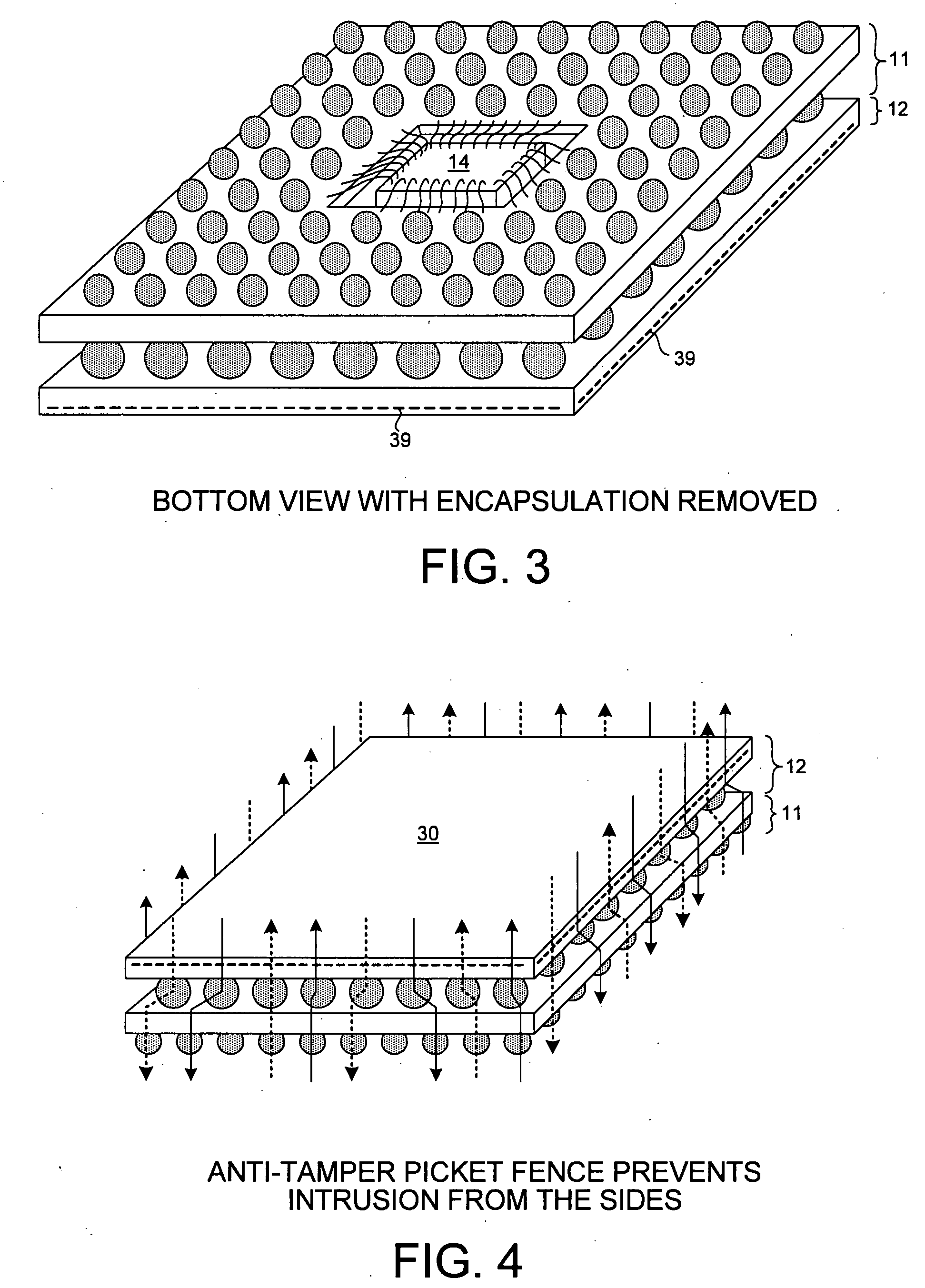

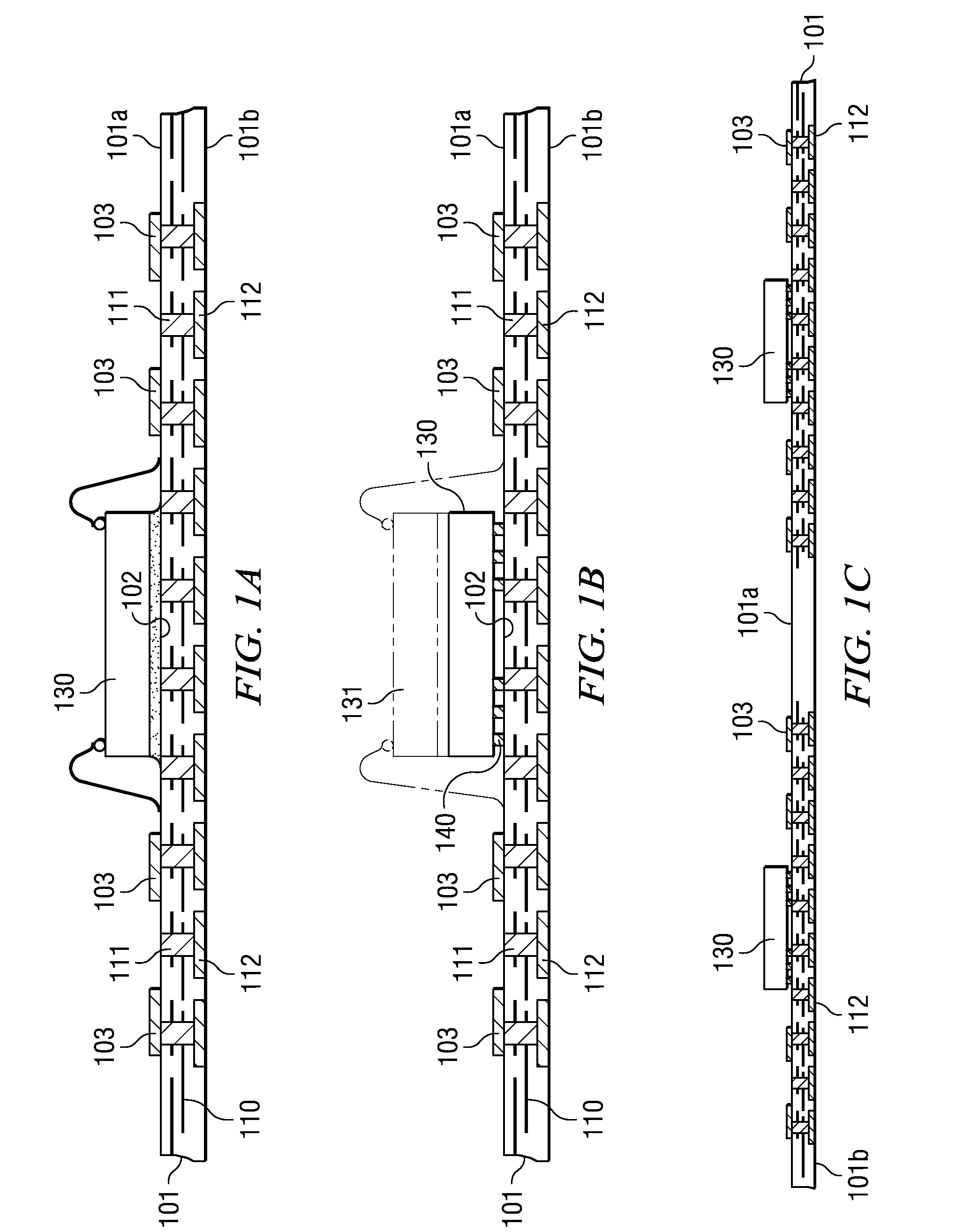

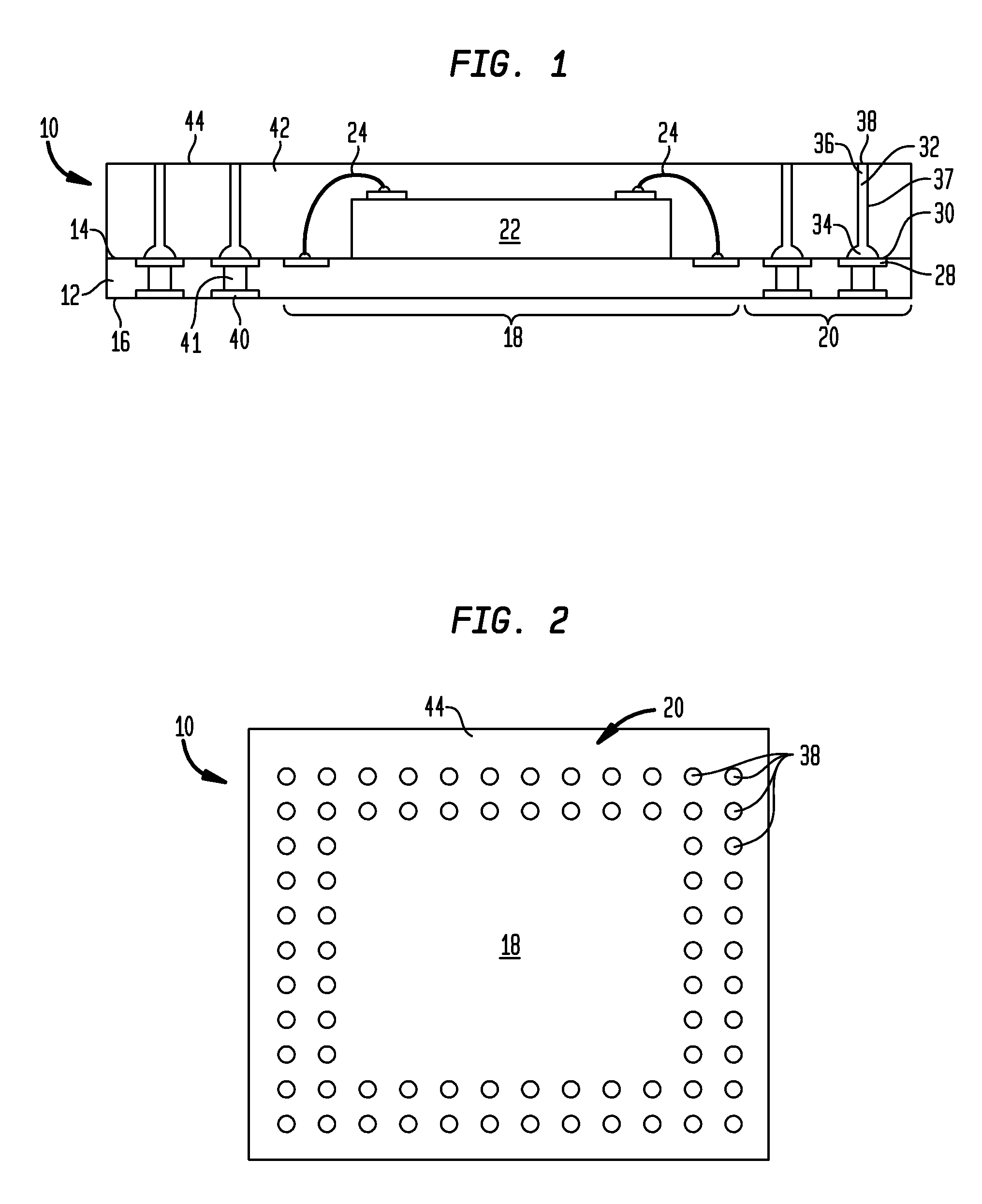

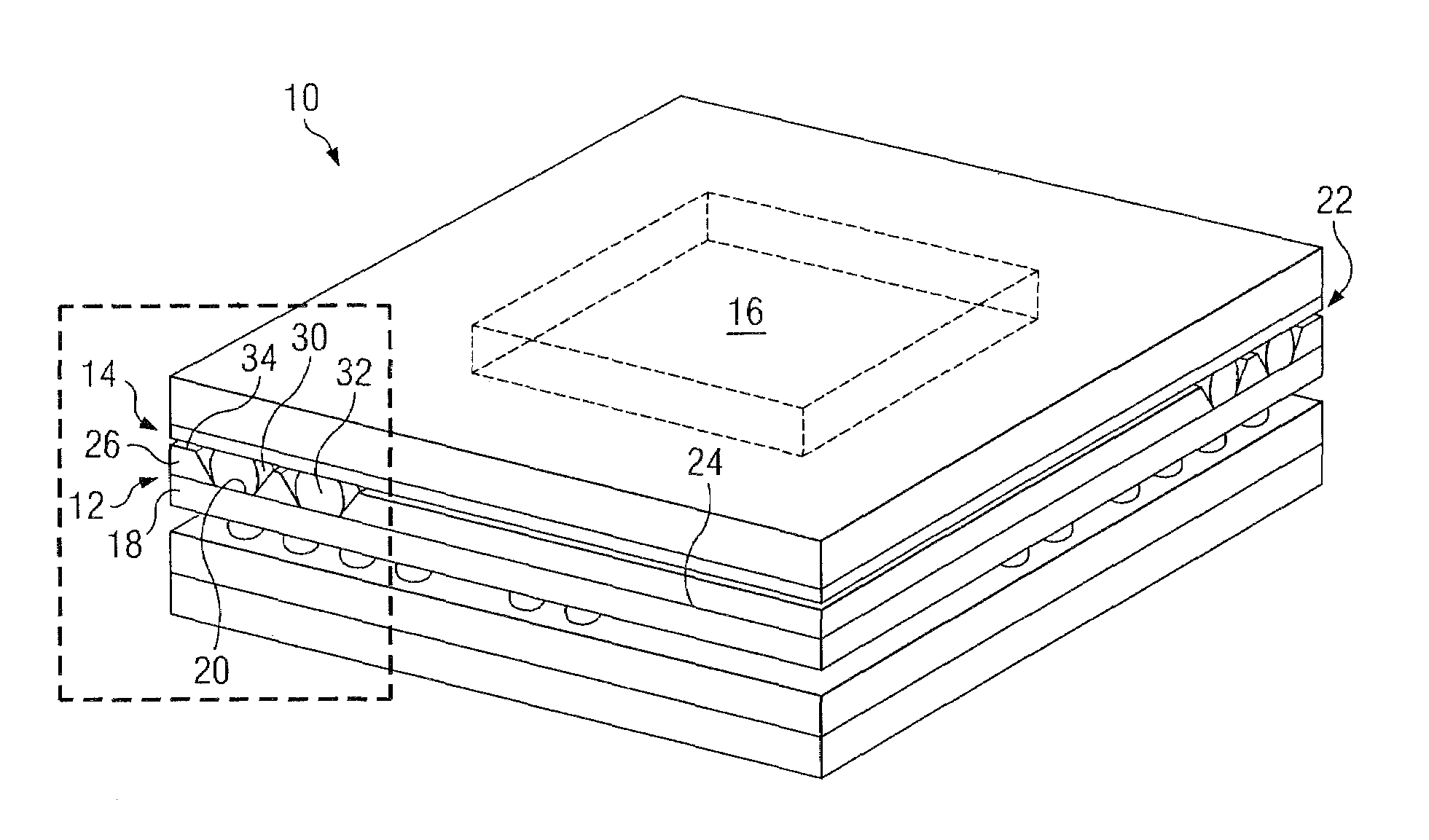

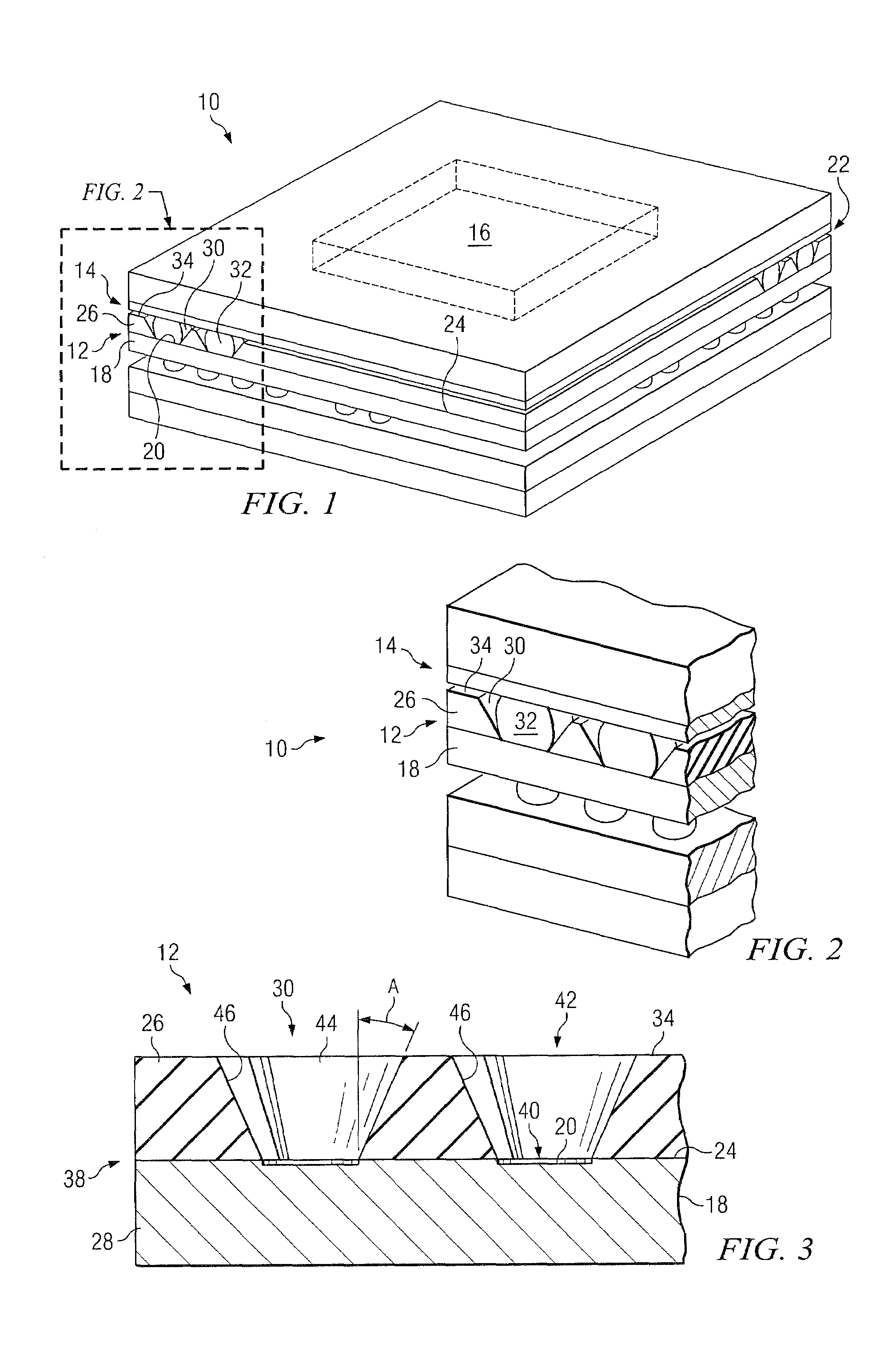

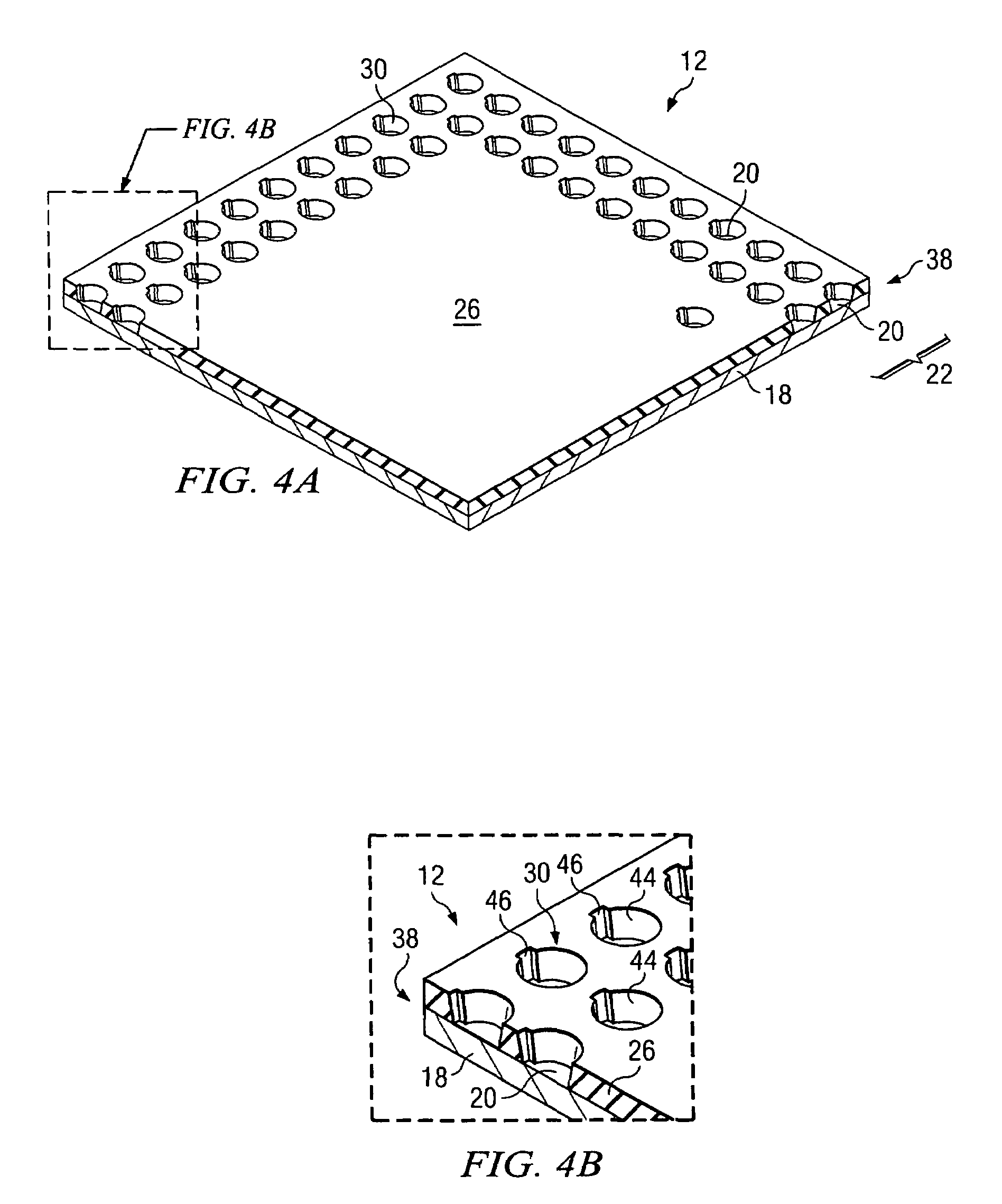

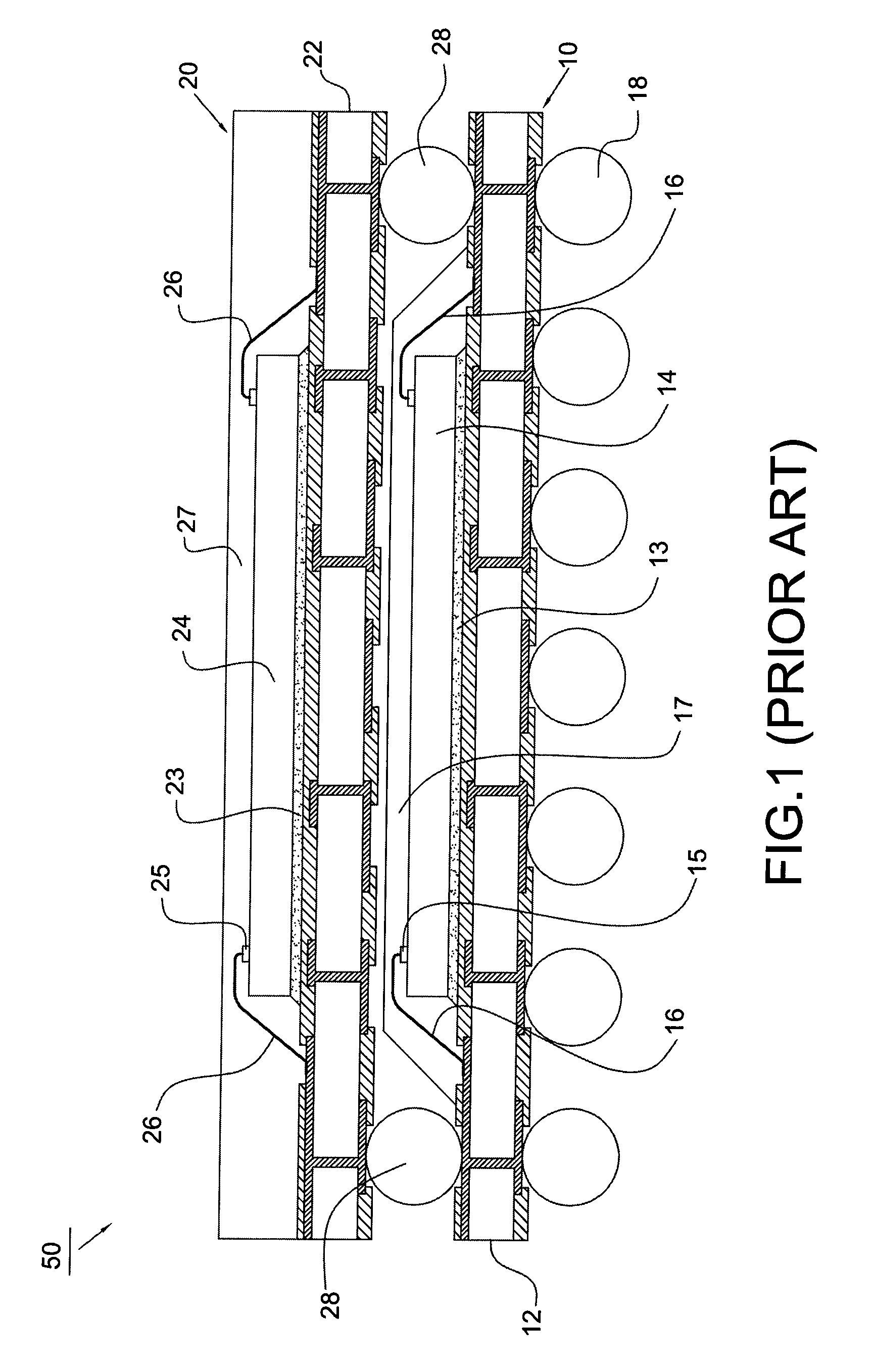

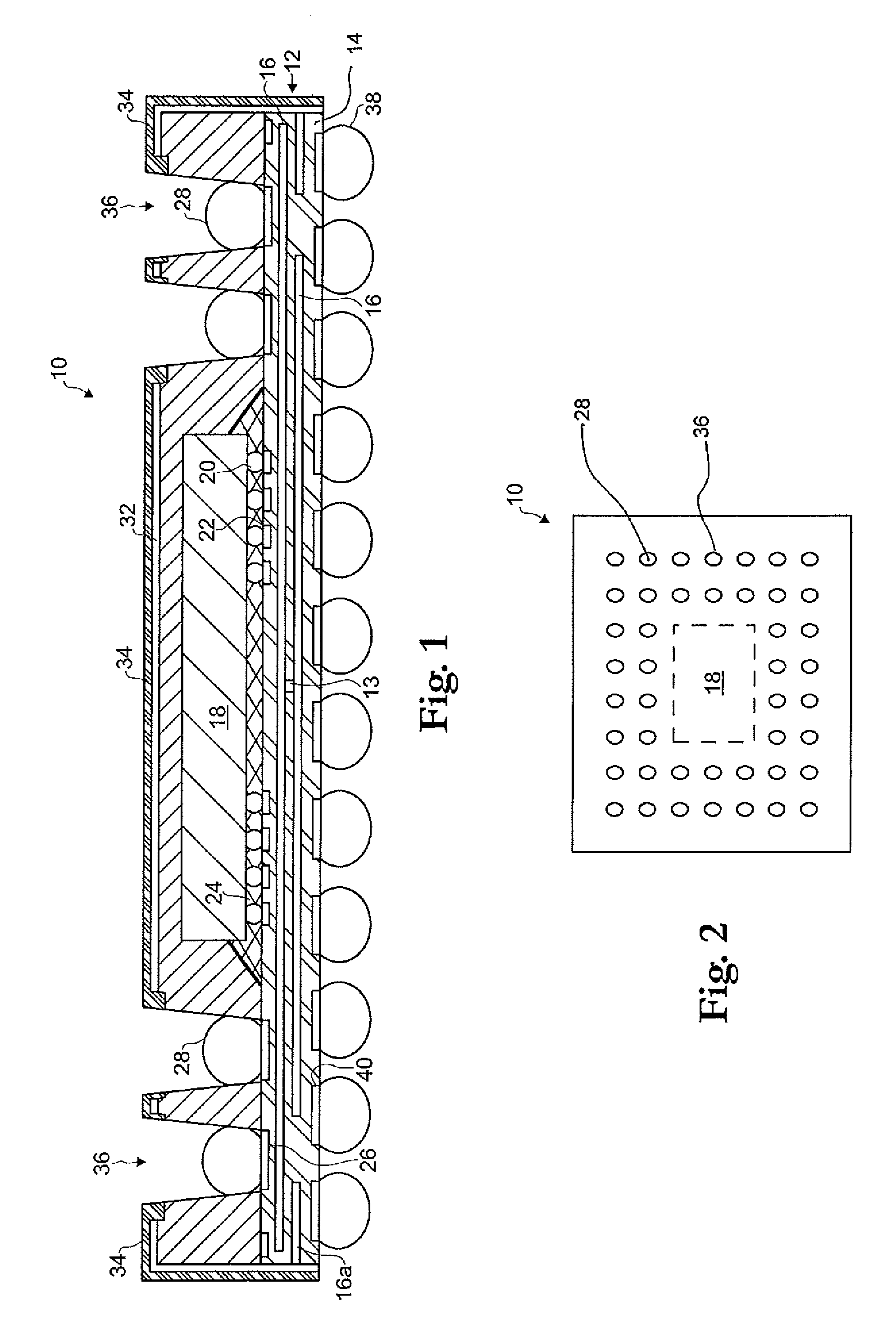

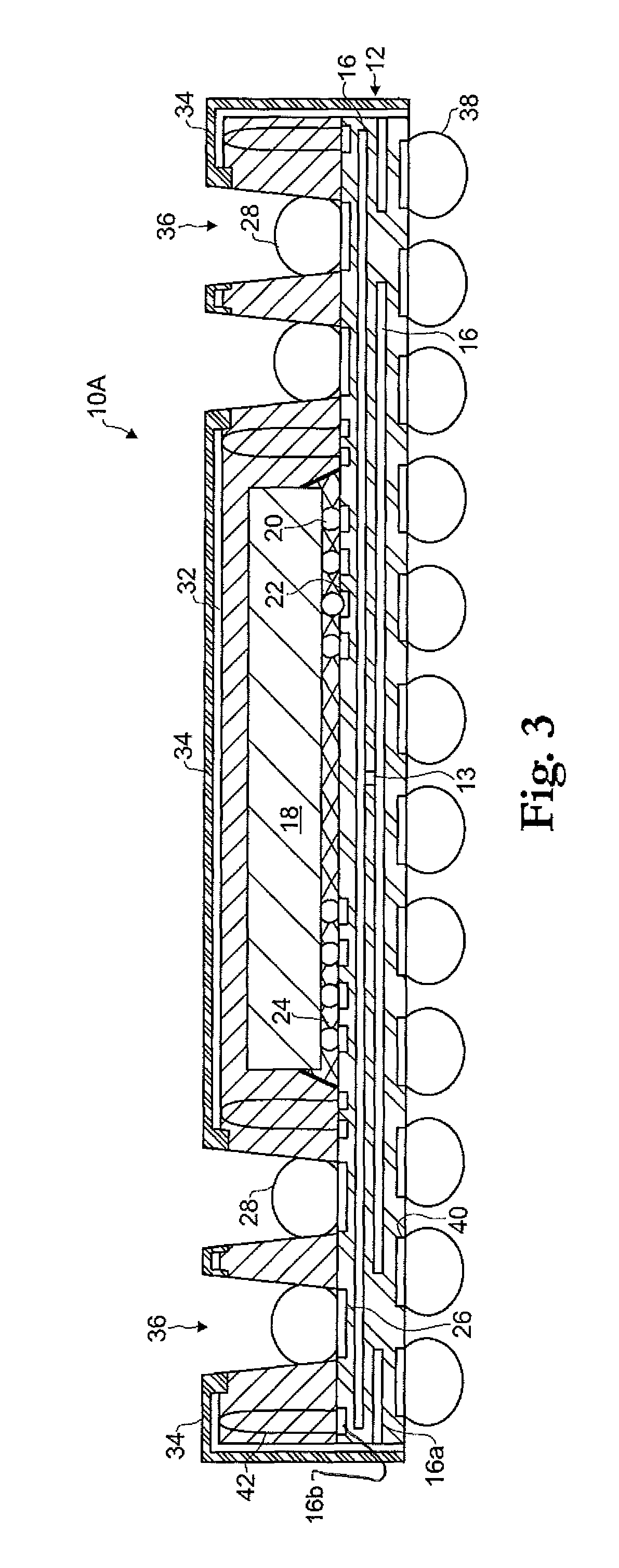

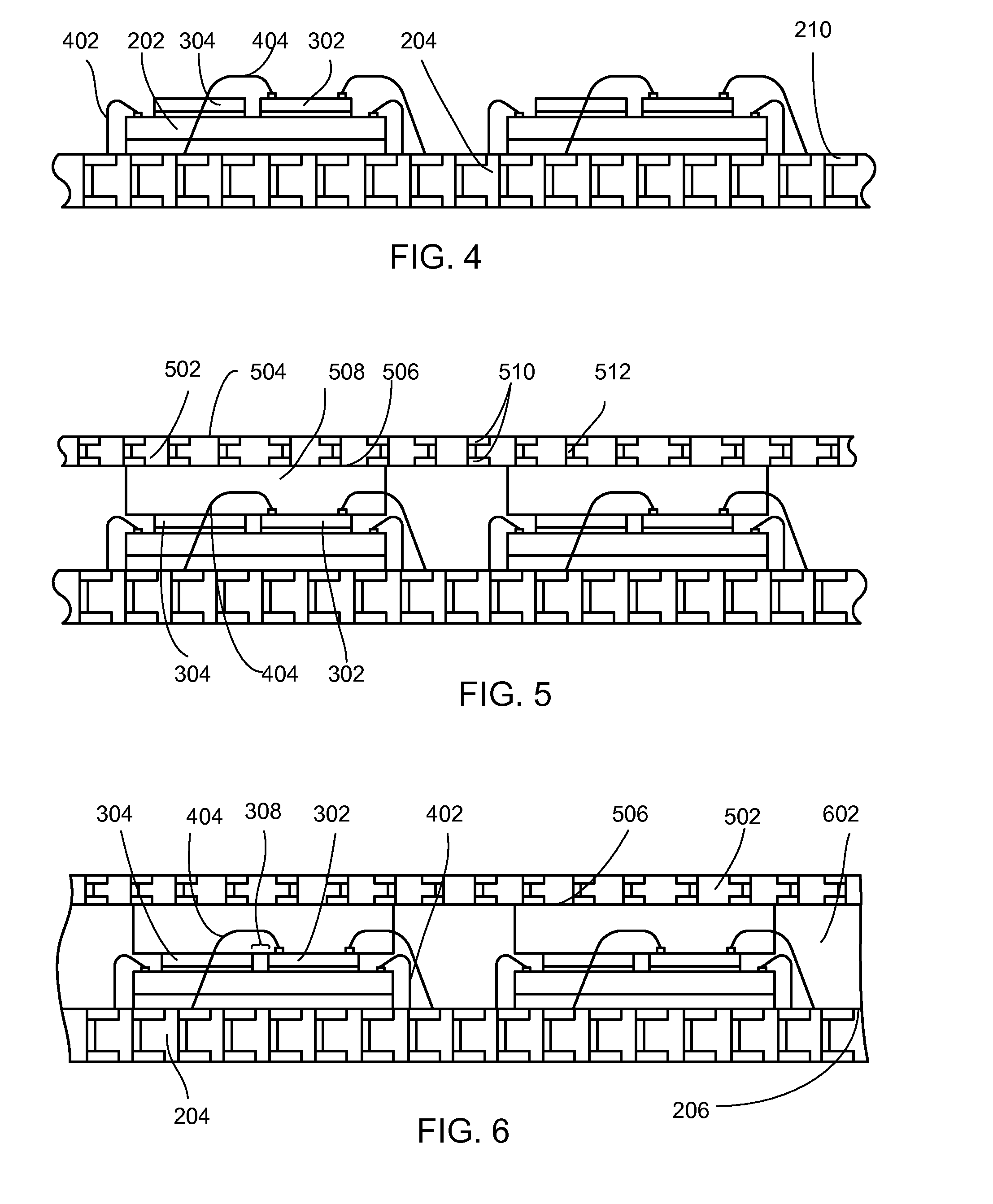

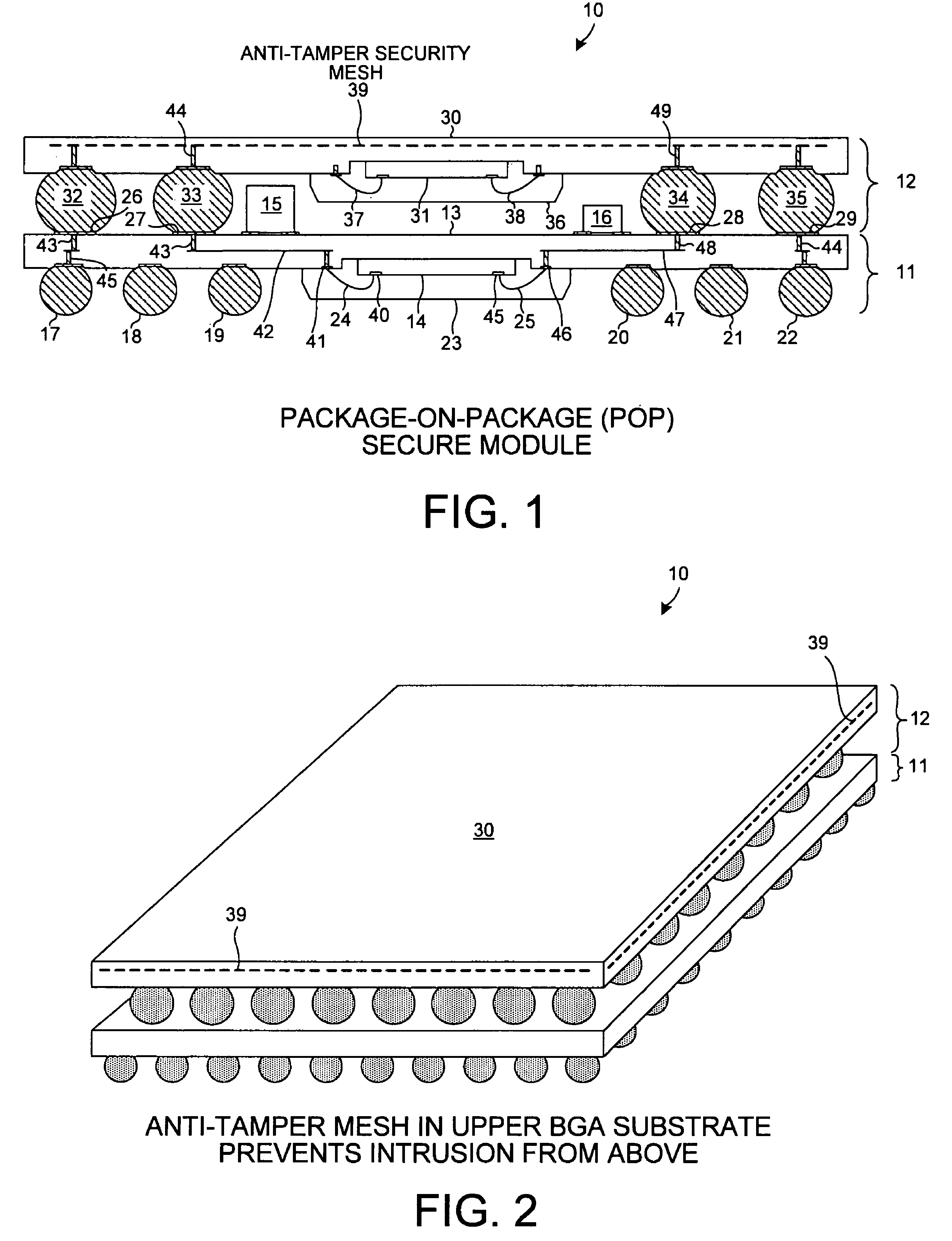

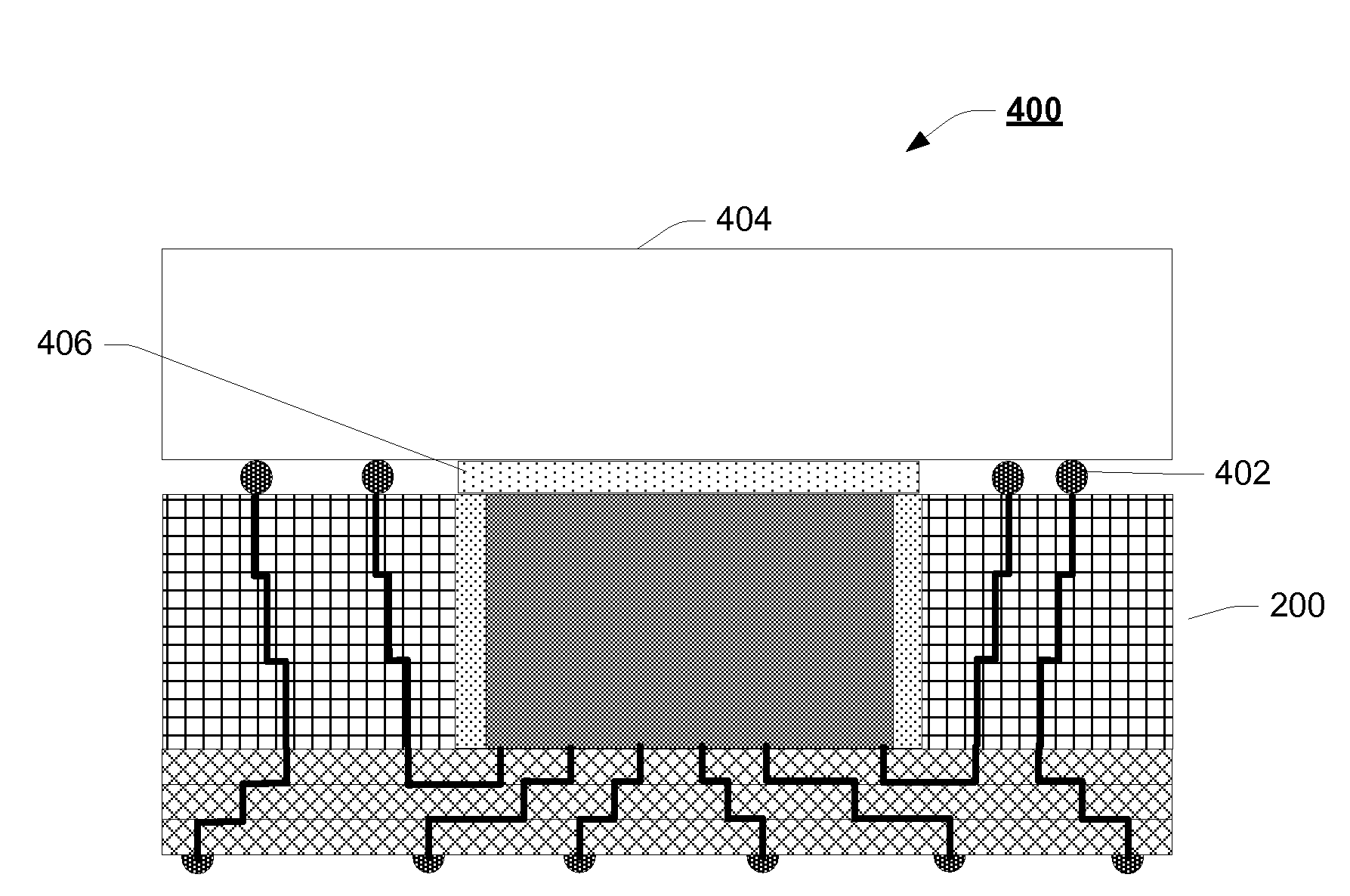

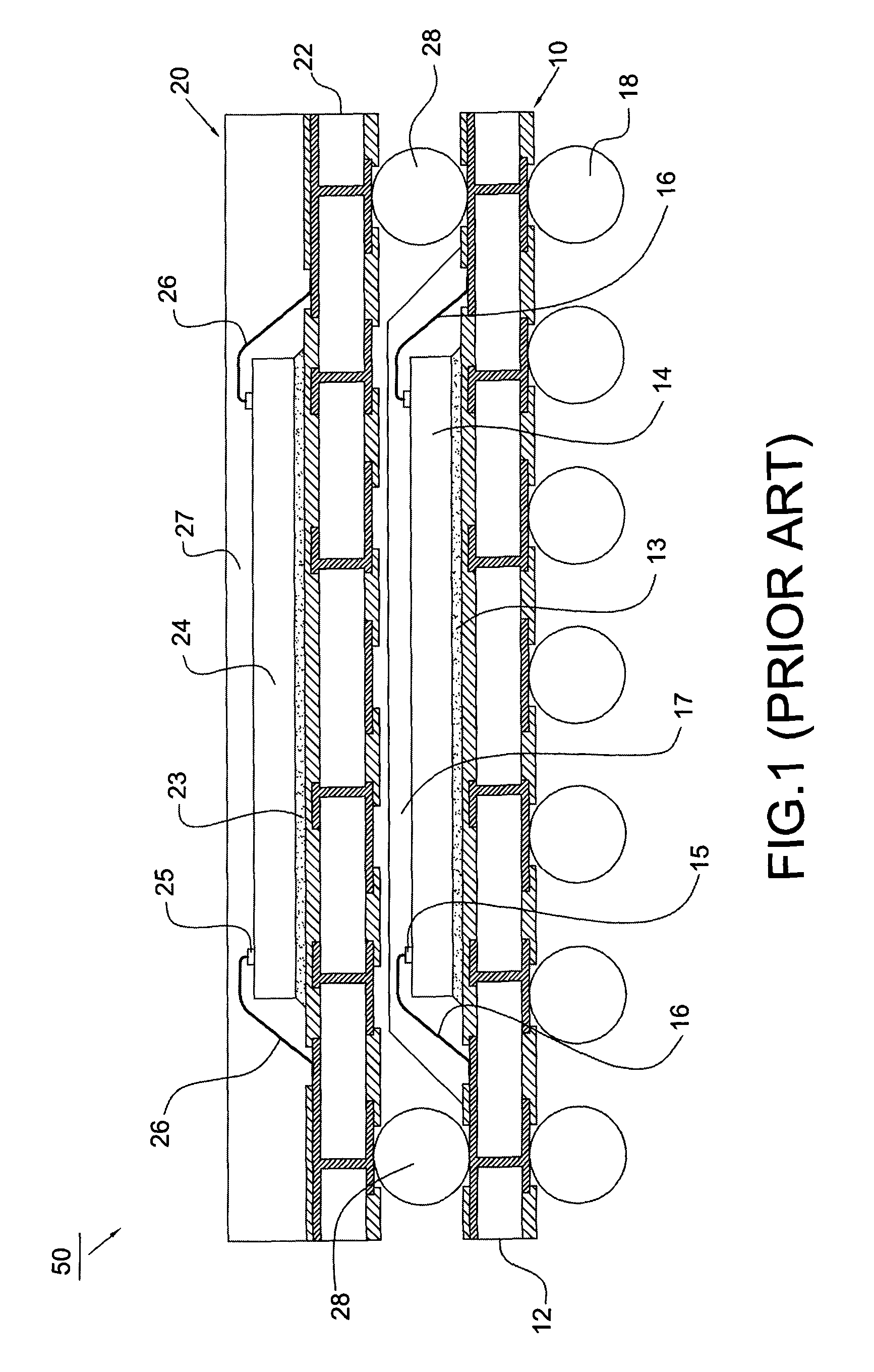

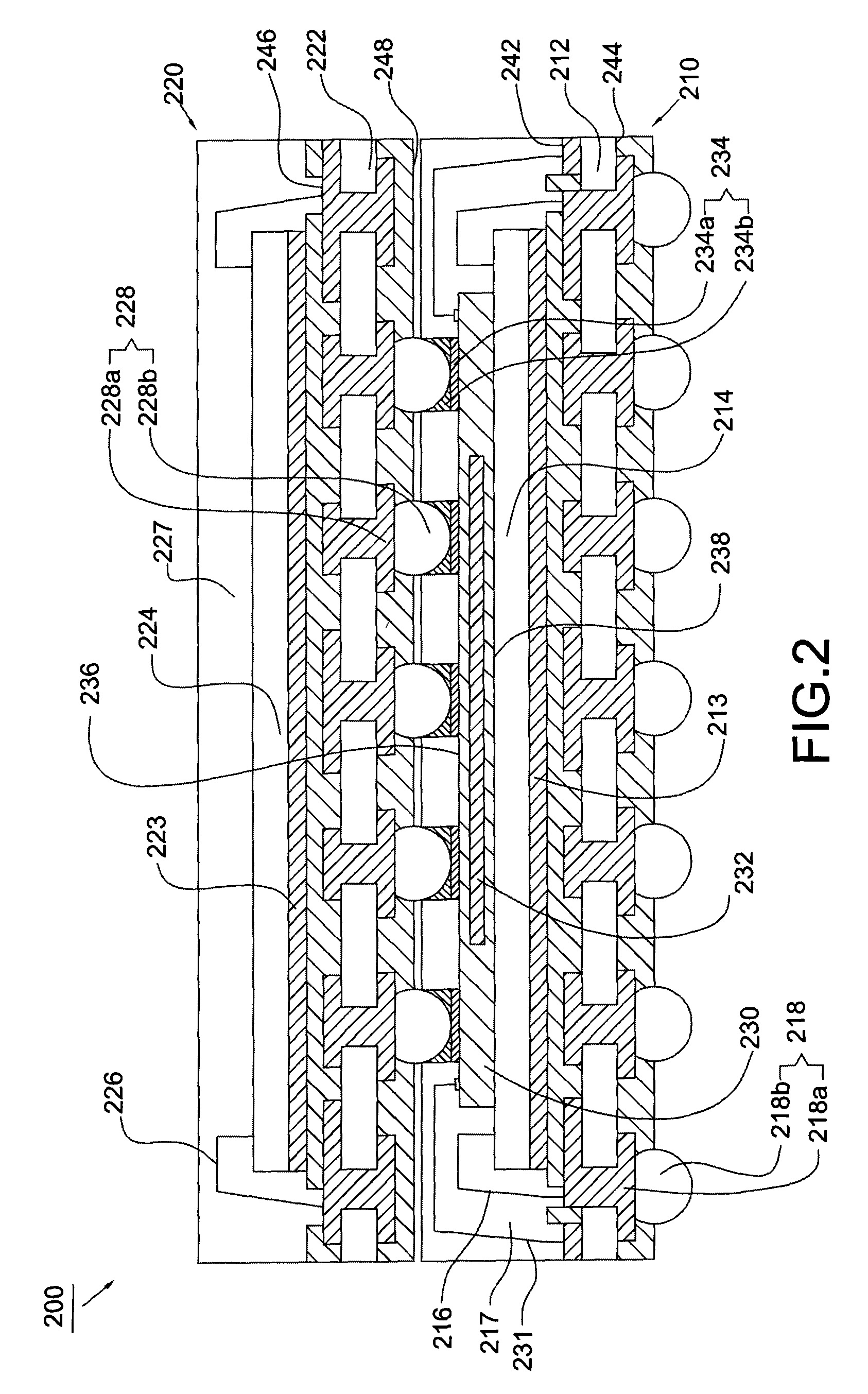

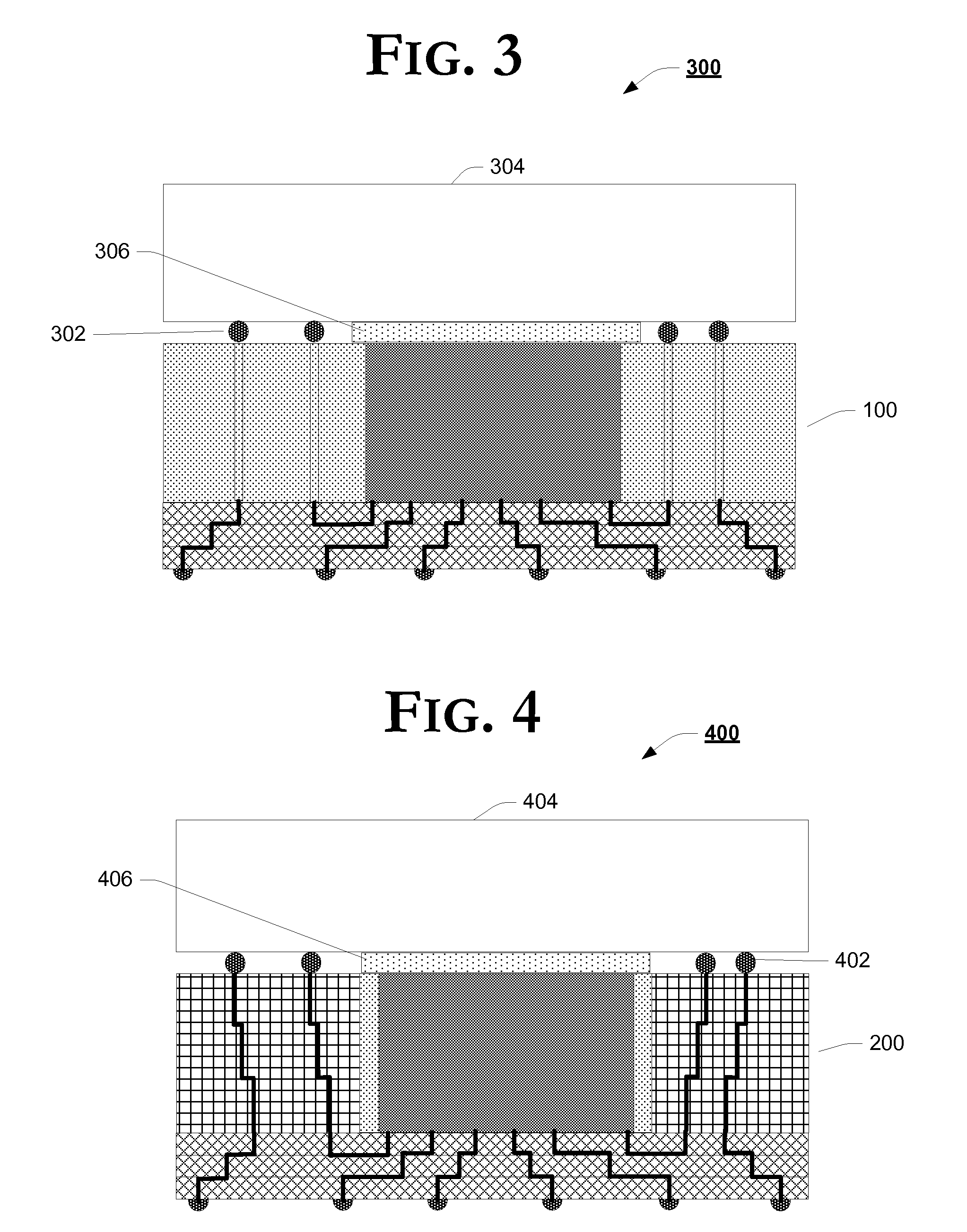

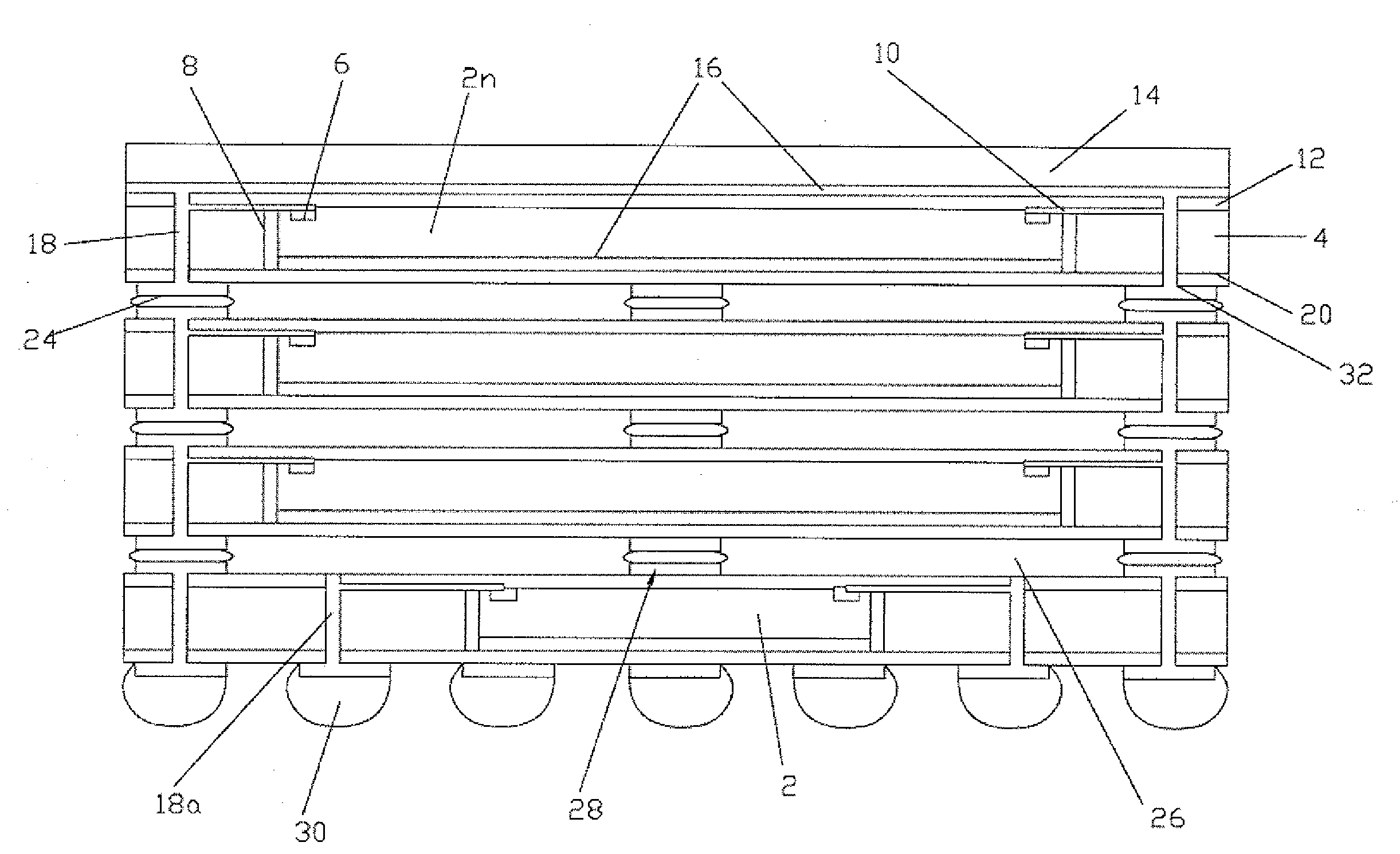

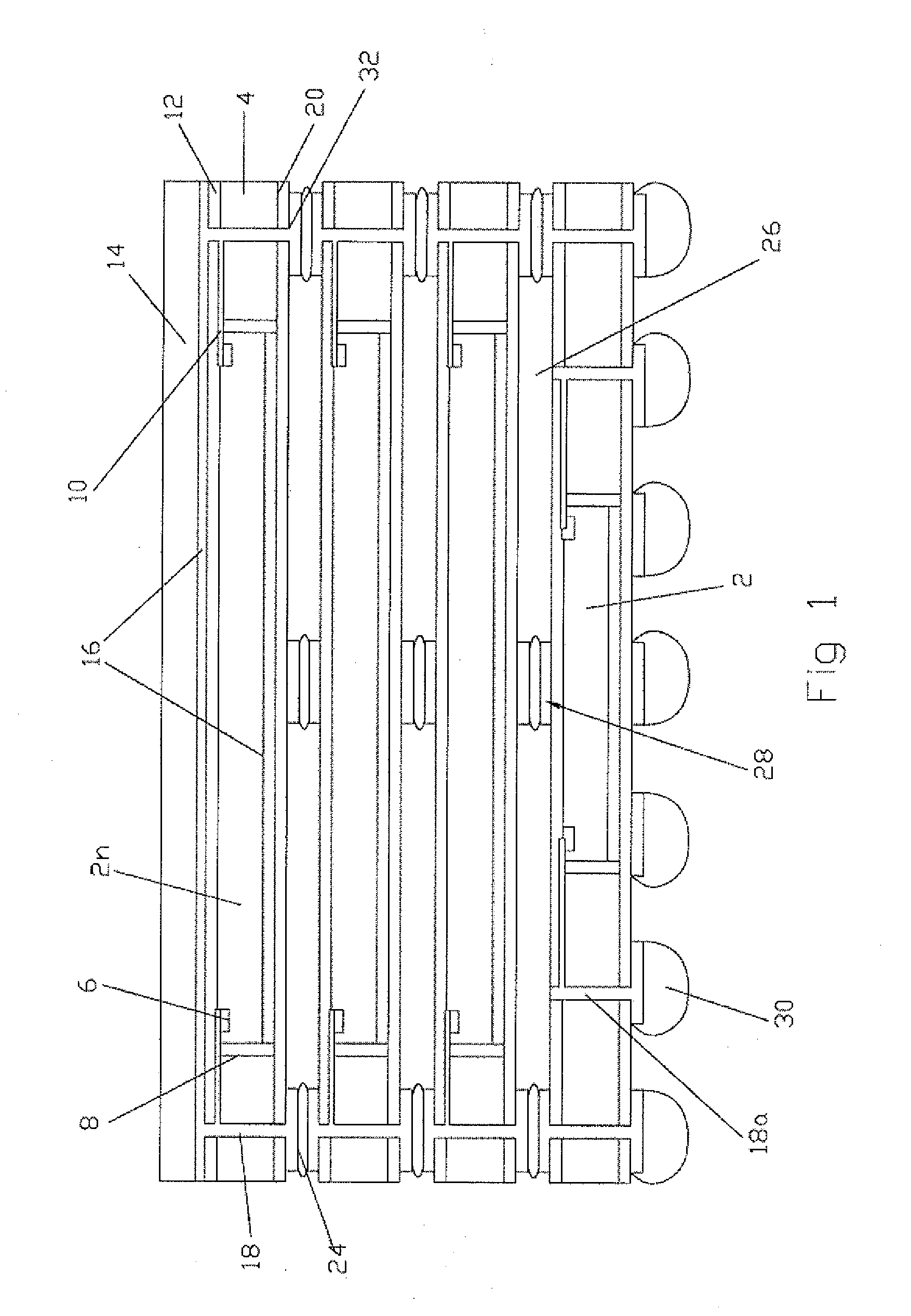

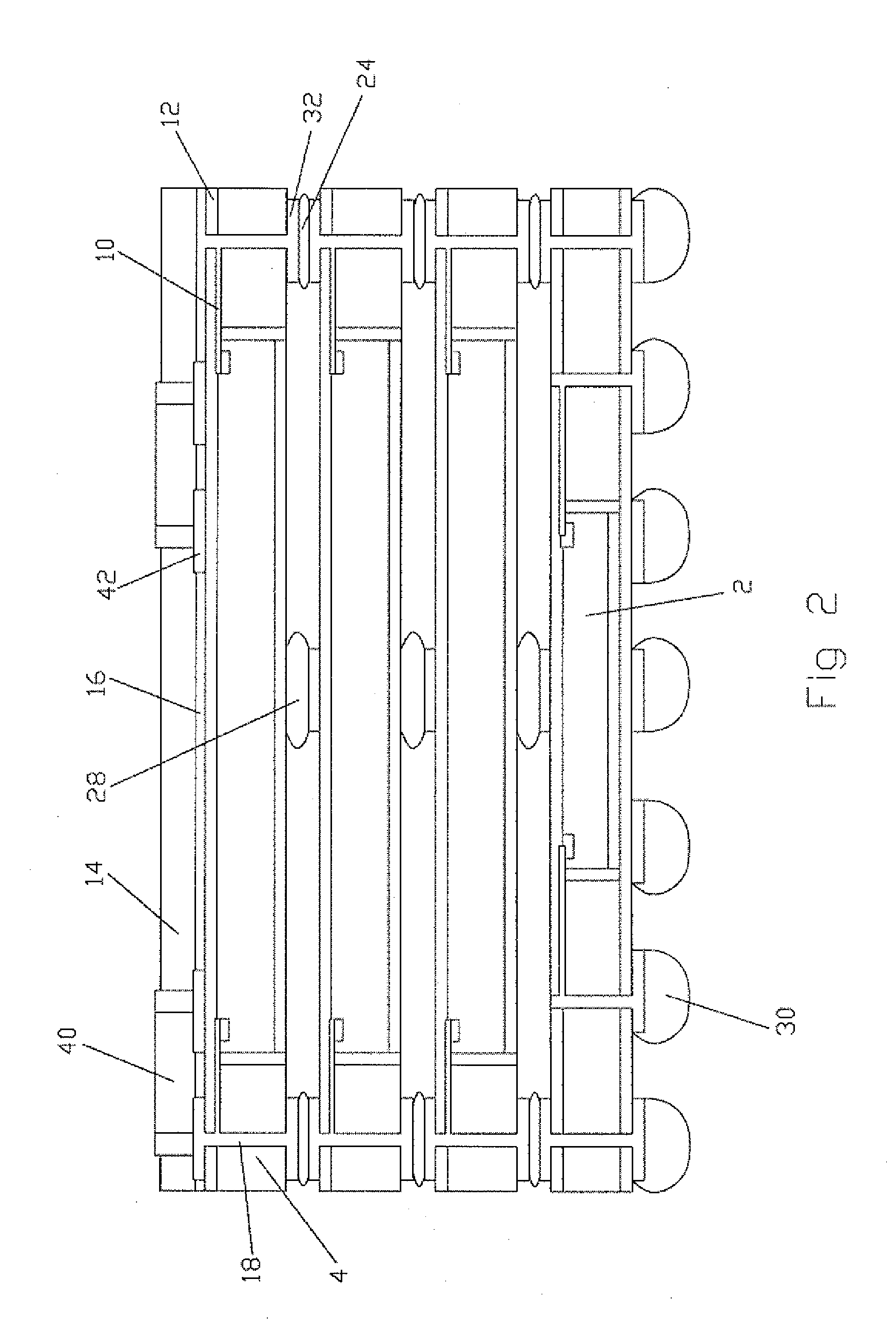

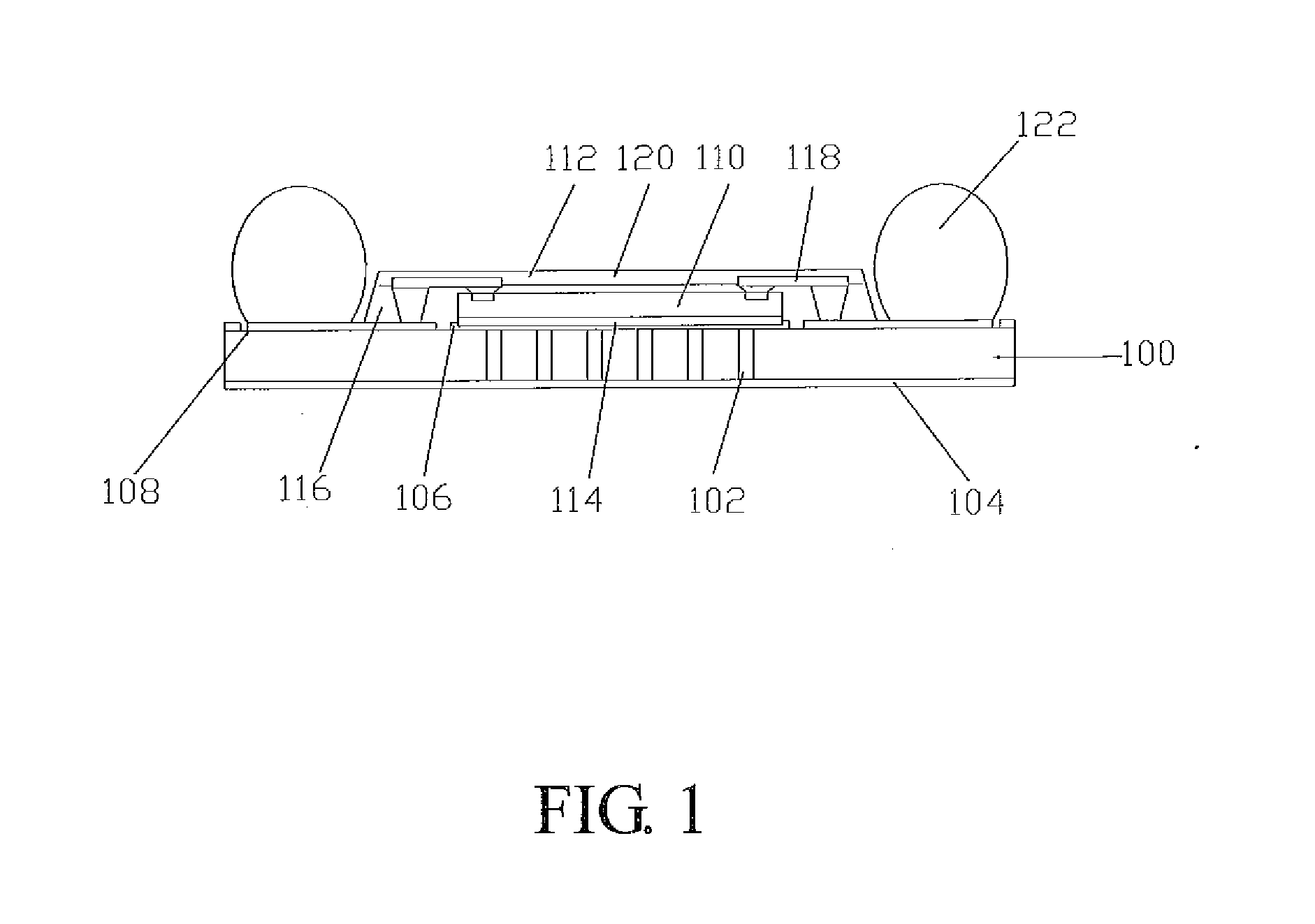

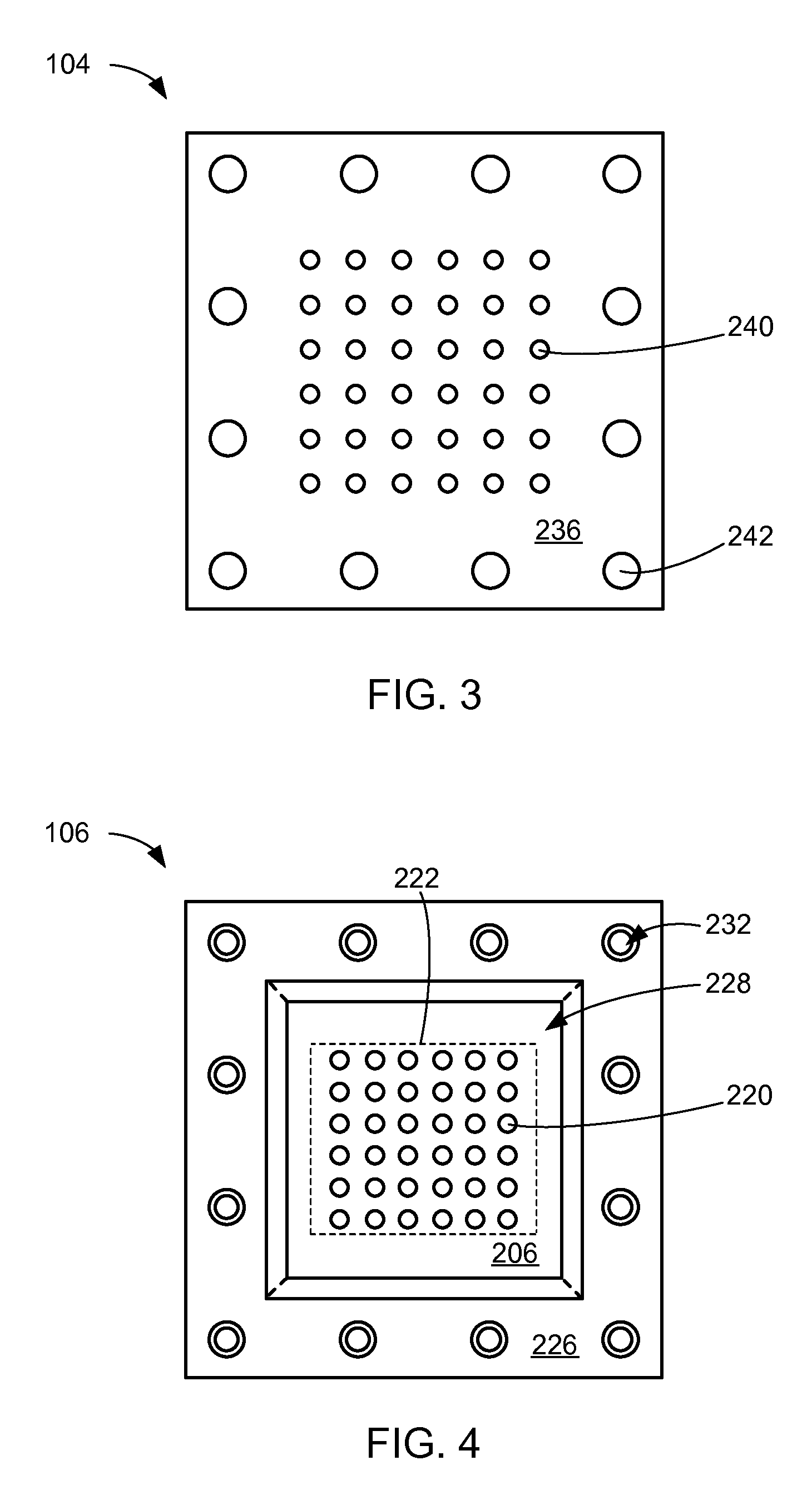

Package-on-package secure module having BGA mesh cap

InactiveUS20080251906A1Low costLarge massSemiconductor/solid-state device detailsSolid-state devicesMicrocontrollerTamper resistance

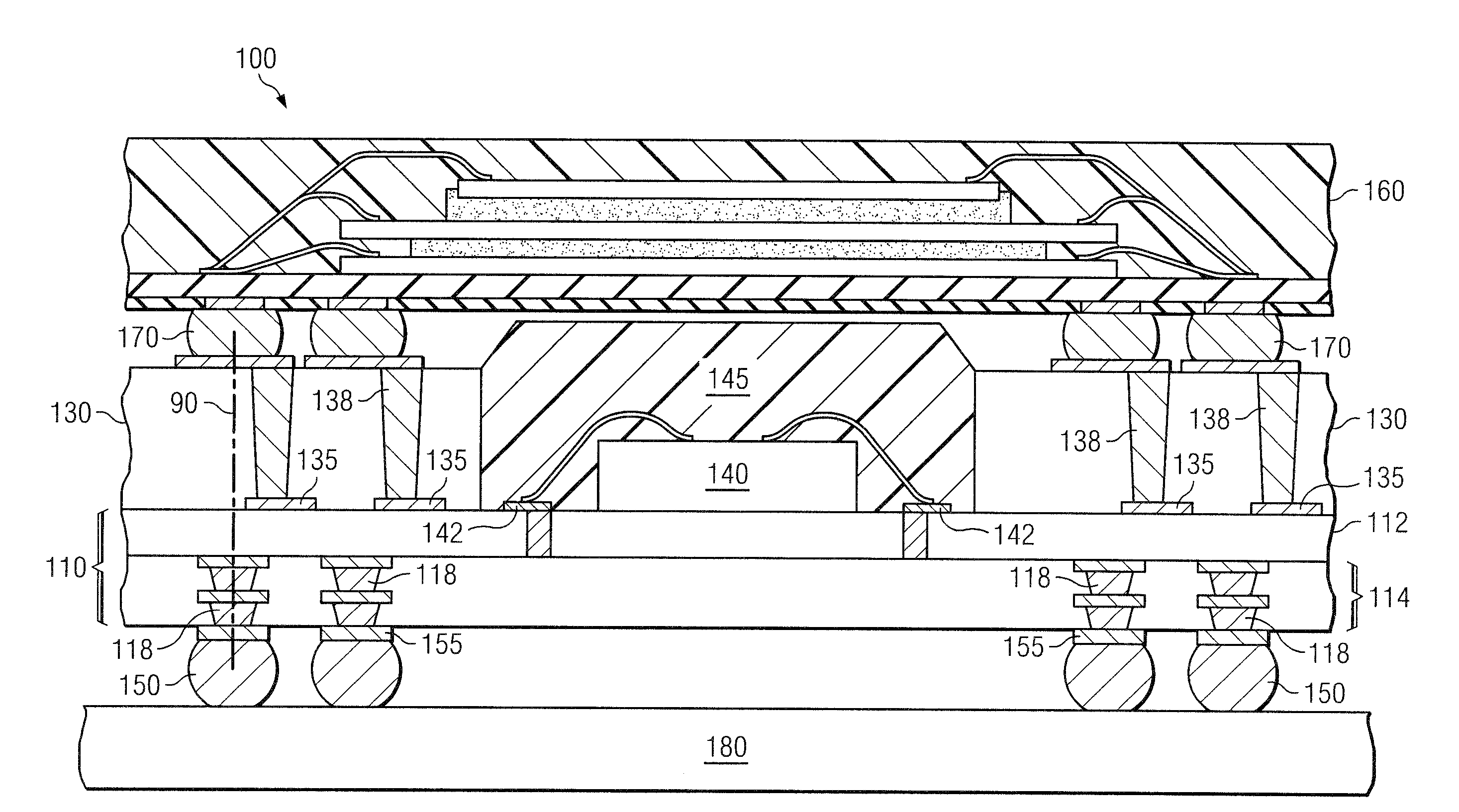

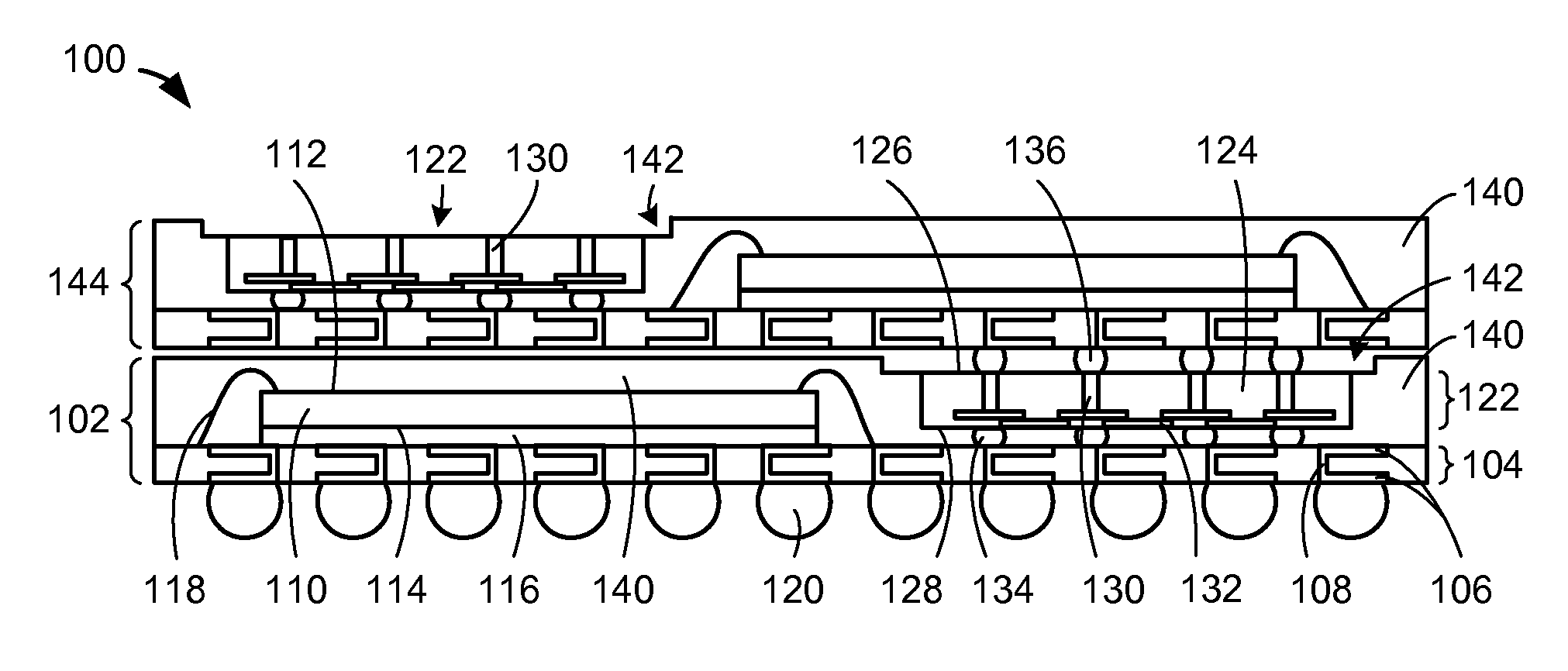

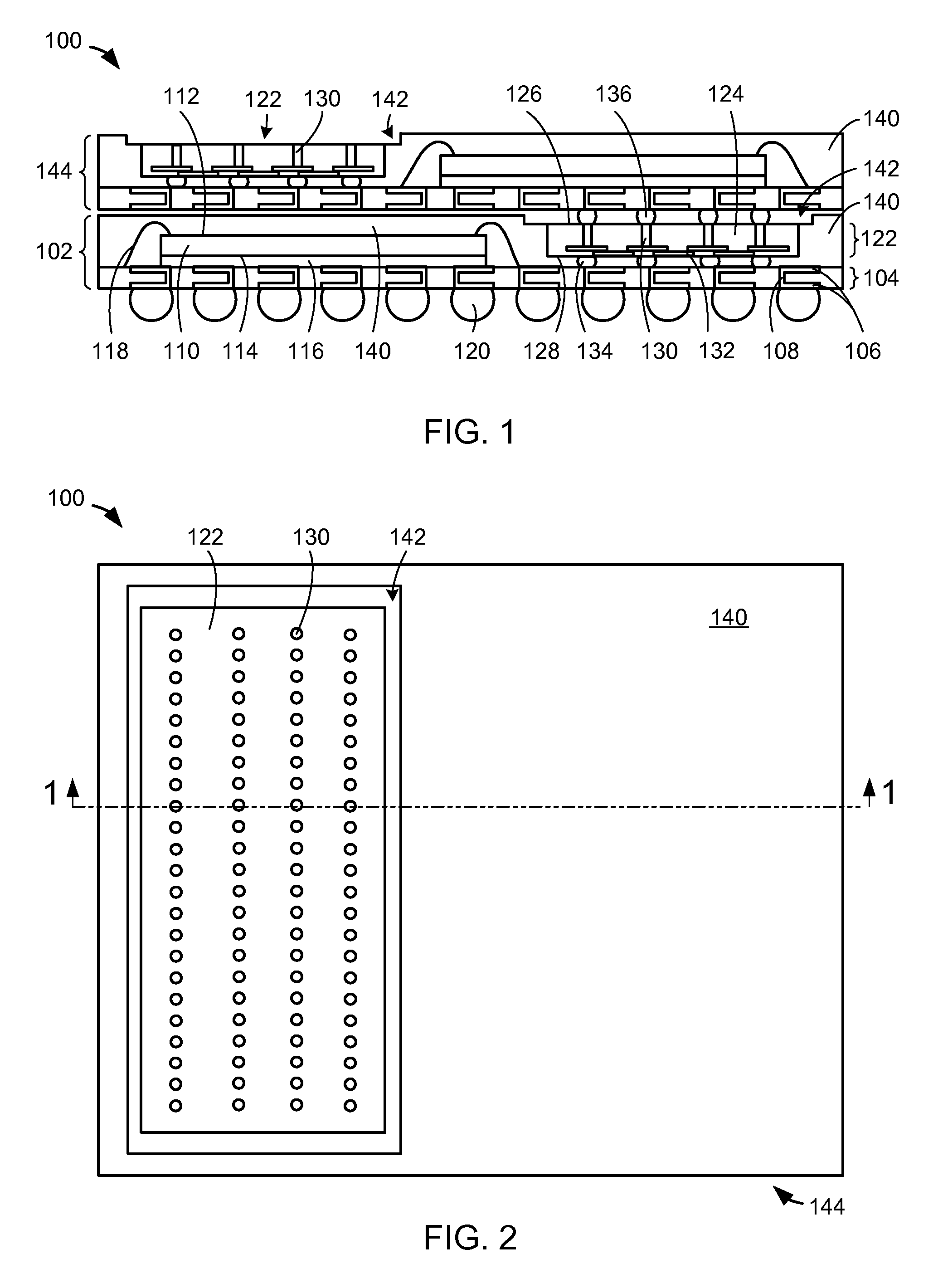

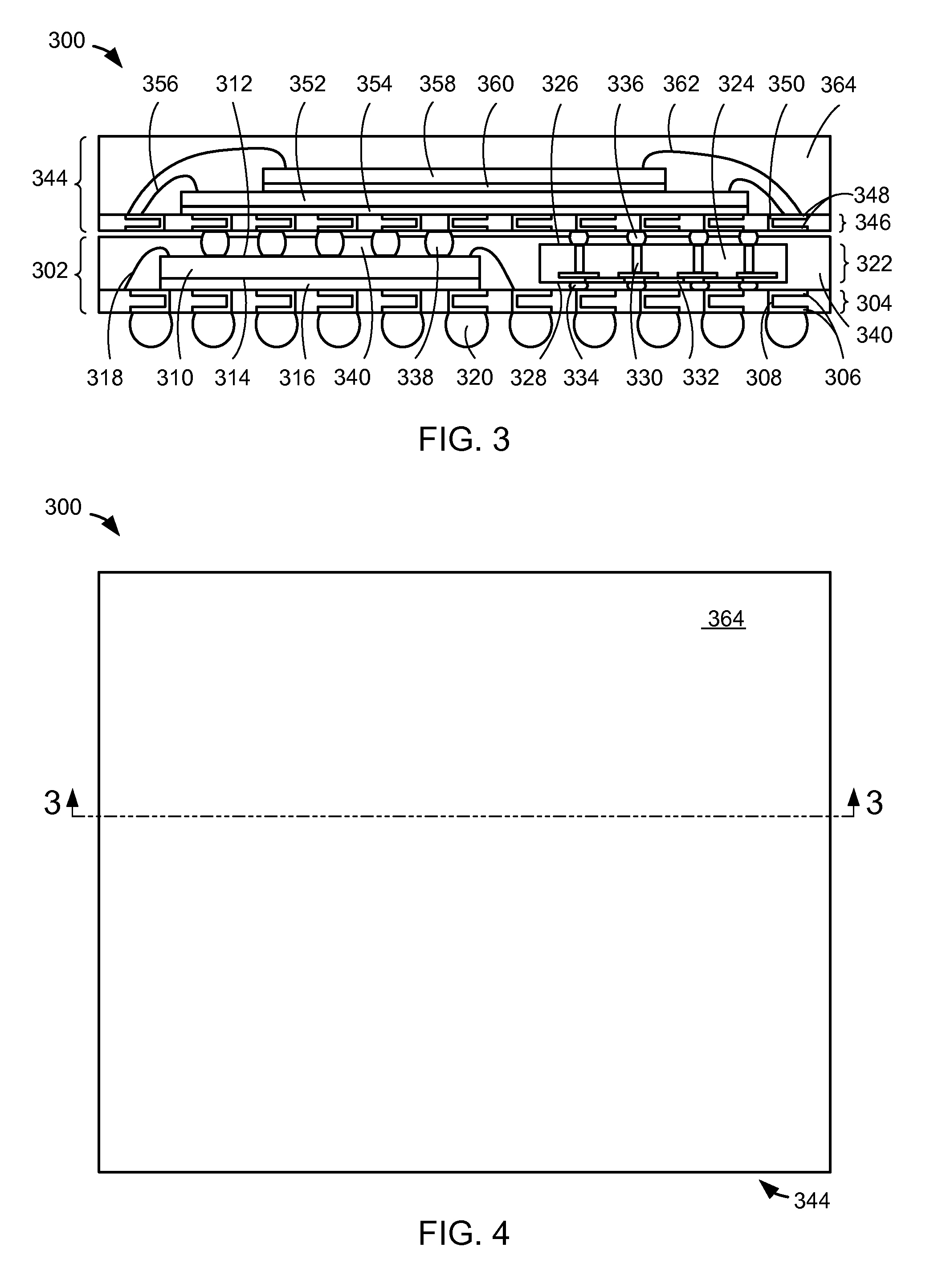

A package-on-package (POP) secure module includes a BGA mesh cap, a first BGA package, and a second BGA package. The first BGA package includes a first integrated circuit (for example, a microcontroller that includes tamper detect logic). The second BGA package includes a second integrated circuit (for example, a memory). The second BGA package is piggy-back mounted to the first BGA package and the BGA mesh cap is piggy-back mounted to the second BGA package. A printed circuit board substrate member of the BGA mesh cap includes an embedded anti-tamper mesh. This mesh is connected in a protected manner within the module to the first integrated circuit. When the module is in use, a mesh embedded in an underlying printed circuit board is coupled to the BGA cap mesh so that both anti-tamper meshes are controlled by the tamper detect logic.

Owner:MAXIM INTEGRATED PROD INC

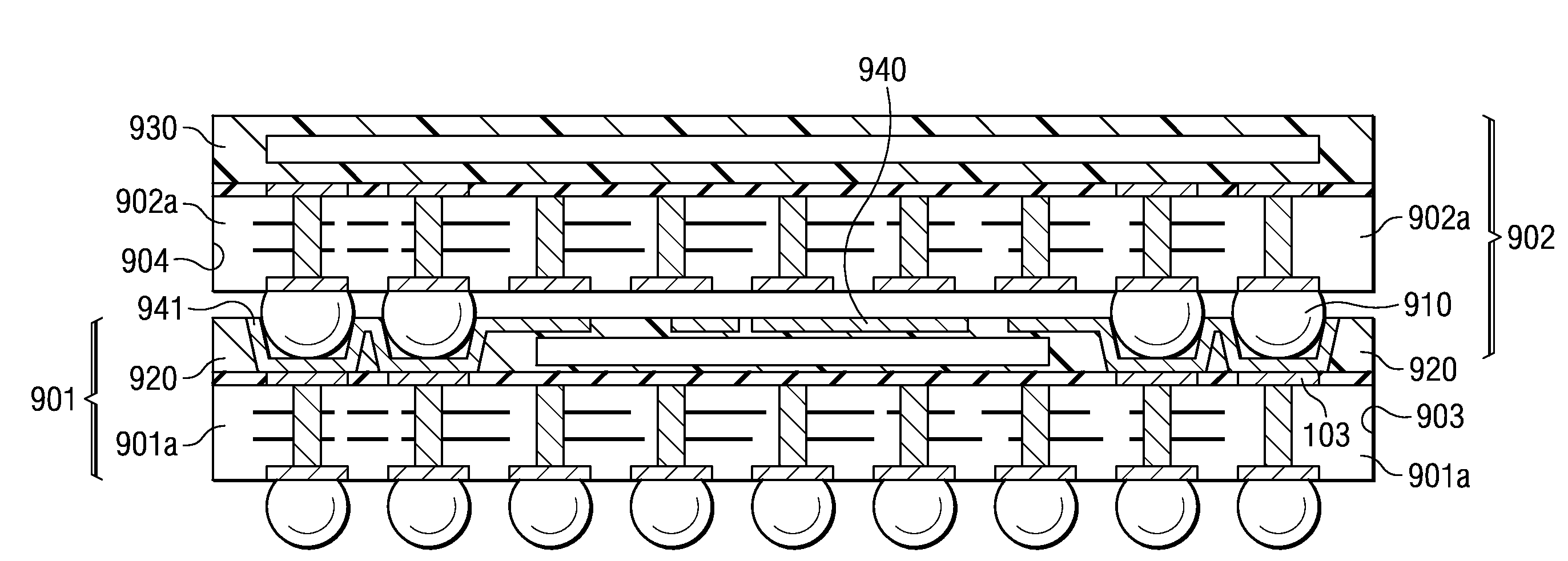

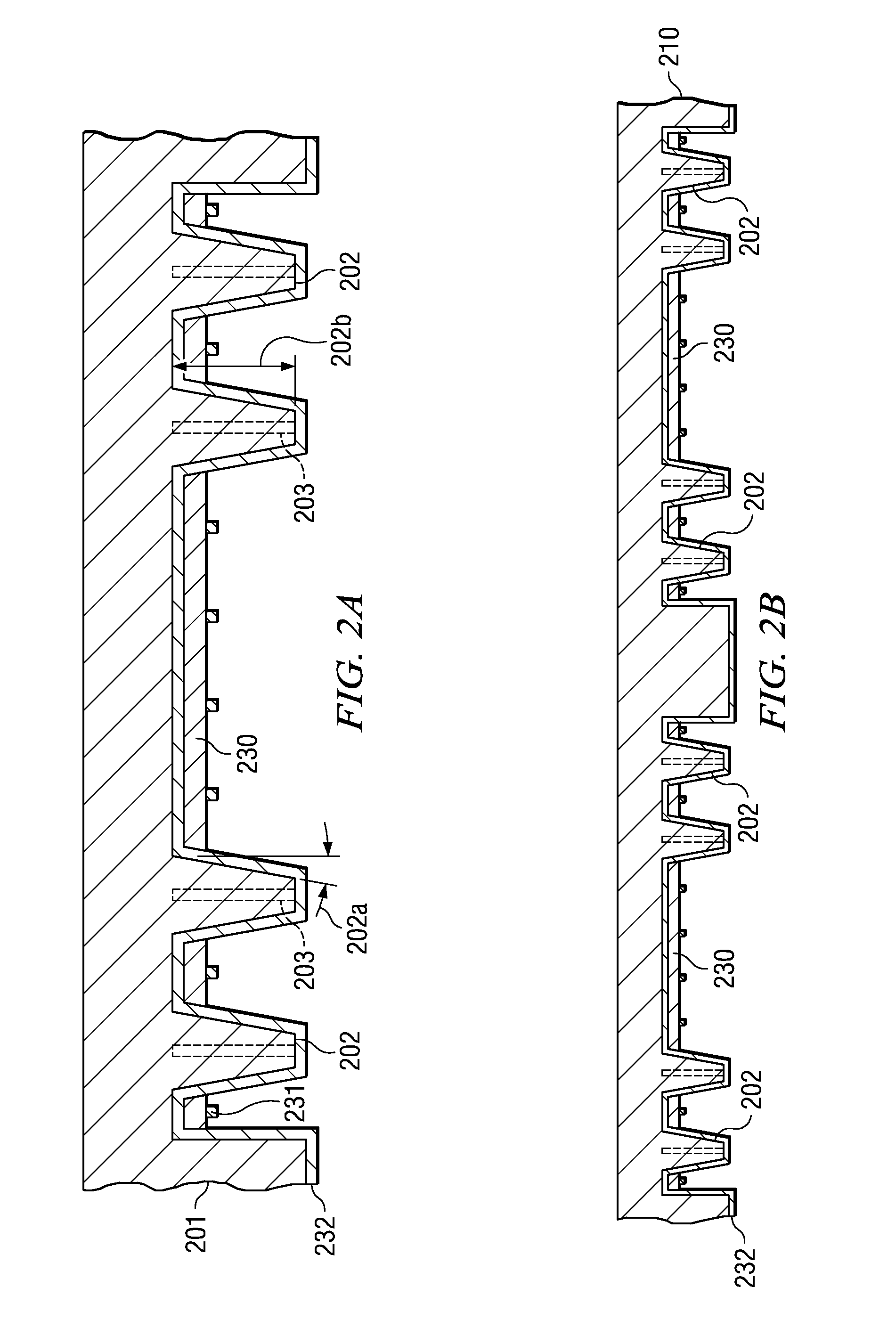

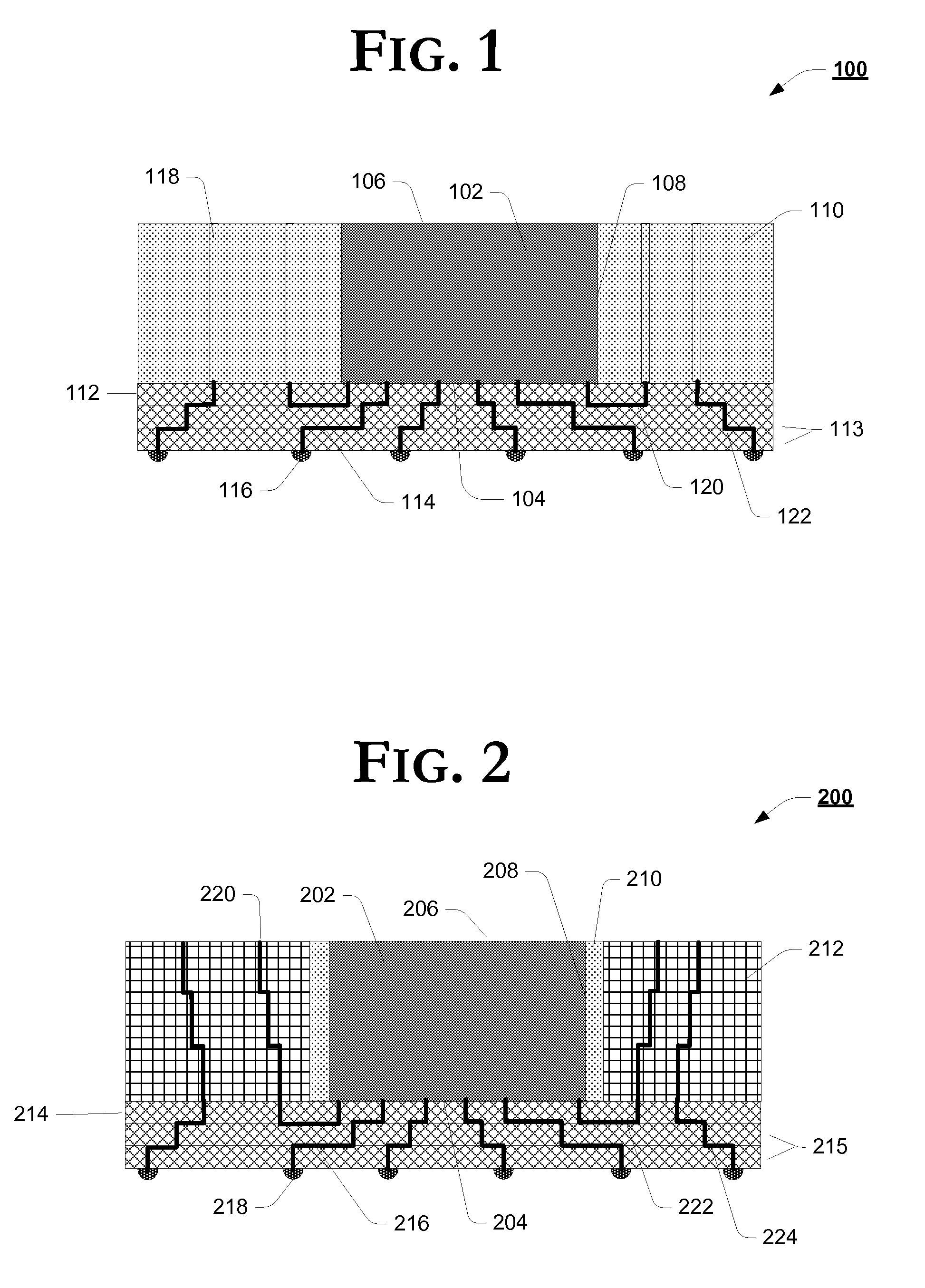

Array molded package-on-package having redistribution lines

ActiveUS20080315385A1Shorten the time to marketSimple methodSemiconductor/solid-state device detailsSolid-state devicesContact padCoupling

A semiconductor device with a sheet-like insulating substrate (101) integral with two or more patterned layers of conductive lines and vias, a chip attached to an assembly site, and contact pads (103) in pad locations has an encapsulated region on the top surface of the substrate, extending to the edge of the substrate, enclosing the chip, and having contact apertures (703) at the pad locations for external communication with the pad metal surfaces. The apertures may have not-smooth sidewall surfaces and may be filled with solder material (704) to contact the pads. Metal-filled surface grooves (710) in the encapsulated region, with smooth groove bottom and sidewalls, are selected to serve as customized routing interconnections, or redistribution lines, between selected apertures and thus to facilitate the coupling with another semiconductor device to form a package-on-package assembly.

Owner:TEXAS INSTR INC

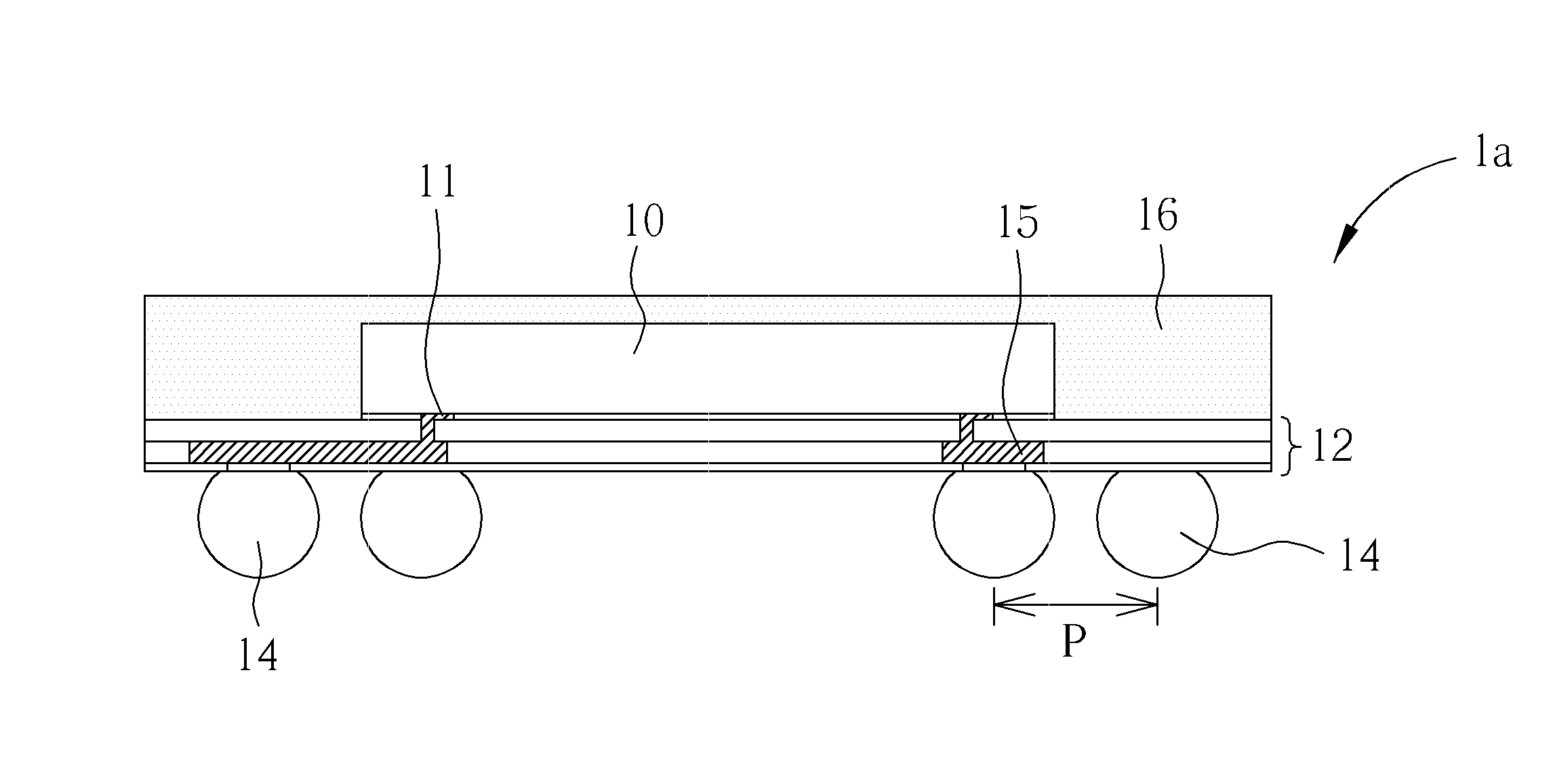

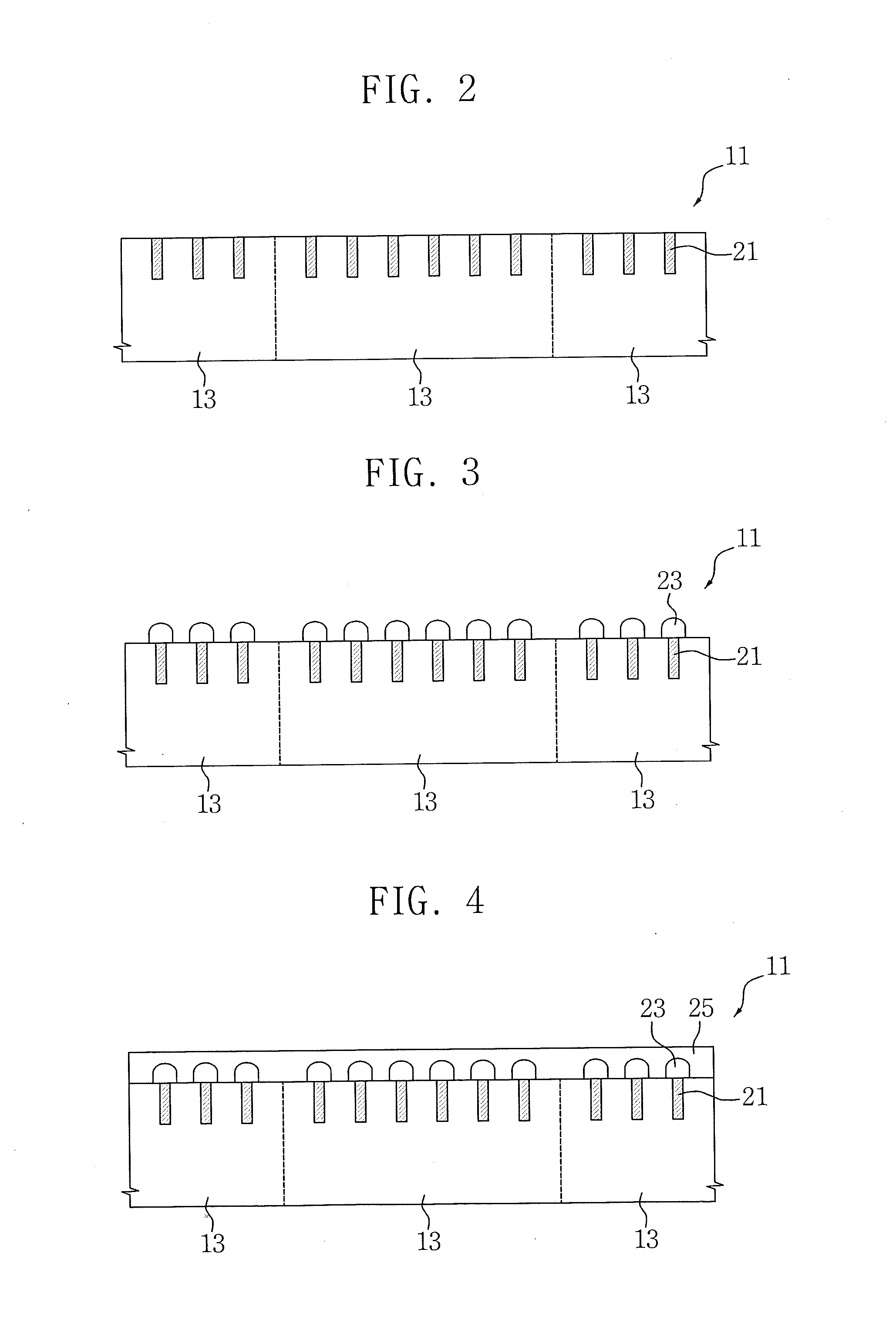

Bottom substrate of package on package and manufacturing method thereof

InactiveUS20080006942A1Increasing the thicknessSemiconductor/solid-state device detailsSolid-state devicesInsulation layerSolder ball

A bottom substrate of package on package and manufacturing method thereof is disclosed. A bottom substrate of a package on package electrically connected to a top substrate by means of a solder ball, including a core board, a solder ball pad formed on a surface of the core board in correspondence with a location of the solder ball, an insulation layer laminated on the core board, a through hole formed by removing a part of the insulation layer such that the solder ball pad is exposed, and a metallic layer filled in the through hole and connected electrically with the solder ball, allows the number of ICs mounted on a bottom substrate to be increased without increasing the size of a solder ball, and allows the size and pitch of the solder balls to be made smaller by controlling the thickness of the insulation layer laminated on the bottom substrate, whereby more signal transmission is possible between a top substrate and a bottom substrate.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

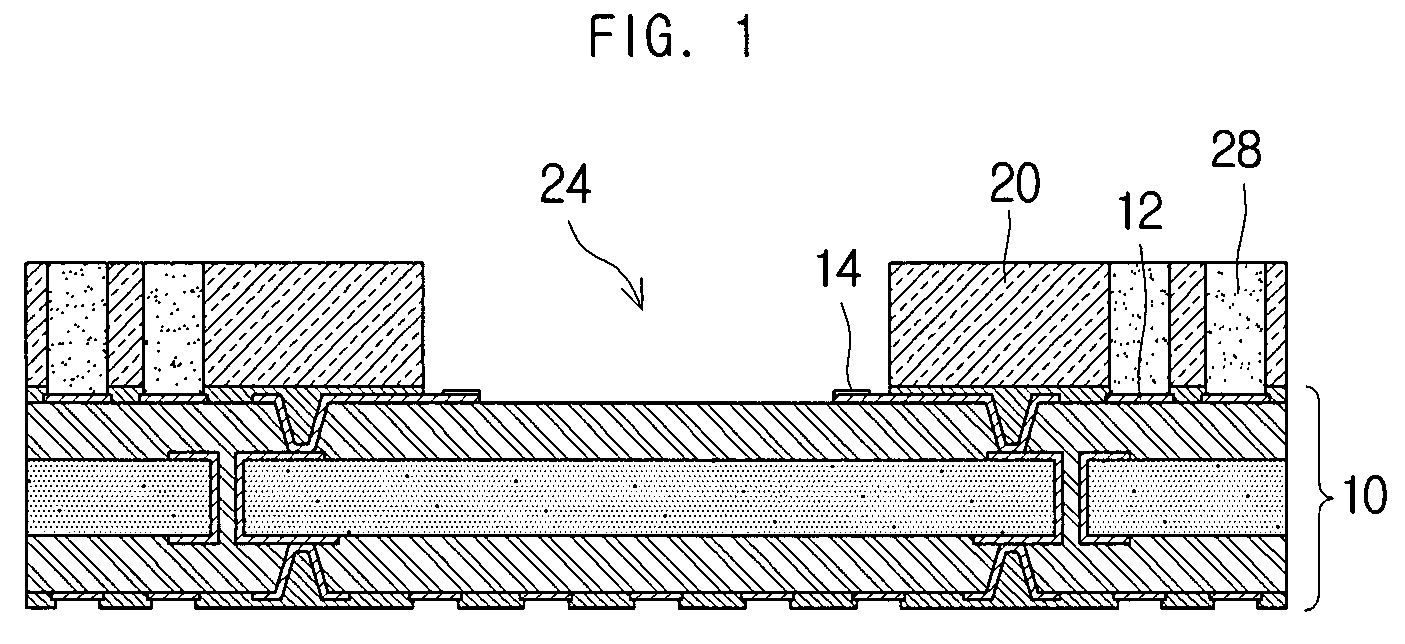

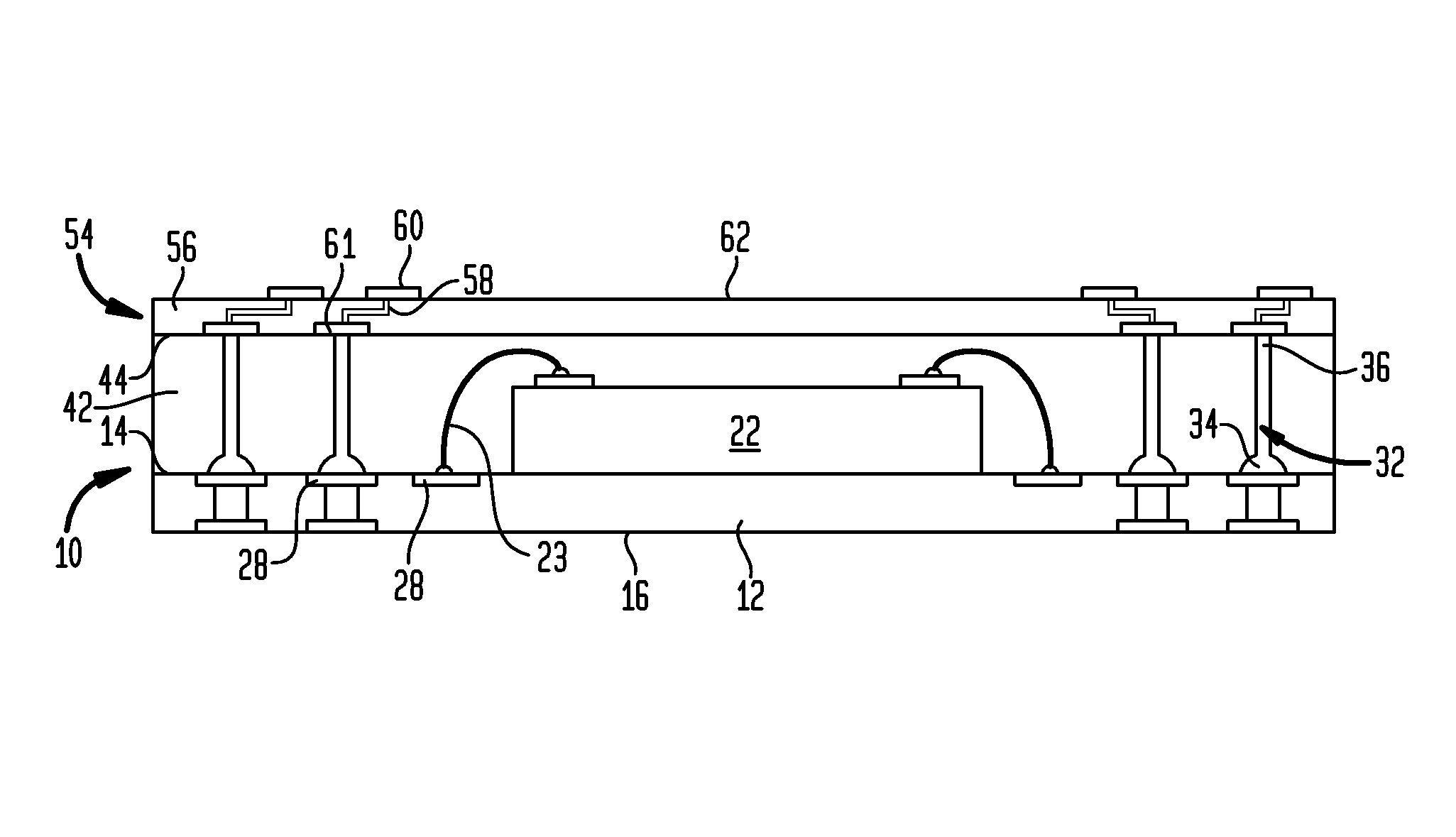

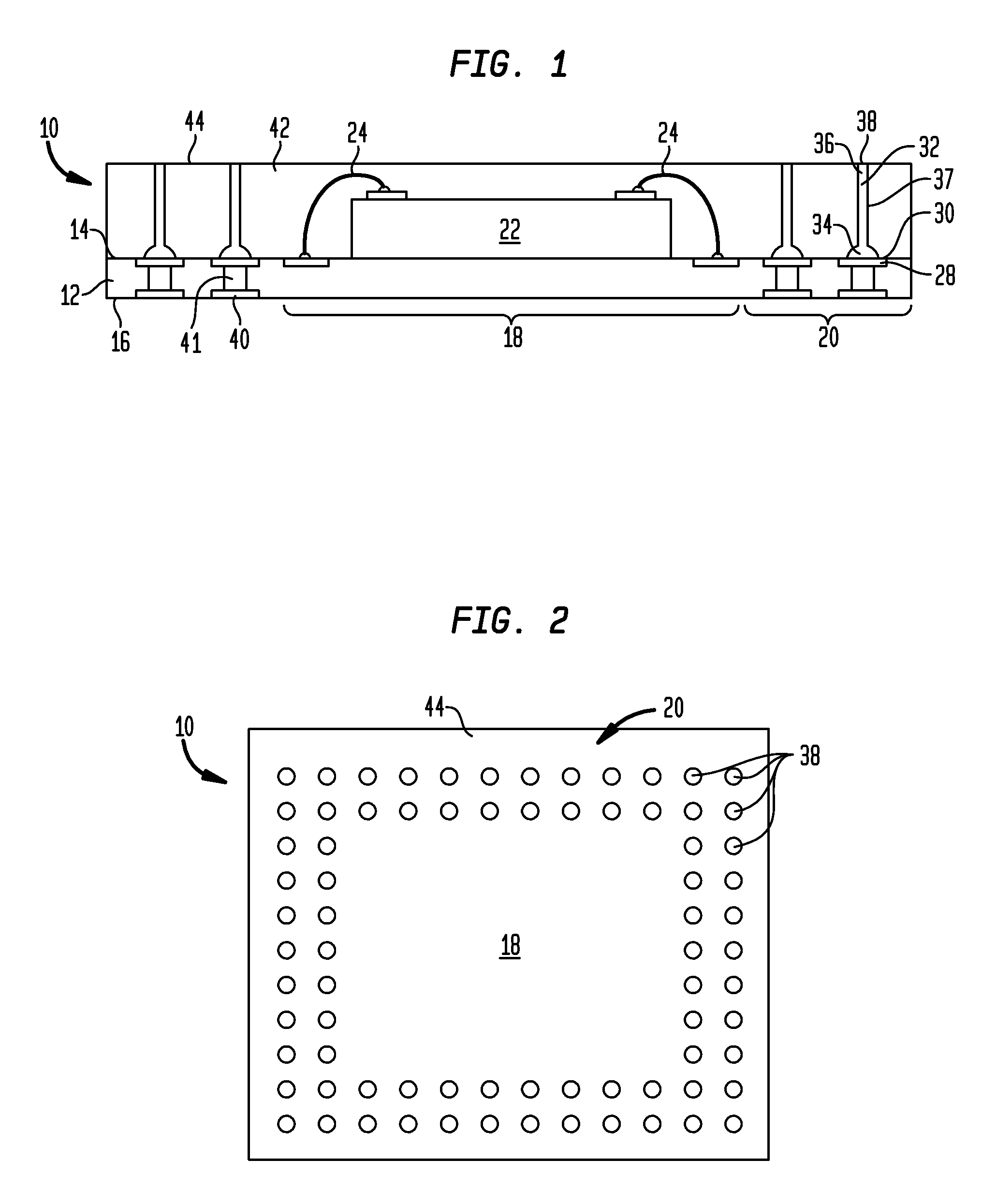

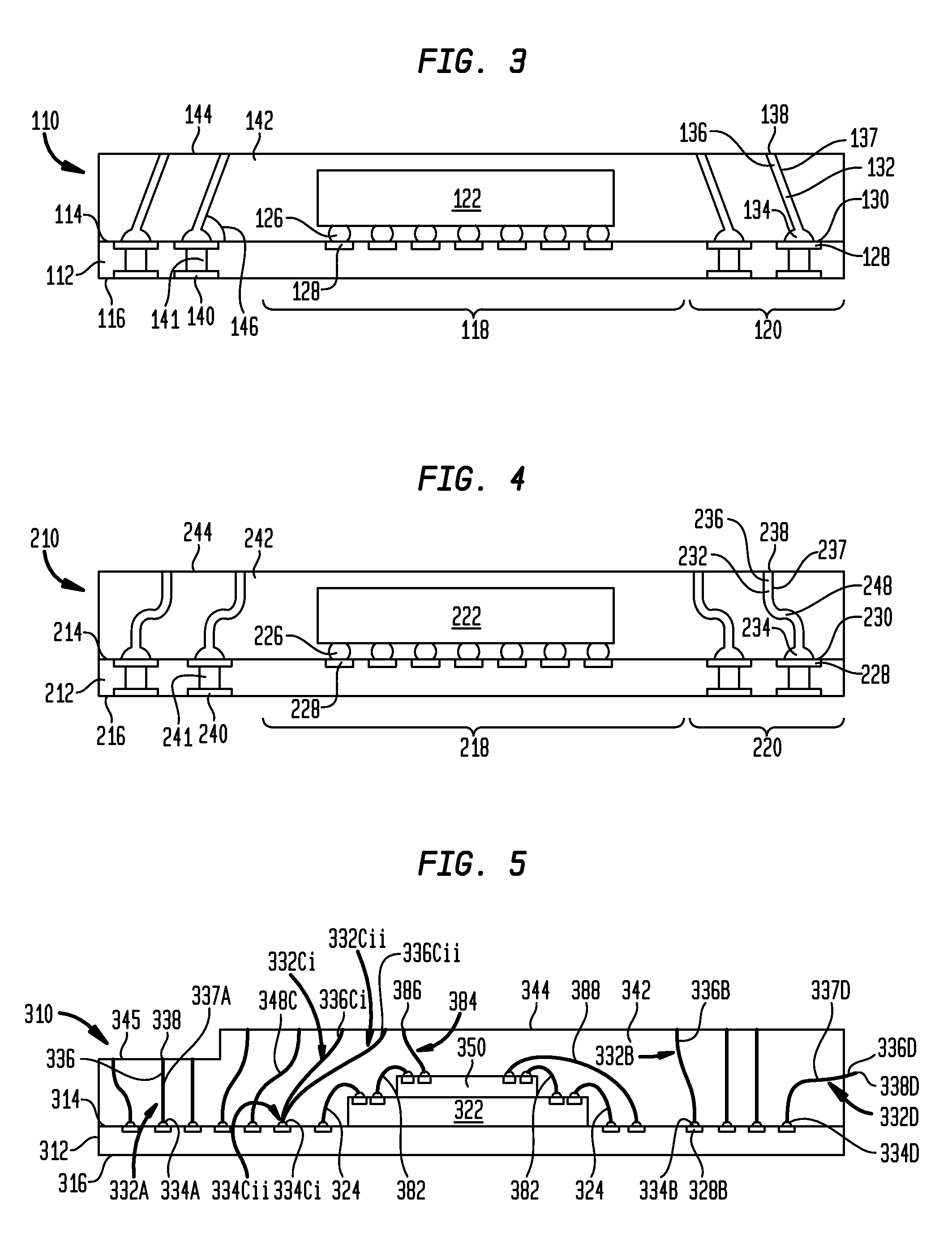

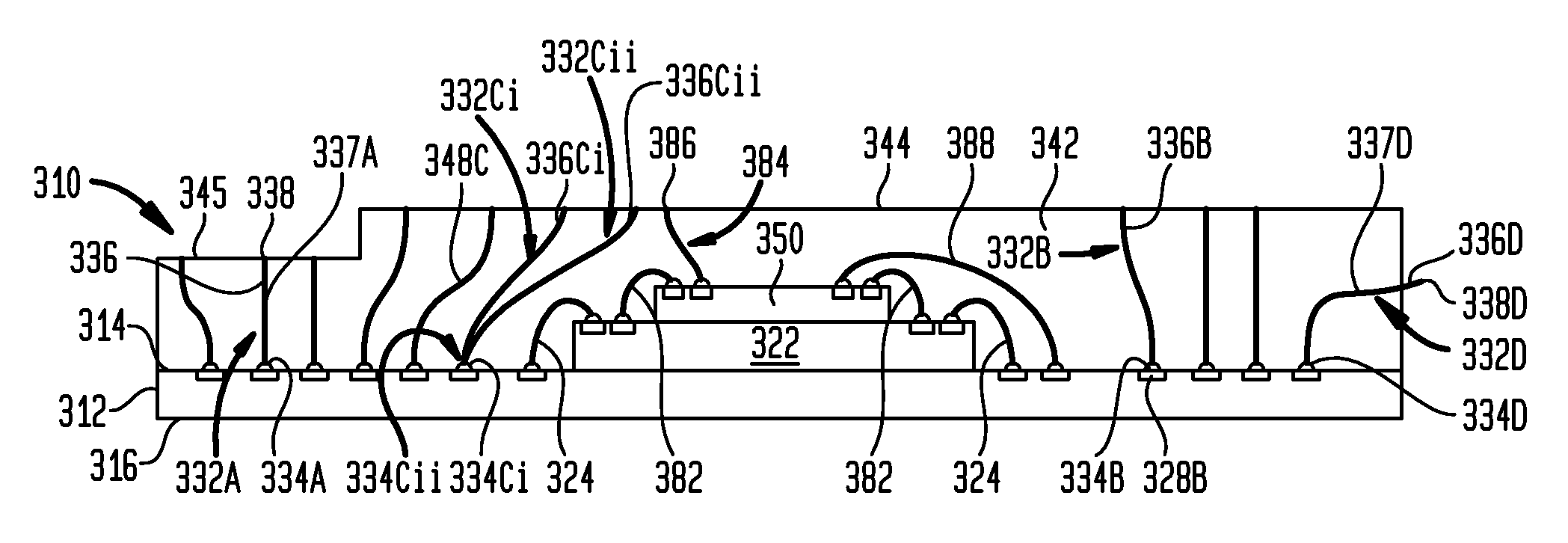

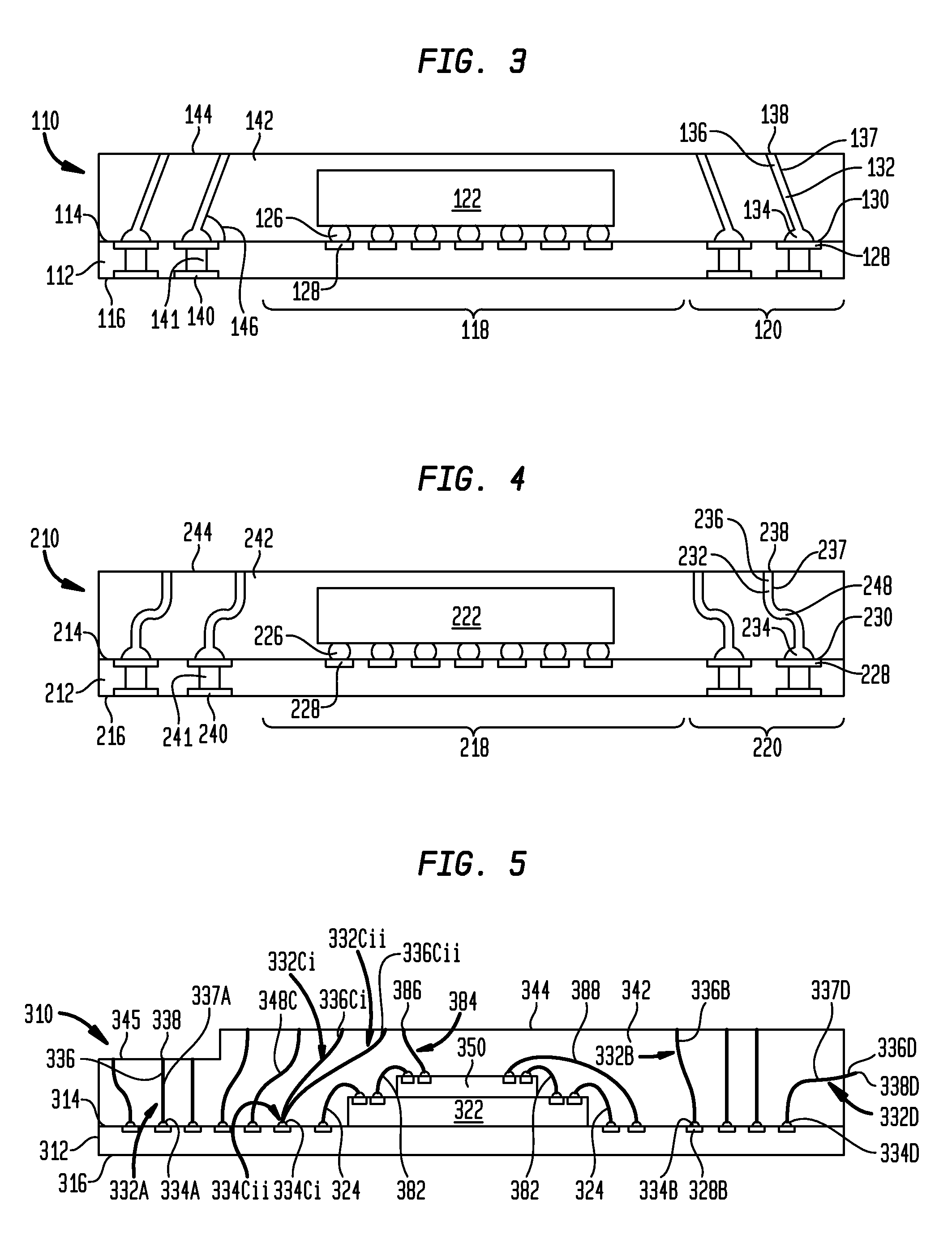

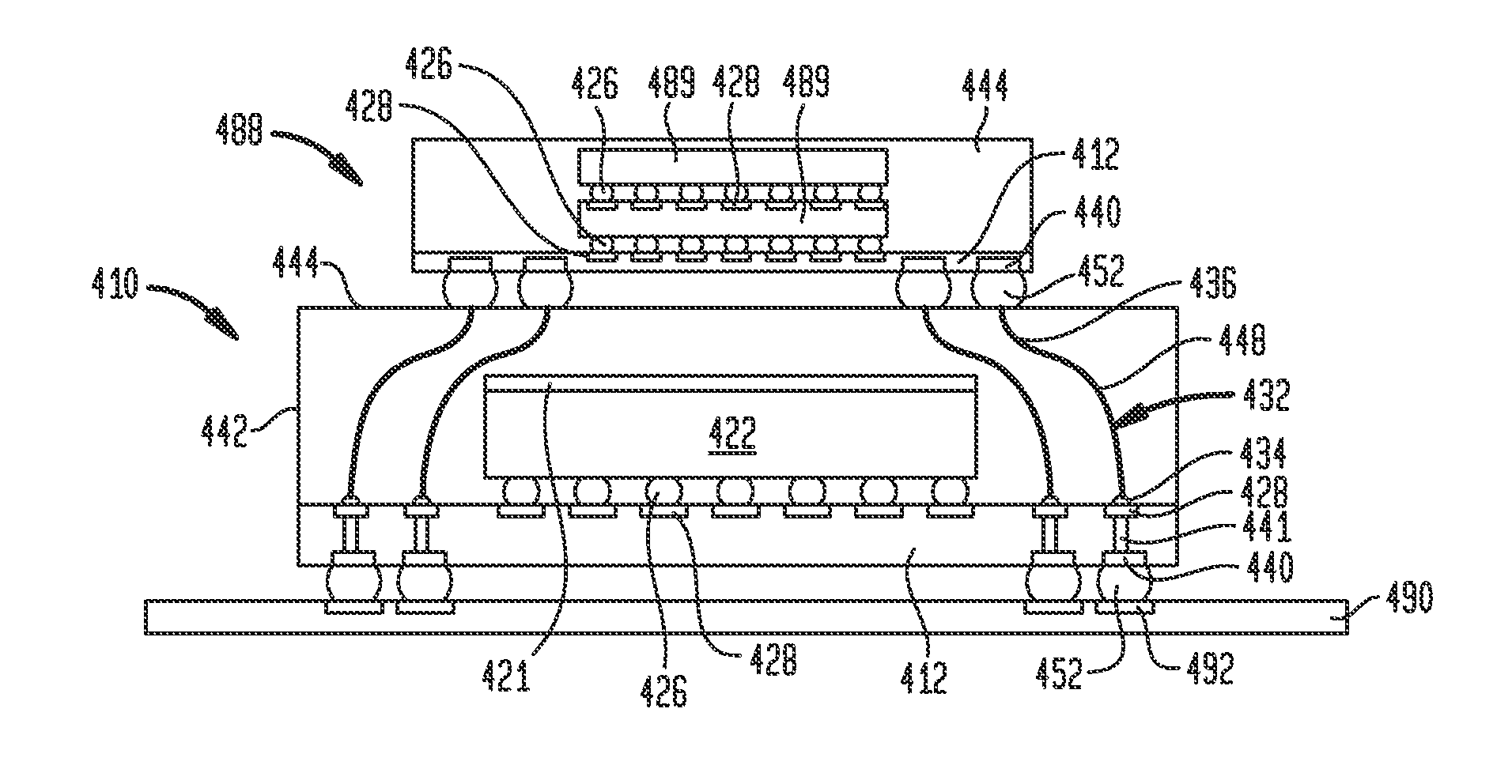

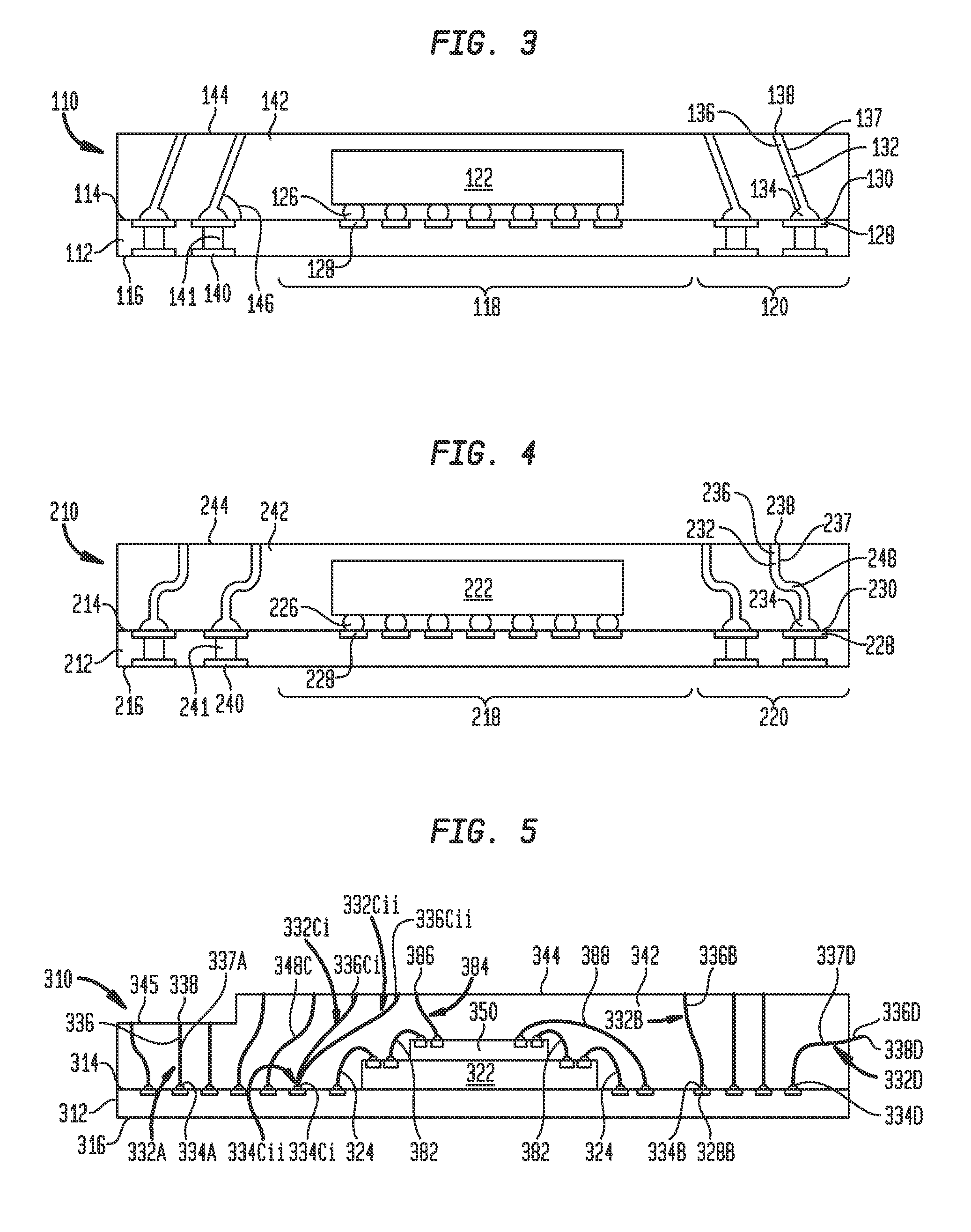

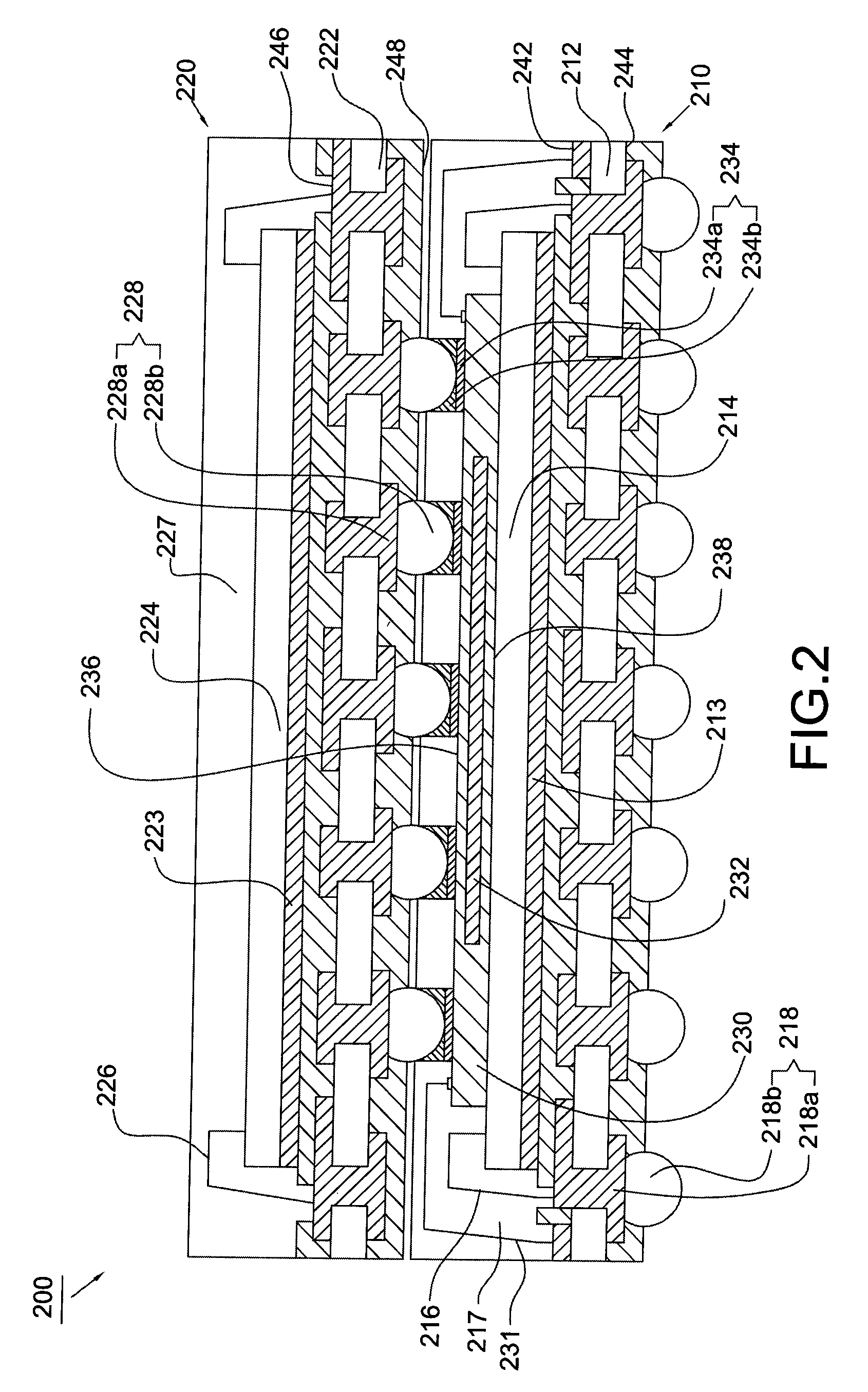

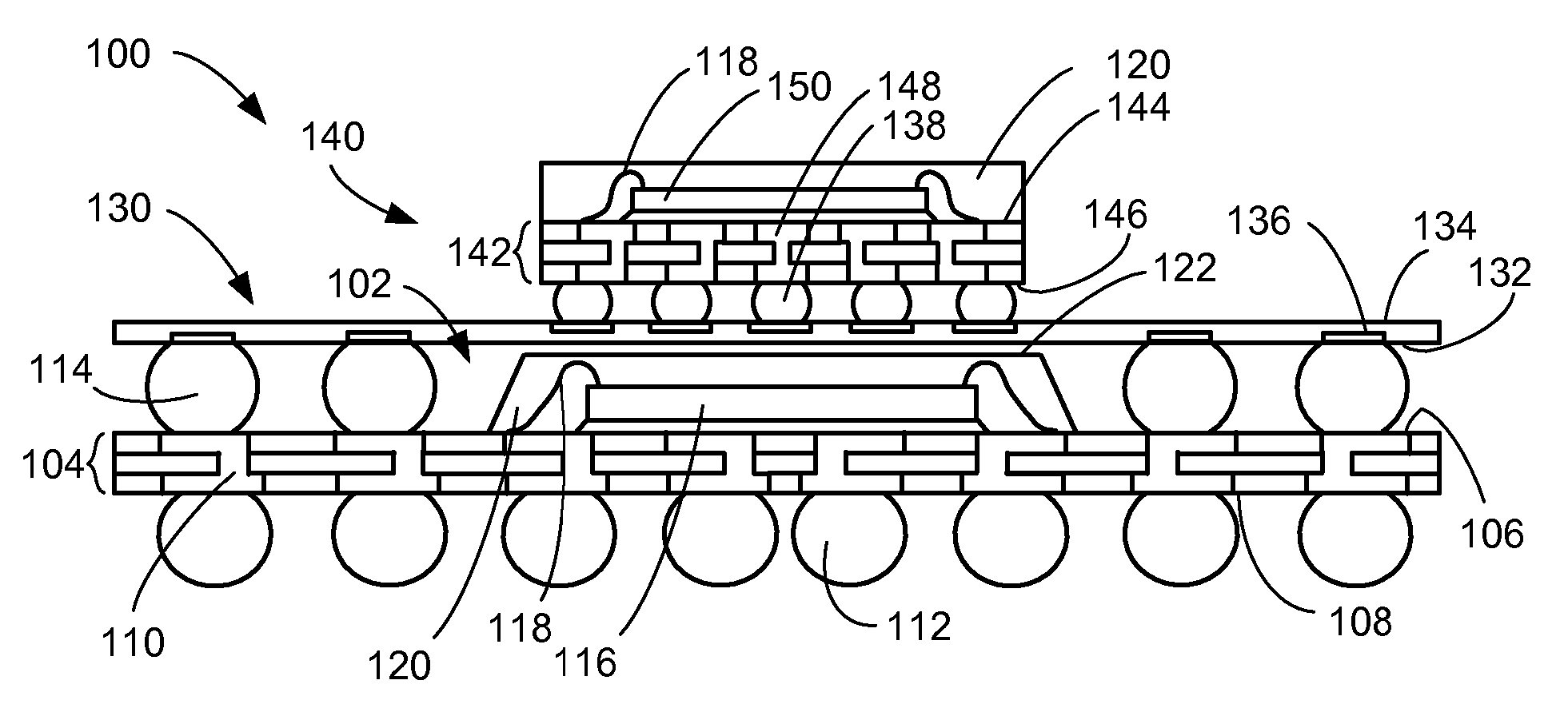

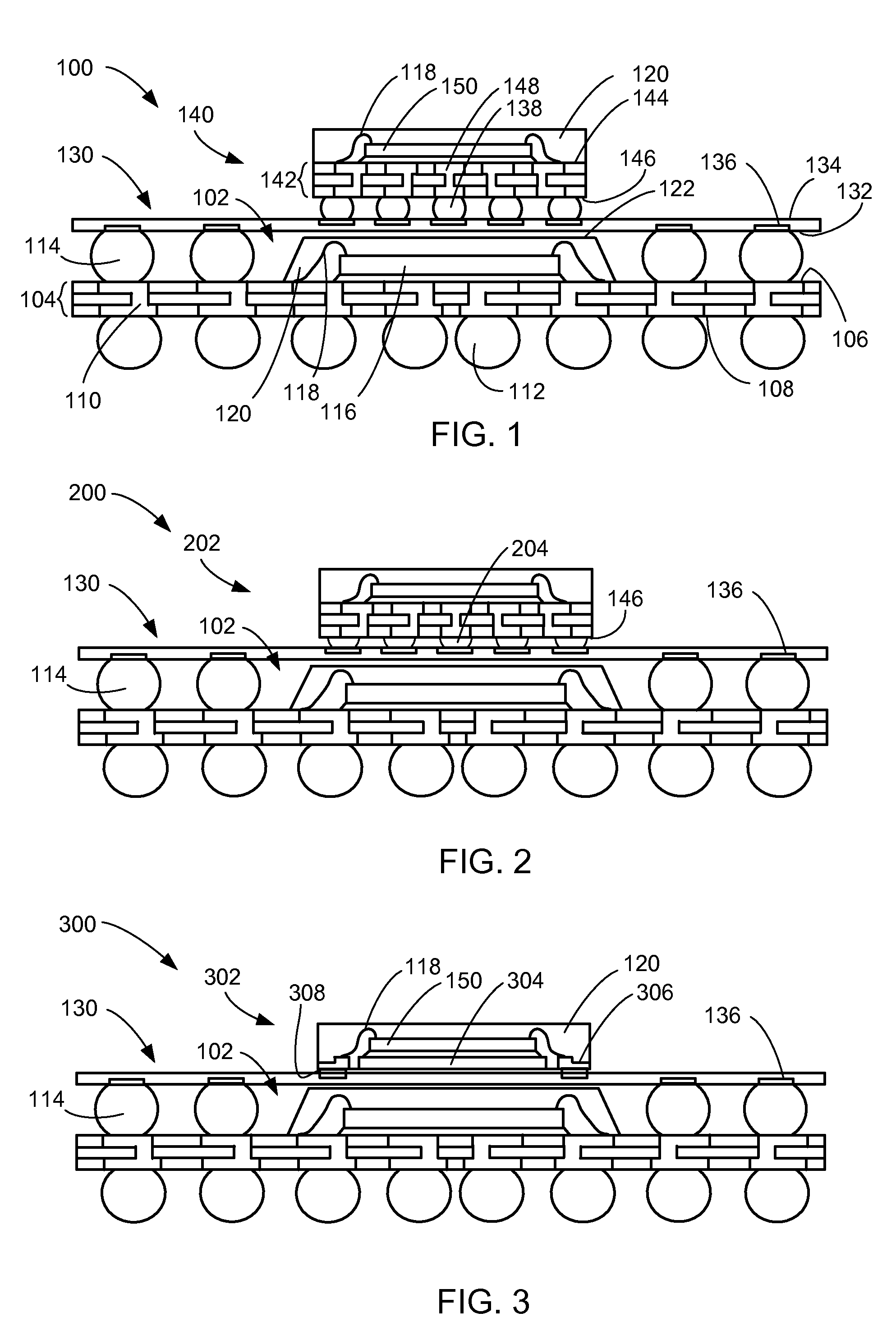

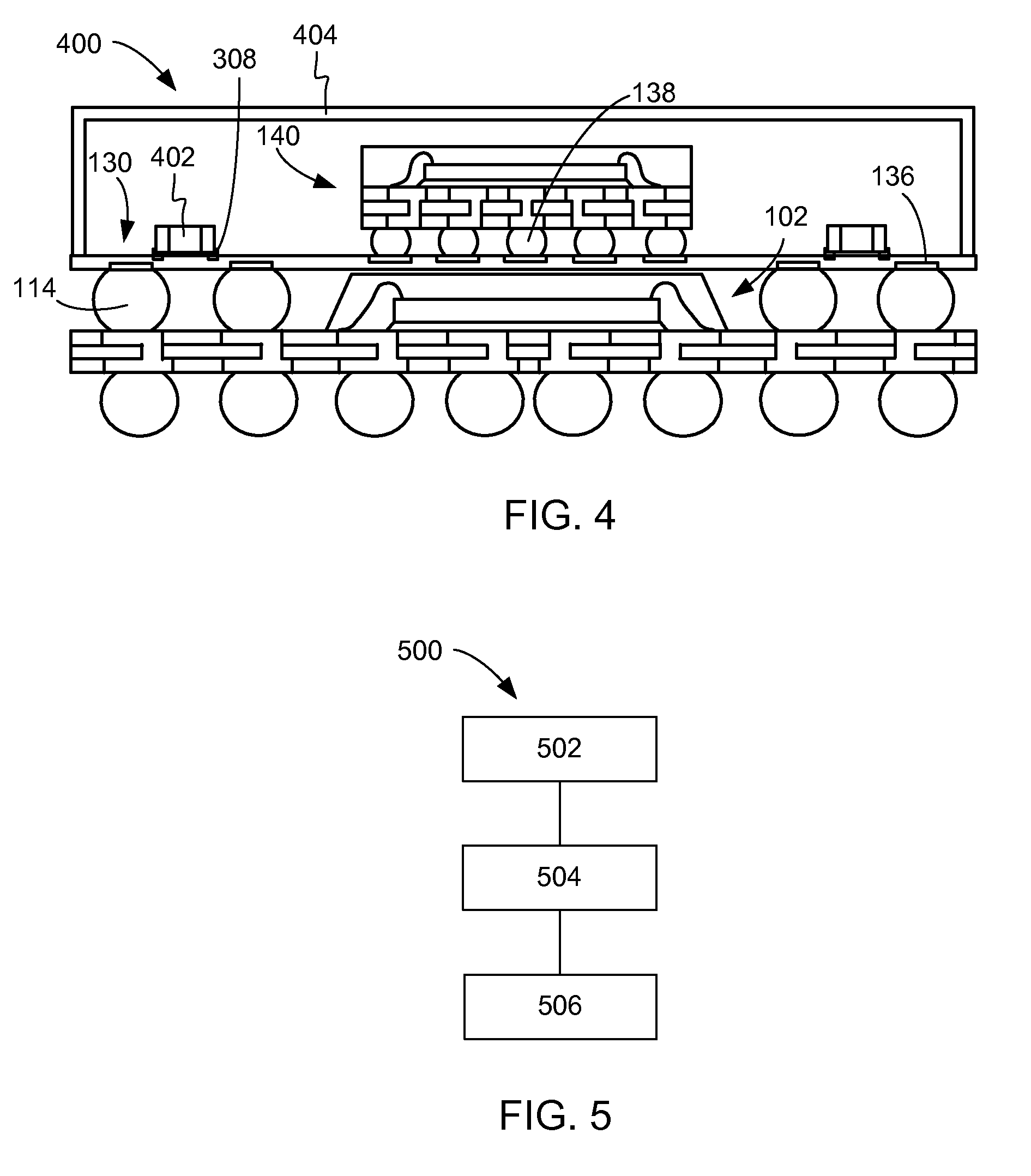

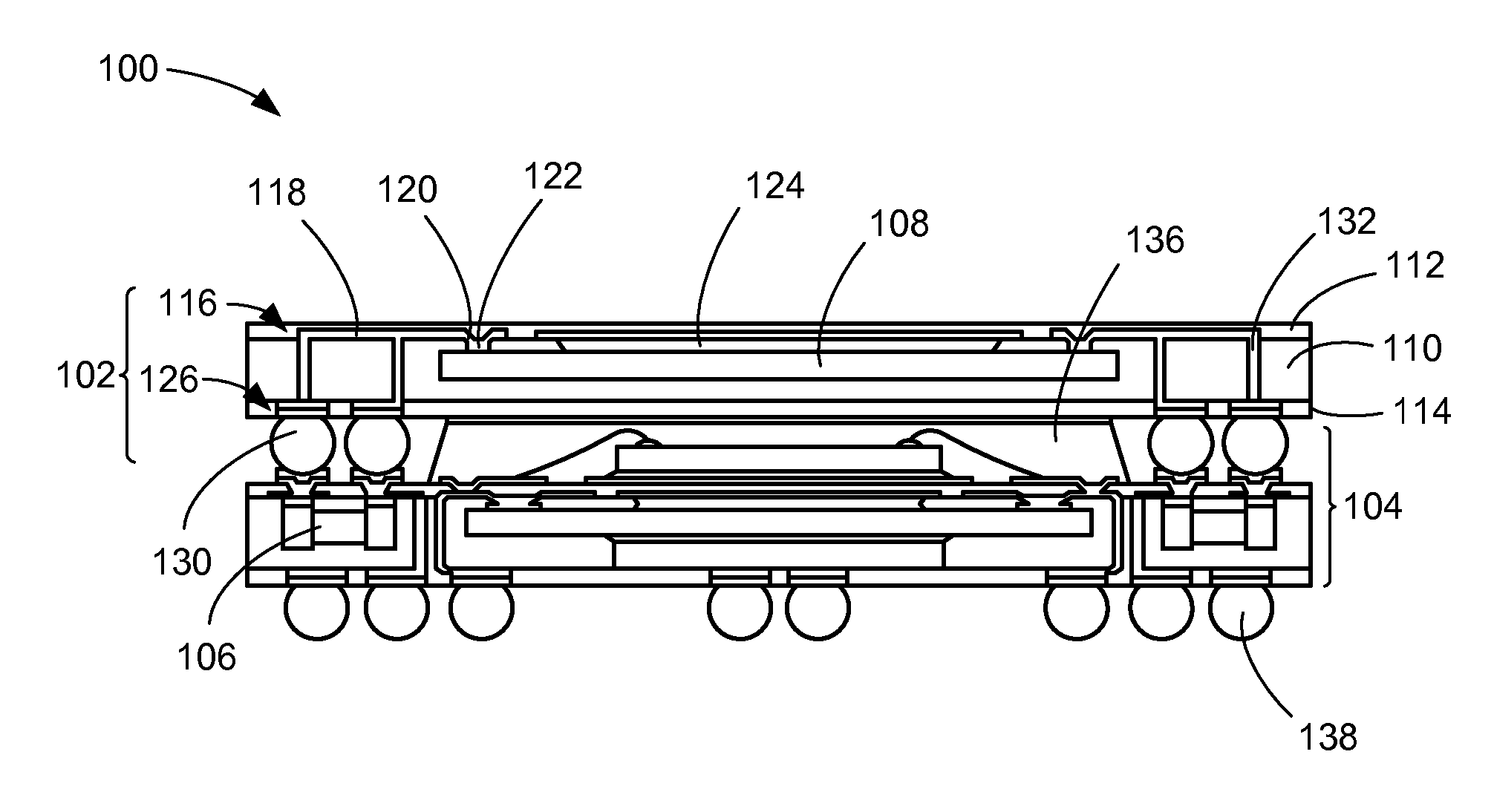

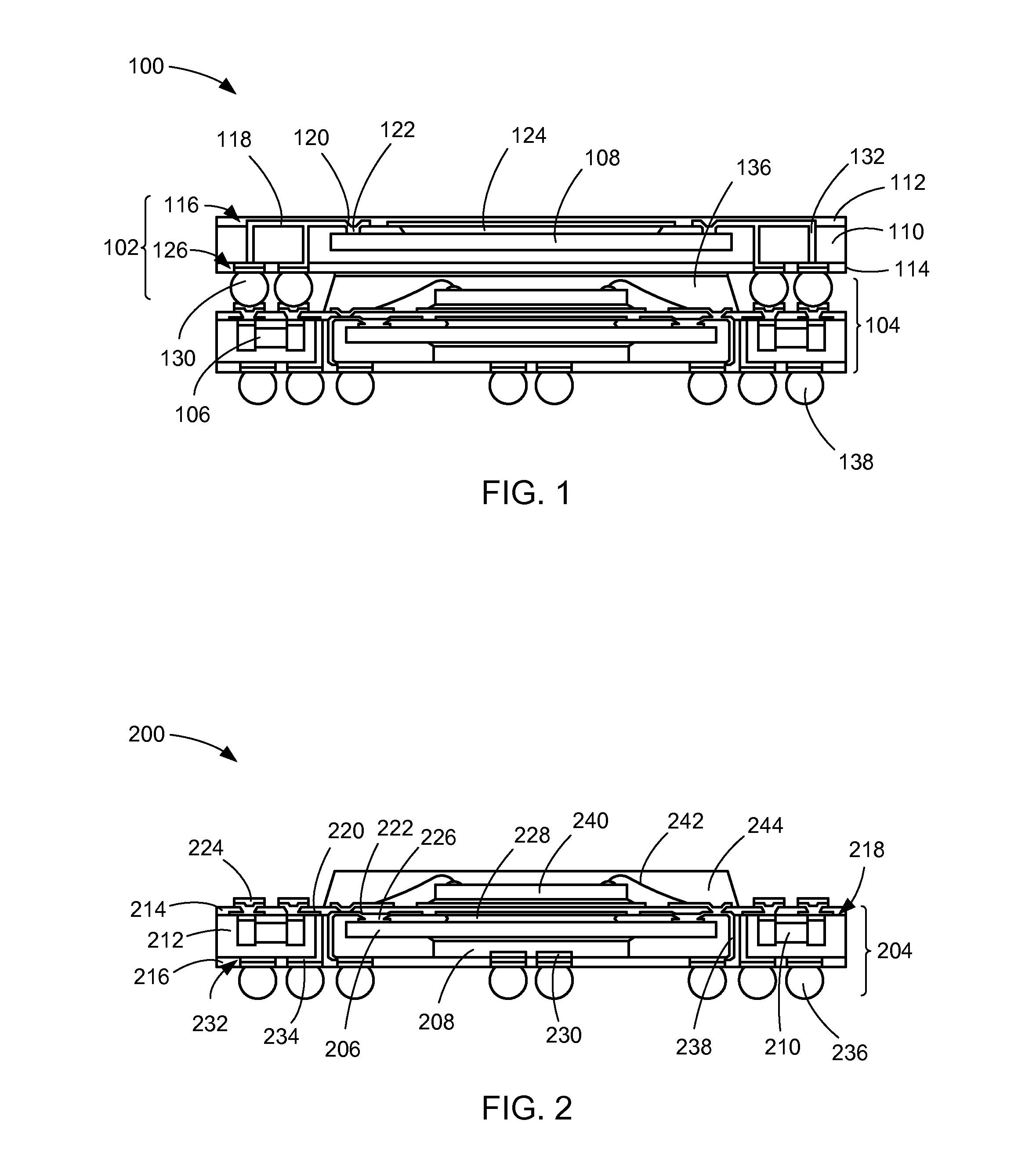

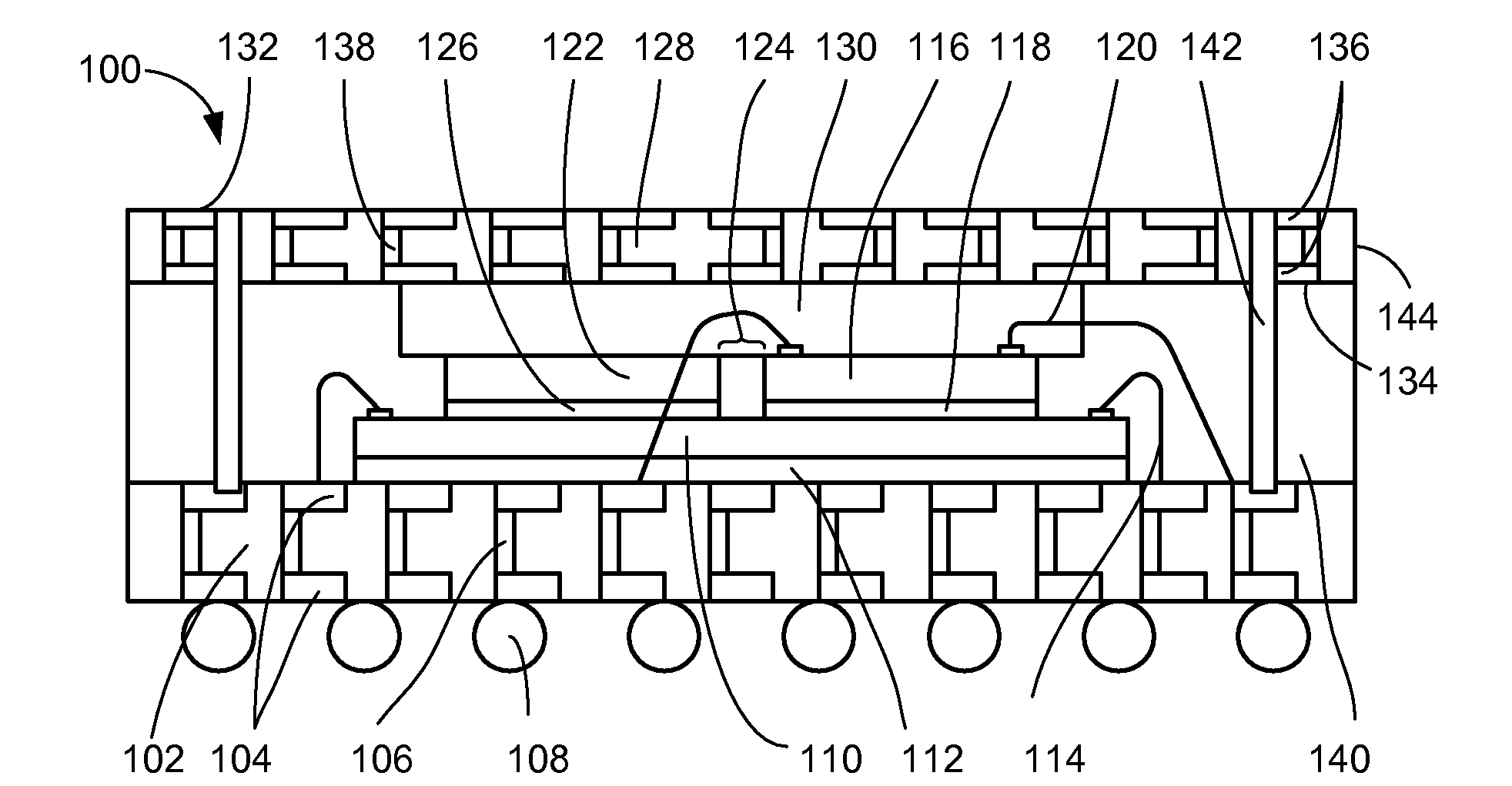

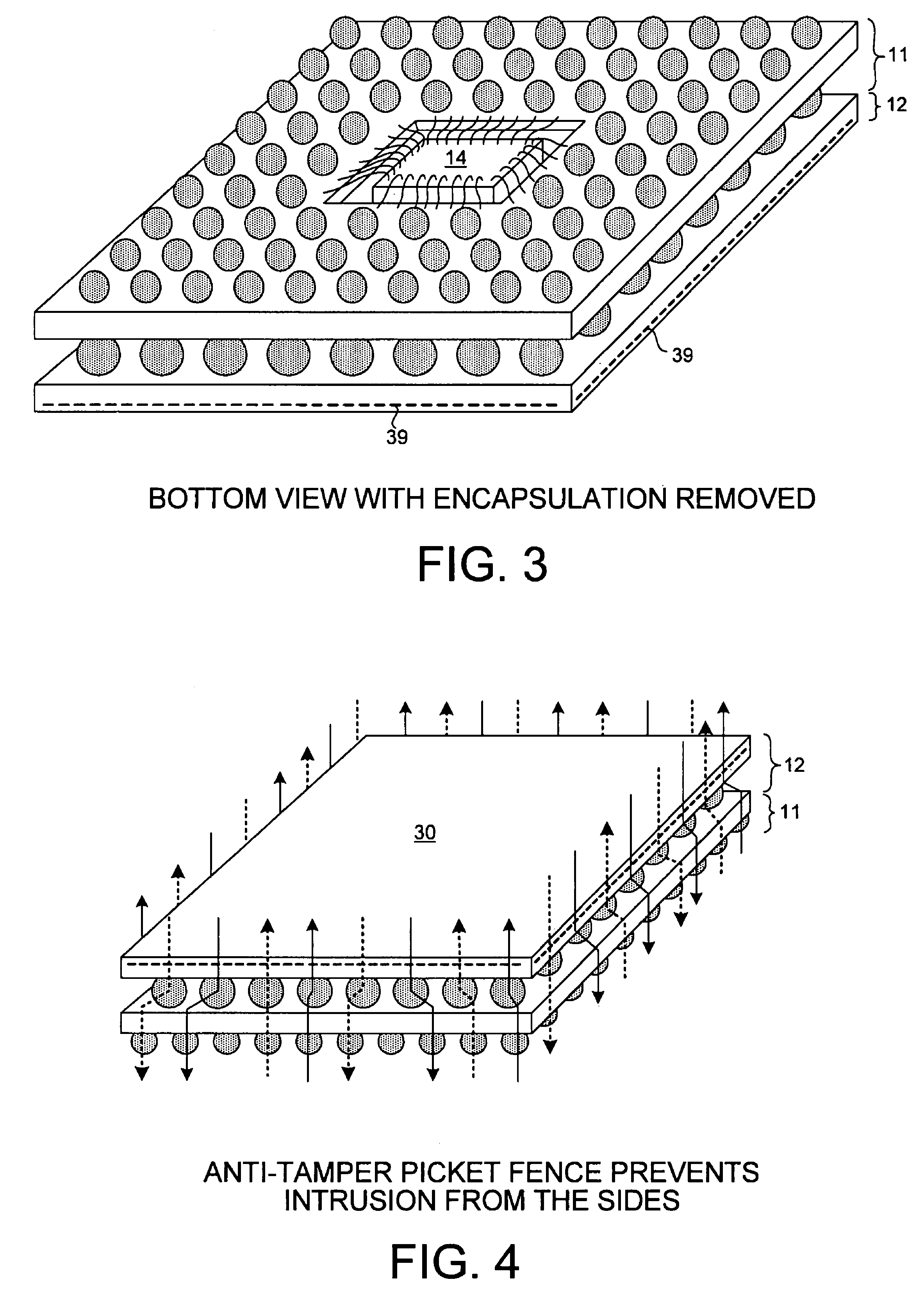

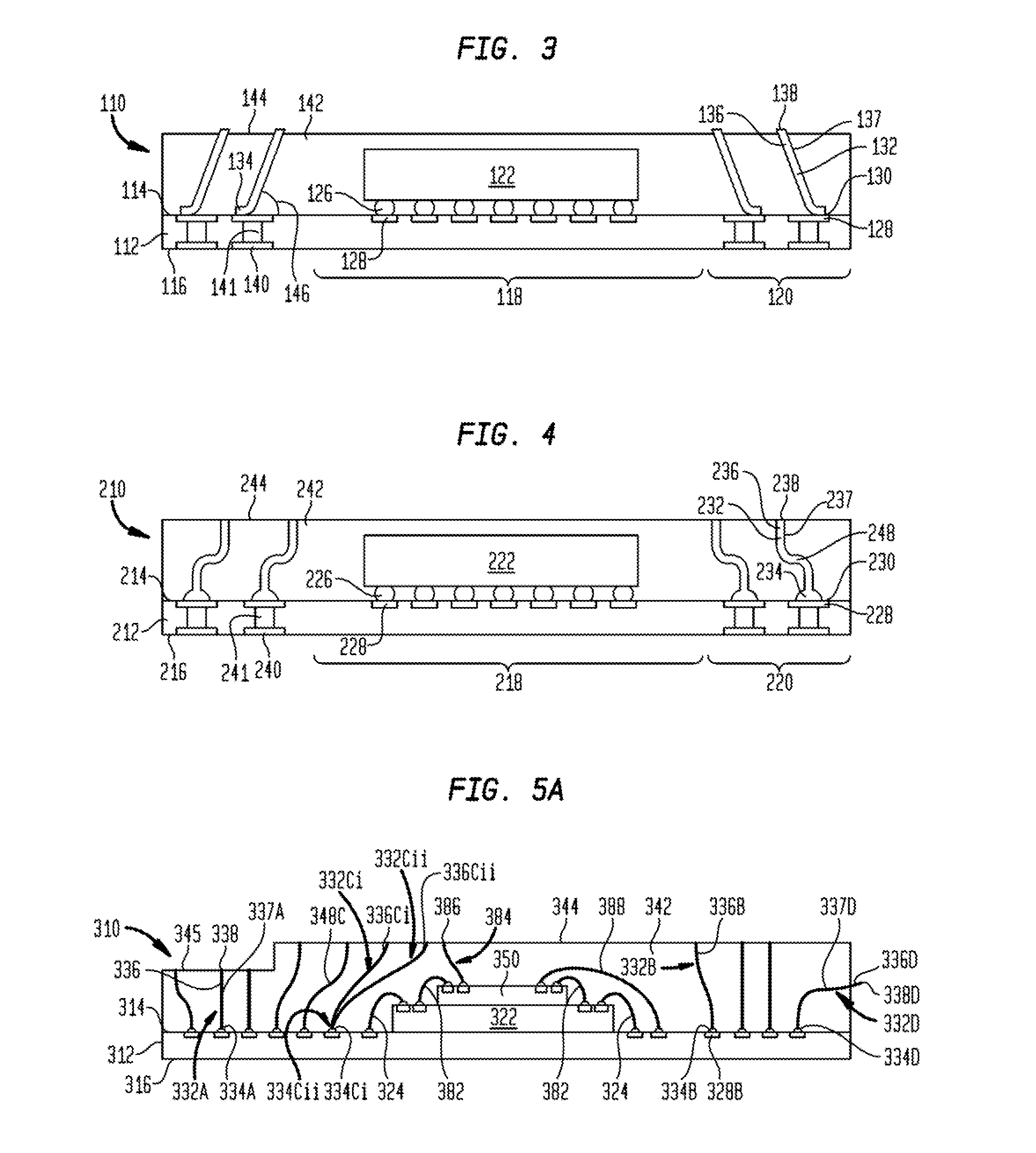

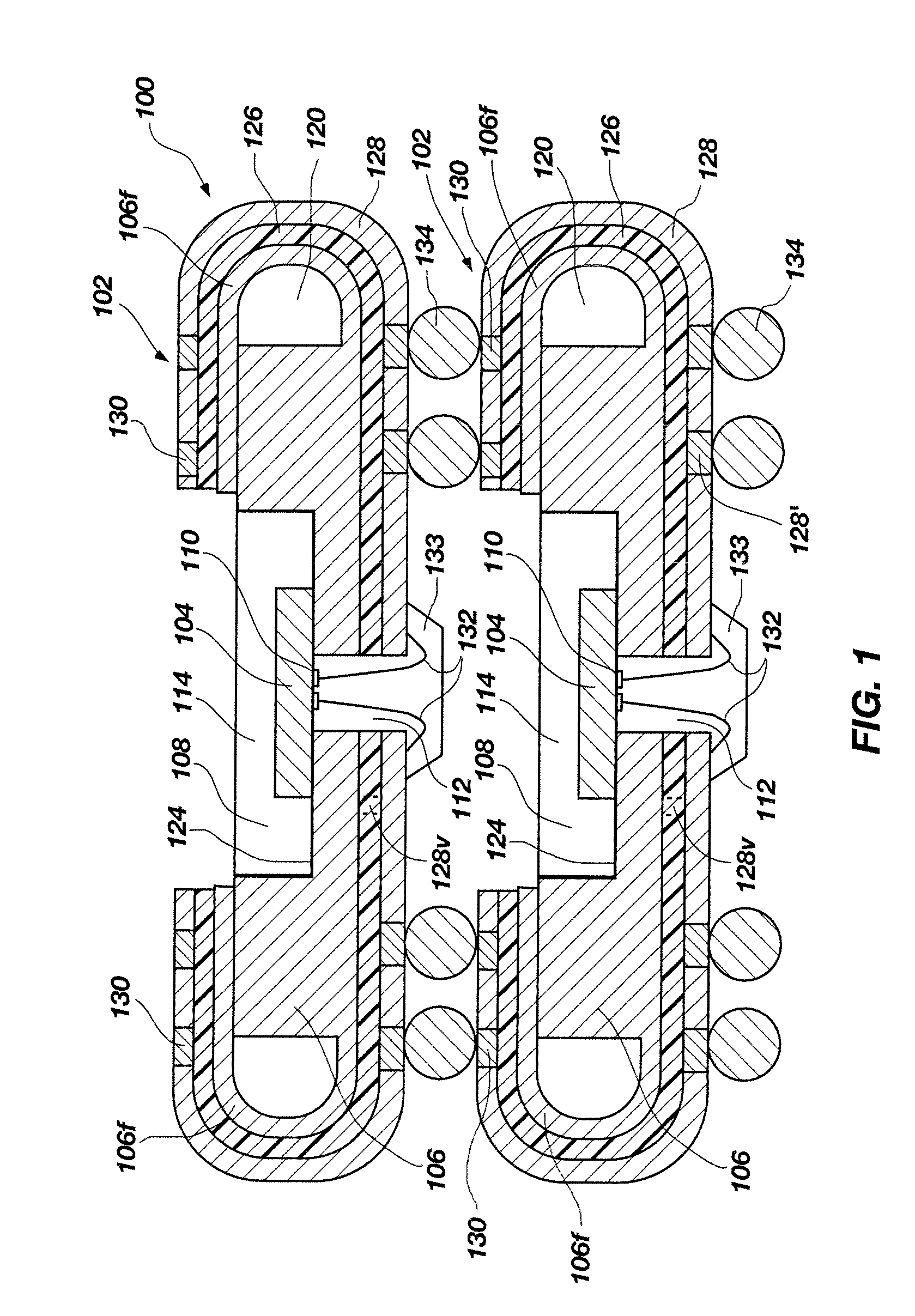

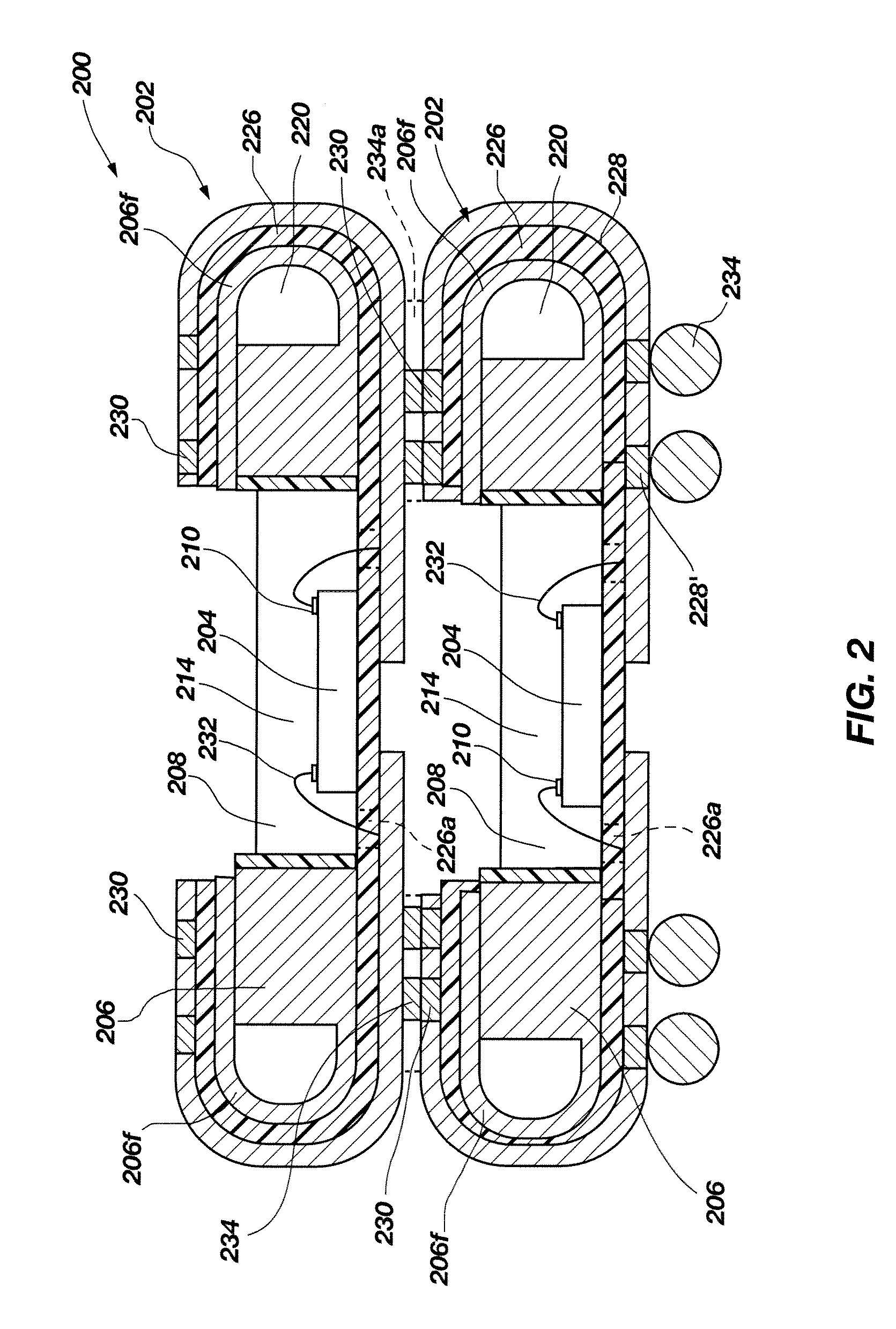

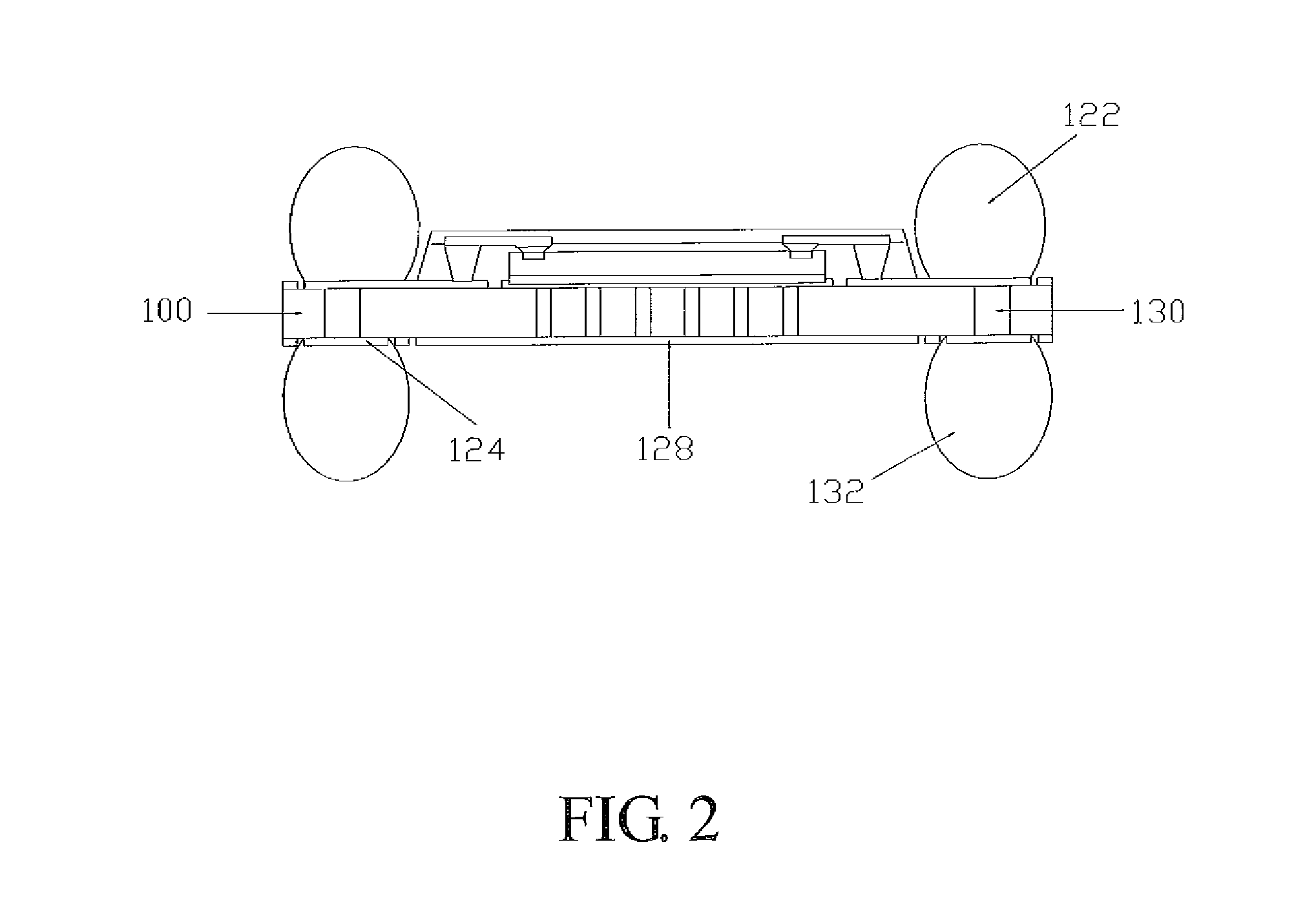

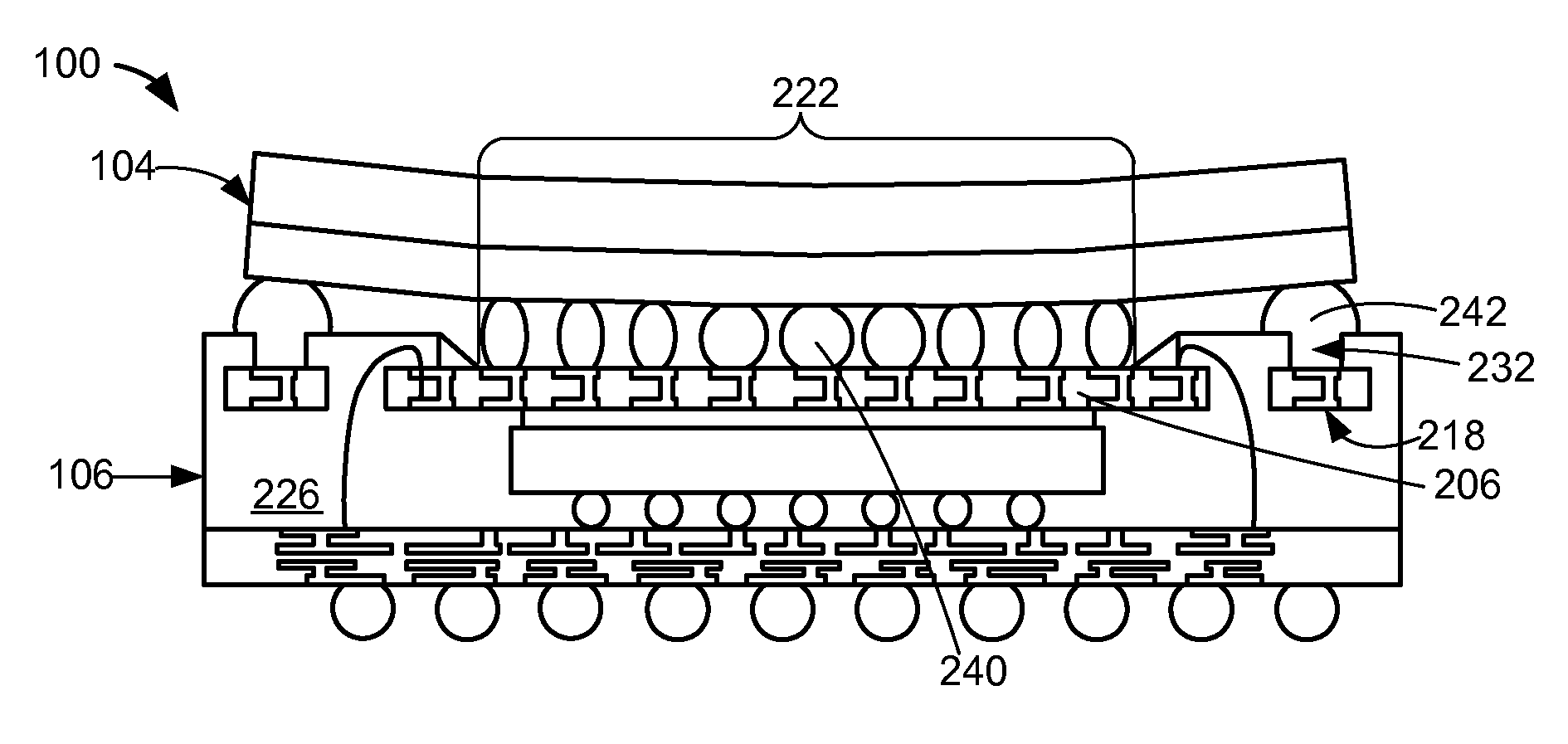

Package-on-package assembly with wire bonds to encapsulation surface

ActiveUS8618659B2Semiconductor/solid-state device detailsSolid-state devicesEdge surfaceLead bonding

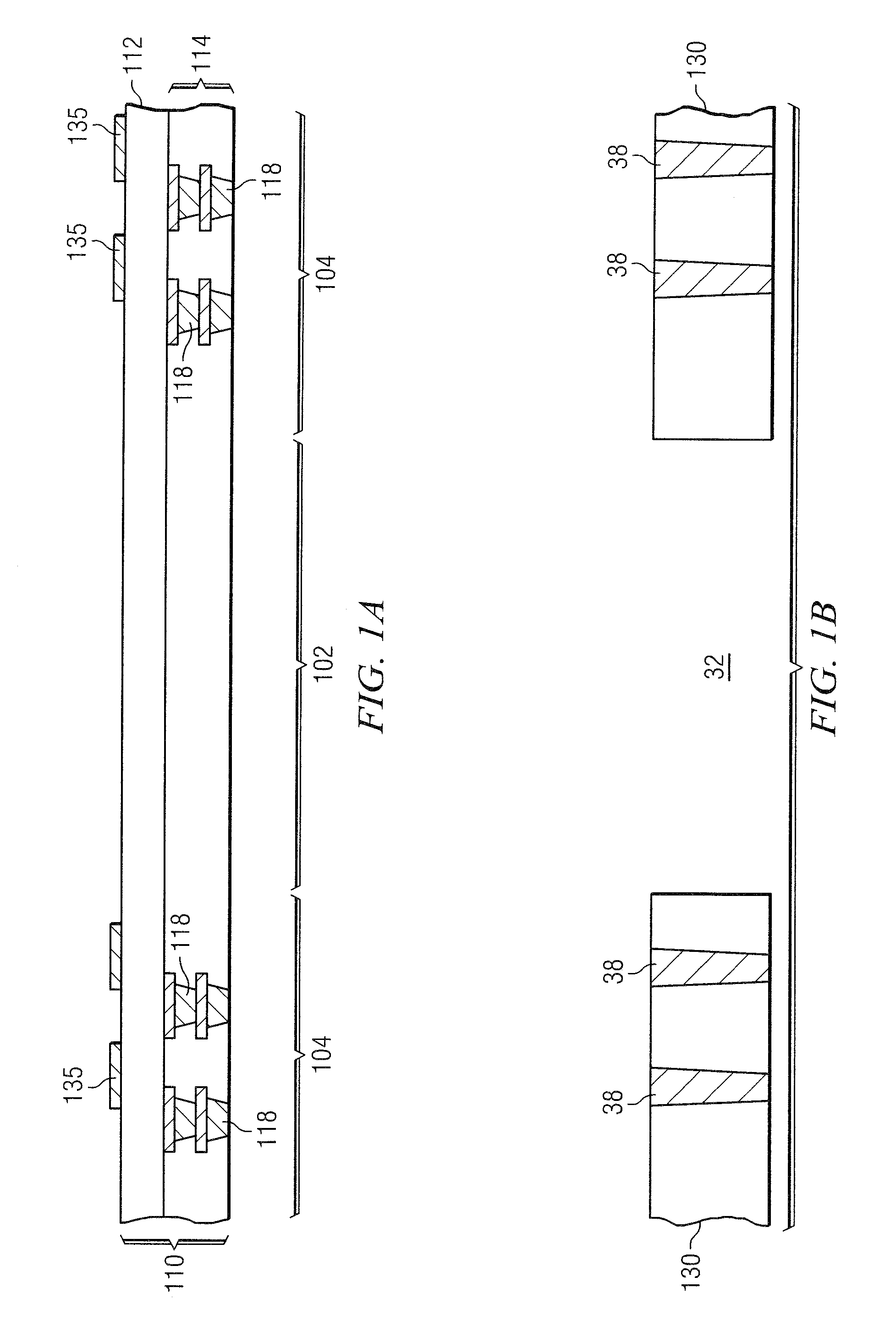

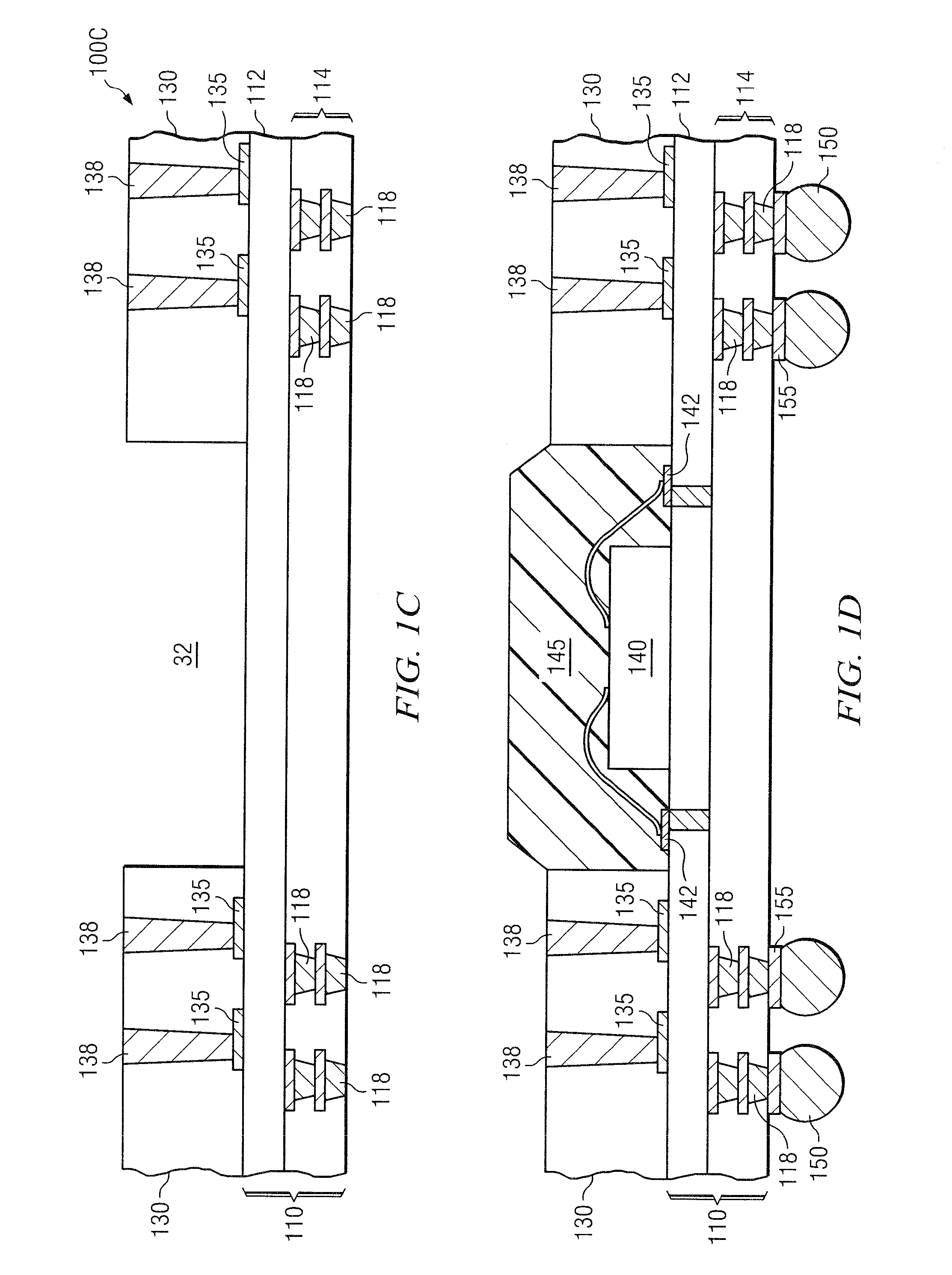

A microelectronic assembly includes a substrate having a first surface and a second surface remote from the first surface. A microelectronic element overlies the first surface and first electrically conductive elements are exposed at one of the first surface and the second surface. Some of the first conductive elements are electrically connected to the microelectronic element. Wire bonds have bases joined to the conductive elements and end surfaces remote from the substrate and the bases, each wire bond defining an edge surface extending between the base and the end surface. An encapsulation layer extends from the first surface and fills spaces between the wire bonds such that the wire bonds are separated by the encapsulation layer. Unencapsulated portions of the wire bonds are defined by at least portions of the end surfaces of the wire bonds that are uncovered by the encapsulation layer.

Owner:TESSERA LLC

Package-on-package assembly with wire bonds to encapsulation surface

ActiveUS20120280386A1Semiconductor/solid-state device detailsSolid-state devicesEdge surfaceLead bonding

A microelectronic assembly includes a substrate having a first surface and a second surface remote from the first surface. A microelectronic element overlies the first surface and first electrically conductive elements are exposed at one of the first surface and the second surface. Some of the first conductive elements are electrically connected to the microelectronic element. Wire bonds have bases joined to the conductive elements and end surfaces remote from the substrate and the bases, each wire bond defining an edge surface extending between the base and the end surface. An encapsulation layer extends from the first surface and fills spaces between the wire bonds such that the wire bonds are separated by the encapsulation layer. Unencapsulated portions of the wire bonds are defined by at least portions of the end surfaces of the wire bonds that are uncovered by the encapsulation layer.

Owner:TESSERA LLC

Method for package-on-package assembly with wire bonds to encapsulation surface

ActiveUS8372741B1Less thicknessSemiconductor/solid-state device detailsSolid-state devicesEdge surfaceEngineering

A microelectronic assembly includes a substrate having a first and second opposed surfaces. A microelectronic element overlies the first surface and first electrically conductive elements can be exposed at at least one of the first surface or second surfaces. Some of the first conductive elements are electrically connected to the microelectronic element. Wire bonds have bases joined to the conductive elements and end surfaces remote from the substrate and the bases, each wire bond defining an edge surface extending between the base and the end surface. An encapsulation layer can extend from the first surface and fill spaces between the wire bonds, such that the wire bonds can be separated by the encapsulation layer. Unencapsulated portions of the wire bonds are defined by at least portions of the end surfaces of the wire bonds that are uncovered by the encapsulation layer.

Owner:INVENSAS CORP

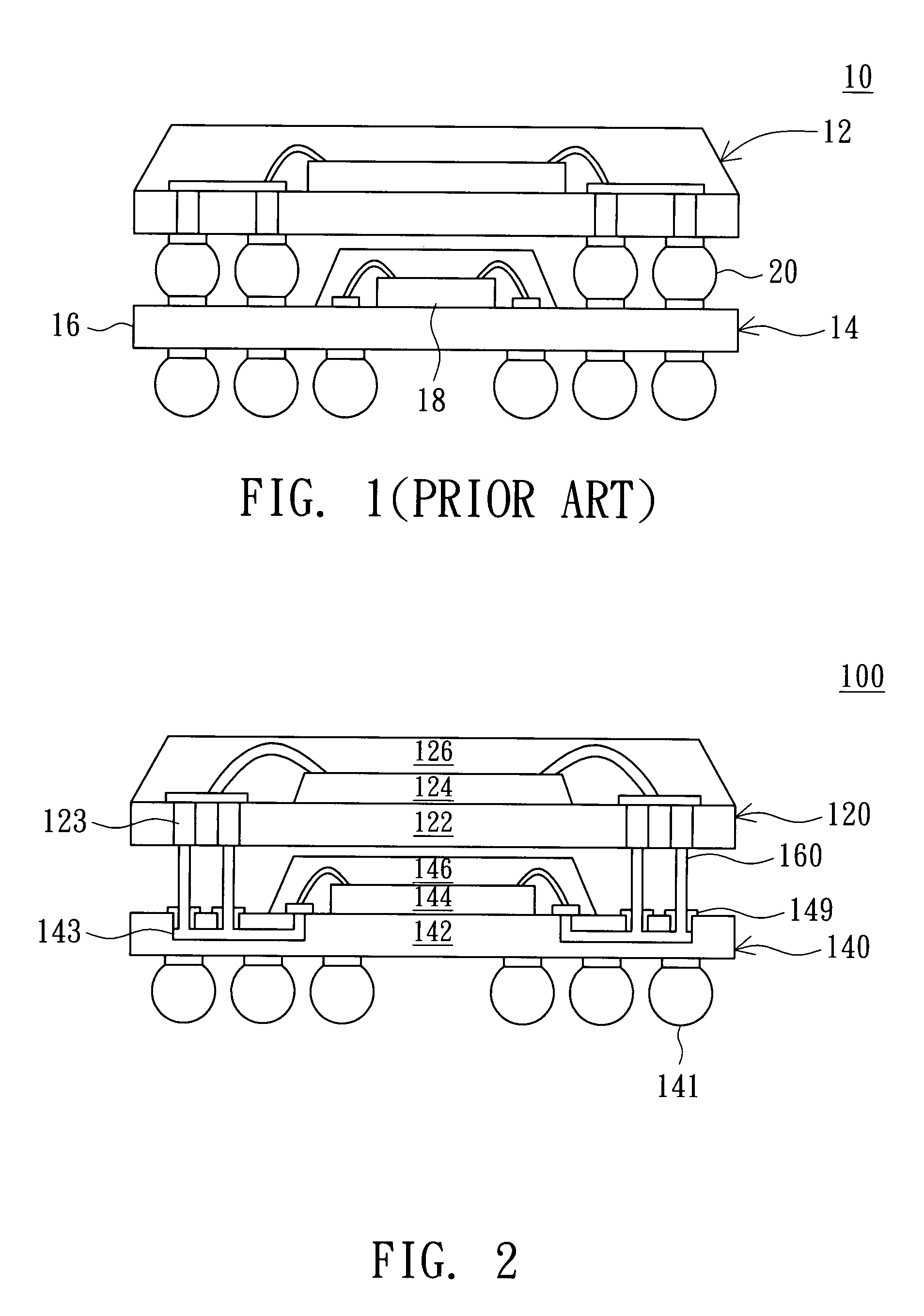

Structure of package on package and method for fabricating the same

ActiveUS7550836B2Increase spacingSemiconductor/solid-state device detailsSolid-state devicesEngineeringPackage on package

A structure of a package on package and a method for fabricating the same are provided. The structure of the package on package includes a first package, a second package and a plurality of pins. The first package includes a first substrate and a first chip disposed thereon. The second package includes a second substrate and a second chip disposed thereon. The second package is disposed under the first package. The second package includes a plurality of holes. The pins are disposed on the first package and inserted to the holes so as to electrically connect the first package and the second package.

Owner:ADVANCED SEMICON ENG INC

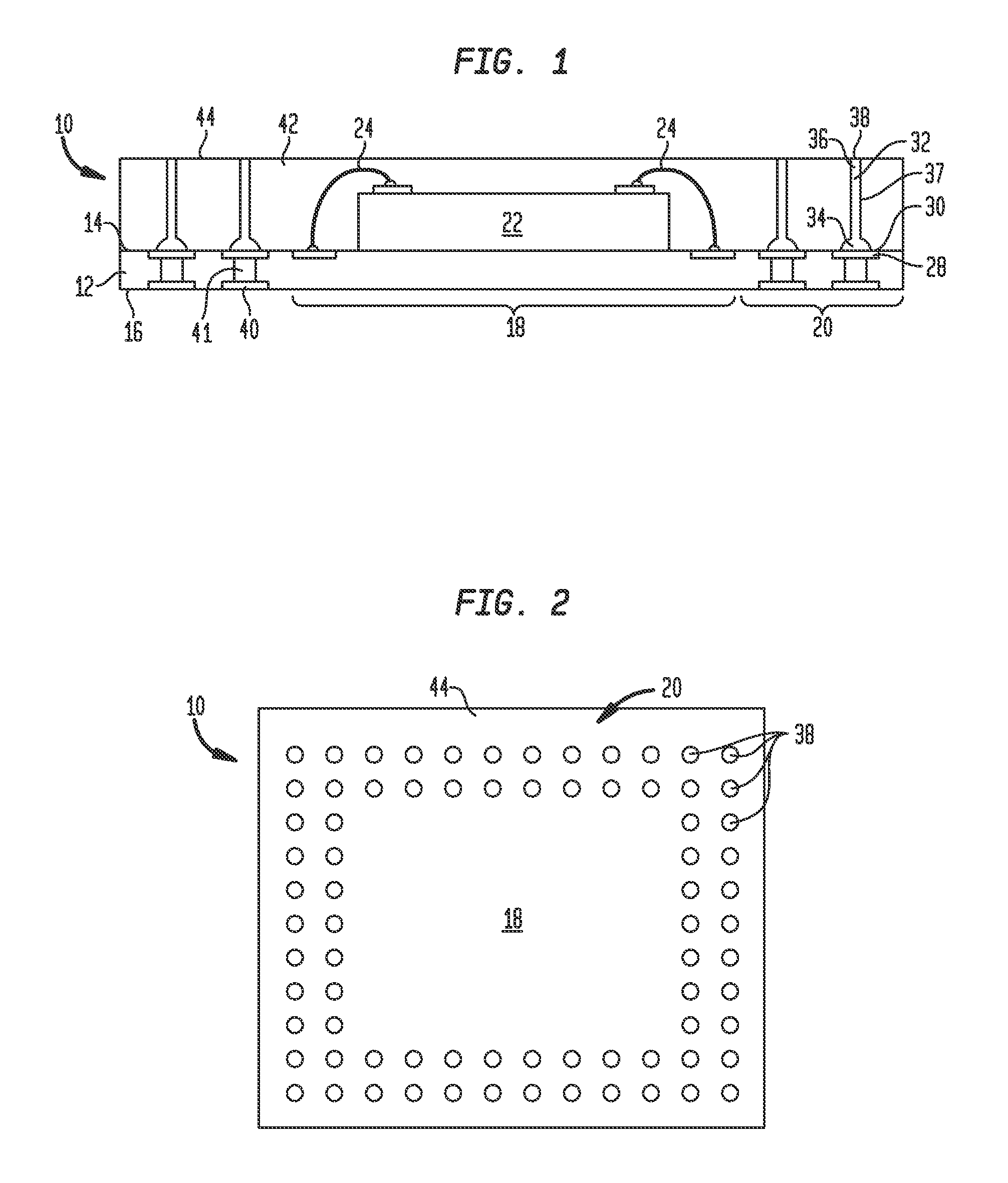

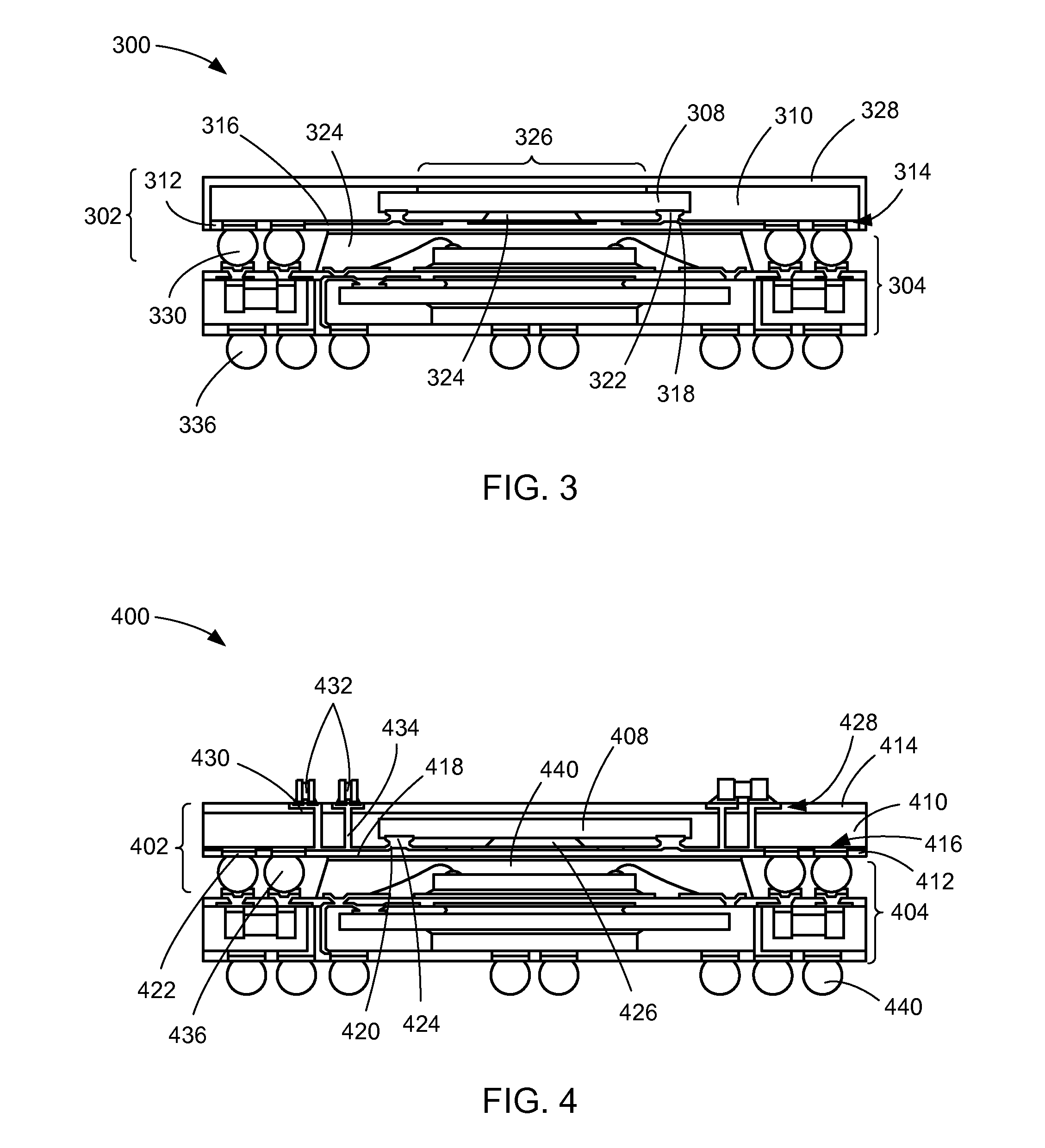

Package-on-package semiconductor assembly

ActiveUS7675152B2Improve robustnessReduce warpageSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

Disclosed are methods and devices for providing improved semiconductor packages and POP IC assemblies using the improved packages with reduced warping. According to disclosed embodiments of the inventions, a packaged semiconductor device for use in a POP assembly includes an encapsulated region generally defined by the substrate surface. The encapsulant is provided with contact apertures permitting external communication with contacts on the substrate and coupled to an encapsulated chip. Preferred embodiments of the invention are described in which the contact aperture sidewalls are angled within the range of approximately 10-30 degrees or more from vertical and in which the contact aperture is provided a gas release channel to permit gas to escape during reflow.

Owner:TEXAS INSTR INC

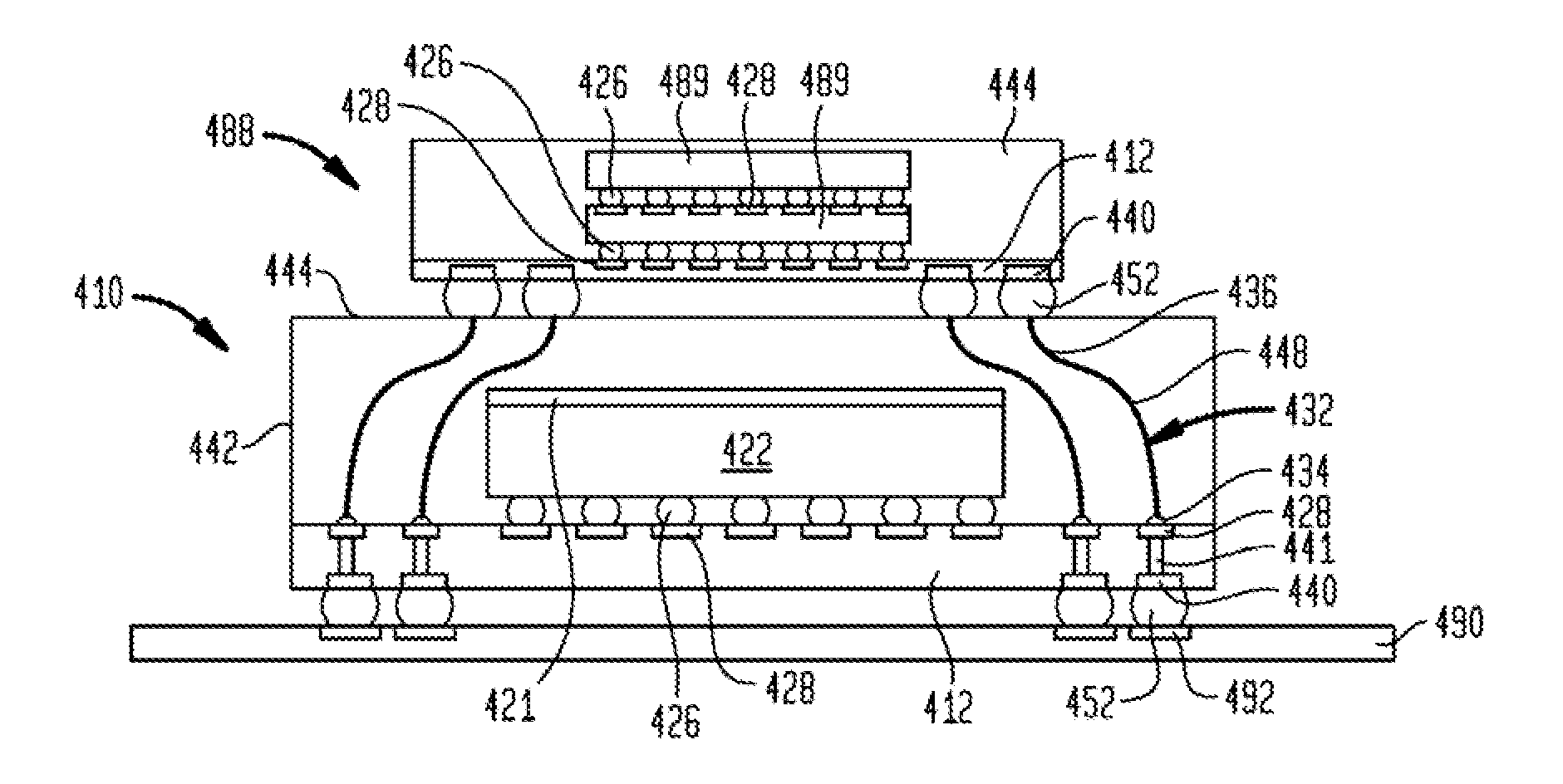

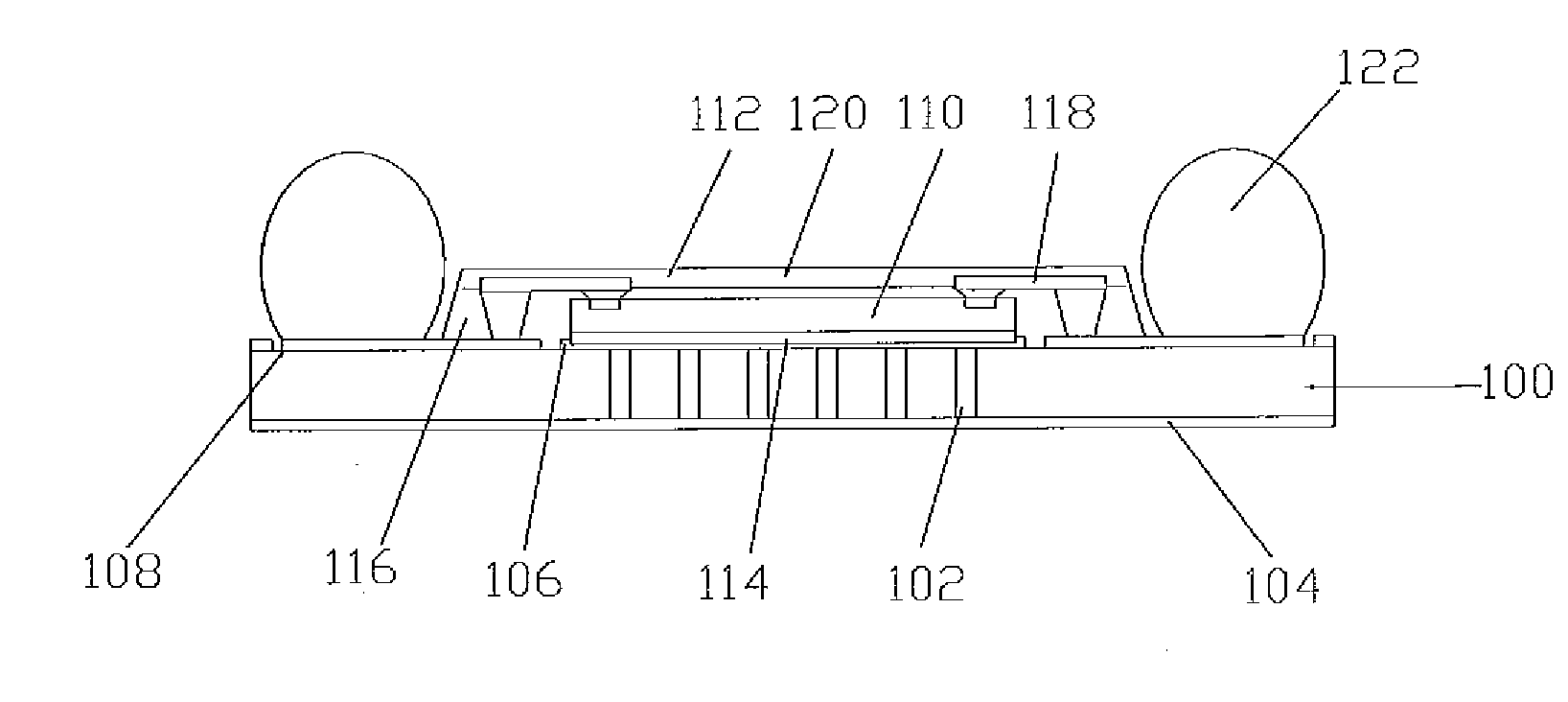

Package-on-package device, semiconductor package and method for manufacturing the same

ActiveUS20100133675A1Many functionsSemiconductor/solid-state device detailsSolid-state devicesInterposerSemiconductor package

A semiconductor package includes a substrate, a chip, an interposer and a molding compound. The chip is electrically connected to the upper surface of the substrate. The interposer is disposed on the chip, and electrically connected to the upper surface of the substrate. The interposer includes an embedded component and a plurality of electric contacts, wherein the embedded component is located between the upper and lower surfaces of the interposer, and the electric contacts are located on the upper surface of the interposer. The molding compound seals the chip and covers the upper surface of the substrate and the lower surface of the interposer.

Owner:ADVANCED SEMICON ENG INC

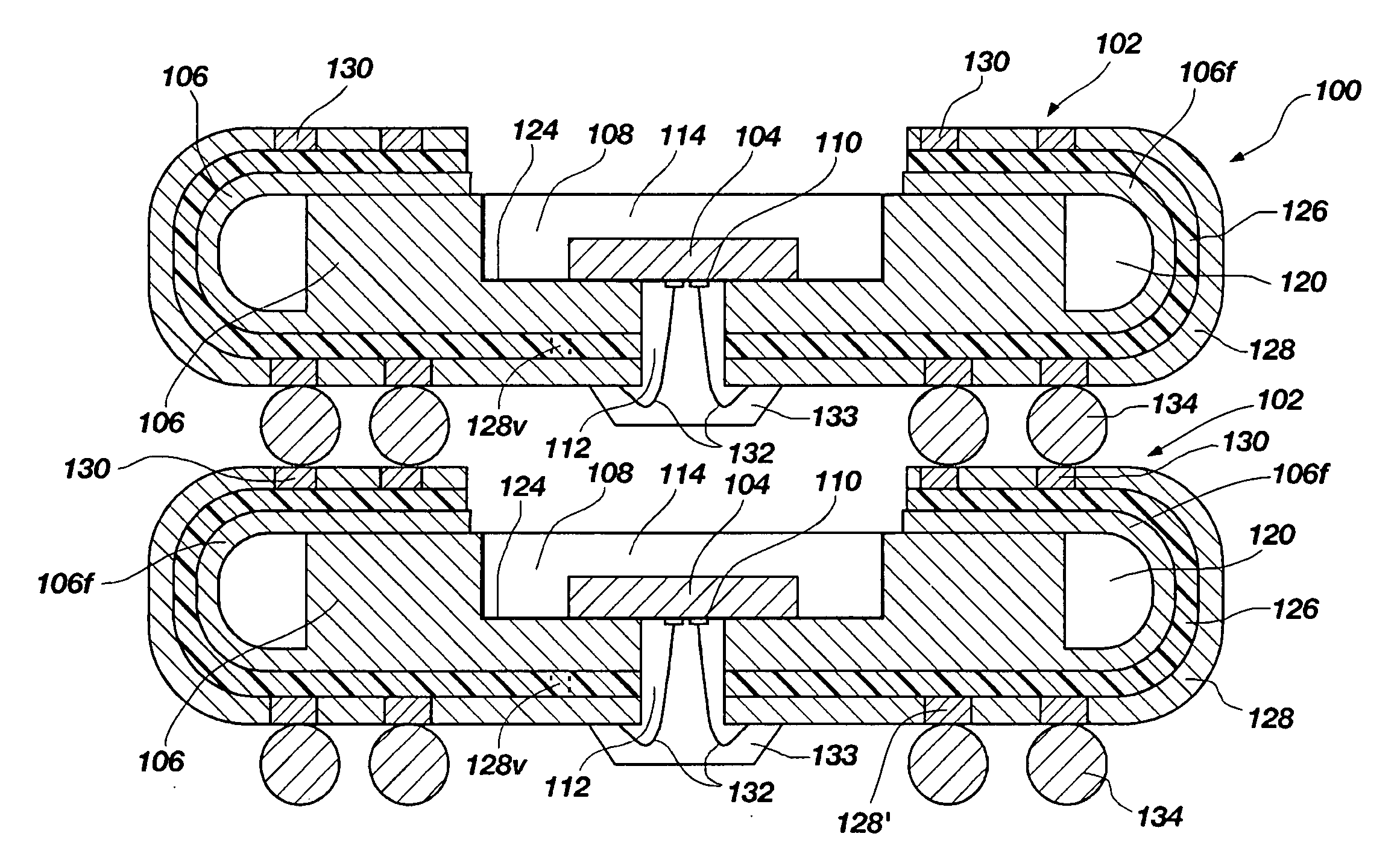

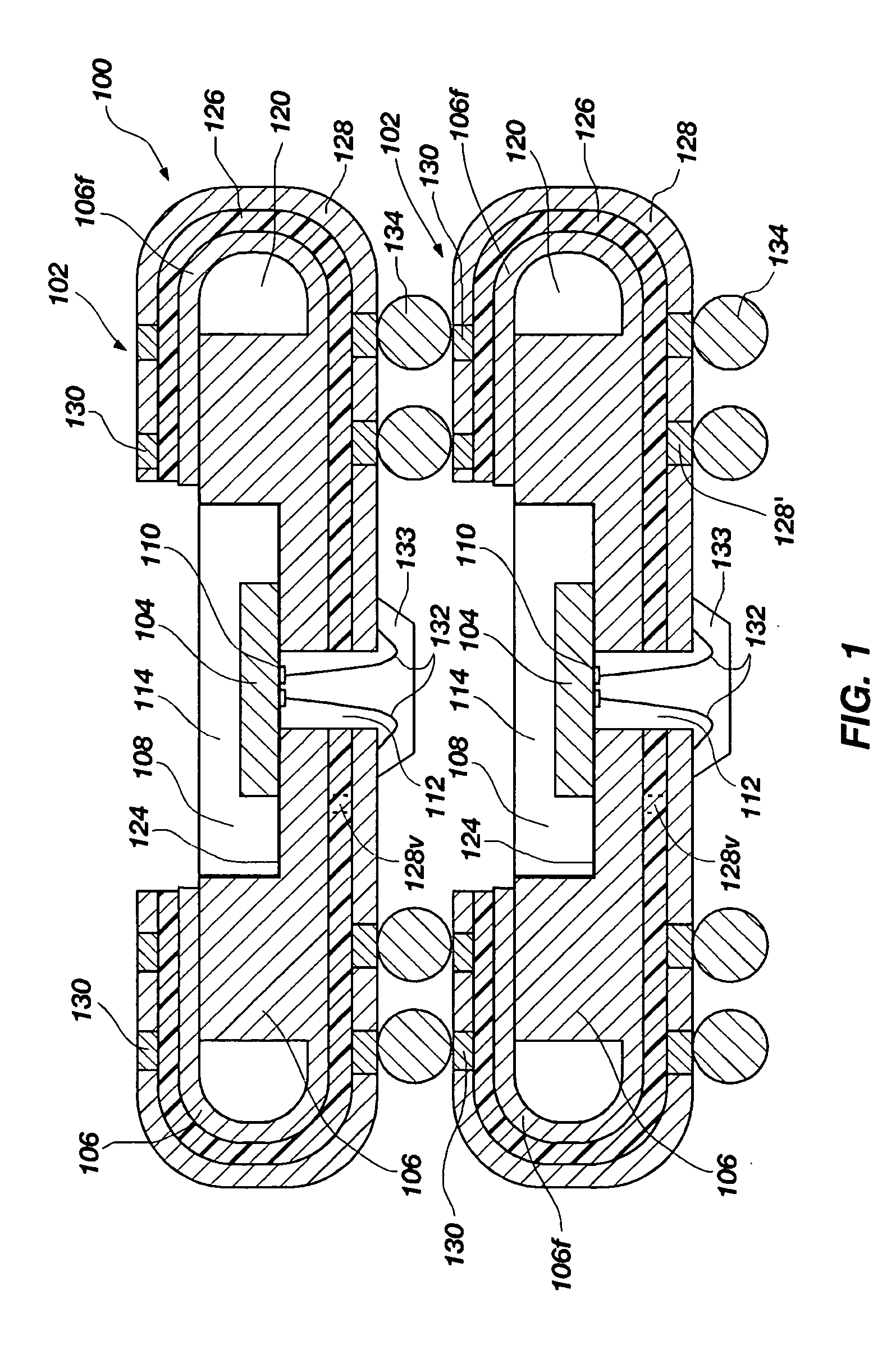

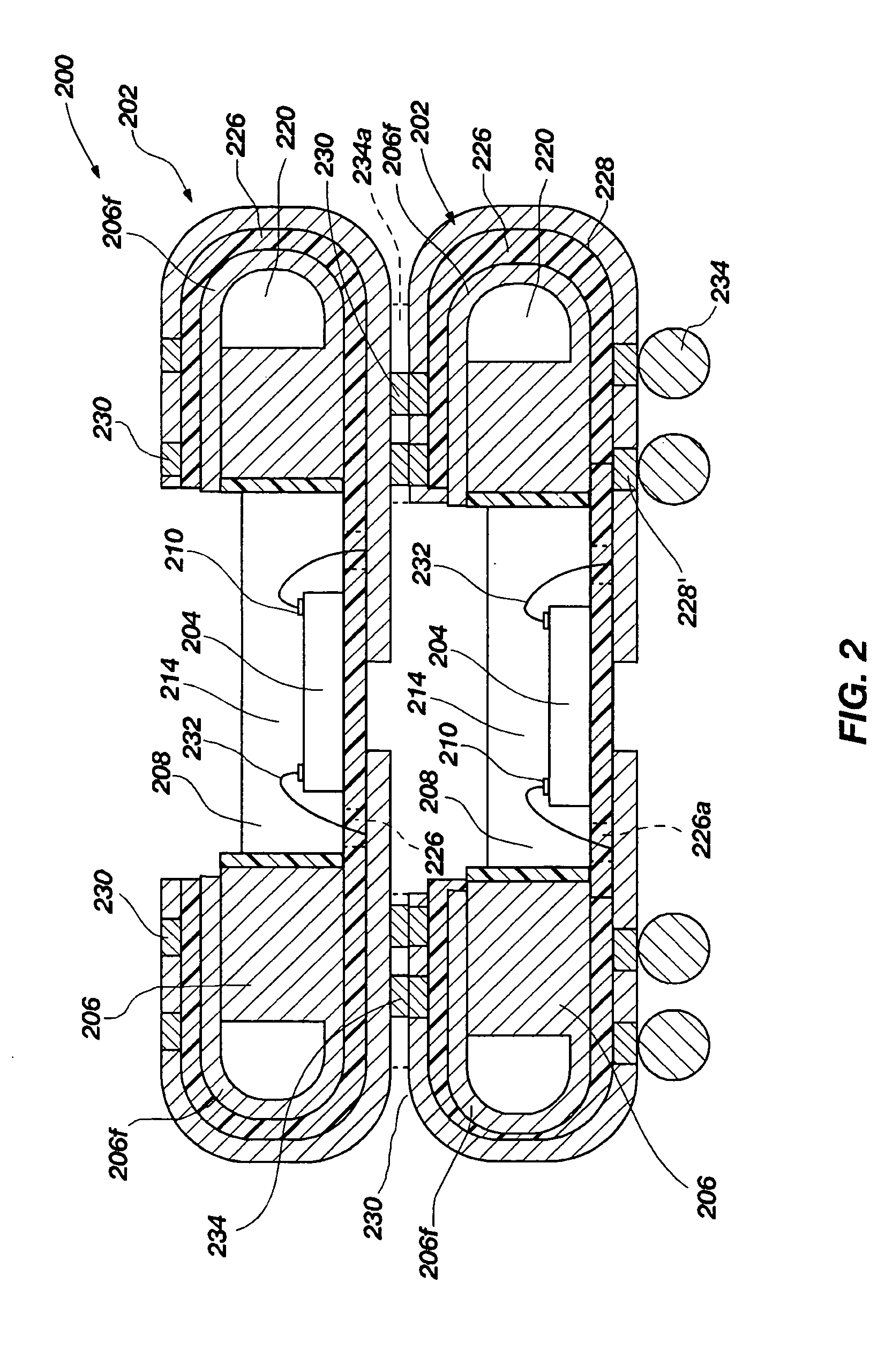

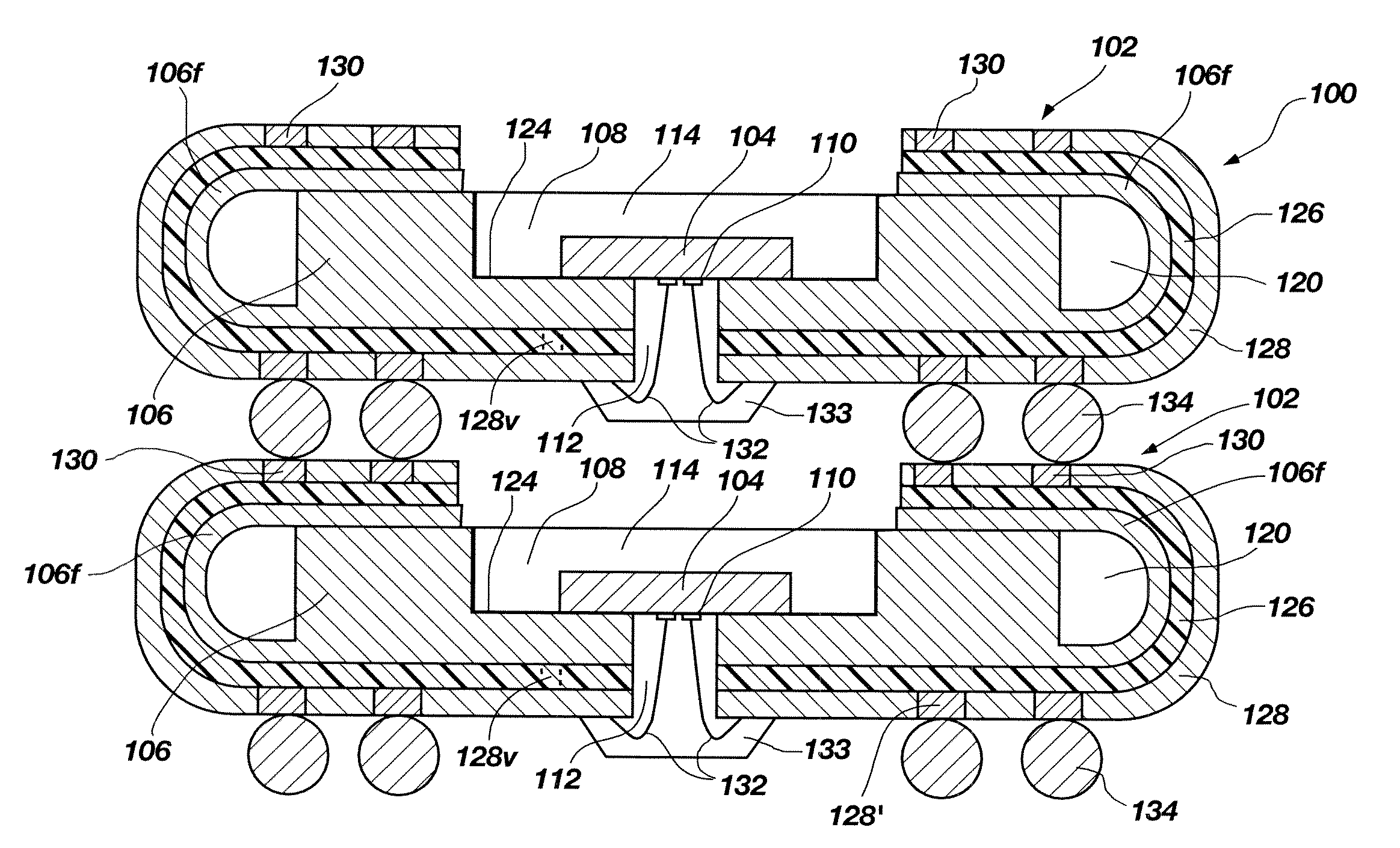

Metal core foldover package structures, systems including same and methods of fabrication

ActiveUS20080048309A1Additive manufacturing apparatusSemiconductor/solid-state device detailsOn boardAlloy

Chip scale packages and assemblies thereof and methods of fabricating such packages including Chip-On-Board, Board-On-Chip, and vertically stacked Package-On-Package modules are disclosed. The chip scale package includes a core member of a metal or alloy having a recess for at least partially receiving a die therein and includes at least one flange member partially folded over another portion of the core member. Conductive traces extend from one side of the package over the at least one flange member to an opposing side of the package. Systems including the chip scale packages and assemblies are also disclosed.

Owner:MICRON TECH INC

Integrated circuit package-on-package stacking system

InactiveUS20070108583A1Semiconductor/solid-state device detailsPrinted circuit aspectsInterposerPackage on package

An integrated circuit package-on-package stacking system is provided including providing a first integrated circuit package, mounting a metalized interposer substrate over the first integrated circuit package and attaching a second integrated circuit package on the metalized interposer substrate.

Owner:STATS CHIPPAC LTD

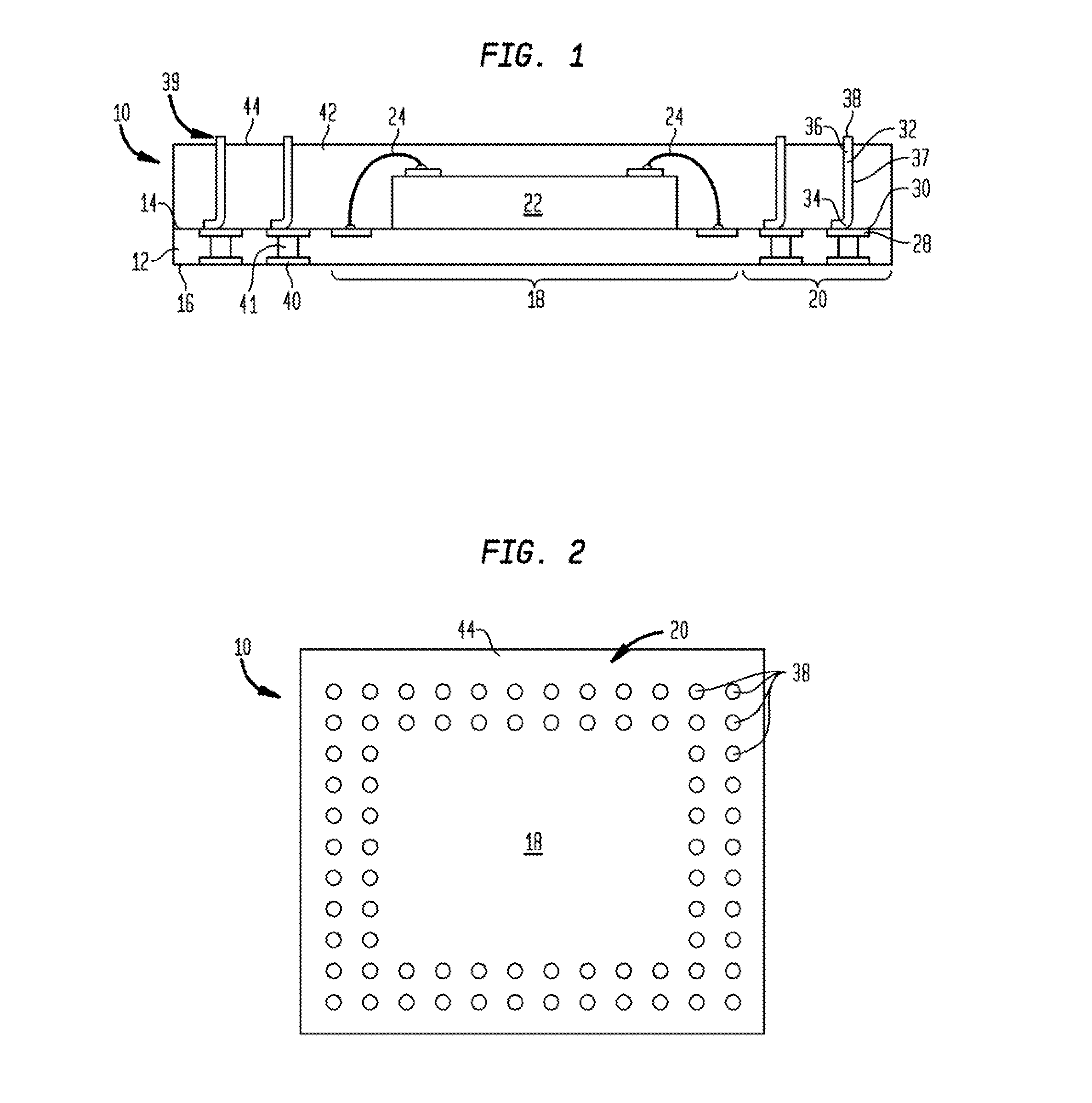

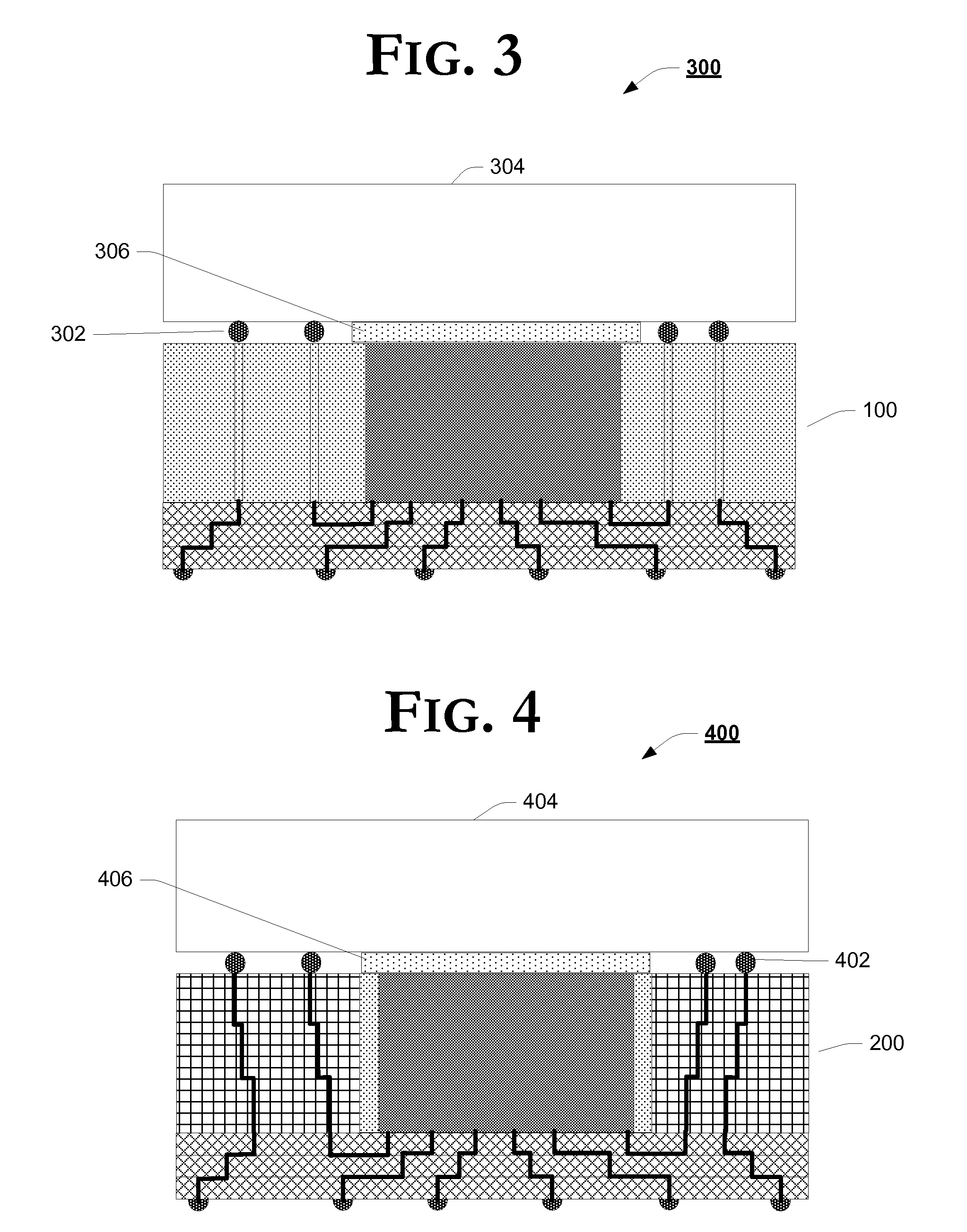

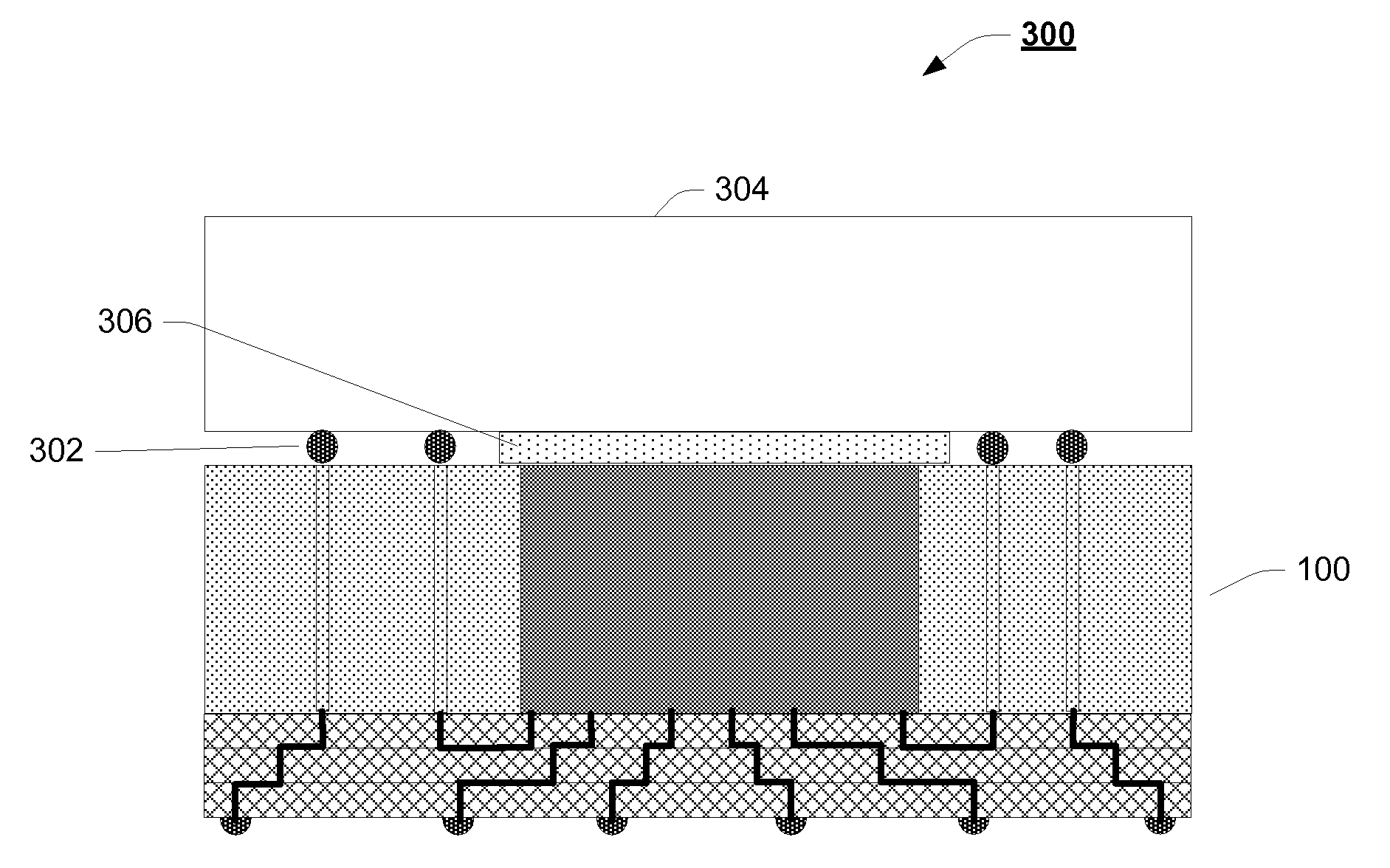

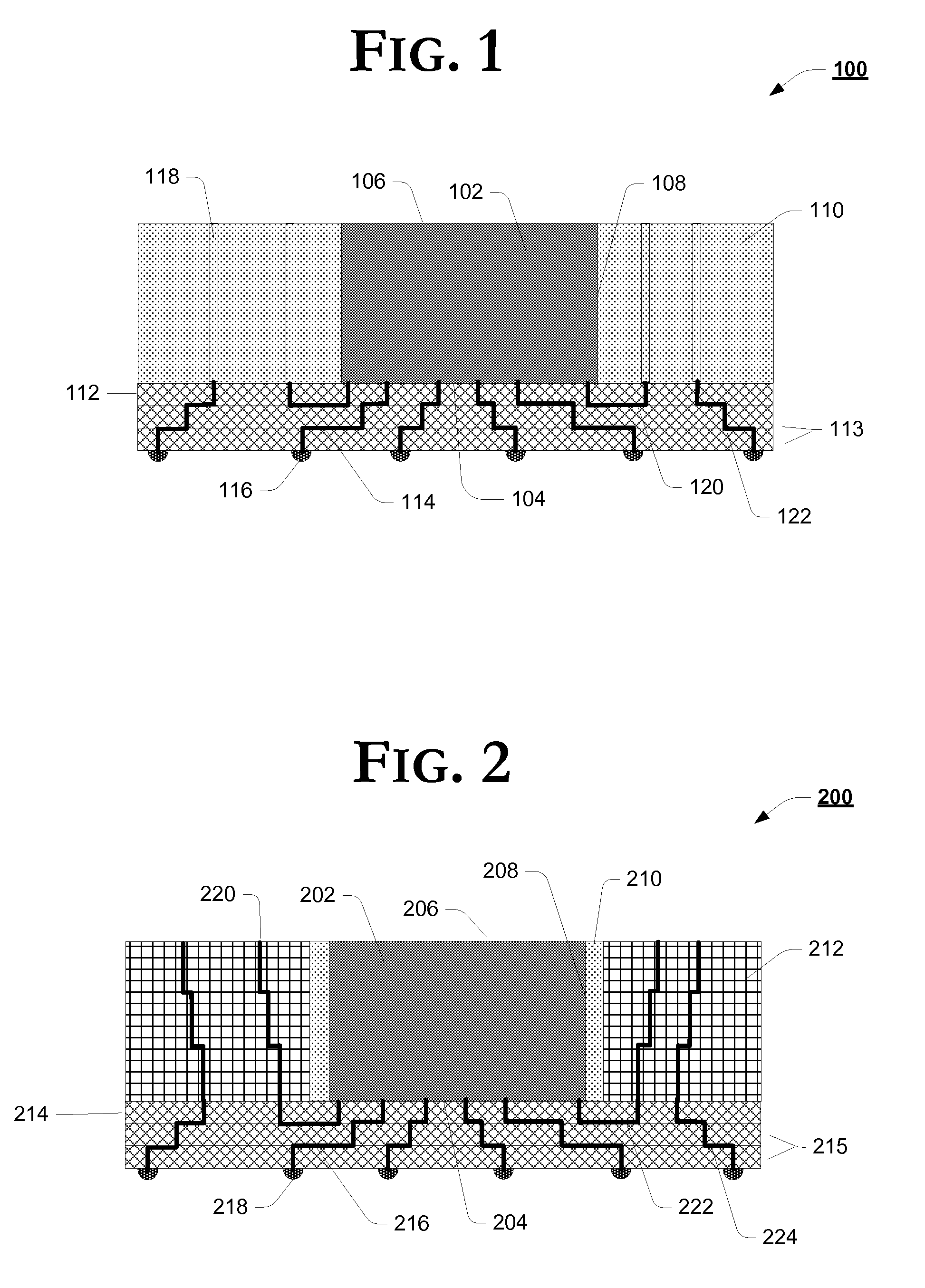

Substrate structure for cavity package

InactiveUS20110024899A1Improved cavity substrate structureImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

Various embodiments provide semiconductor devices having cavity substrate structures for package-on-package assembly and methods for their fabrication. In one embodiment, the cavity substrate structure can include at least one top interconnect via formed within a top substrate. The top substrate can be disposed over a base substrate having at least one base interconnect via that is not aligned with the top interconnect via. Semiconductor dies can be assembled in an open cavity of the top substrate and attached to a base center portion of the base substrate of the cavity substrate structure. A top semiconductor package can be mounted over the top substrate of the cavity substrate structure.

Owner:TEXAS INSTR INC

System and method for shielding of package on package (PoP) assemblies

ActiveUS7851894B1Semiconductor/solid-state device detailsSolid-state devicesConductive coatingSemiconductor package

A semiconductor package has a first substrate having a plurality of metal traces. At least one die is electrically coupled to the first surface of the first substrate. A plurality of land pads is formed on the first surface of the first substrate. A mold compound encapsulates portions of the die and portions of the first surface of the first substrate. A conductive coating is applied to the mold compound and electrically coupled to at least one metal trace. A non-conductive coating is formed over the conductive coating and portions of the mold compound. A plurality of vias is formed through the non-conductive coating and the mold compound to expose the land pads.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

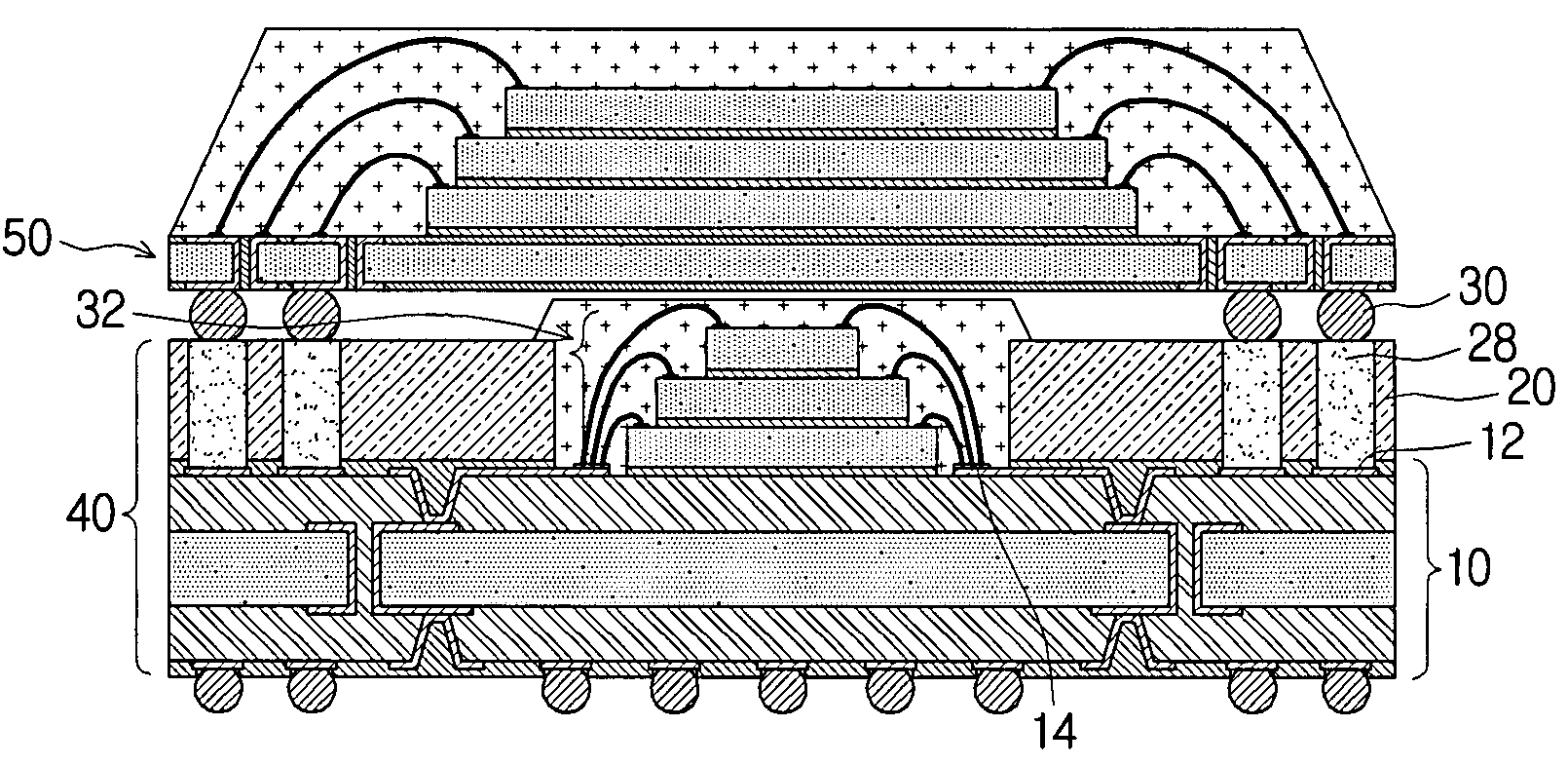

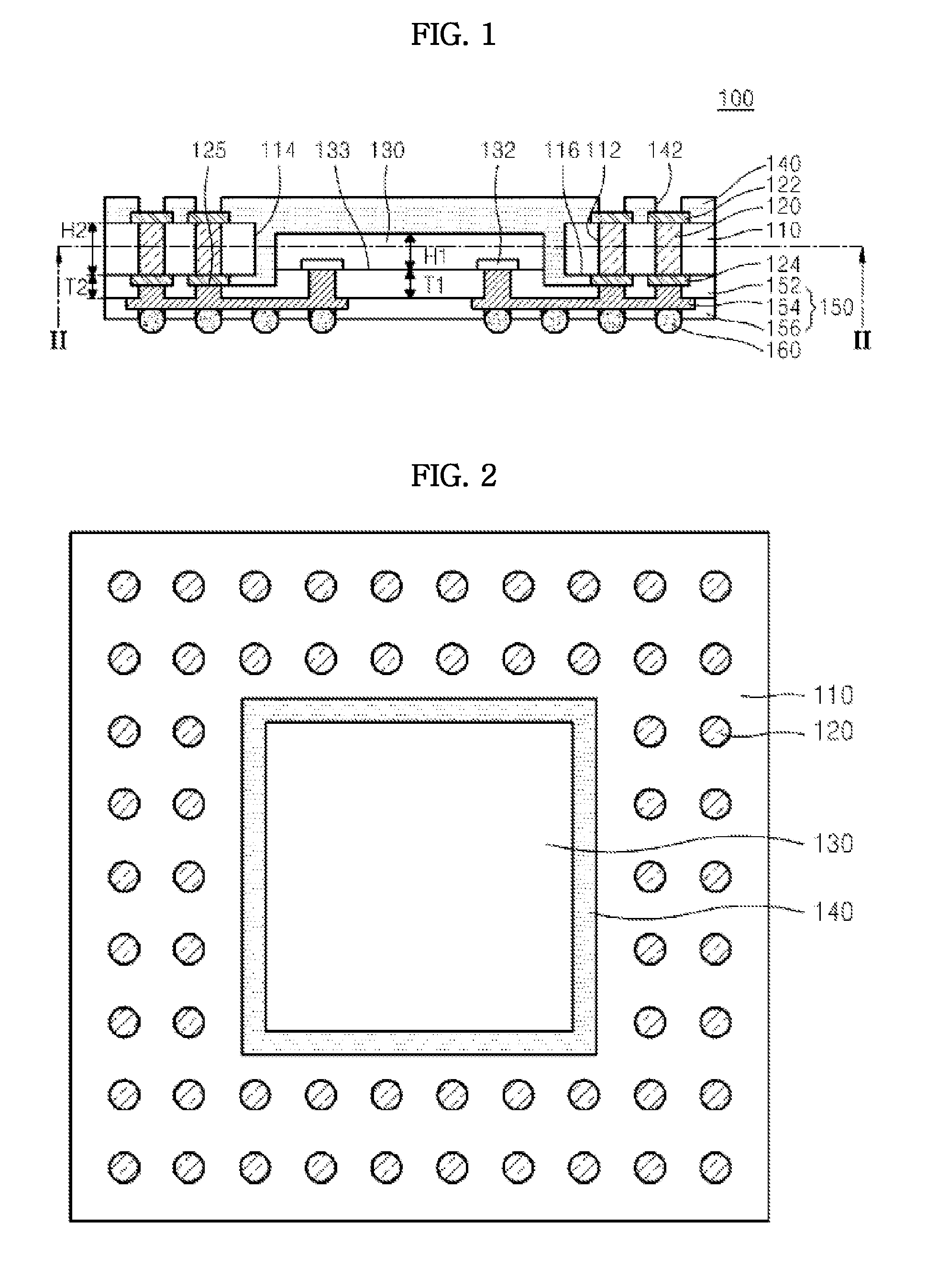

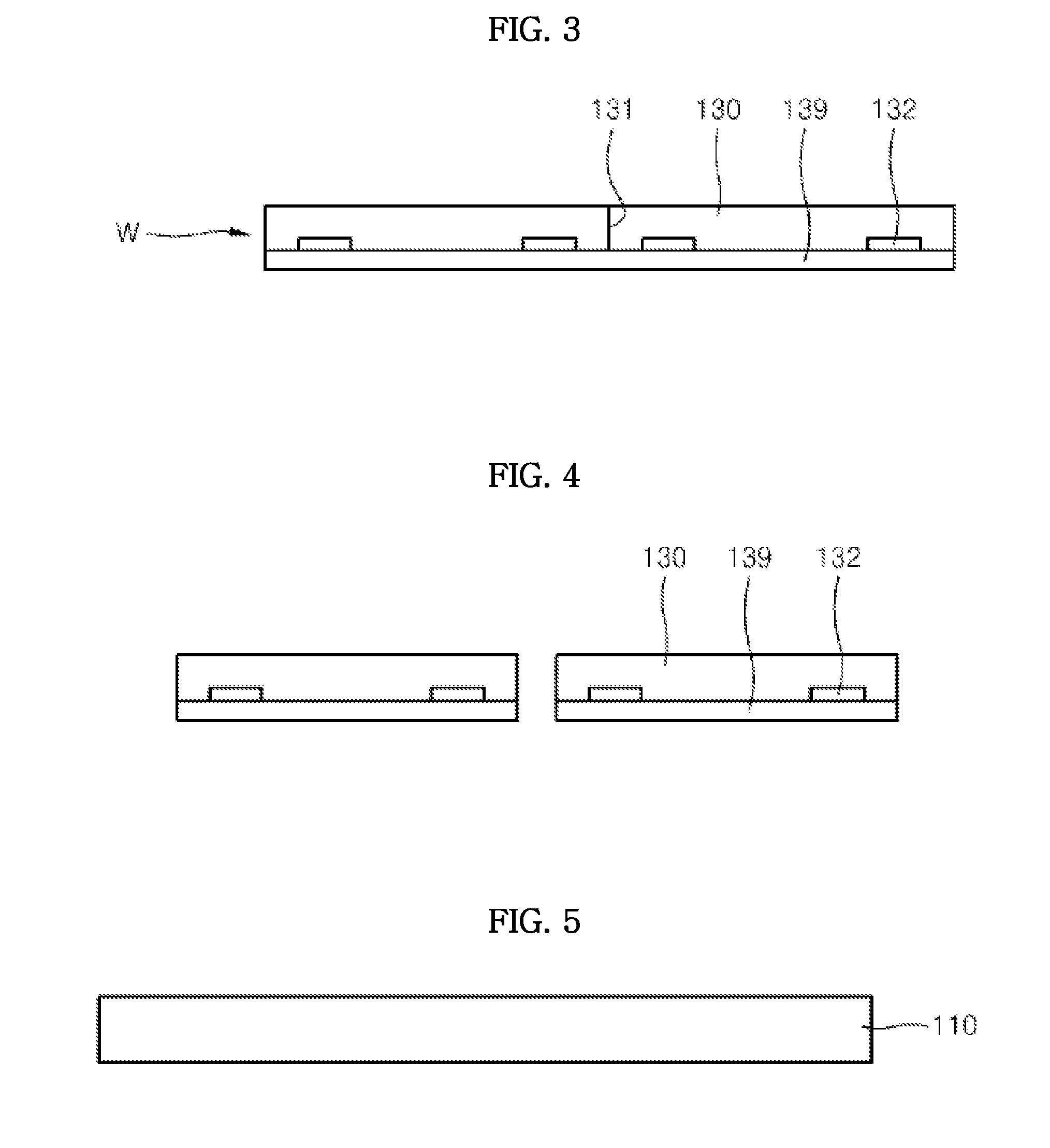

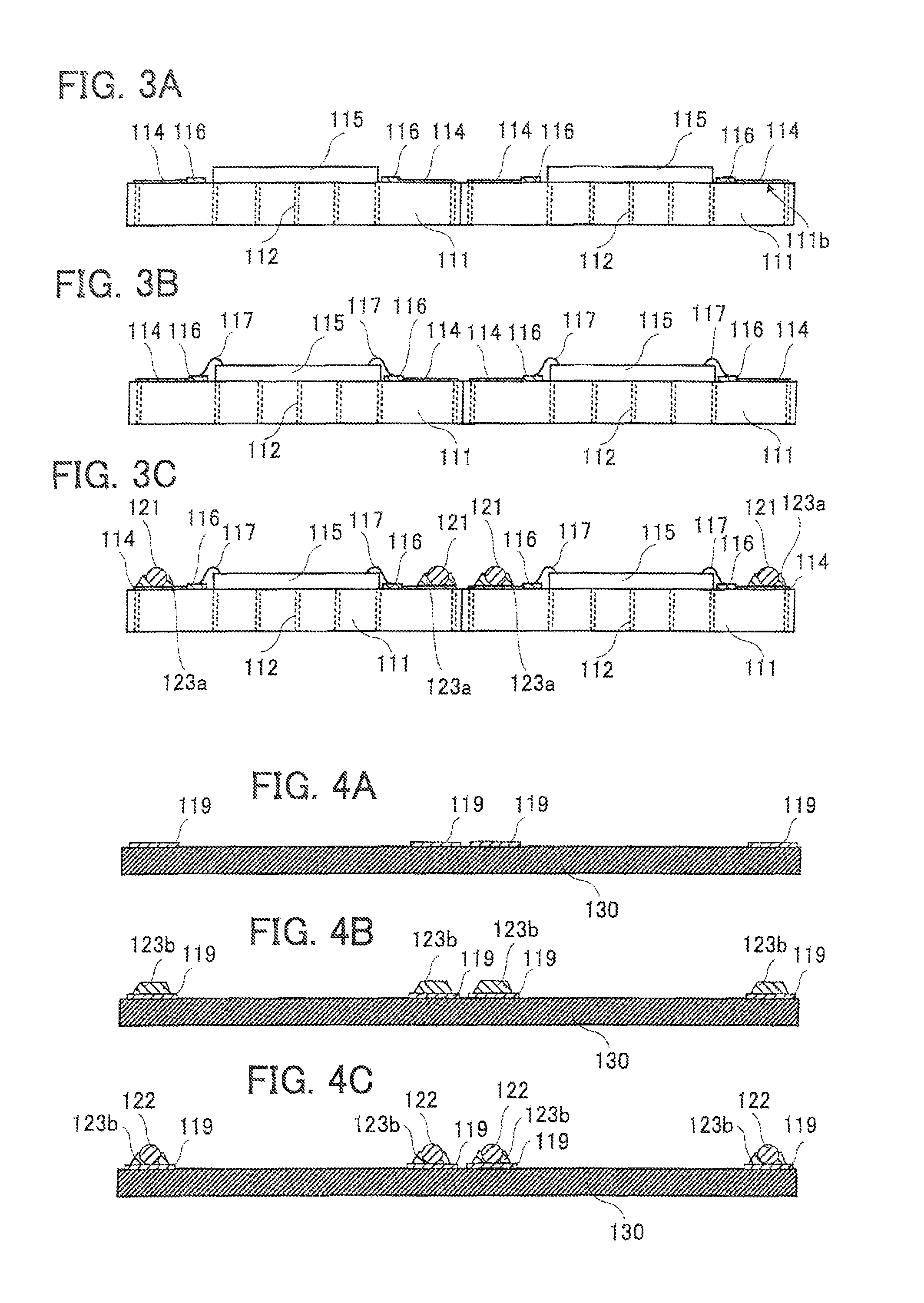

Semiconductor package, fabrication method therefor, and package-on package

ActiveUS20150187742A1Reduce harmPrecise processSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

Provided is a method of manufacturing a semiconductor package including a through wiring having precision and a low process defect. The semiconductor package includes an insulating substrate including a first through portion and a second through portion; a through wiring which fills the first through portion, and is located to penetrate the insulating substrate; a semiconductor chip which is located in the second through portion, and is electrically connected to the through wiring; a molding member molding the semiconductor chip and the insulating substrate; and a re-wiring pattern layer which is located at a lower side of the insulating substrate, and electrically connects the through wiring and the semiconductor chip.

Owner:NEPES CO LTD

Embedded integrated circuit package-on-package system

ActiveUS20070246813A1Semiconductor/solid-state device detailsSolid-state devicesEmbedded systemPackage on package

An embedded integrated circuit package-on-package system is provided forming a first integrated circuit package system, forming a second integrated circuit package system, and mounting the second integrated circuit package system over the first integrated circuit package system with the first integrated circuit package system, the second integrated circuit package system, or a combination thereof being an embedded integrated circuit package system or an embedded stacked integrated circuit package system.

Owner:STATS CHIPPAC LTD

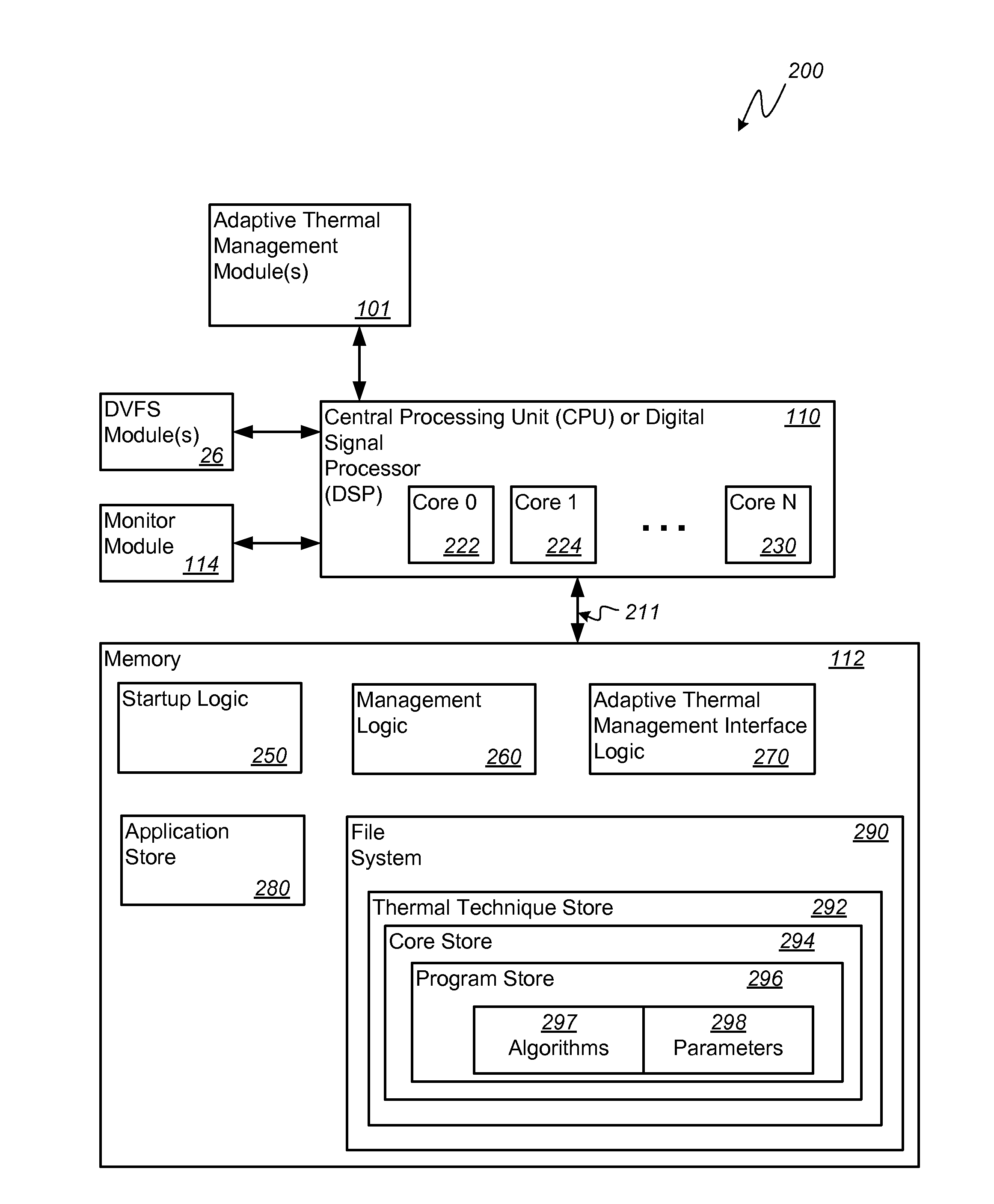

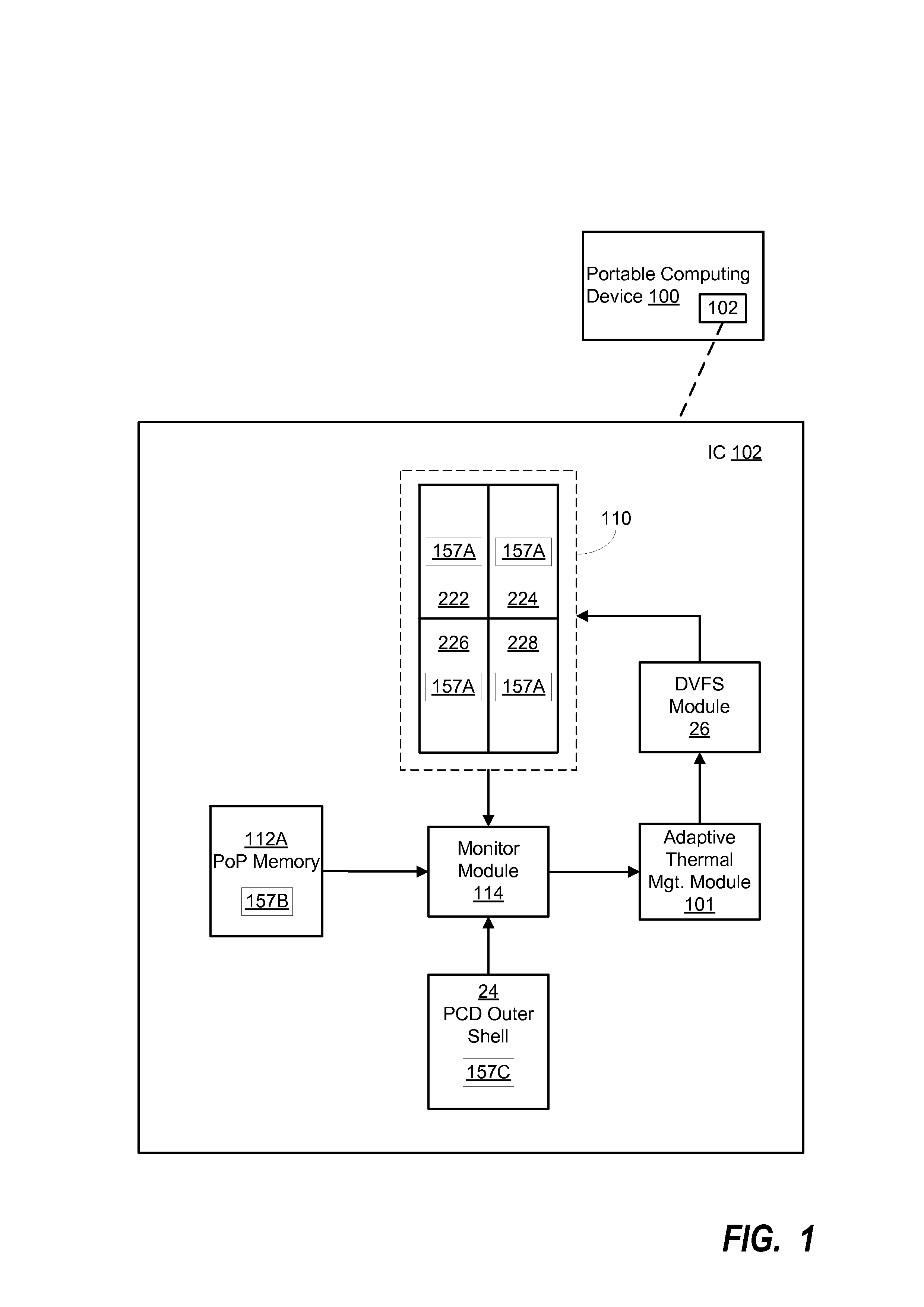

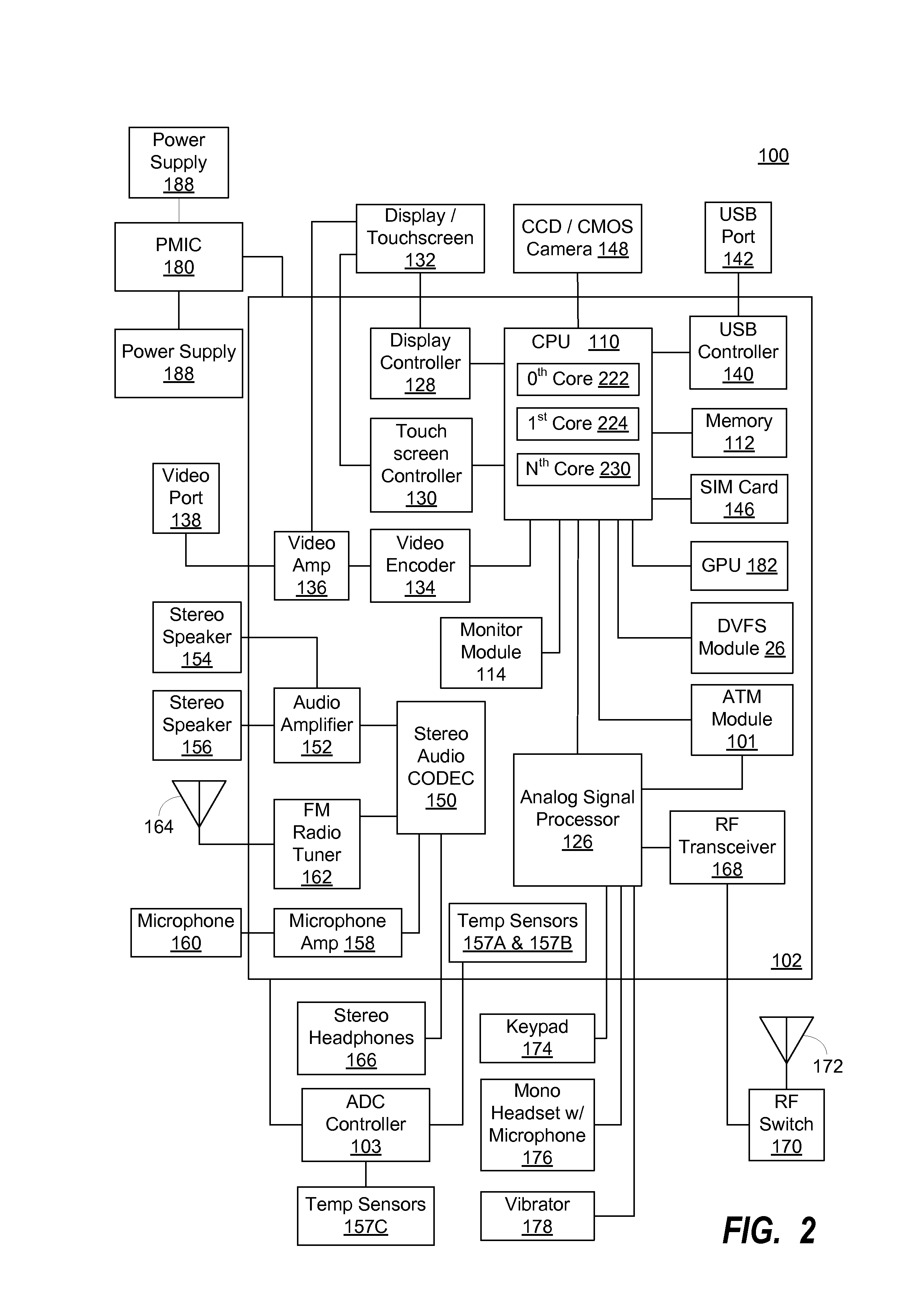

System and Method For Adaptive Thermal Management In A Portable Computing Device

ActiveUS20140006818A1Reduced performance levelLower performance requirementsVolume/mass flow measurementHardware monitoringJunction temperatureSelf adaptive

Owner:QUALCOMM INC

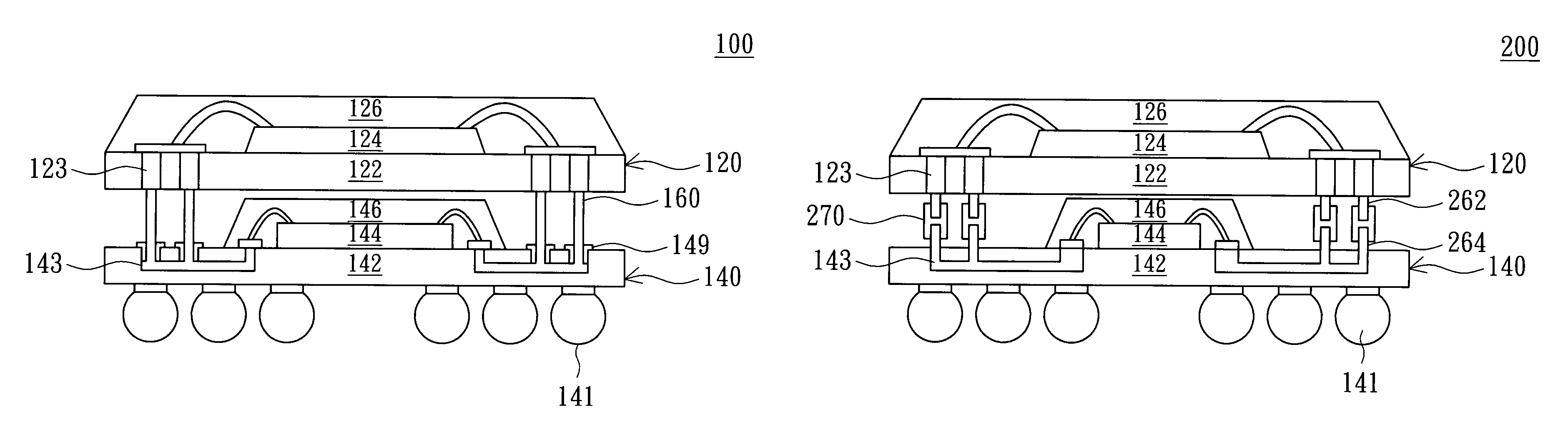

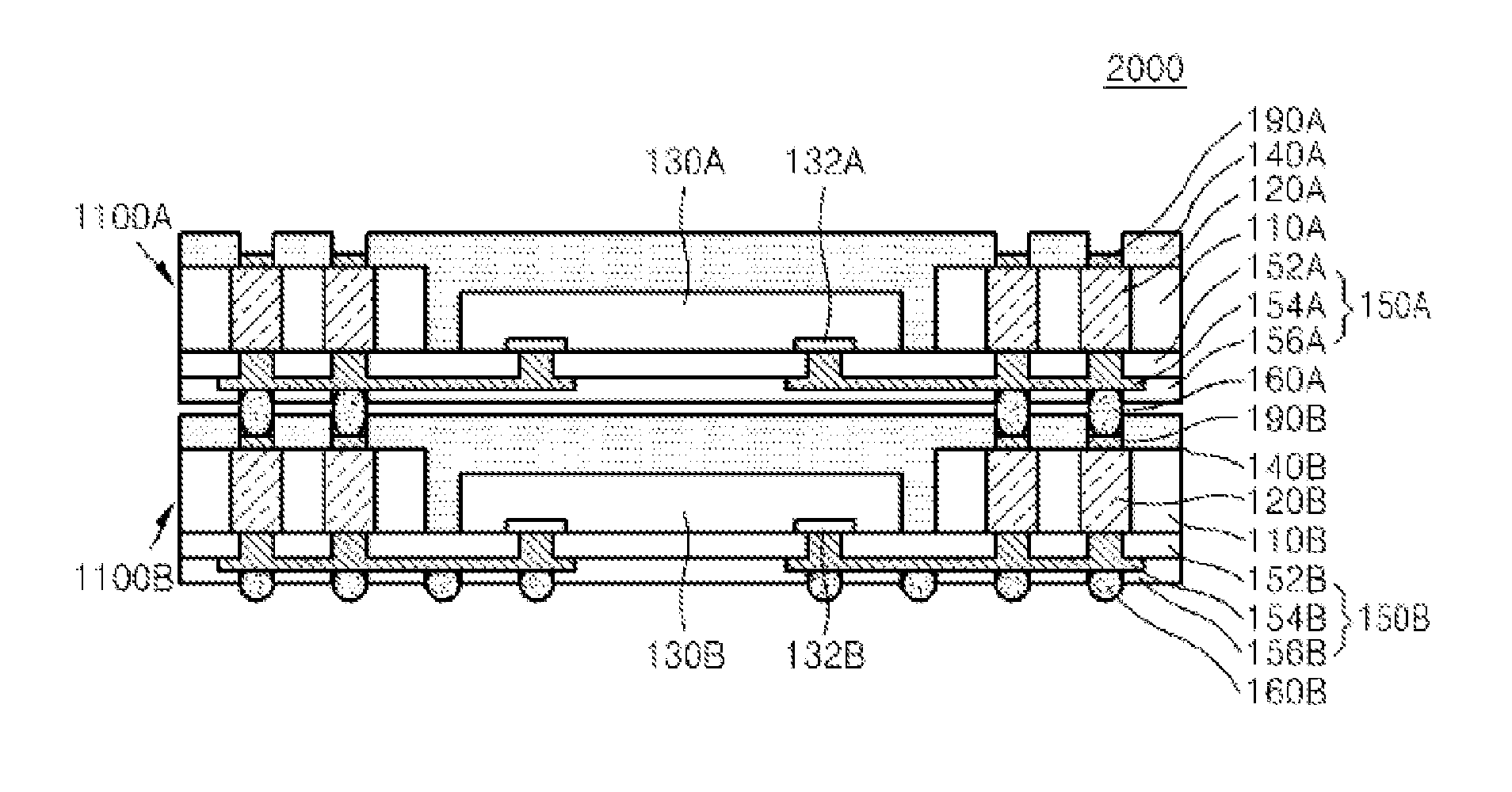

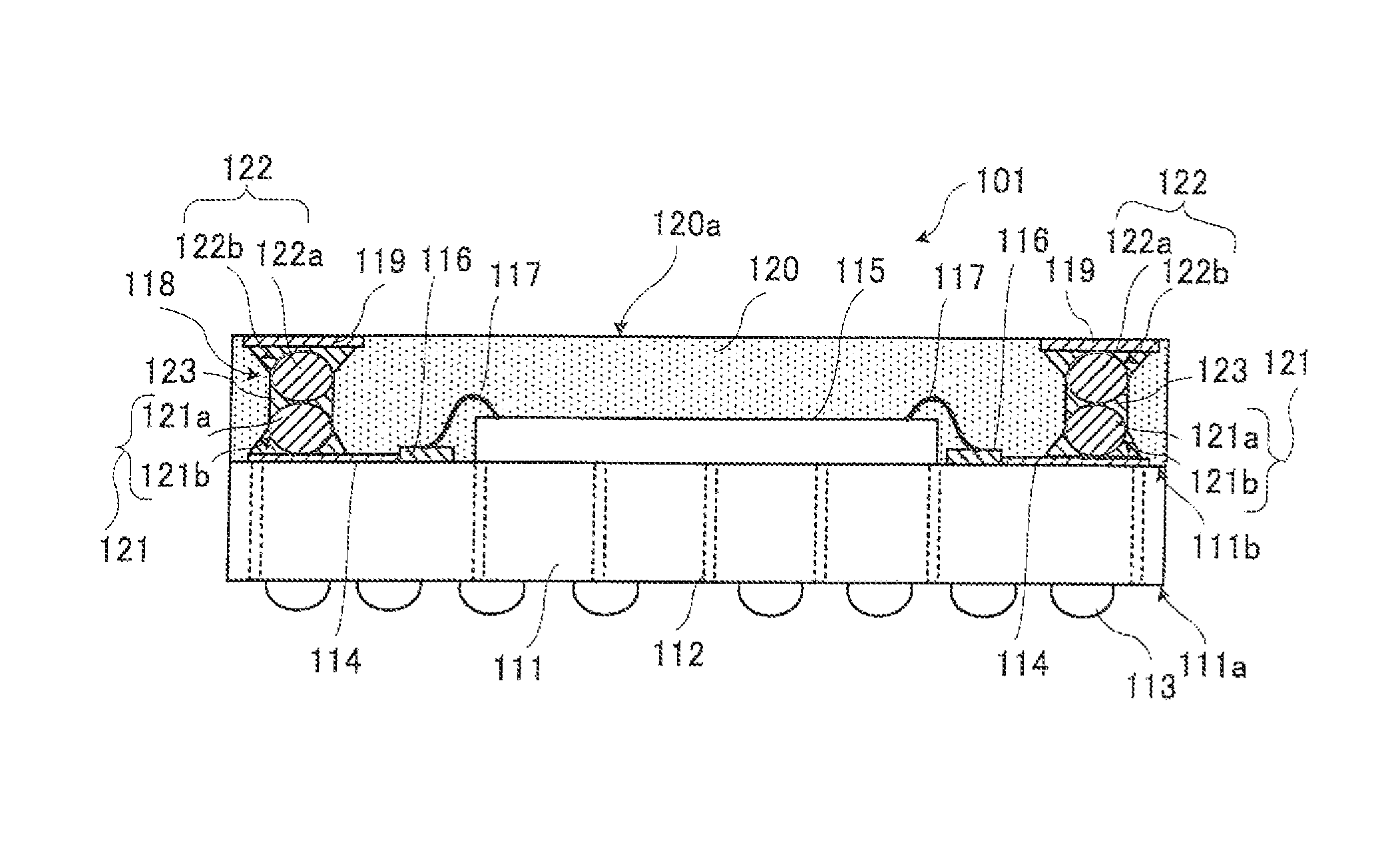

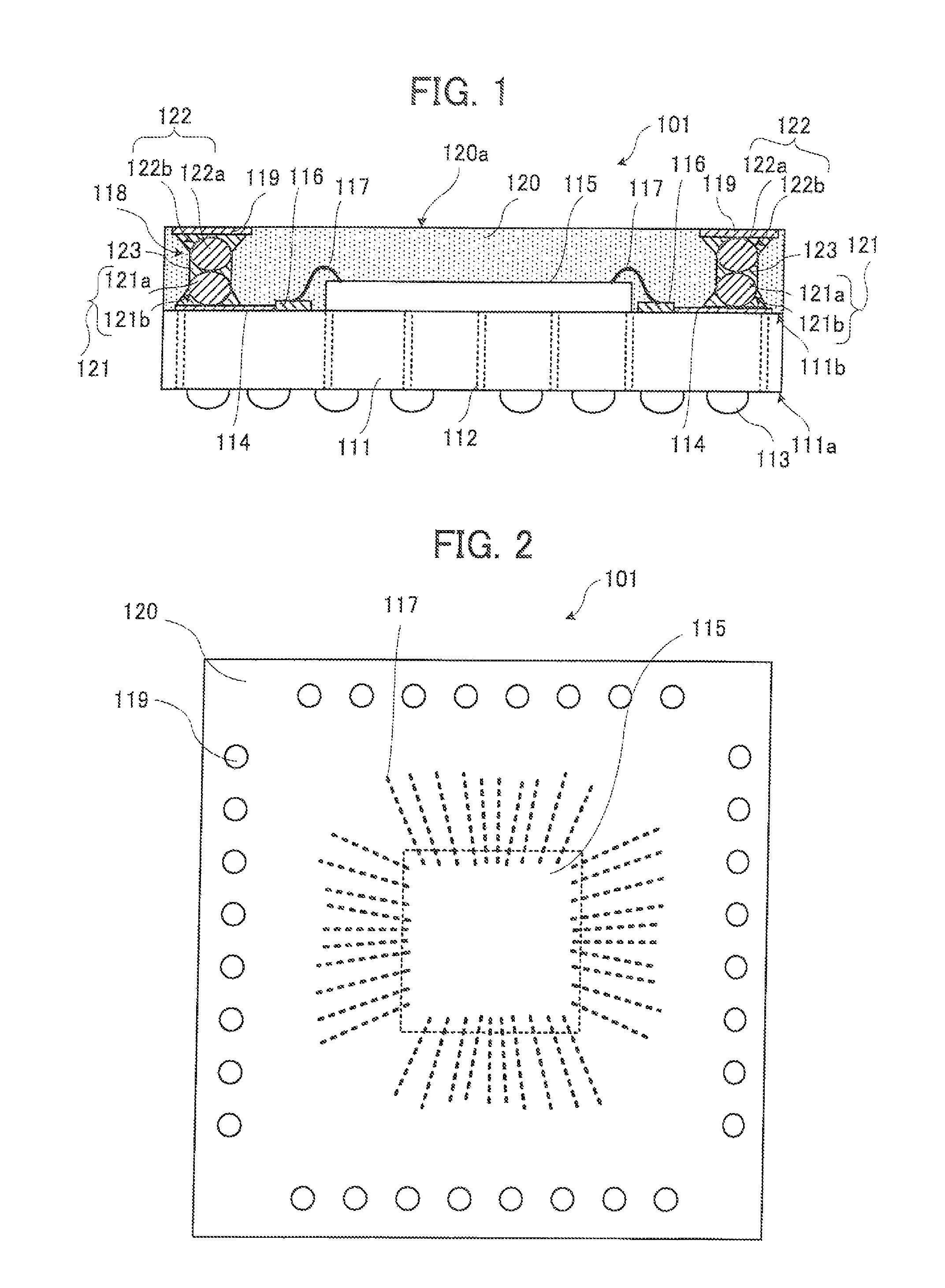

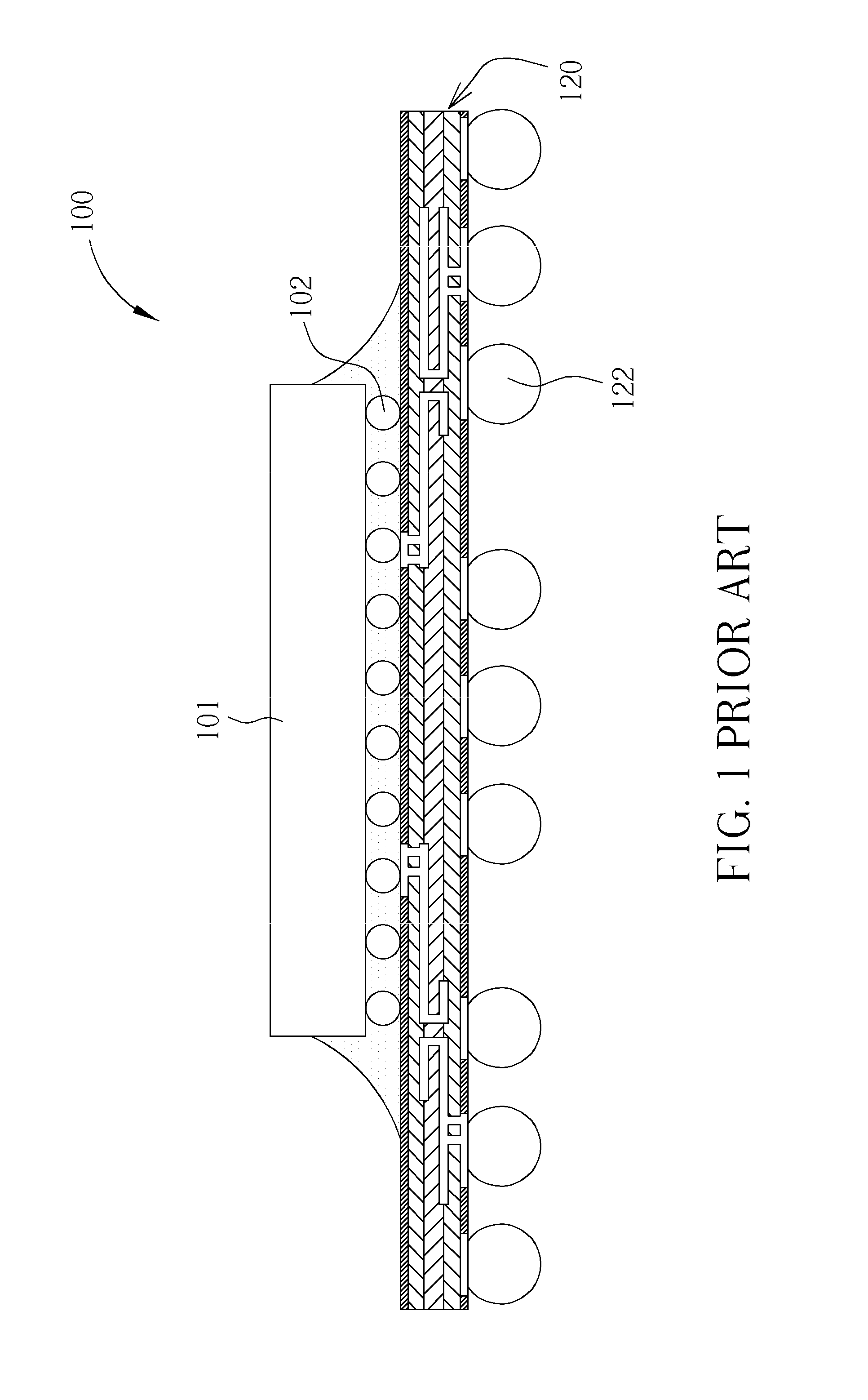

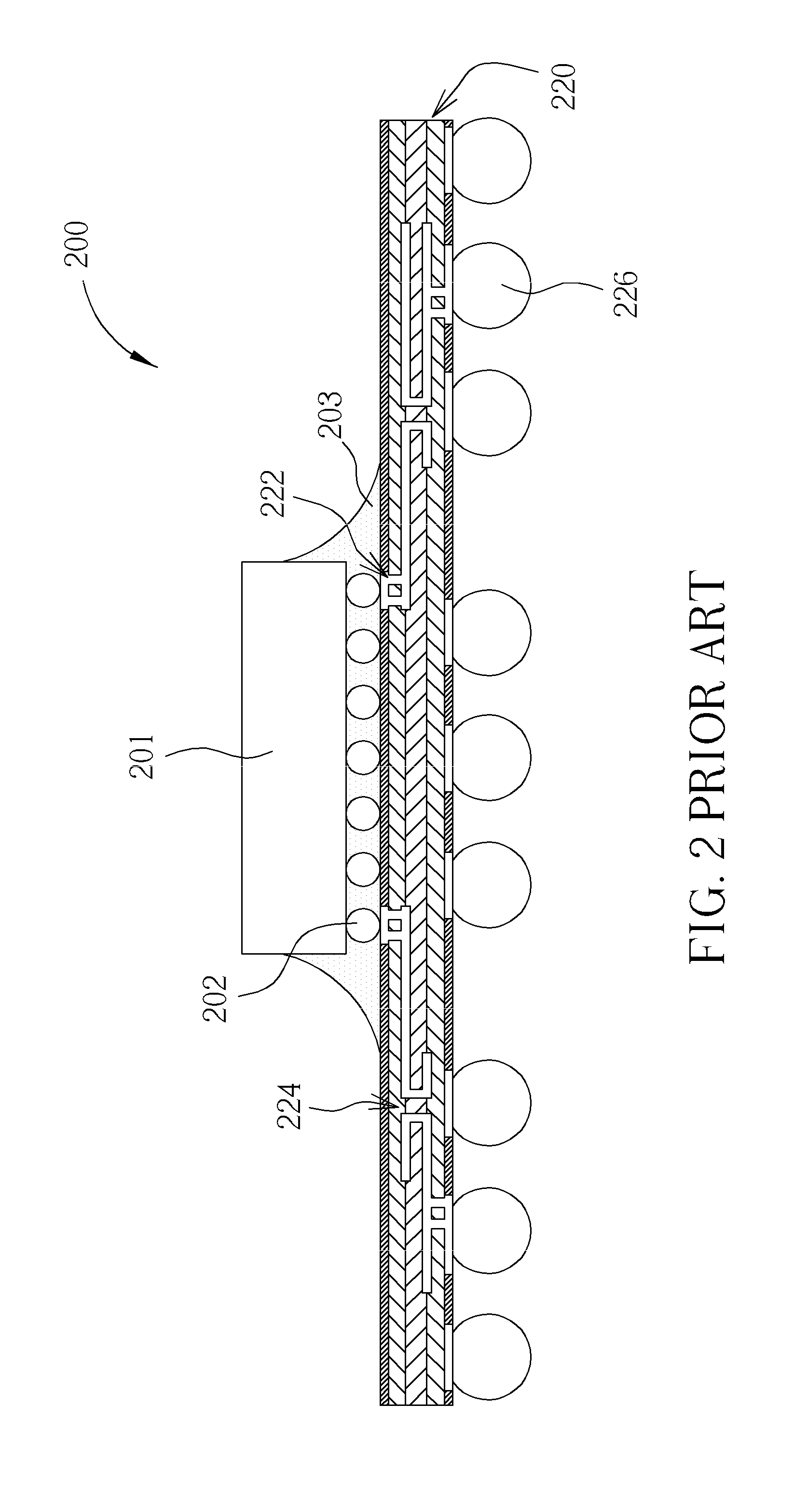

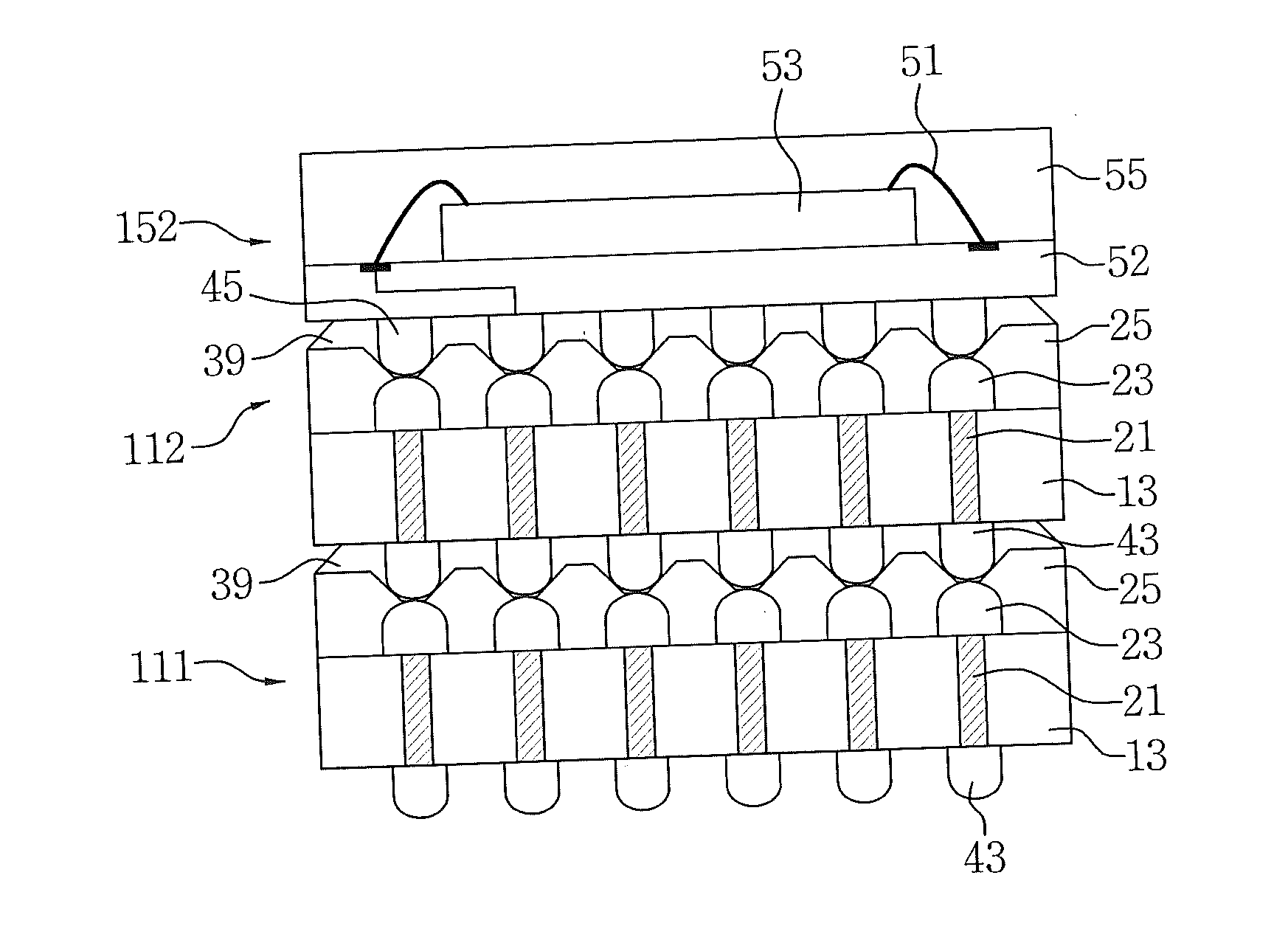

Semiconductor package and package-on-package semiconductor device

ActiveUS8314492B2Low priceLow costSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A semiconductor package includes a wiring board; a first electrode for external connection; a ball pad; a semiconductor chip; a mold resin; an electrode unit connected with the ball pad and penetrating the mold resin; and a second electrode for external connection connected with a portion of the electrode unit on a side of an outer surface of the mold resin. The electrode unit includes a first ball disposed on the ball pad; a second ball disposed between the first ball and the second electrode; and a solder material connecting between the ball pad and the first ball, between the first ball and the second ball, and between the second ball and the second electrode for external connection; each of the first ball and the second ball including a core part having a glass transition temperature which is higher than a melting point of the solder material.

Owner:LAPIS SEMICON CO LTD

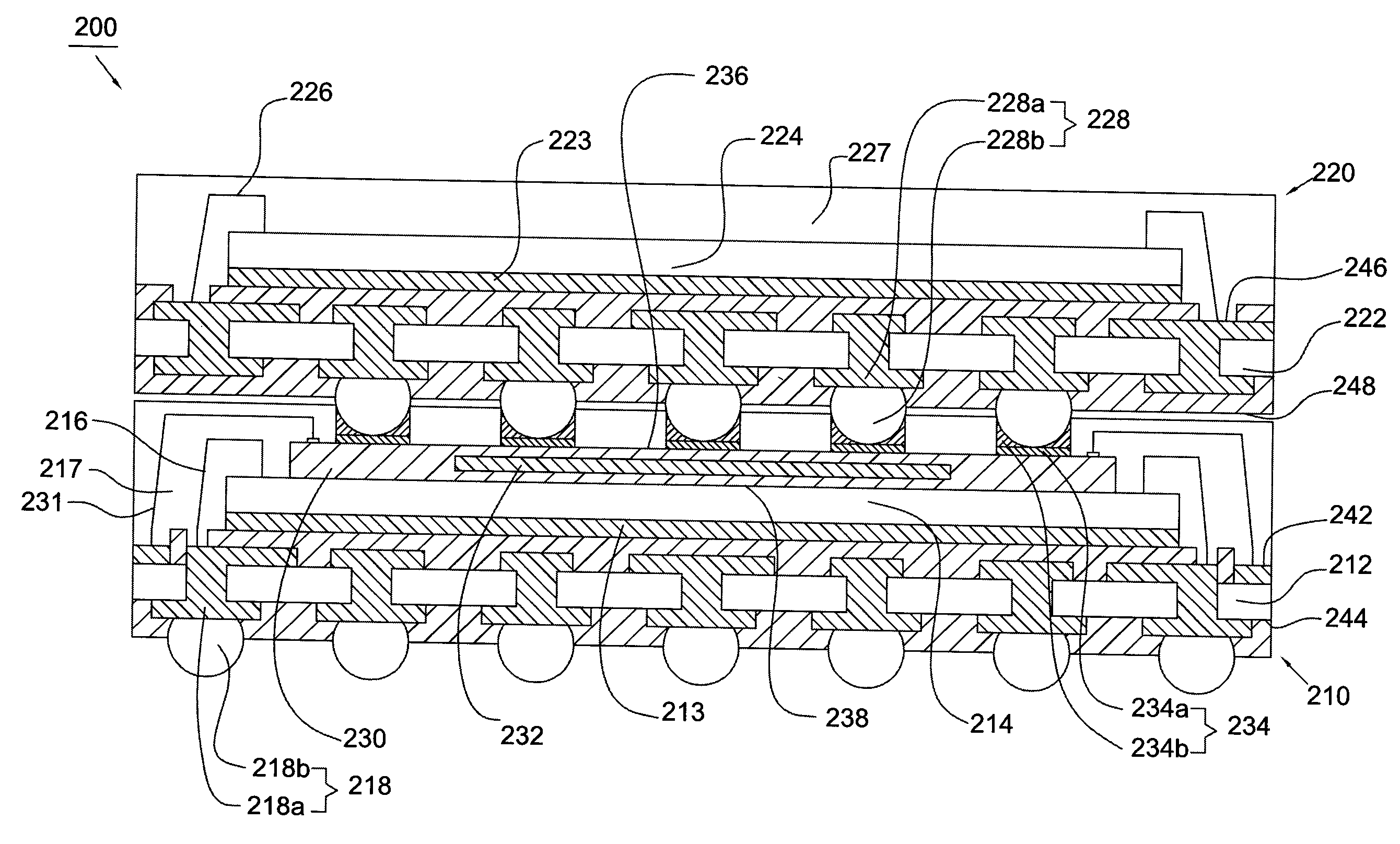

Package-on-package system with via z-interconnections

ActiveUS20090236752A1Semiconductor/solid-state device detailsSolid-state devicesInterconnectionEngineering

A package-on-package system includes: providing an interposer substrate; mounting a base substrate under the interposer substrate and having a first integrated circuit die connected thereto; forming an encapsulant between the interposer substrate and the base substrate, the encapsulant encapsulating the first integrated circuit die; and forming a via z-interconnection extending through the encapsulant and one of the substrates to the other of the substrates.

Owner:STATS CHIPPAC LTD

Package-on-package with fan-out wlcsp

ActiveUS20120032314A1Overcome limitationsCost-effectiveSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipPackage on package

A package-on-package includes a package carrier; a semiconductor die assembled face-down to a chip side of the package carrier; a rewiring laminate structure between the semiconductor die and the package carrier; a plurality of bumps arranged on the rewiring laminate structure for electrically connecting the semiconductor die with the package carrier; and an IC package mounted on the package carrier. The IC package and the semiconductor die are at least partially overlapped.

Owner:MEDIATEK INC

Integrated circuit packaging system with package-on-package and method of manufacture thereof

ActiveUS20110037157A1Semiconductor/solid-state device detailsSolid-state devicesComputer moduleEngineering

A method of manufacture of an integrated circuit packaging system includes: providing a substrate; mounting a component over a side of the substrate; forming an interface module having a module via in any location for connectivity to the substrate; and mounting the entirety of the interface module over a portion of the side of the substrate next to the component.

Owner:STATS CHIPPAC LTD

Package on-package secure module having BGA mesh cap

InactiveUS7868441B2Semiconductor/solid-state device detailsSolid-state devicesMicrocontrollerEngineering

A package-on-package (POP) secure module includes a BGA mesh cap, a first BGA package, and a second BGA package. The first BGA package includes a first integrated circuit (for example, a microcontroller that includes tamper detect logic). The second BGA package includes a second integrated circuit (for example, a memory). The second BGA package is piggy-back mounted to the first BGA package and the BGA mesh cap is piggy-back mounted to the second BGA package. A printed circuit board substrate member of the BGA mesh cap includes an embedded anti-tamper mesh. This mesh is connected in a protected manner within the module to the first integrated circuit. When the module is in use, a mesh embedded in an underlying printed circuit board is coupled to the BGA cap mesh so that both anti-tamper meshes are controlled by the tamper detect logic.

Owner:MAXIM INTEGRATED PROD INC

Package-on-package assembly with wire bond vias

ActiveUS20130093087A1Semiconductor/solid-state device detailsPrinted circuit aspectsEdge surfaceLead bonding

A microelectronic package can include wire bonds having bases bonded to respective ones of conductive elements exposed at a surface of a substrate. The wire bonds may have exterior edge surfaces disposed at an angle between 25° and 90° relative to the bases, and ends remote, e.g., opposite, from the bases, and remote from the ends which are connected to the bases. A dielectric encapsulation layer extends from the substrate and covers portions of the wire bonds such that covered portions of the wire bonds are separated from one another by the encapsulation layer, wherein unencapsulated portions of the wire bonds are defined by portions of the wire bonds that are uncovered by the encapsulation layer, the unencapsulated portions including the ends of the wire bonds.

Owner:INVENSAS LLC

Method Of Forming Package-On-Package And Device Related Thereto

ActiveUS20110237027A1Easy to fallSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor chip

Provided is a method of forming a package-on-package. An encapsulation is formed to cover a wafer using a wafer level molding process. The wafer includes a plurality of semiconductor chips and a plurality of through silicon vias (TSVs) passing through the semiconductor chips. The encapsulant may have openings aligned with the TSVs. The encapsulant and the semiconductor chips are divided to form a plurality of semiconductor packages. Another semiconductor package is stacked on one selected from the semiconductor packages. The other semiconductor package is electrically connected to the TSVs.

Owner:SAMSUNG ELECTRONICS CO LTD

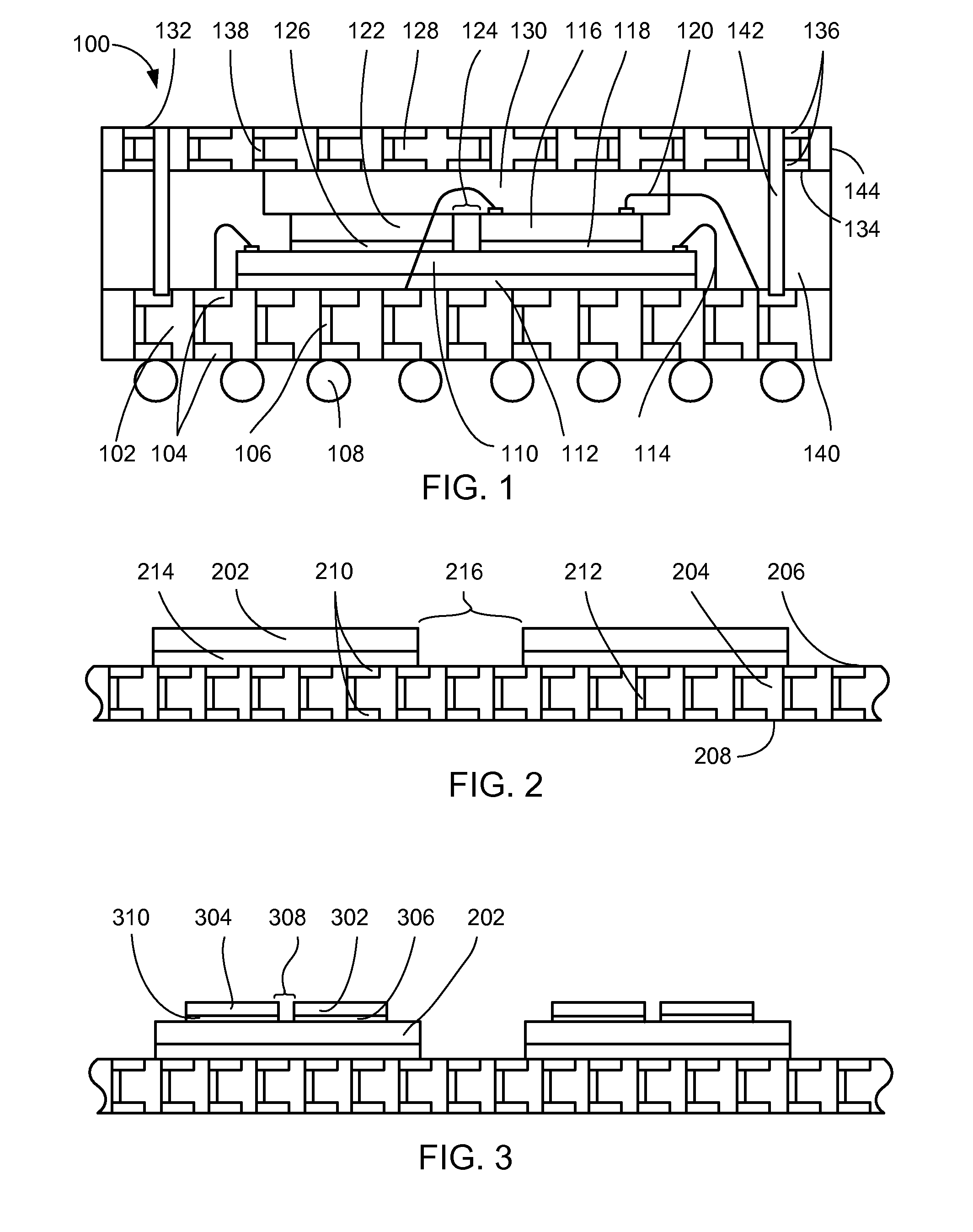

Package on package using a bump-less build up layer (BBUL) package

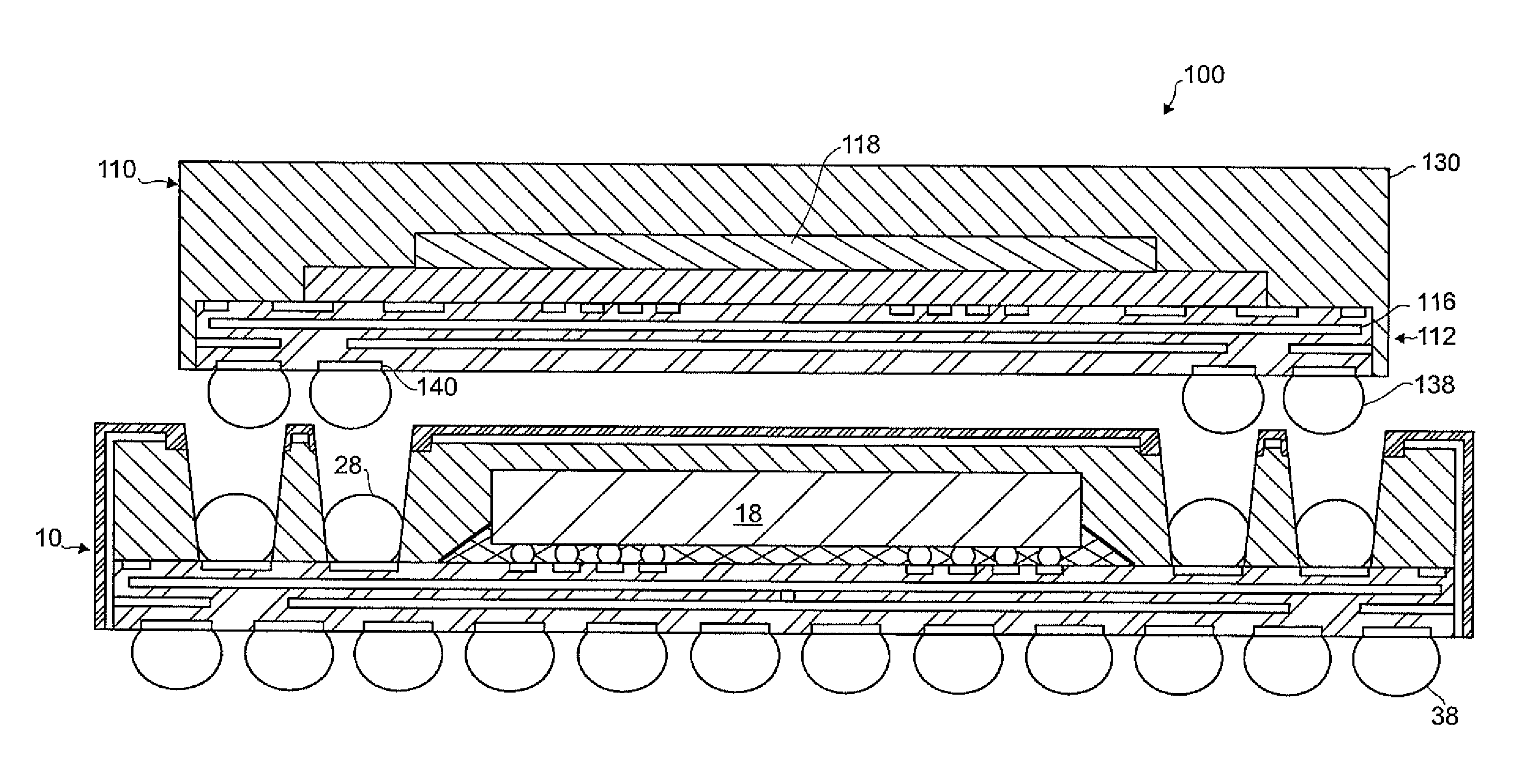

ActiveUS20090294942A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringActive surface

In some embodiments, package on package using a bump-less build up layer (BBUL) package is presented. In this regard, an apparatus is introduced comprising a microelectronic die having an active surface, an inactive surface parallel to said active surface, and at least one side, an encapsulation material adjacent said at least one microelectronic die side, wherein said encapsulation material includes a bottom surface substantially planar to said microelectronic die active surface and a top surface substantially planar to said microelectronic die inactive surface, a through via connection in said encapsulation material extending from said top surface to said bottom surface, a first dielectric material layer disposed on at least a portion of said microelectronic die active surface and said encapsulation material surface, a plurality of build-up layers disposed on said first dielectric material layer, and a plurality of conductive traces disposed on said first dielectric material layer and said build-up layers and in electrical contact with said microelectronic die active surface. Other embodiments are also disclosed and claimed.

Owner:INTEL CORP

Package-on-package device, semiconductor package and method for manufacturing the same

ActiveUS7838334B2Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageInterposer

A semiconductor package includes a substrate, a chip, an interposer and a molding compound. The chip is electrically connected to the upper surface of the substrate. The interposer is disposed on the chip, and electrically connected to the upper surface of the substrate. The interposer includes an embedded component and a plurality of electric contacts, wherein the embedded component is located between the upper and lower surfaces of the interposer, and the electric contacts are located on the upper surface of the interposer. The molding compound seals the chip and covers the upper surface of the substrate and the lower surface of the interposer.

Owner:ADVANCED SEMICON ENG INC

Package on package using a bump-less build up layer (BBUL) package

ActiveUS8093704B2Semiconductor/solid-state device detailsSolid-state devicesEngineeringActive surface

Owner:INTEL CORP

Metal core foldover package structures

ActiveUS7425758B2Additive manufacturing apparatusSemiconductor/solid-state device detailsOn boardEngineering

Chip-scale packages and assemblies thereof and methods of fabricating such packages including Chip-On-Board, Board-On-Chip, and vertically stacked Package-On-Package modules are disclosed. The chip-scale package includes a core member of a metal or alloy having a recess for at least partially receiving a die therein and includes at least one flange member partially folded over another portion of the core member. Conductive traces extend from one side of the package over the at least one flange member to an opposing side of the package. Systems including the chip-scale packages and assemblies are also disclosed.

Owner:MICRON TECH INC

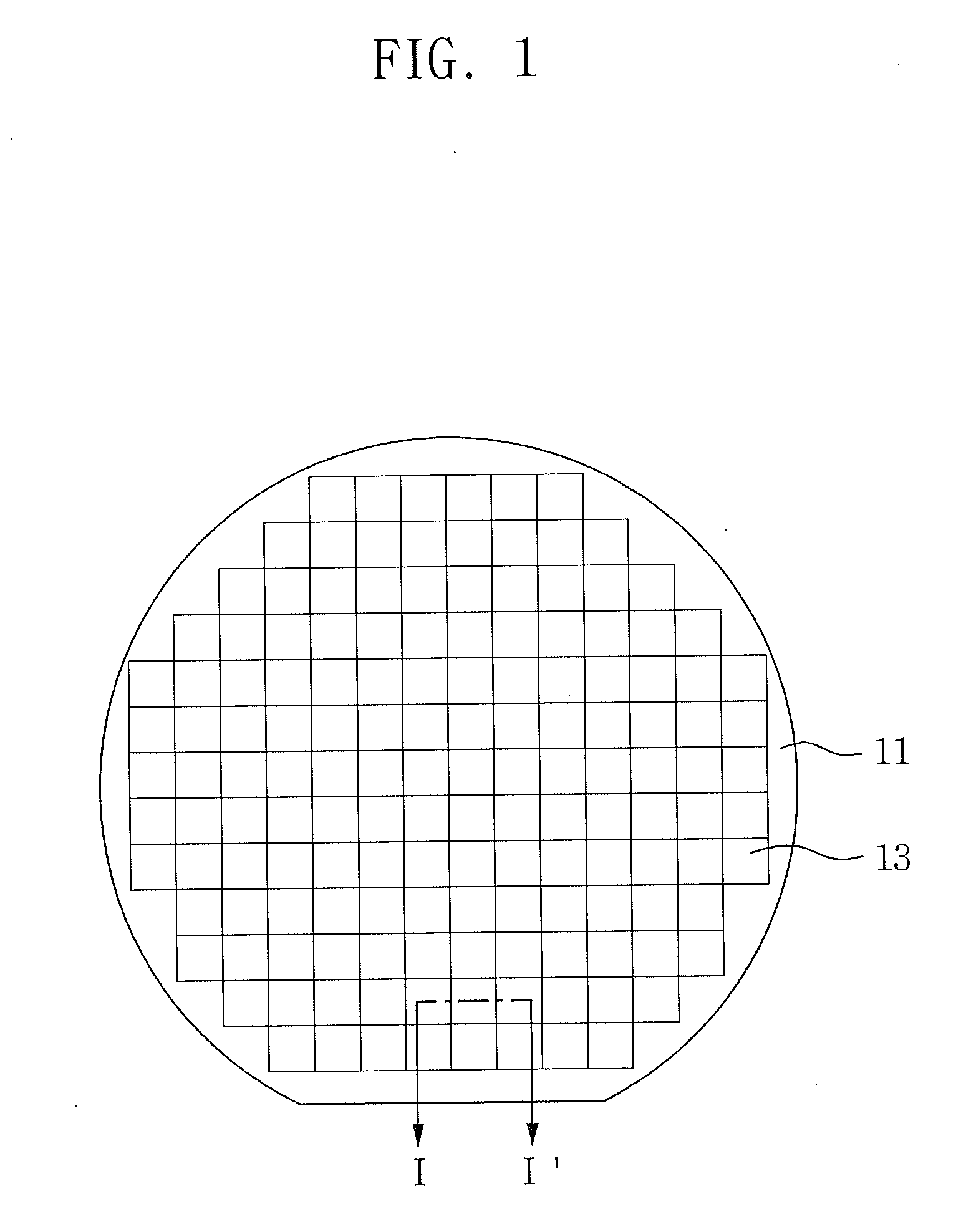

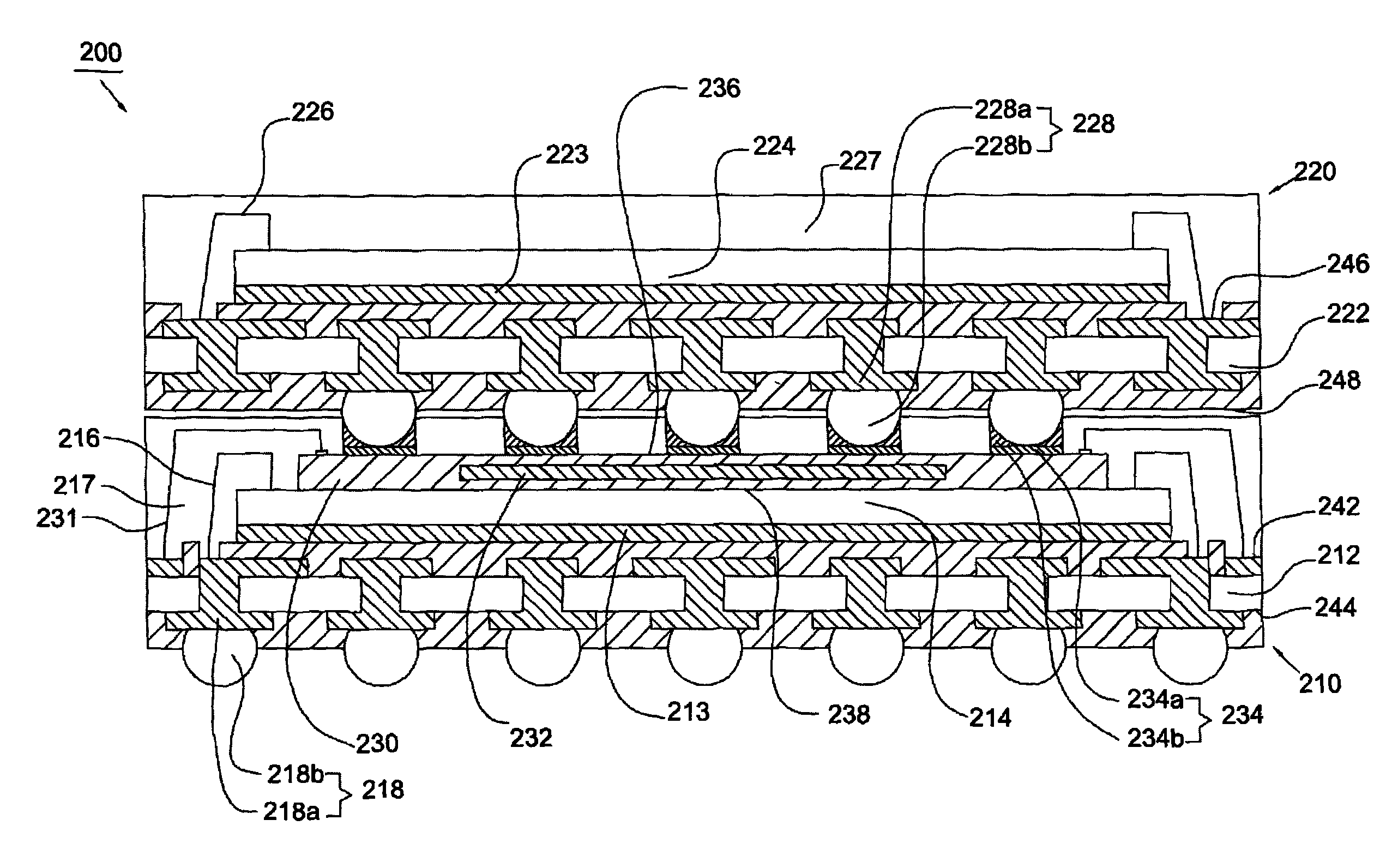

Package on package structure for semiconductor devices and method of the same

InactiveUS20080157327A1Low costImprove performanceSemiconductor/solid-state device detailsSolid-state devicesContact padPackage on package

A package on package structure for semiconductor devices comprises at least one first level package having at least first level semiconductor die therein, wherein the package having first level contact pads formed on a first upper and lower surfaces of the first level package, the first level package having a first level upper build up layers and / or a first level lower build up layer to couple to bonding pads of the first level semiconductor die to contact first level pads on the both upper and lower surfaces of the first level package; a second level package having at least one second semiconductor die contained therein, wherein the second level package has a second level contact pads on a second upper and lower surfaces of the second level package, and conductive connecting through holes; wherein the second level package have a second level upper build up layer and / or second level lower build up layer to couple second level bonding pads of the second semiconductor die to contact second level pads and the conductive connecting through holes on the upper and lower surface of the second level package, conductive through holes being coupled to the first level pads of upper and lower surfaces of the first level package and the second level pads of upper and lower surface of the second level package; and adhesion materials attached on lower surface of the first level package and the upper surface of the second level package.

Owner:ADVANCED CHIP ENG TECH

Semiconductor device package to improve functions of heat sink and ground shield

InactiveUS20080258293A1Improve cooling effectSimple processSemiconductor/solid-state device detailsSolid-state devicesContact padAdhesive

The present invention provides a package structure and a method for forming the same. The structure comprises a substrate with contact pads and through holes filled with conducting metals for performing heat dissipation and ground shielding A chip with bonding pads is attached on the contact pad by an adhesive with high thermal conductivity to achieve heat dissipation. A RDL is formed on the substrate and the chip to couple the bonding pad and the contact pad formed on the substrate. The structure of present invention can improve the thickness thereof, and the heat dissipation and ground shielding of the structure are enhanced. Furthermore, the structure can achieve package on package (PoP) structure.

Owner:ADVANCED CHIP ENG TECH

Integrated circuit packaging system with package on package support and method of manufacture thereof

ActiveUS20120319284A1Semiconductor/solid-state device detailsSolid-state devicesInterposerEngineering

A method of manufacture of an integrated packaging system includes: providing a substrate; mounting a die over the substrate; mounting an interposer having a slot over the die; covering a first encapsulant over the die and the interposer, a central region of the interposer exposed from the first encapsulant; and forming a hole through the first encapsulant to expose a peripheral portion of the interposer.

Owner:STATS CHIPPAC LTD