Multistage amplifier

A multi-stage amplifier and MOS tube technology, applied in the direction of amplifiers, differential amplifiers, DC-coupled DC amplifiers, etc., can solve the problems of amplifier gain bandwidth reduction, amplifier power supply voltage reduction, large circuit scale, etc., and achieve the effect of improving gain

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] As mentioned in the background section, in the prior art, the number of amplifier stages is usually increased to solve the technical problem of low gain and unity gain bandwidth of the amplifier.

[0034] Specifically, the inventor of the present application analyzed a multi-stage amplifier in the prior art.

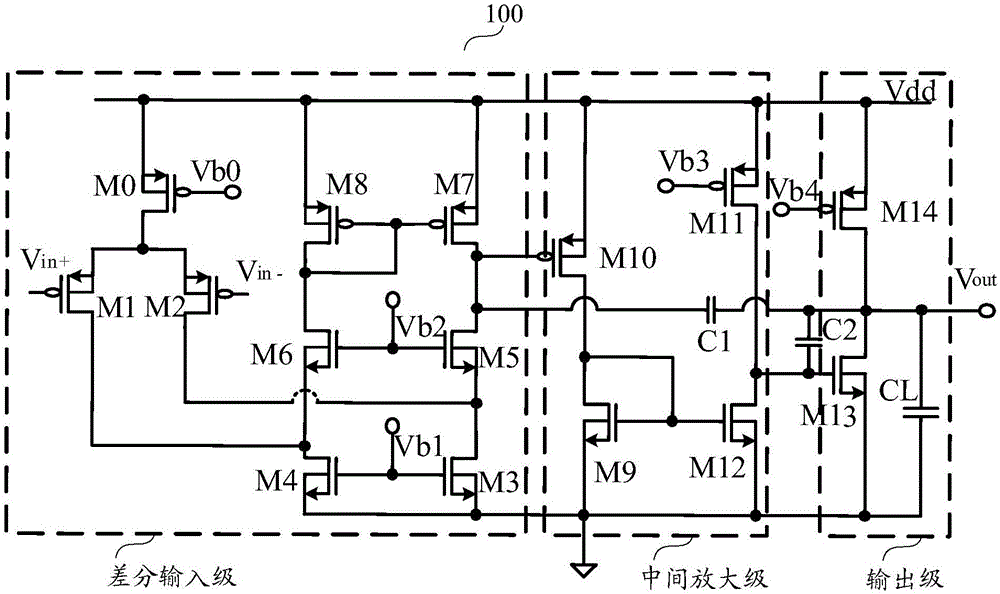

[0035] Such as figure 1 As shown, the multi-stage amplifier 100 may include a differential input stage, at least one intermediate amplification stage, and an output stage. The multi-stage amplifier 100 is only taken as an example including a single intermediate amplification stage.

[0036] In the differential input stage, the voltage-controlled current source composed of MOS transistor M0 is suitable for providing bias current to the outside to ensure the normal operation of the differential input stage; MOS transistors M1, M2, M3, and M4 constitute the folded differential input Cascode structure, MOS transistors M5 to M8 are differential input stage loads, whe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More