Full-automatic wafer test method and equipment accomplishing the method

A wafer test, fully automatic technology, applied in the direction of semiconductor/solid-state device test/measurement, electronic circuit test, single semiconductor device test, etc., can solve problems such as inability to judge the accuracy of dots, increase wafer test time, etc., to achieve test Low cost, high degree of automation and high efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The present invention will be further described below in conjunction with specific drawings and embodiments.

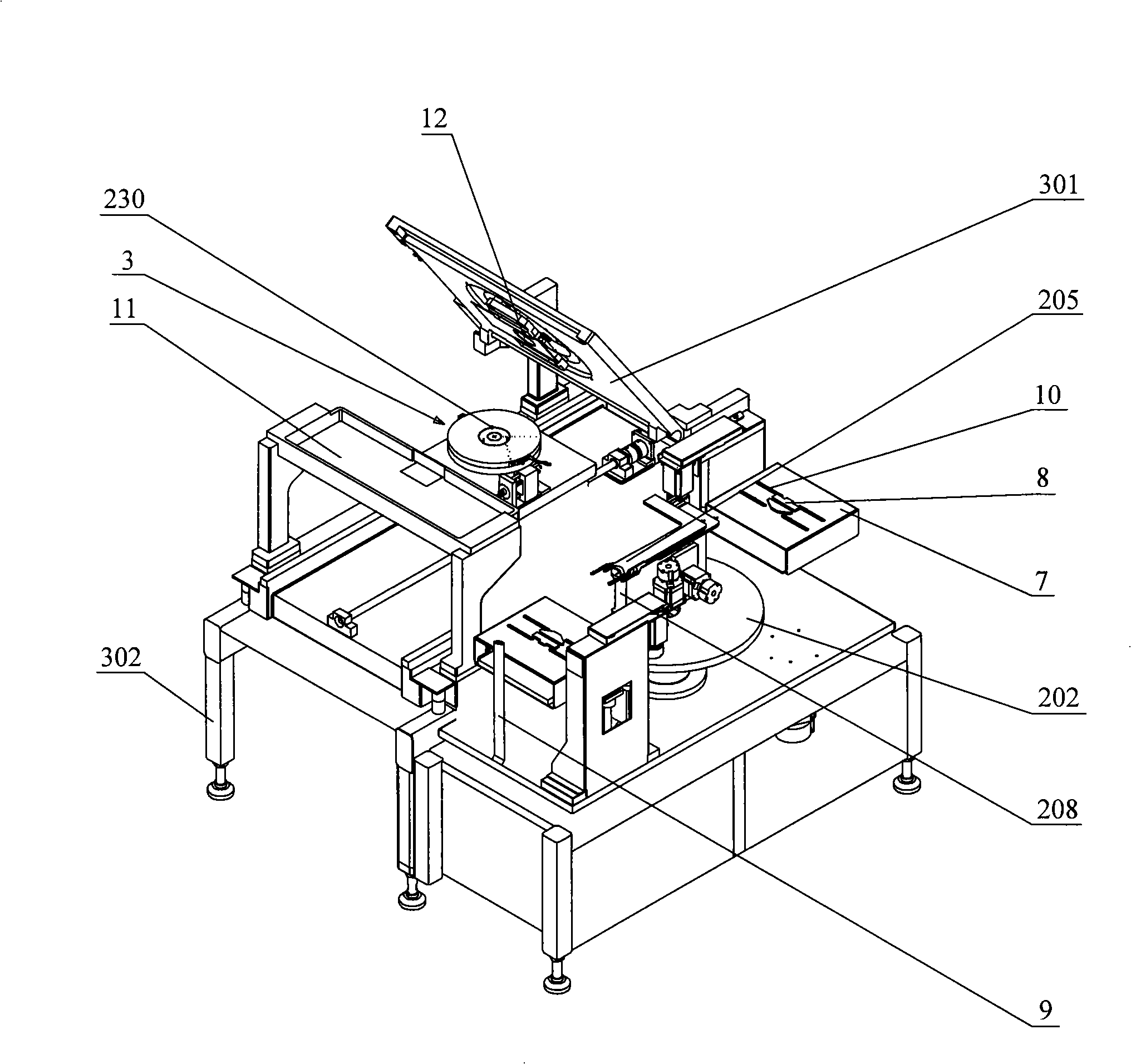

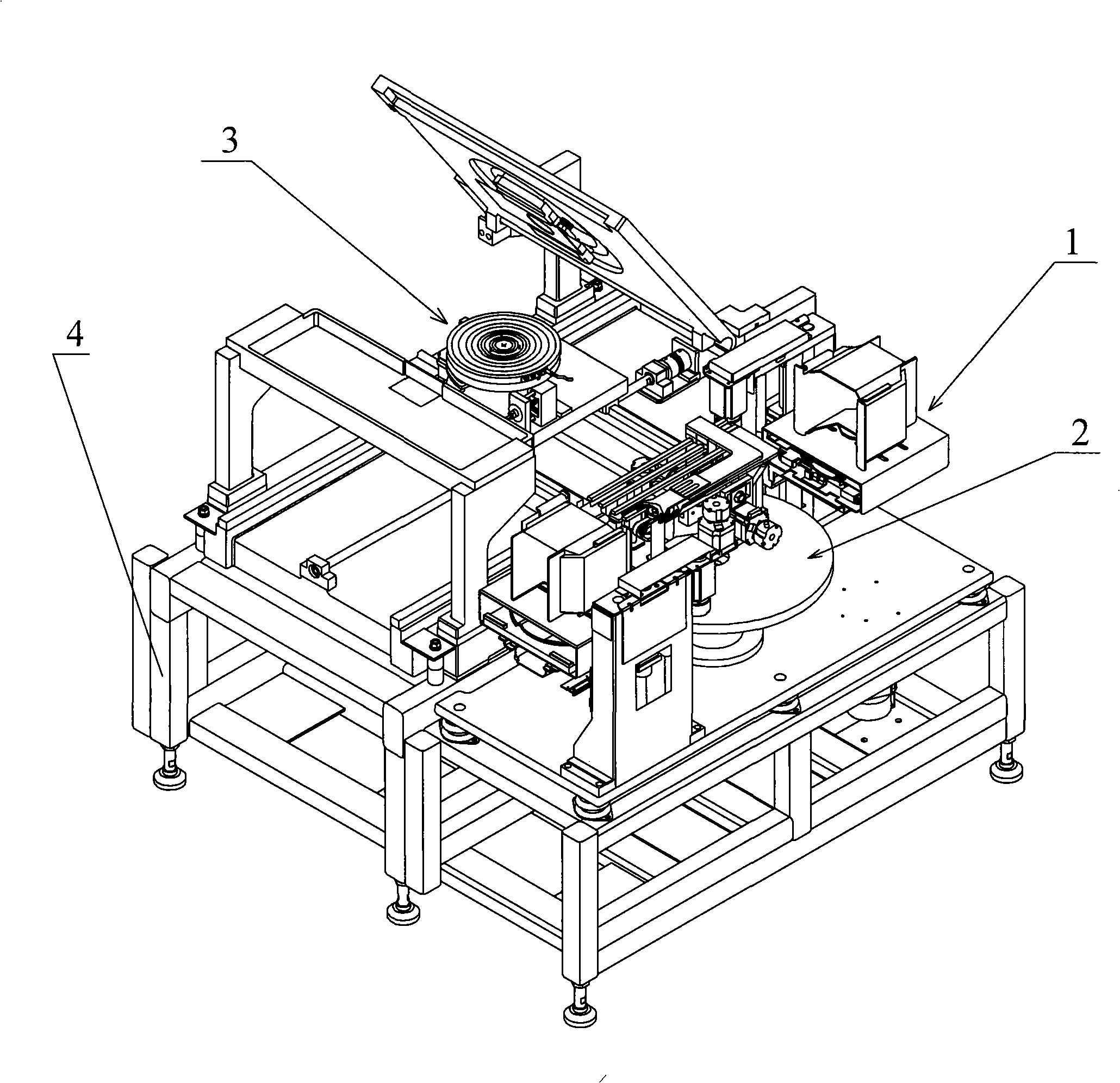

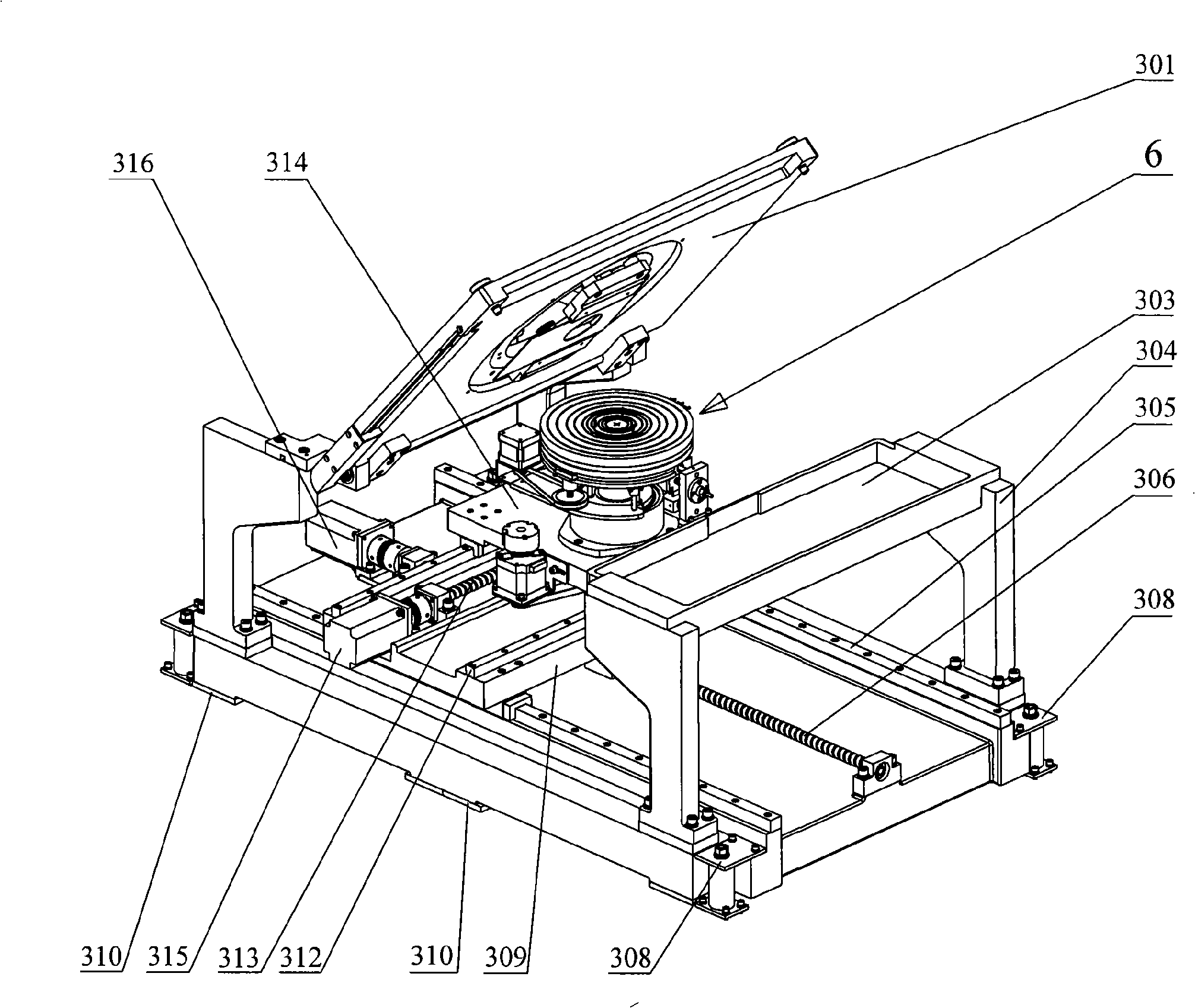

[0049] The fully automatic wafer testing method includes: a cassette placement frame 7 for carrying a wafer cassette 103; a wafer detection sensor 10 for recording the position and quantity of wafers in the cassette; taking a wafer clamp 205 for handling Wafer; the suction cup device 209 arranged on the top of the detection shaft 208 is used to rotate the wafer; the optical sensor mounting plate 11 is used to place the optical sensor for detecting the eccentricity of the wafer; the optical system is used to produce different multiples of the wafer Imaging; image acquisition device, used to obtain wafer images; computer, used to process image data and motion data; motion control card connected with computer, used to control motor drive mechanism; motor drive mechanism, used to obtain motion instructions and drive motor.

[0050] Such as figure 1 , the host is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More