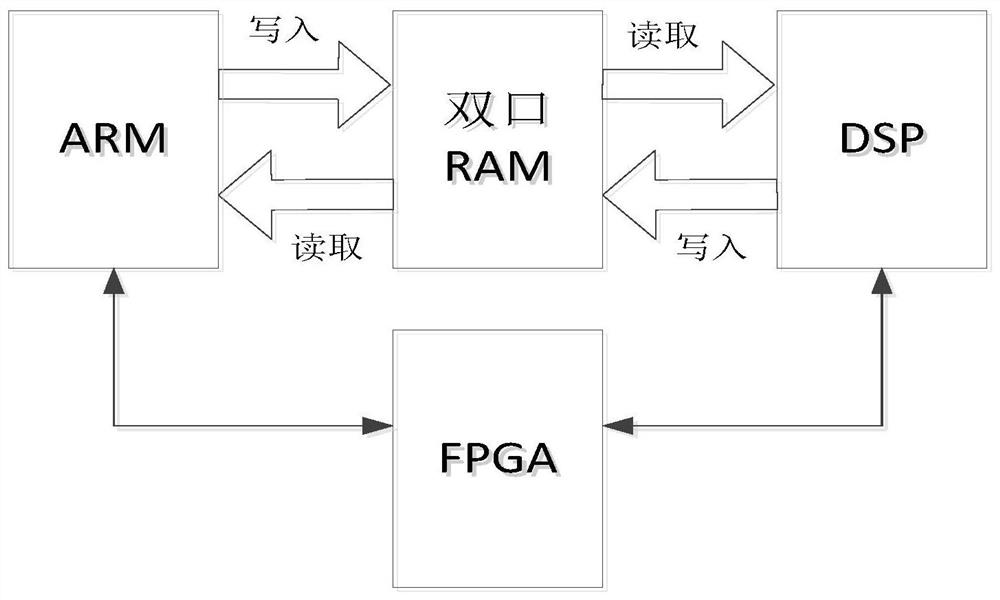

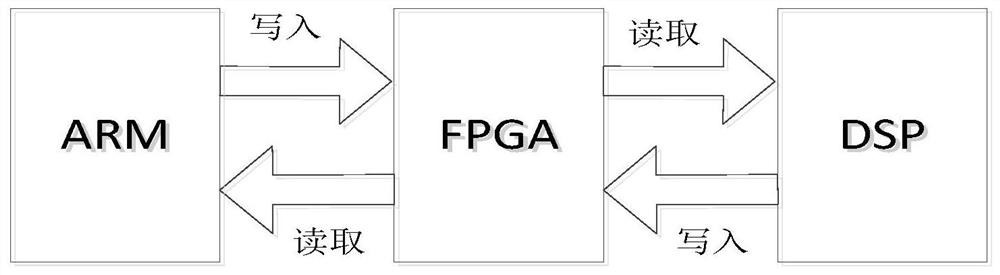

Asynchronous data interaction method and system based on ARM + FPGA + DSP architecture

A technology of asynchronous data and interactive methods, applied in the field of control systems, can solve problems such as low reliability of asynchronous data transmission and uncertain delay, and achieve the effects of improving communication efficiency, ensuring correctness, and stable and reliable transmission

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0074] This embodiment illustrates the structure of the data frame and its application on the basis of the above-mentioned principle of the present invention.

[0075] In order to ensure the reliability and stability of data transmission, in the communication protocol, this embodiment adds a heartbeat signal to judge whether there is new data input. At the same time, a CRC checksum is added to the protocol to ensure that the data is Integrity in. This embodiment adopts the following communication protocol for communication:

[0076] The structure of the data frame that the ARM of the present embodiment sends to DSP is as Figure 6 As shown, the data frame includes a 5-byte data header, a 1-byte data checksum, and variable-length data content. The data header includes a 2-byte heartbeat signal and a 1-byte function code. 2 bytes of data length information. In order to improve the efficiency of data interaction, it is stipulated that the data length of a frame is up to 64 byt...

Embodiment 2

[0088] This embodiment describes the reverse data transmission from DSP to ARM. This embodiment can be used in combination with Embodiment 1.

[0089] When the DSP needs to send data to the ARM, the specific transmission process is as follows Figure 8 shown.

[0090] 1) The DSP encapsulates the data to be sent according to the format of the data transmission protocol, and sends the encapsulated data to the FPGA through the UPP interface;

[0091] 2) The FPGA writes the received UPP data into the internal dual-port RAM;

[0092] 3) ARM checks whether there is any data received by means of circular query. That is, ARM checks the data in the dual-port RAM every fixed period. If the heartbeat signal of the data in the dual-port RAM is the current ARM heartbeat signal data plus 1, it means that there is data reception.

Embodiment 3

[0094] This embodiment is basically the same as Embodiment 1, the difference is that the FPGA and the DSP in this embodiment adopt dual-port RAM communication, such as Figure 9 Shown: When the FPGA receives the ARM data and sends it to the DSP through the dual-port RAM, the DSP checks whether there is new data to receive by polling. The real-time performance of this embodiment is worse than that of Embodiment 1, and the hardware resource consumption of the increased FPGA is more than that of Embodiment 1.

[0095] To sum up, the present invention can significantly improve communication efficiency; through the asynchronous data interaction method, stable and reliable data transmission among the three can be realized. And add heartbeat information and data verification to the data frame, analyze the data according to the change of the heartbeat information, improve the efficiency of data analysis, avoid unnecessary data analysis; data verification can ensure the correctness of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More