Patents

Literature

108 results about "Crossbar array" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

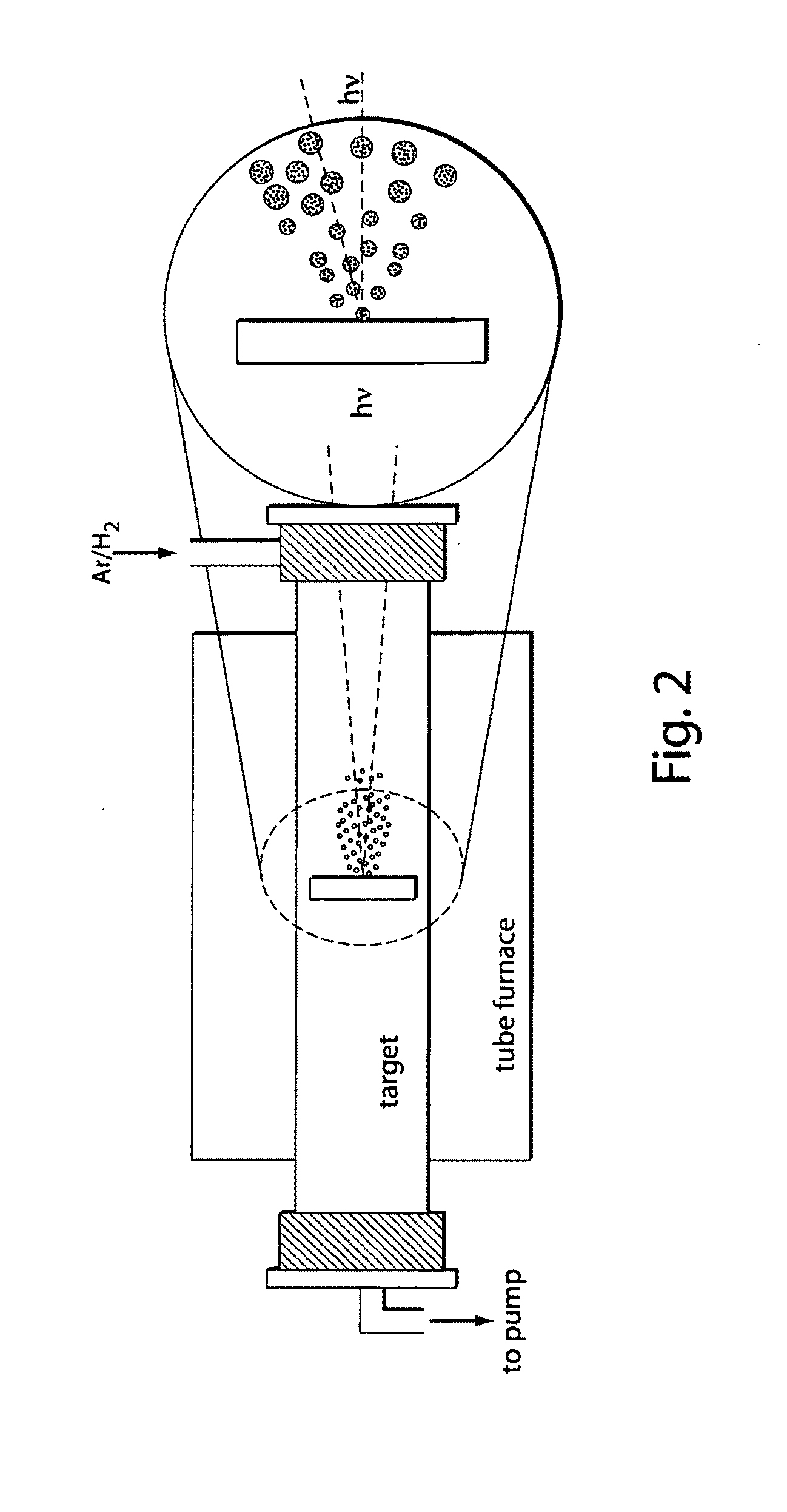

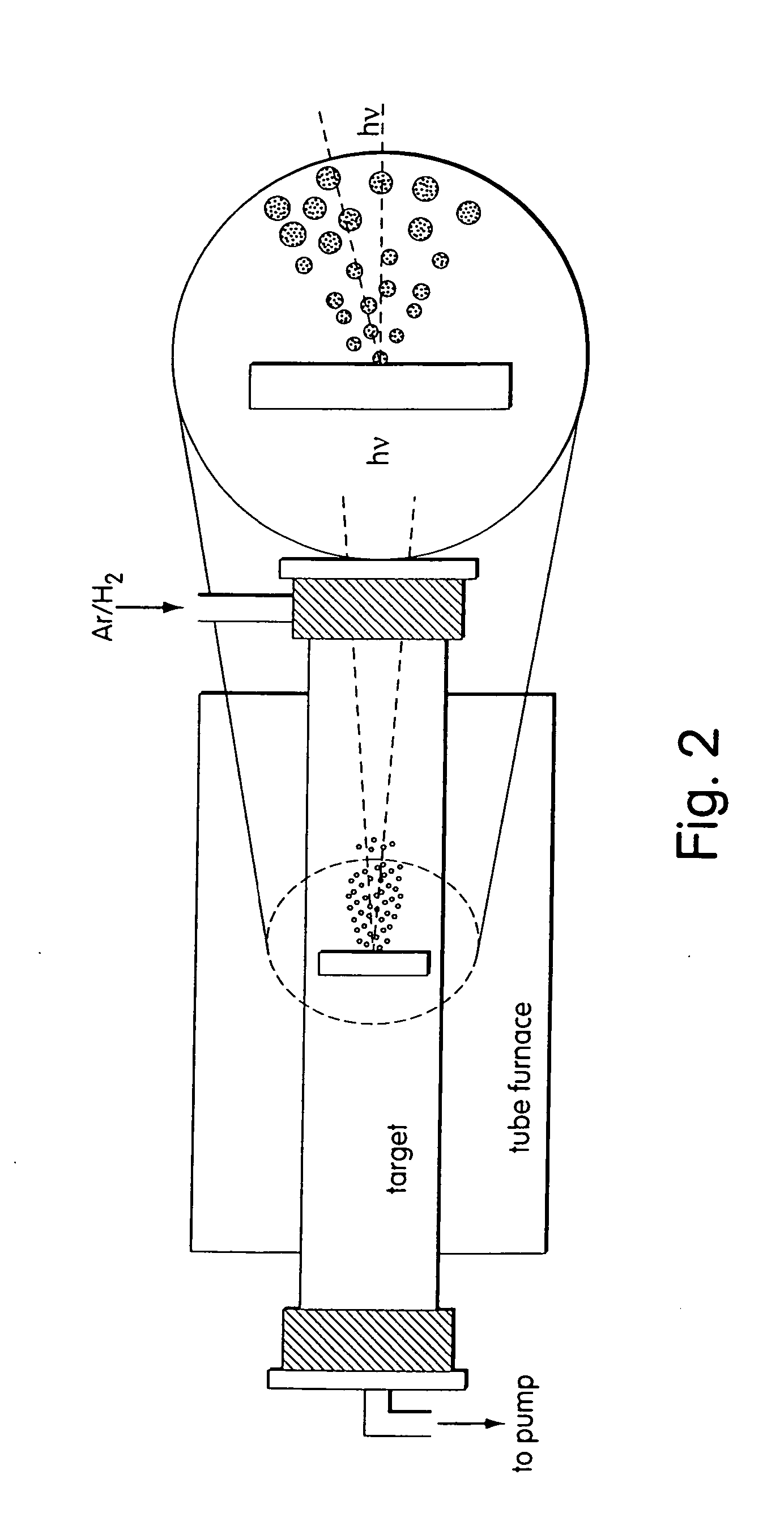

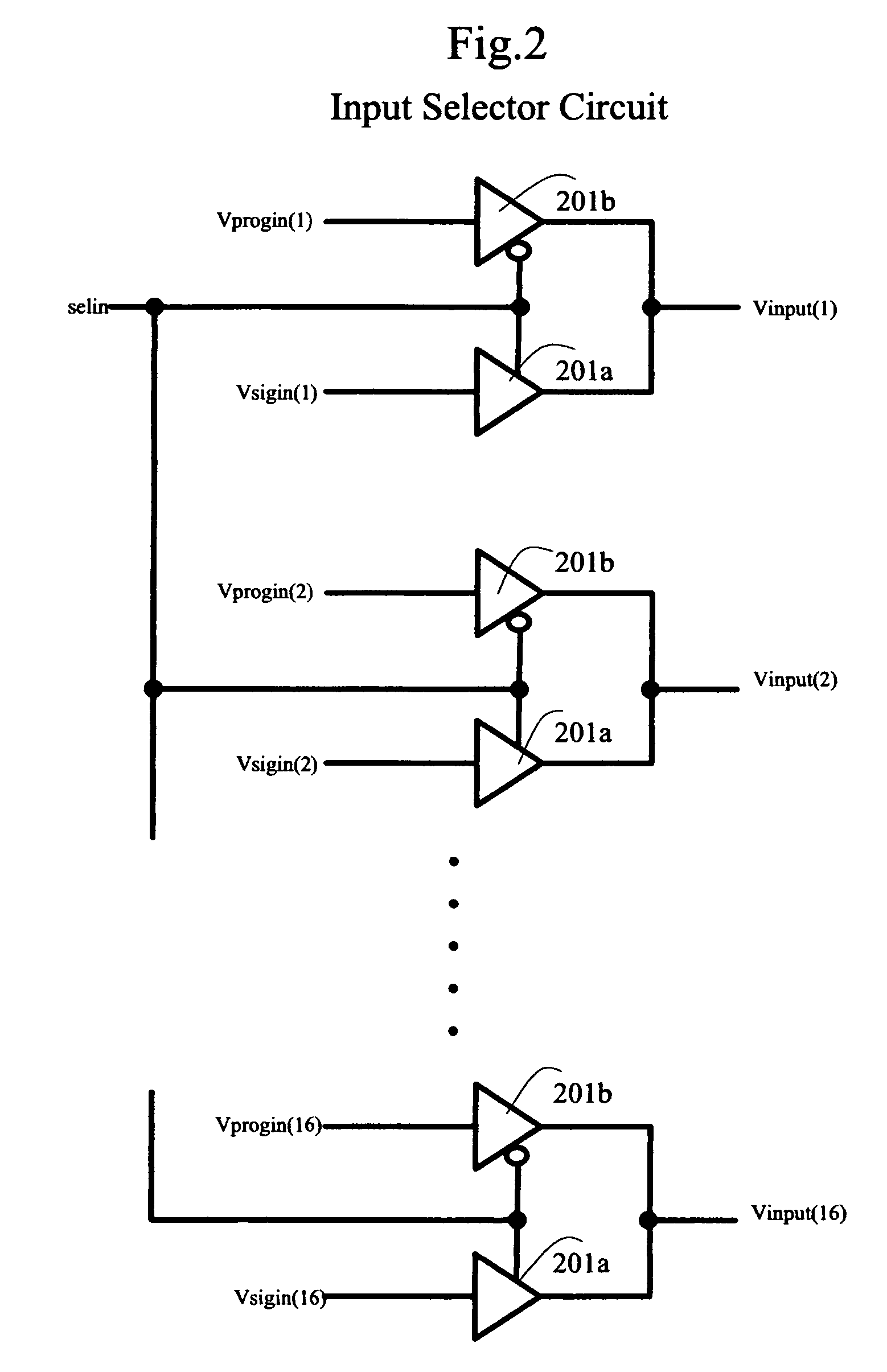

Nanoscopic wire-based devices, arrays, and methods of their manufacture

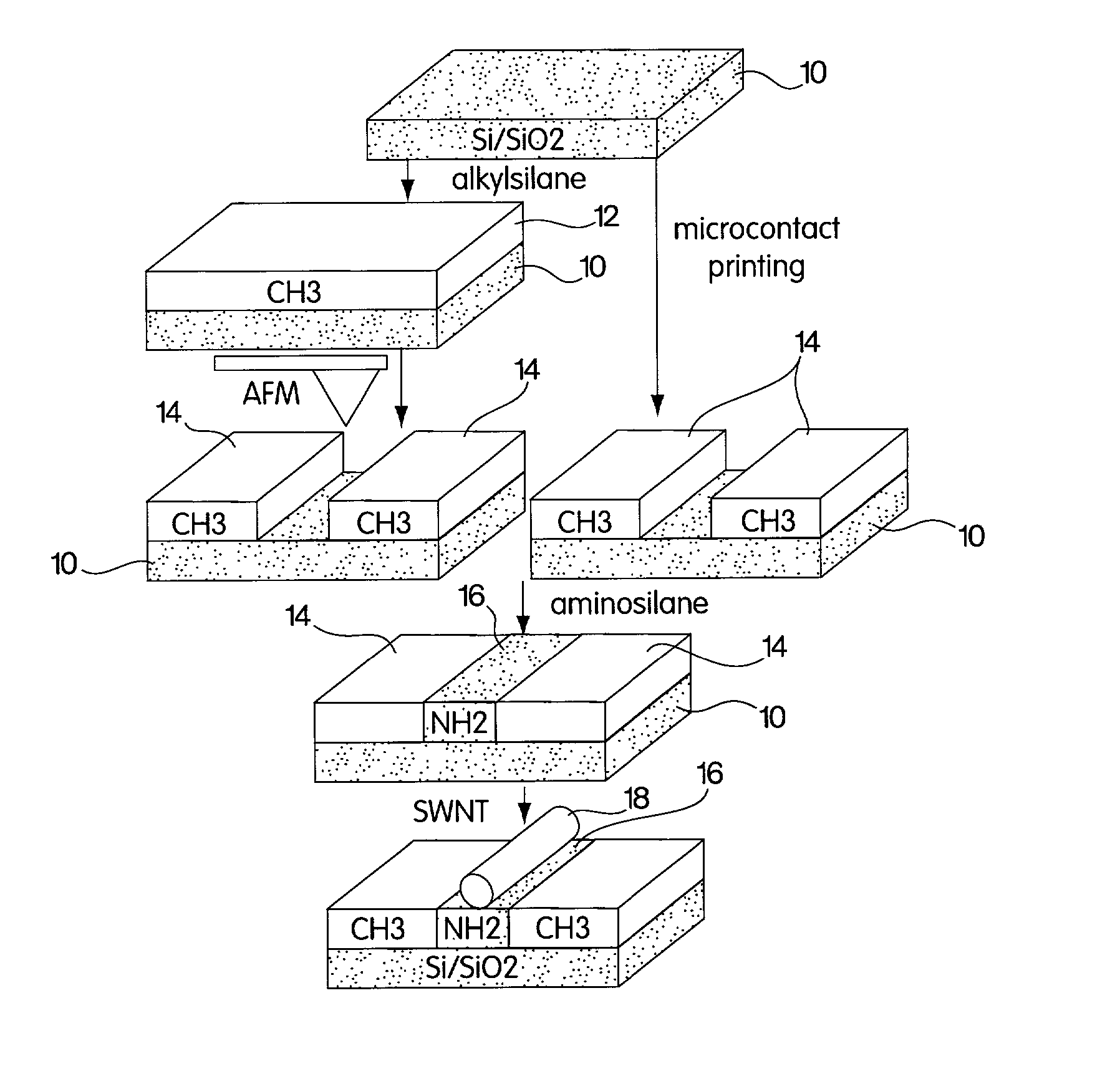

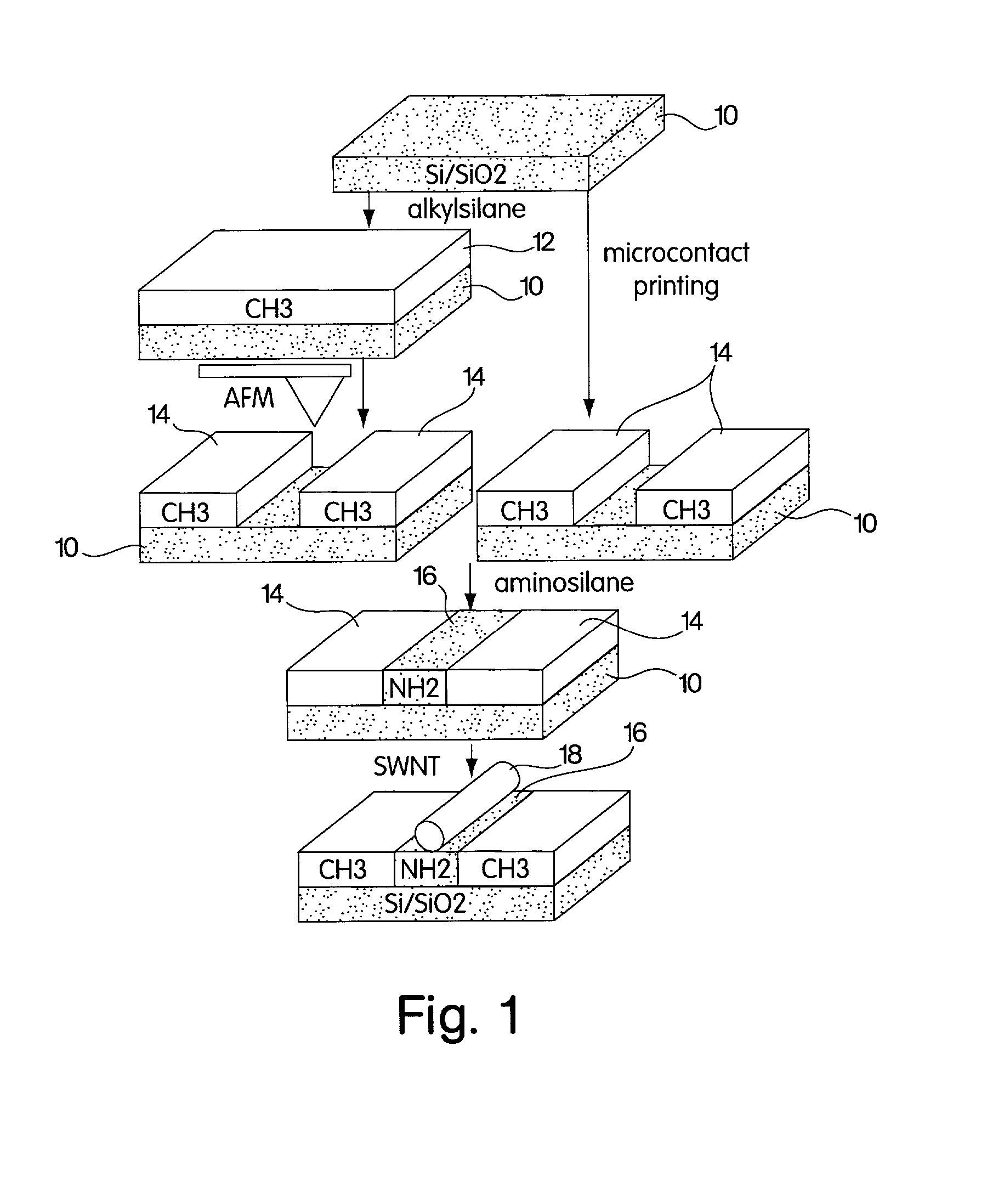

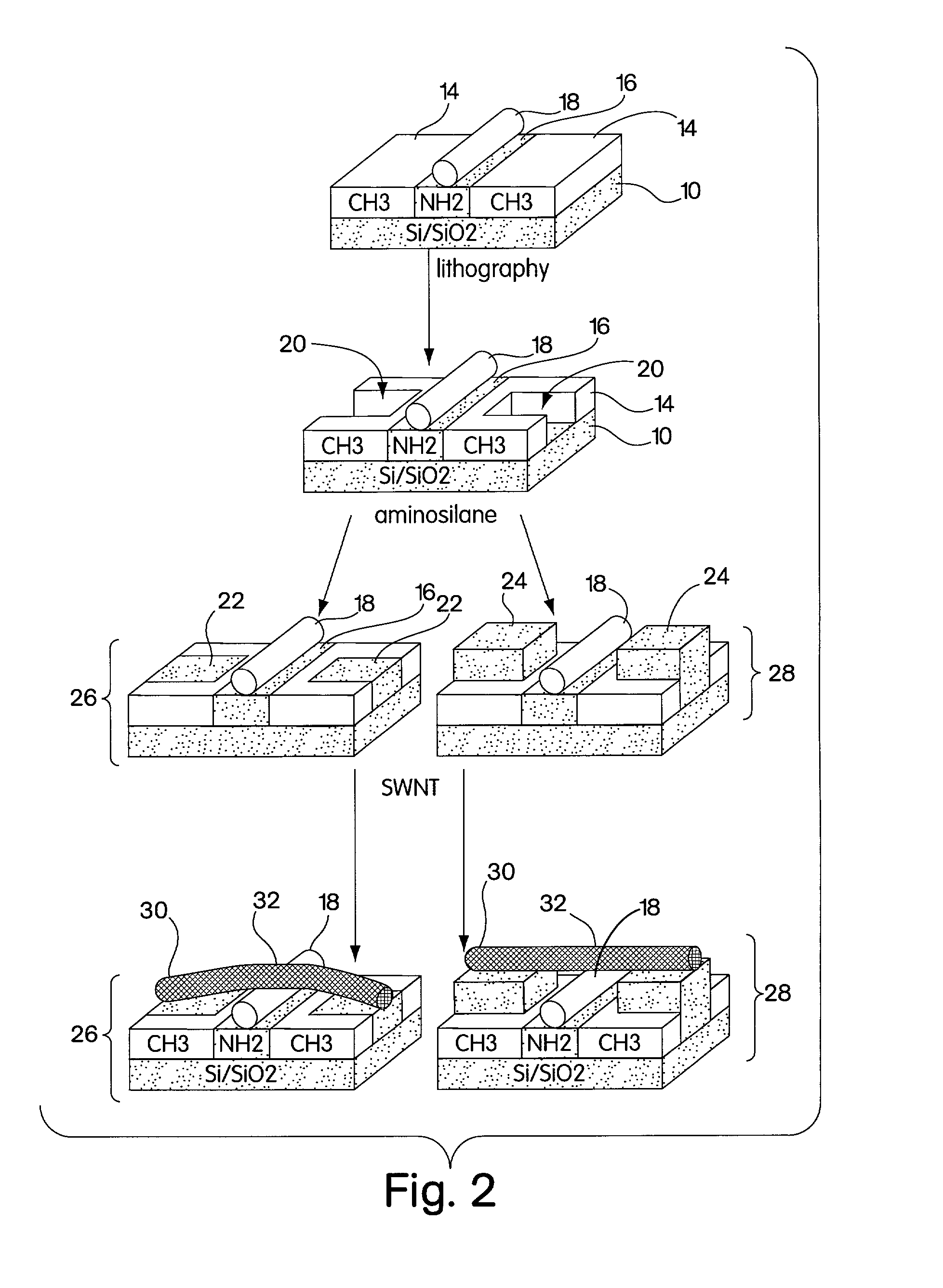

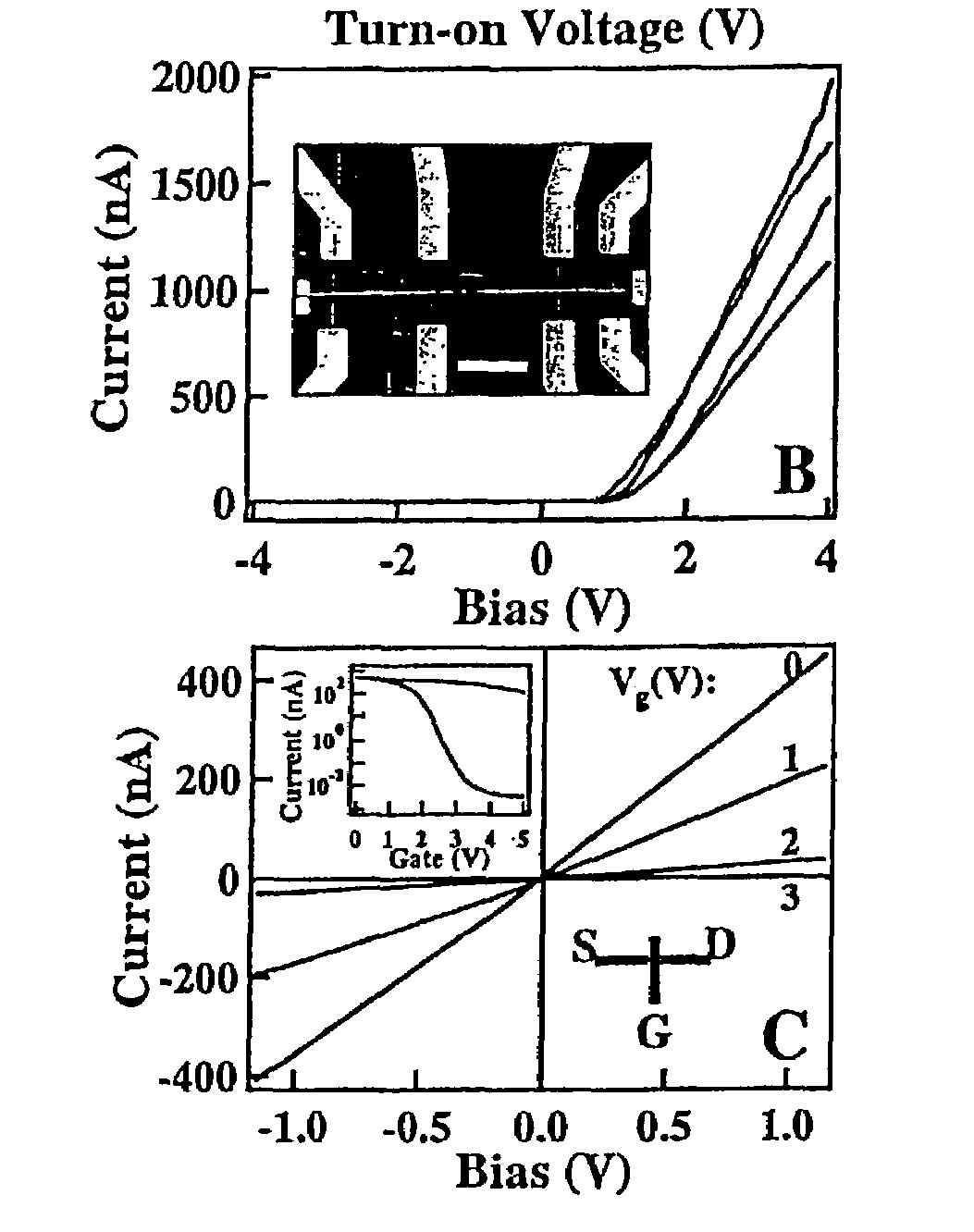

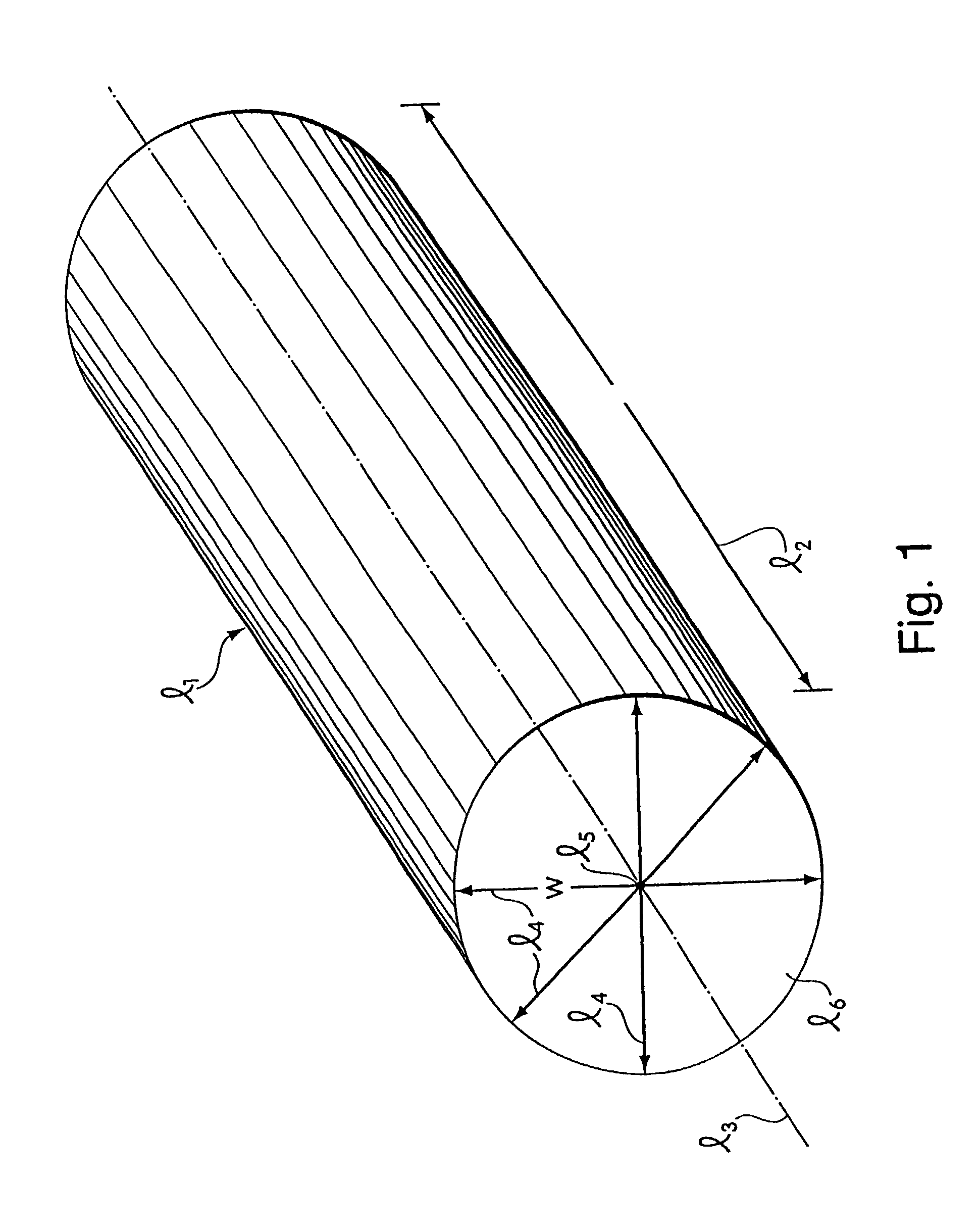

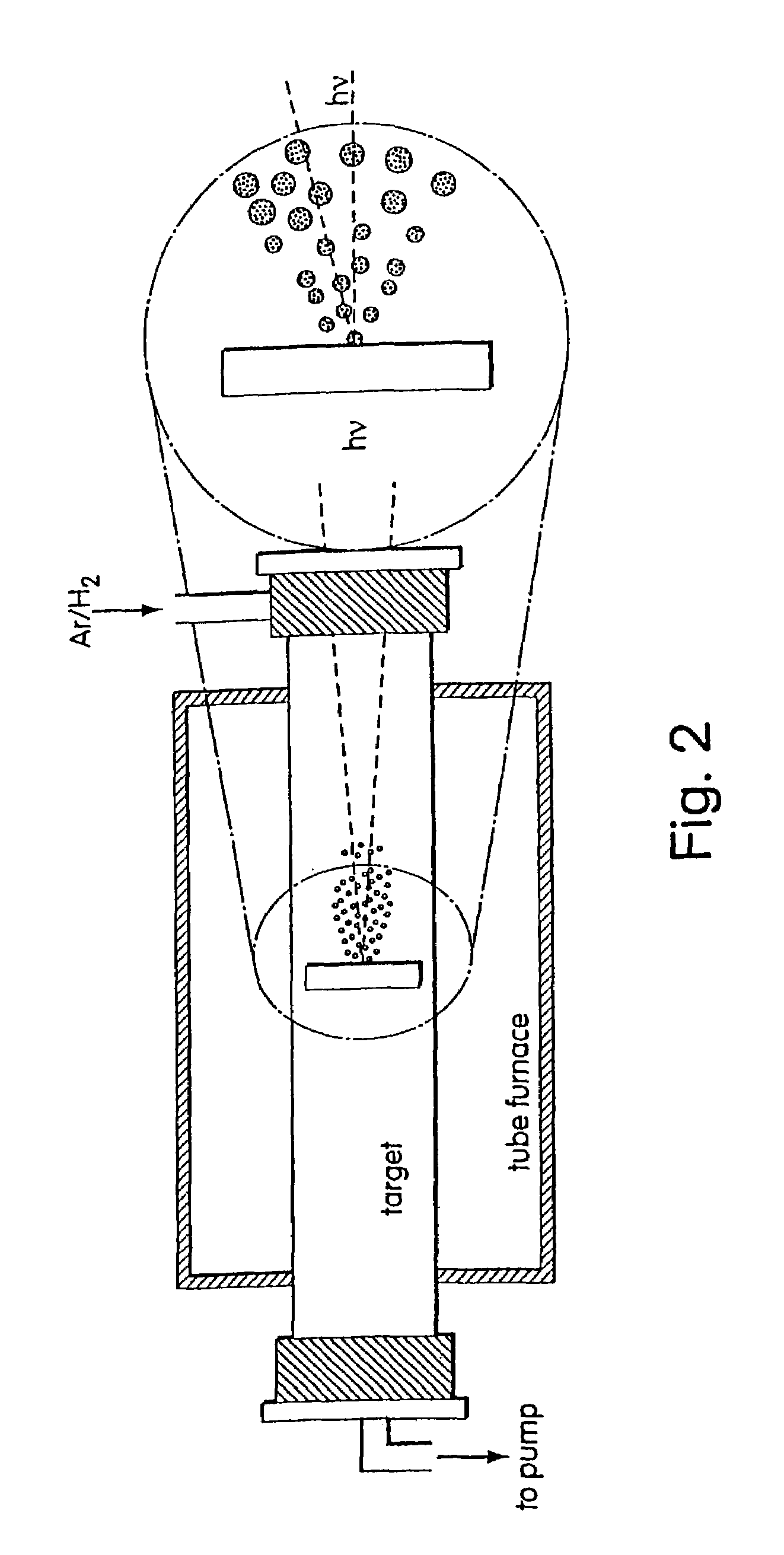

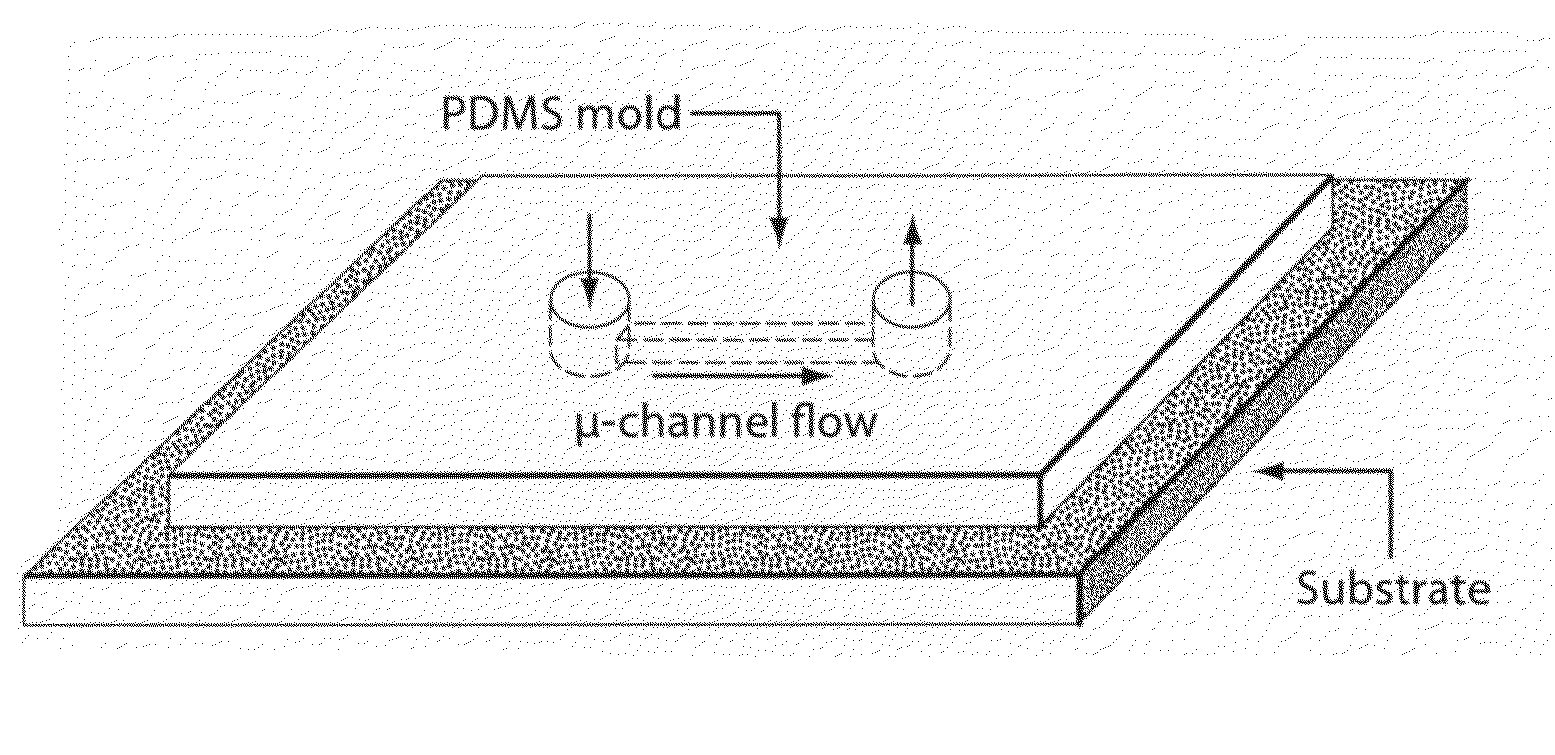

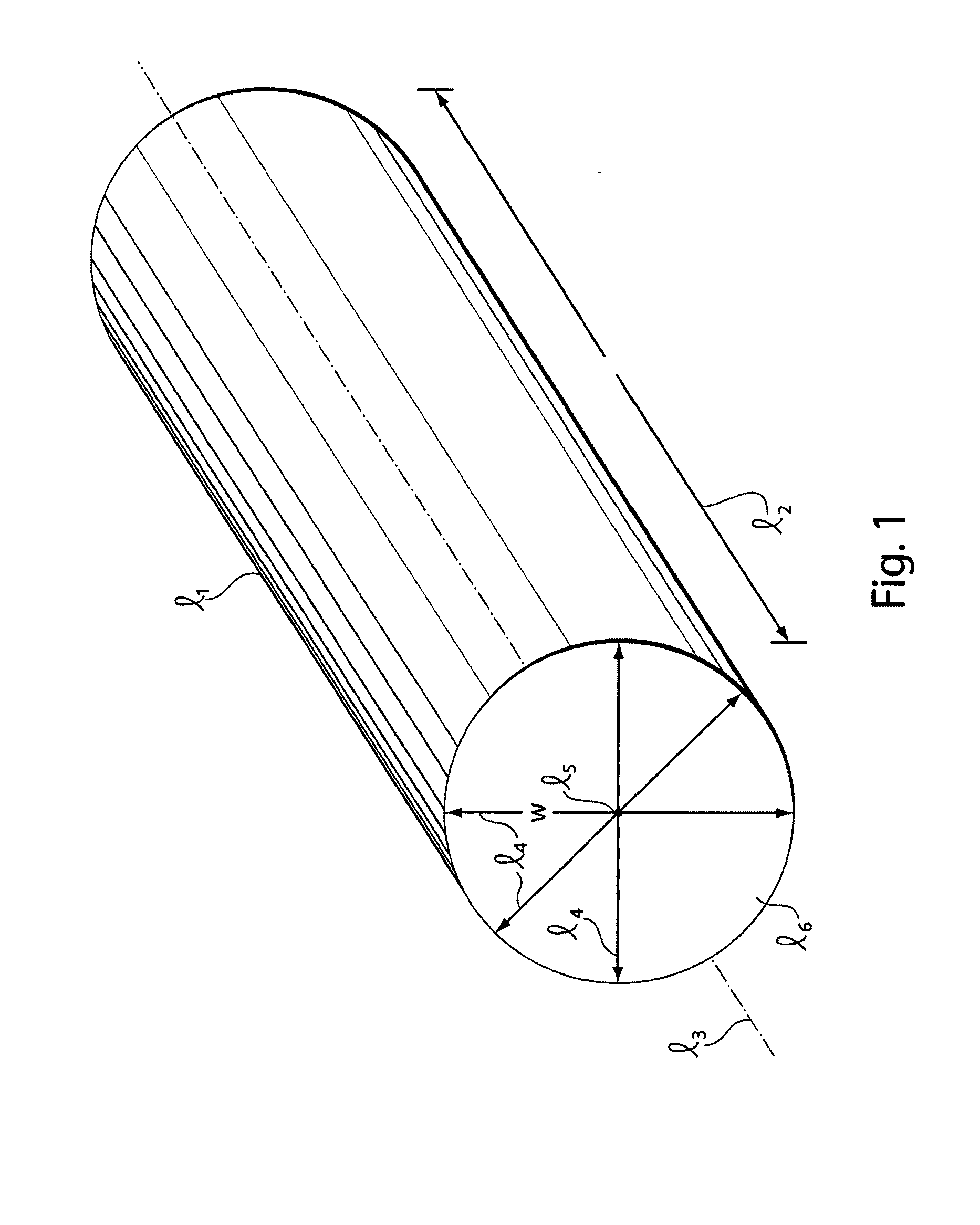

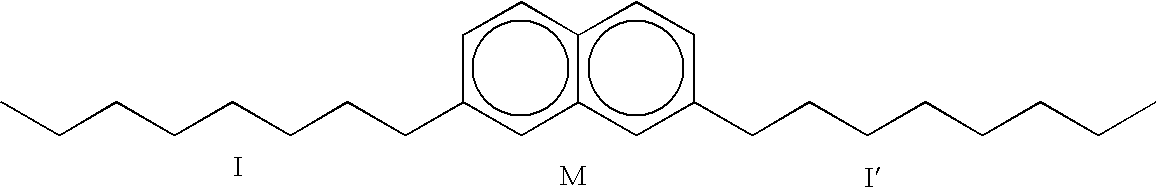

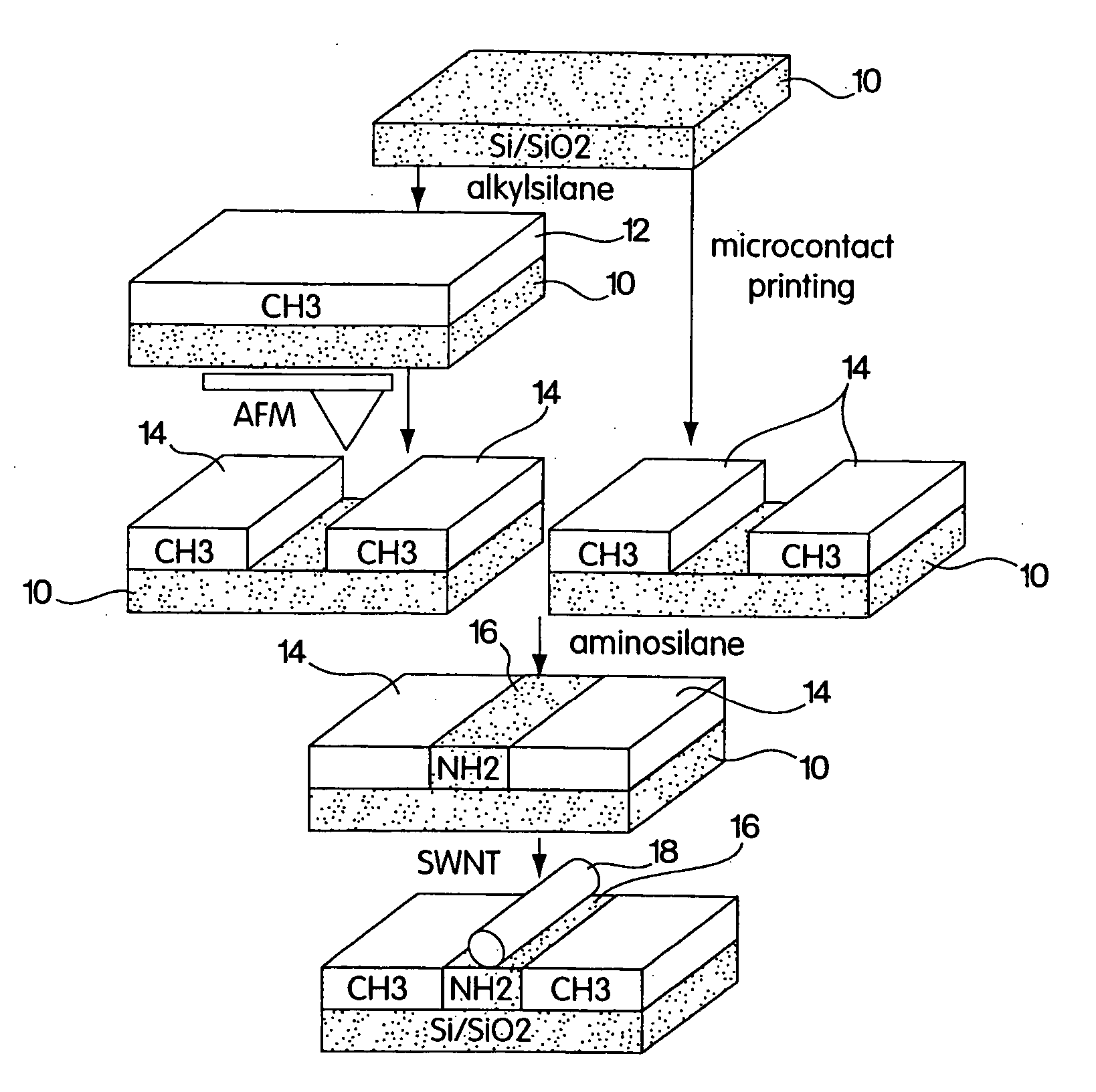

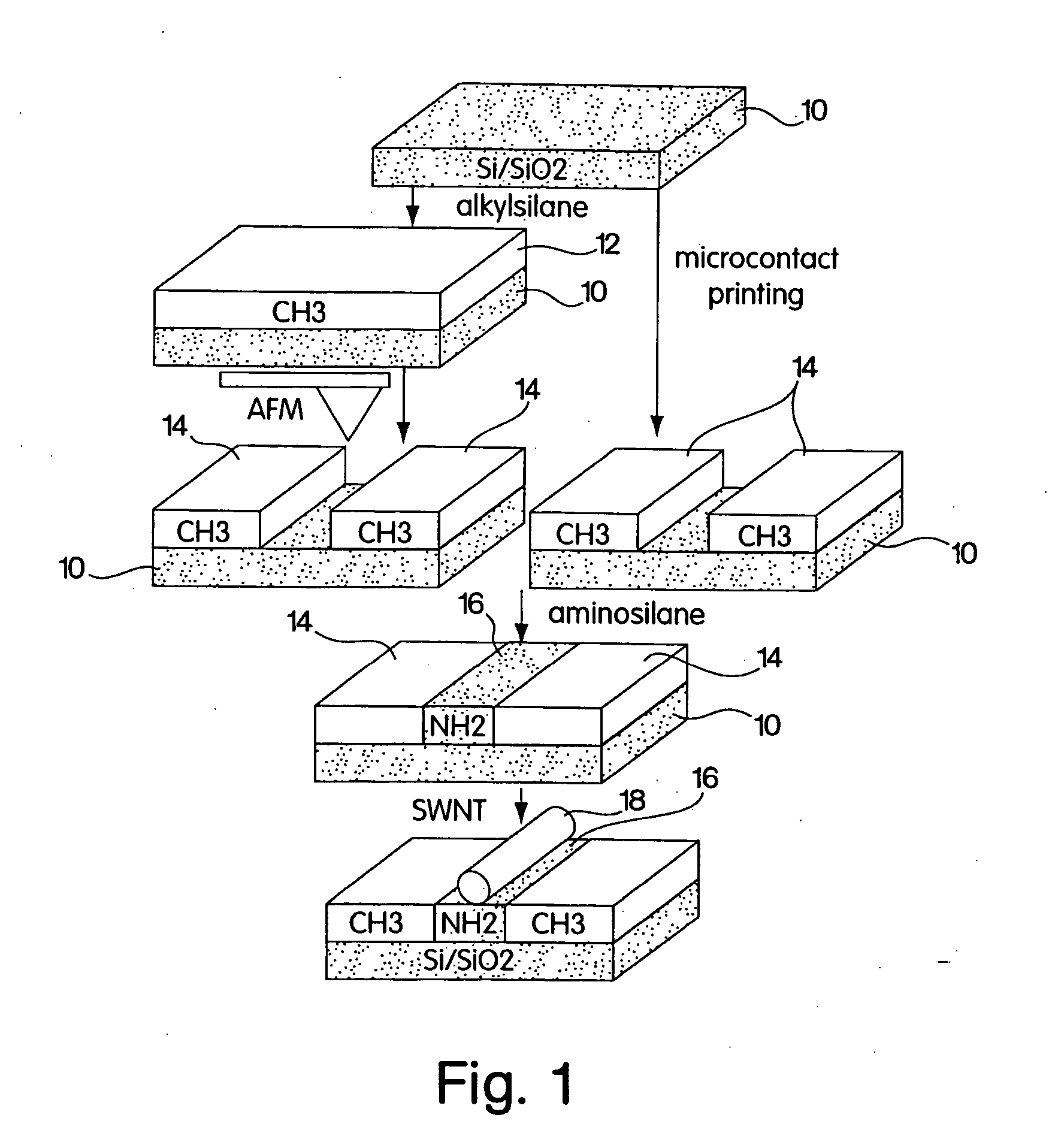

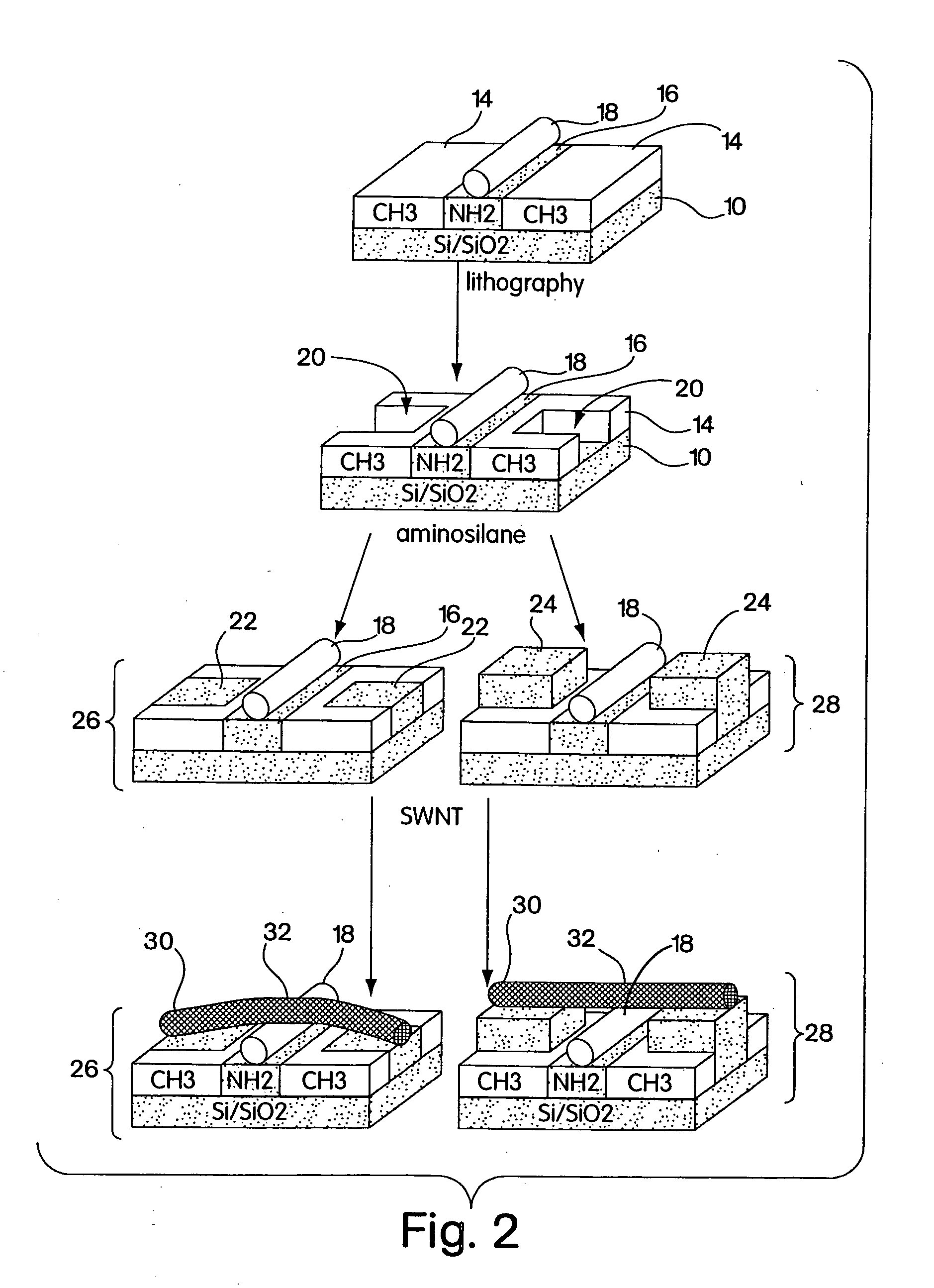

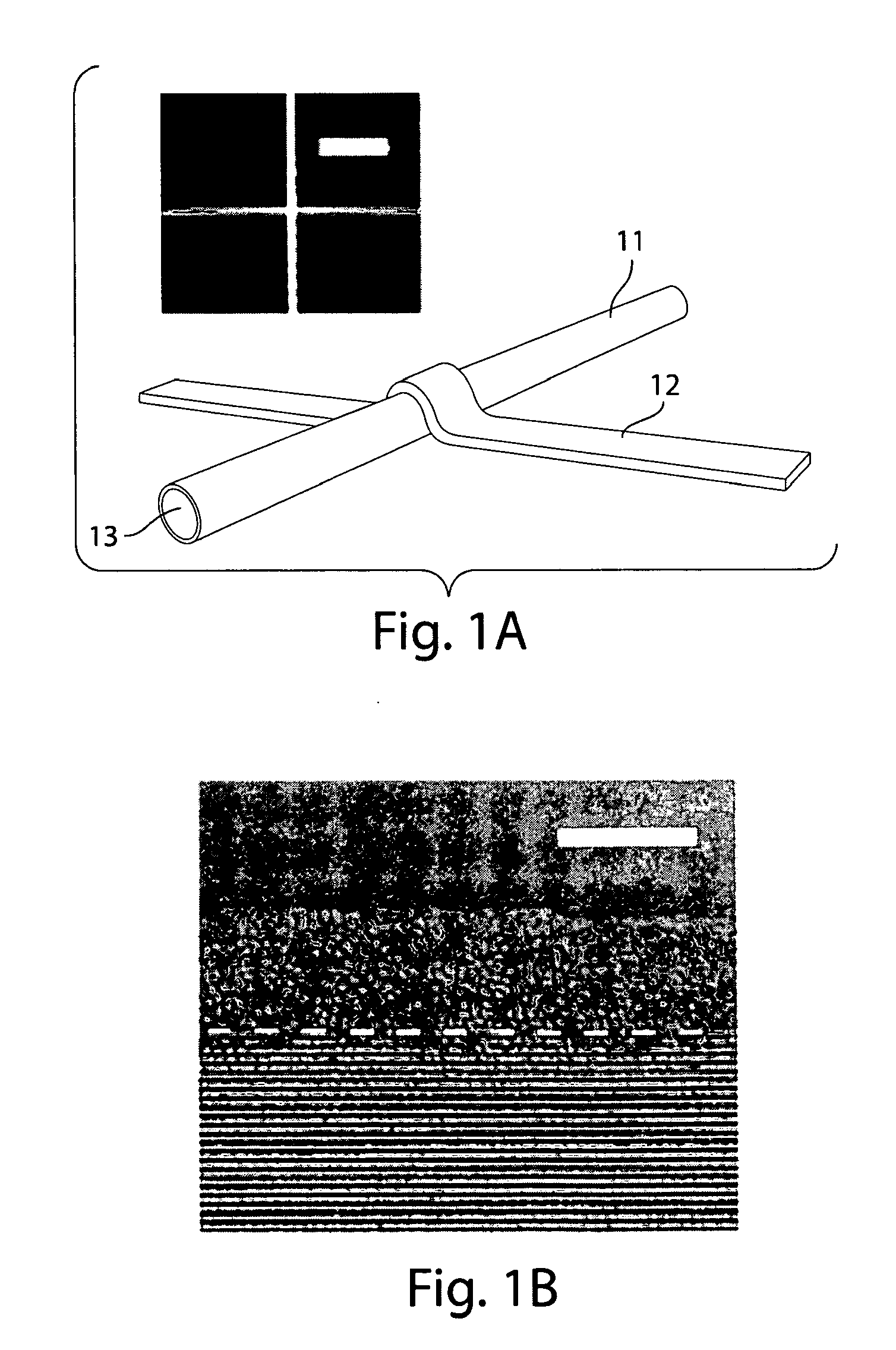

Electrical devices comprised of nanoscopic wires are described, along with methods of their manufacture and use. The nanoscopic wires can be nanotubes, preferably single-walled carbon nanotubes. They can be arranged in crossbar arrays using chemically patterned surfaces for direction, via chemical vapor deposition. Chemical vapor deposition also can be used to form nanotubes in arrays in the presence of directing electric fields, optionally in combination with self-assembled monolayer patterns. Bistable devices are described.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

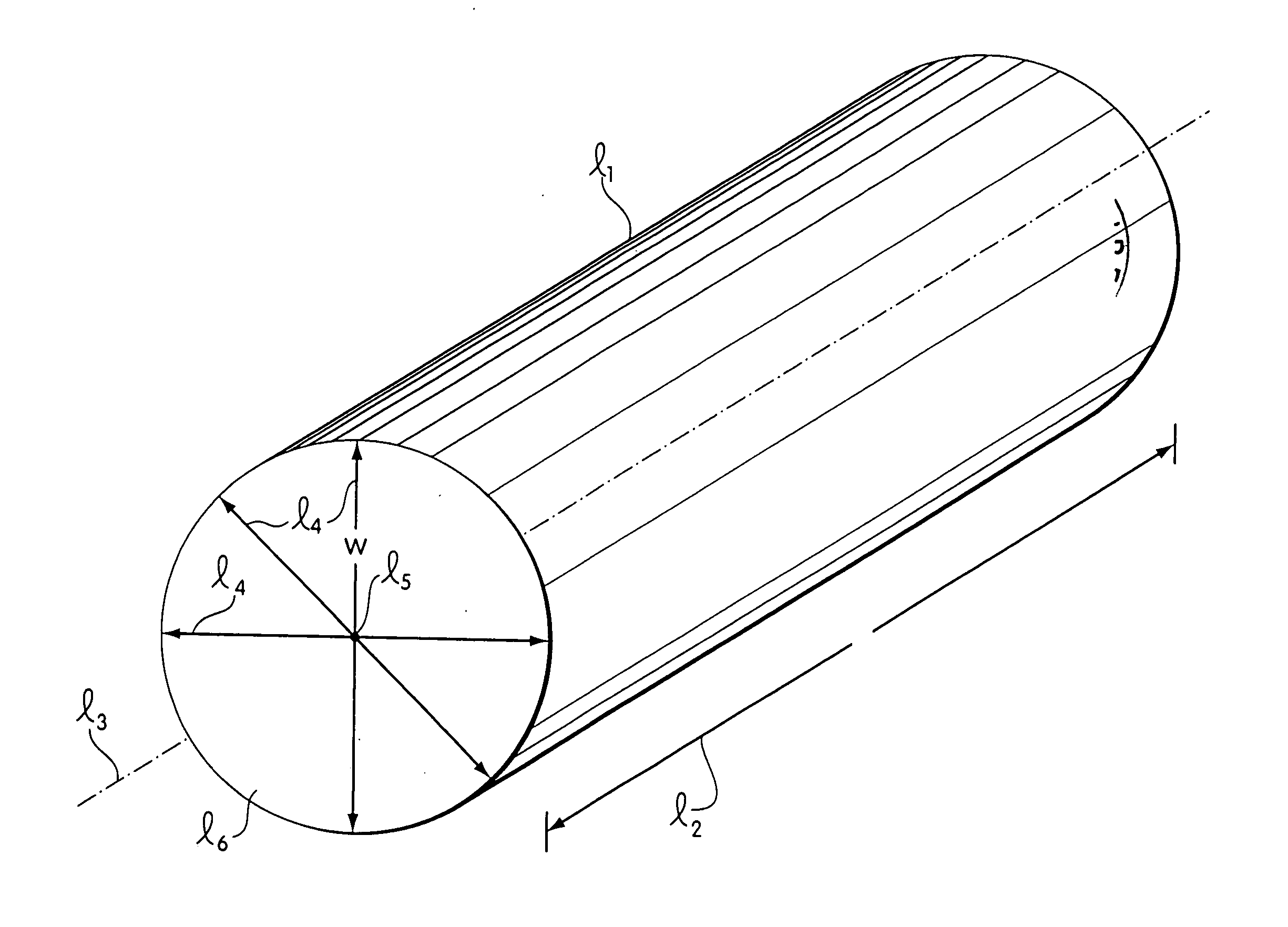

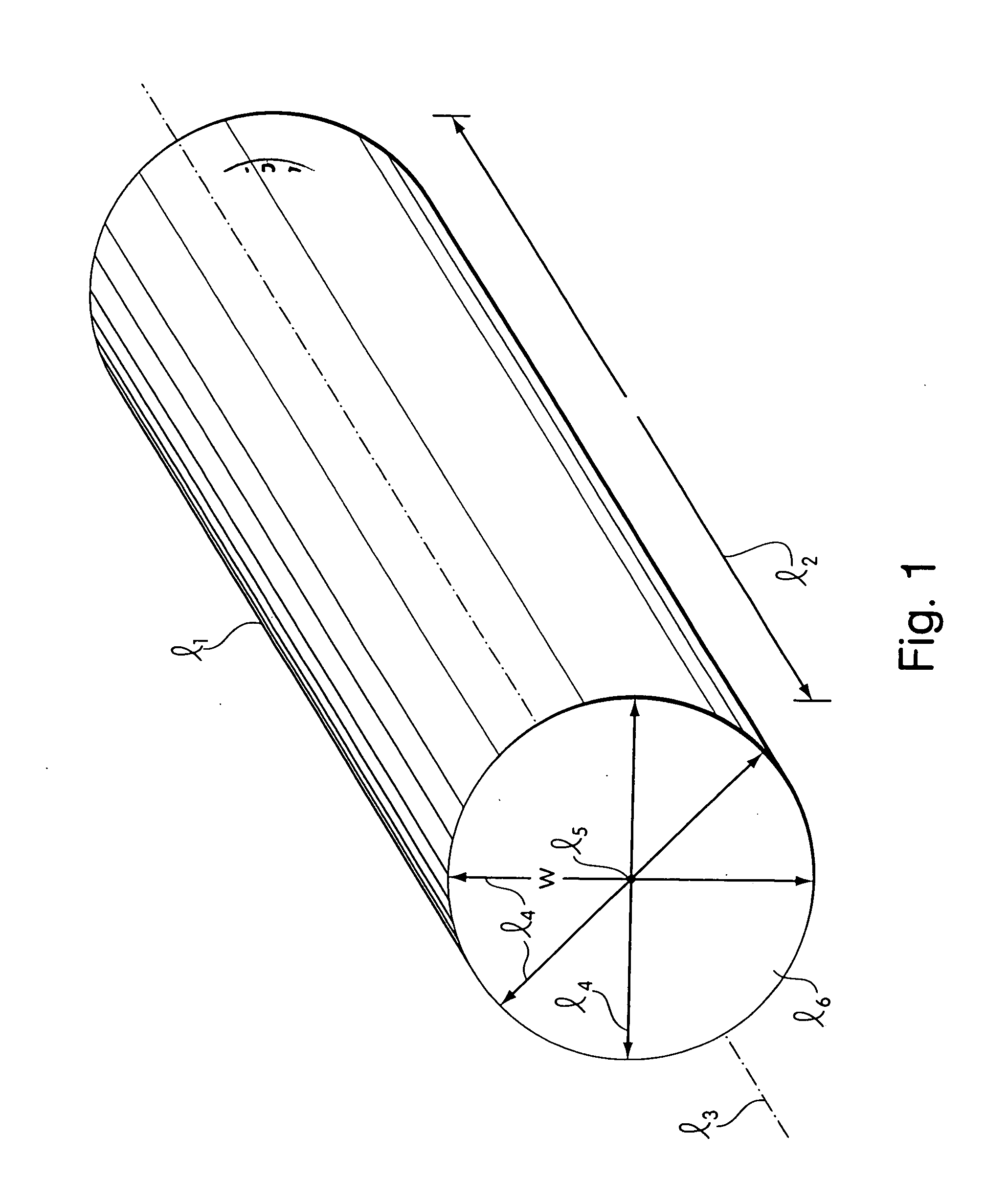

Nanoscale wires and related devices

InactiveUS7301199B2Material nanotechnologySemiconductor/solid-state device detailsDopantTunnel diode

The present invention relates generally to sub-microelectronic circuitry, and more particularly to nanometer-scale articles, including nanoscale wires which can be selectively doped at various locations and at various levels. In some cases, the articles may be single crystals. The nanoscale wires can be doped, for example, differentially along their length, or radially, and either in terms of identity of dopant, concentration of dopant, or both. This may be used to provide both n-type and p-type conductivity in a single item, or in different items in close proximity to each other, such as in a crossbar array. The fabrication and growth of such articles is described, and the arrangement of such articles to fabricate electronic, optoelectronic, or spintronic devices and components. For example, semiconductor materials can be doped to form n-type and p-type semiconductor regions for making a variety of devices such as field effect transistors, bipolar transistors, complementary inverters, tunnel diodes, light emitting diodes, sensors, and the like.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

Nanoscale wires and related devices

The present invention relates generally to sub-microelectronic circuitry, and more particularly to nanometer-scale articles, including nanoscale wires which can be selectively doped at various locations and at various levels. In some cases, the articles may be single crystals. The nanoscale wires can be doped, for example, differentially along their length, or radially, and either in terms of identity of dopant, concentration of dopant, or both. This may be used to provide both n-type and p-type conductivity in a single item, or in different items in close proximity to each other, such as in a crossbar array. The fabrication and growth of such articles is described, and the arrangement of such articles to fabricate electronic, optoelectronic, or spintronic devices and components. For example, semiconductor materials can be doped to form n-type and p-type semiconductor regions for making a variety of devices such as field effect transistors, bipolar transistors, complementary inverters, tunnel diodes, light emitting diodes, sensors, and the like.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

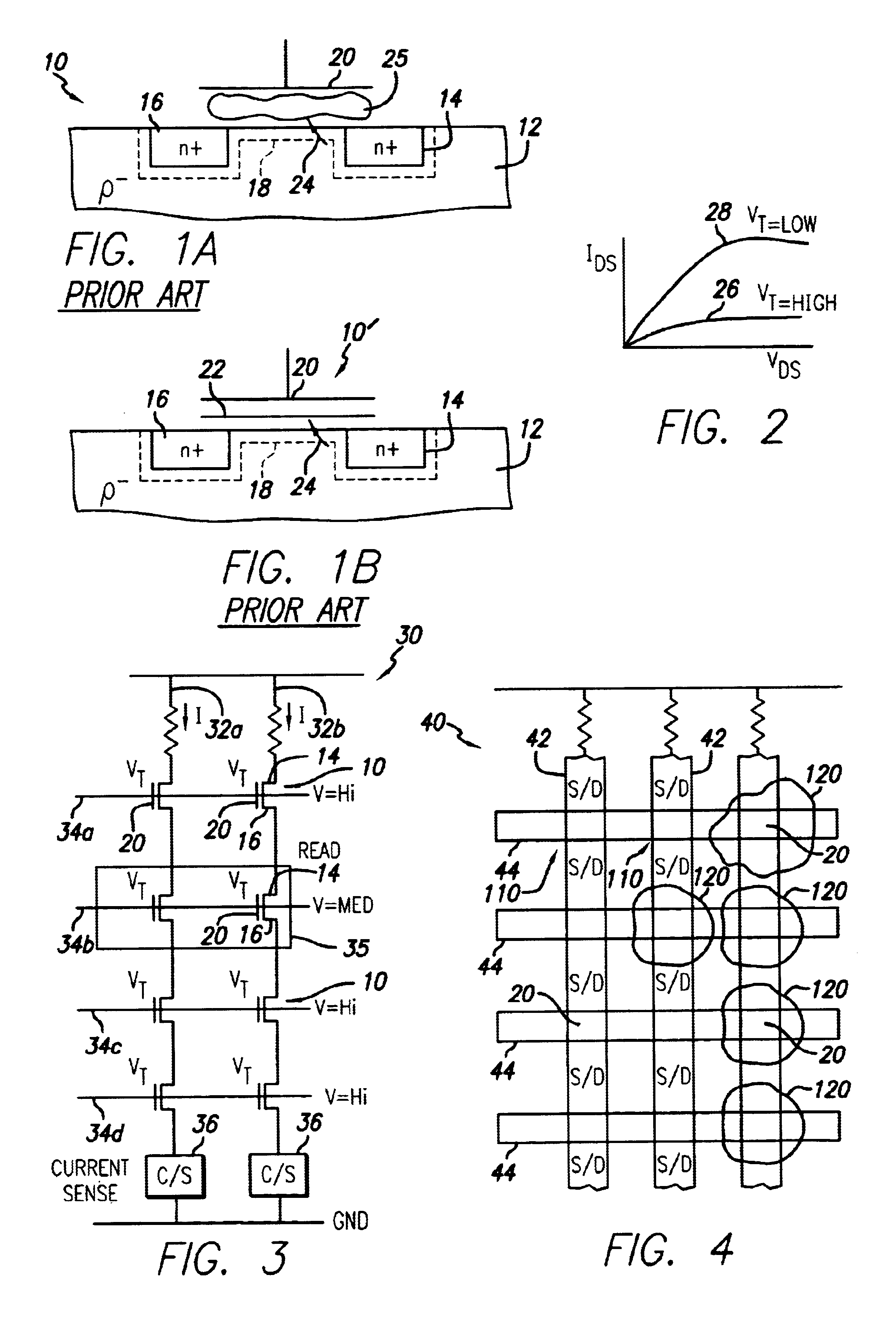

Molecular wire crossbar flash memory

InactiveUS6760245B2Process economyNanoinformaticsSolid-state devicesSemiconductor materialsMolecular wire

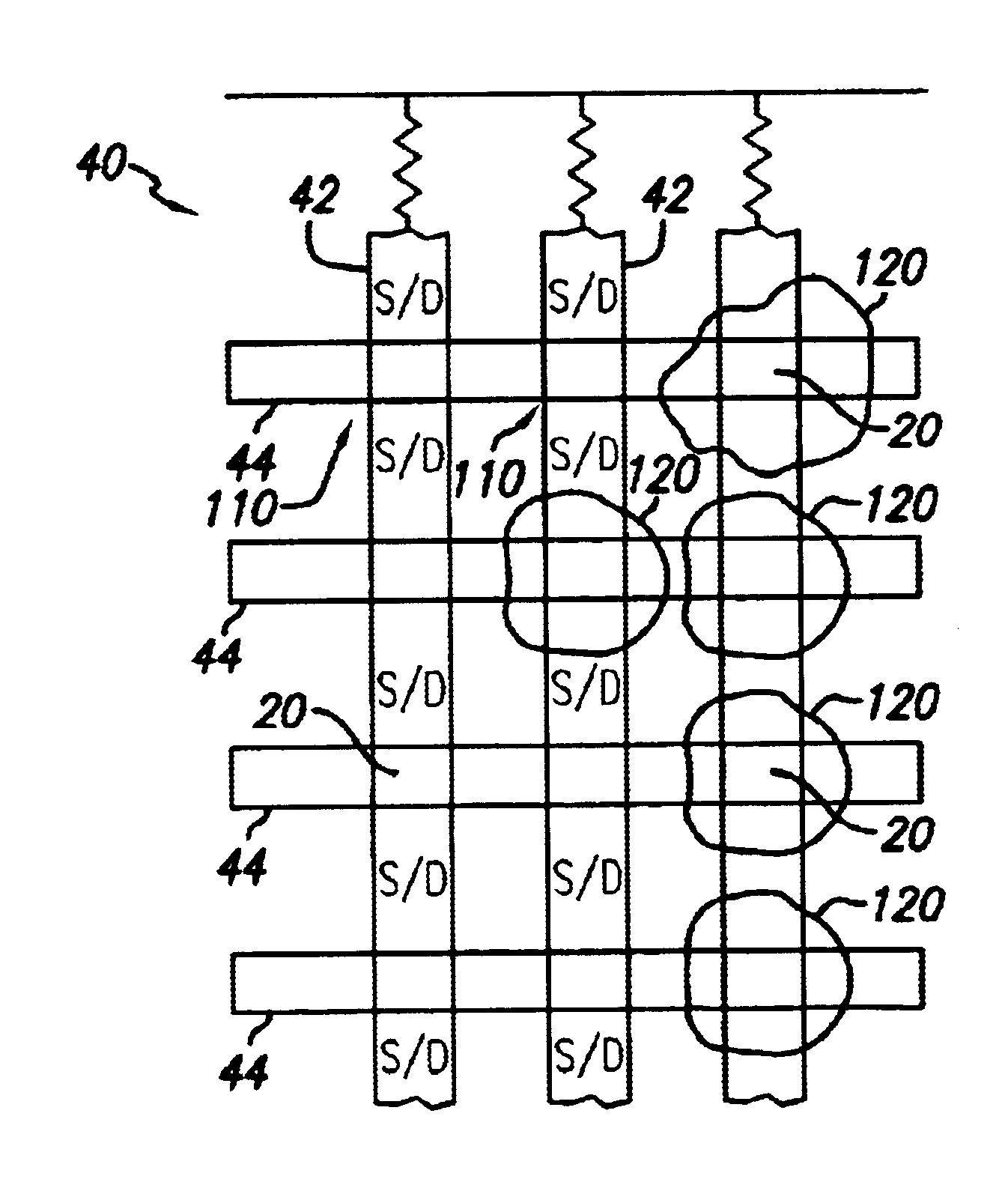

A nano-scale flash memory comprises: (a) source and drain regions in a plurality of approximately parallel first wires, the first wires comprising a semiconductor material, the source and drain regions separated by a channel region; (b) gate electrodes in a plurality of approximately parallel second wires, the second wires comprising either a semiconductor material or a metal, the second wires crossing the first wires at a non-zero angle over the channel regions, to form an array of nanoscale transistors; and (c) a hot electron trap region at each intersection of the first wires with the second wires. Additionally, crossed-wire transistors are provided that can either form a configurable transistor or a switch memory bit that is capable of being set by application of a voltage. The crossed-wire transistors can be formed in a crossbar array.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

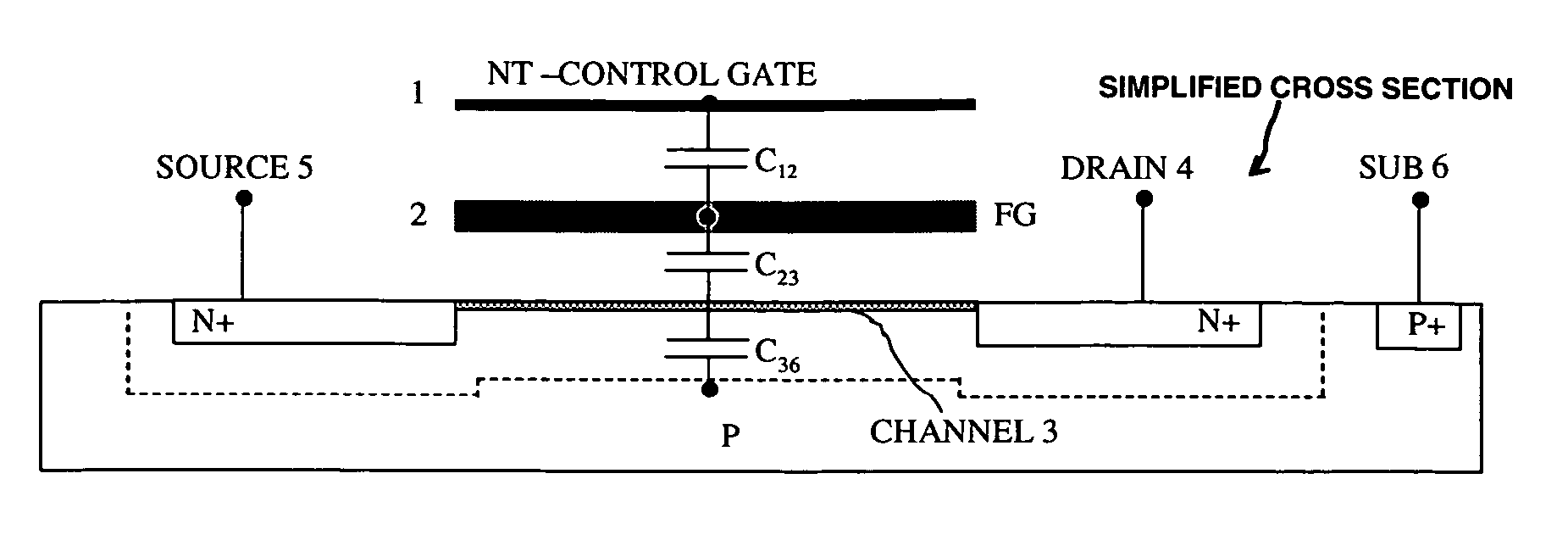

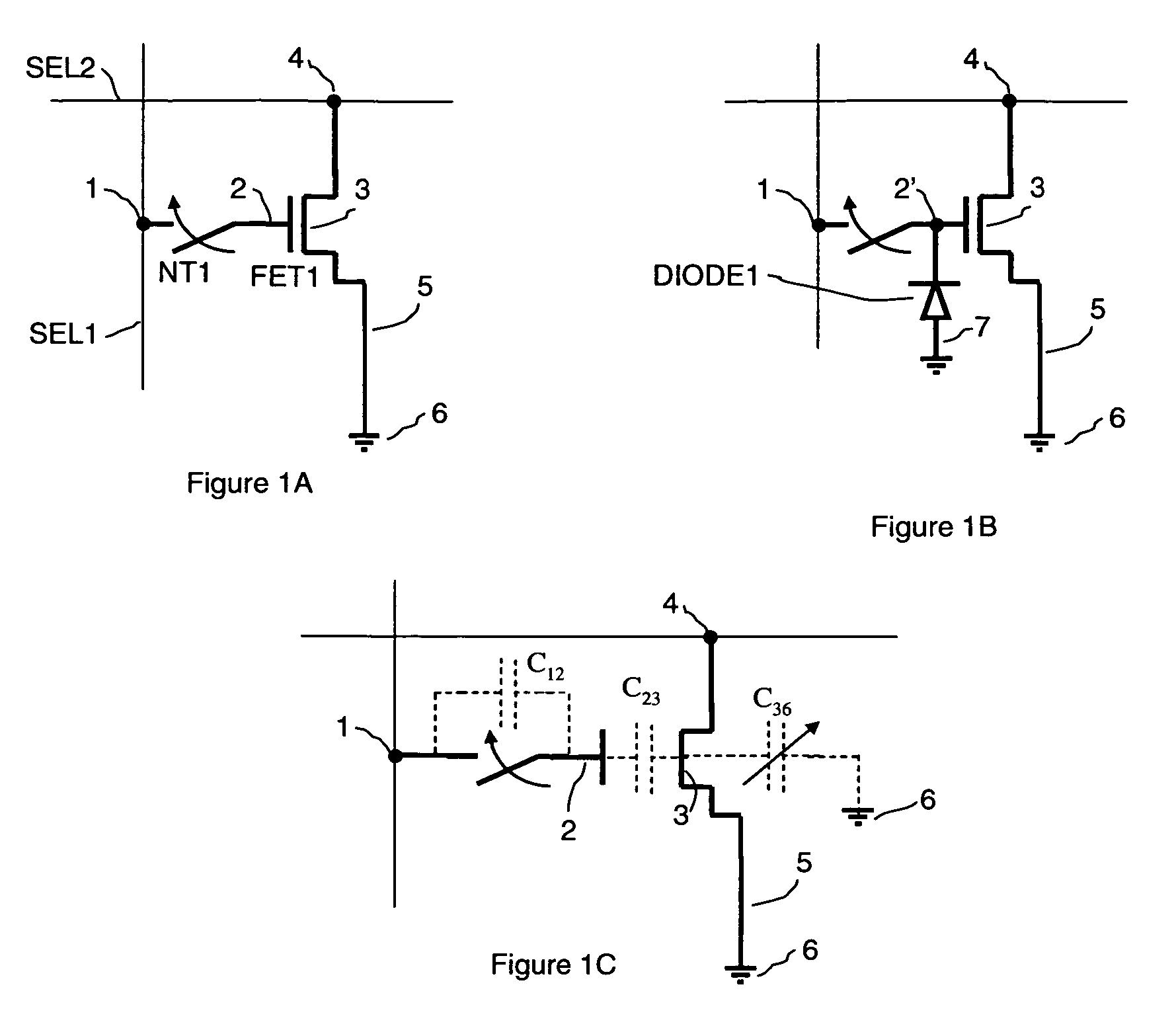

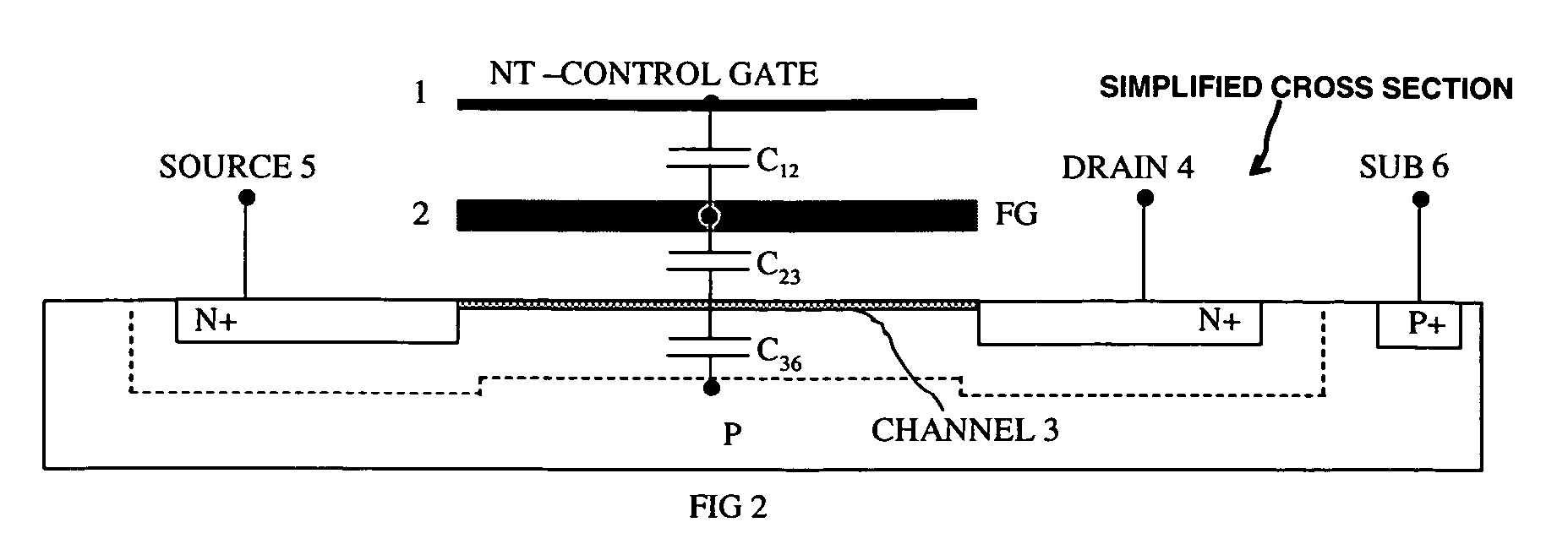

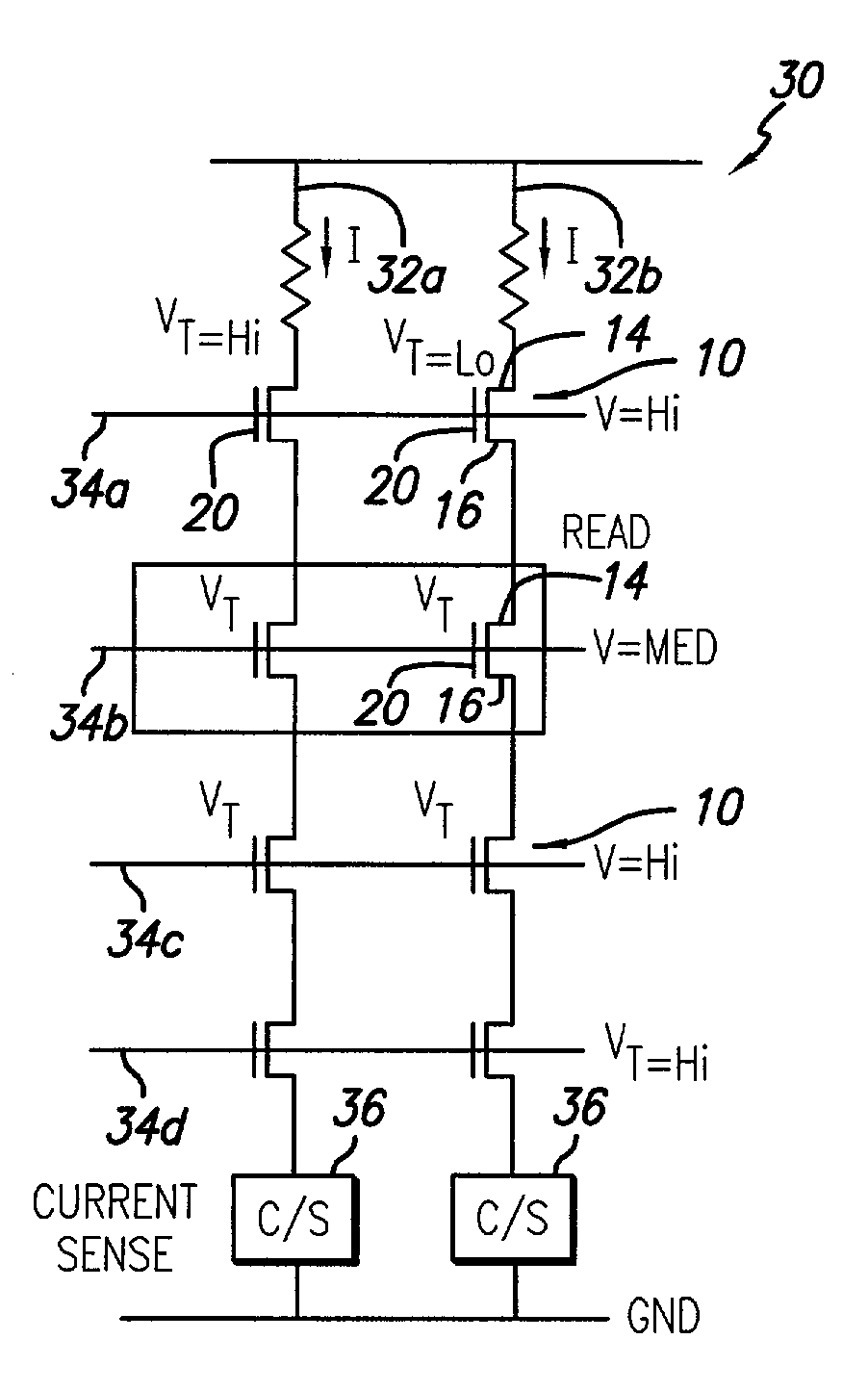

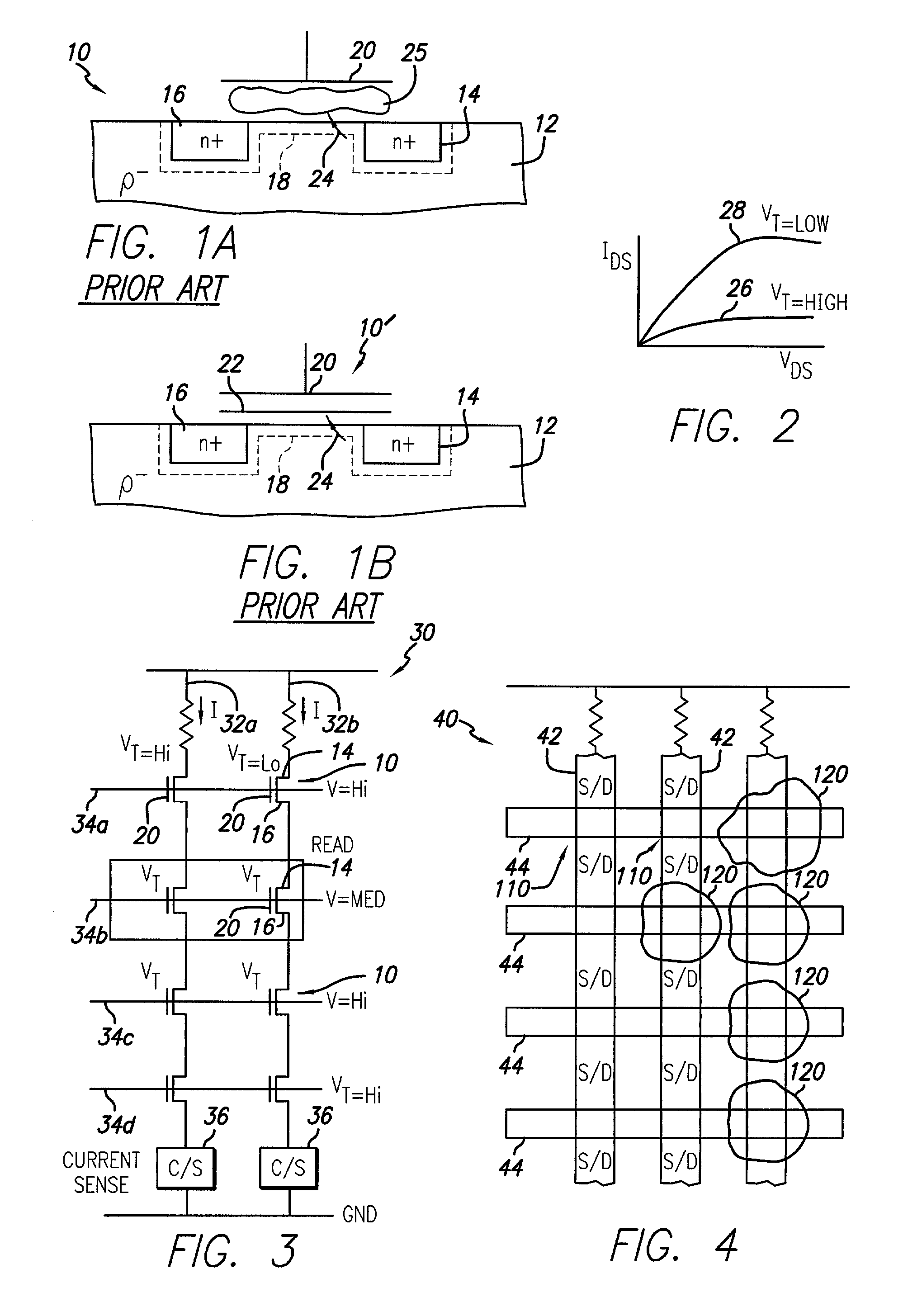

Nanotube-on-gate FET structures and applications

Nanotube on gate FET structures and applications of such, including n2 crossbars requiring only 2n control lines. A non-volatile transistor device includes a source region and a drain region of a first semiconductor type of material and a channel region of a second semiconductor type of material disposed between the source and drain region. A gate structure is made of at least one of semiconductive or conductive material and is disposed over an insulator over the channel region. A control gate is made of at least one of semiconductive or conductive material. An electromechanically-deflectable nanotube switching element is in fixed contact with one of the gate structure and the control gate structure and is not in fixed contact with the other of the gate structure and the control gate structure. The device has a network of inherent capacitances, including an inherent capacitance of an undeflected nanotube switching element in relation to the gate structure. The network is such that the nanotube switching element is deflectable into contact with the other of the gate structure and the control gate structure in response to signals being applied to the control gate and one of the source region and drain region. Certain embodiments of the device have an area of about 4 F2. Other embodiments include a release line is positioned in spaced relation to the nanotube switching element, and having a horizontal orientation that is parallel to the orientation of the source and drain diffusions. Other embodiments provide an n2 crossbar array having n2 non-volatile transistor devices, but require only 2n control lines.

Owner:NANTERO +1

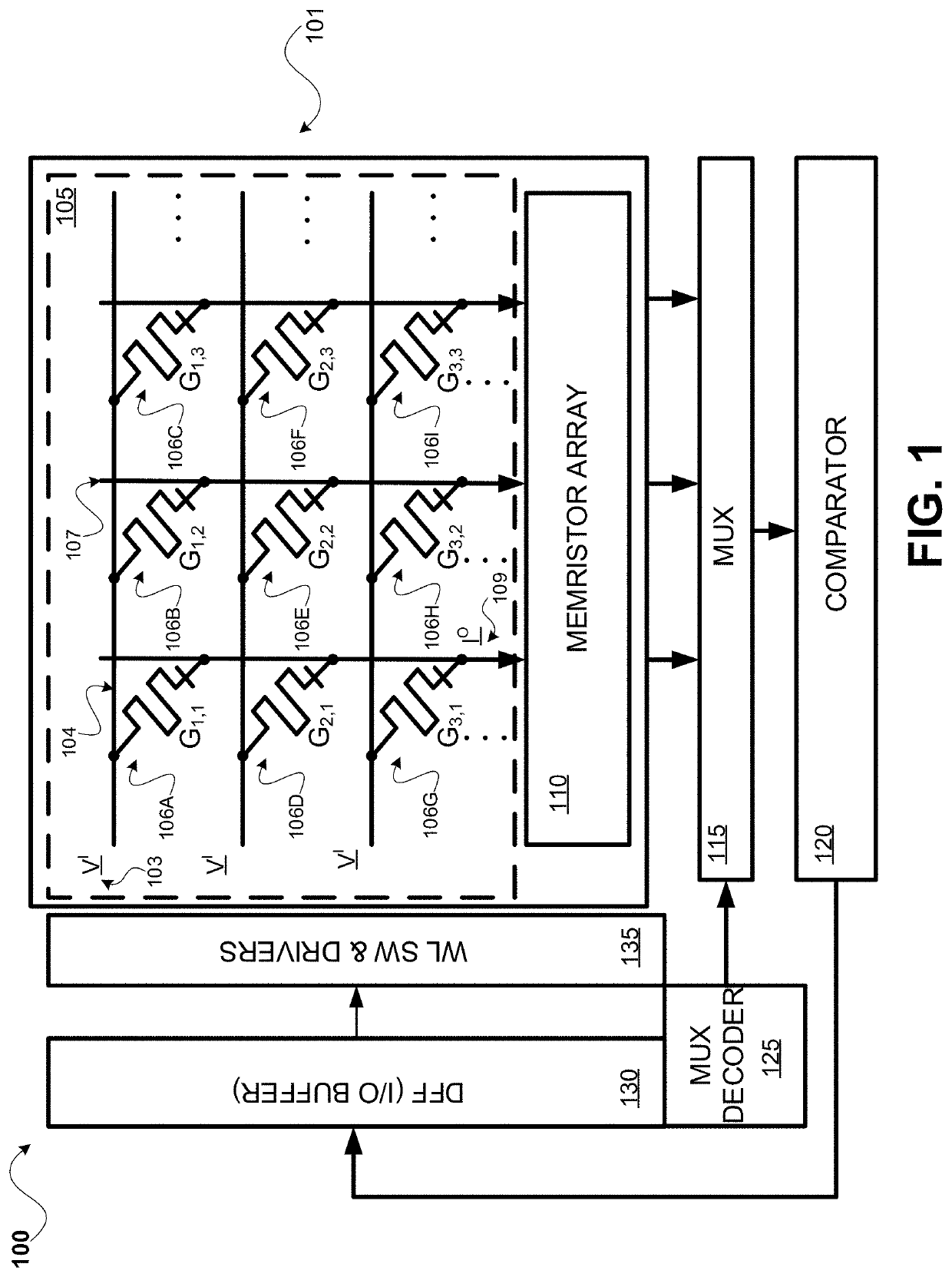

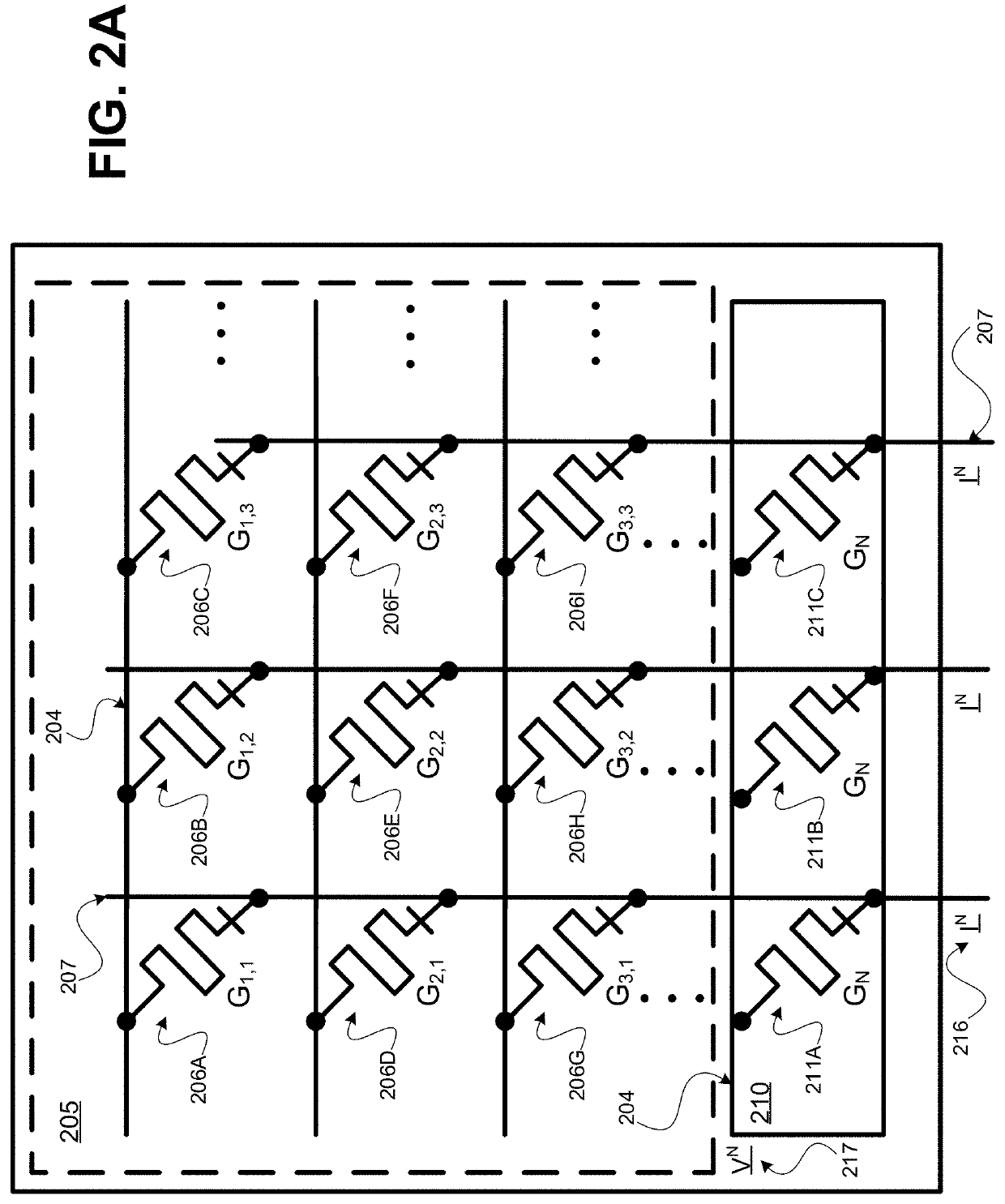

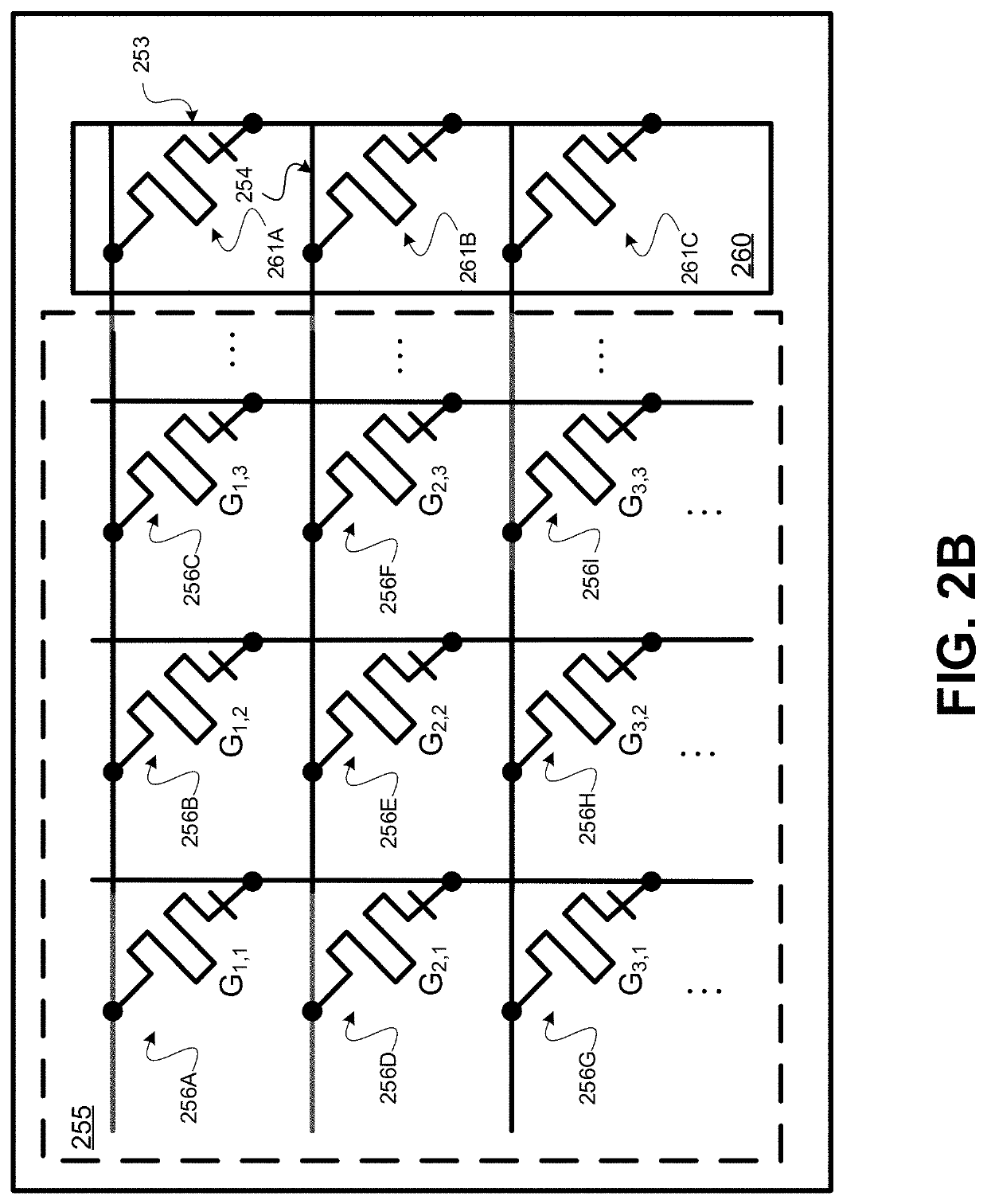

Method and apparatus for performing close-loop programming of resistive memory devices in crossbar array based hardware circuits and systems

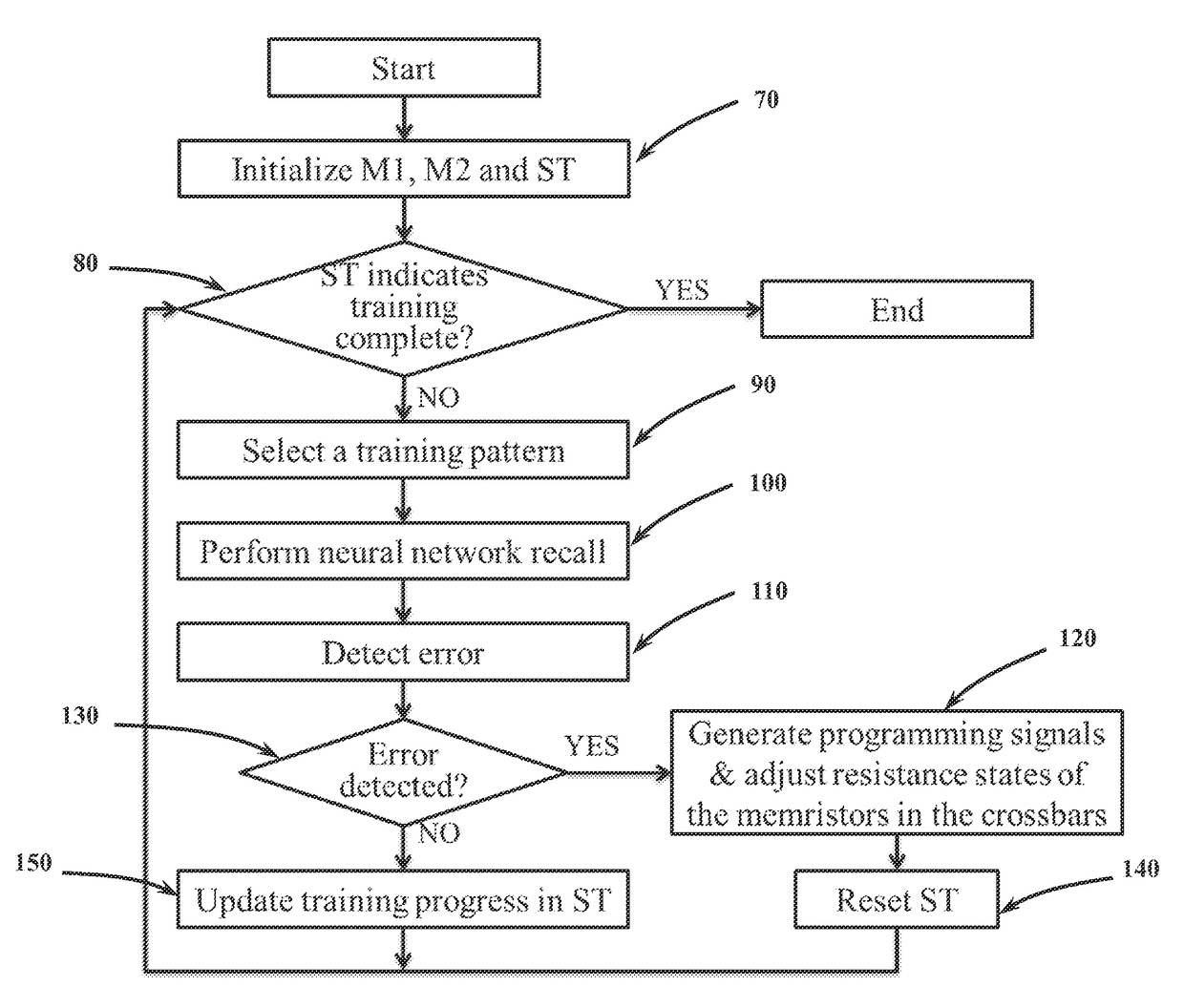

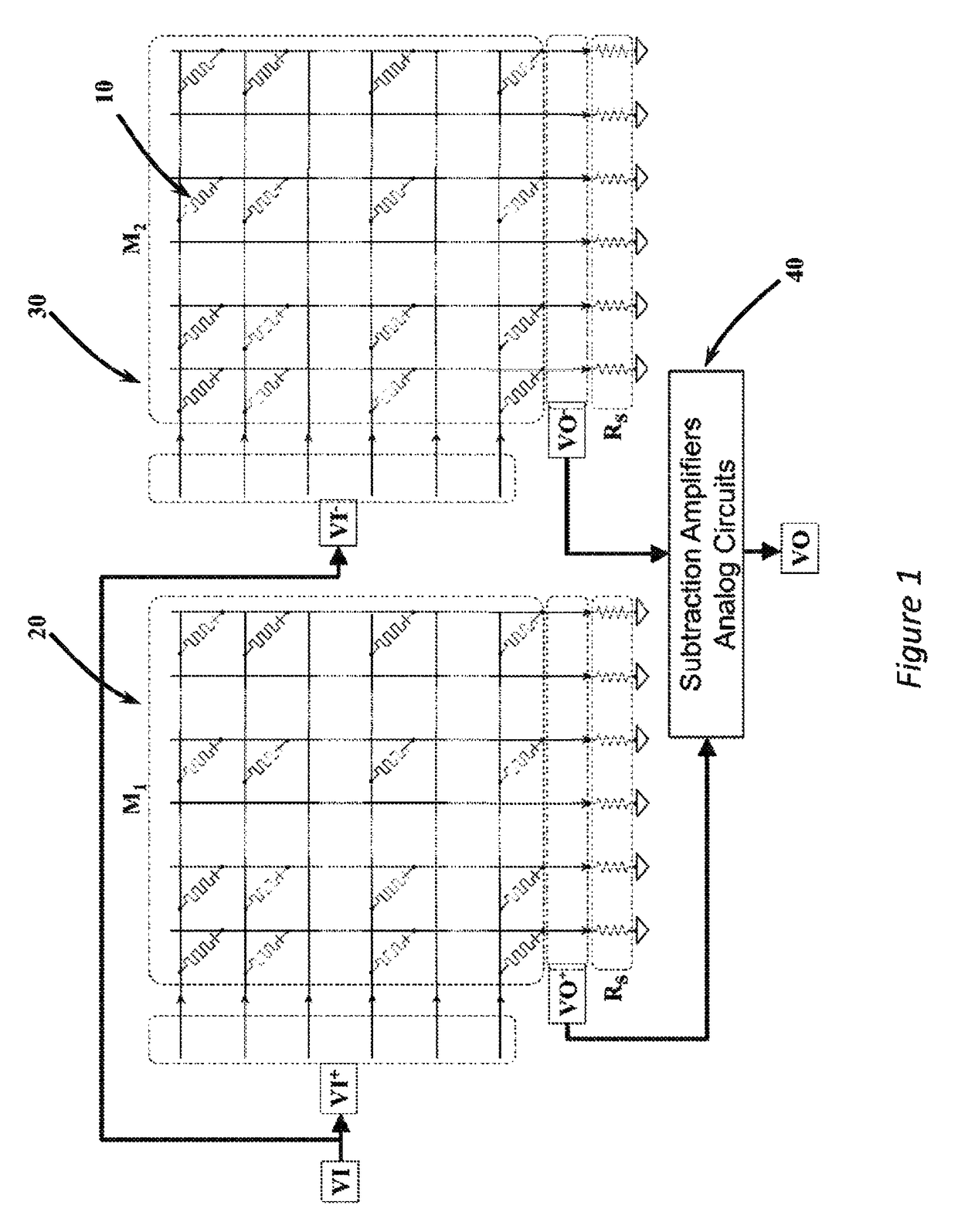

ActiveUS20150170025A1Reduce Design ComplexityConvenient and accurateDigital computer detailsDigital storageObservational errorElectrical resistance and conductance

Method and apparatus for performing close-loop programming of resistive memory devices in crossbar array based hardware circuits and systems. Invention provides iterative training of memristor crossbar arrays for neural networks by applying voltages corresponding to selected training patterns. Error is detected and measured as a function of the actual response to the training patterns versus the expected response to the training pattern.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE

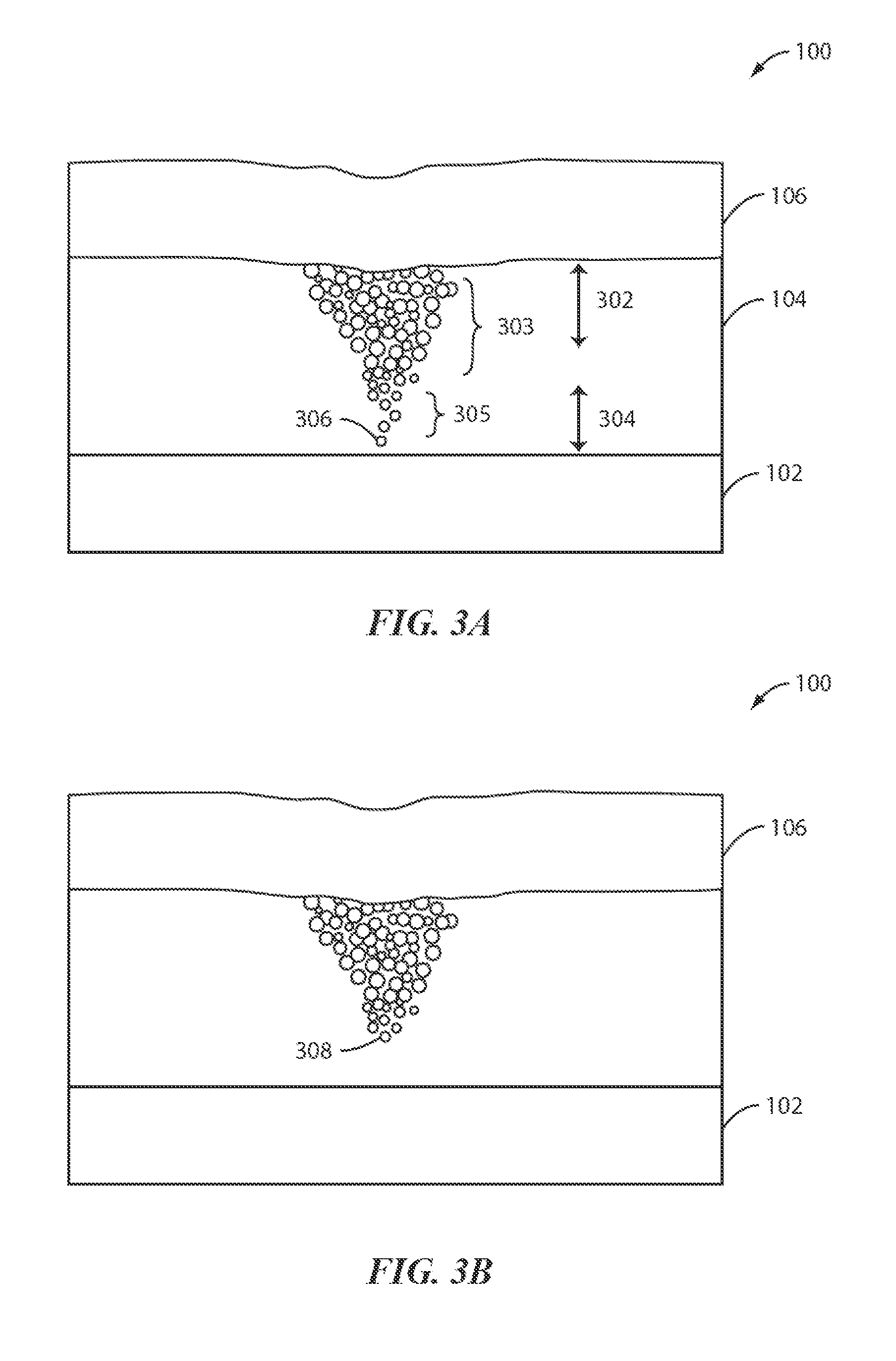

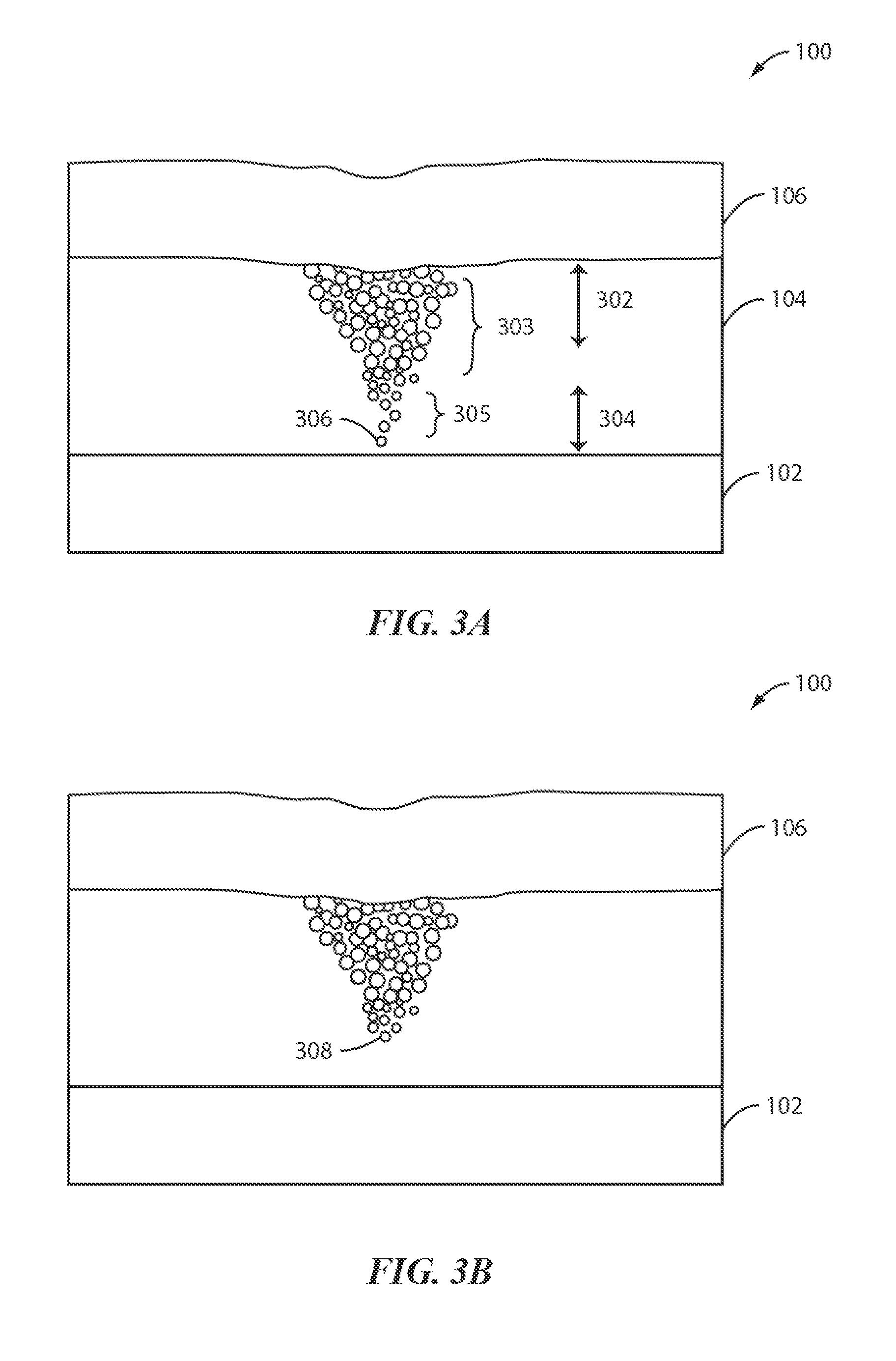

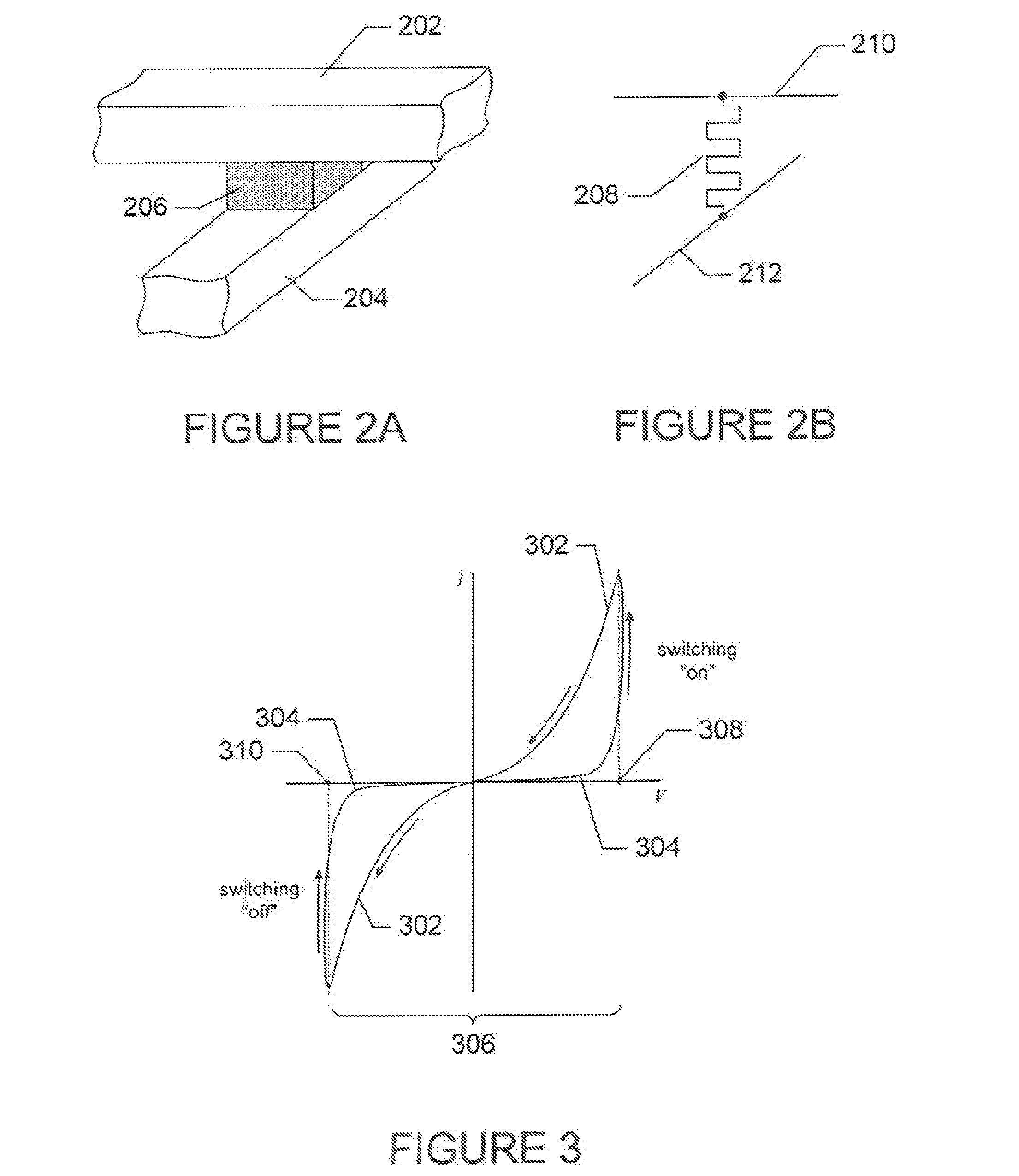

Interface control for improved switching in rram

ActiveUS20110305064A1Solid-state devicesSemiconductor/solid-state device manufacturingAmorphous siliconOptoelectronics

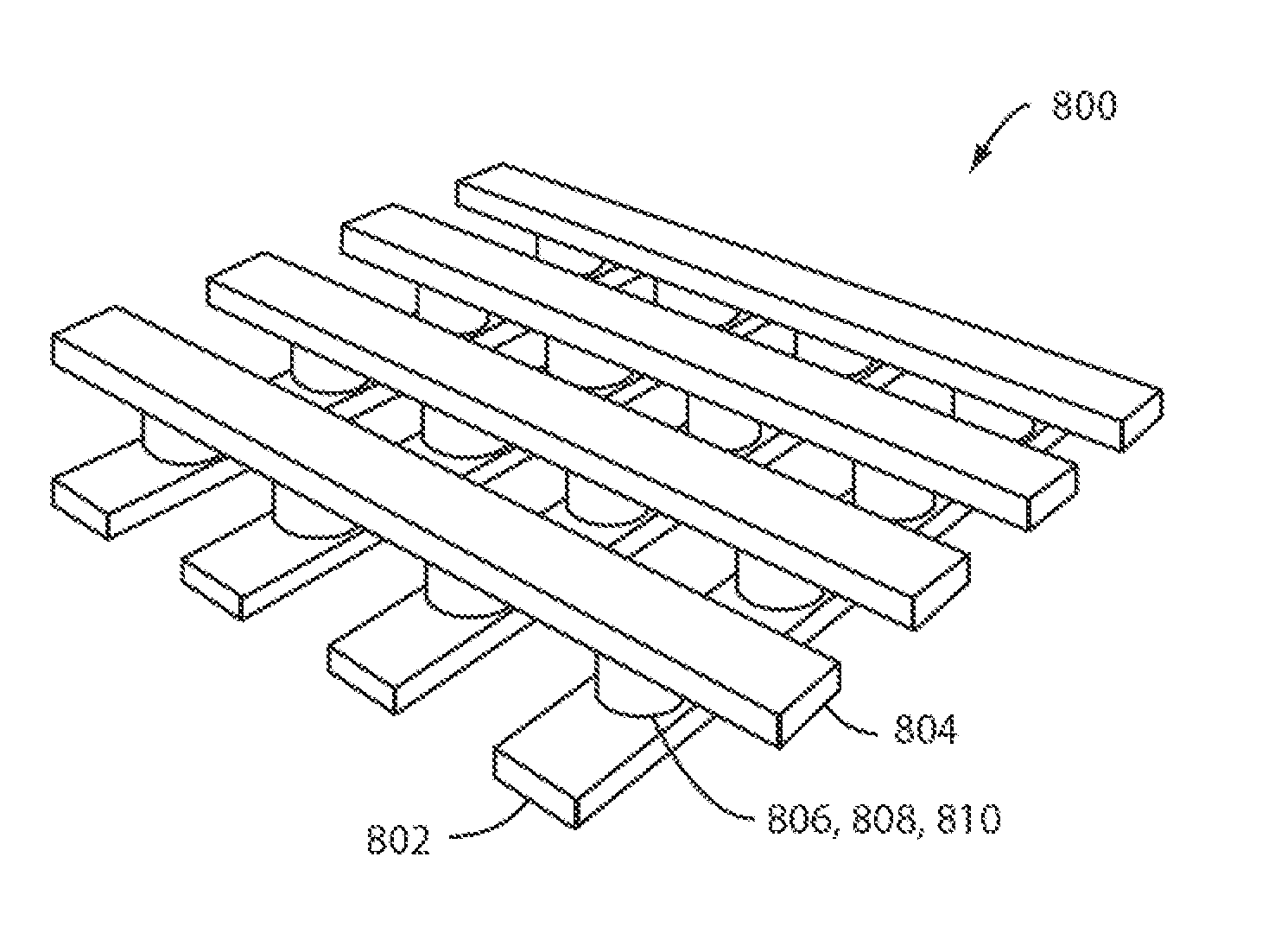

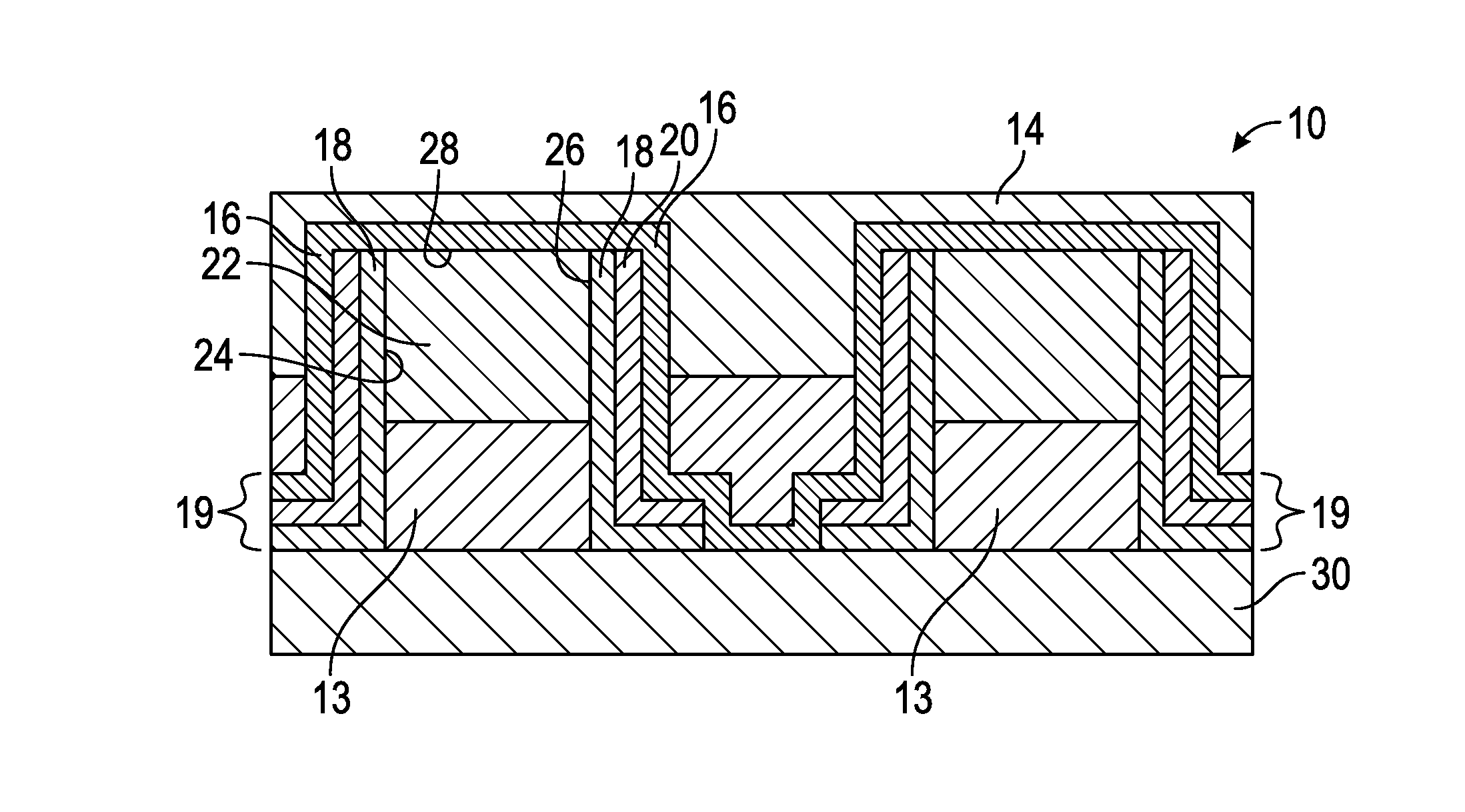

A memory device has a crossbar array including a first array of first electrodes extending along a first direction. A second array of second electrodes extends along a second direction. A non-crystalline silicon structure provided between the first electrode and the second electrode at an intersection defined by the first array and the second array. The non-crystalline silicon structure has a first layer having a first defect density and a second layer having a second defect density different from the first defect density. Each intersection of the first array and the second array defines a two-terminal memory cell.

Owner:INNOSTAR SEMICON SHANGHAI CO LTD

Nanoscale wires and related devices

The present invention relates generally to sub-microelectronic circuitry, and more particularly to nanometer-scale articles, including nanoscale wires which can be selectively doped at various locations and at various levels. In some cases, the articles may be single crystals. The nanoscale wires can be doped, for example, differentially along their length, or radially, and either in terms of identity of dopant, concentration of dopant, or both. This may be used to provide both n-type and p-type conductivity in a single item, or in different items in close proximity to each other, such as in a crossbar array. The fabrication and growth of such articles is described, and the arrangement of such articles to fabricate electronic, optoelectronic, or spintronic devices and components. For example, semiconductor materials can be doped to form n-type and p-type semiconductor regions for making a variety of devices such as field effect transistors, bipolar transistors, complementary inverters, tunnel diodes, light emitting diodes, sensors, and the like.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

Molecular wire crossbar flash memory

InactiveUS20030206436A1Process economyHigh densityNanoinformaticsSolid-state devicesSemiconductor materialsEngineering

A nano-scale flash memory comprises: (a) source and drain regions in a plurality of approximately parallel first wires, the first wires comprising a semiconductor material, the source and drain regions separated by a channel region; (b) gate electrodes in a plurality of approximately parallel second wires, the second wires comprising either a semiconductor material or a metal, the second wires crossing the first wires at a non-zero angle over the channel regions, to form an array of nanoscale transistors; and (c) a hot electron trap region at each intersection of the first wires with the second wires. Additionally, crossed-wire transistors are provided that can either form a configurable transistor or a switch memory bit that is capable of being set by application of a voltage. The crossed-wire transistors can be formed in a crossbar array.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Nanoscopic wire-based devices and arrays

InactiveUS20050117441A1Material nanotechnologyElectrostatic/electro-adhesion relaysNanowireGas phase

Electrical devices comprised of nanoscopic wires are described, along with methods of their manufacture and use. The nanoscopic wires can be nanotubes, preferably single-walled carbon nanotubes. They can be arranged in crossbar arrays using chemically patterned surfaces for direction, via chemical vapor deposition. Chemical vapor deposition also can be used to form nanotubes in arrays in the presence of directing electric fields, optionally in combination with self-assembled monolayer patterns. Bistable devices are described.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

Interface control for improved switching in RRAM

A memory device has a crossbar array including a first array of first electrodes extending along a first direction. A second array of second electrodes extends along a second direction. A non-crystalline silicon structure provided between the first electrode and the second electrode at an intersection defined by the first array and the second array. The non-crystalline silicon structure has a first layer having a first defect density and a second layer having a second defect density different from the first defect density. Each intersection of the first array and the second array defines a two-terminal memory cell.

Owner:INNOSTAR SEMICON SHANGHAI CO LTD

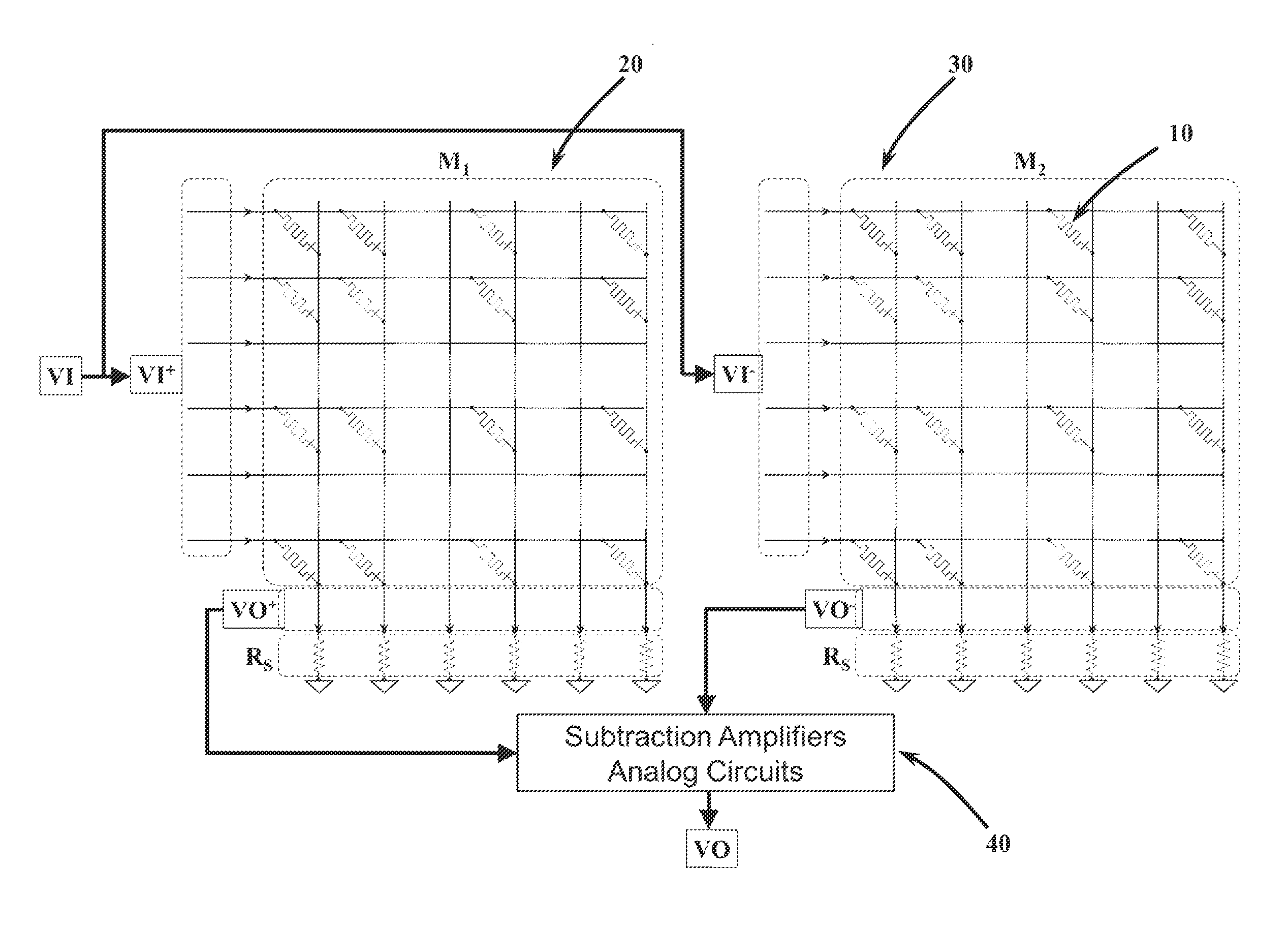

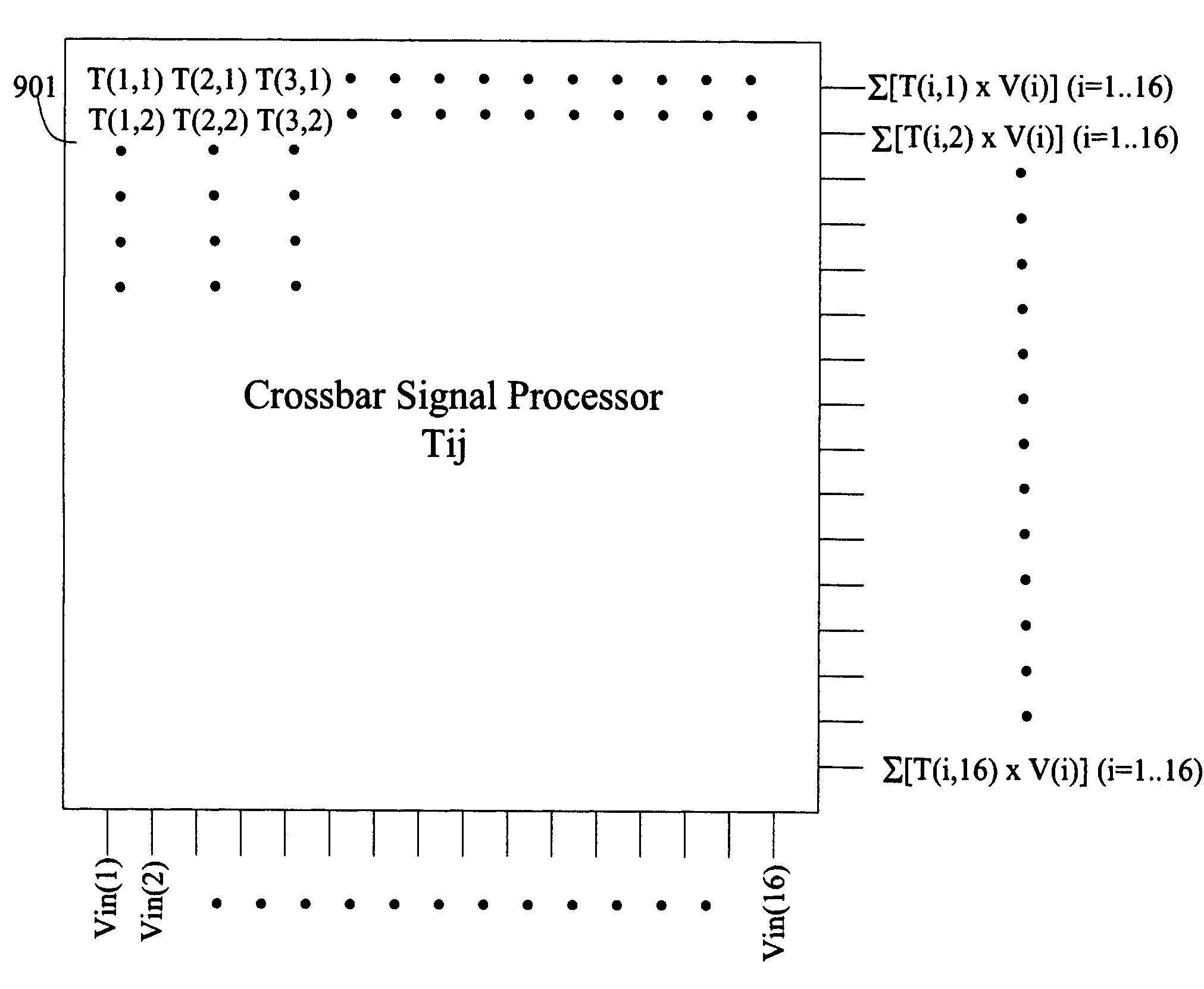

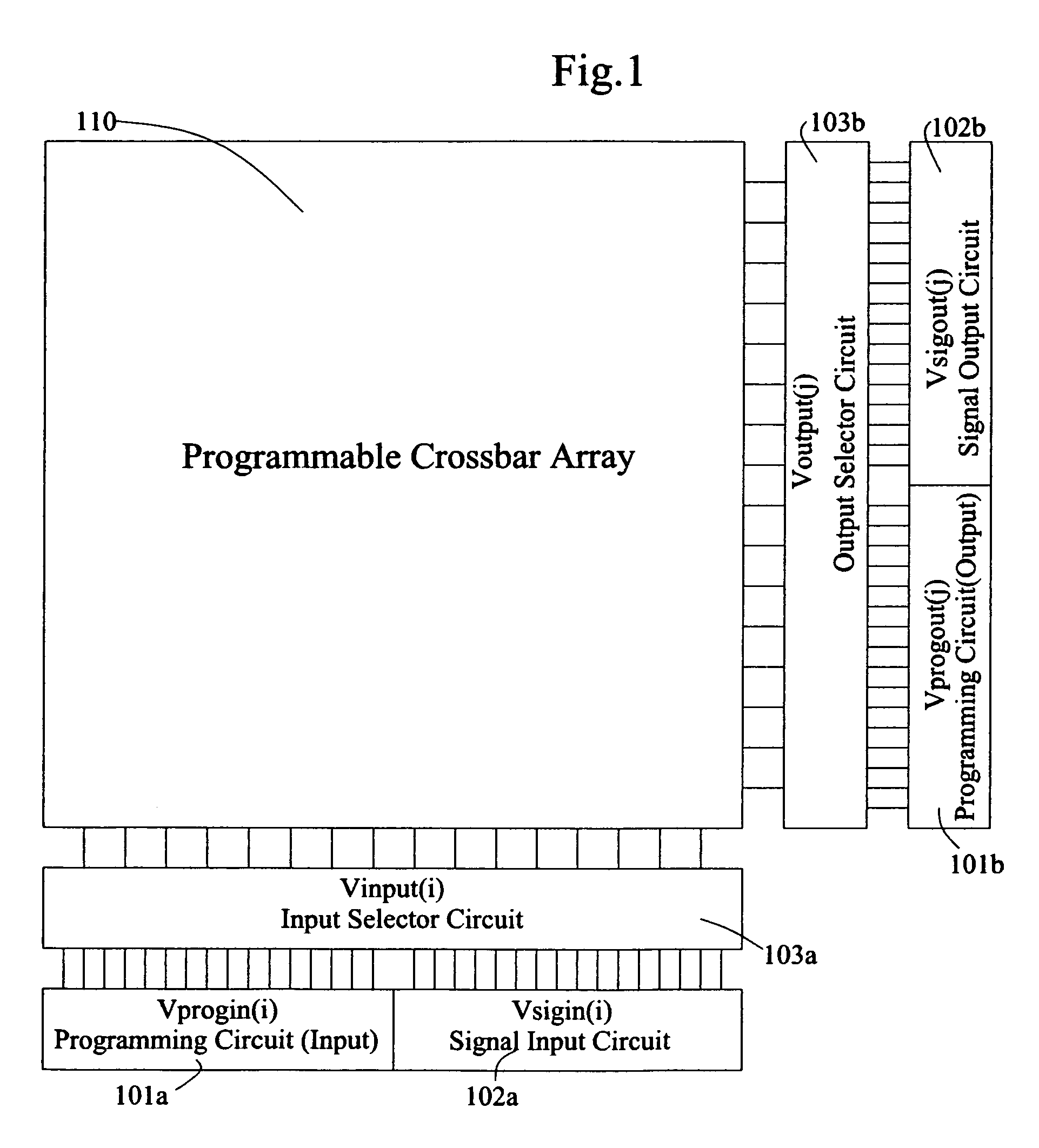

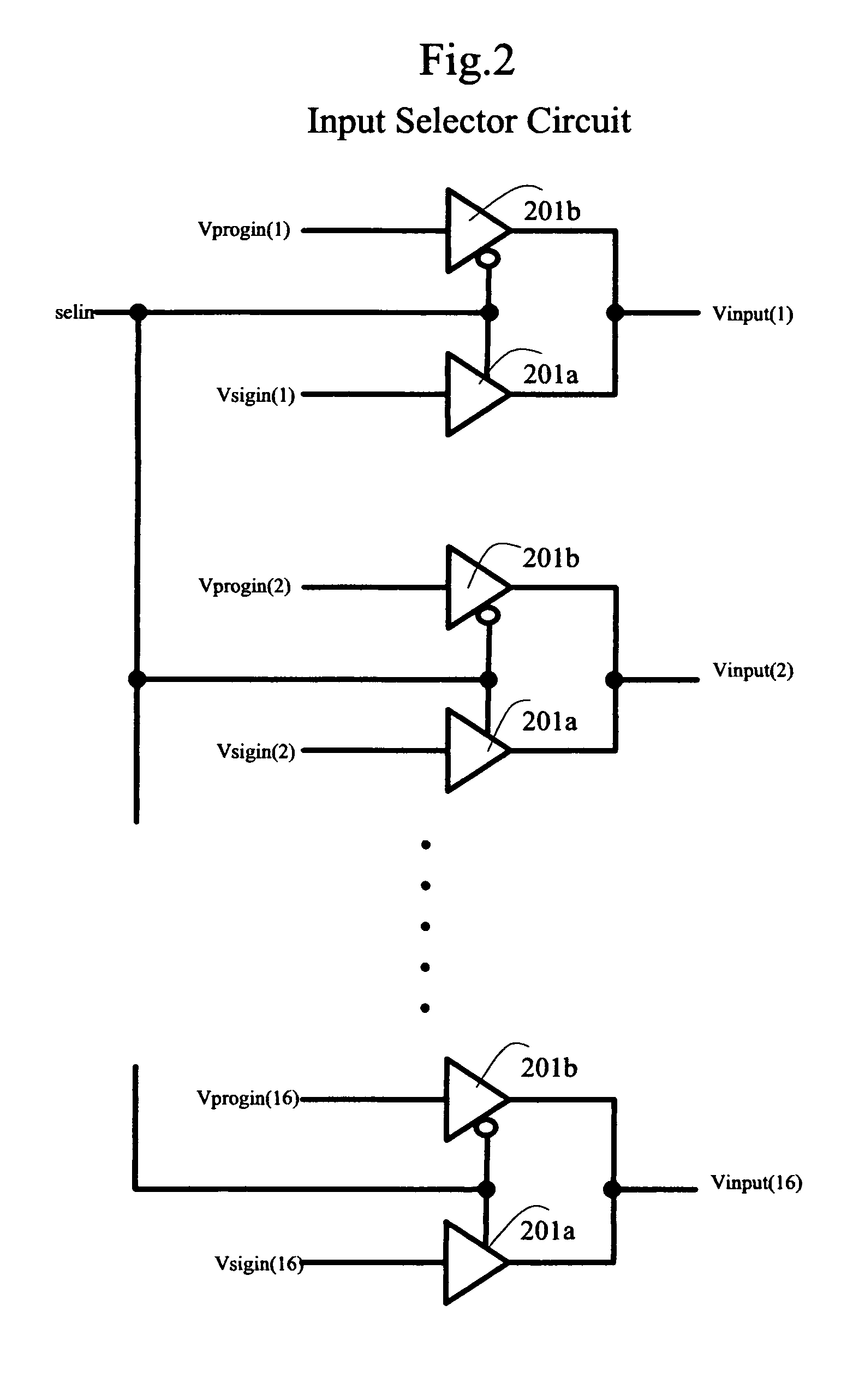

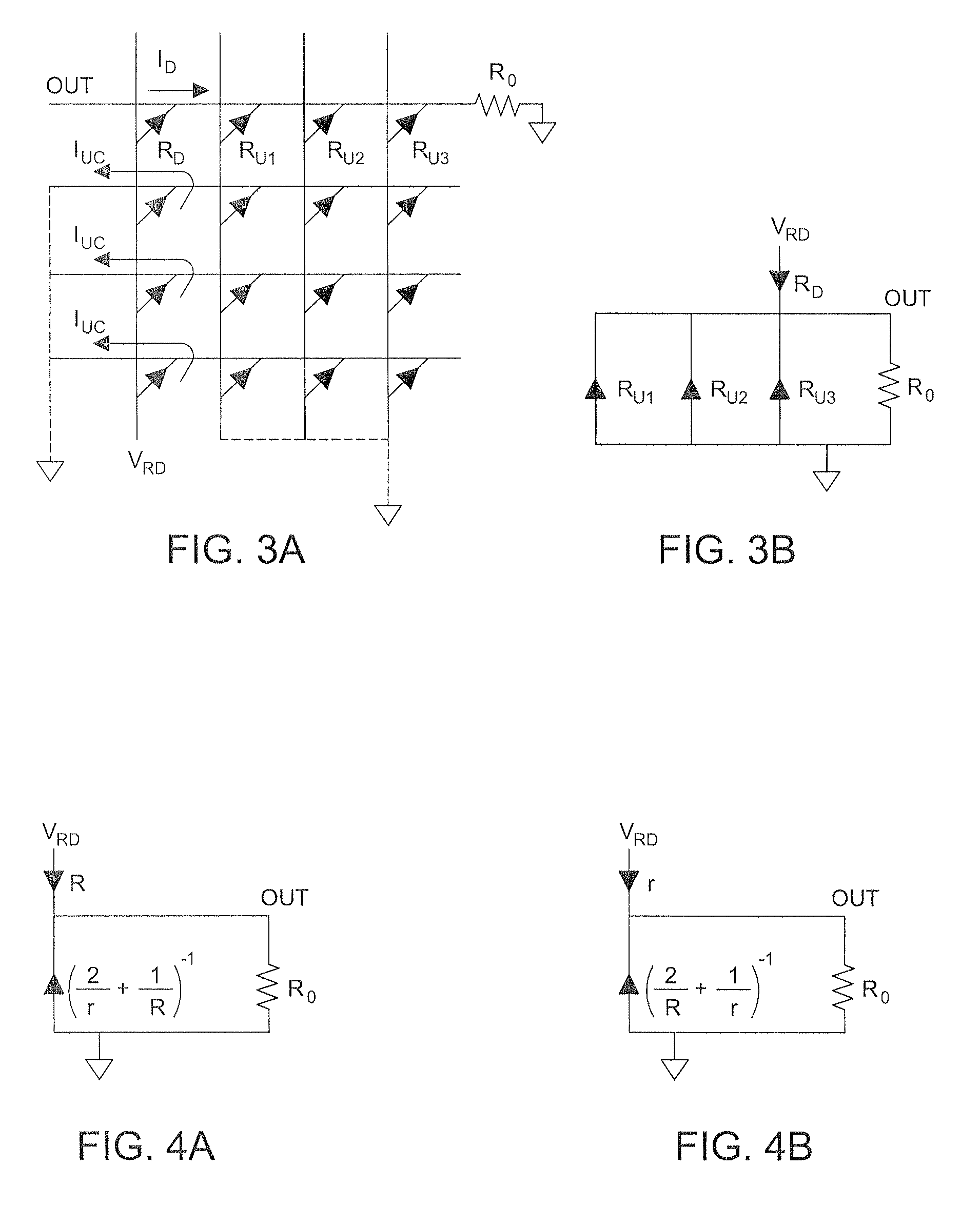

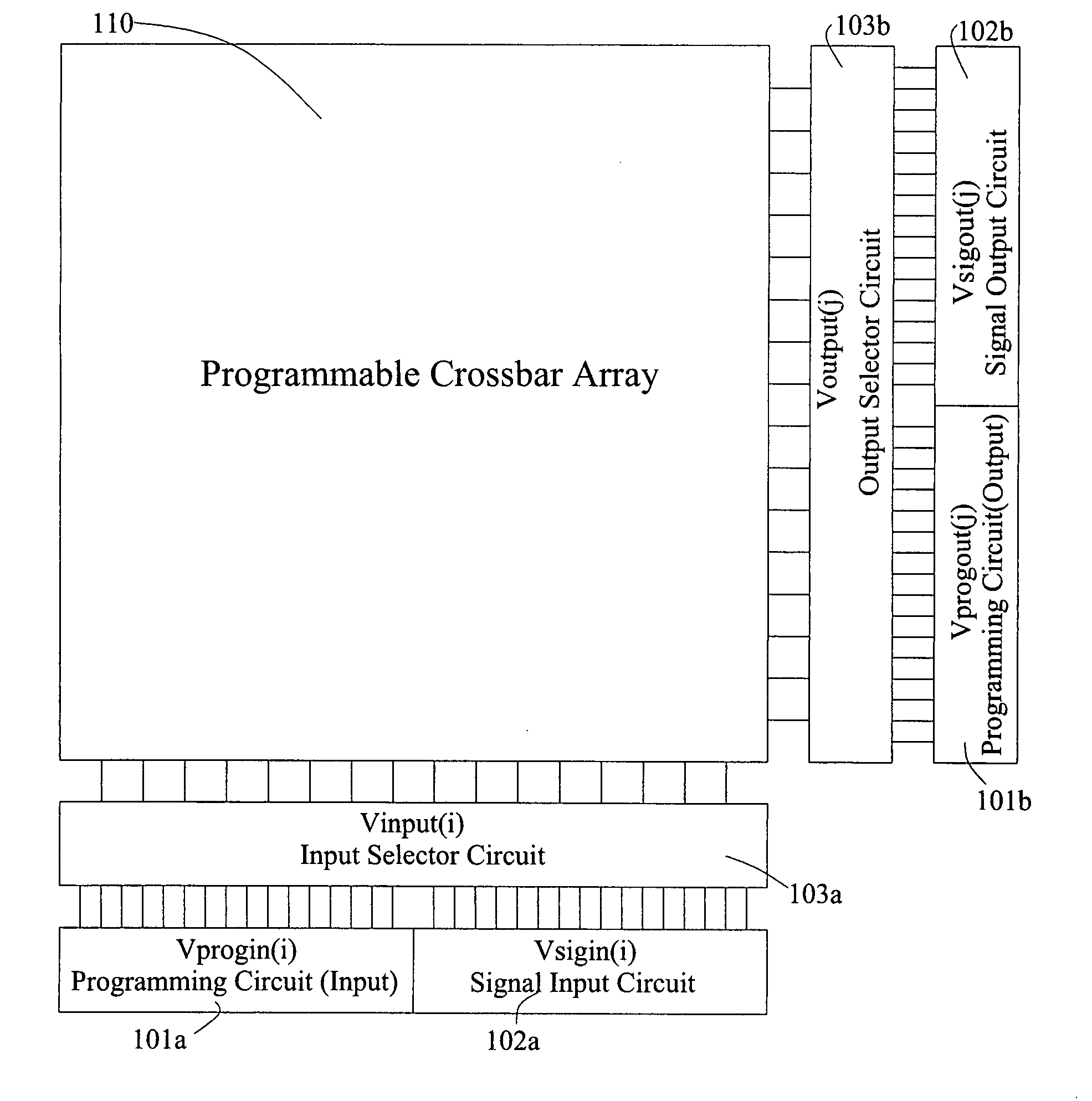

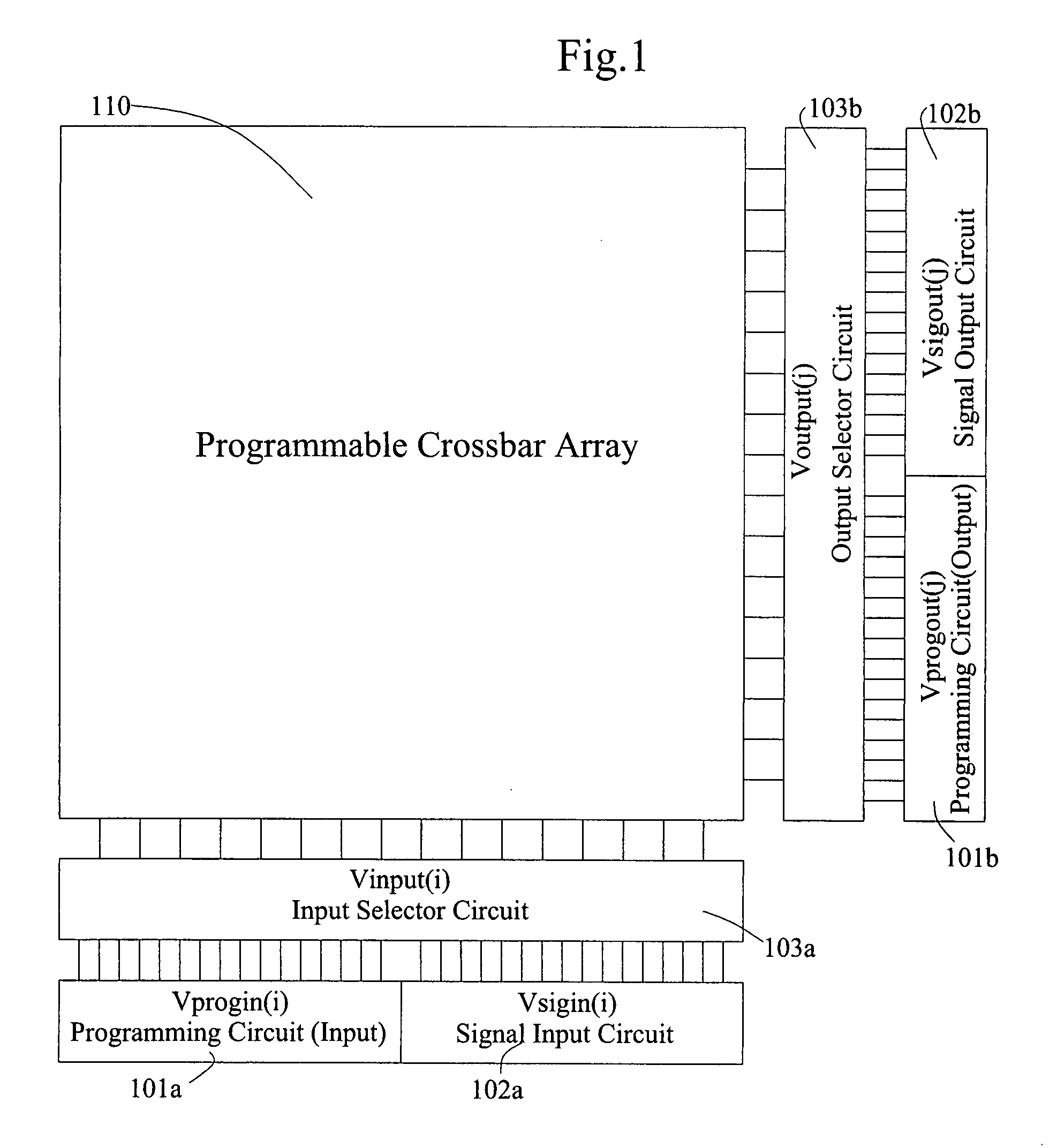

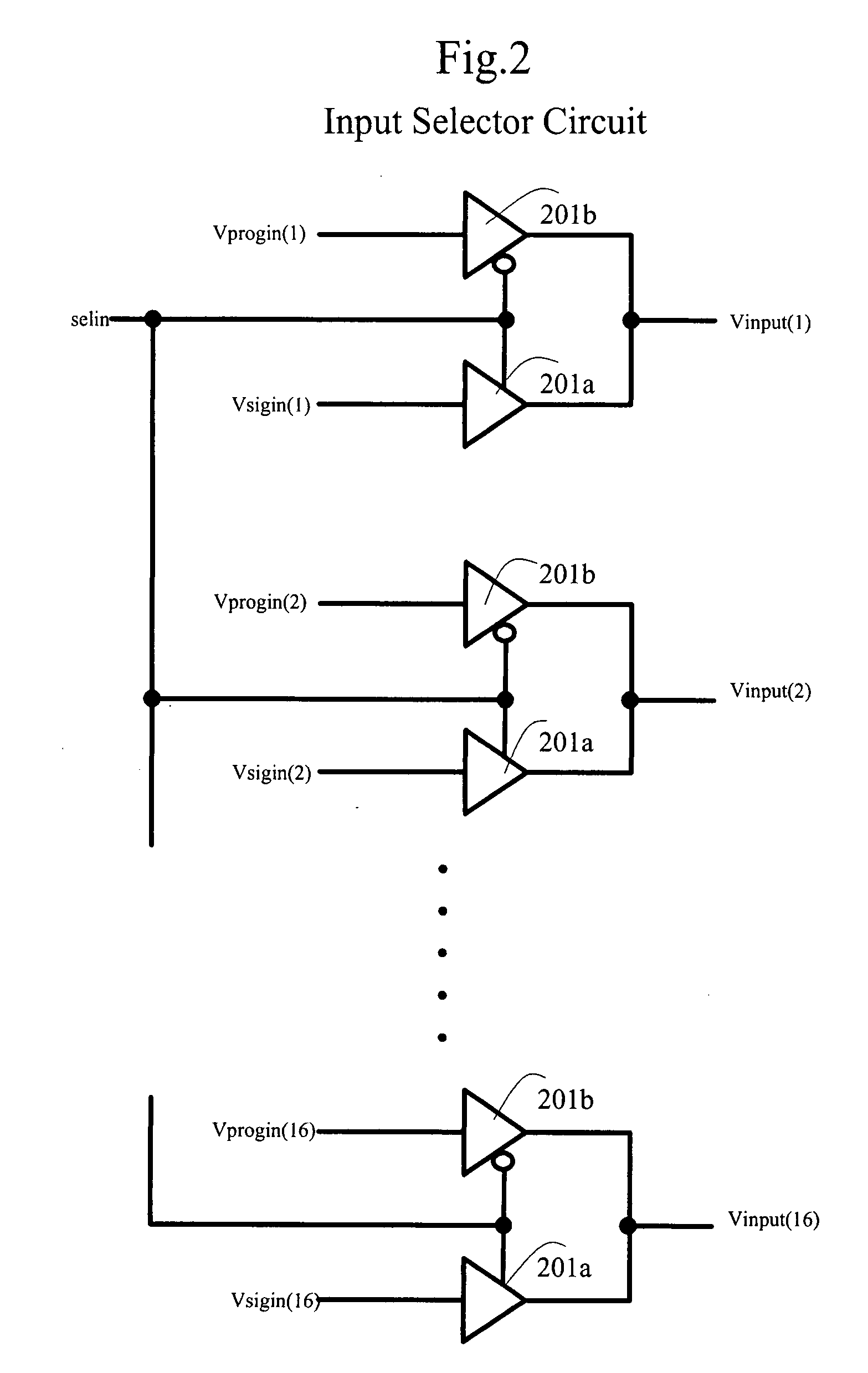

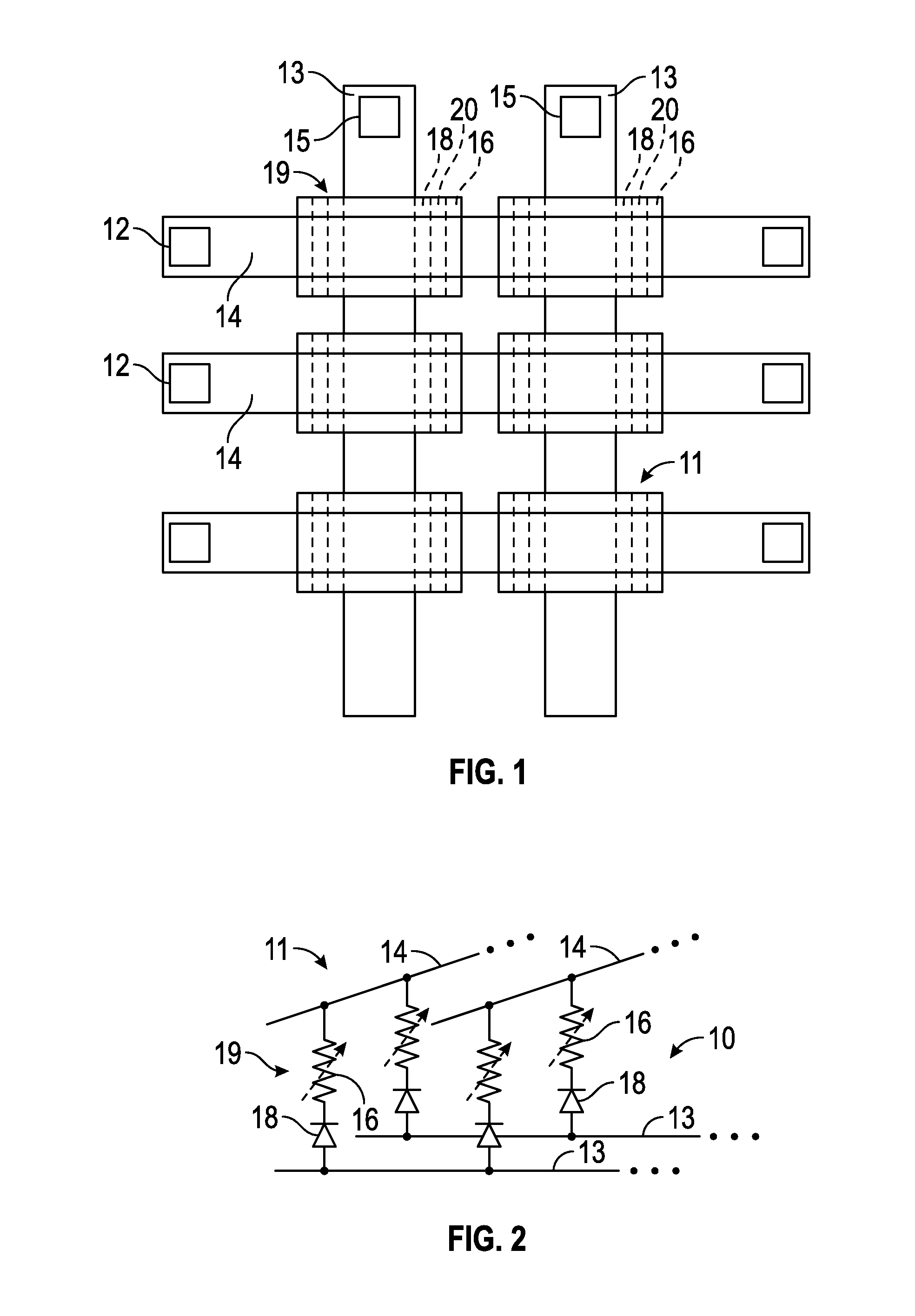

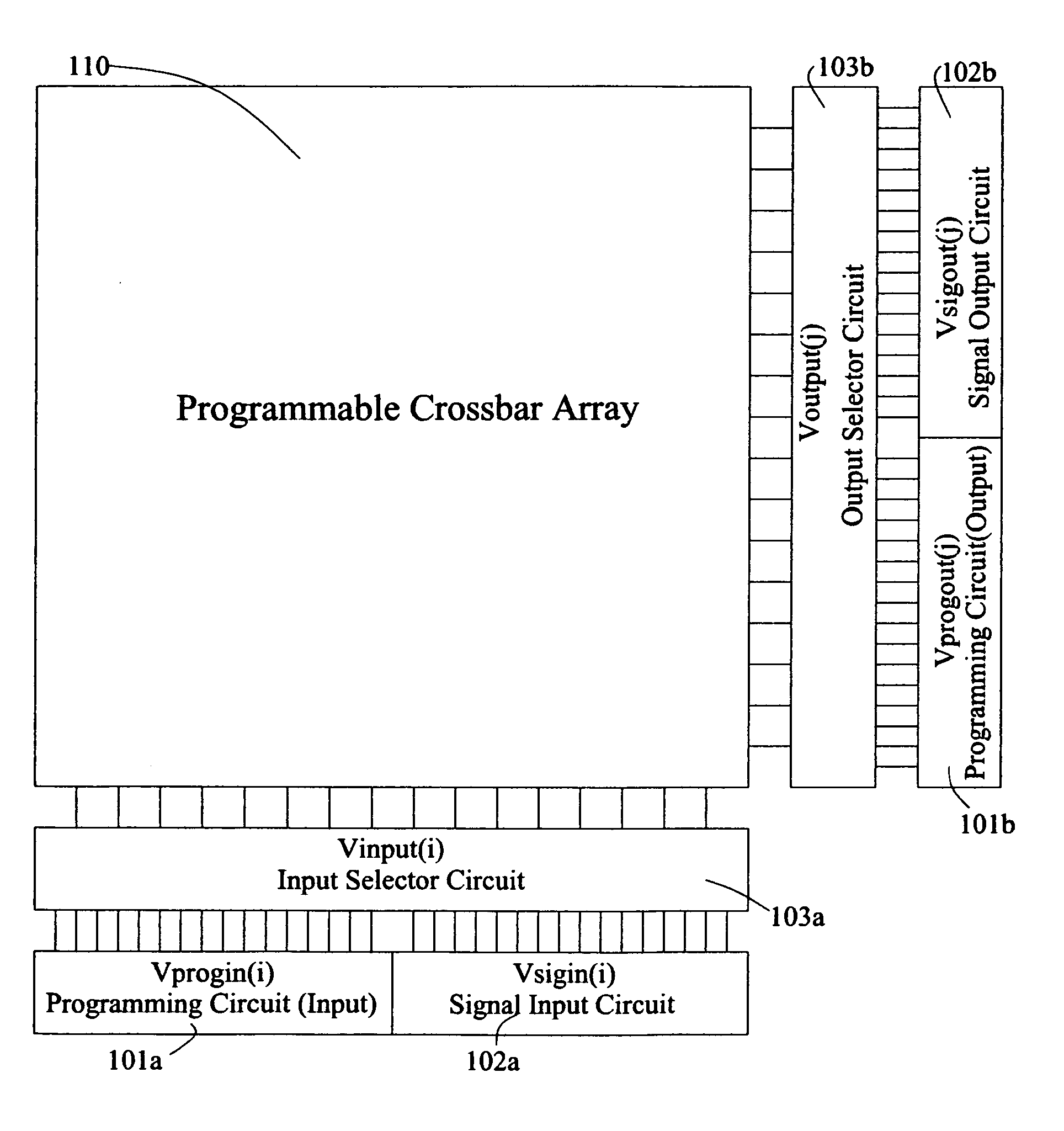

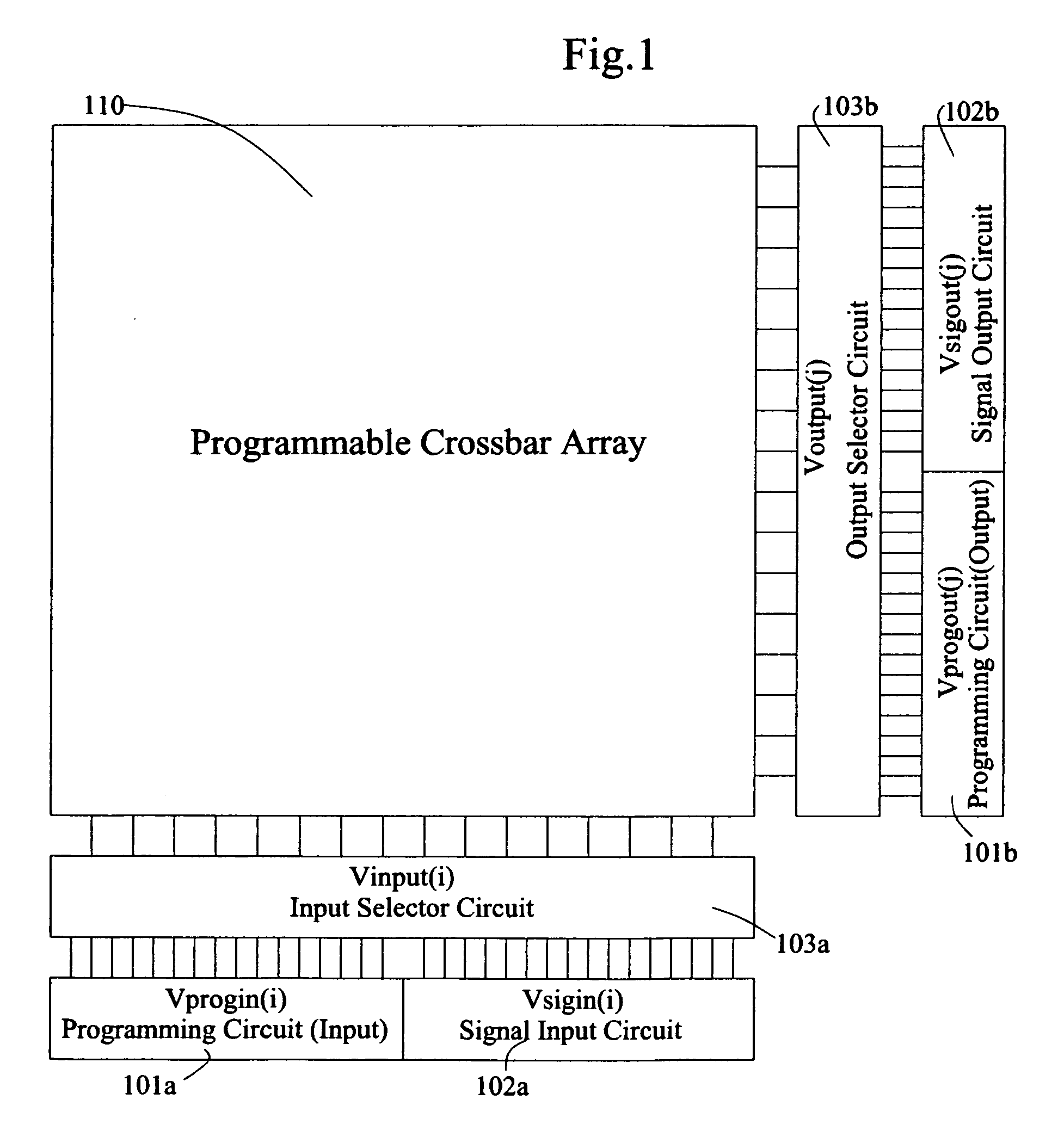

Programmable crossbar signal processor

A signal processing system is taught to be formed by combining a crossbar array with programming circuitry and signal input circuitry so as to provide a linear transformation from a set of input signals to a set of output signals. Applications of such a system to waveform generation, signal filtering, communications, and pattern recognition are explained. In one embodiment the crossbar array of the signal processing system may be a molecular nanowire crossbar array in which the crossbar interconnects are addressed via dual arrays of scanning probe tips so as to provide an interface between the molecular crossbar electronics and conventional solid state electronics used in the programming and signal processing circuitry.

Owner:MOUTTET BLAISE LAURENT

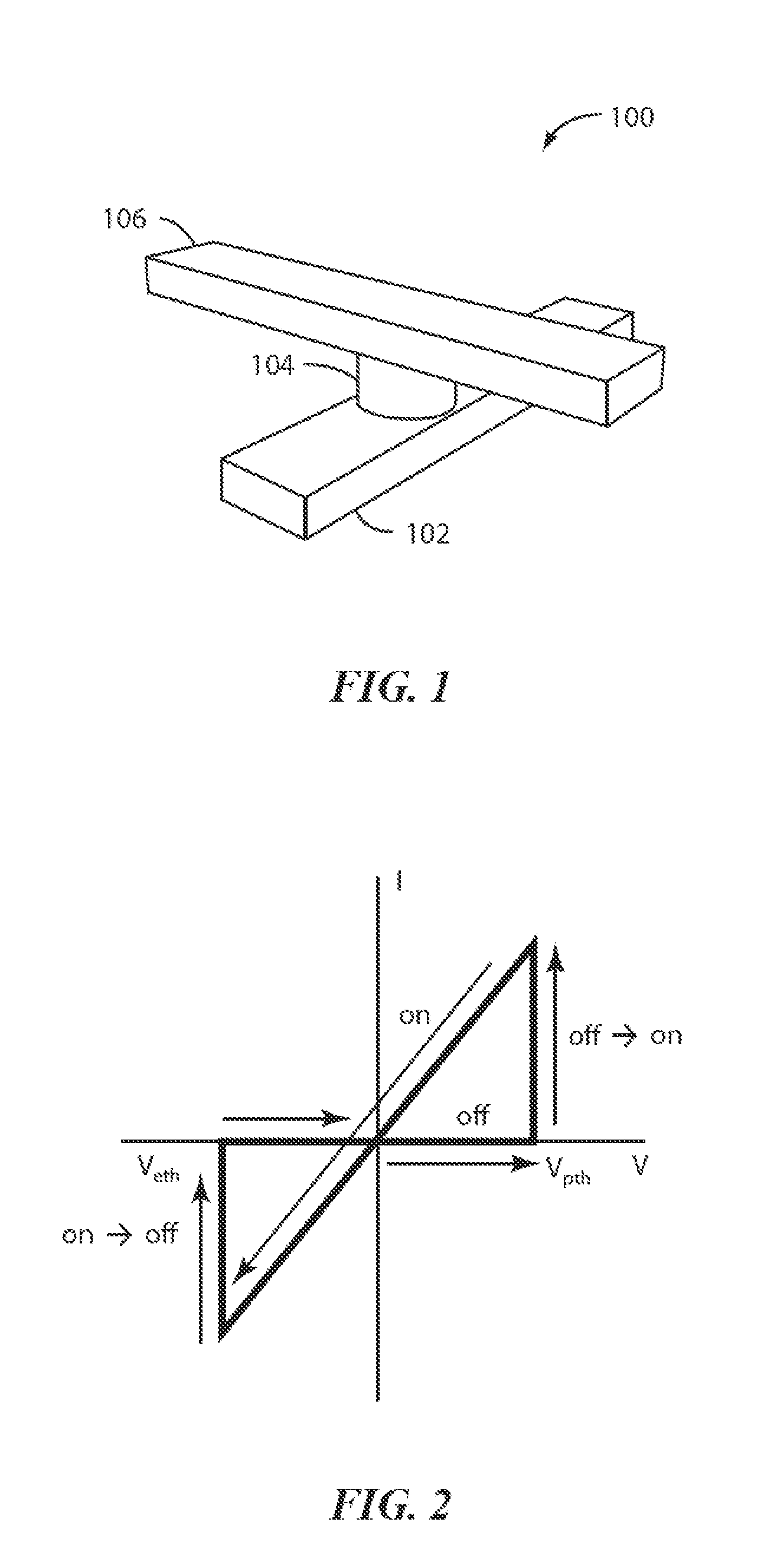

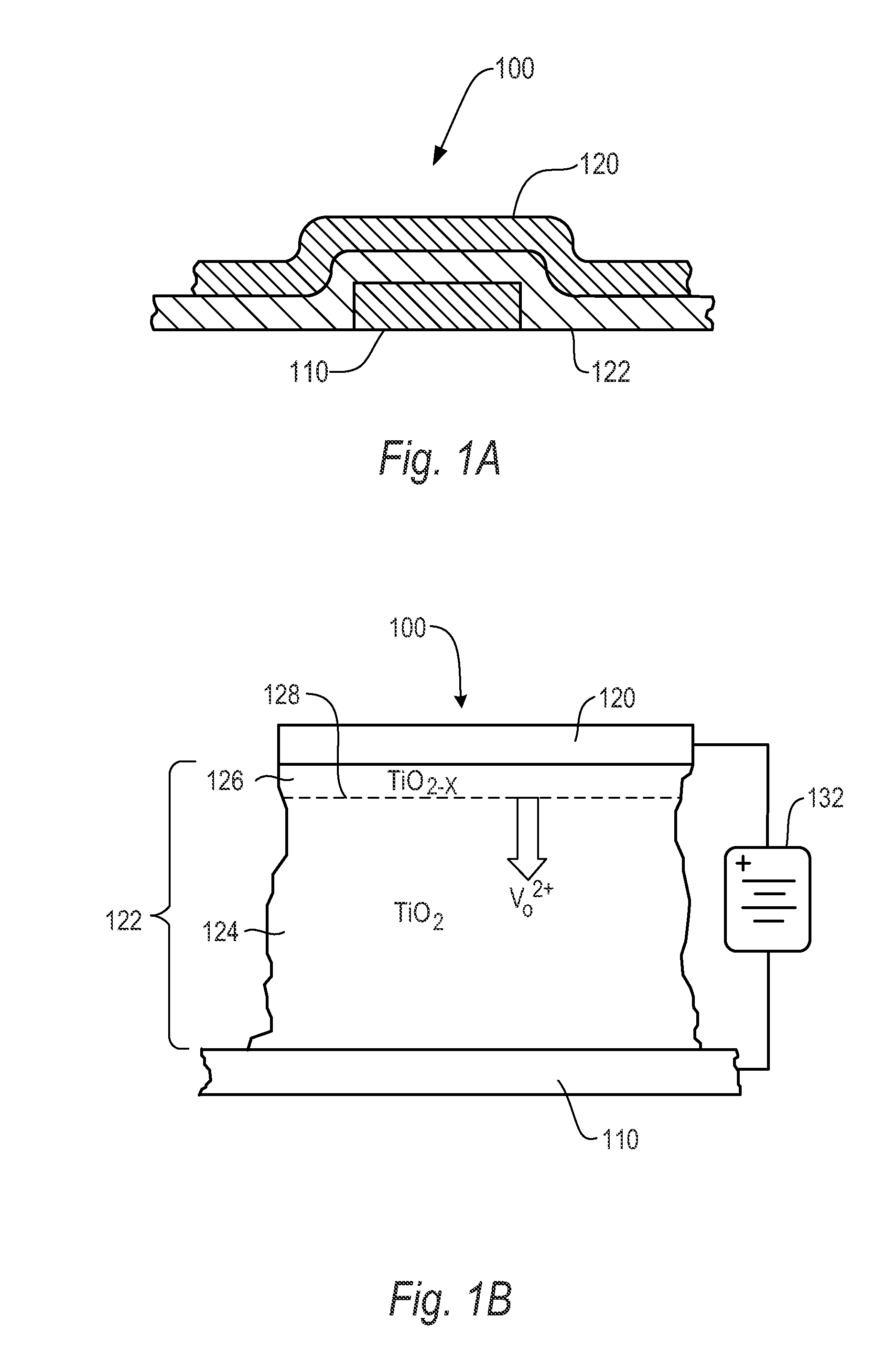

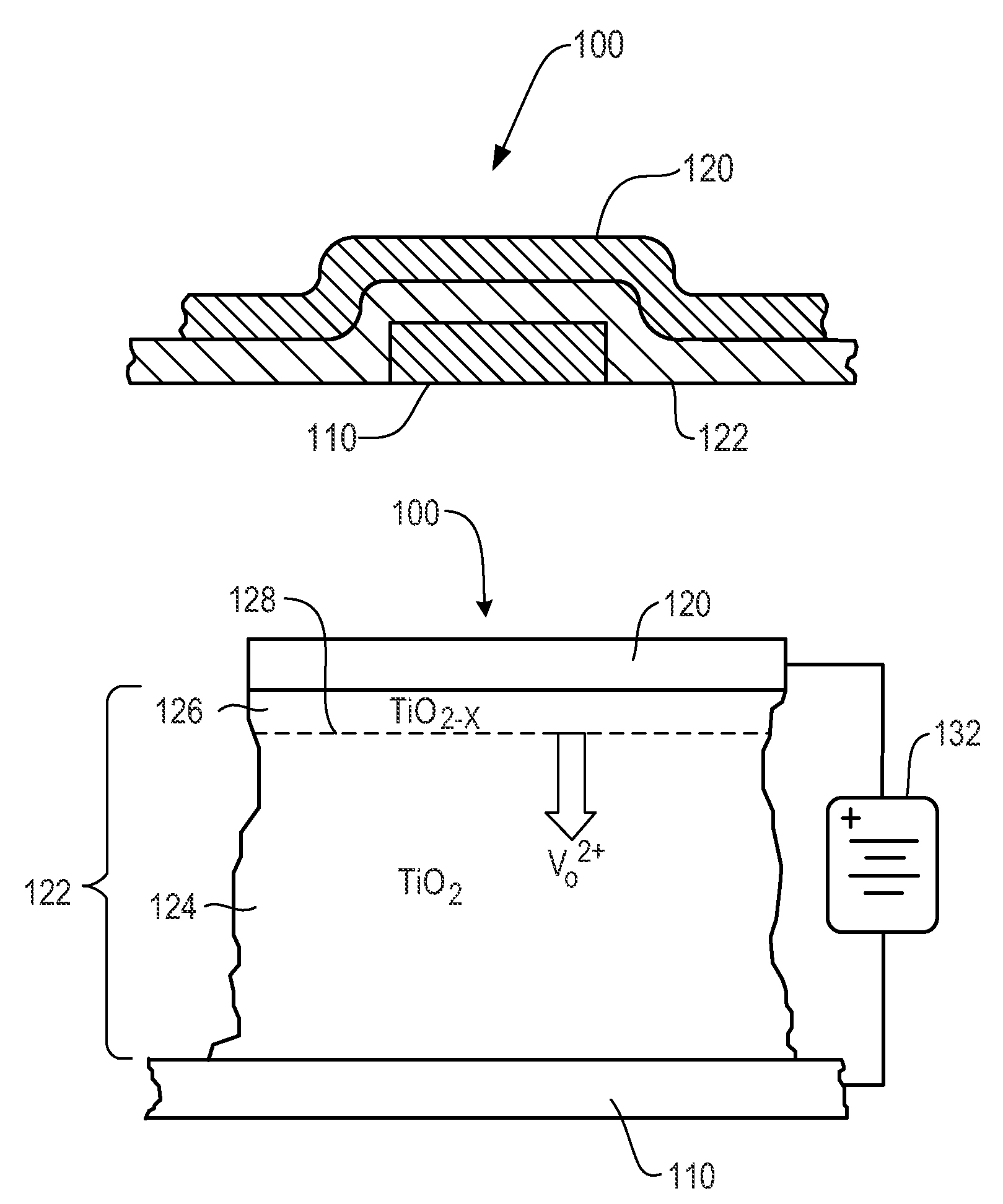

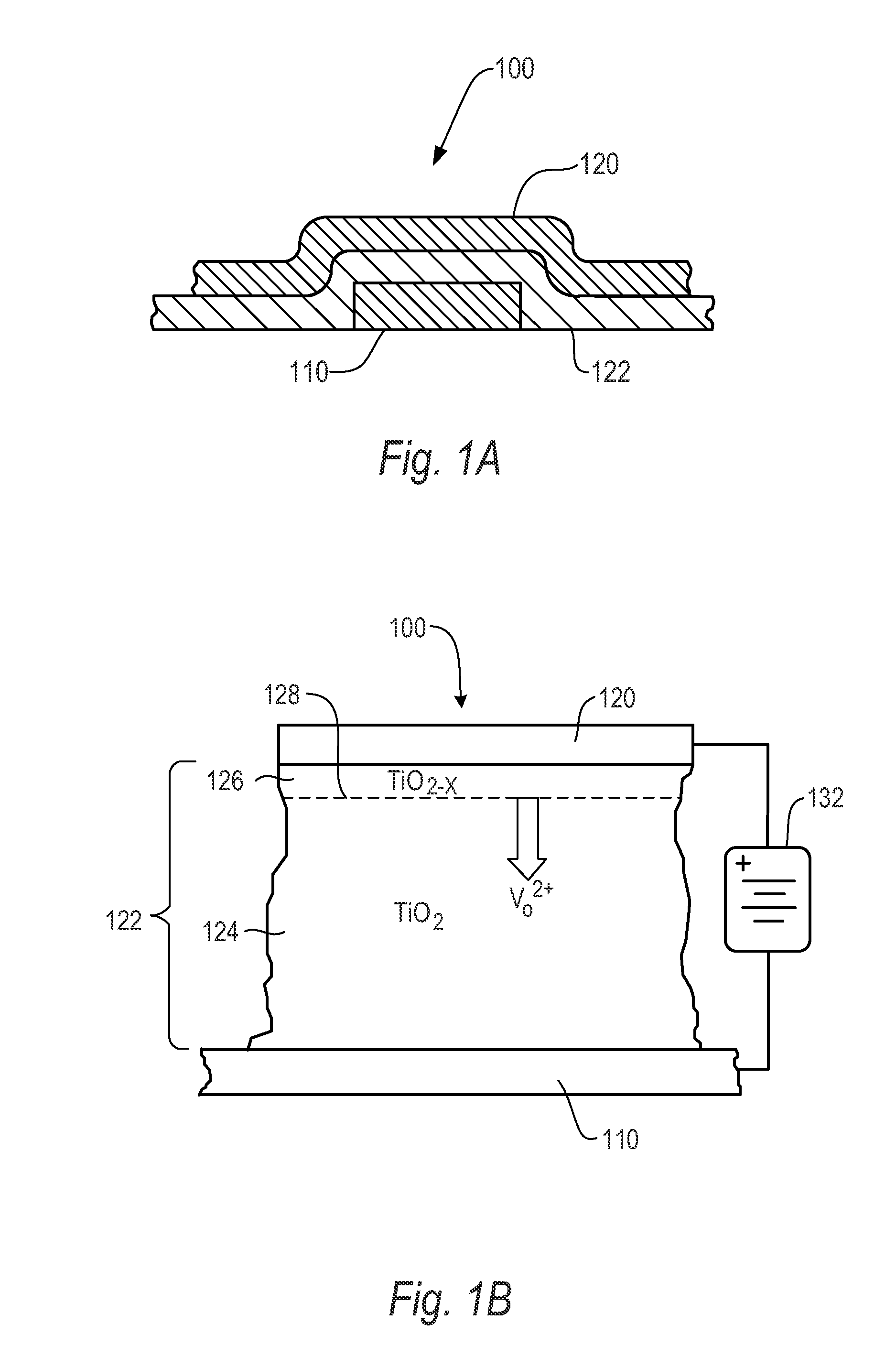

Memristors with an electrode metal reservoir for dopants

ActiveUS20120074372A1Solid-state devicesSemiconductor/solid-state device manufacturingDopantElectrical conductor

A memristor includes a first electrode of a nanoscale width; a second electrode of a nanoscale width; and an active region disposed between the first and second electrodes. The active region has a both a non-conducting portion and a source of dopants portion induced by electric field. The non-conducting portion comprises an electronically semiconducting or nominally insulating material and a weak ionic conductor switching material capable of carrying a species of dopants and transporting the dopants under an electric field. The non-conducting portion is in contact with the first electrode and the source of dopants portion is in contact with the second electrode. The second electrode comprises a metal reservoir for the dopants. A crossbar array comprising a plurality of the nanoscale switching devices is also provided. A process for making at least one nanoscale switching device is further provided.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

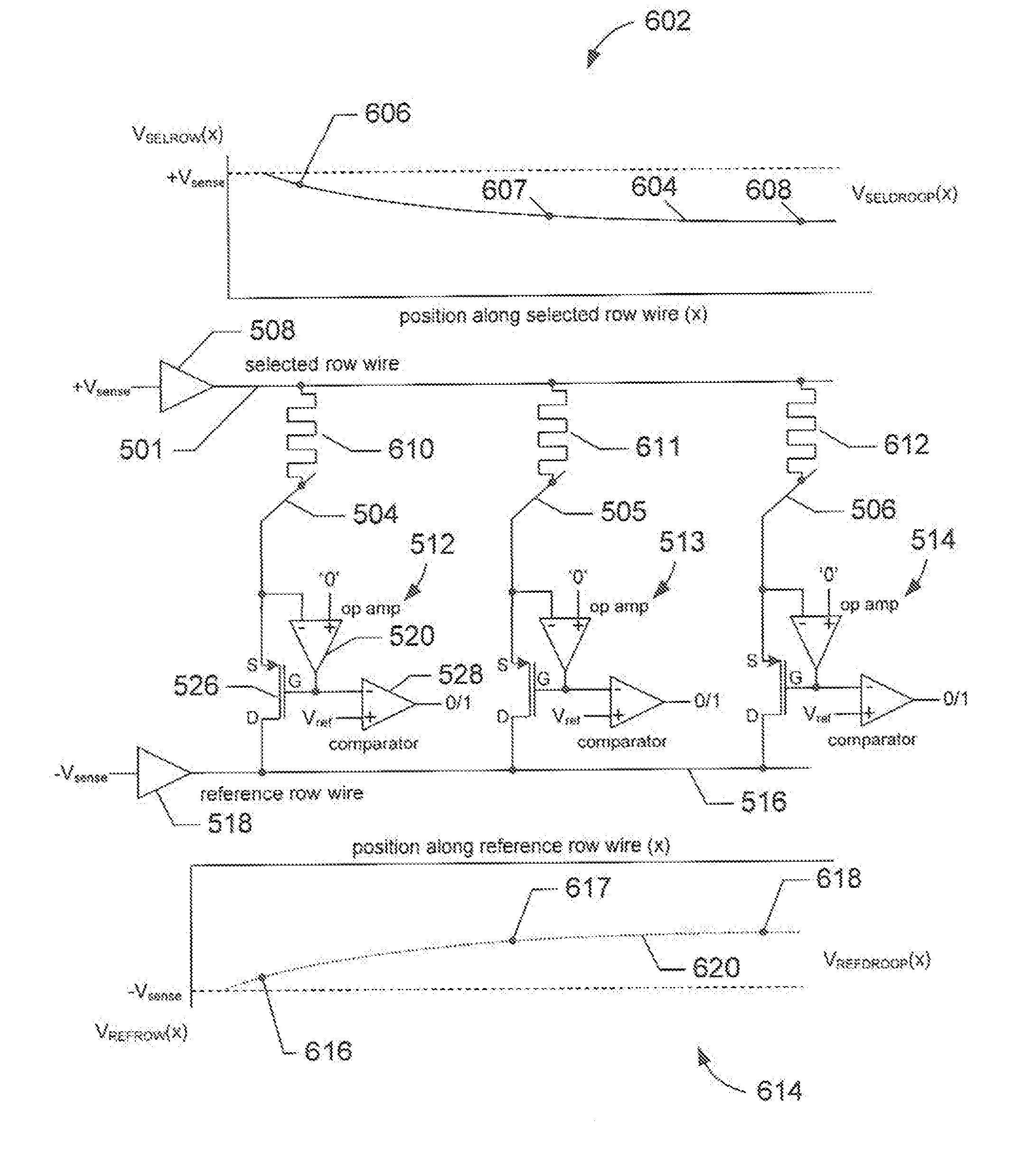

Systems and methods for row-wire voltage-loss compensation in crossbar arrays

ActiveUS20130010521A1NanoinformaticsDigital storageElectrical resistance and conductanceAudio power amplifier

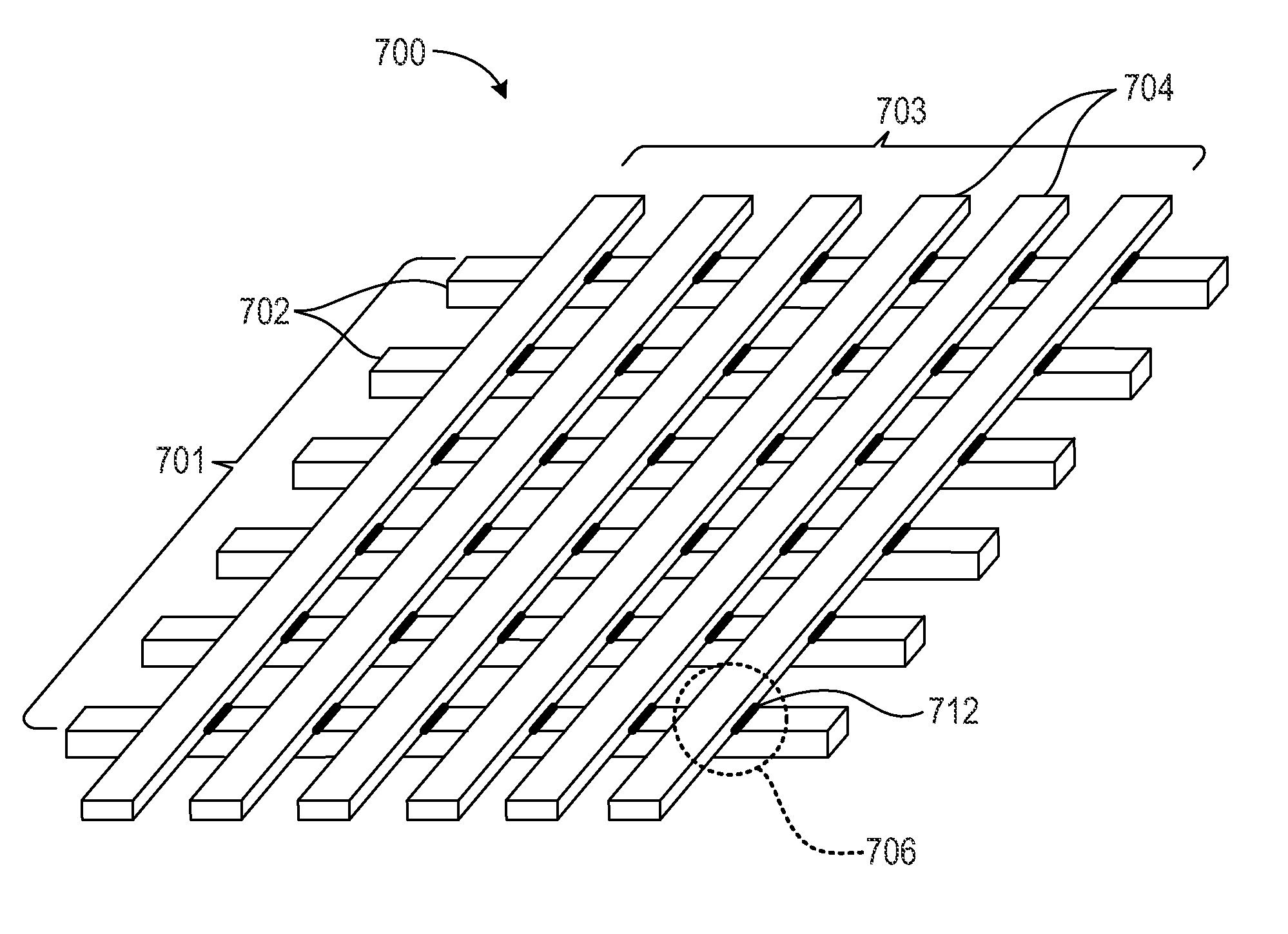

Embodiments of the present invention are directed systems and methods for reading the resistance states of crossbar junctions of a crossbar array. In one aspect, a system includes one or more sense amplifiers (512-514) connected to column wires of the crossbar array, a reference row wire (516) connected to each sense amp, and a wire driver (518) connected to the reference row wire and configured to drive the reference row wire. The sense amplifiers are configured so that when a selected row wire of the crossbar array is driven by a sense voltage, the column wires are held at approximately zero volts and pass currents through the column wires and sense amplifiers to the reference row wire so that resistive voltage losses along the reference row wire substantially mirror the resistive voltage losses along the selected row wire, allowing the sense amplifiers to determine the crossbar junction resistance states.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

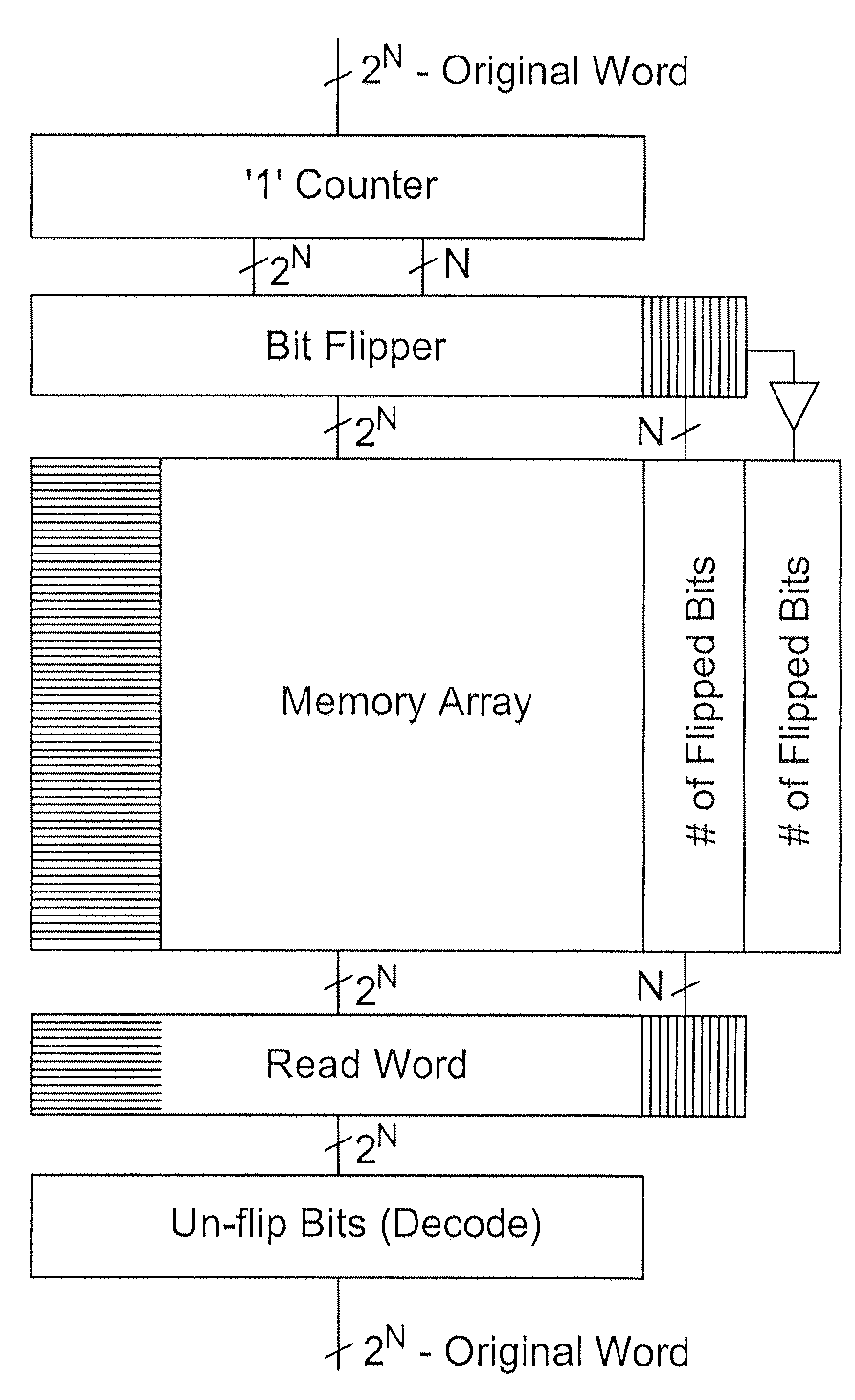

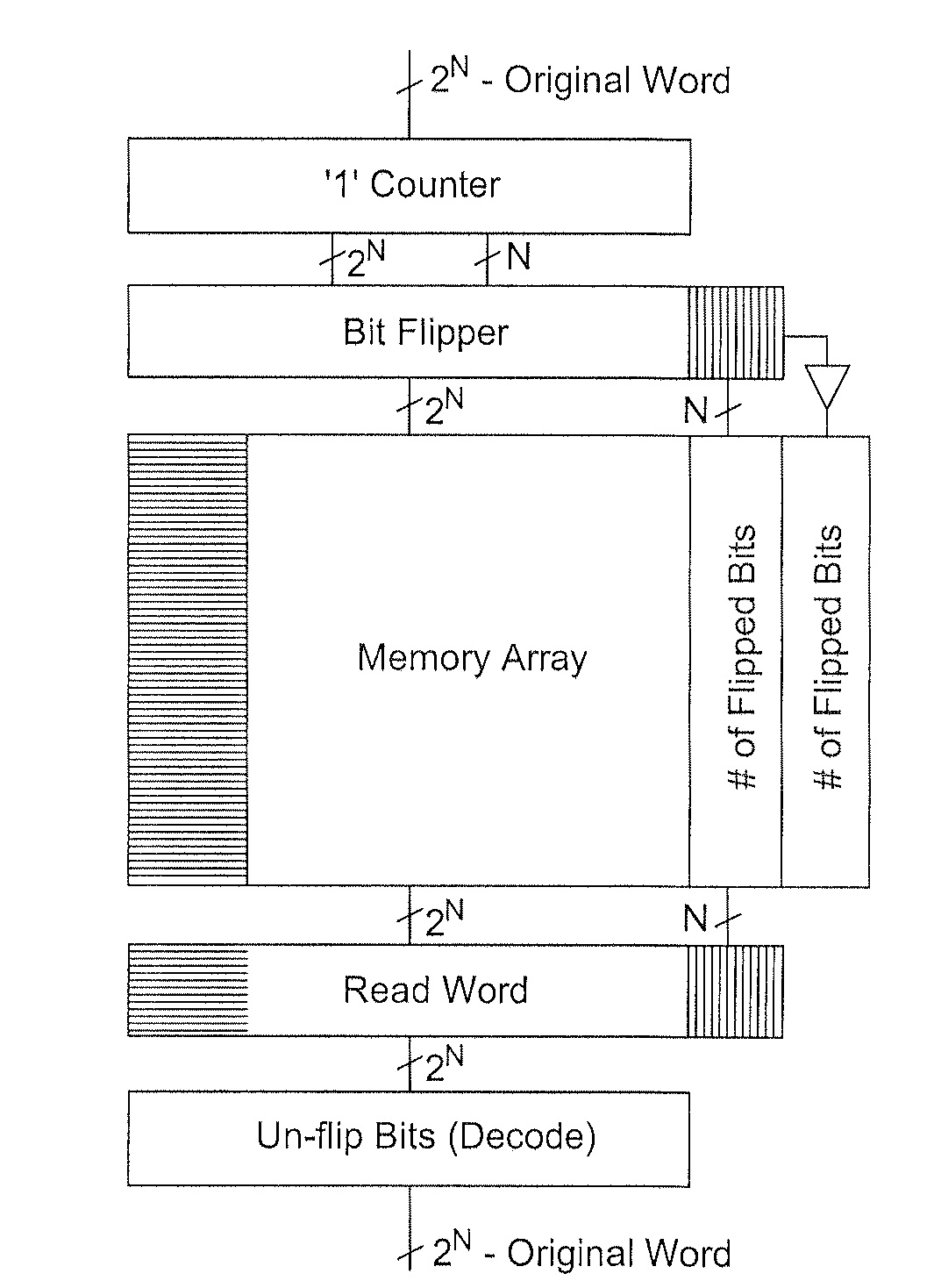

Method and system for encoding to eliminate parasitics in crossbar array memories

ActiveUS8000161B2Increase in sizeEliminate the effects ofNanoinformaticsCode conversionNanowireOriginal data

Owner:UNIV OF VIRGINIA ALUMNI PATENTS FOUND

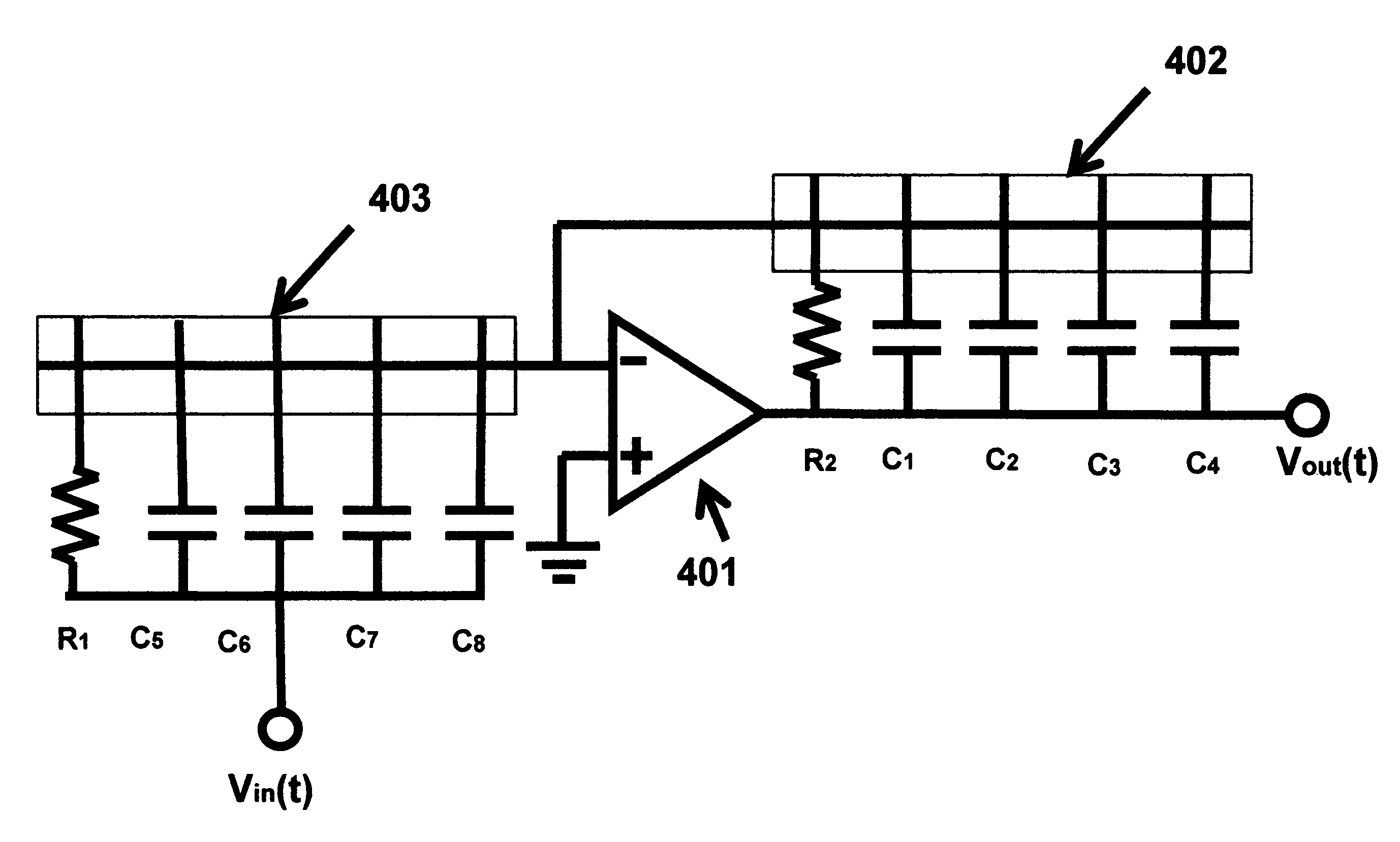

Programmable crossbar signal processor with op-amp outputs

A device including a crossbar array including a programmable material layer and an array of op-amps connected to outputs of the crossbar array.

Owner:MOUTTET BLAISE LAURENT

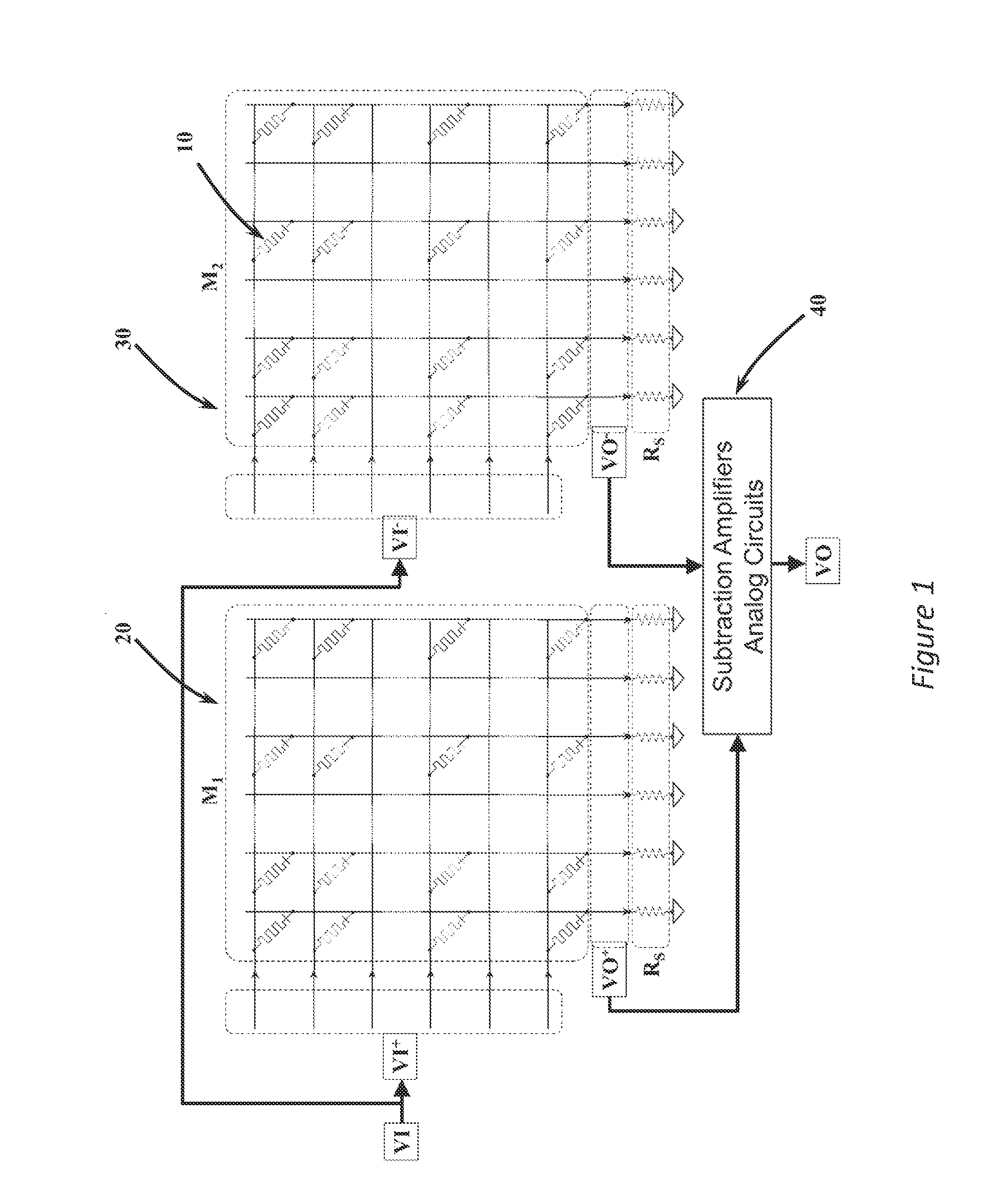

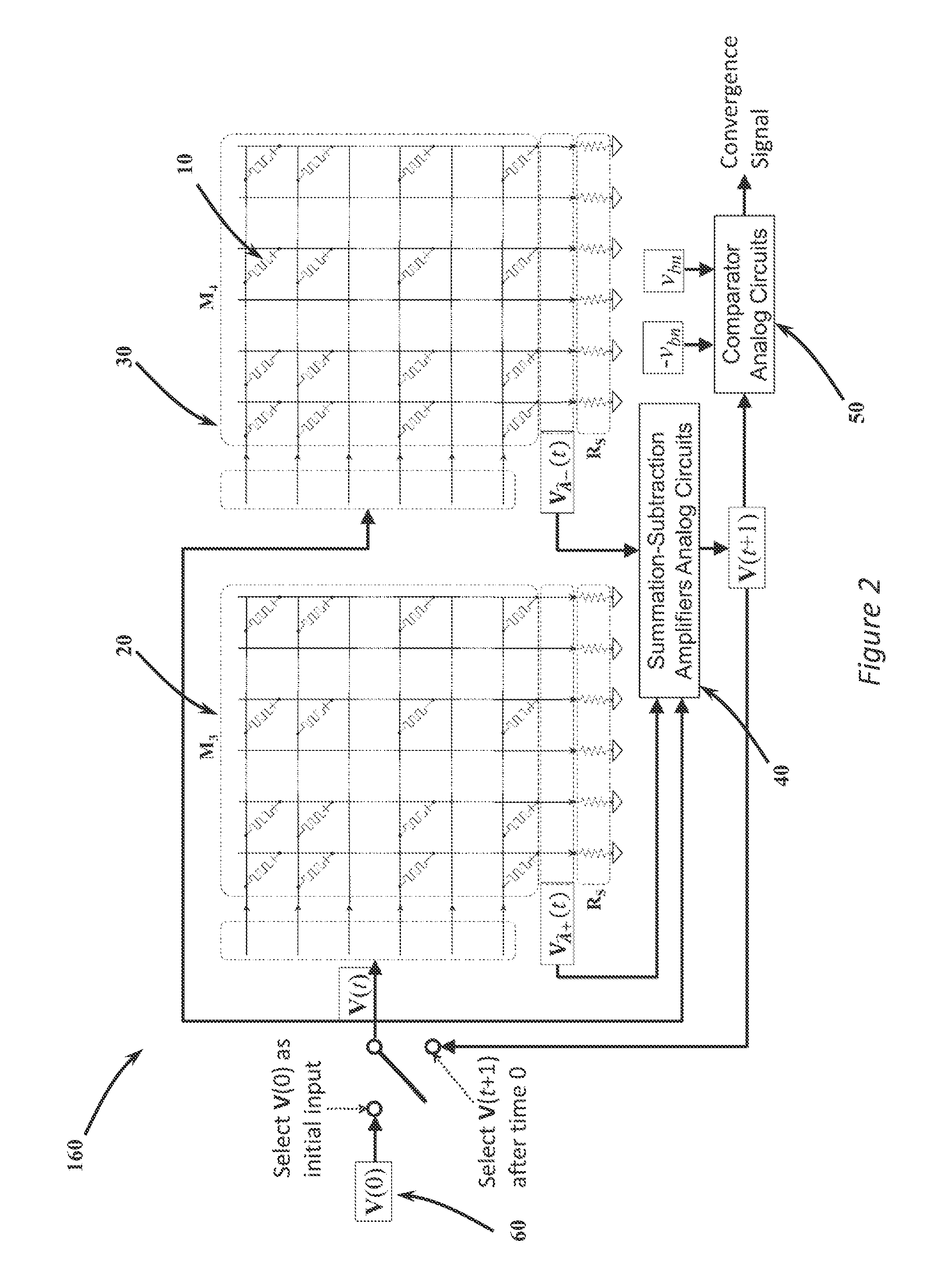

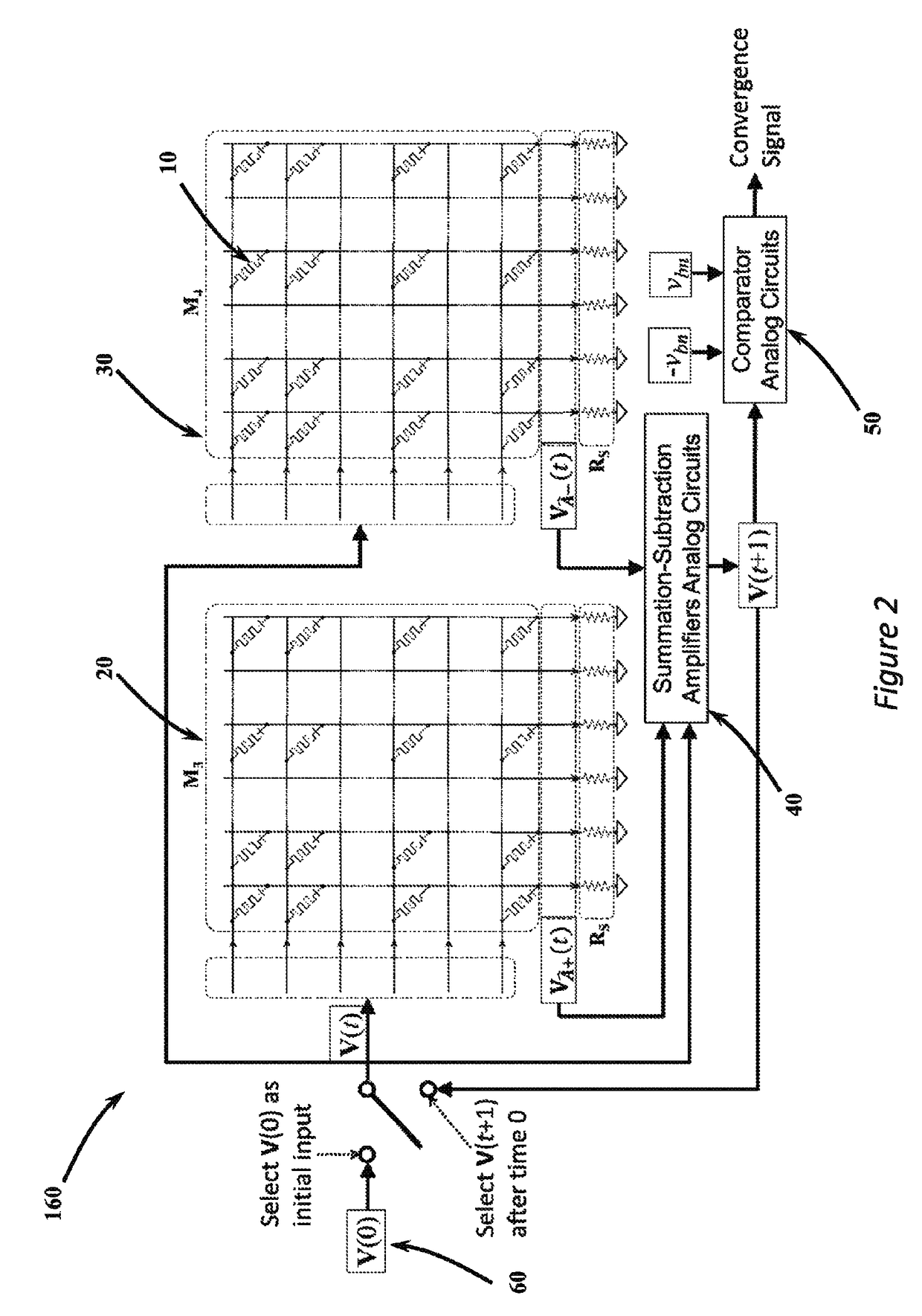

Systems for introducing memristor random telegraph noise in hopfield neural networks

Systems are provided for implementing a hardware accelerator. The hardware accelerator emulate a stochastic neural network, and includes a first memristor crossbar array, and a second memristor crossbar array. The first memristor crossbar array can be programmed to calculate node values of the neural network. The nodes values can be calculated in accordance with rules to reduce an energy function associated with the neural network. The second memristor crossbar array is coupled to the first memristor crossbar array and programmed to introduce noise signals into the neural network. The noise signals can be introduced such that the energy function associated with the neural network converges towards a global minimum and modifies the calculated node values.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Operational amplifier with resistance switch crossbar feedback

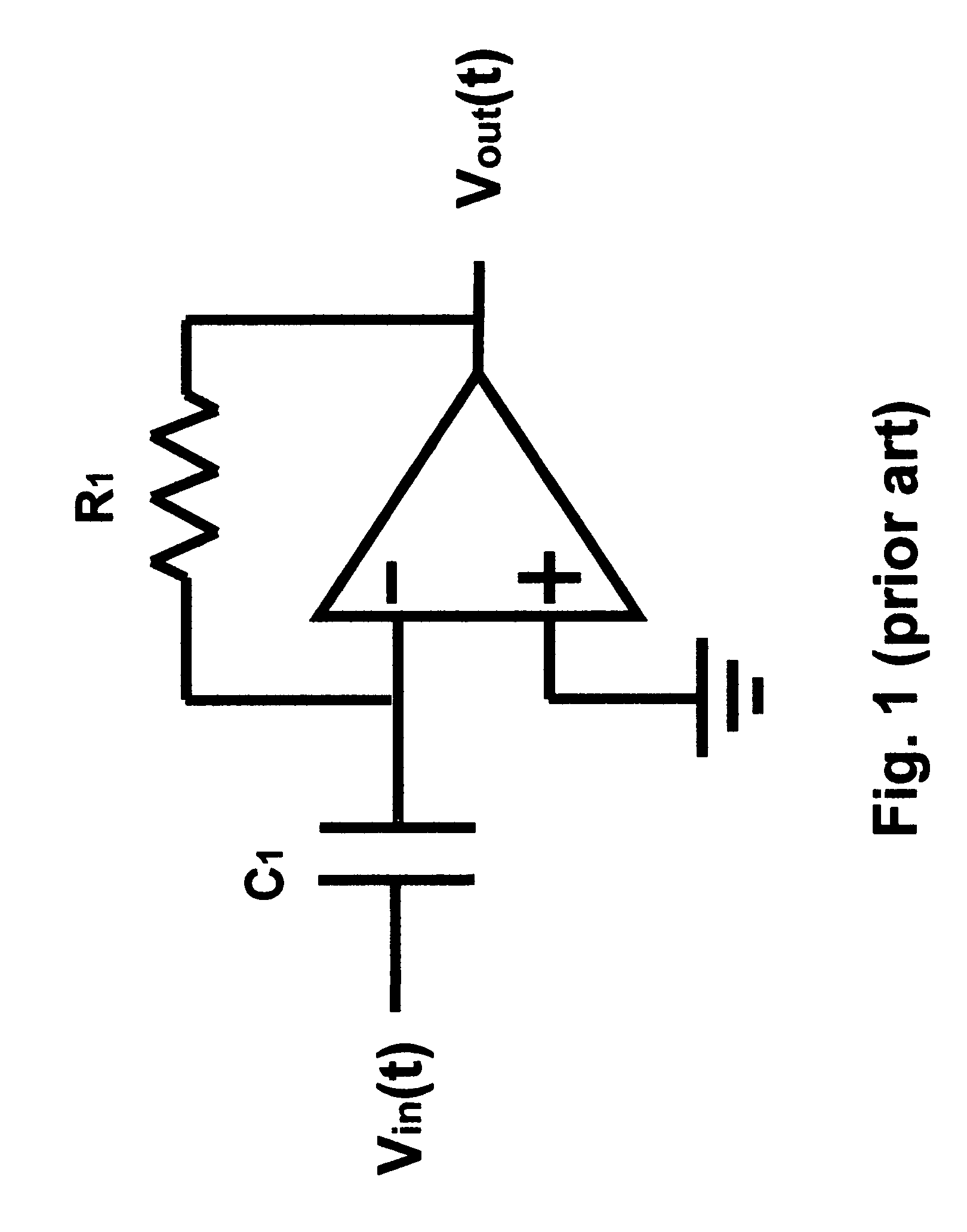

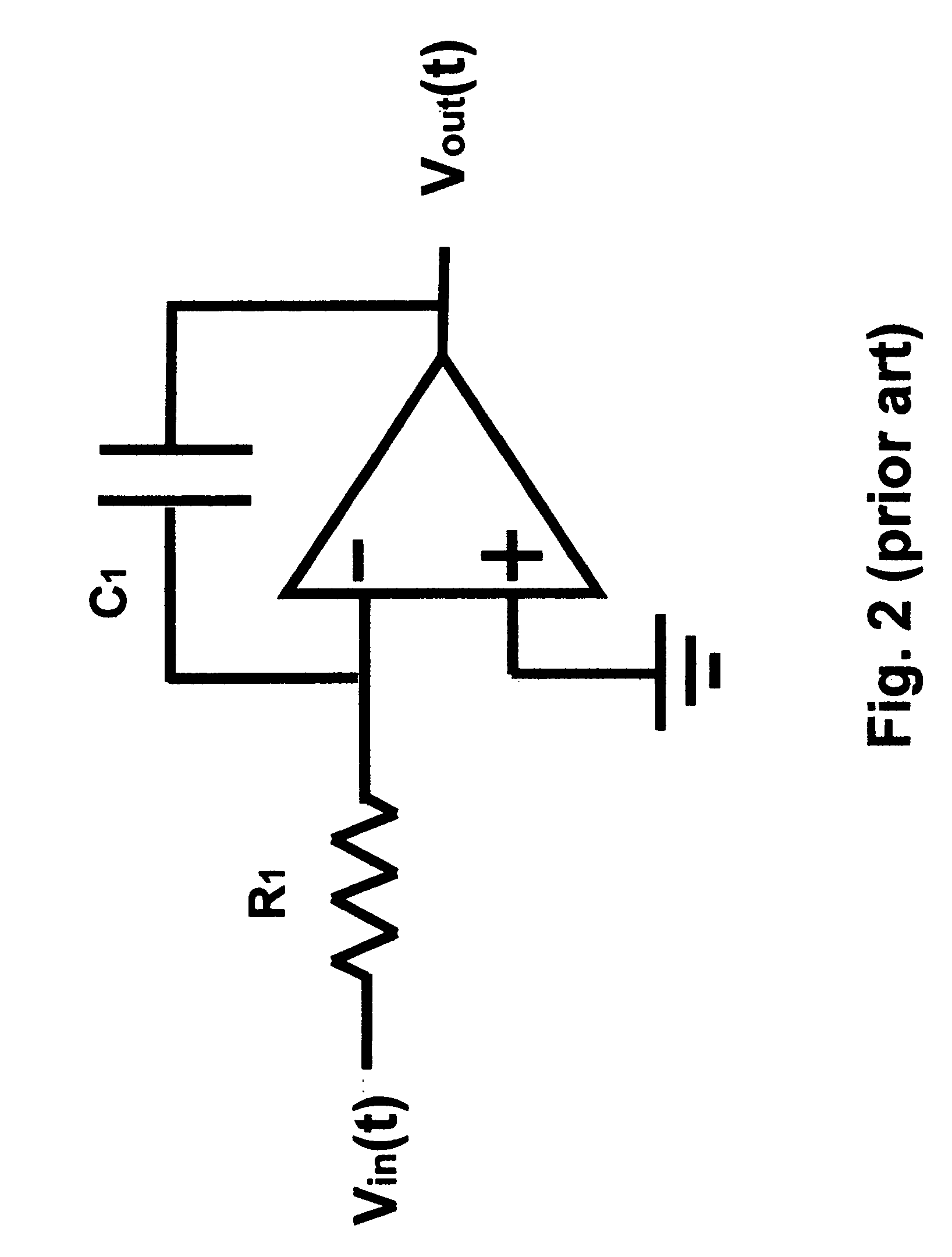

InactiveUS7755424B2Negative-feedback-circuit arrangementsAmplifier modifications to reduce temperature/voltage variationElectrical resistance and conductanceAudio power amplifier

A control circuit includes an operational amplifier having an inverting input, a non-inverting input, and an output, an array of impedance elements including capacitors are connected to the output of the operational amplifier, and a resistance switch crossbar array configured to store data in the form of high or low resistance states, wherein the resistance switch crossbar array is electrically connected between the array of impedance elements and the inverting input of the operational amplifier. The crossbar control circuit may be implemented in a control system to provide for adjustment of the control system to changes in environmental conditions or to change the function of the control system.

Owner:MOUTTET BLAISE LAURENT

Non-volatile resistive random access memory crossbar devices with maximized memory element density and methods of forming the same

ActiveUS20160087197A1Solid-state devicesSemiconductor/solid-state device manufacturingBit lineCrossbar switch

Non-volatile resistive random access memory crossbar devices and methods of fabricating the same are provided herein. In an embodiment, a non-volatile resistive random access memory crossbar device includes a crossbar array including a bitline and a wordline. A hardmask that includes dielectric material is disposed over the bitline. The hardmask and the bitline include a first sidewall. A memory element layer and a selector layer are disposed in overlying relationship on the first sidewall of the bitline and hardmask. The memory element layer and a selector layer are further disposed between the bitline and the wordline, to form a first memory element and selector pair.

Owner:GLOBALFOUNDRIES SINGAPORE PTE LTD

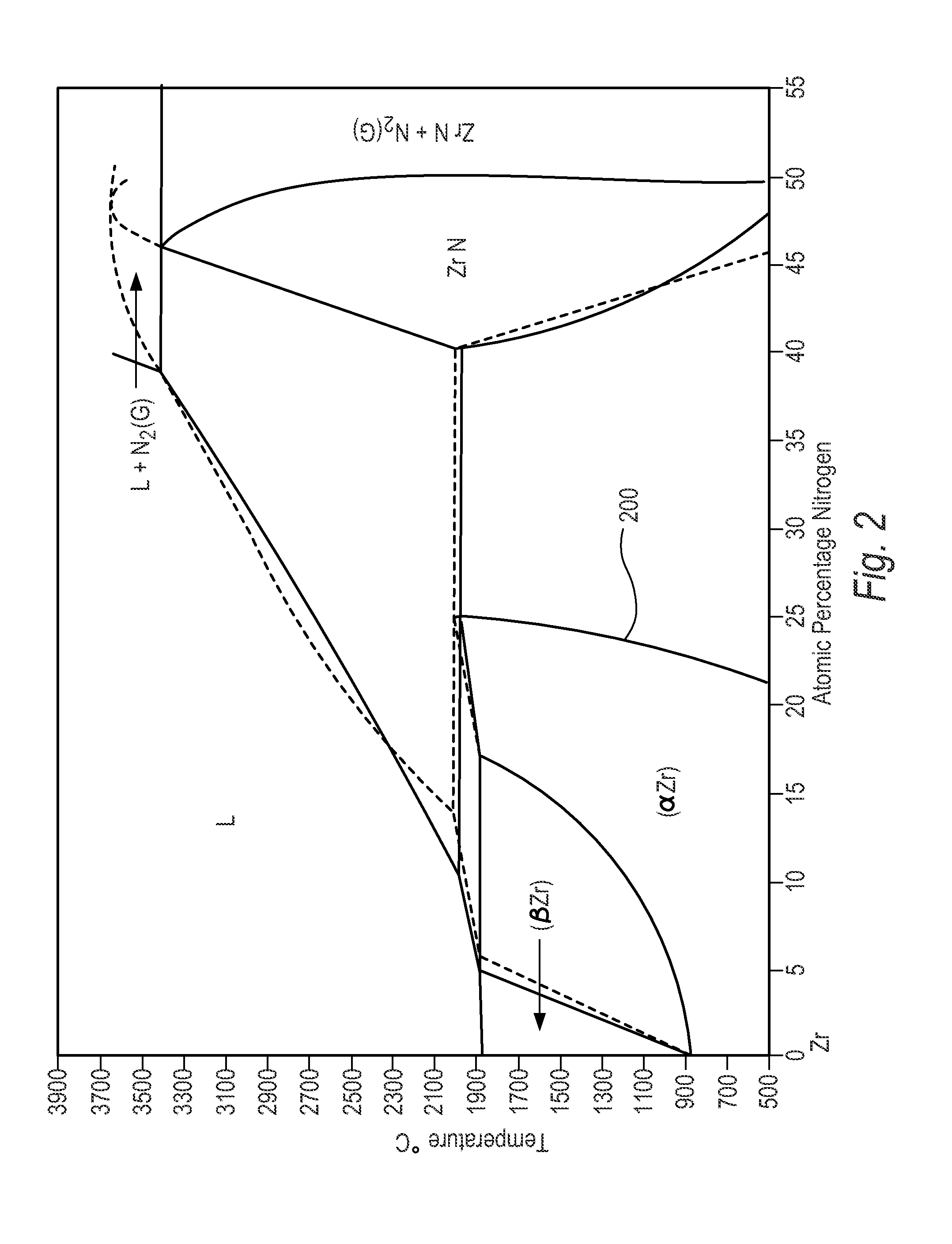

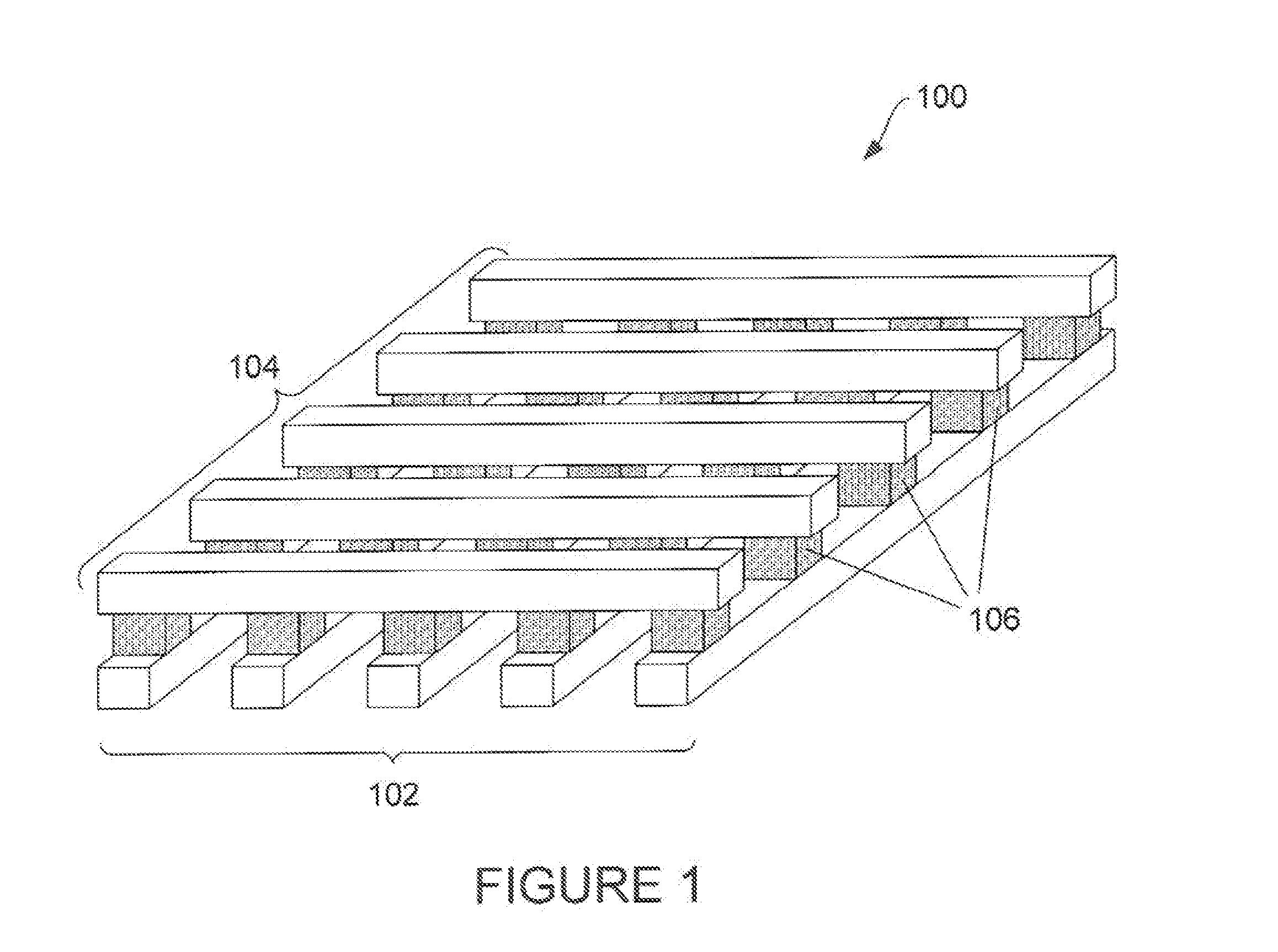

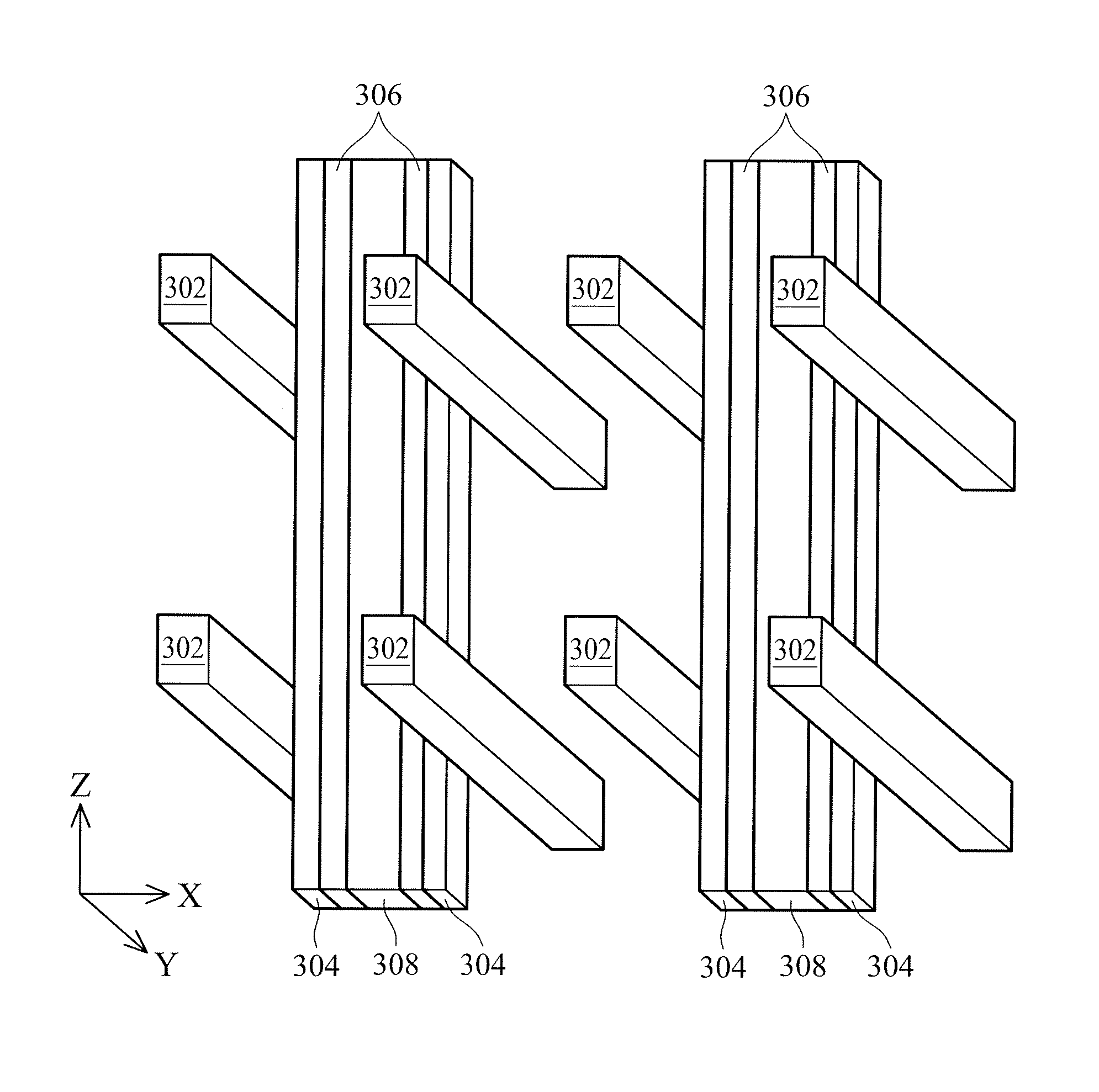

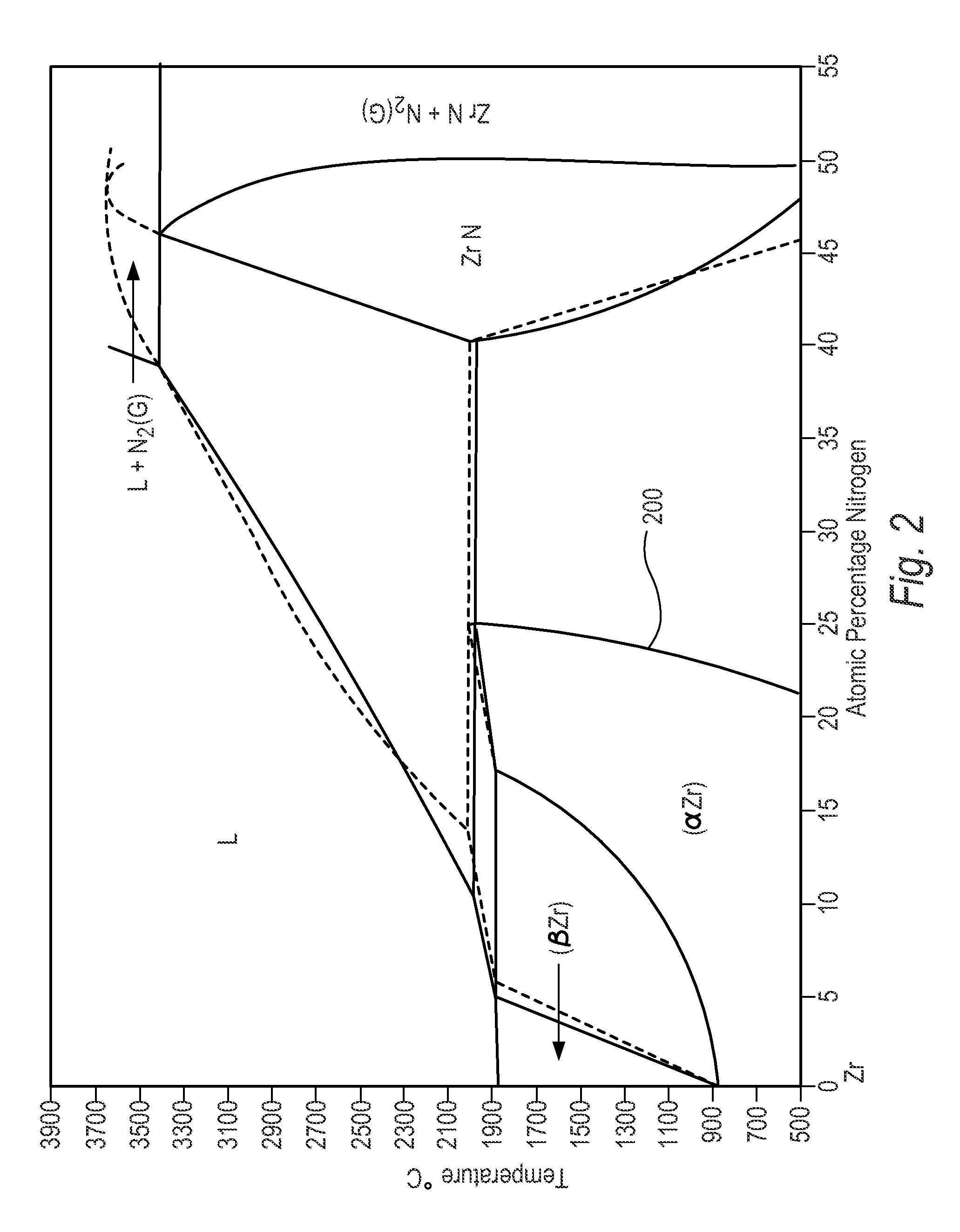

Self-rectifying rram cell structure and rram 3D crossbar array architecture

ActiveUS20160064453A1Solid-state devicesBulk negative resistance effect devicesResistive switchingEngineering

The present disclosure provides a self-rectifying RRAM cell structure including a first electrode layer formed of a nitride of a first metal element, a second electrode layer formed of a second metal element that is different from the first metal element, a first resistive switching layer and a second resistive switching layer. The first resistive switching layer is sandwiched between the first electrode layer and the second resistive switching layer, and the second resistive switching layer is sandwiched between the first resistive switching layer and the second electrode layer. The first resistive switching layer has a first bandgap that is lower than the second bandgap of the second resistive switching layer. Furthermore, a RRAM 3D crossbar array architecture is also provided.

Owner:WINBOND ELECTRONICS CORP

Method and apparatus for performing close-loop programming of resistive memory devices in crossbar array based hardware circuits and systems

ActiveUS9715655B2Reduce Design ComplexityConvenient and accurateDigital storageNeural architecturesElectrical resistance and conductanceNerve network

Method and apparatus for performing close-loop programming of resistive memory devices in crossbar array based hardware circuits and systems. Invention provides iterative training of memristor crossbar arrays for neural networks by applying voltages corresponding to selected training patterns. Error is detected and measured as a function of the actual response to the training patterns versus the expected response to the training pattern.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE

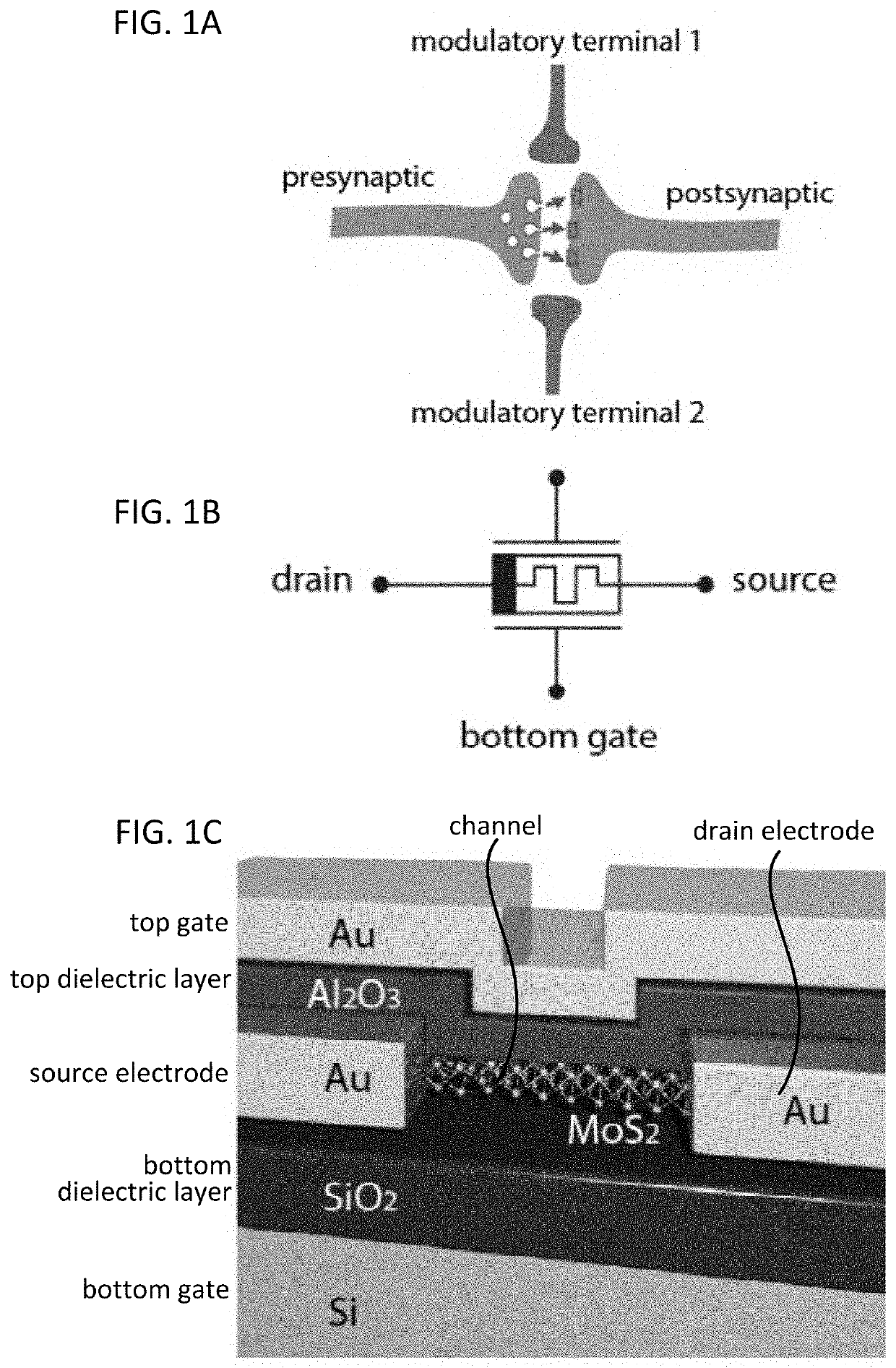

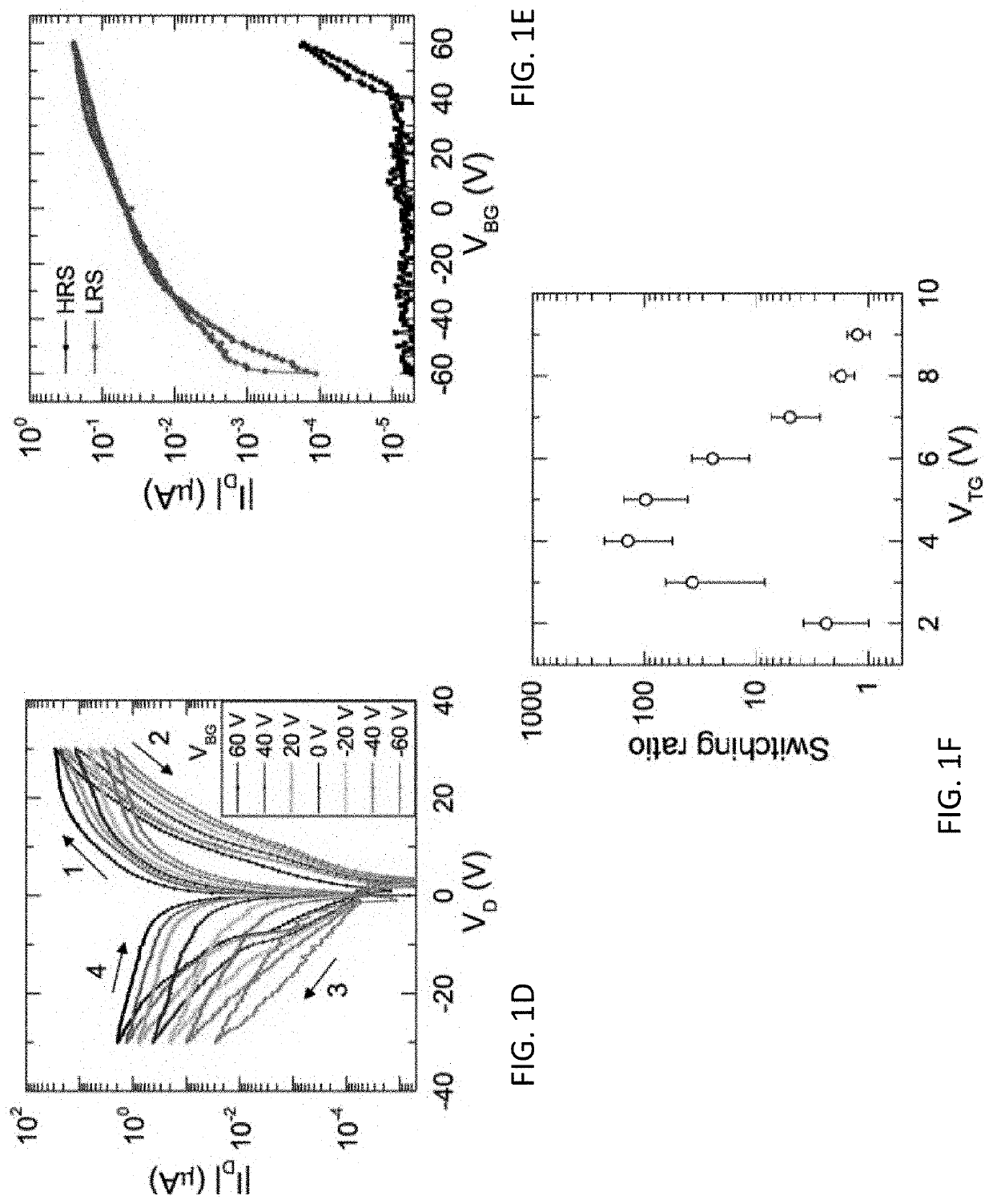

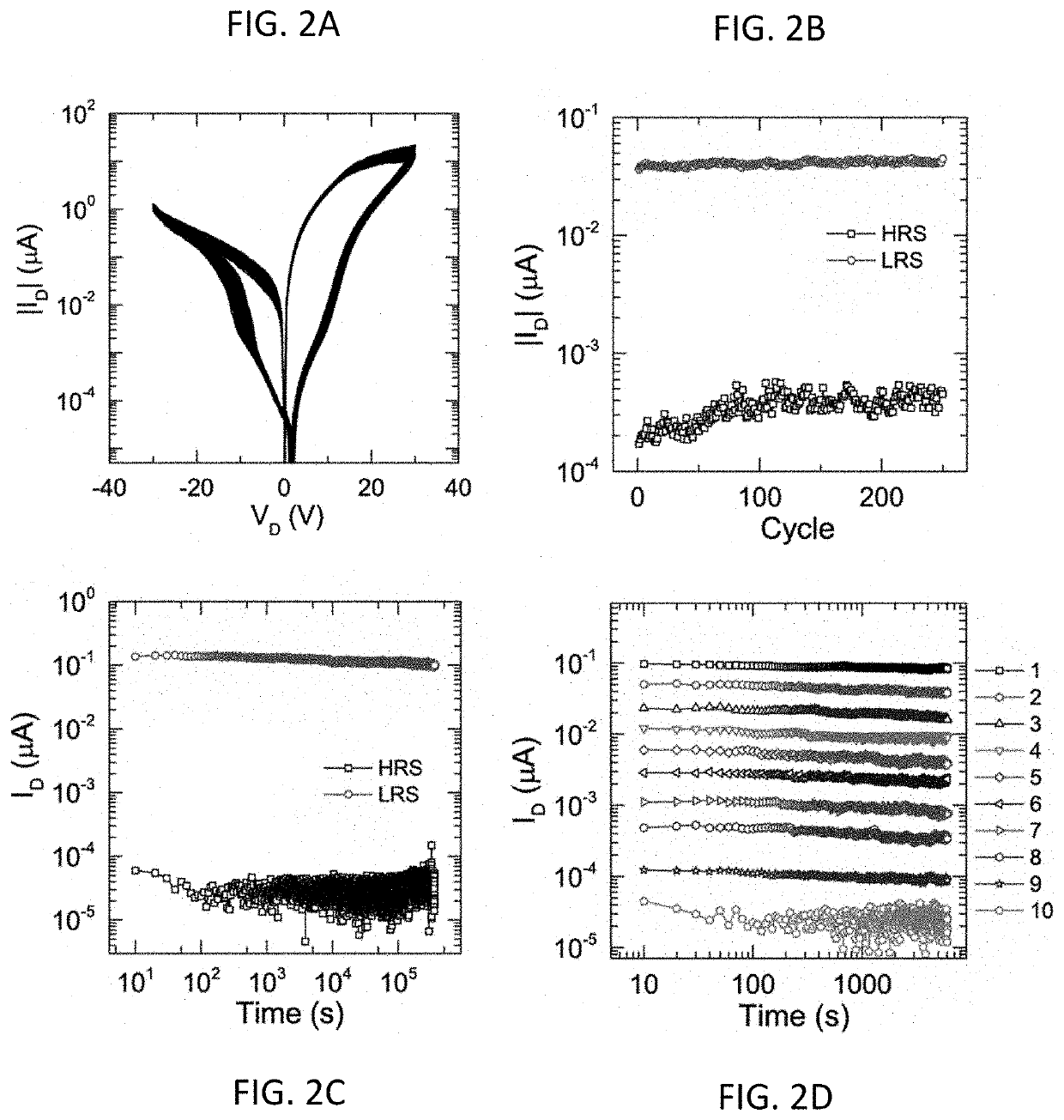

Dual-gated memtransistor crossbar array, fabricating methods and applications of same

PendingUS20210098611A1Improve scalabilityCurrent becomes issueNanoinformaticsSolid-state devicesCapacitanceBottom gate

A memtransistor includes a top gate electrode and a bottom gate electrode; a polycrystalline monolayer film formed of an atomically thin material disposed between the top gate electrode and the bottom gate electrode; and source and drain electrodes spatial-apart formed on the polycrystalline monolayer film to define a channel in the polycrystalline monolayer film between the source and drain electrodes. The top gate electrode and the bottom gate electrode are capacitively coupled with the channel.

Owner:NORTHWESTERN UNIV

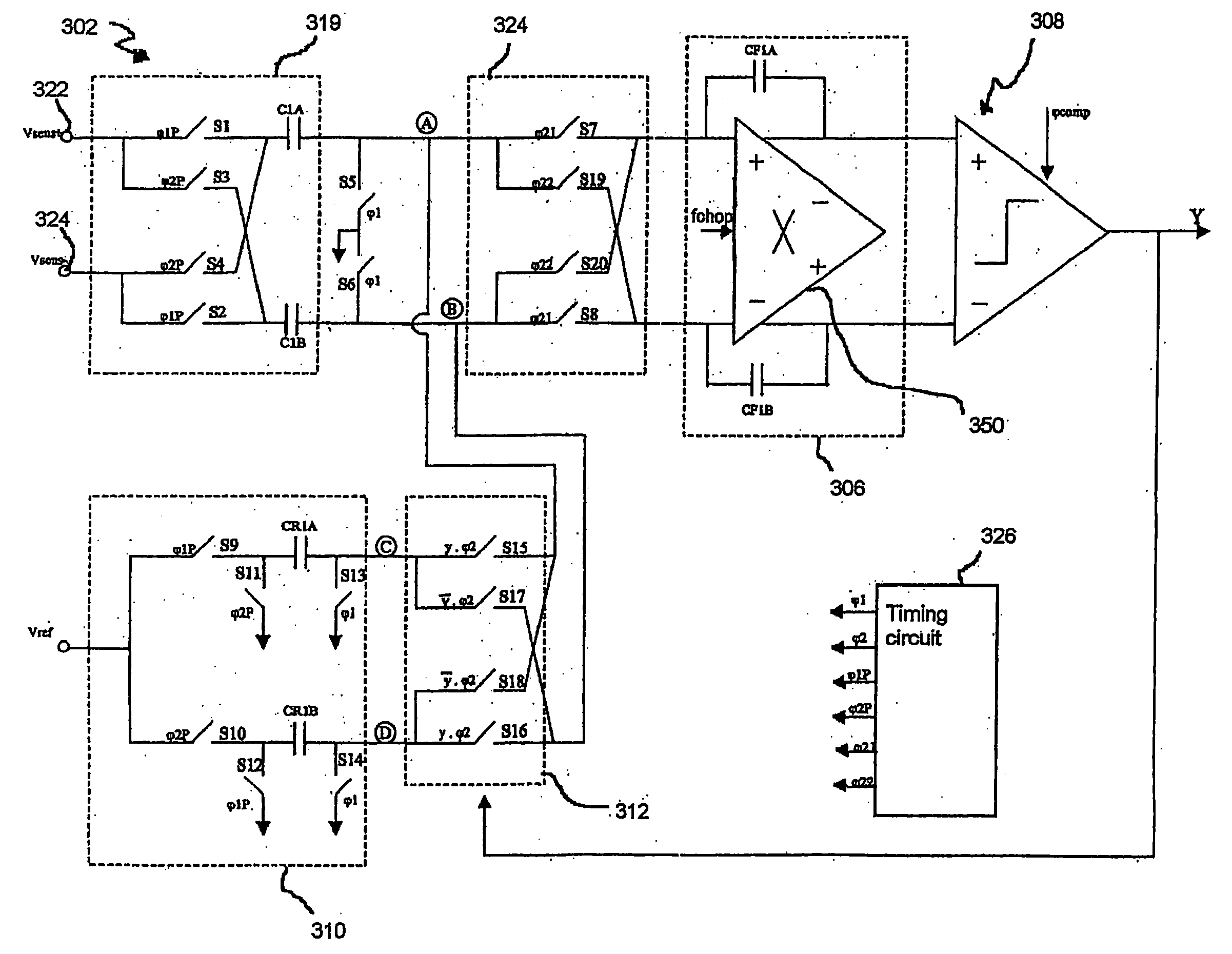

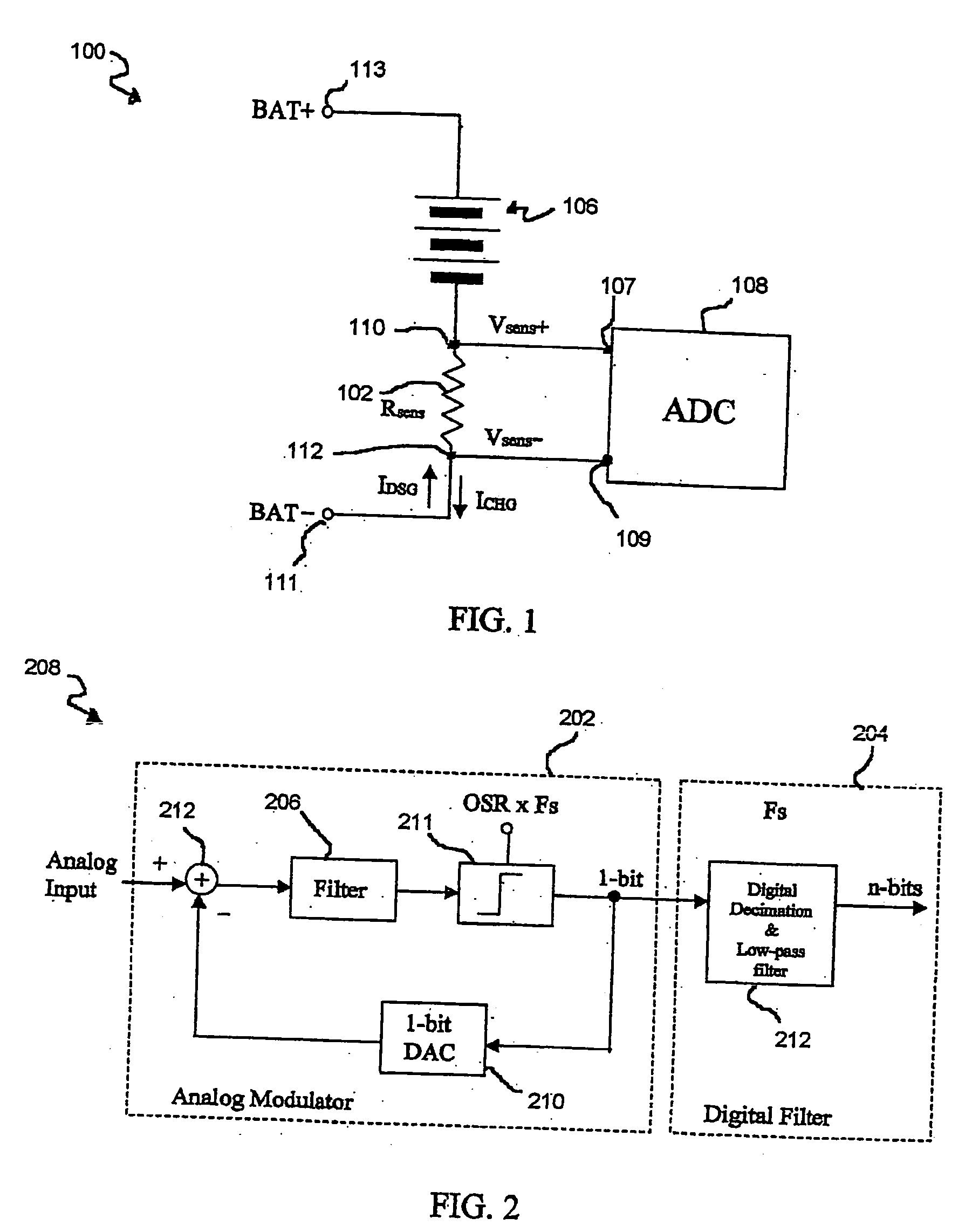

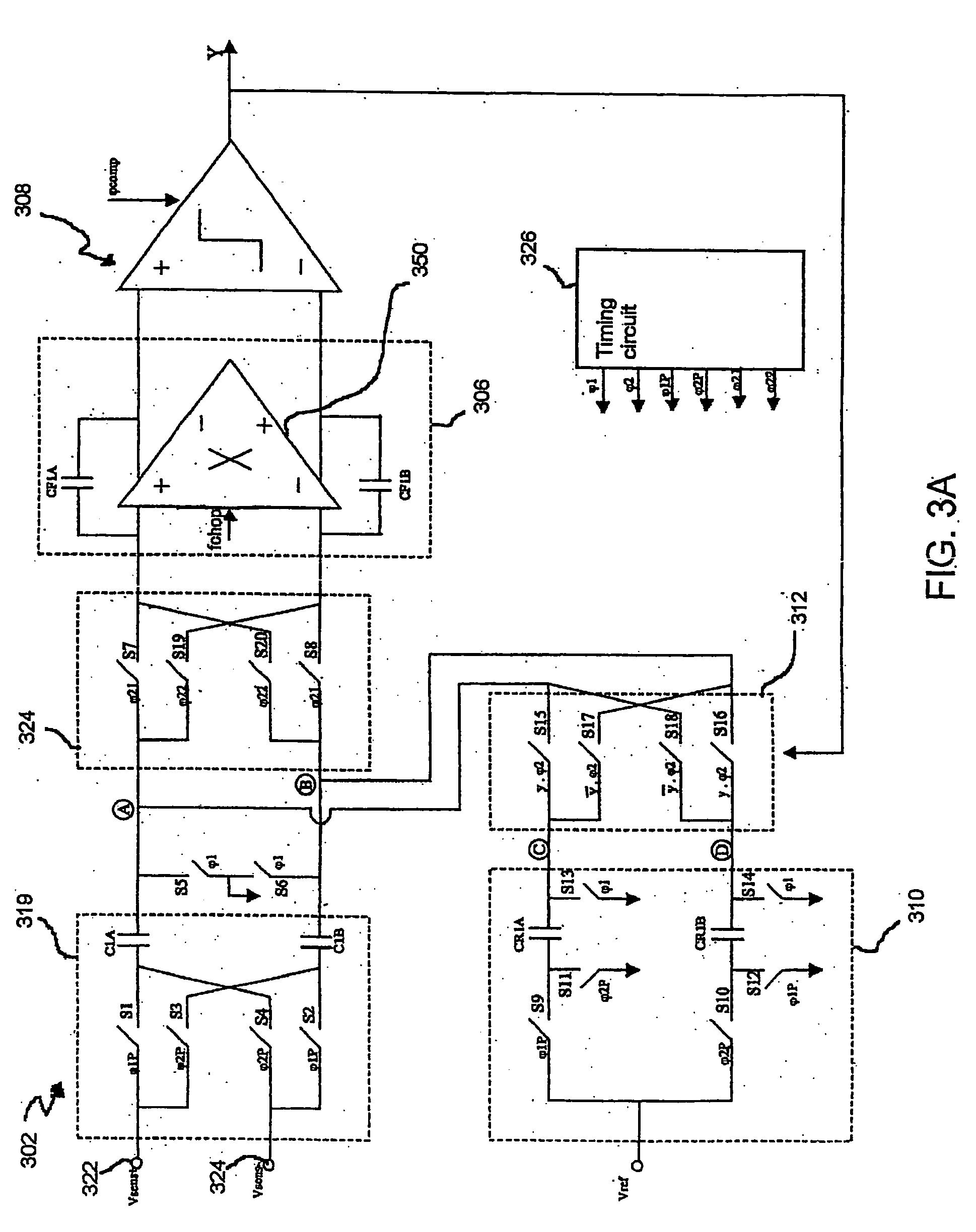

High precision analog to digital converter

An analog to digital converter may include an input switch array configured to alternately sample a first and a second input signal to a first and a second input capacitor during two different sample time intervals, an integrator having a first and second integration capacitor, and a cross switch array coupled to the input switch array and the integrator. The cross switch array may be configured to alternately transfer charges from the first and second input capacitors to the first and second integration capacitors during two different transfer time intervals. A system including an analog to digital converter consistent with an embodiment and an associated method of sampling and transferring charges in an analog to digital converter are also provided.

Owner:O2 MICRO INT LTD

Method and System For Encoding to Eliminate Parasitics in Crossbar Array Memories

ActiveUS20090003040A1Without riskReduce incidenceNanoinformaticsCode conversionNanowireOriginal data

A method of encoding data stored in a crossbar memory array, such as a nanowire crossbar memory array, to enable significant increases in memory size, modifies data words to have equal numbers of ‘1’ bits and ‘0’ bits, and stores the modified words together with information enabling the original data to be retrieved upon being read out from memory.

Owner:UNIV OF VIRGINIA ALUMNI PATENTS FOUND

Programmable crossbar signal processor

A signal processing system is taught to be formed by combining a crossbar array with programming circuitry and signal input circuitry so as to provide a linear transformation from a set of input signals to a set of output signals. Applications of such a system to waveform generation, signal filtering, communications, and pattern recognition are explained. In one embodiment the crossbar array of the signal processing system may be a molecular nanowire crossbar array in which the crossbar interconnects are addressed via dual arrays of scanning probe tips so as to provide an interface between the molecular crossbar electronics and conventional solid state electronics used in the programming and signal processing circuitry.

Owner:MOUTTET BLAISE LAURENT

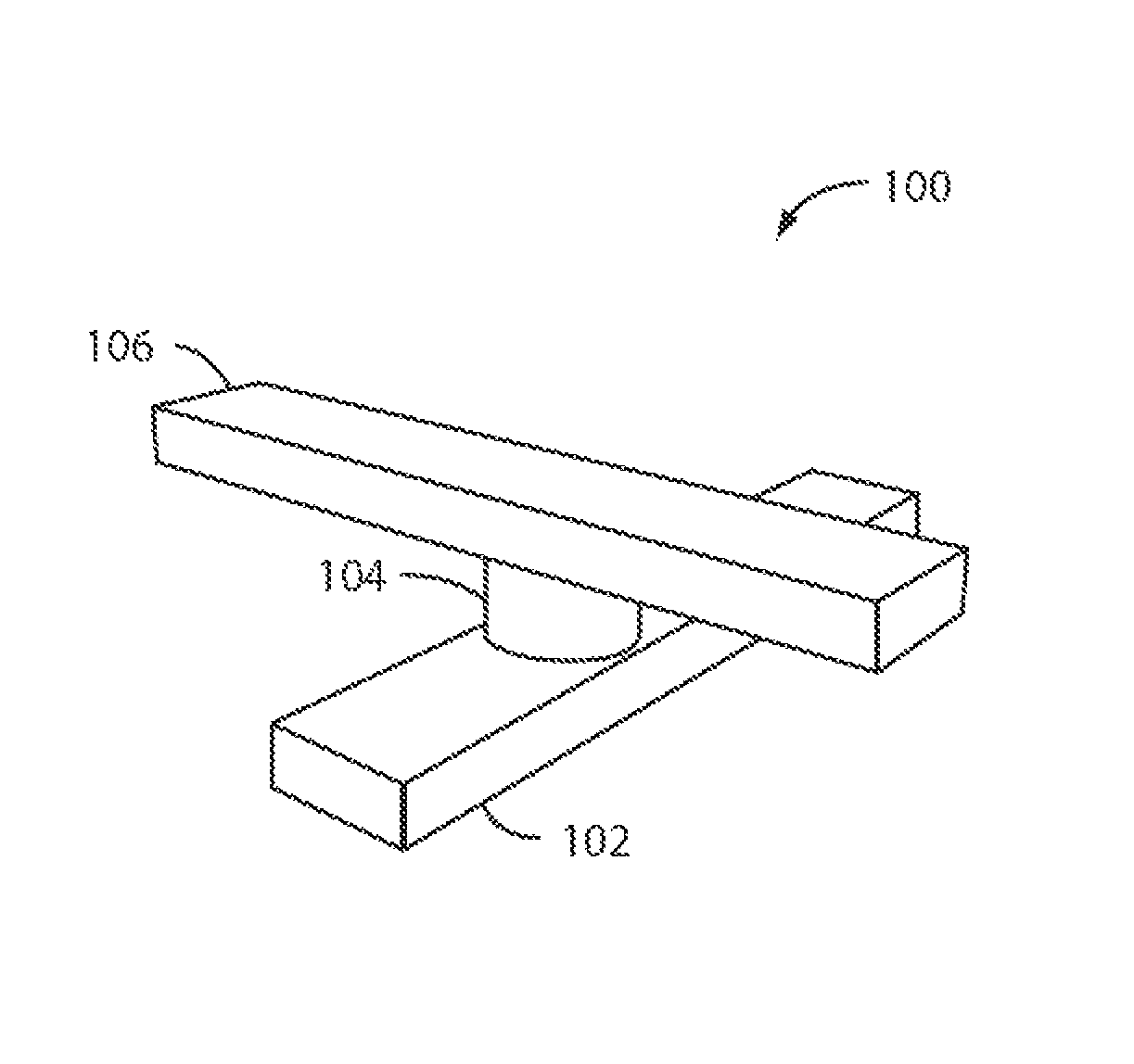

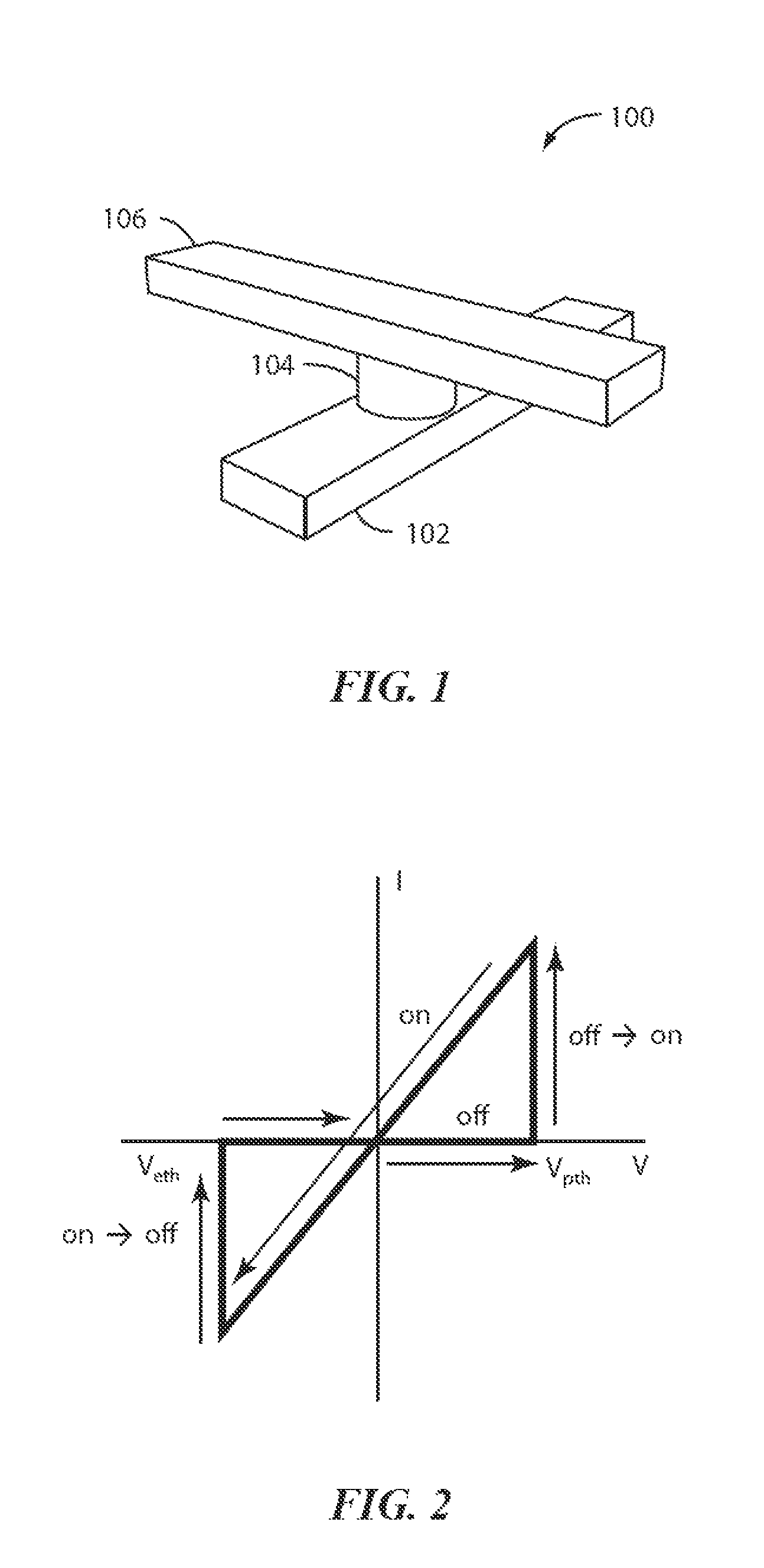

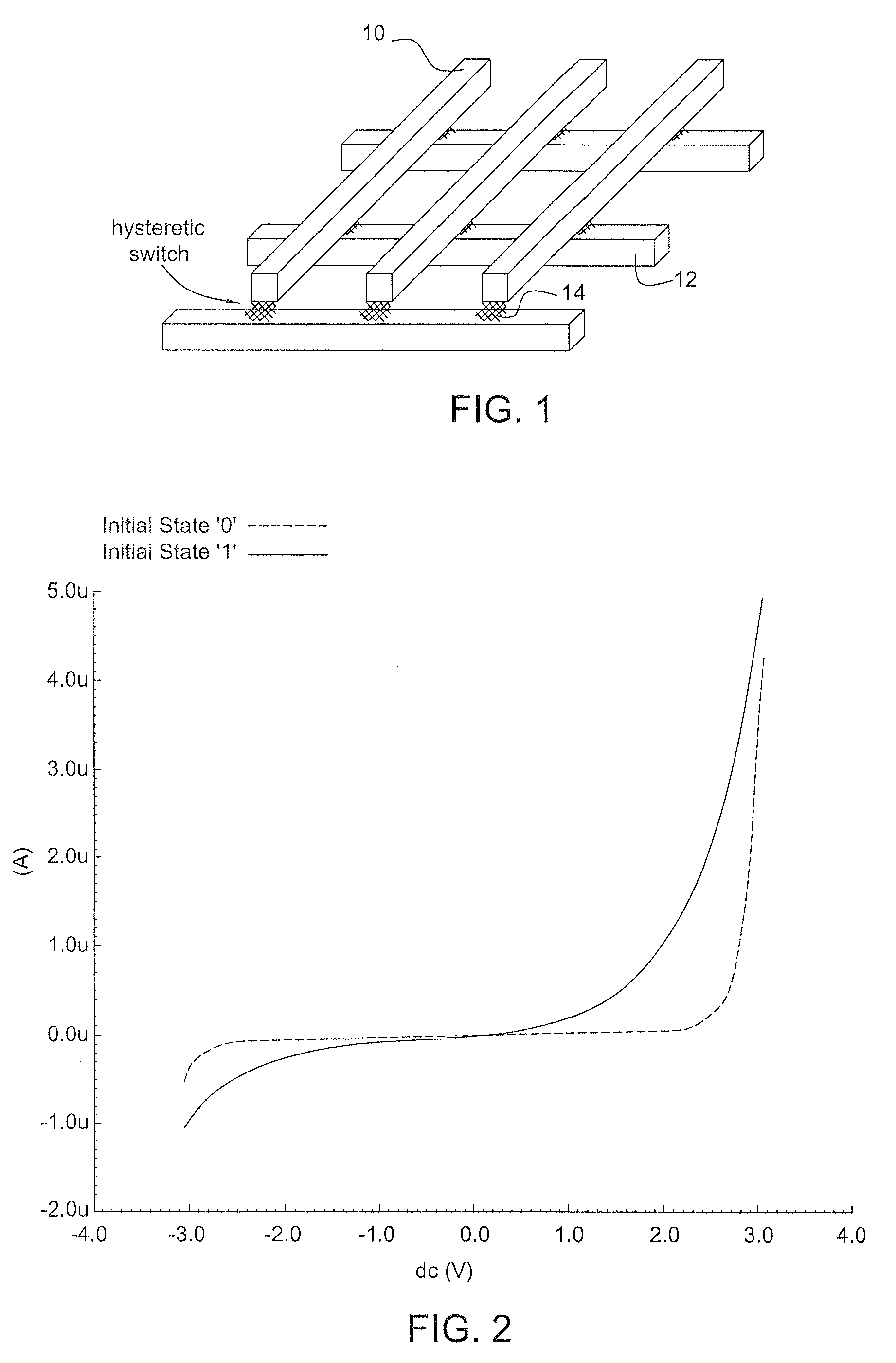

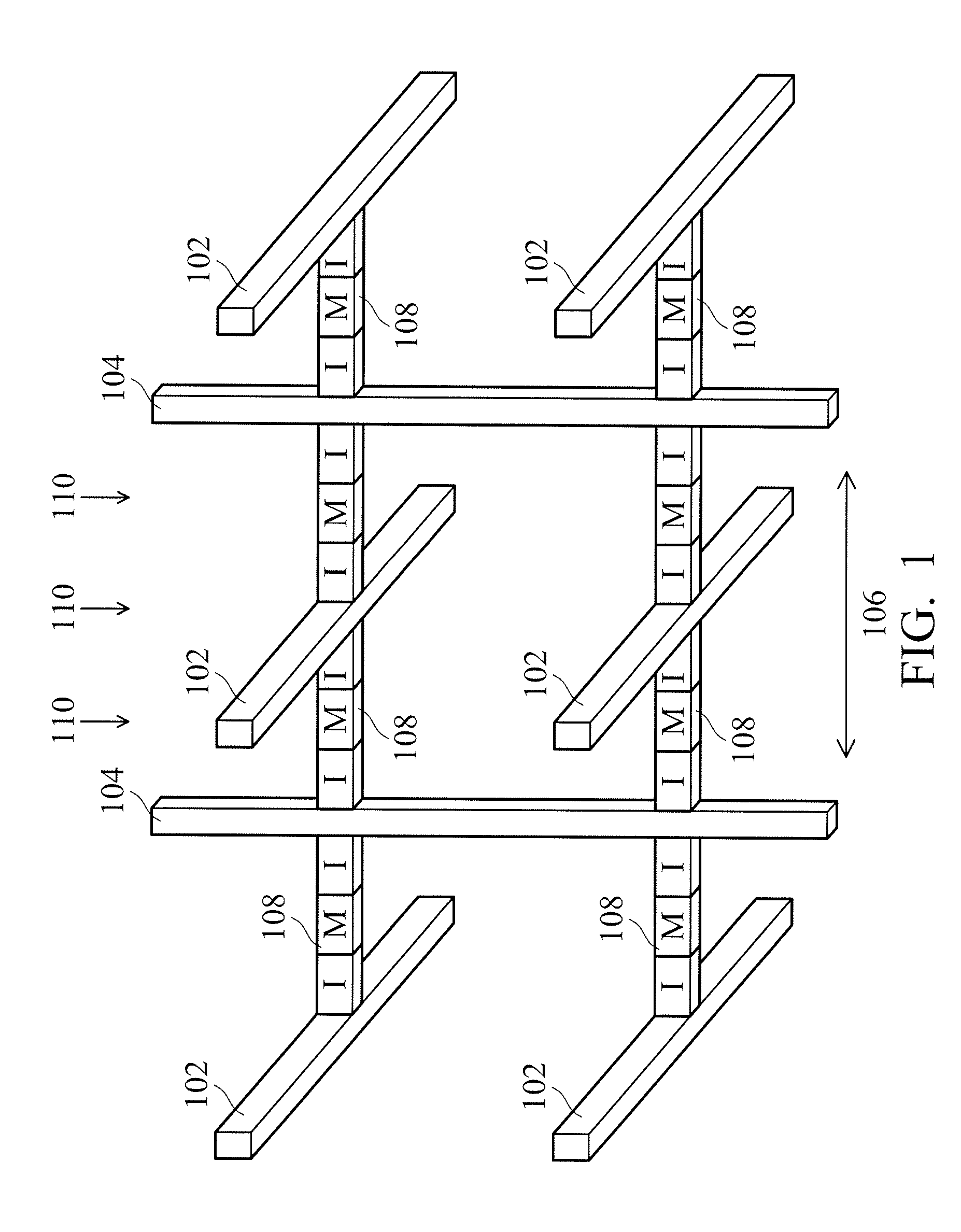

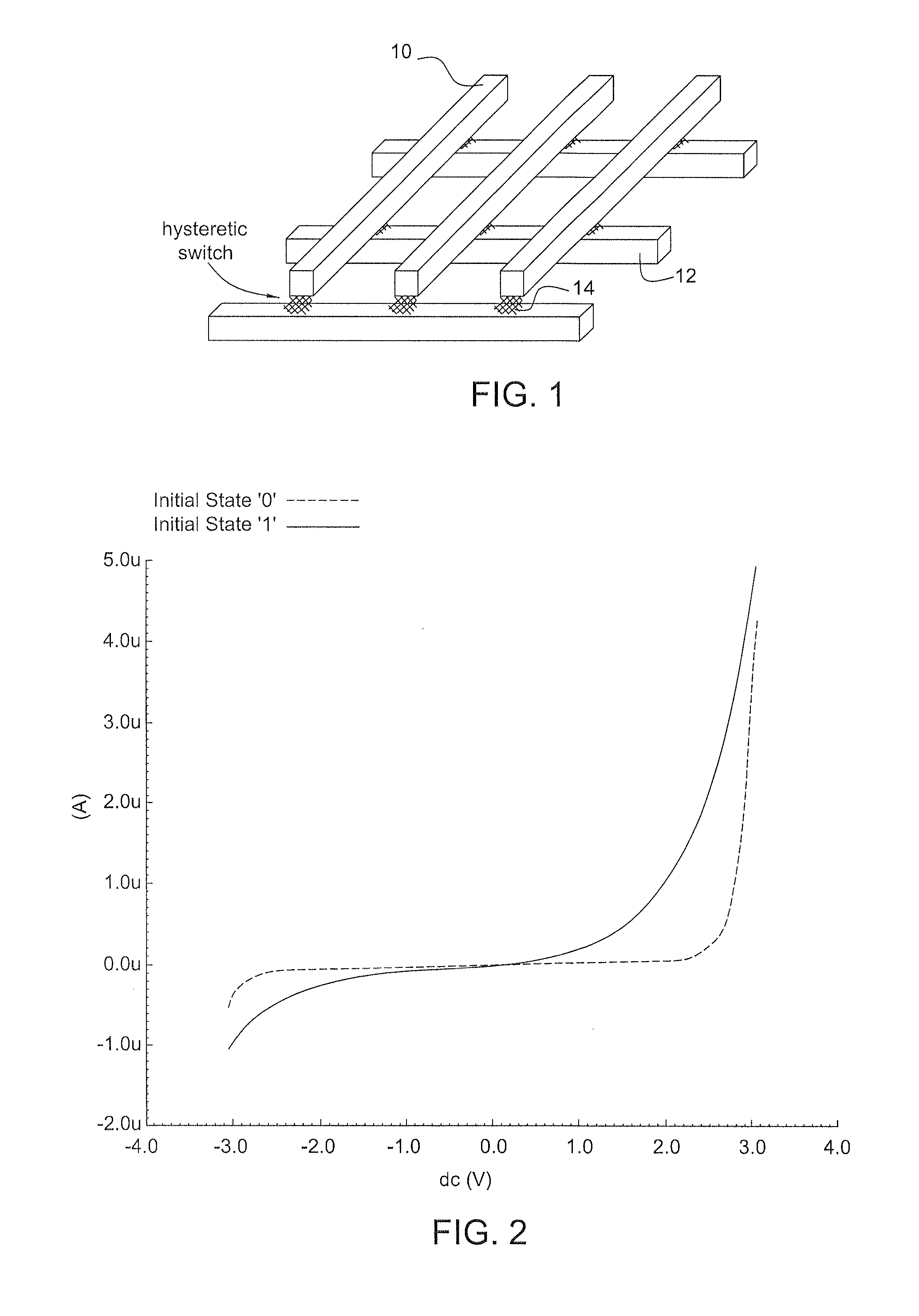

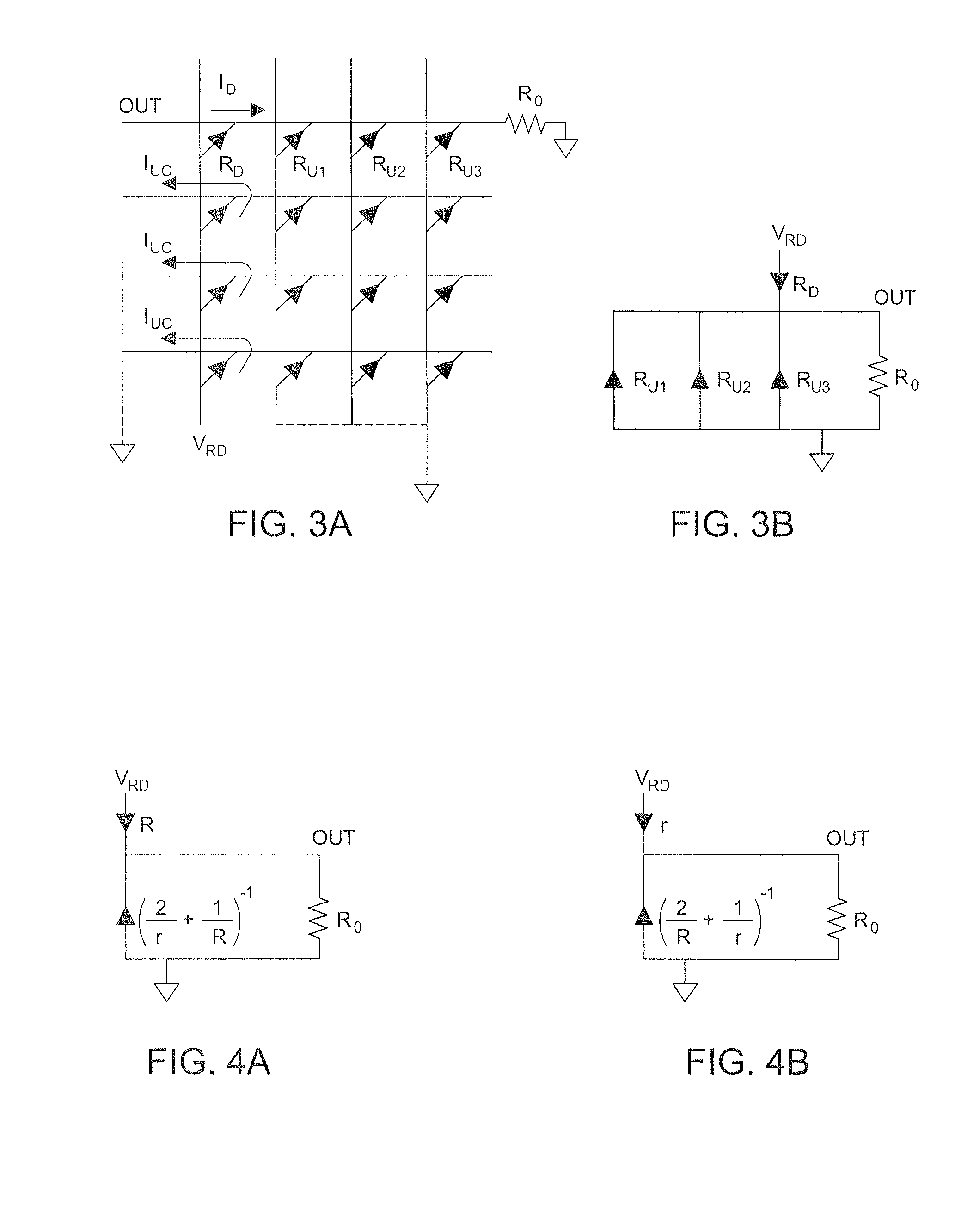

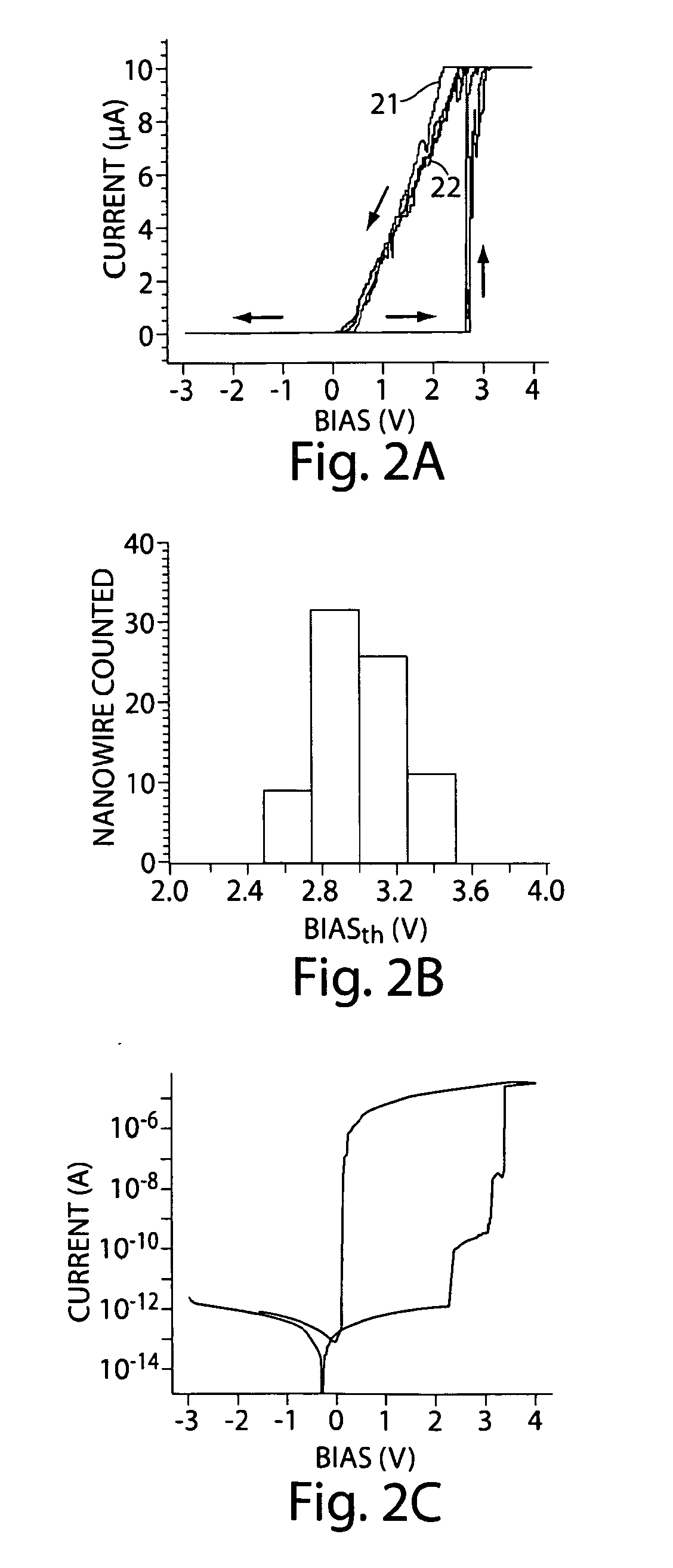

Nanoscale wire-based memory devices

The present invention generally relates to nanotechnology and sub-microelectronic devices that can be used in circuitry, and, in particular, to nanoscale wires and other nanostructures able to encode data. One aspect of the present invention is directed to a device comprising an electrical crossbar array comprising at least two crossed wires at a cross point. In some cases, at least one of the crossed wires is a nanoscale wire, and in certain instances, at least one of the crossed wires is a nanoscale wire comprising a core and at least one shell surrounding the core. For instance, the core may comprise a crystal (e.g., crystalline silicon) and the shell may be at least partially amorphous (e.g., amorphous silicon). In certain embodiments, the cross point may exhibit intrinsic current rectification, or other electrical behaviors, and the cross point can be used as a memory device. For example, in one embodiment, the cross point may exhibit a first conductance at a positive voltage, and the cross point may exhibit a second conductance at a negative voltage. Accordingly, by applying suitable voltages to the cross point, data may be stored at the cross point. Other aspects of the present invention are directed to systems and methods for making or using such devices, kits involving such devices, or the like.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

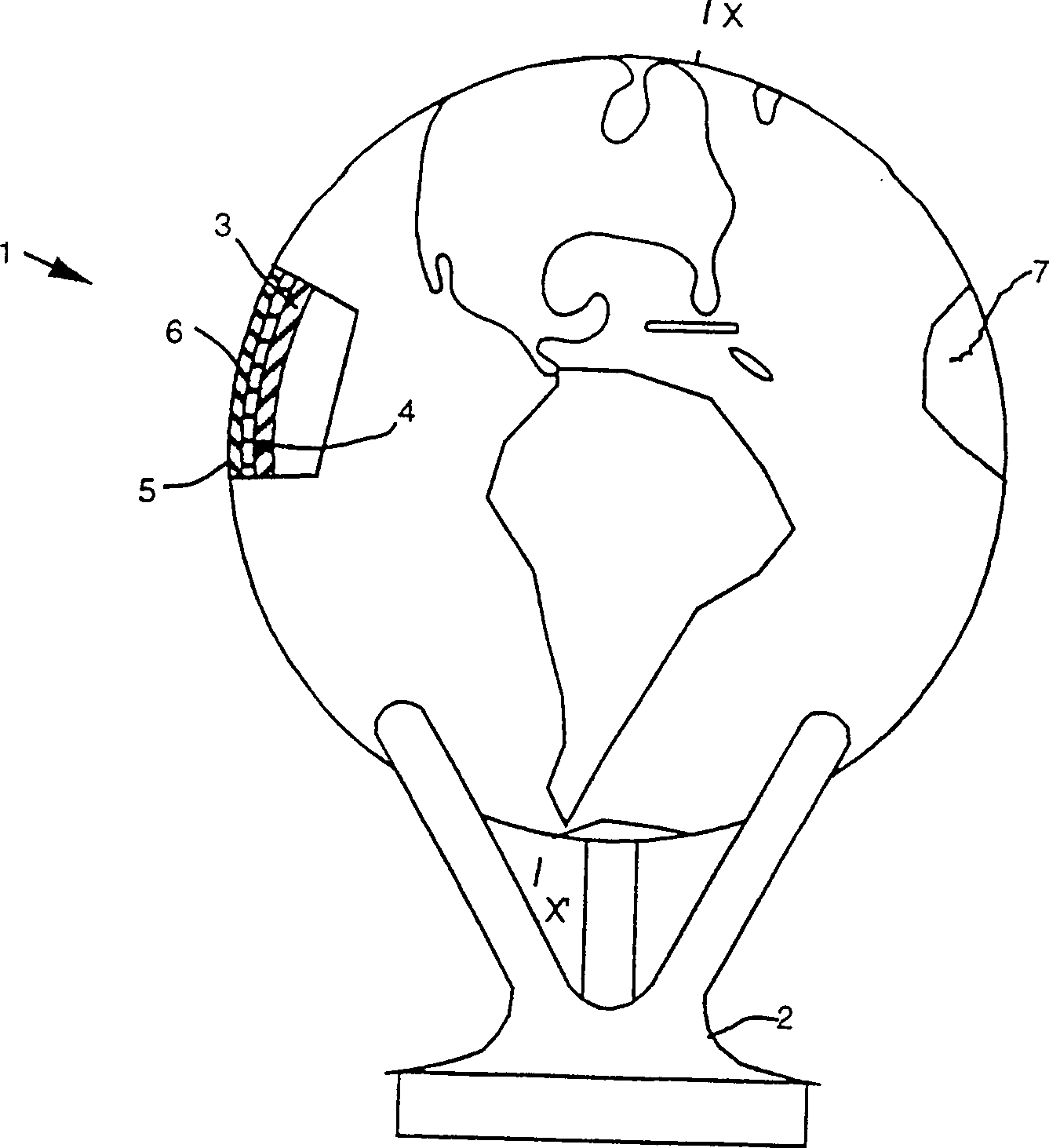

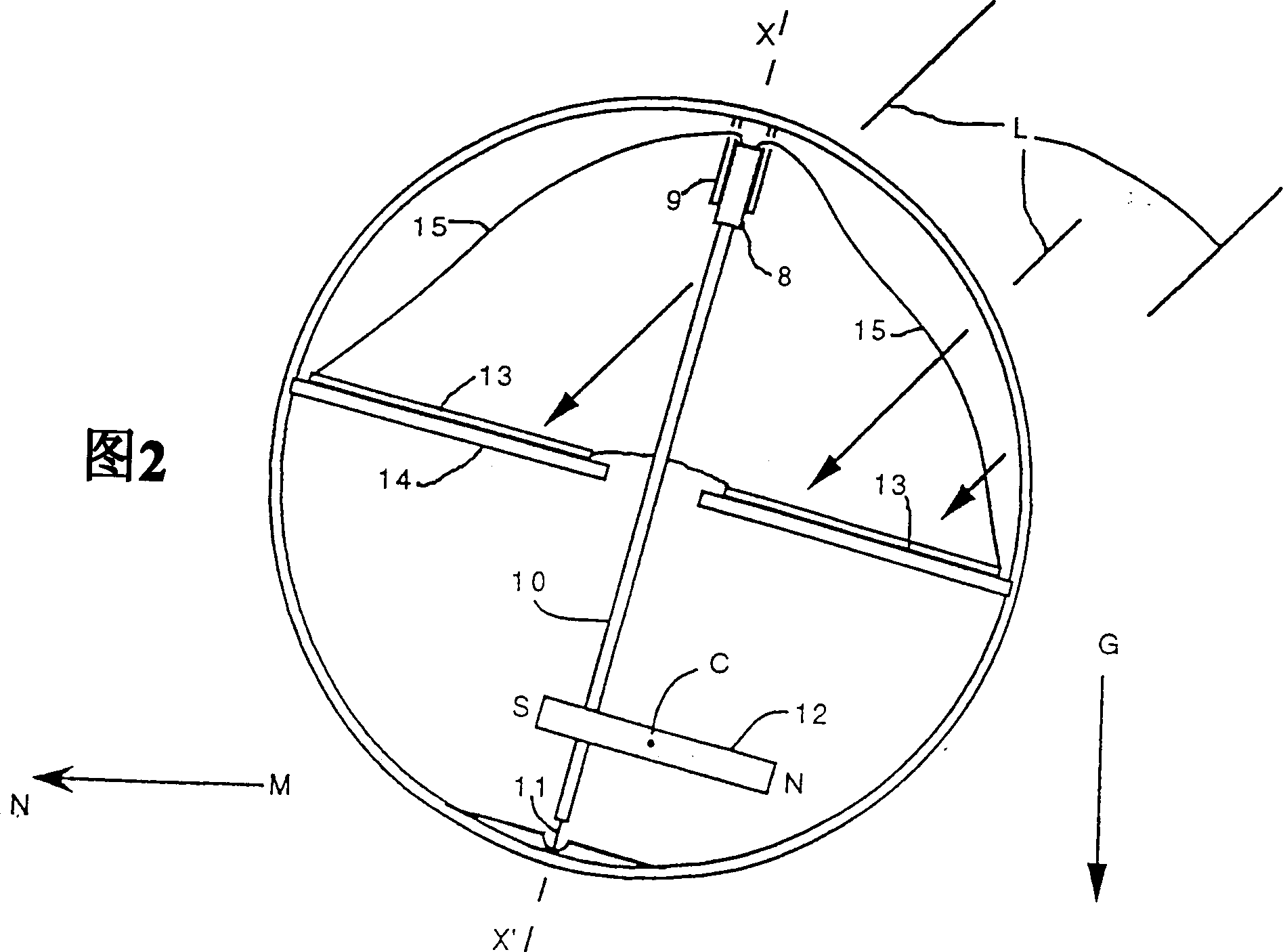

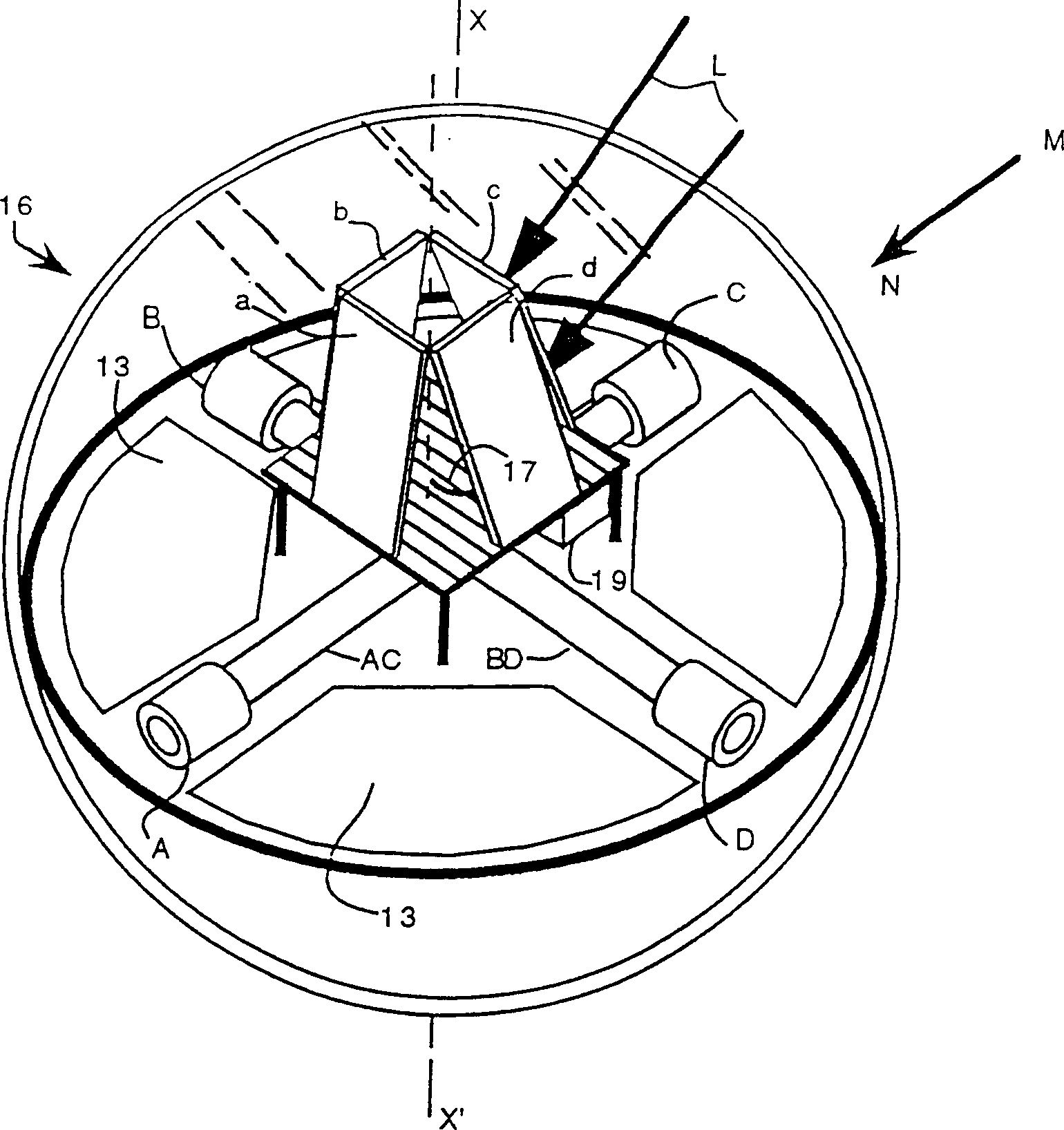

Self rotating display spherical device

An intriguing and educational display structure (2) includes a translucent earth globe body (3) suspended by energy derived from solar cells (14) integral to the globe. The globe is suspended by magnetic forces between magnets within the support assembly (10) which is controlled by a servo system substantially integral to the globe and powered by the solar cells (14). The servo mechanism can be made to launch and land the suspended globe in response to changing levels of illumination. Energy can be stored within the globe to power occasional periods of suspension, even in very low light levels.

Owner:TURTLETECH DESIGN

Memristors with an electrode metal reservoir for dopants

ActiveUS8325507B2Solid-state devicesSemiconductor/solid-state device manufacturingDopantElectrical conductor

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

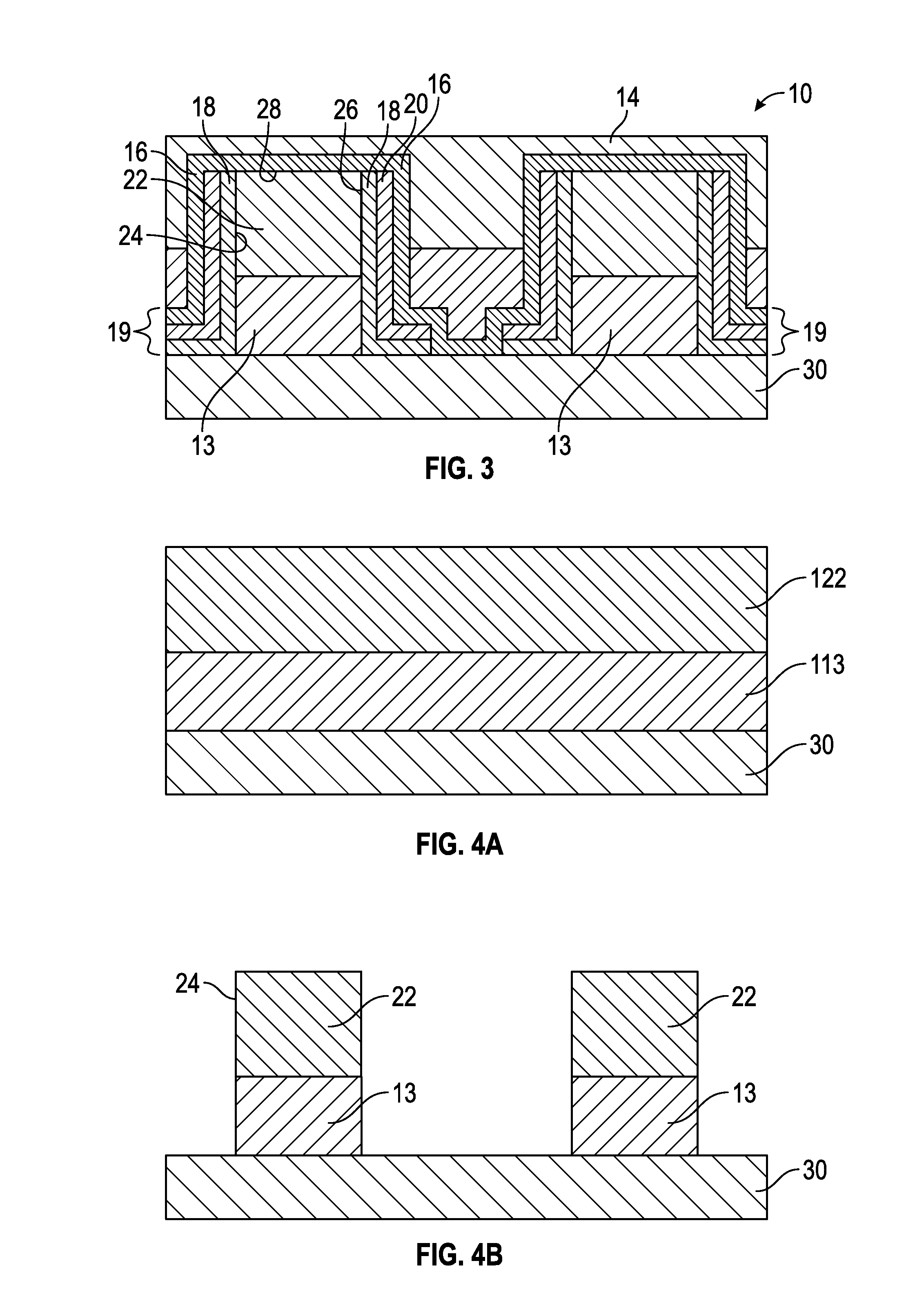

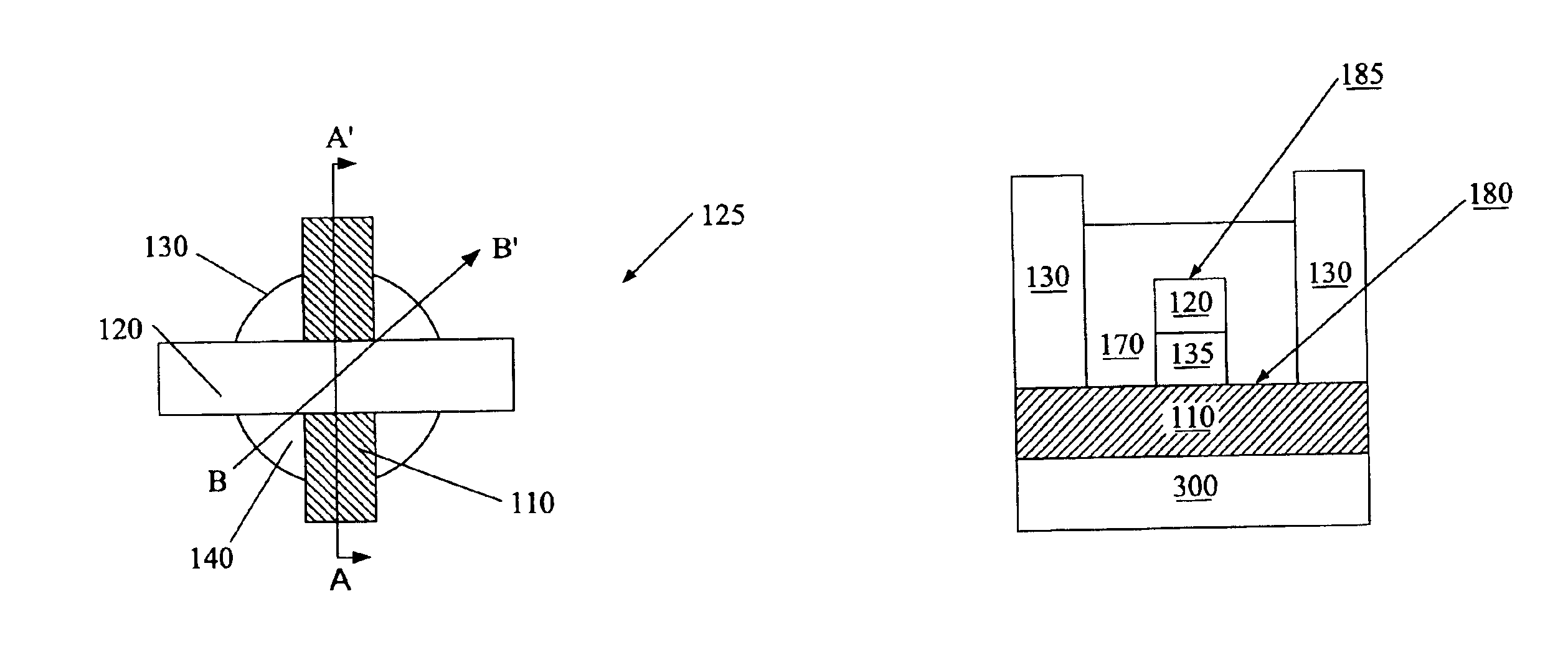

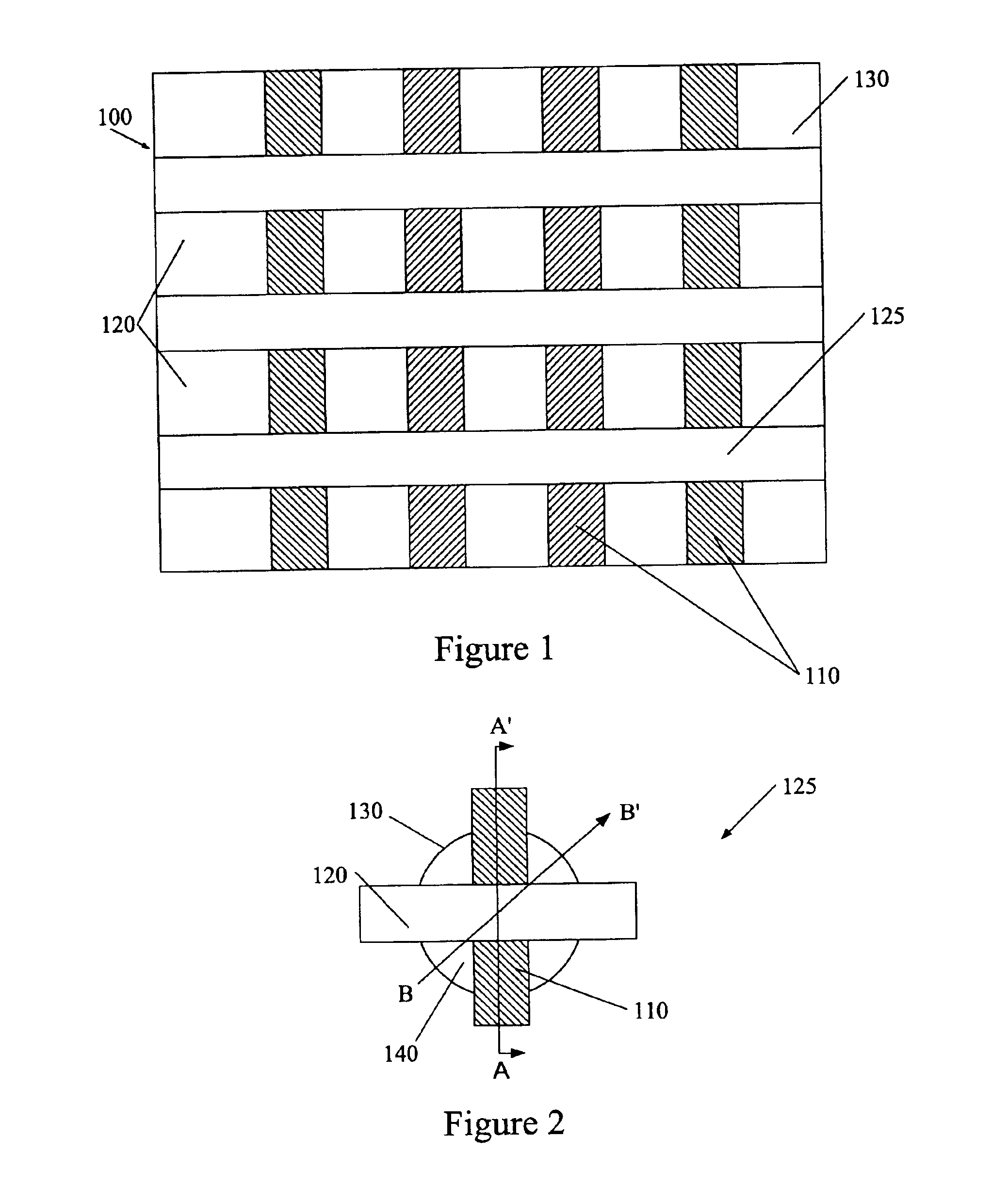

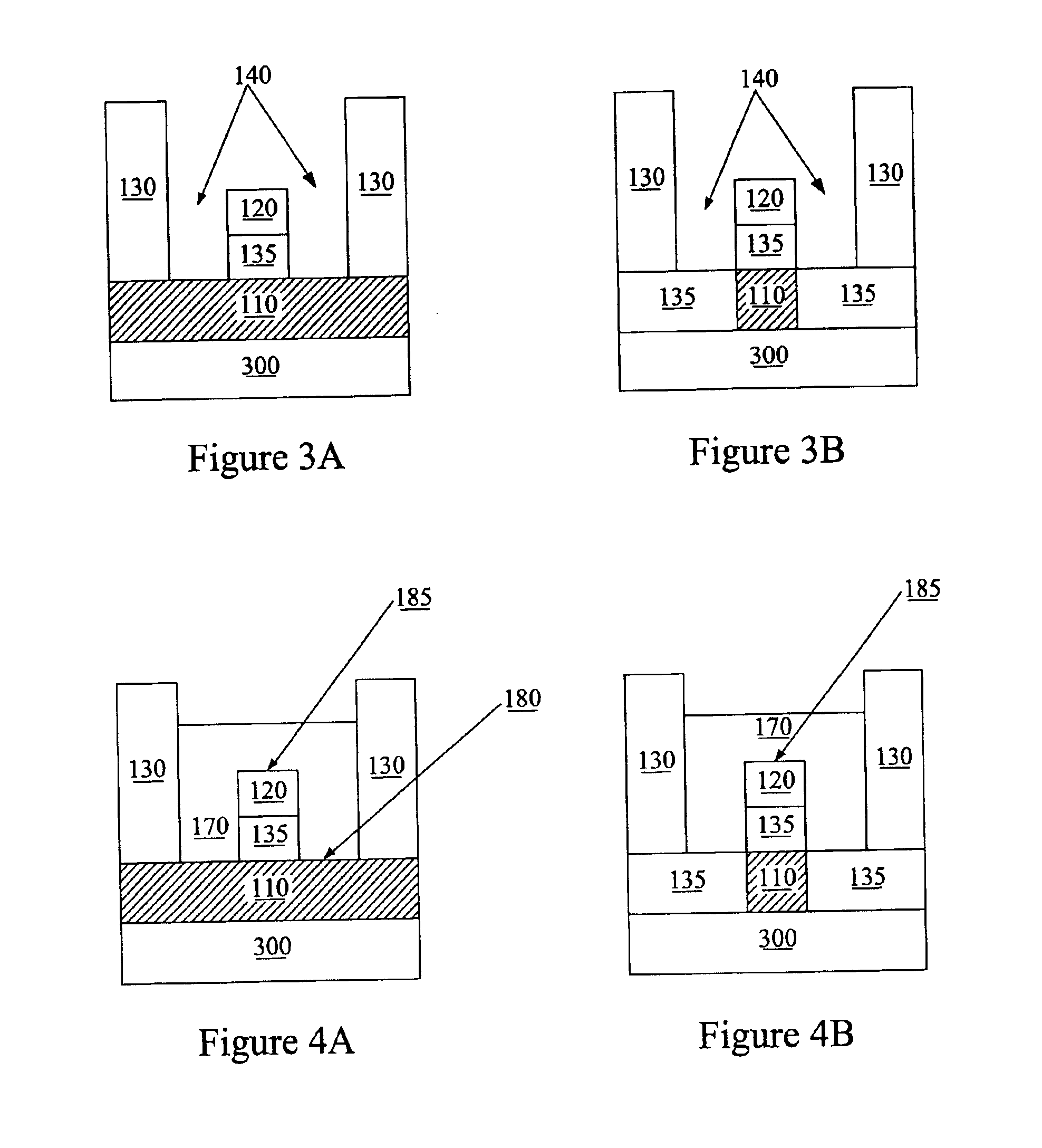

Methods of fabricating crossbar array microelectronic electrochemical cells

InactiveUS6958270B2TransistorPrimary cell to battery groupingElectronic structureElectrical conductor

The present invention provides microelectronic electrochemical structures and related fabrication methods. A composite microelectronic structure is provided that includes first and second conductors dielectrically isolated from one another at a crossing thereof, the crossing surrounded by a dielectric material. A portion of the dielectric material around the crossing of the first and second conductors is removed to form a well that exposes respective outer surfaces of the first and second conductors and a molecule is deposited in the well such that the deposited molecule contacts the exposed outer surfaces of the first and second conductors.

Owner:NORTH CAROLINA STATE UNIV

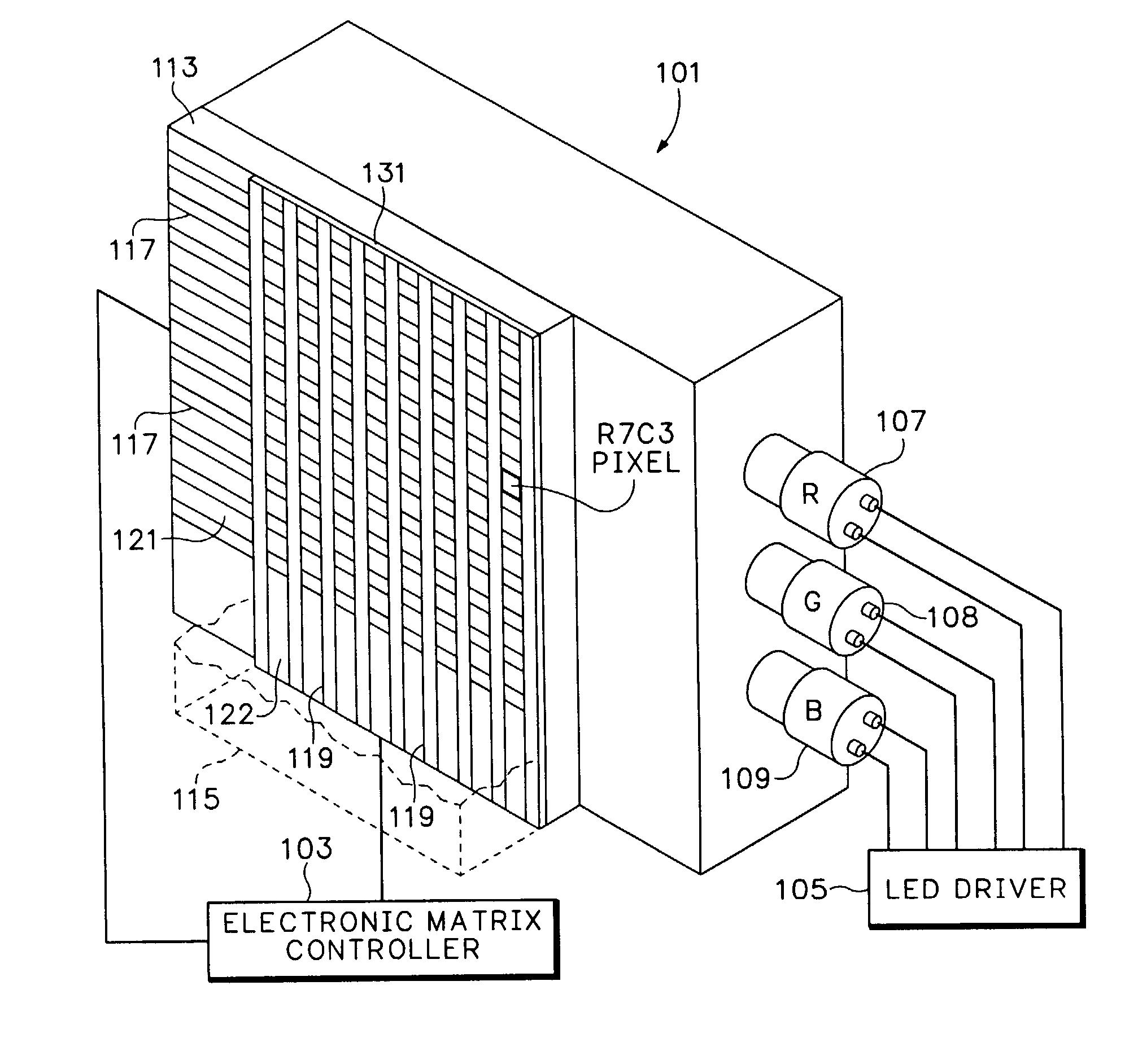

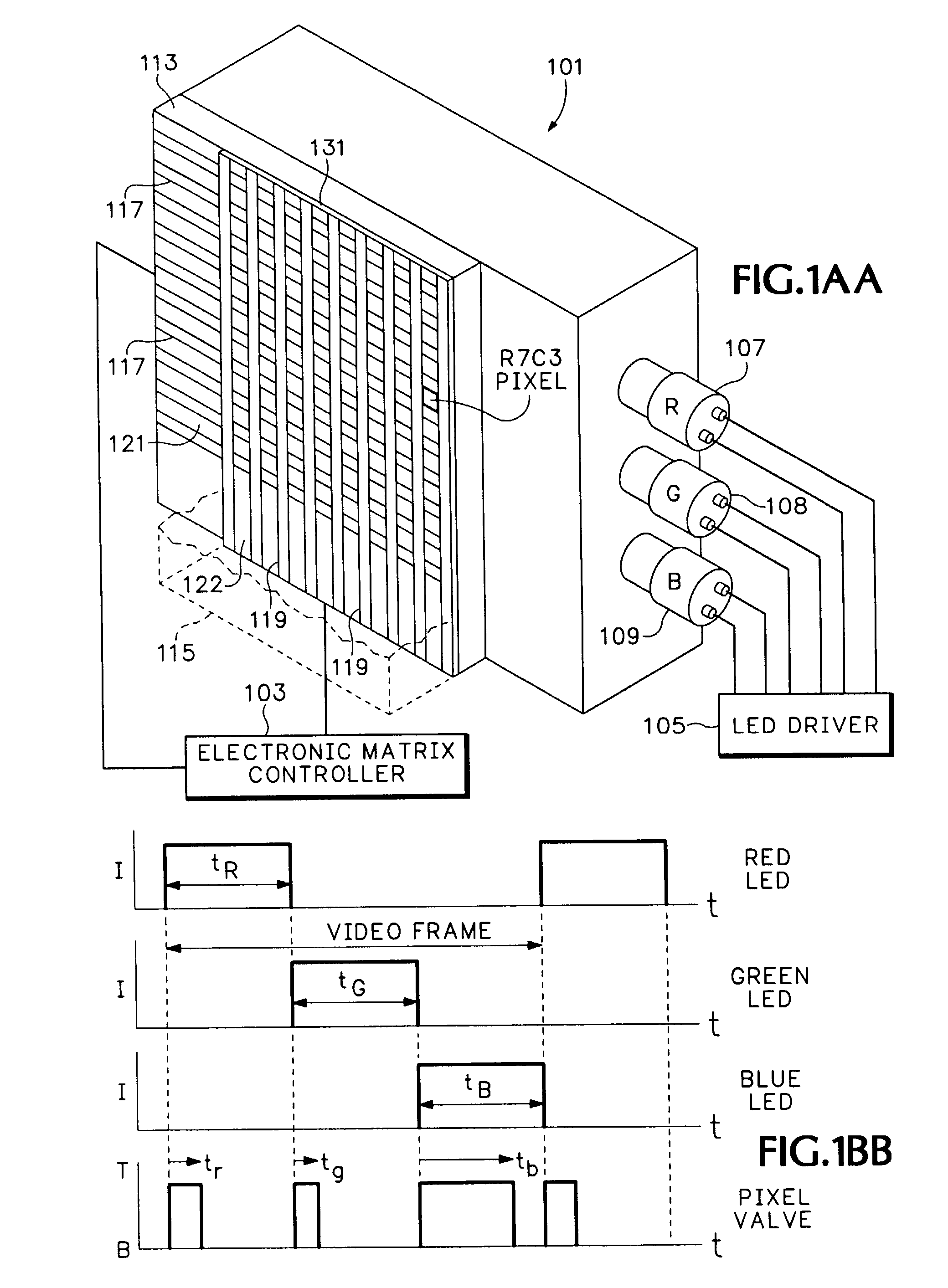

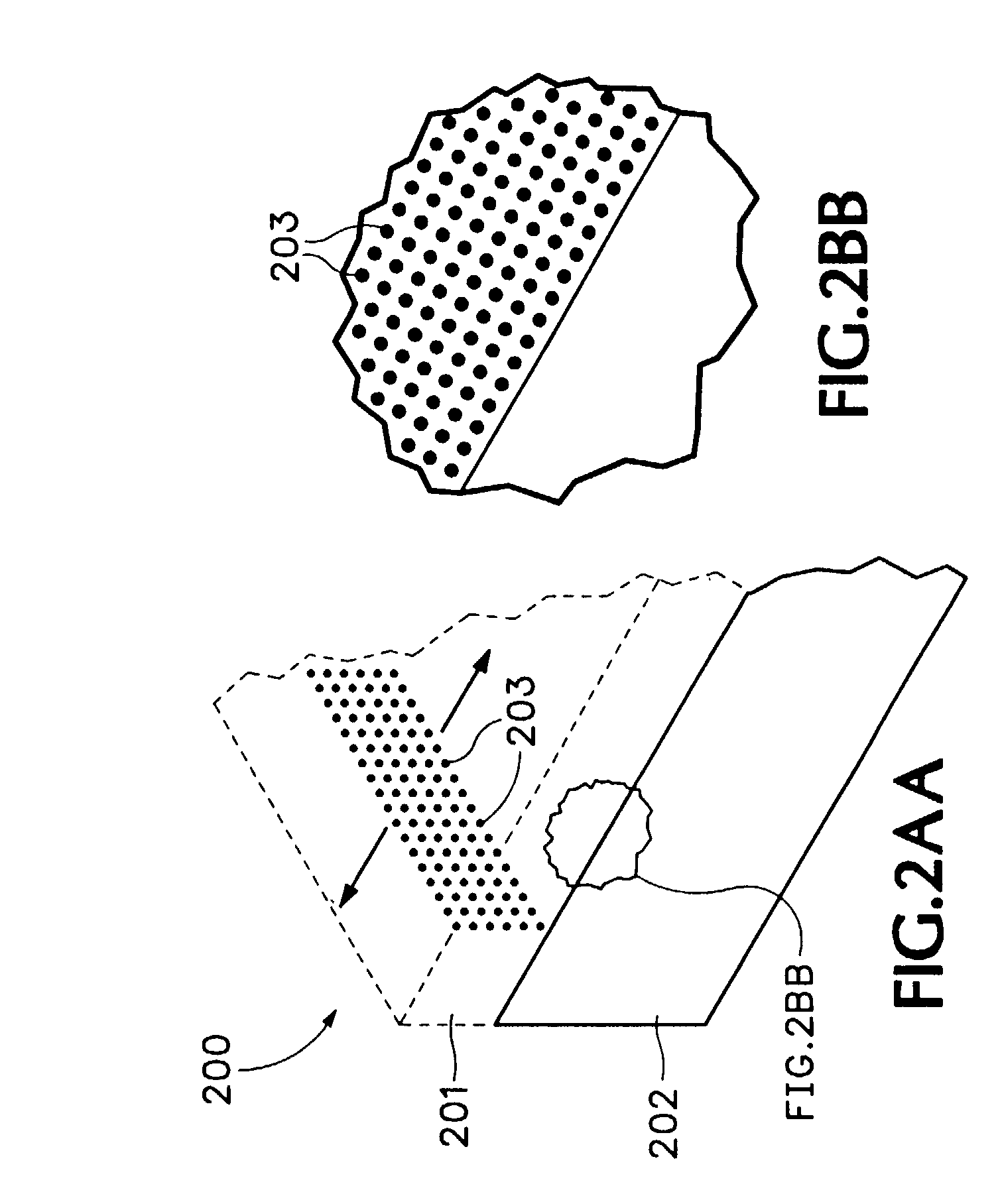

Molecular light valve display having sequenced color illumination

InactiveUS7113165B2Easy to understandStatic indicating devicesCoupling light guidesGamutImage resolution

A molecular light valve controlled color display. The display is formed through a layer of such molecules between a crossbar array of transparent electrodes, the crossbar intersections forming addressable pixels. A rapid sequencing of primary colors is controlled by molecular light valves congruent with display pixels. Native display resolution for a full gamut of colors is maintained for each pixel via a temporally distributed color pixel scheme. Both still and motion images can be displayed. Molecular valves, or switches, transition between two optically distinct states, e.g., transparent and black.

Owner:HEWLETT PACKARD DEV CO LP