Automated design method, device and optimization method applied for neural network processor

A technology of neural network and design method, applied in biological neural network model, electrical digital data processing, CAD circuit design, etc., can solve the problems of large circuit scale, high energy consumption, and long casting cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the object, technical solution, design method and advantages of the present invention clearer, the present invention will be further described in detail through specific embodiments in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to explain the present invention, and It is not intended to limit the invention.

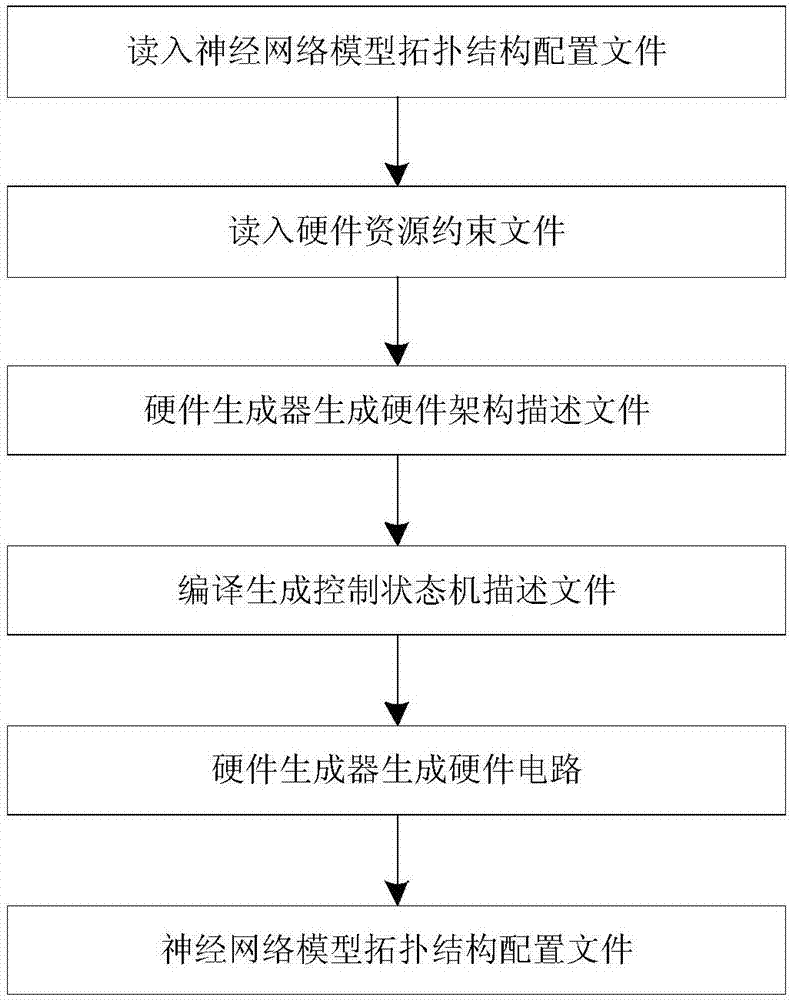

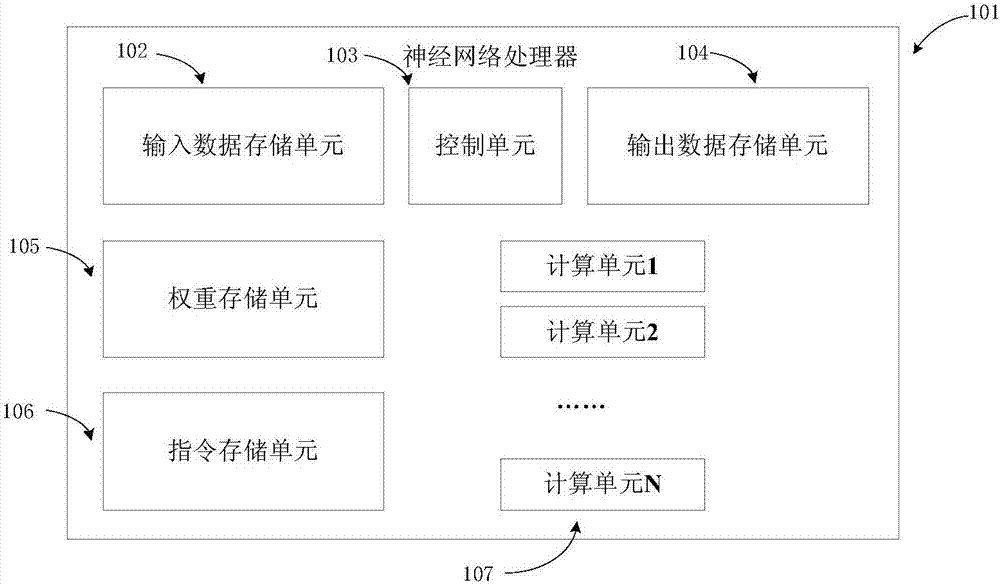

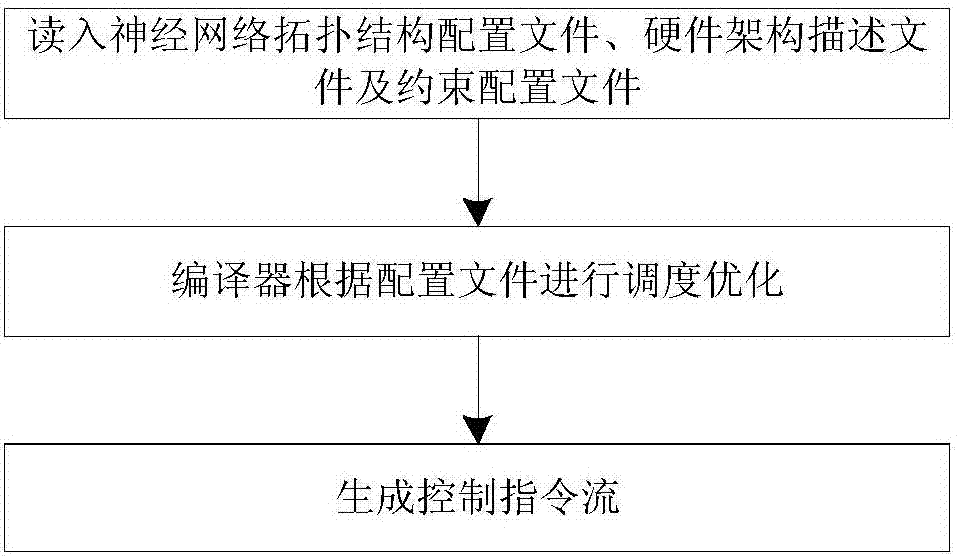

[0040] The present invention aims to provide an automatic design method, device and optimization method suitable for neural network processors. The device includes a hardware generator and a compiler, and the hardware generator can The hardware description language code of the neural network processor is automatically generated, and then the designer uses the existing hardware circuit design method to generate the processor hardware circuit through the hardware description language; the compiler can generate control and data scheduling instructions according to the n...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More