Deep neural network acceleration platform based on FPGA

A technology of deep neural network and neural network, which is applied in the design field of FPGA-based deep neural network acceleration platform, can solve problems such as long development cycle and achieve good performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

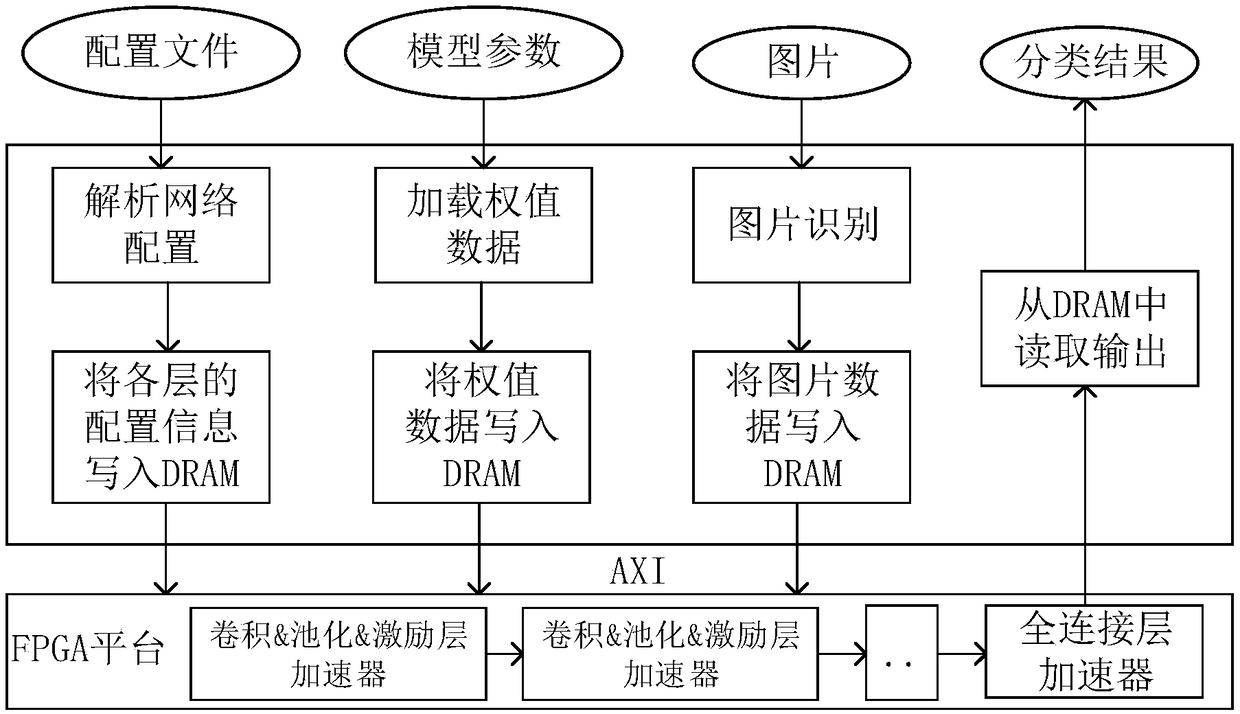

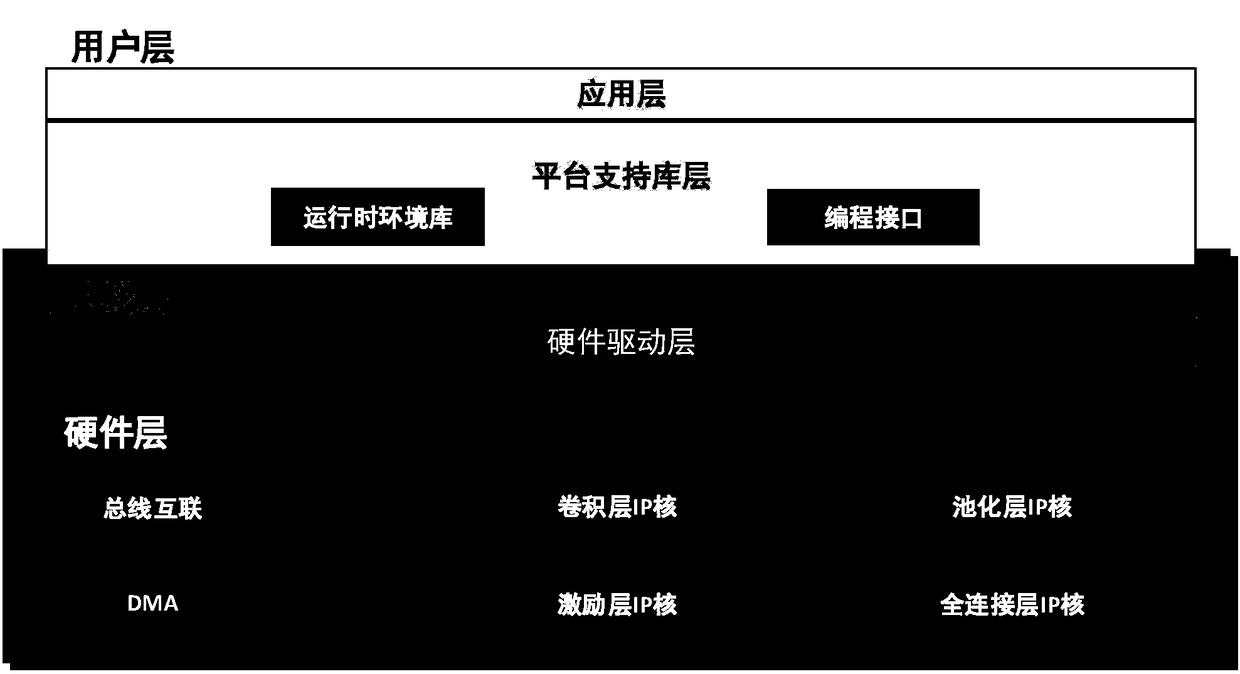

[0051] The deep neural network acceleration platform in the embodiment of the present invention includes a general-purpose processor, a field programmable gate array, and a storage module, wherein the data path between the FPGA and the general-purpose processor can use the PCI-E bus protocol, the AXI bus protocol, and the like. The data path in the drawings of the embodiments of the present invention is illustrated by using the AXI bus protocol as an example, but the present invention is not limited thereto.

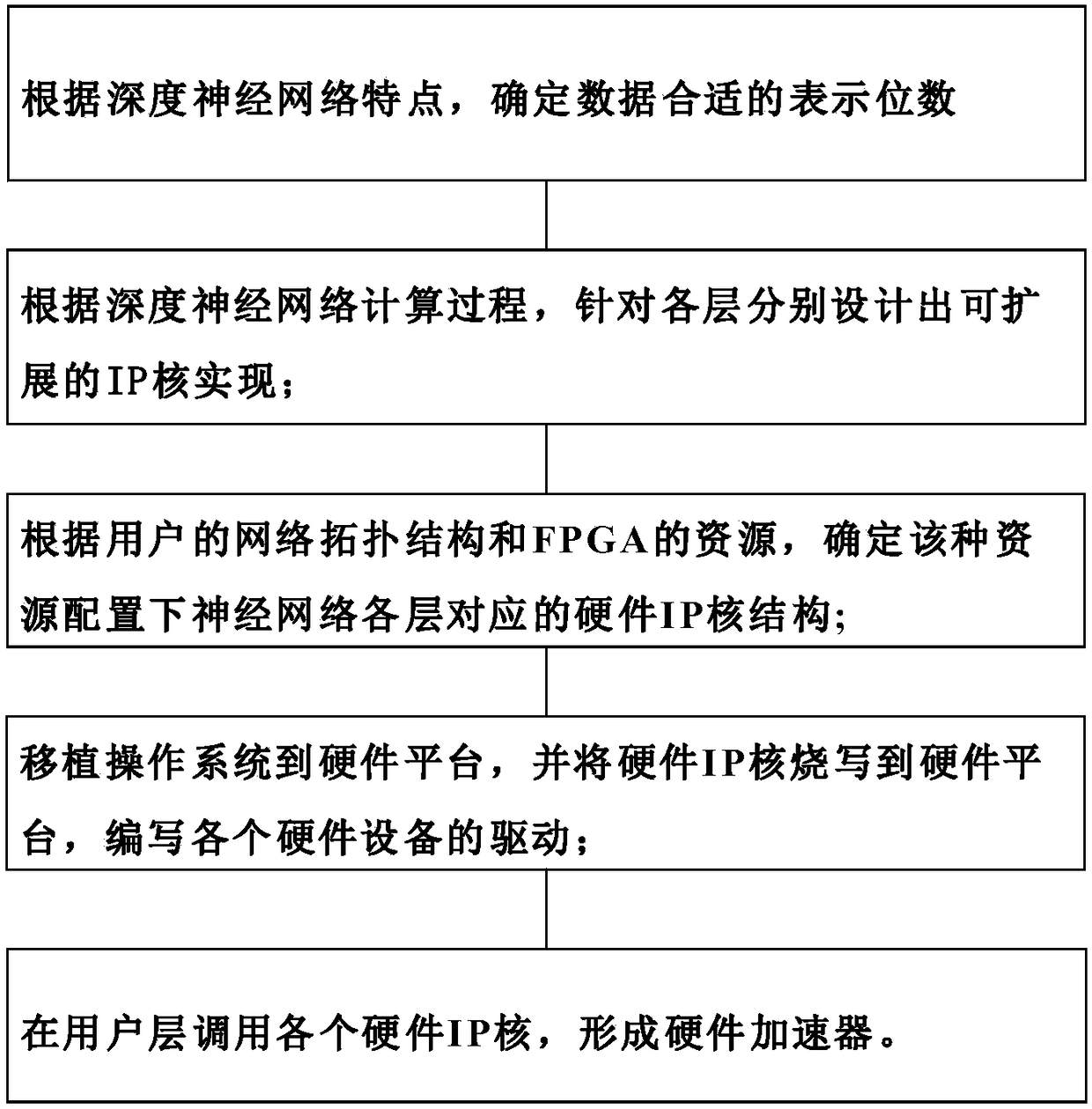

[0052] figure 1 It is a design flowchart of the acceleration system platform of the embodiment of the present invention, and the steps included are as follows:

[0053] The general processor is used to analyze the neural network configuration information and weight data, and write the neural network configuration information and weight data into DRAM;

[0054] FPGA reads configuration information from DRAM to generate FPGA accelerator;

[0055] The general processor re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More