Circuit and method for resisting SEU of SRAM FPGA device

A circuit and device technology, which is applied in the field of two-dimensional CRC check circuit, enables dynamic reconfigurable hardware to have anti-SEU function in the field of circuit structure, can solve the waste of time and power consumption, cannot check data per frame, and takes a long time to check, etc. problems, to reduce the time and power consumption of reconstruction, to extend the mean time between failures, and to achieve the effect of easy implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

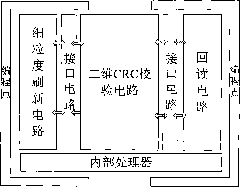

[0029] The anti-SEU circuit proposed by the present invention is valuable in the application of preventing the single event upset effect from causing damage to the hardware based on the SRAM structure, and should cooperate with the overall process to play a role.

[0030] Utilize the anti-SEU circuit that the present invention proposes to implement the concrete steps of anti-SEU error function as Figure 7 As shown, the specific description is as follows:

[0031] (1) Fine-grained readback. The programming point information is output to the read-back register through the read-back amplifier, and the output of the frame address decoder and the intra-frame address decoder is controlled by the instruction stored in the FAR register, and the use of the tri-state Buffer of the programming point that needs to be read back The enabling terminal of the tri-state Buffer corresponding to the programming point that does not need to be read back is set to a low level.

[0032] (2) Two-d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More