FPGA (Field Programmable Gate Array)-based general matrix fixed-point multiplier and calculation method thereof

A fixed-point multiplier and matrix technology, applied in the field of high-performance computing, to achieve the effect of improving computing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The present invention will be further described below in conjunction with the embodiments and accompanying drawings, but the protection scope of the present invention should not be limited thereby.

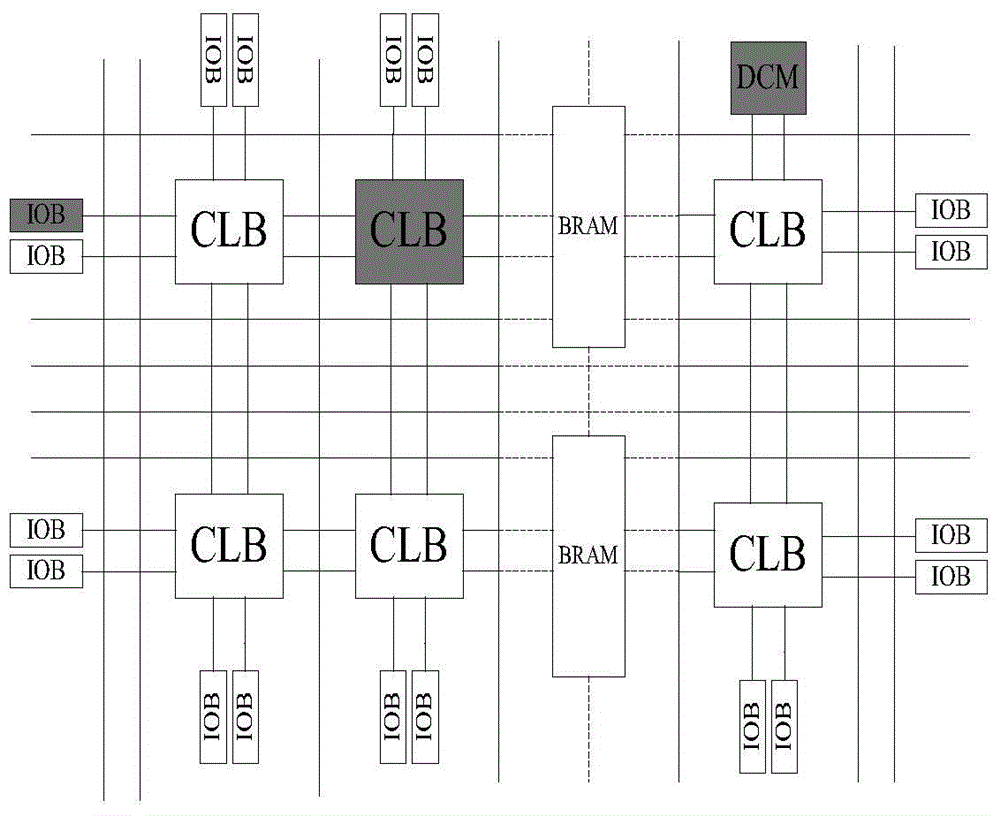

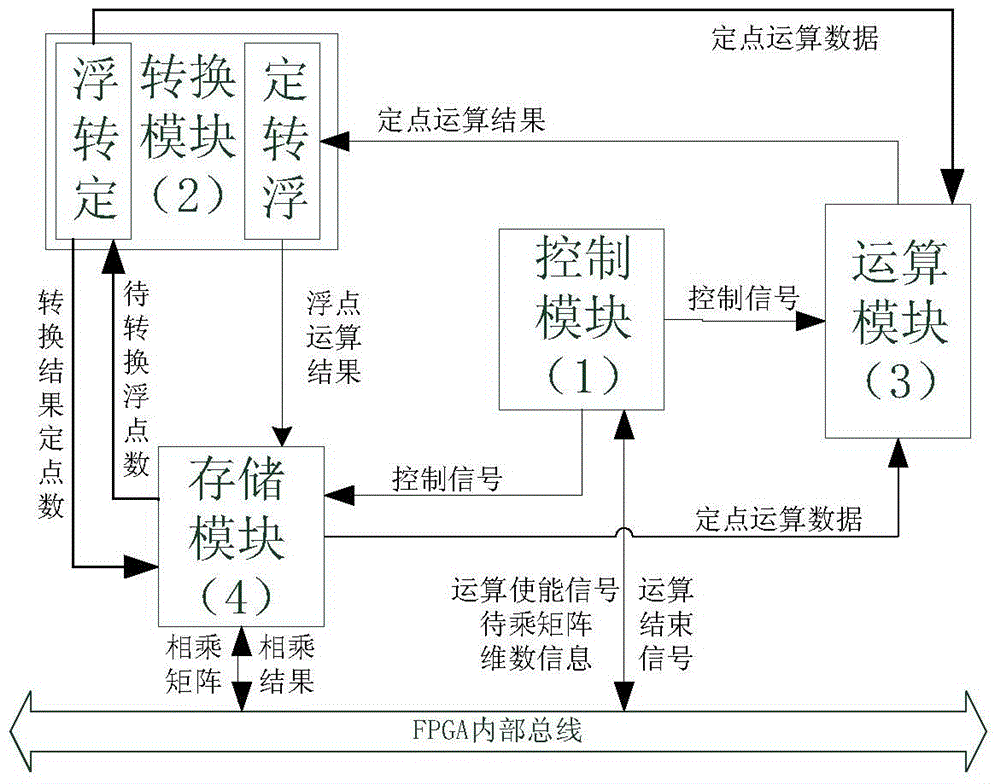

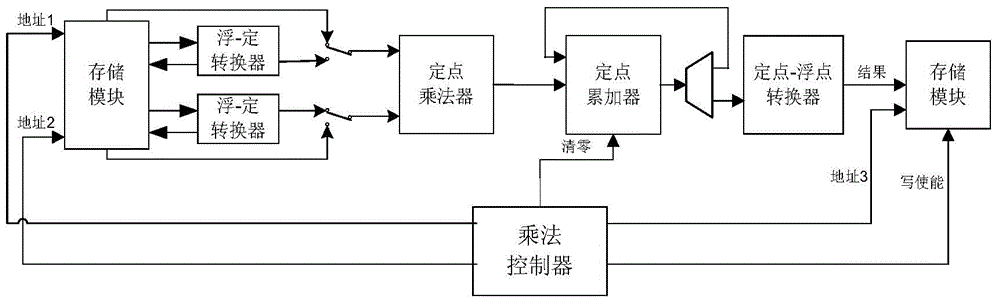

[0052] The general-purpose matrix fixed-point multiplier based on FPGA of the present invention is mainly composed of four parts: control module, conversion module, operation module and storage module, and its overall structure and internal signal flow are as follows: figure 2 shown. The general-purpose matrix fixed-point multiplier is realized by using the Virtex IV (XC4VFX12-10-ffg668) chip of Xilinx. The specific implementation process of each module is as follows:

[0053] 1. Control module

[0054] In this embodiment, the control module is composed of digital logic circuits such as LUTs (look-up tables) and FFs (flip-flops) inside the XC4VFX12-10-ffg668 chip. The circuit controls the orderly progress of the entire matrix multiplication process, and generates various...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More