Patents

Literature

89 results about "Matrix multiplier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

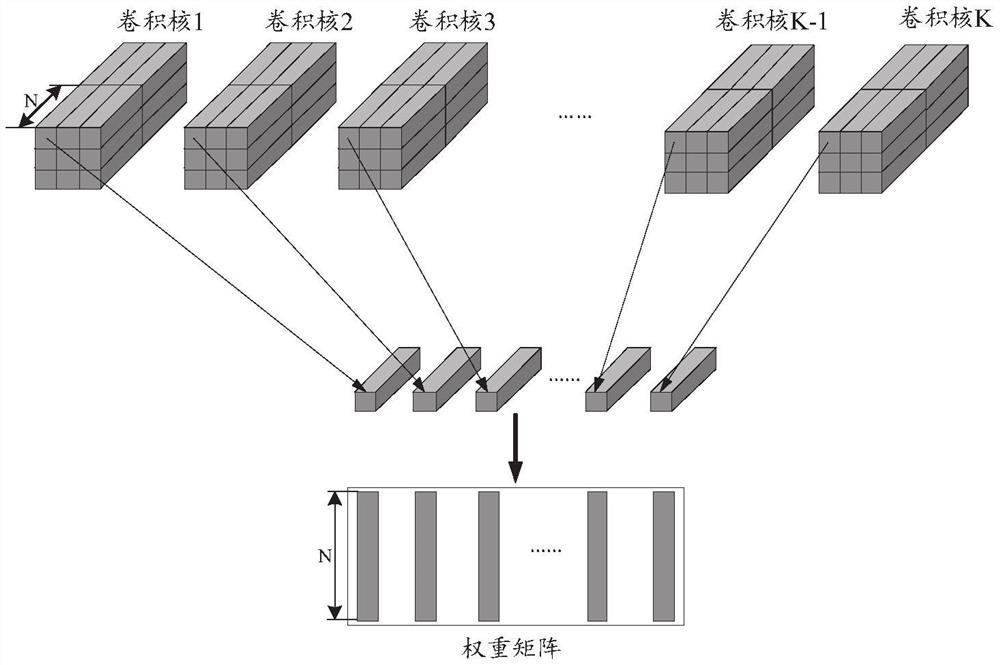

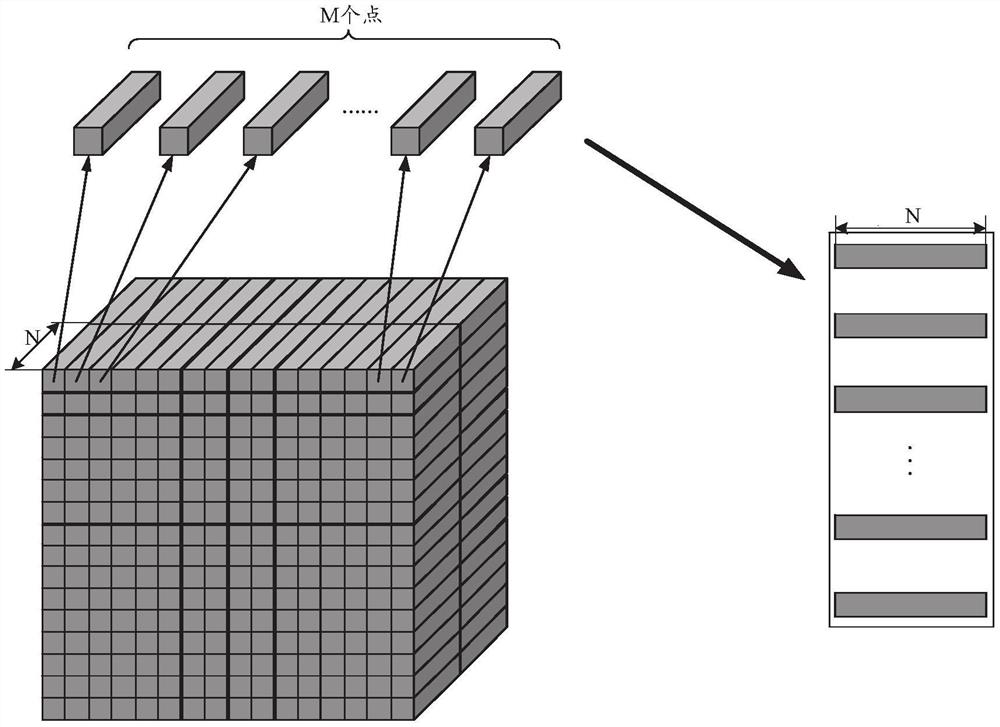

Method for accelerating convolution neutral network hardware and AXI bus IP core thereof

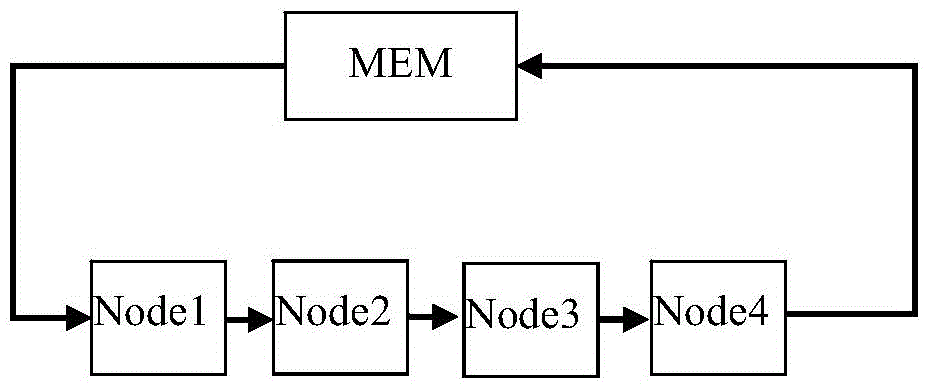

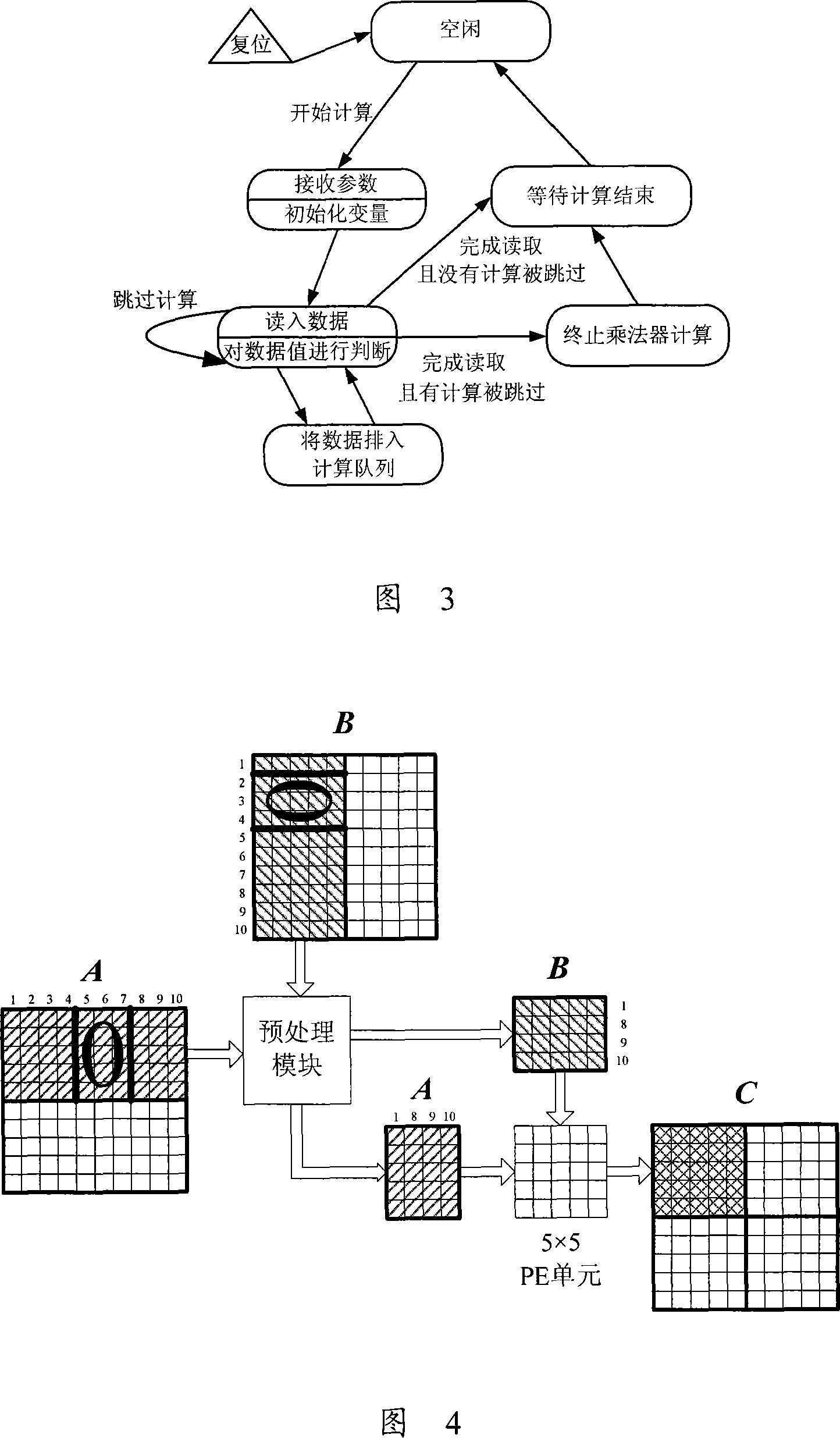

ActiveCN104915322AImprove adaptabilityIncrease flexibilityResource allocationMultiple digital computer combinationsChain structureMatrix multiplier

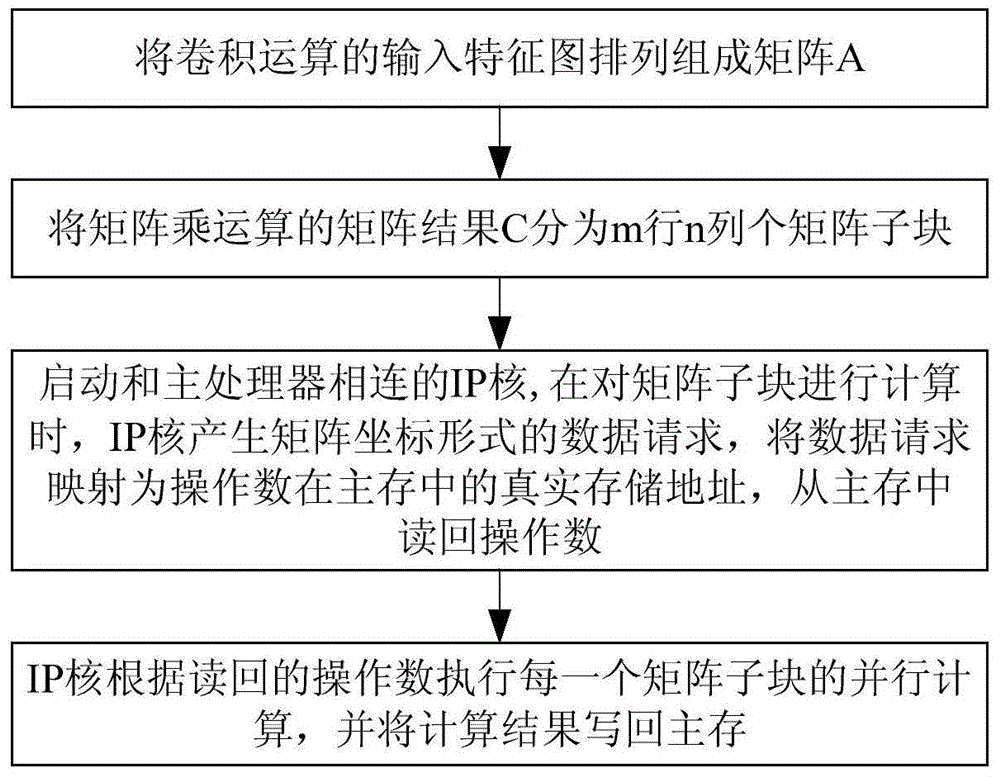

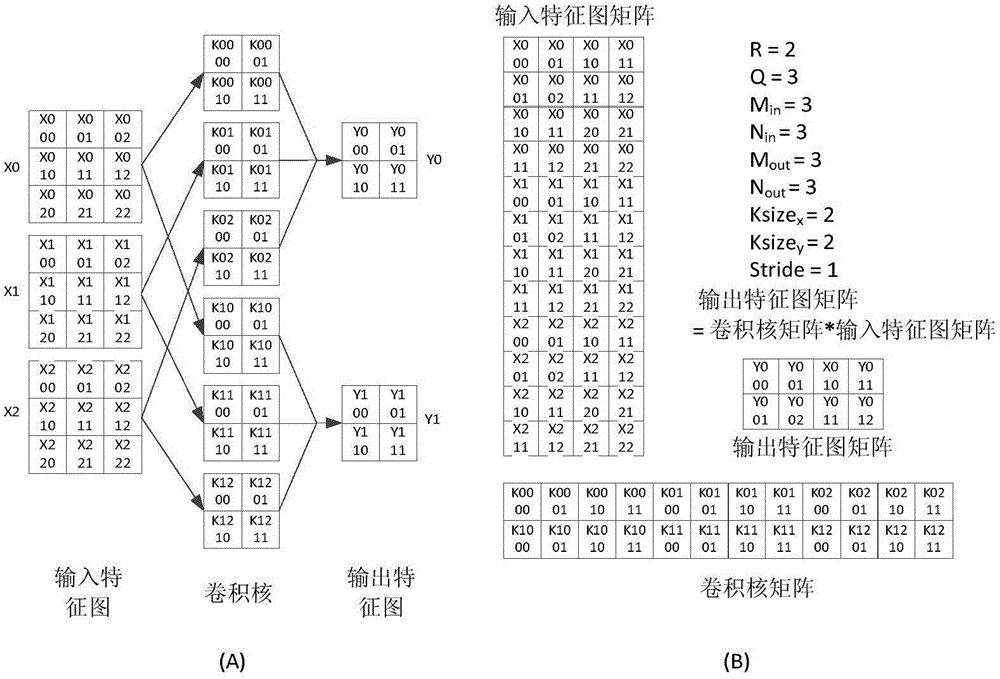

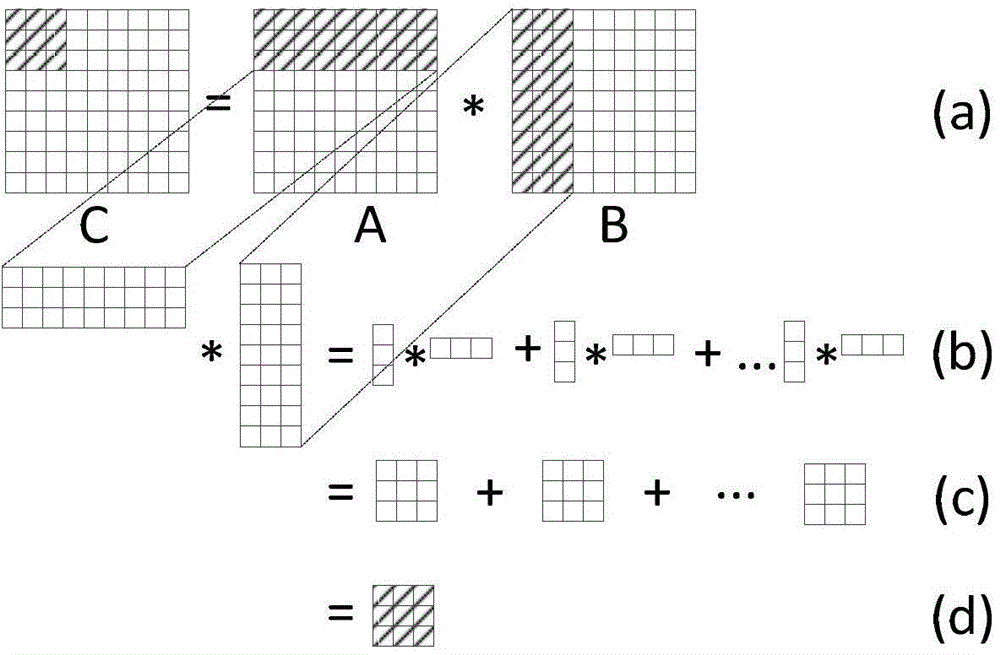

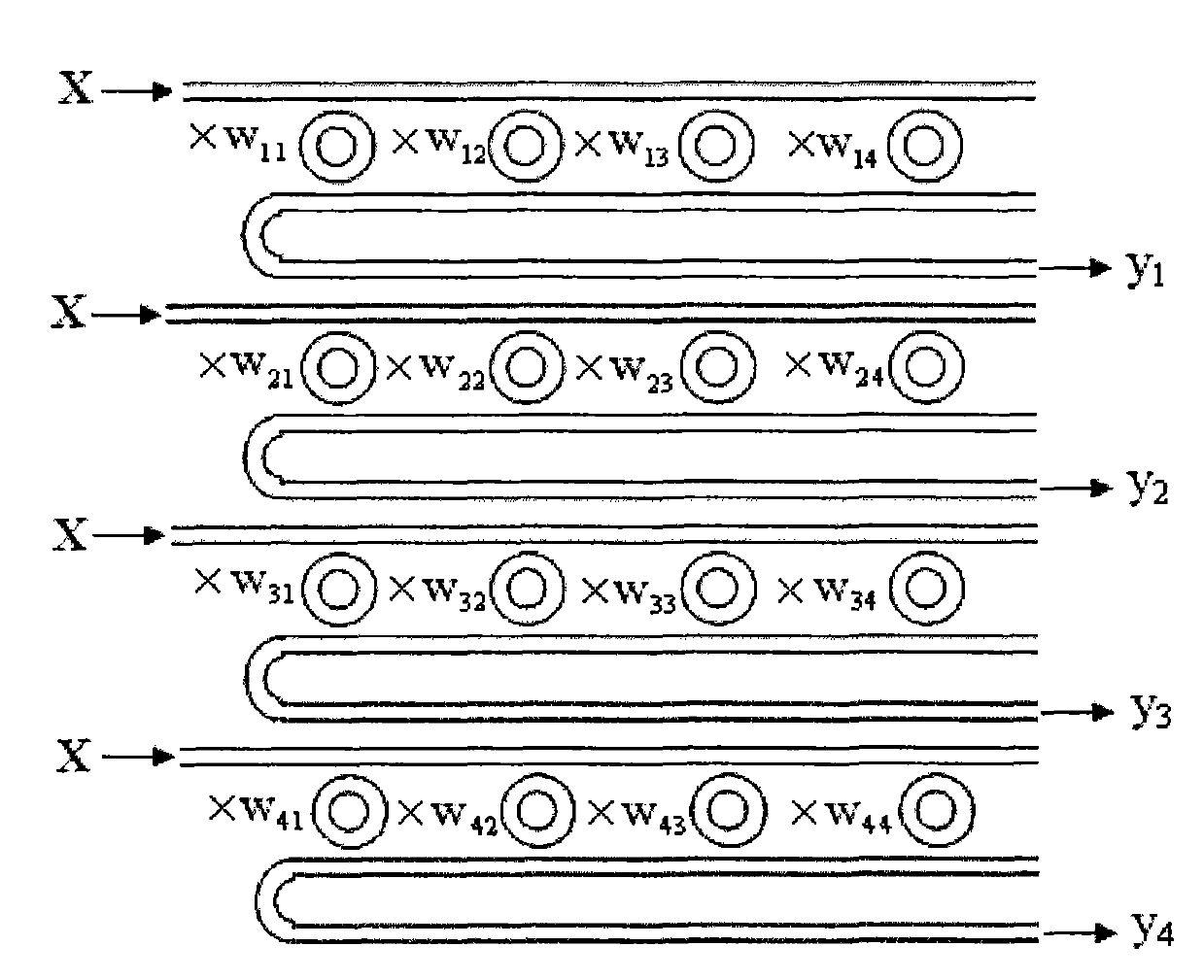

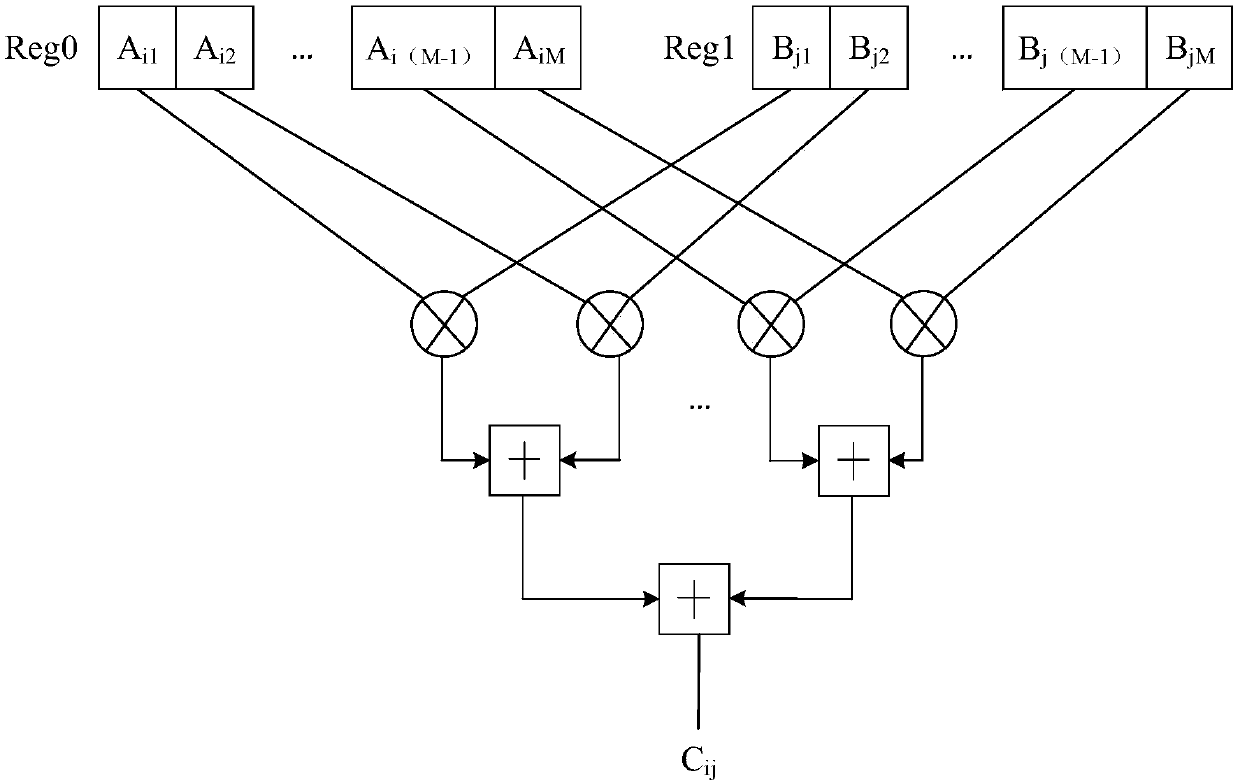

The invention discloses a method for accelerating convolution neutral network hardware and an AXI bus IP core thereof. The method comprises the first step of performing operation and converting a convolution layer into matrix multiplication of a matrix A with m lines and K columns and a matrix B with K lines and n columns; the second step of dividing the matrix result into matrix subblocks with m lines and n columns; the third step of starting a matrix multiplier to prefetch the operation number of the matrix subblocks; and the fourth step of causing the matrix multiplier to execute the calculation of the matrix subblocks and writing the result back to a main memory. The IP core comprises an AXI bus interface module, a prefetching unit, a flow mapper and a matrix multiplier. The matrix multiplier comprises a chain type DMA and a processing unit array, the processing unit array is composed of a plurality of processing units through chain structure arrangement, and the processing unit of a chain head is connected with the chain type DMA. The method can support various convolution neutral network structures and has the advantages of high calculation efficiency and performance, less requirements for on-chip storage resources and off-chip storage bandwidth, small in communication overhead, convenience in unit component upgrading and improvement and good universality.

Owner:NAT UNIV OF DEFENSE TECH

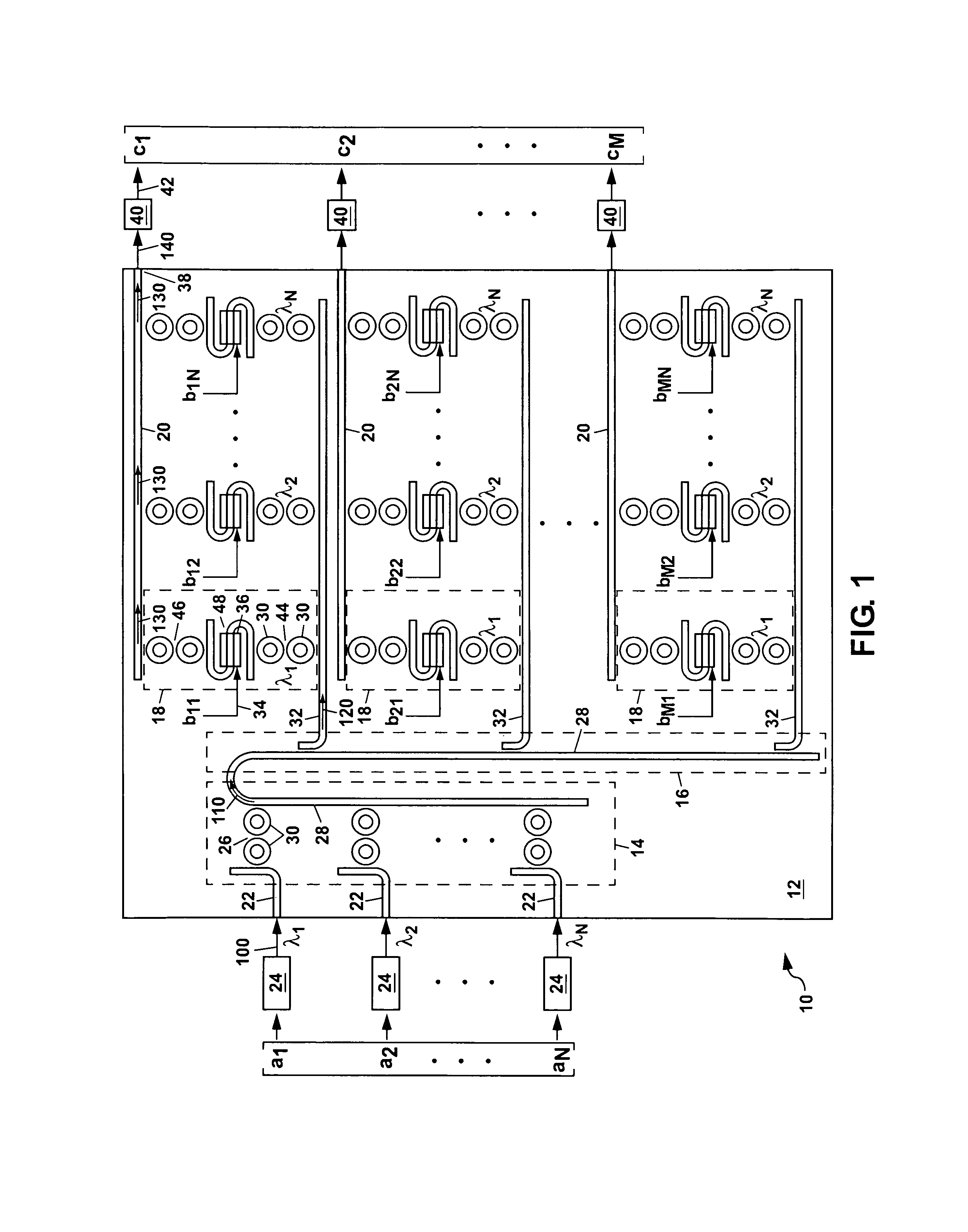

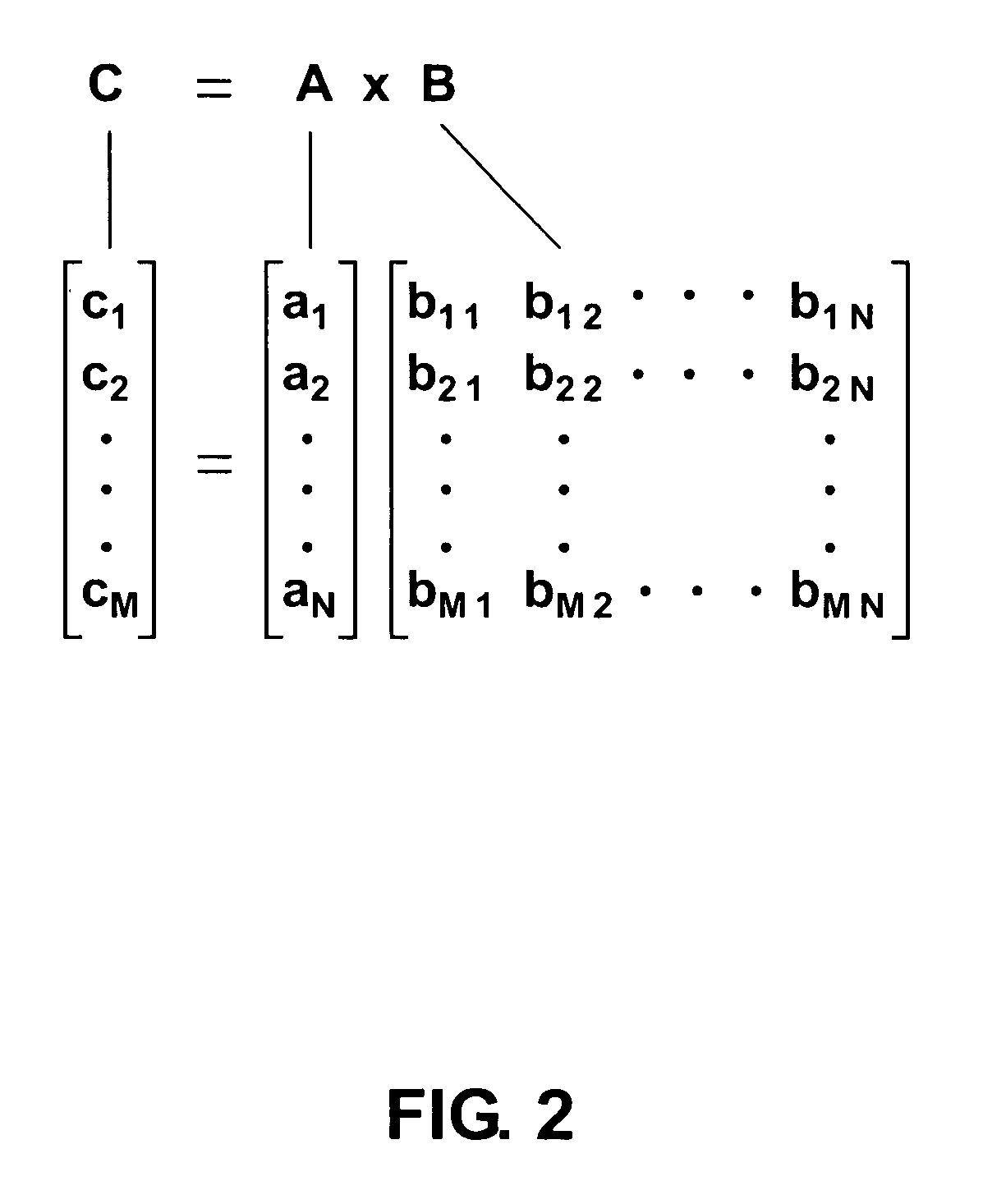

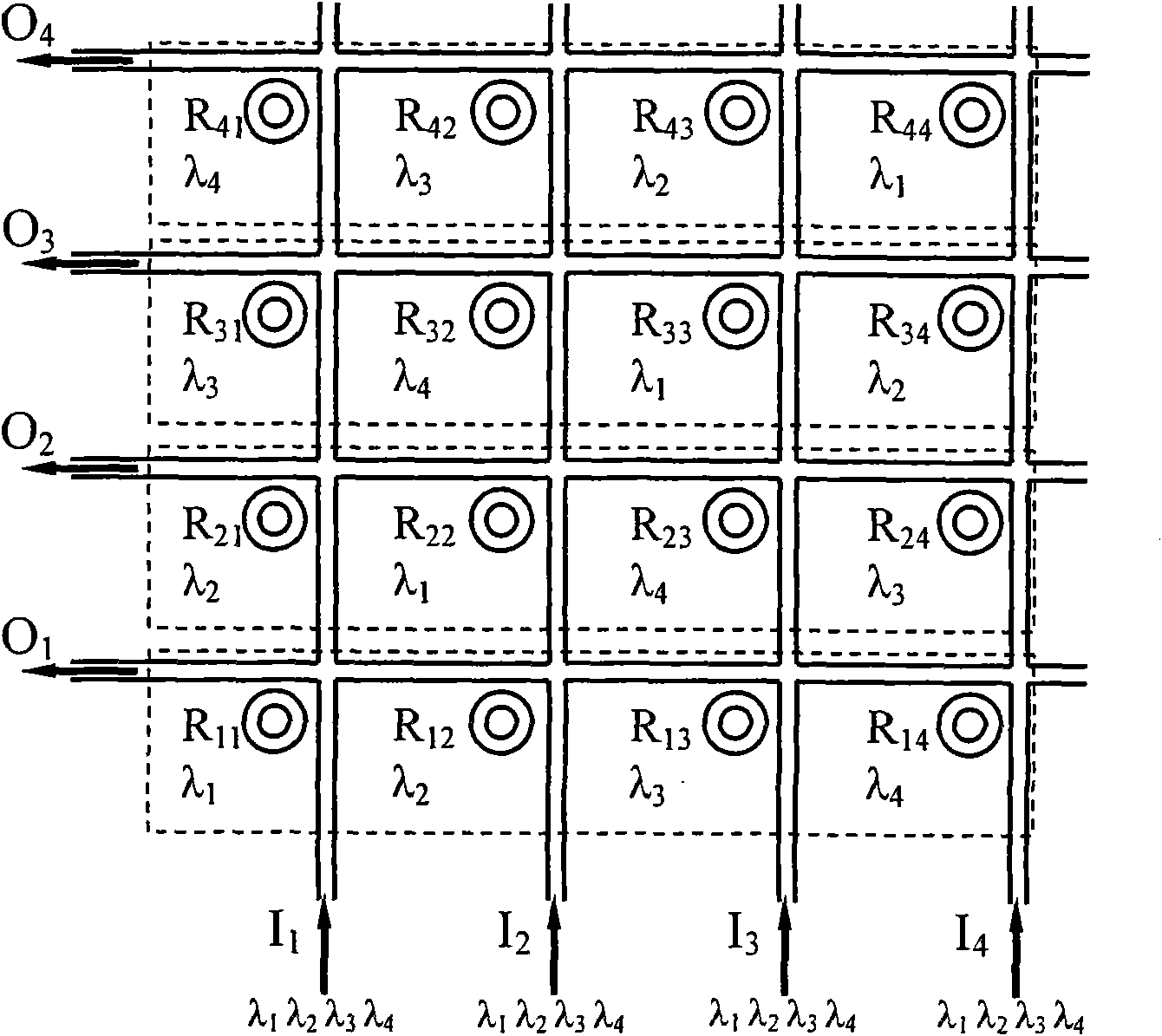

Integrated optic vector-matrix multiplier

ActiveUS8027587B1Computing operations for integration/differentiationWavelength-division multiplex systemsMatrix multiplierLength wave

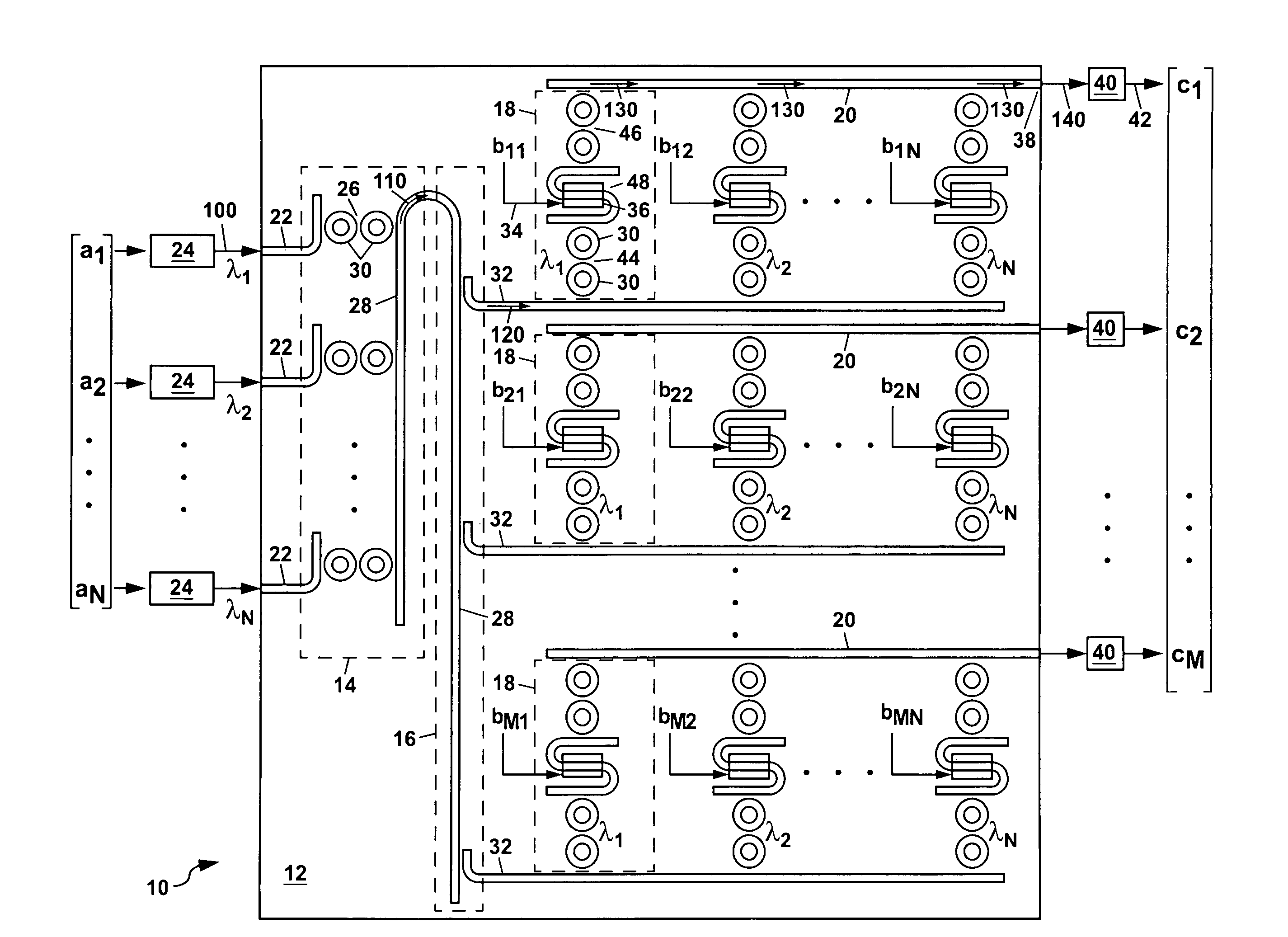

A vector-matrix multiplier is disclosed which uses N different wavelengths of light that are modulated with amplitudes representing elements of an N×1 vector and combined to form an input wavelength-division multiplexed (WDM) light stream. The input WDM light stream is split into N streamlets from which each wavelength of the light is individually coupled out and modulated for a second time using an input signal representing elements of an M×N matrix, and is then coupled into an output waveguide for each streamlet to form an output WDM light stream which is detected to generate a product of the vector and matrix. The vector-matrix multiplier can be formed as an integrated optical circuit using either waveguide amplitude modulators or ring resonator amplitude modulators.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

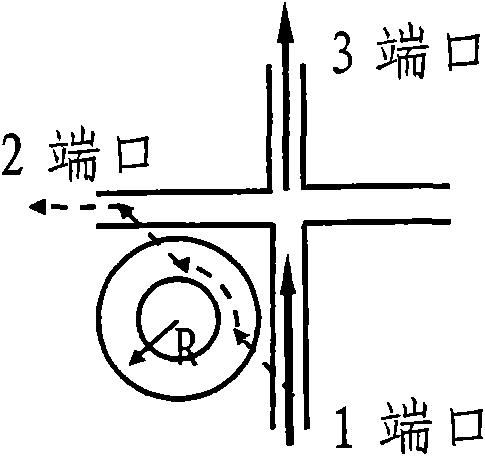

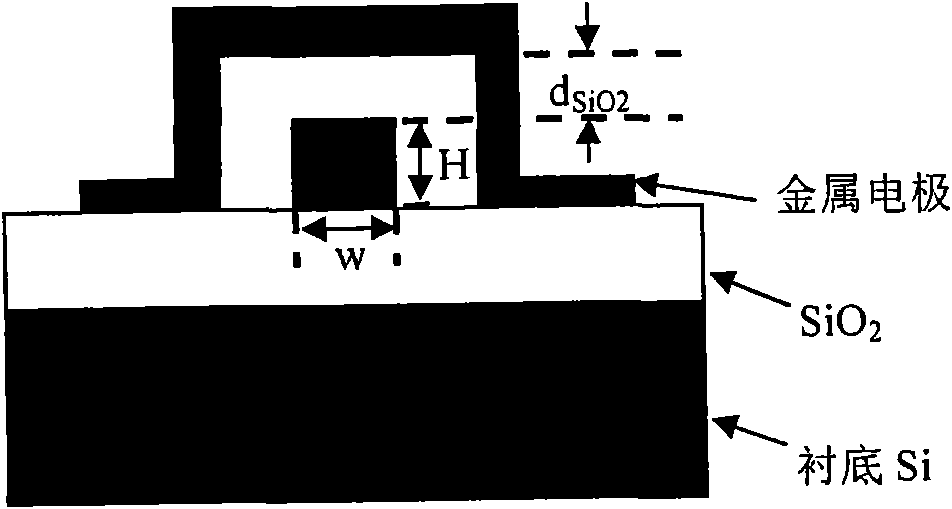

Silicon-based integrated optical vector-matrix multiplier

ActiveCN101630178AReduce volumeReduce power consumptionLogic circuits using opto-electronic devicesNon-linear opticsNanowireMatrix multiplier

The invention discloses a silicon-based integrated optical vector-matrix multiplier, which consists of nano-wire micro-ring resonators arranged periodically, and is used for realizing the multiplication of an N*N matrix and an N*1 vector, wherein elements in the N*N matrix and the N*1 vector are all 0 or 1. The optical vector-matrix multiplier is prepared from a silicon-on-insulator material, the basic units of the multiplier are the nano-wire micro-ring resonators (MRR), and the basic structure is the MRRs which are arranged in N*N and are provided with a thermal modulation mechanism respectively. The silicon-based integrated optical vector-matrix multiplier adopts the prior art, so that the device has small volume, low power consumption and good expansibility and is convenient to be integrated with an electrical element; the silicon-based integrated optical vector-matrix multiplier adopts laser pulses to transmit information, so the speed is high and the delay is short; a digital mode is utilized for processing signals, so the defect that an analog optical computing system has low accuracy and poor programmable capacity is avoided; and waveguides with a great refractive index difference are utilized to transmit light, so the problem that the space diversity efficiency of the conventional optical vector-matrix multiplier is low is avoided.

Owner:HUAWEI TECH CO LTD

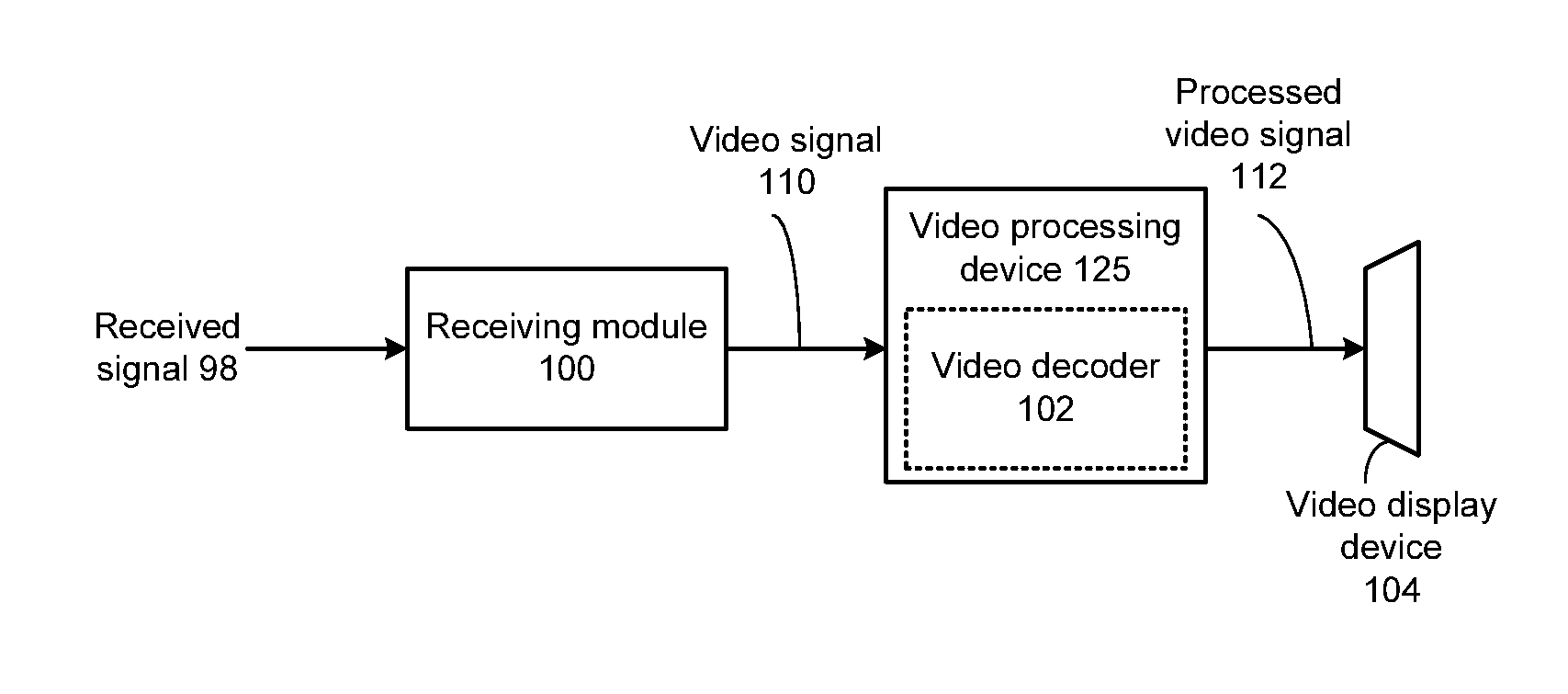

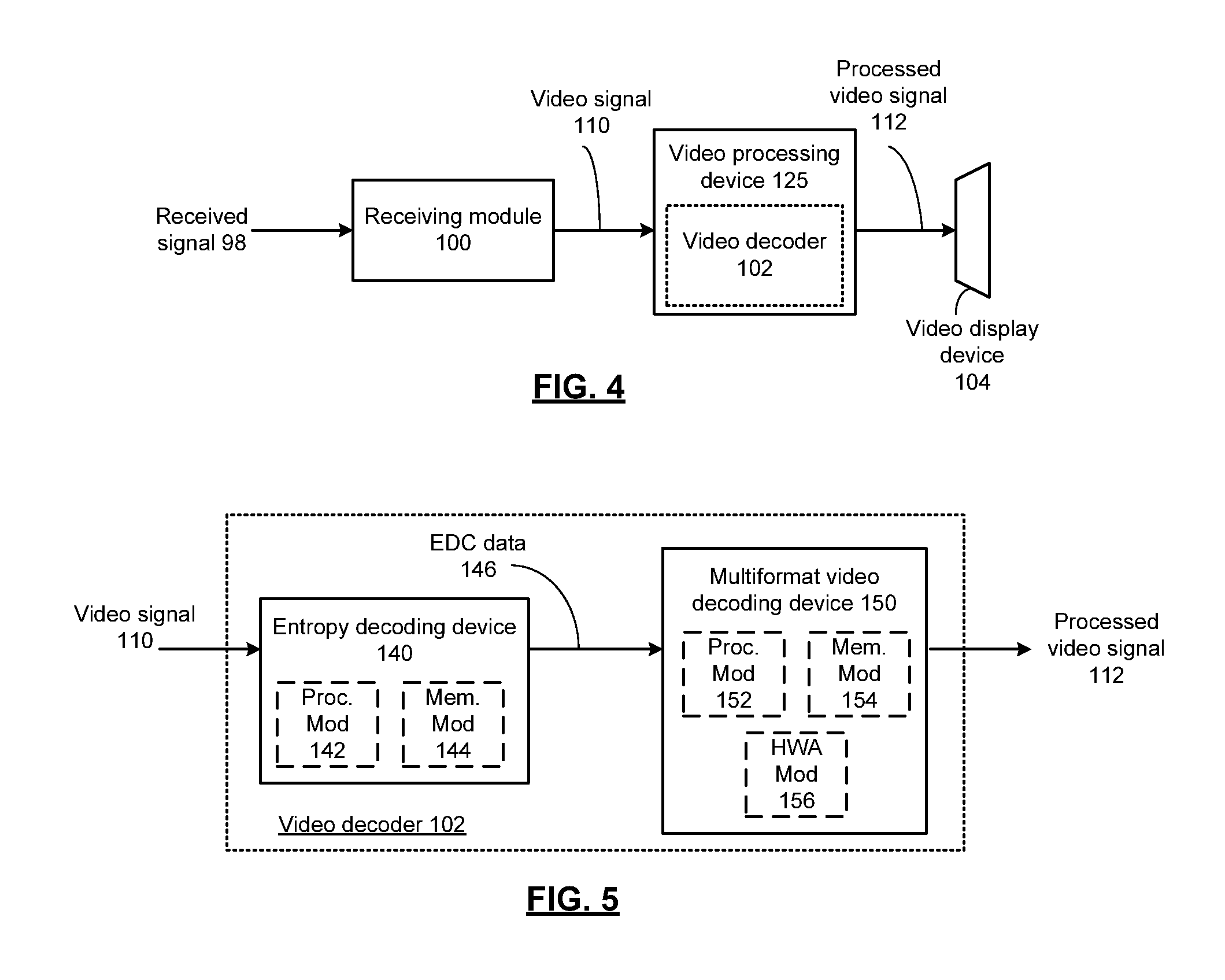

Video decoder with multi-format vector processor and methods for use therewith

ActiveUS20120314774A1Color television with pulse code modulationColor television with bandwidth reductionMatrix multiplierComputer science

A multi-format video decoder includes an entropy decoding device that generates entropy decoded (EDC) data from an encoded video signal. A multi-format video decoding device includes a memory module that stores a plurality of operational instructions including at least one matrix multiply instruction that includes matrix input configuration data. A plurality of vector processor units generate a decoded video signal from the EDC data, wherein at least one of the plurality of vector processors include a matrix multiplier that generates output data based on a multiplication of first input data and second input data in accordance with the matrix input configuration data, wherein the matrix input configuration data indicates the dimensionality of the first input data and the second input data.

Owner:VIXS SYSTEMS INC

Vector-by-matrix multiplier modules based on non-volatile 2d and 3D memory arrays

There are disclosed devices, system and methods for a vector-by-matrix multiplier (VMM) module having a three-dimensional memory matrix of nonvolatile memory devices each having a charge storage, an activation input, a signal input and an output signal in a range that is based on a stored charge and an input signal during assertion of the activation signal. The memory devices are arranged in two dimensional (XY) layers that are vertically disposed along (Z) columns. The activation inputs of each layer are connected to a same activation signal, the memory devices of rows in a first dimension (X) of each layer have signal inputs connected to different input signals and have signal outputs connected in series to a common output. The memory devices of rows in a second dimension (Y) of each layer have signal inputs connected to a set of the same inputs along the first dimension.

Owner:MENTIUM TECH INC

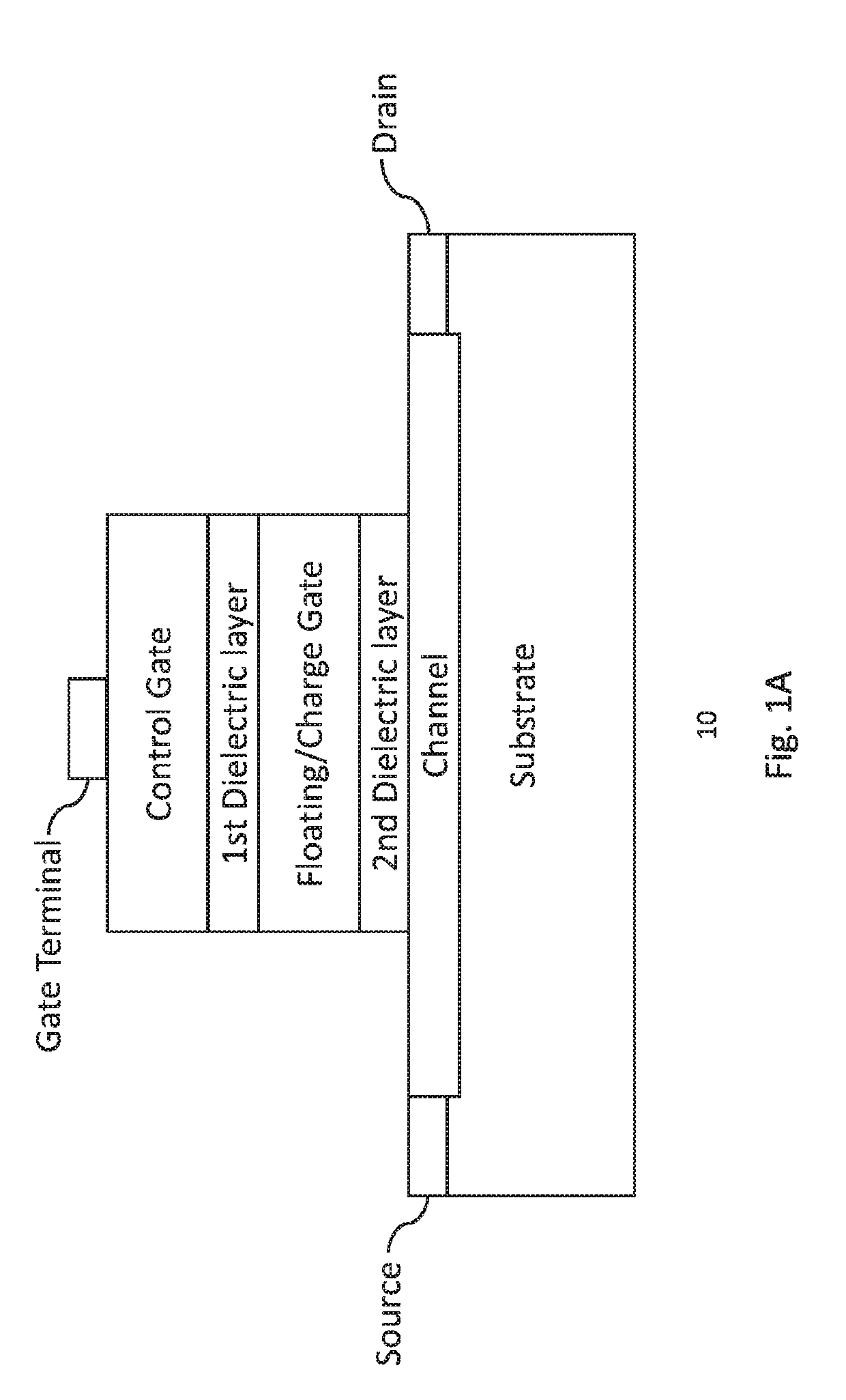

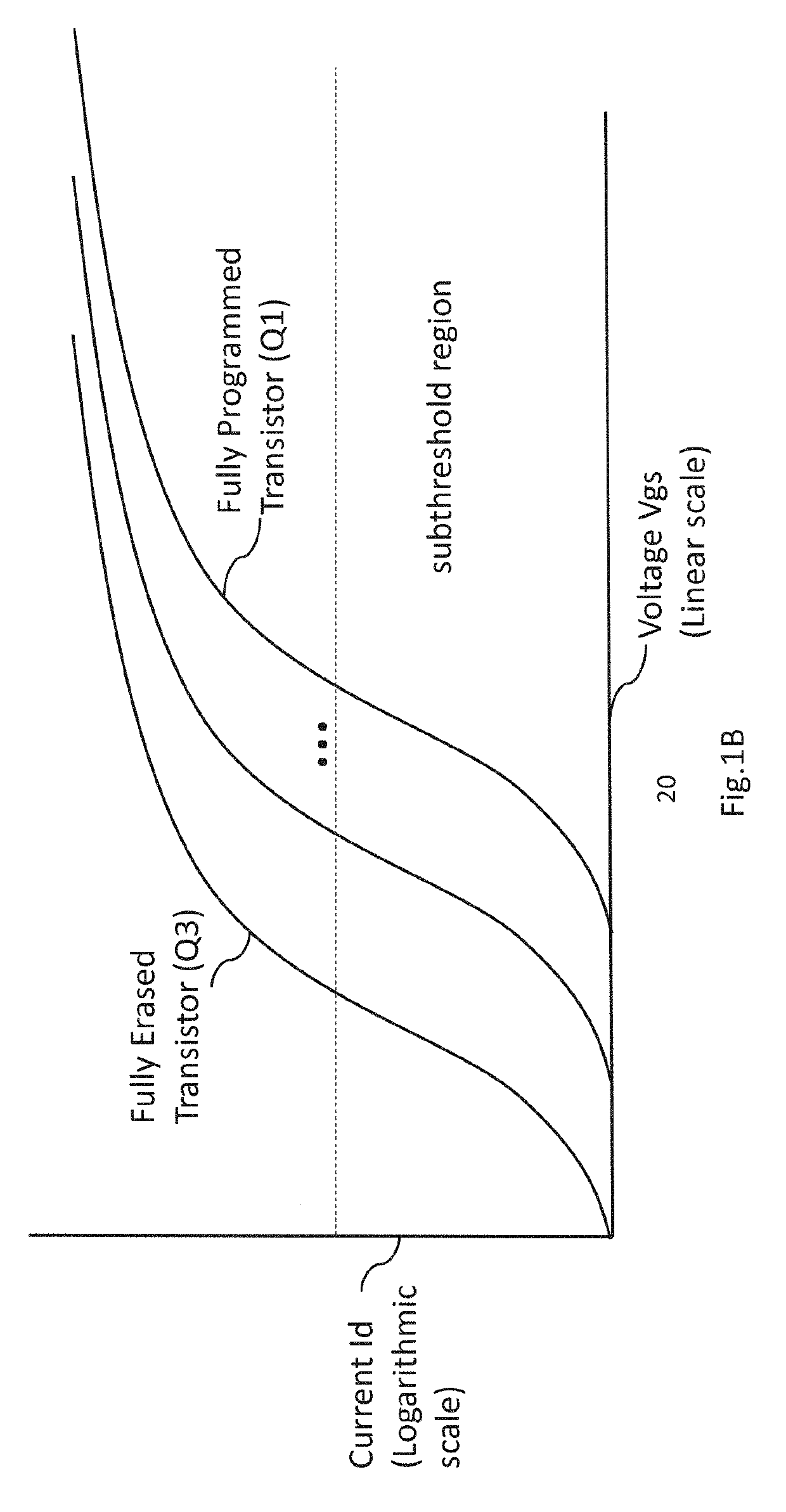

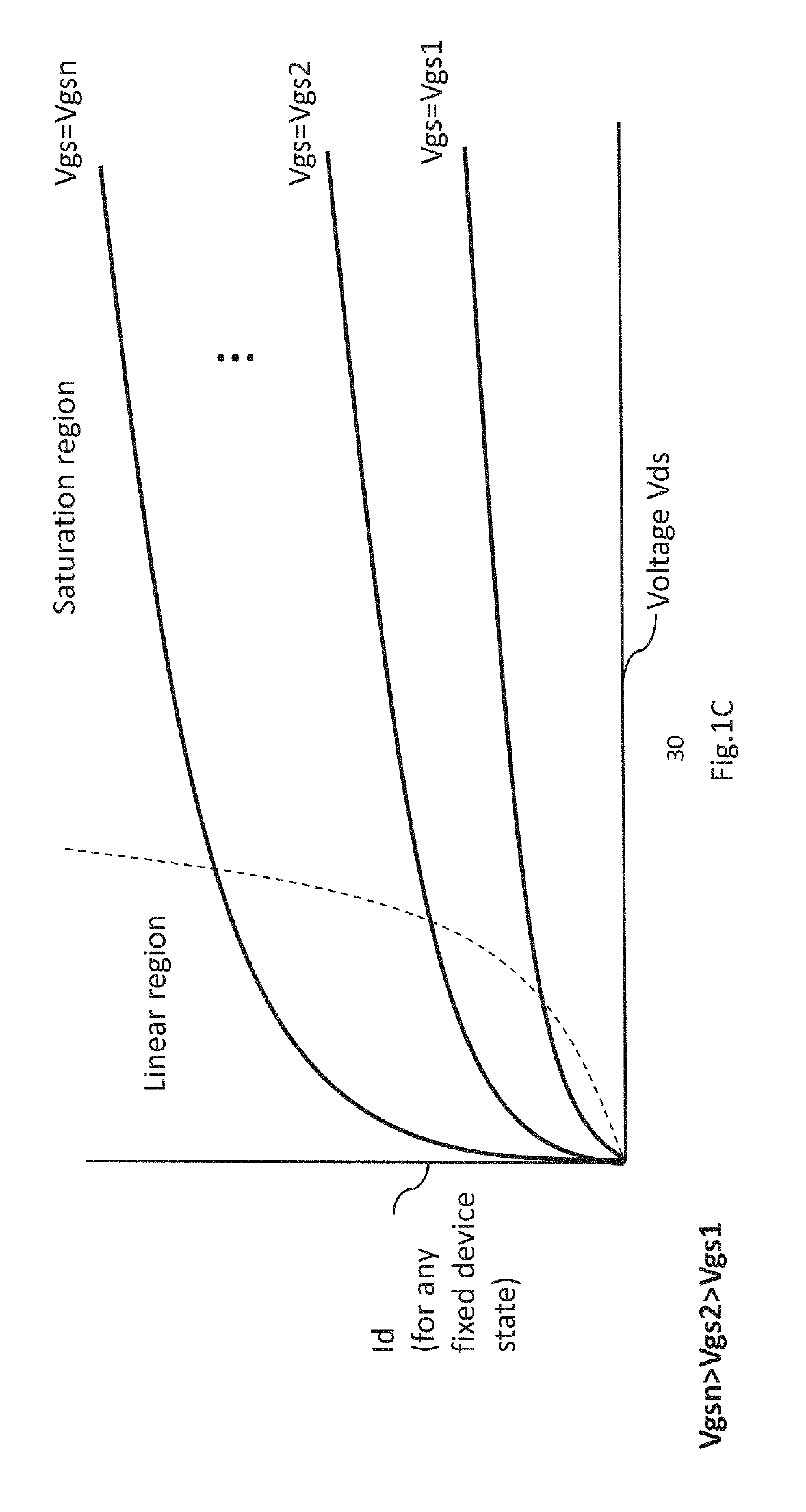

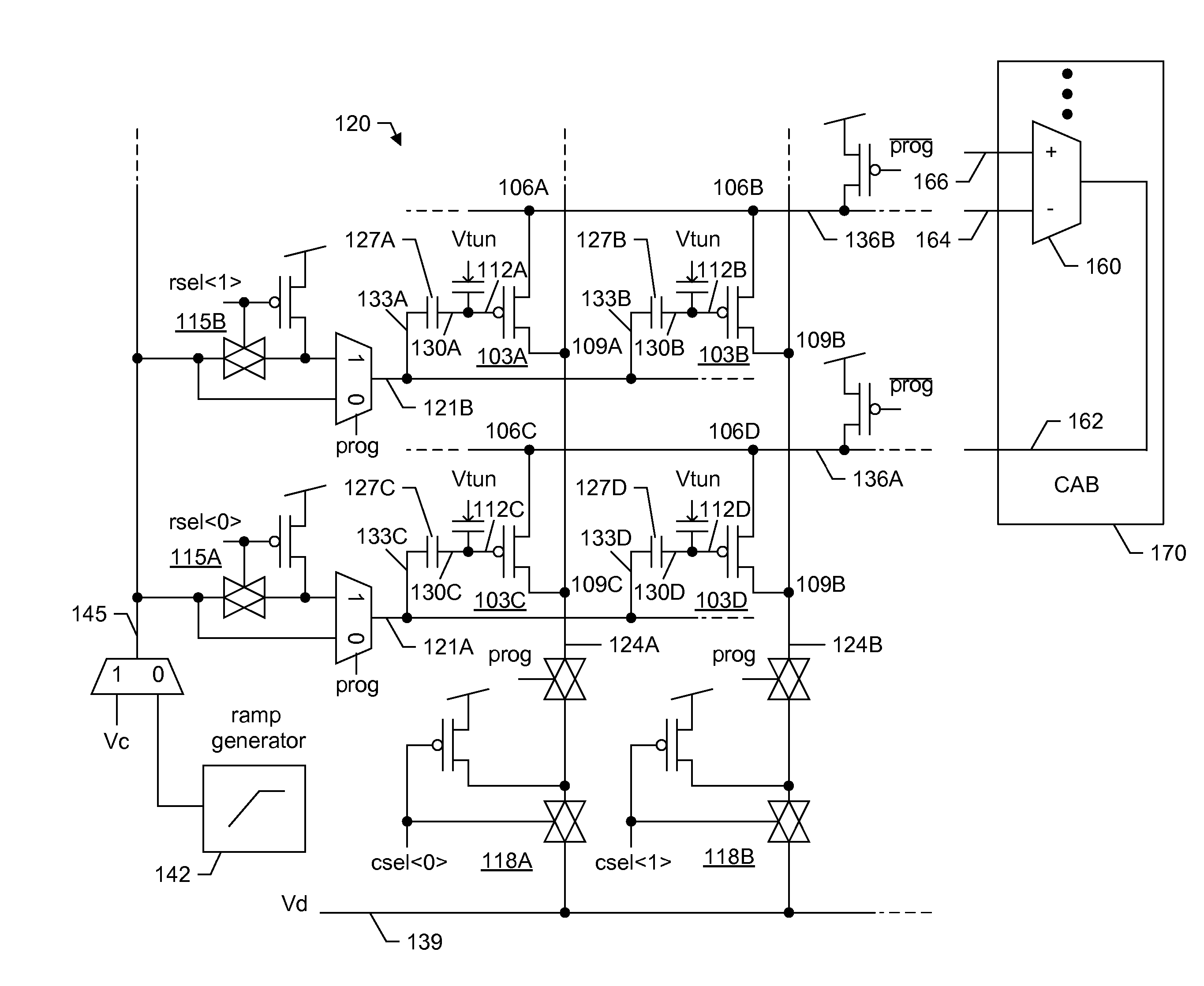

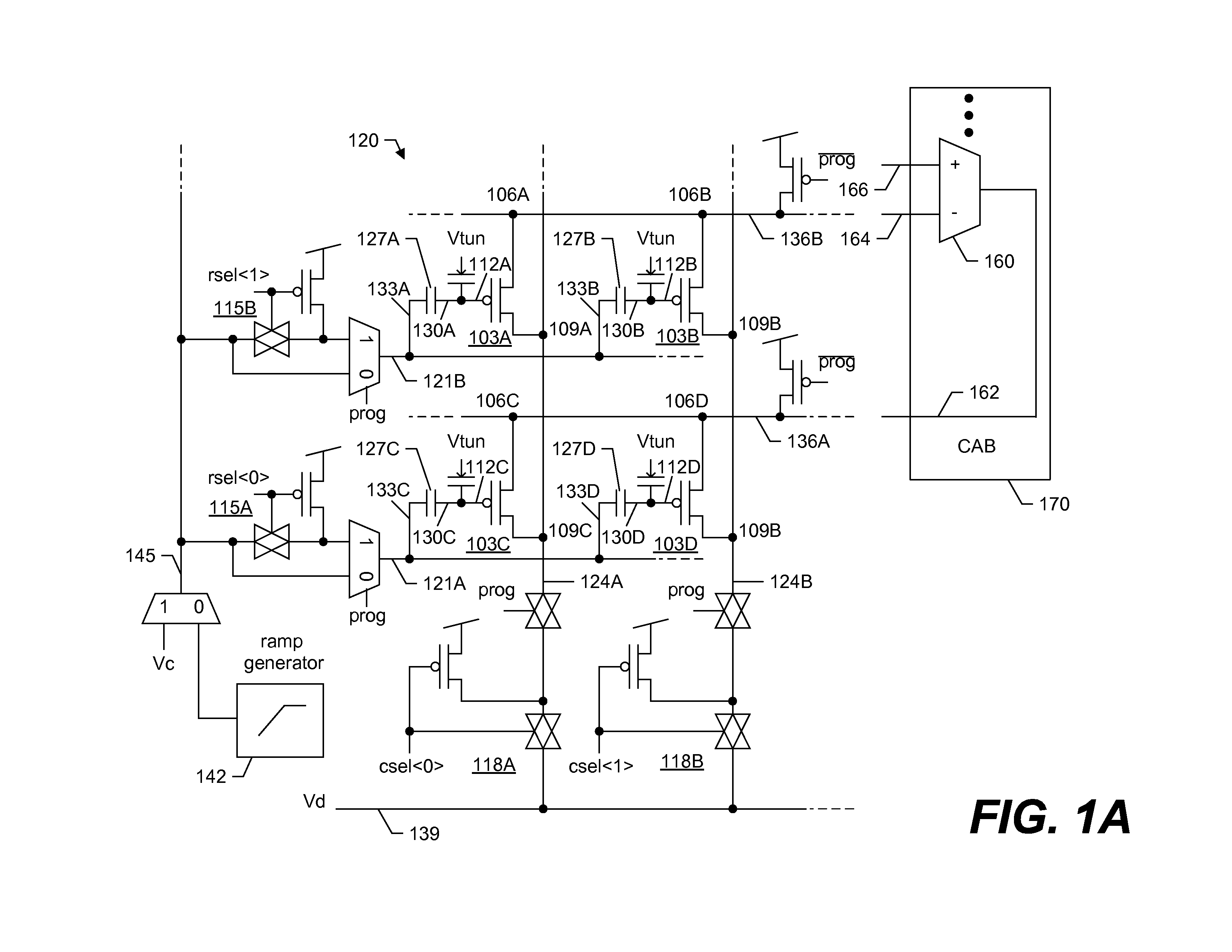

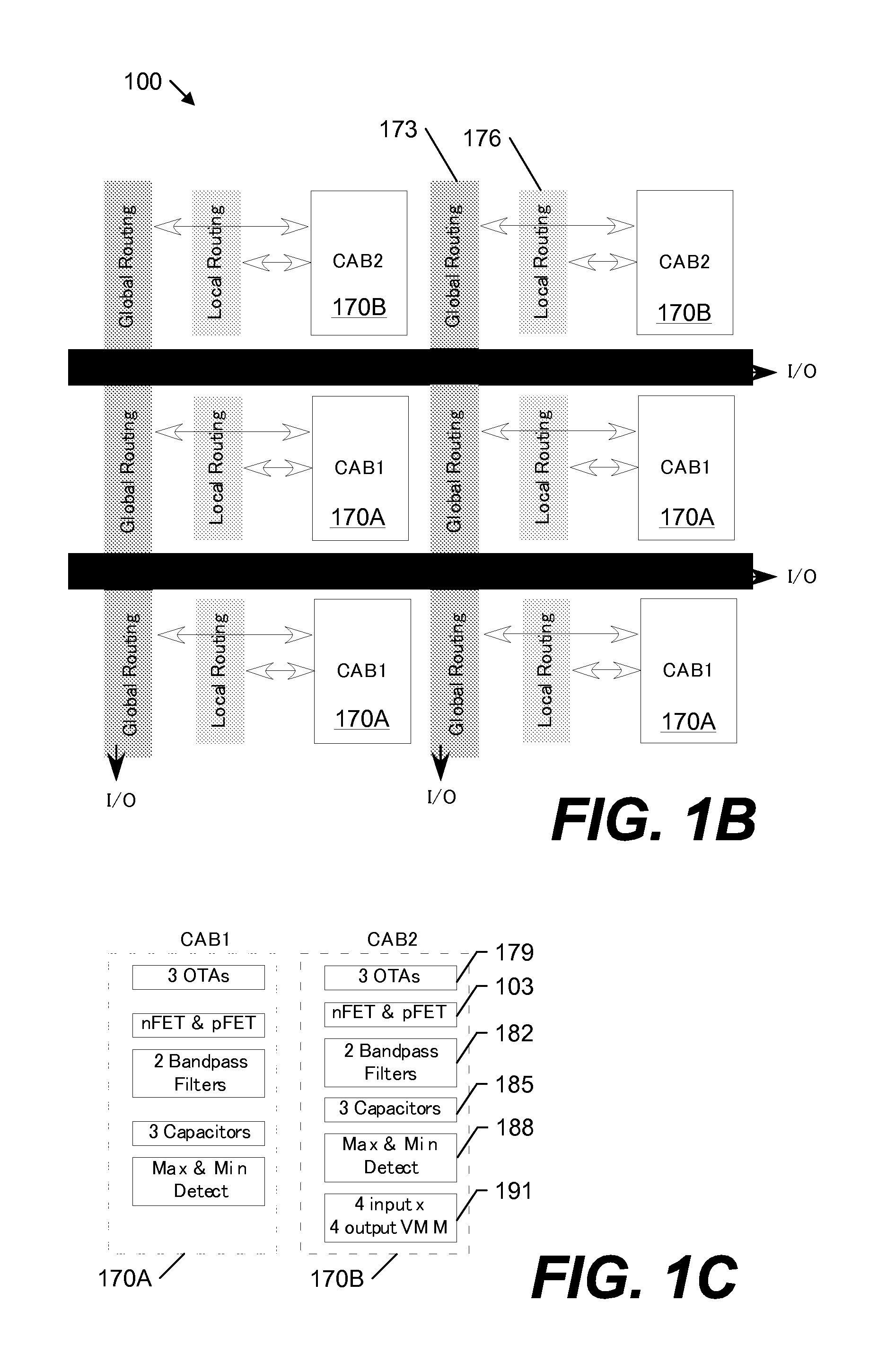

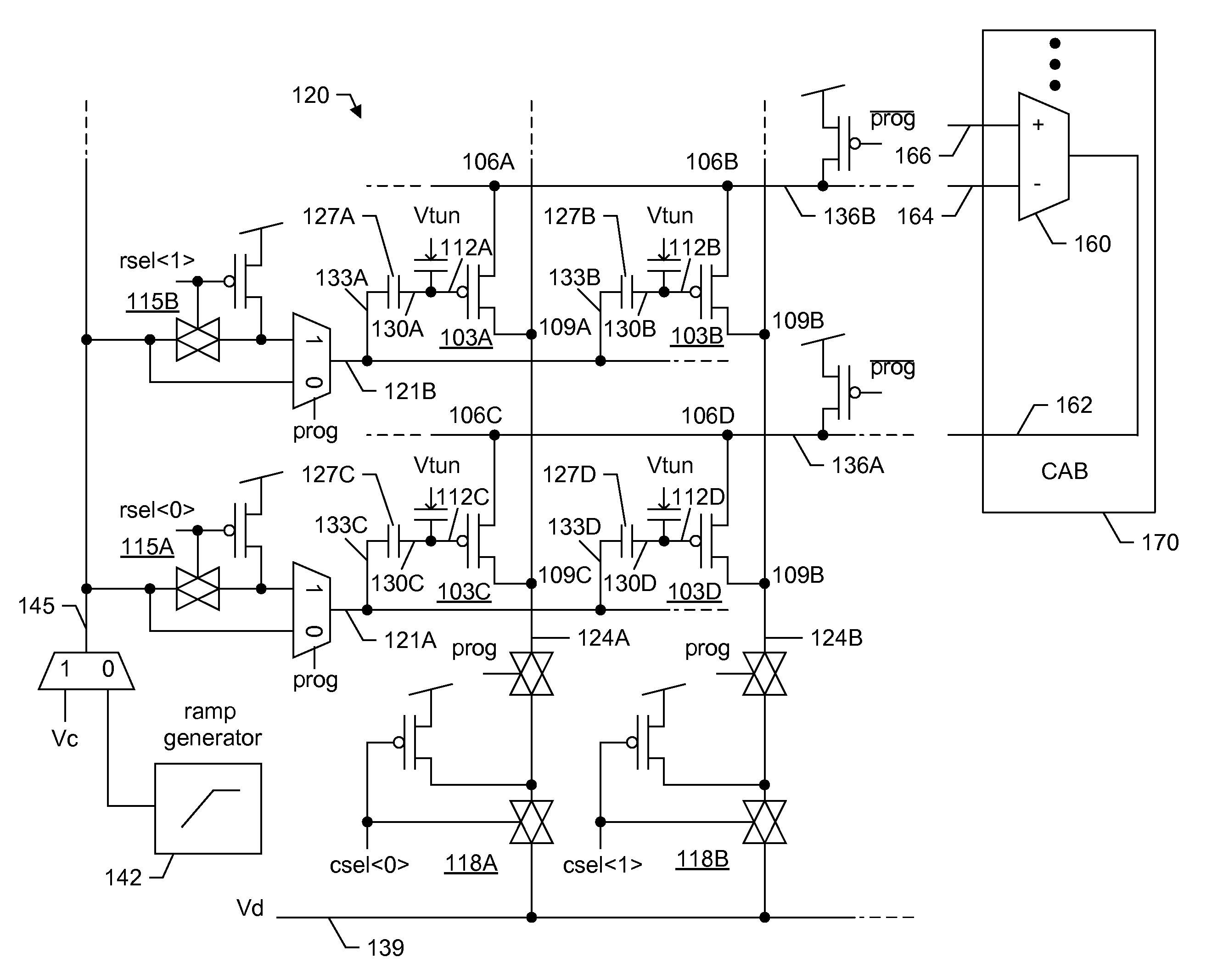

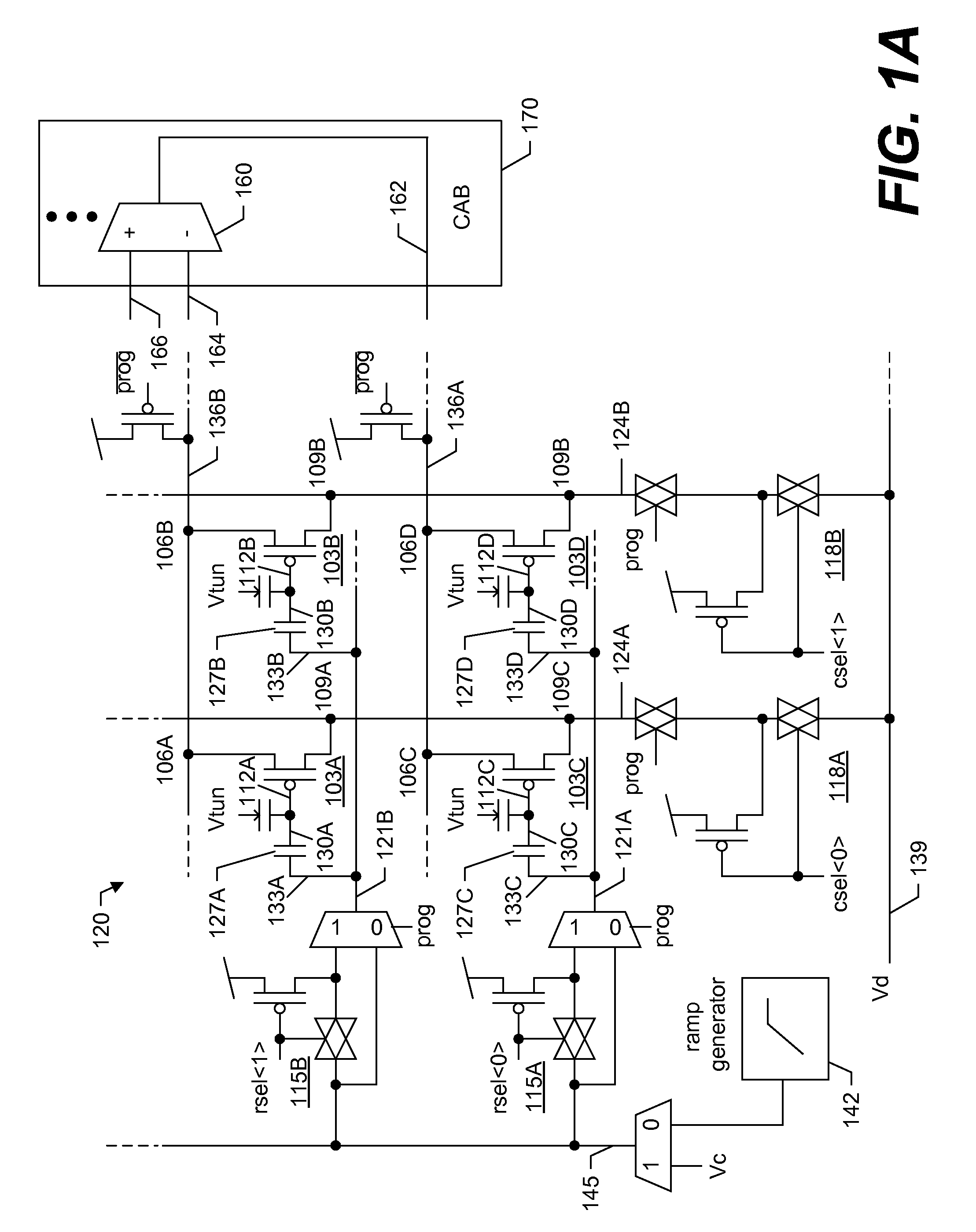

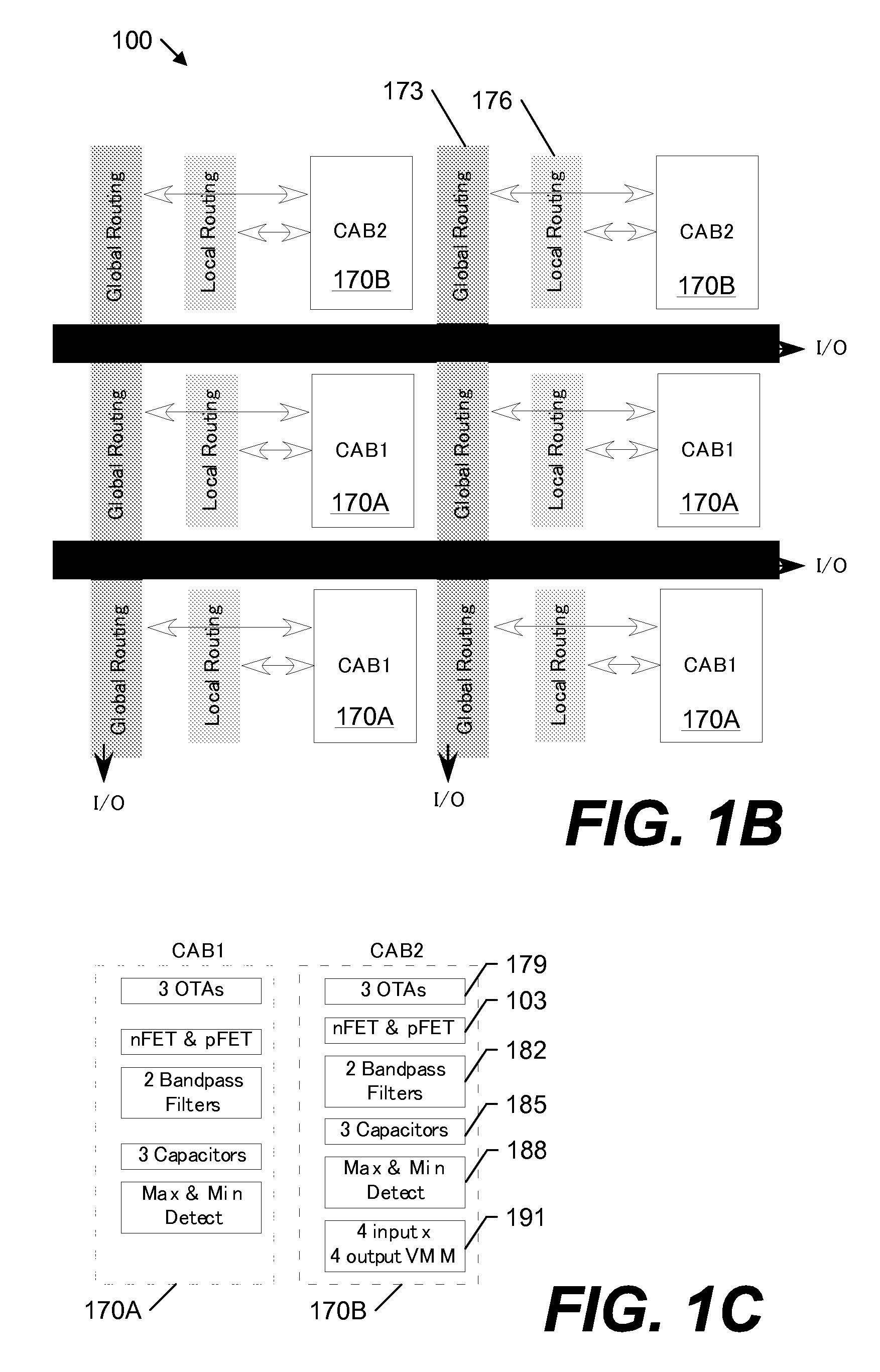

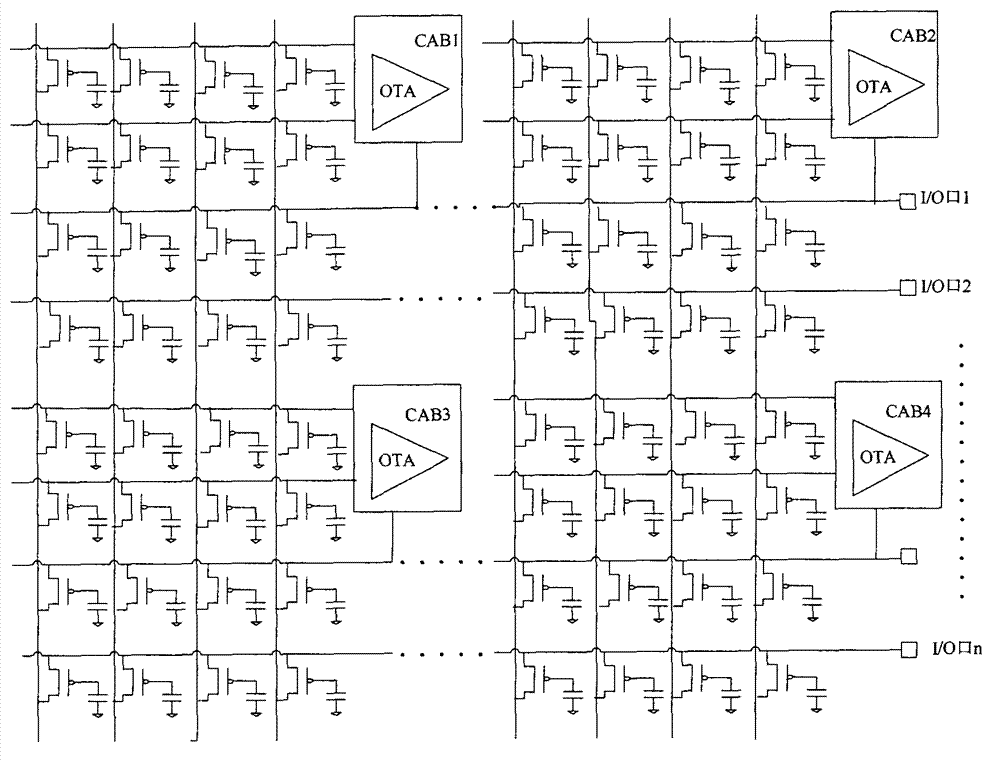

Systems and methods for programming large-scale field-programmable analog arrays

ActiveUS20060261846A1Good flexibilitySolid-state devicesLogic circuits using elementary logic circuit componentsCapacitanceTransistor array

A large-scale field-programmable analog array (FPAA) for rapidly prototyping analog systems and an arbitrary analog waveform generator. The large-scale FPAA includes a floating-gate transistor array and a plurality of computational analog blocks (CABs), which may be adapted to set bias voltages for operational transconductance amplifiers (OTAs), adjust corner frequencies on the capacitively coupled current conveyors, set multiplier coefficients in vector-matrix multipliers, and a variety of other operations. The floating-gate transistors may be used as switch elements, programmable resistor elements, precision current sources, and programmable transistors. Accordingly, the floating-gate transistors within the array allow on-chip programming of the characteristics of the computational elements, while still maintaining compact CABs. The arbitrary analog waveform generator may include programmable floating-gate MOS transistors for use as analog memory cells to store samples of the waveforms.

Owner:GEORGIA TECH RES CORP

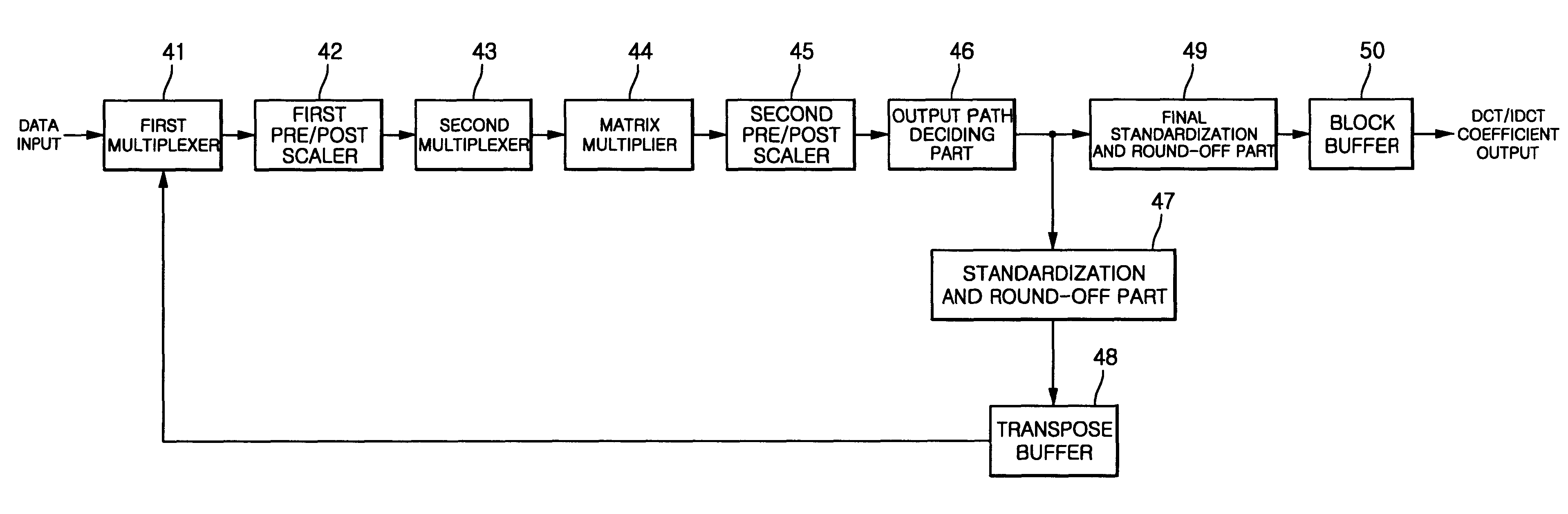

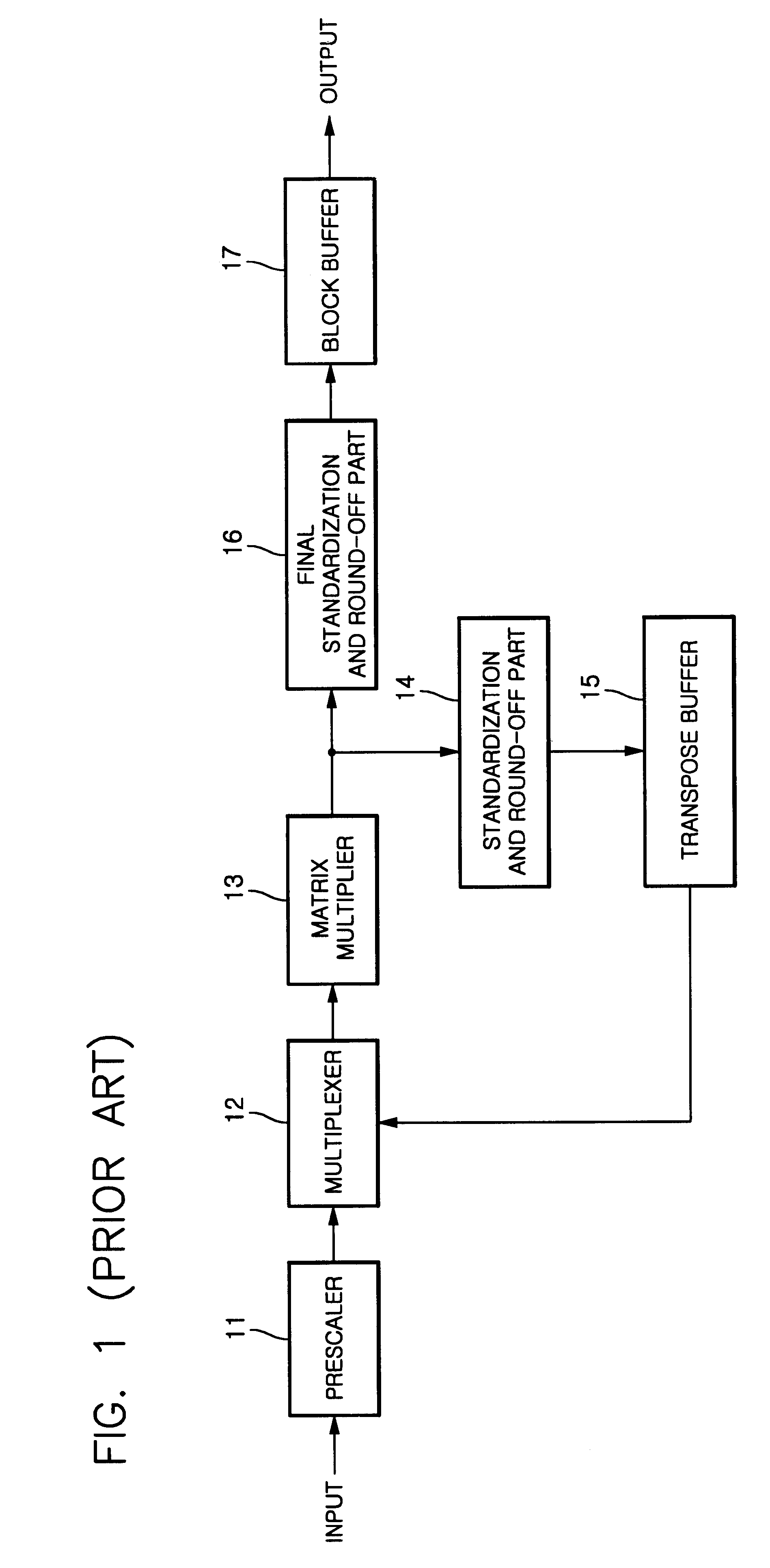

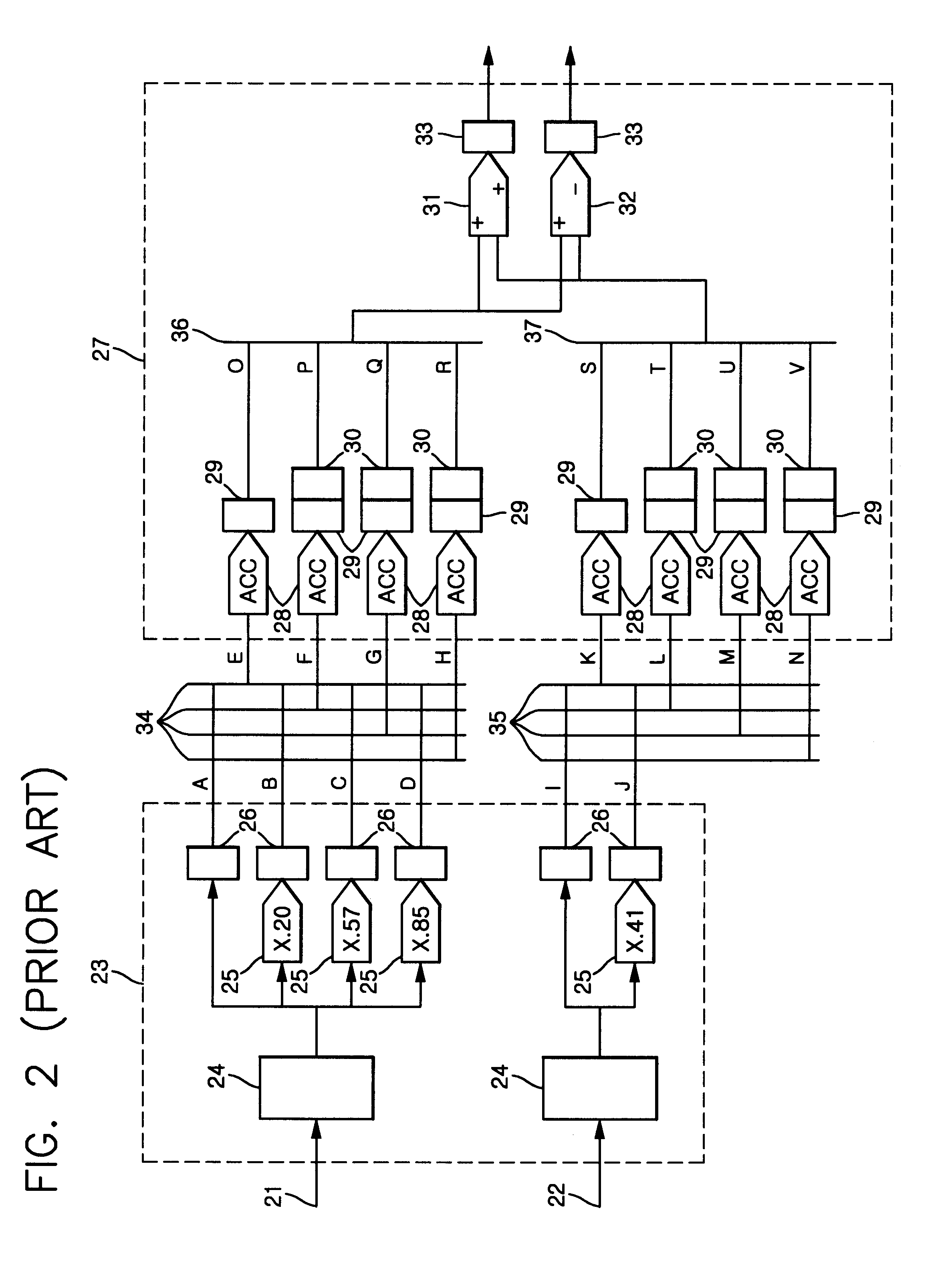

DCT/IDCT processor

InactiveUS6308193B1Pulse modulation television signal transmissionProcessor architectures/configurationMultiplexerMatrix multiplier

In order to execute a rapid and effective DCT and IDCT and embody DCT and IDCT in one processor, in an inventive DCT / IDCT processor, an input multiplexer selects DCT or IDCT coefficients and transfers the coefficients to a matrix multiplier, and DCT / IDCT deciding unit within the matrix multiplier controls a flow of the DCT and IDCT coefficients. An output multiplexer decides an output of the DCT and the IDCT, to thereby embody the DCT and the IDCT in one processor, and perform the DCT and the IDCT at a high speed by reducing the number of multiplication calculation, namely through a decrease of the calculation number.

Owner:HYUNDAI ELECTRONICS IND CO LTD

Residue number matrix multiplier

ActiveUS10387122B1Improve efficiencyIncrease speedComputations using residue arithmeticPhysical realisationFormation matrixAlgorithm

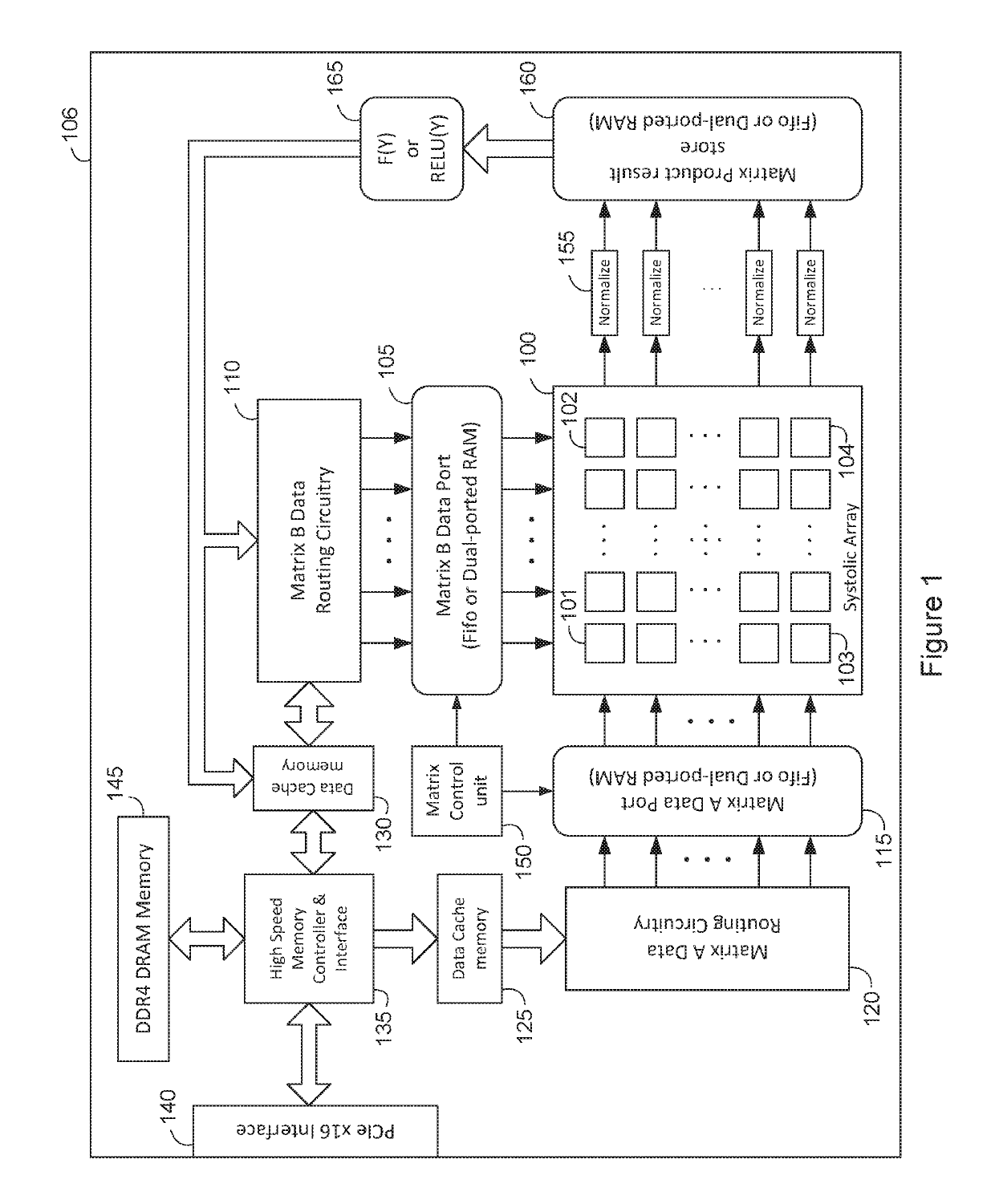

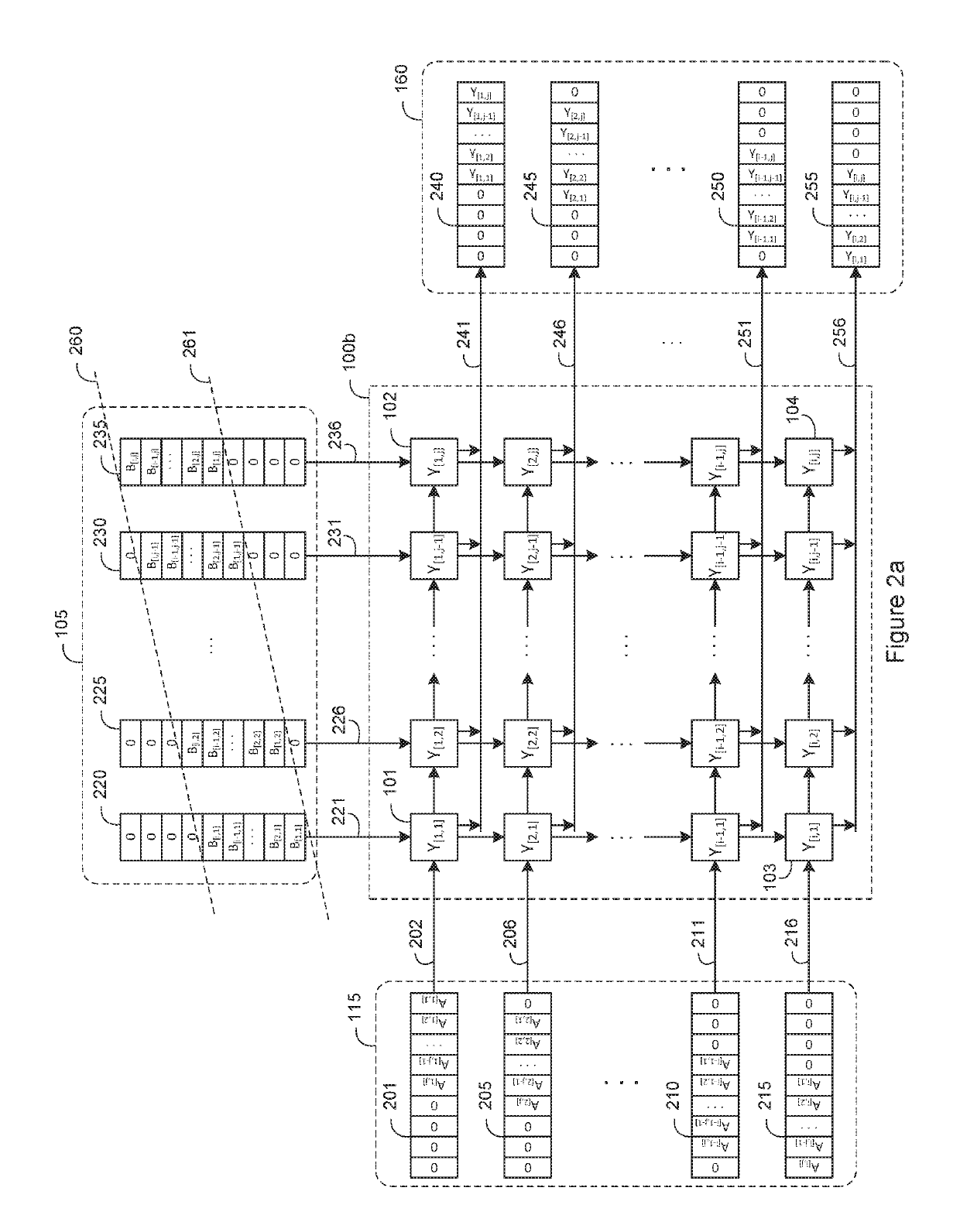

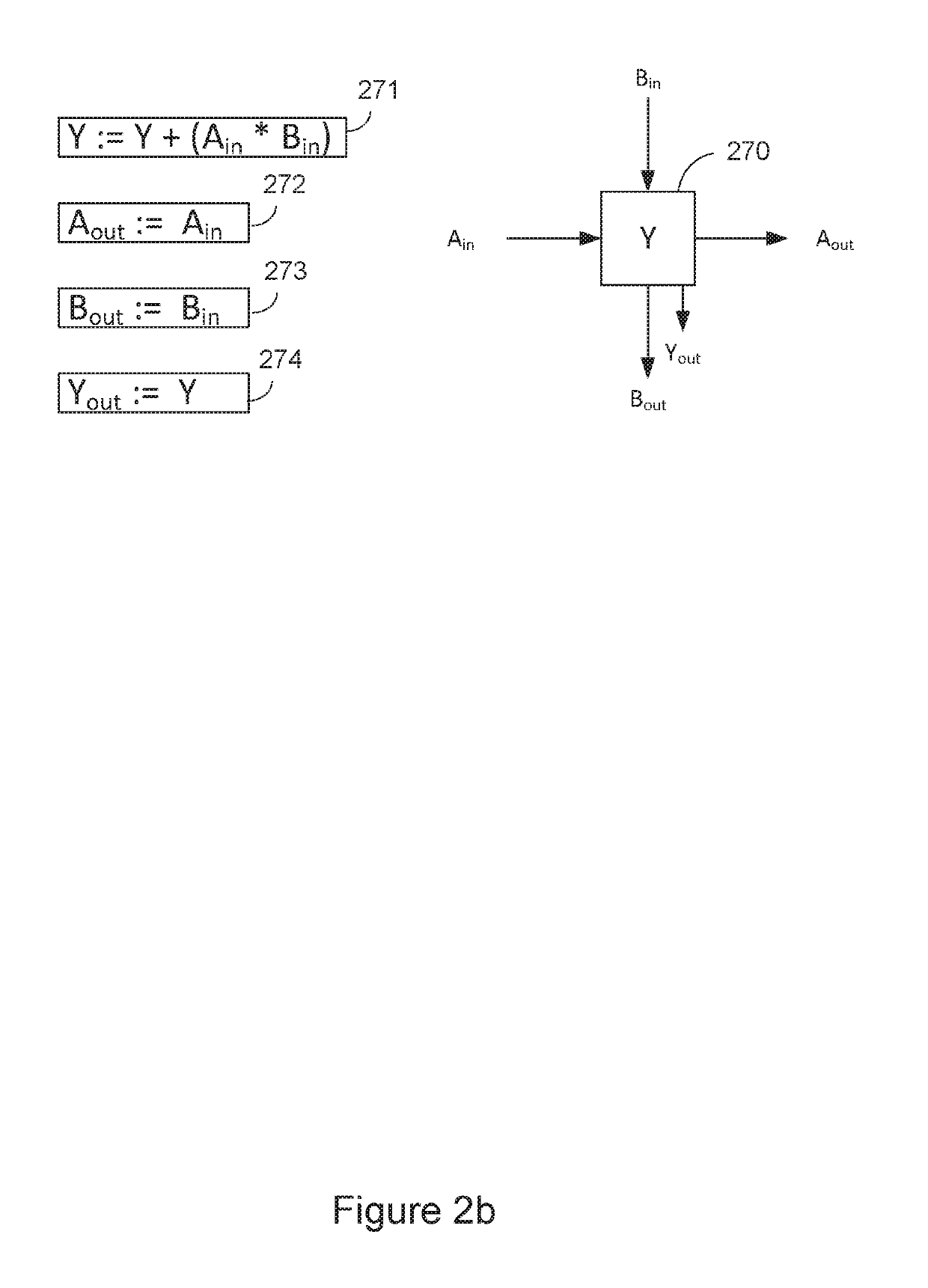

Arithmetic circuits and methods that perform efficient matrix multiplication for hardware acceleration of neural networks, machine learning, web search and other applications are disclosed herein. Various arrays of multiplier-accumulators may be coupled to form a matrix multiplier which processes data using high precision, fixed point residue number arithmetic.

Owner:OLSEN IP RESERVE

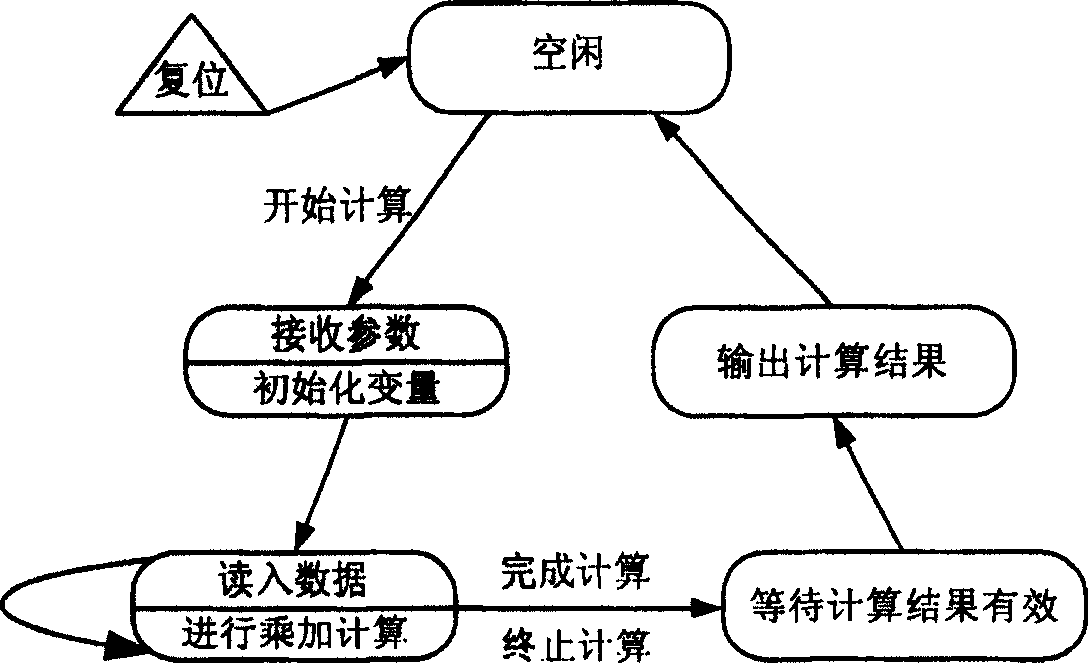

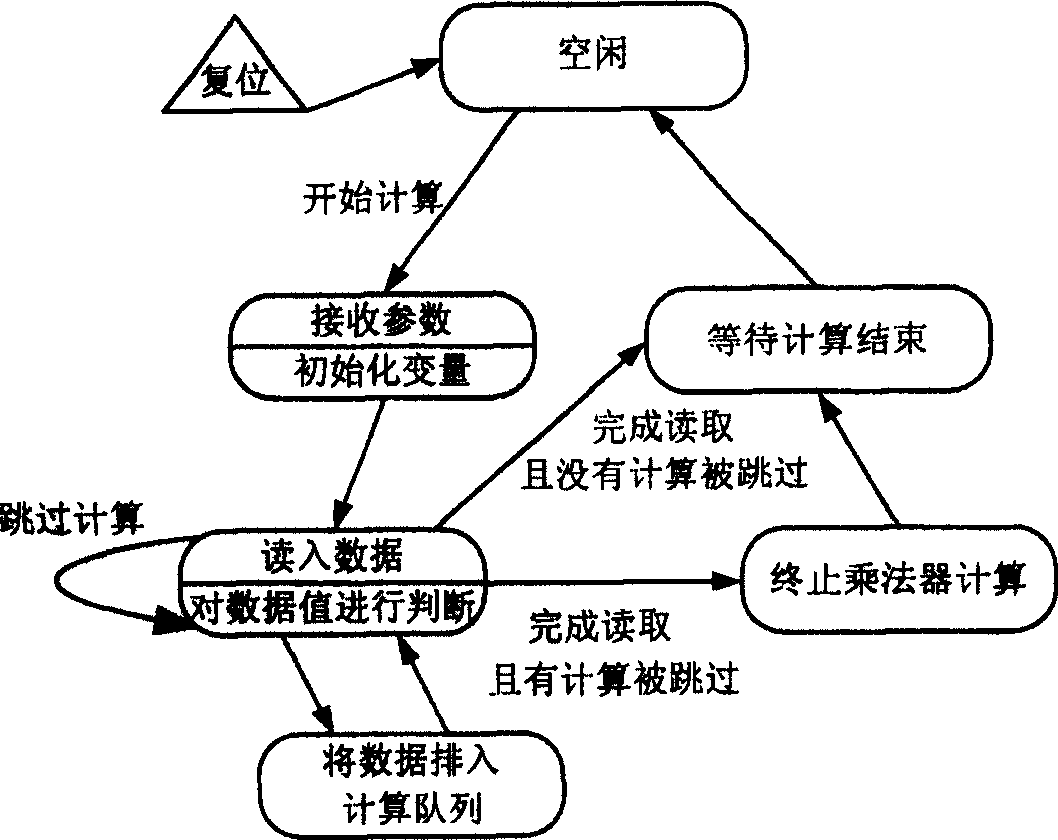

Systolic structure matrix multiplier based on FPGA (Field Programmable Gate Array) and implementation method thereof

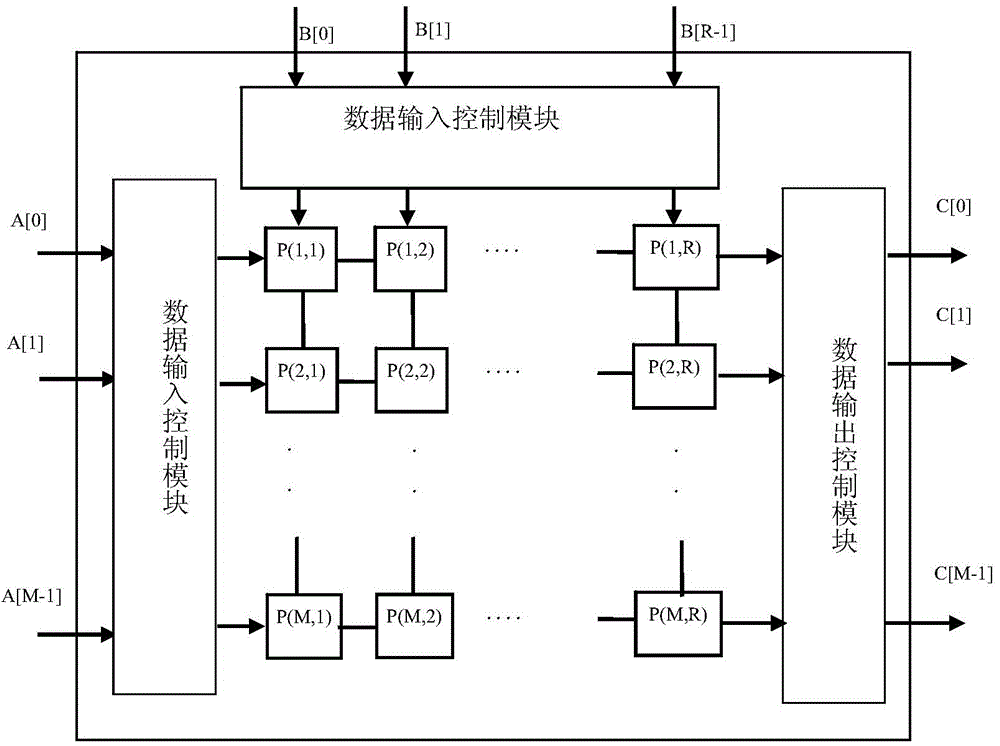

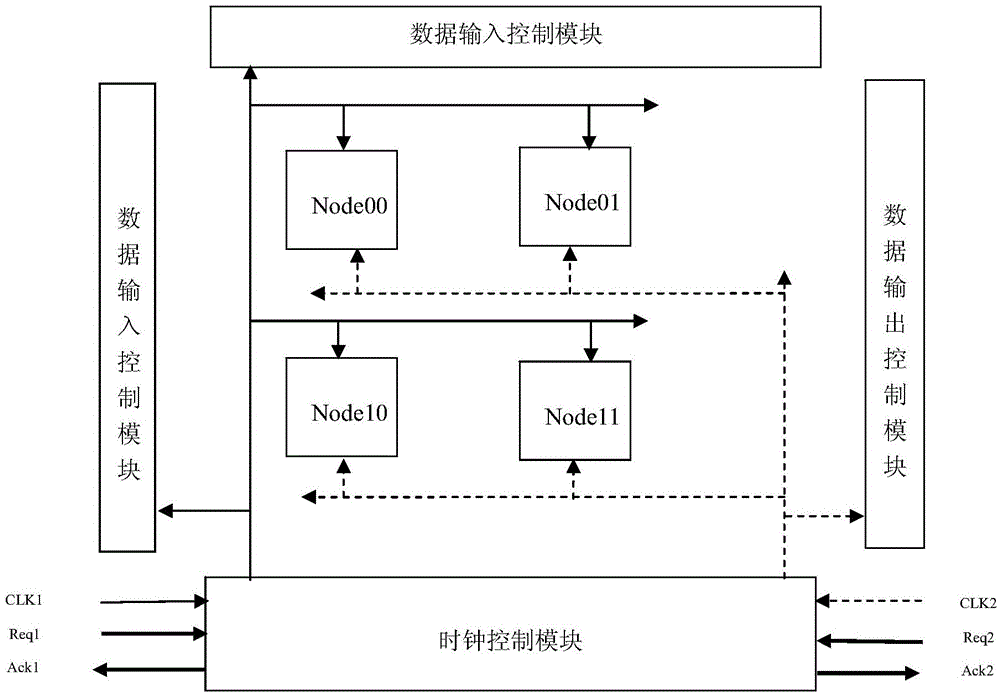

InactiveCN105589677ALow fan-out requirementsImprove computing powerDigital data processing detailsBinary multiplierComputer module

The invention provides a systolic structure matrix multiplier based on an FPGA (Field Programmable Gate Array) and an implementation method thereof. The systolic structure matrix multiplier comprises a multiplier array composed of M x R node units, a clock control module, a data input control module and a data output control module; the M x R node units are interconnected by a two-dimensional mesh array structure of M rows and R columns, used for performing a multiply-accumulate calculation on data, and have systolic structures in each data direction of rows and columns; the clock control module is used for providing a clock, controlling the whole calculation process, and recoding the state of a current multiplier; the data input control module is used for controlling an input matrix to input by rows or by columns, and making the input matrix to satisfy an input rule of time alignment; and the data output control module is used for outputting the calculation results by rows or by columns under the control of an output clock. The implementation method of the matrix multiplier provided by the invention can enable data to enter the matrix multiplier according to the input rule of the systolic structure by rows or by columns, and perform a multiply-add operation and output the calculation results. The systolic structure matrix multiplier based on the FPGA provided by the invention has the advantages of being very high in calculation performance, good in modularity and convenient in reconfiguration.

Owner:SHENYANG GOLDING NC & INTELLIGENCE TECH CO LTD

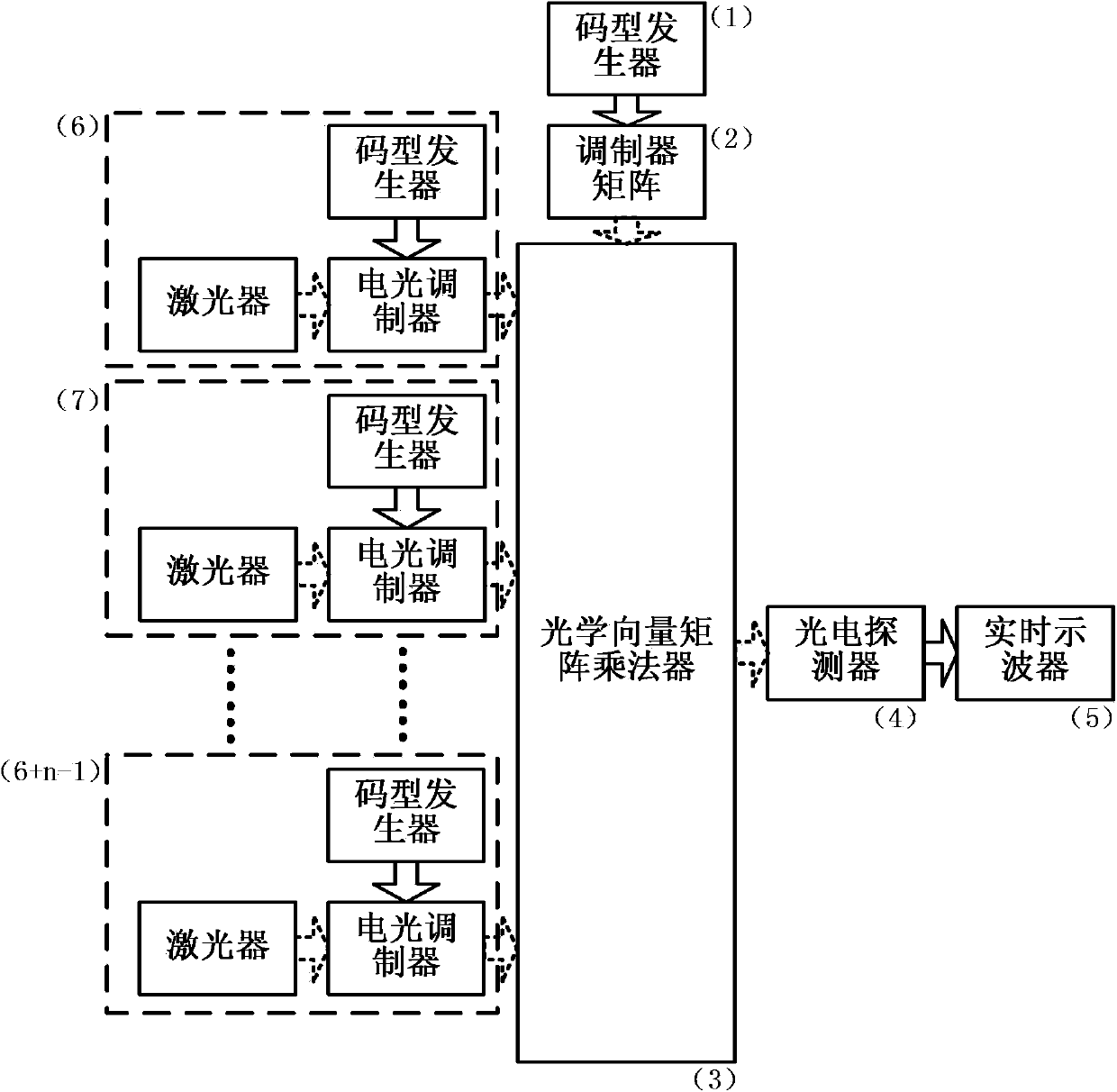

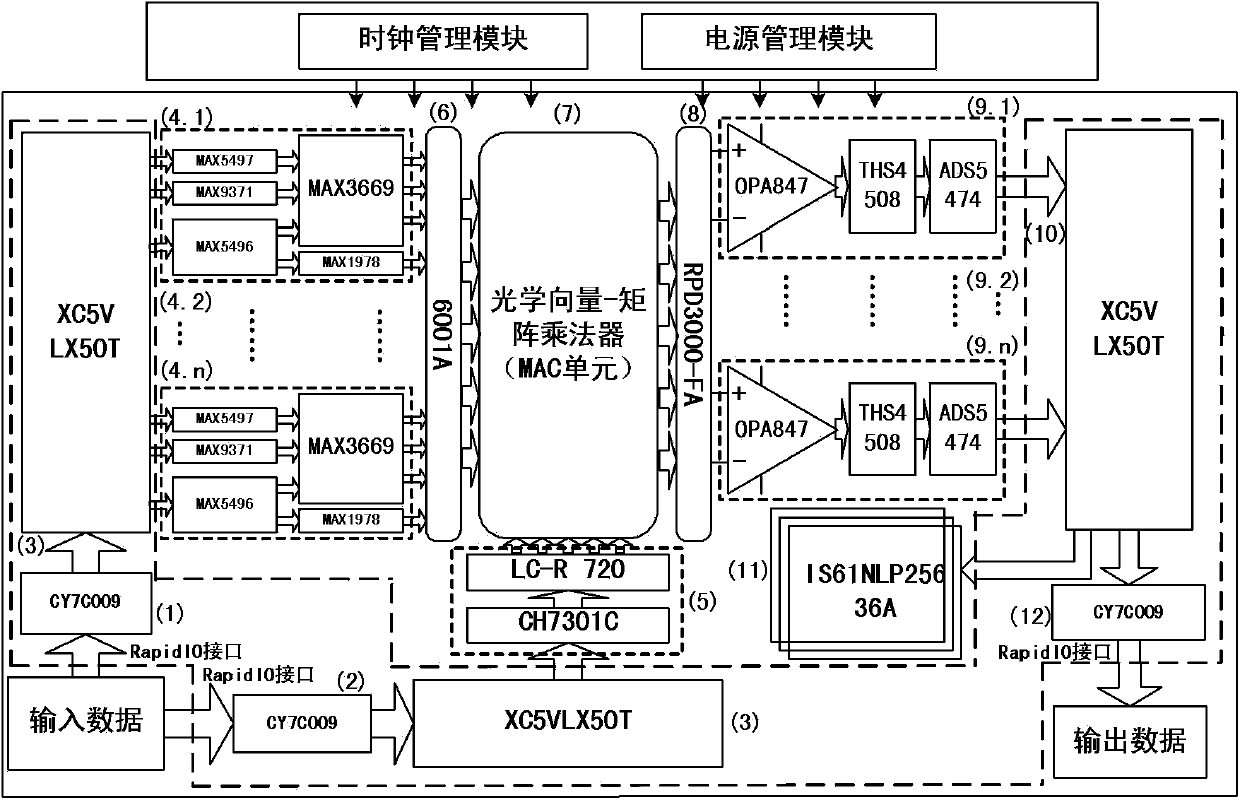

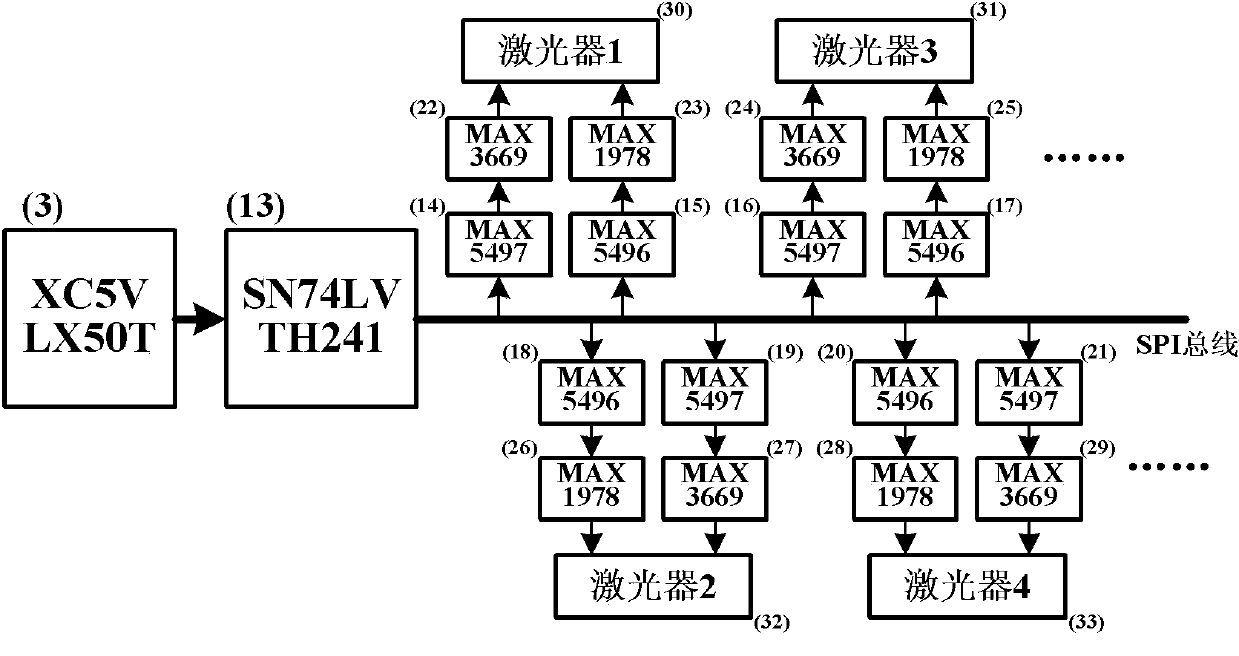

System for loading and extracting parallel information of optical vector-matrix multiplier

InactiveCN103473213AEasy to testEasy to analyzeComplex mathematical operationsBinary multiplierMatrix multiplier

The invention provides a system for loading and extracting parallel information of an optical vector-matrix multiplier. The system serves as an independently running organic whole with a self-contained system and slips the leash of discrete equipment such as a signal generator, an oscilloscope and an optical amplifier, and the optical vector-matrix multiplier can be conveniently, visually, flexibly and accurately tested and analyzed.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

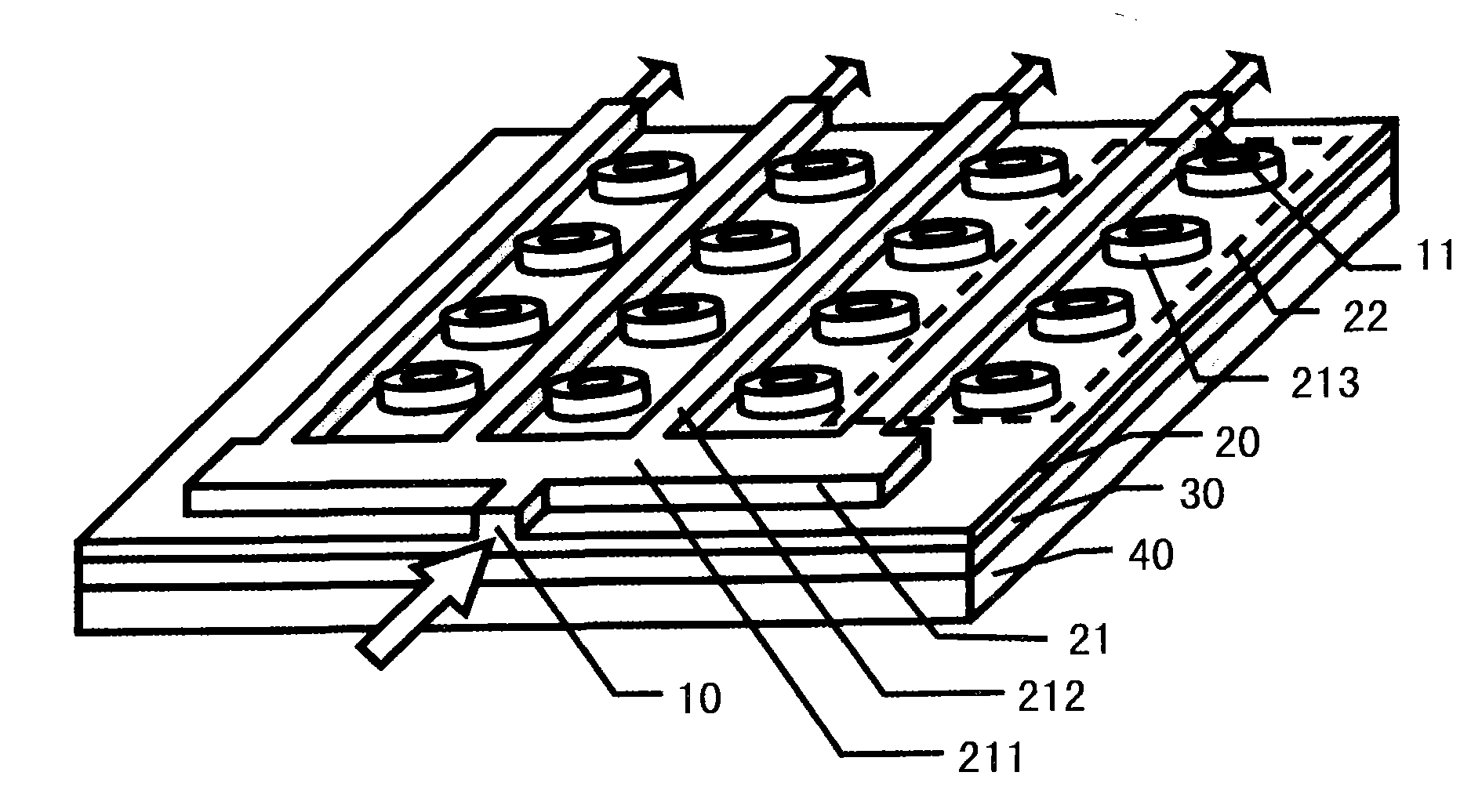

Integrated optical vector-matrix multiplier based on micro-ring resonators

ActiveCN102023672AReduce volumeReduce power consumptionLogic circuits using opto-electronic devicesComputation using denominational number representationMatrix multiplierComputing systems

The invention discloses an integrated optical vector-matrix multiplier. The optical vector-matrix multiplier comprises extensible inner product operation units formed by a plurality of tunable micro-ring resonators which have a parallel waveguide structure and are arranged in a one-dimensional manner. The optical vector-matrix multiplier realizes a multiplication between a matrix M*N and a vectorN*1 by employing the integrated optical mode, wherein elements in the matrix and the vector are all binary numbers (0 or 1) and M and N are natural numbers. The integrated optical vector-matrix multiplier based on the micro-ring resonators is high in integrated level, good in scalability and convenient in integration with electric elements, and enables to raise information transfer rates, reduce information transfer delays, avoid disadvantages of poor precision and weak programmable ability of analog optical computing systems and solve the problem of low space diversity efficiency of traditional optical vector-matrix multiplier.

Owner:HUAWEI TECH CO LTD

Reconfigurable matrix multiplier architecture and extended borrow parallel counter and small-multiplier circuits

InactiveUS20050240646A1Many solutionsEfficient mergeComputation using non-contact making devicesNumber-of-one countersBinary multiplierParallel computing

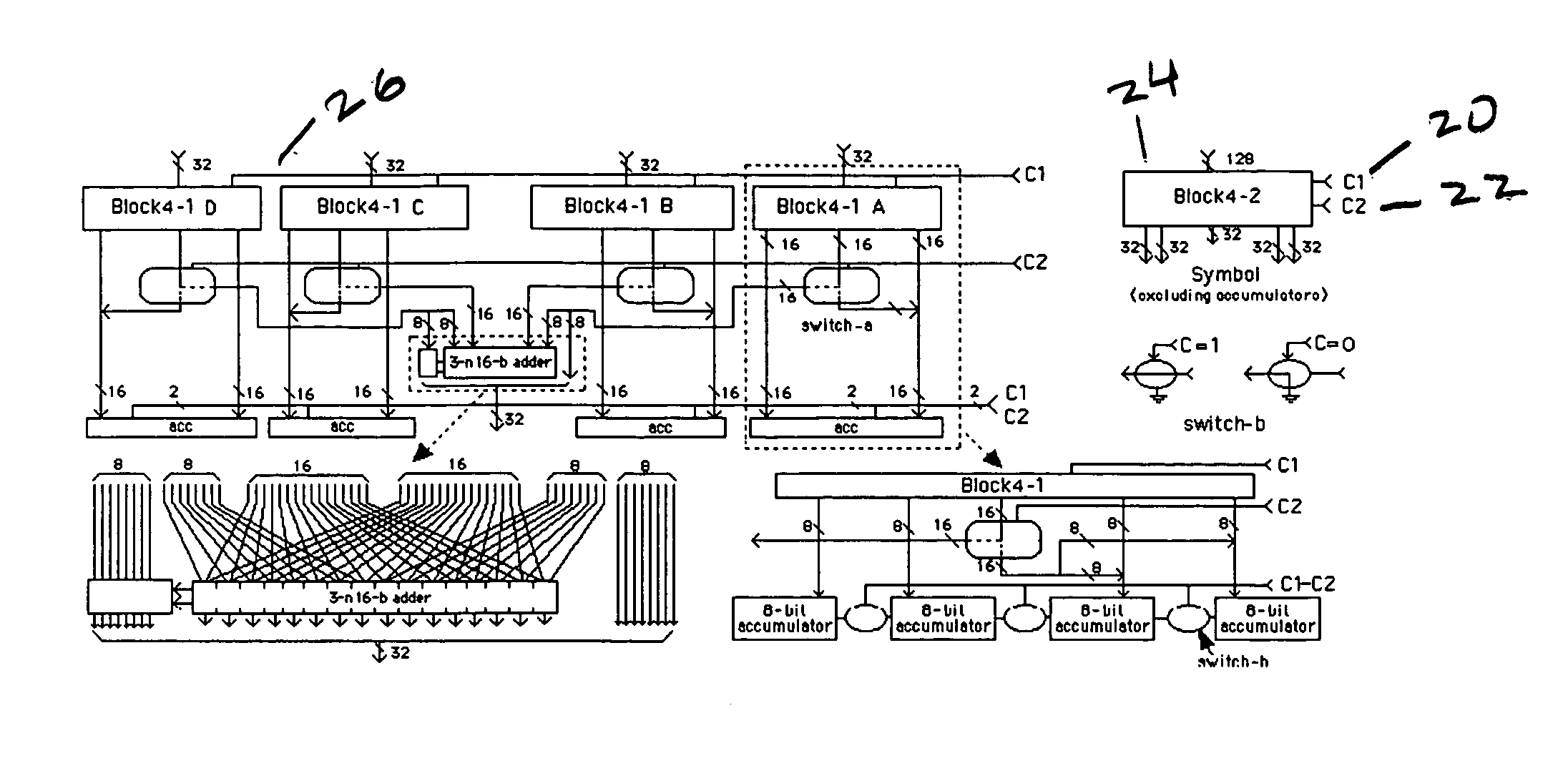

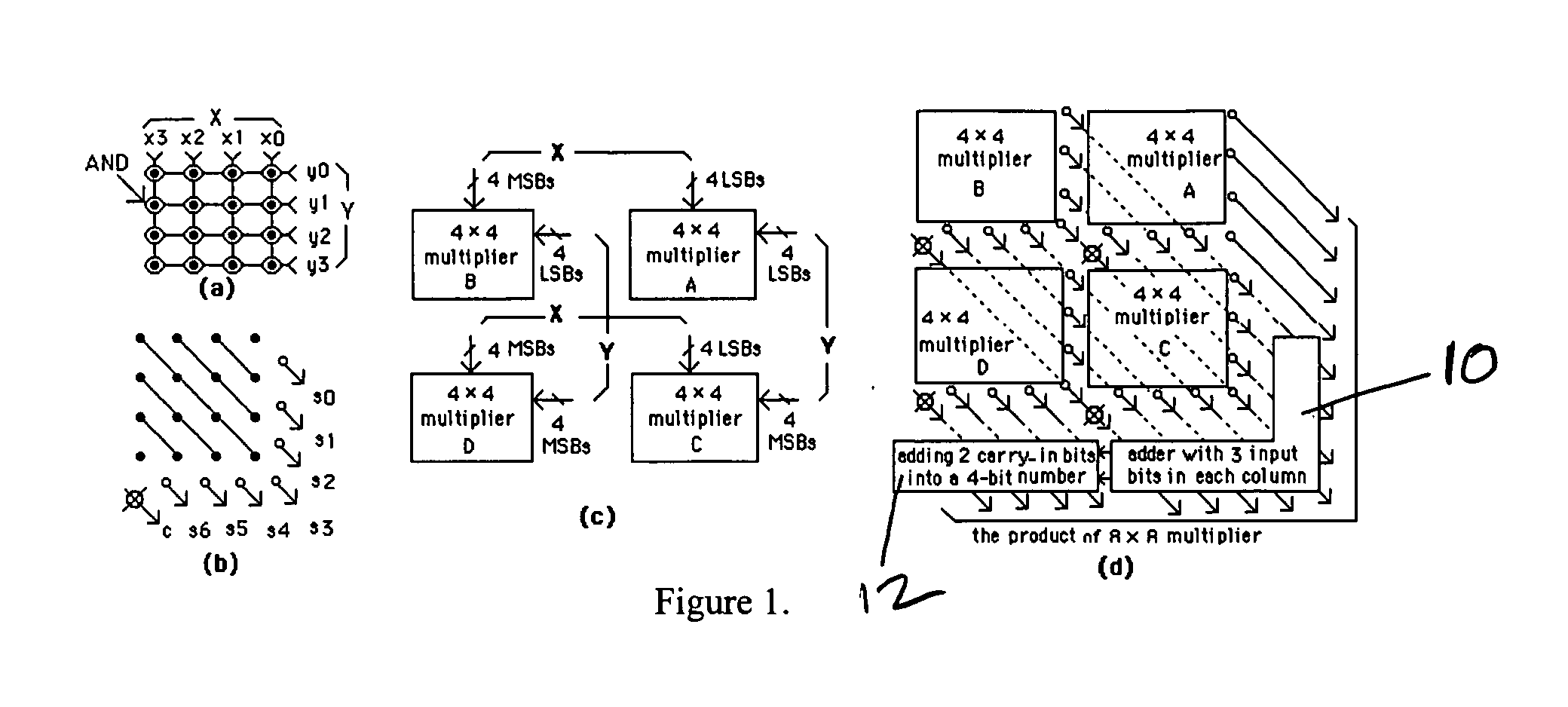

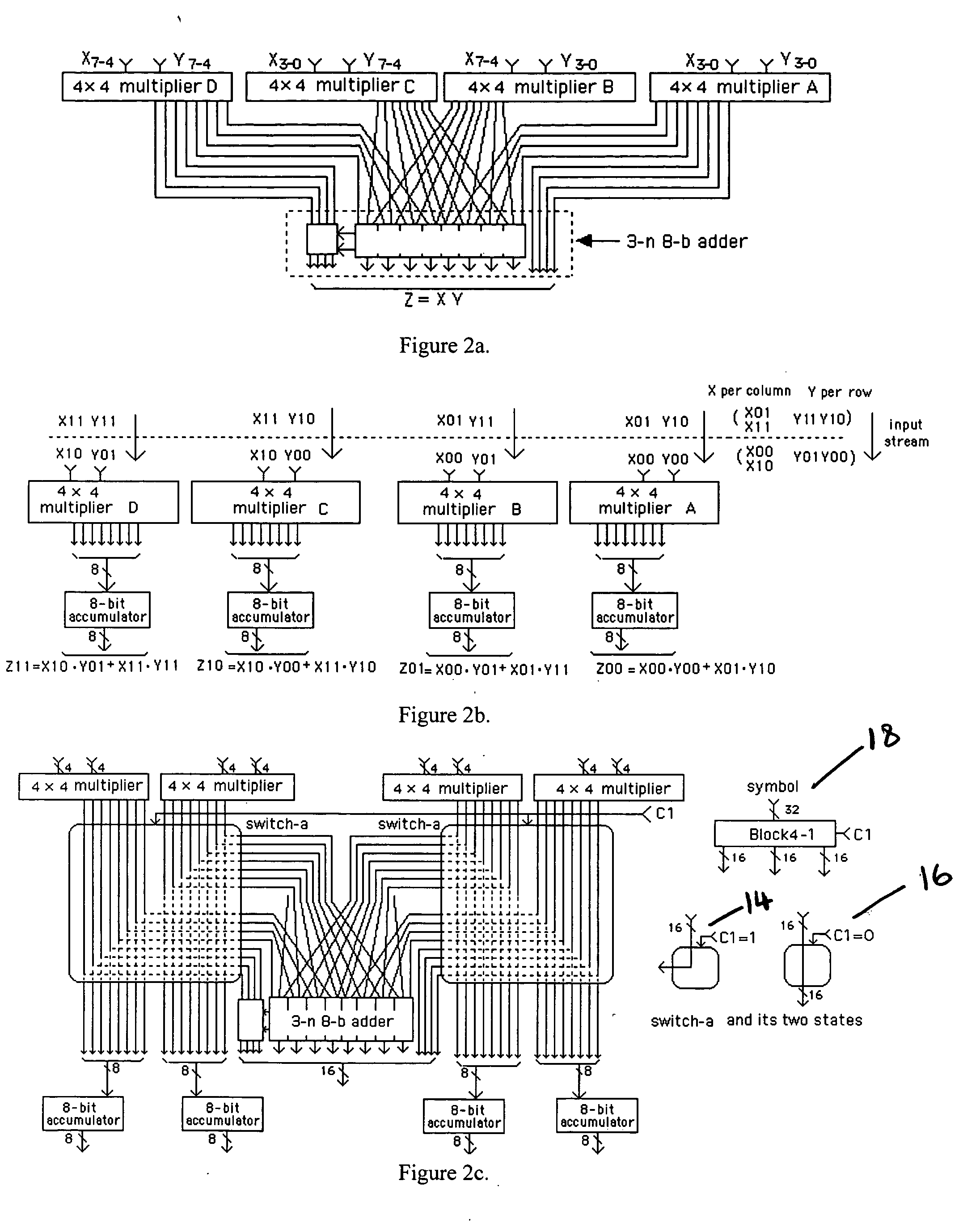

A dynamically or run-time reconfigurable matrix multiplier architecture with a reconfiguration mechanism for computing the product of matrices Xp×r and Yr×q for any integers p, q, r and any item precision b, i.e., bitwidth, ranging from 4 to 64 bits is described. The reconfigurable matrix multiplier uses borrow parallel counters with new circuits, 6—0, and 6—1 and the improved small multiplier library. The reconfigurable matrix multiplier architecture is based on a novel scheme of trading data bitwidth for processing array or matrix size. The matrix multiplier achieves an extra compact, low power, high speed design through the use of a borrow parallel counters and a library of small borrow parallel multiplier circuits. The matrix multiplying processor using area comparable with a single 64×64-b multiplier constructed of very large-scale integrated (VLSI) circuits, can be reconfigured to produce the product of two matrices X(4×4) and Y(4×4) of 8, 16, and 32-bit data items in every 1, 4, and 16 pipeline cycles, respectively, or the product of two 64-b numbers in every pipeline cycle.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

Matrix multiplier

ActiveCN109992743AImprove efficiencyGood application effectComputation using non-contact making devicesComplex mathematical operationsParallel computingMatrix multiplier

The embodiment of the invention discloses a matrix multiplier, relates to the technical field of data calculation, and aims to perform block calculation on two matrixes. The matrix multiplier includes: a first memory, a second memory, an operational circuit and a controller, wherein the operational circuit can be in data communication with the first memory and the second memory through a bus; andthe controller is used for controlling the first matrix and the second matrix to separate; according to a preset program or an instruction, and controlling the operation circuit to multiply the corresponding blocks in the first memory and the second memory according to the dividing result of the controller. The matrix multiplier can be used for carrying out multiplication operation on two matrixes.

Owner:HUAWEI TECH CO LTD

Image processing model establishing method and device and image processing method and system

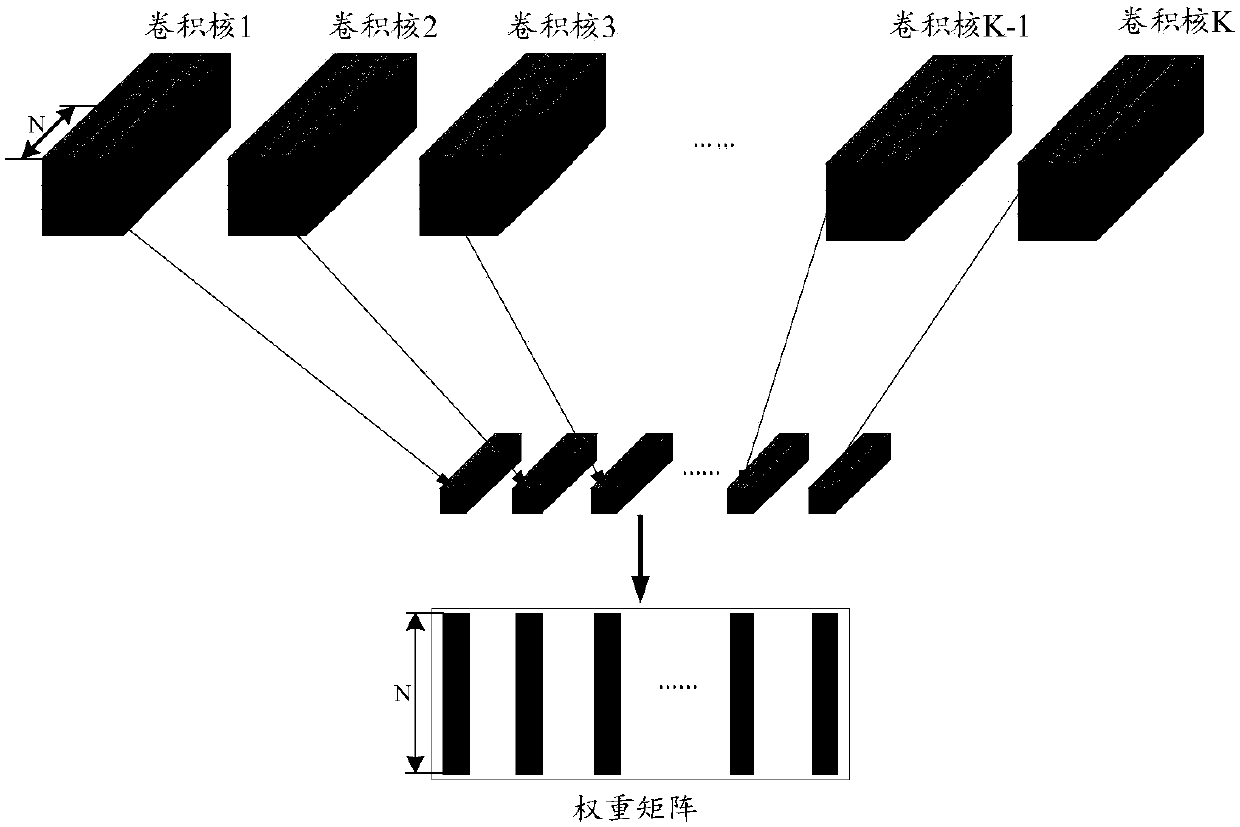

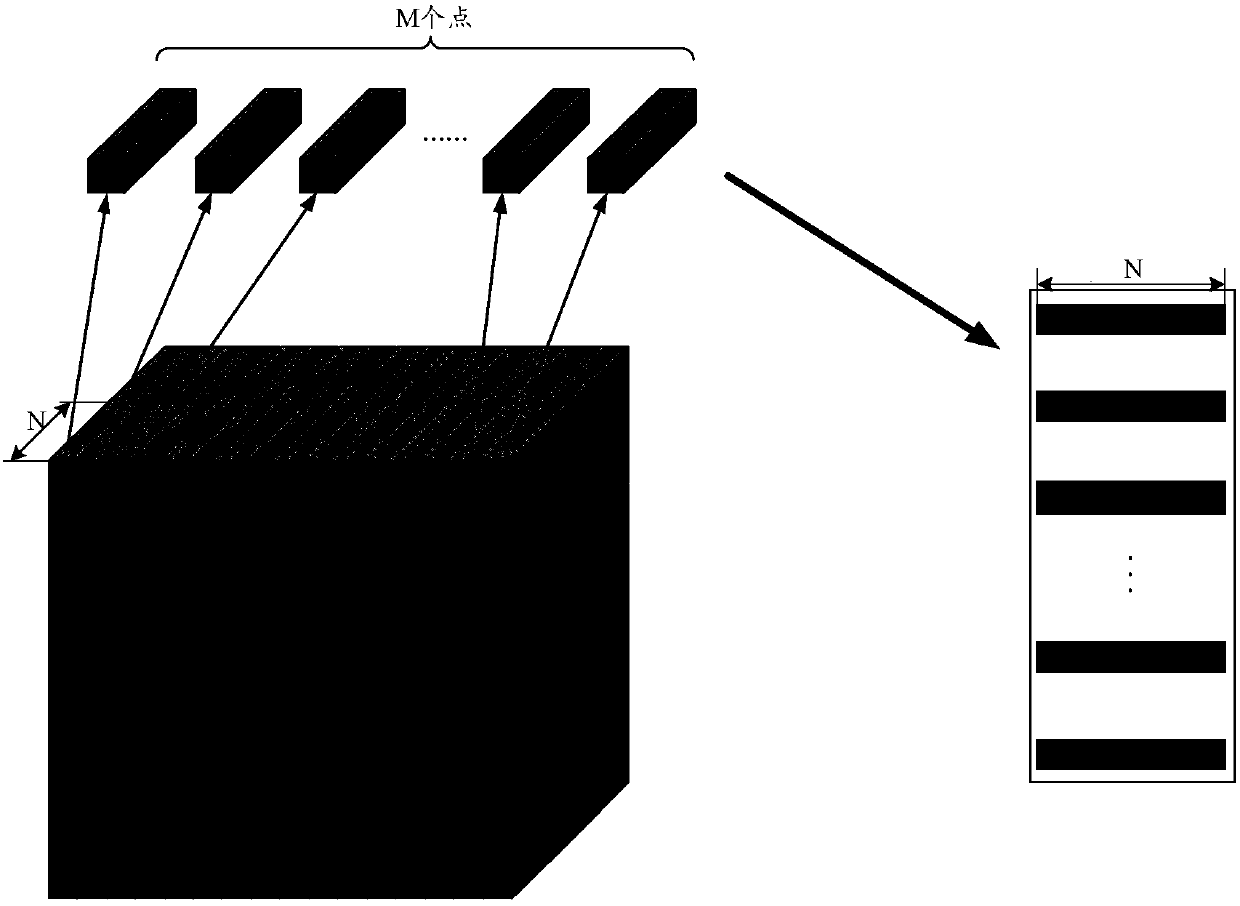

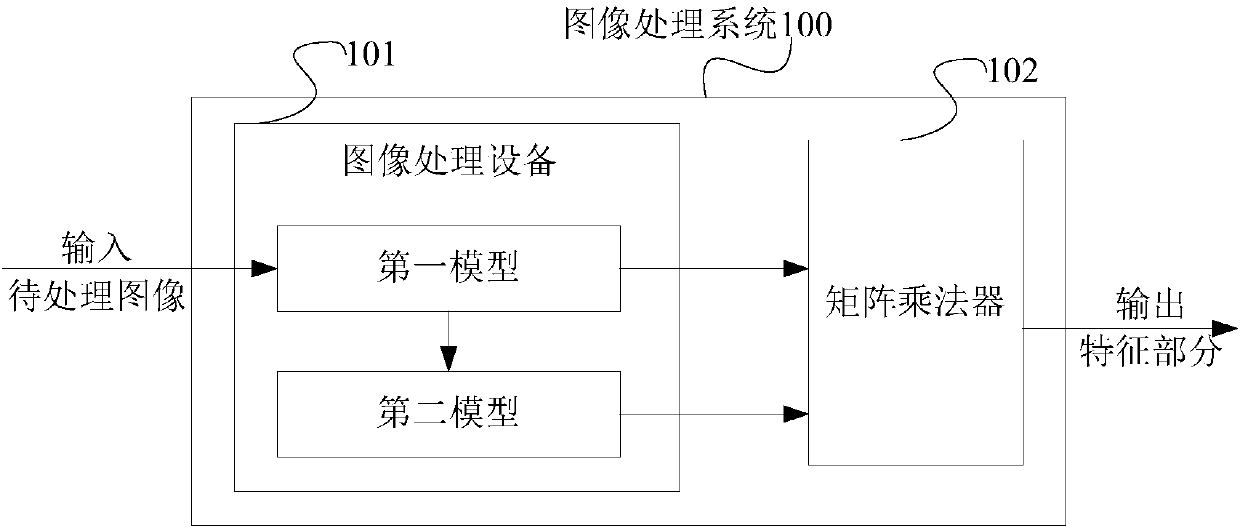

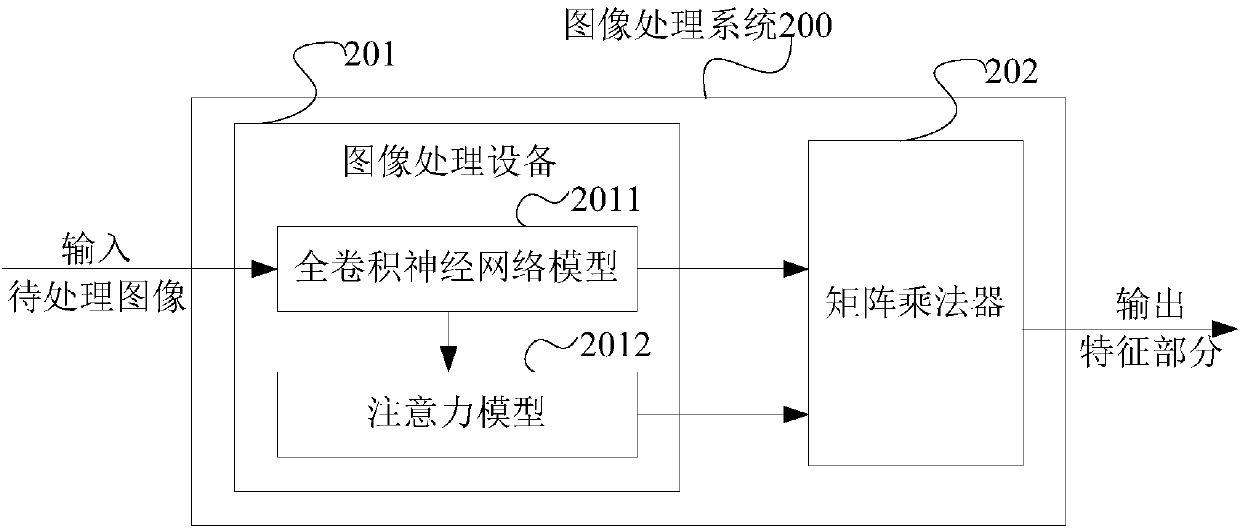

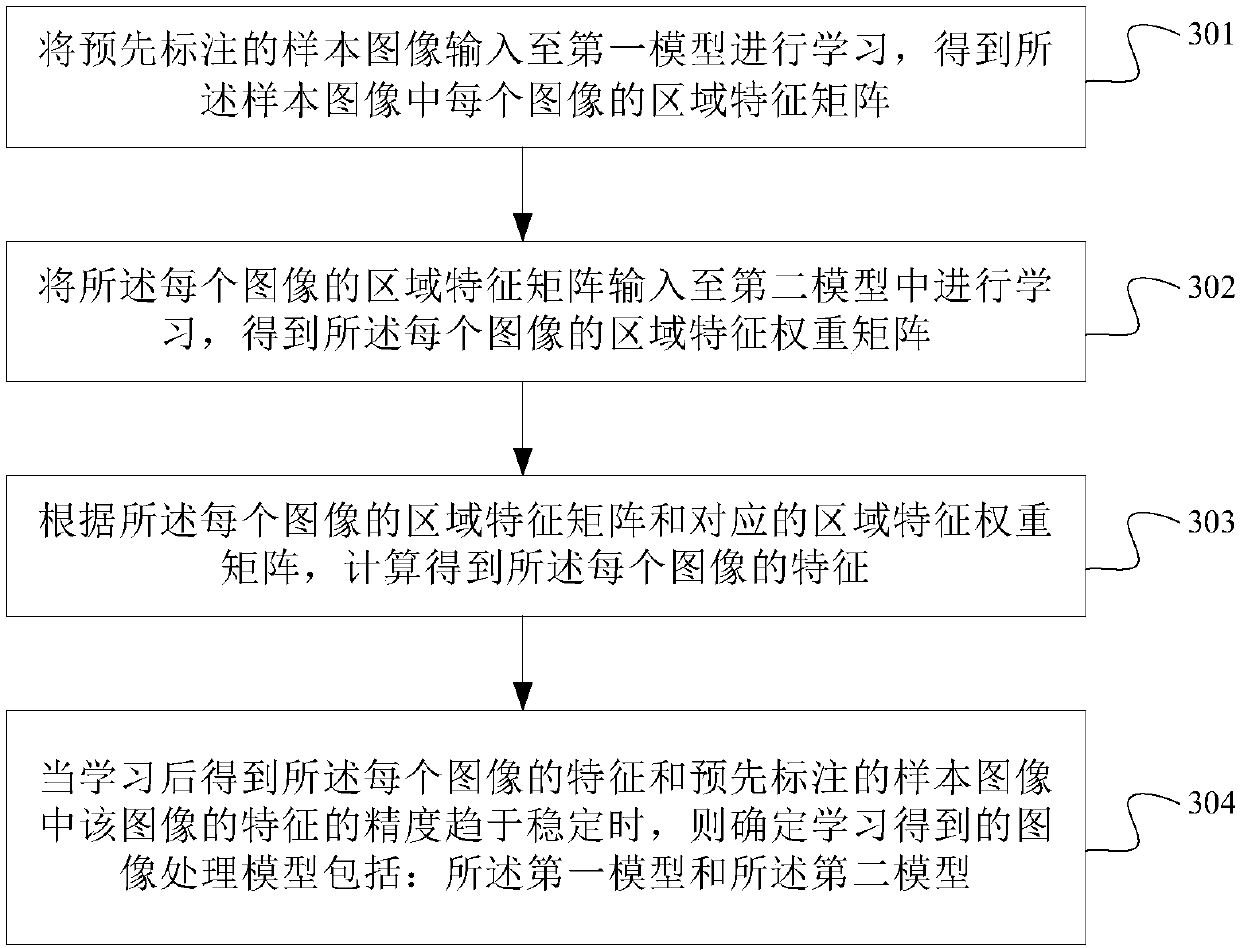

ActiveCN107729901AReduce labeling workloadImprove learning efficiencyCharacter and pattern recognitionManual annotationImaging processing

The invention provides an image processing model establishing method and device and an image processing method and system, having consistent technical thoughts. The image processing system comprises image processing equipment and a matrix multiplying unit, wherein the image processing equipment is configured with a pre-established image processing model; the image processing model comprises a first model and a second model; the image processing equipment is used for processing a to-be-processed image through the image processing model so as to obtain a regional feature matrix and a regional feature weight matrix of the to-be-processed image; and the matrix multiplying unit is used for multiplying the regional feature matrix of the to-be-processed image by the regional feature weight matrixso as to obtain features of the to-be-processed image. The image processing system is capable of rapidly realizing the end-to-end feature extraction from images to features, and through the image processing model establishing process, sample capacity demand is greatly decreased, so that the manual annotation cost in the early stage is decreased.

Owner:ALIBABA GRP HLDG LTD

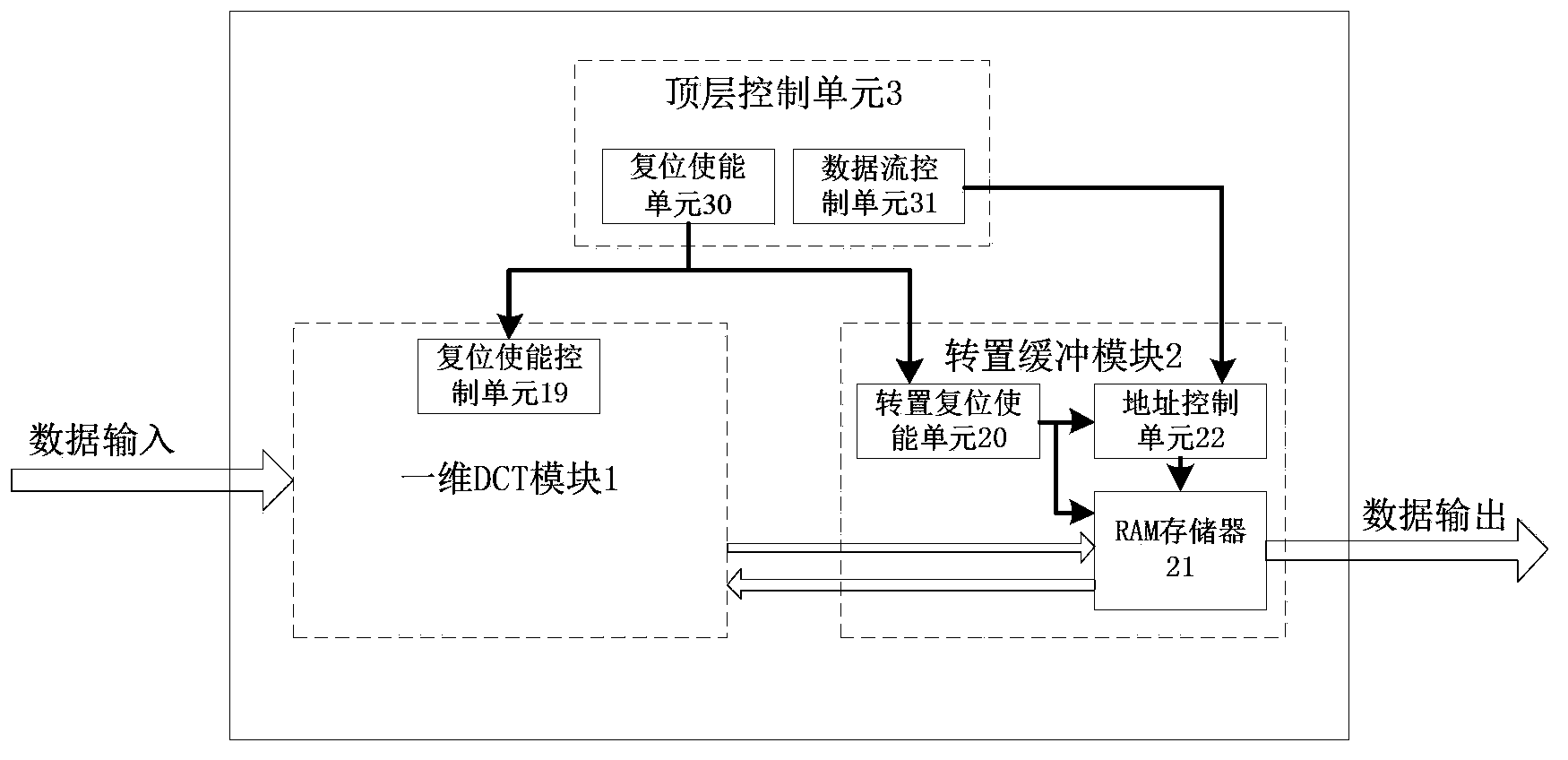

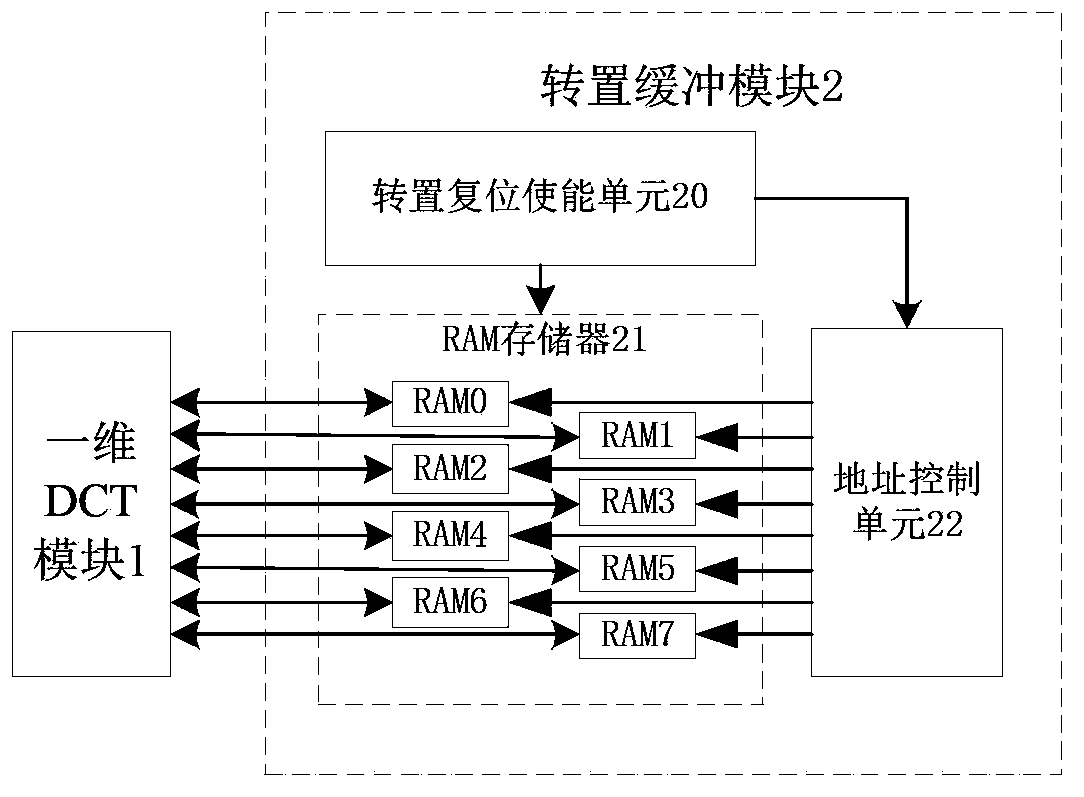

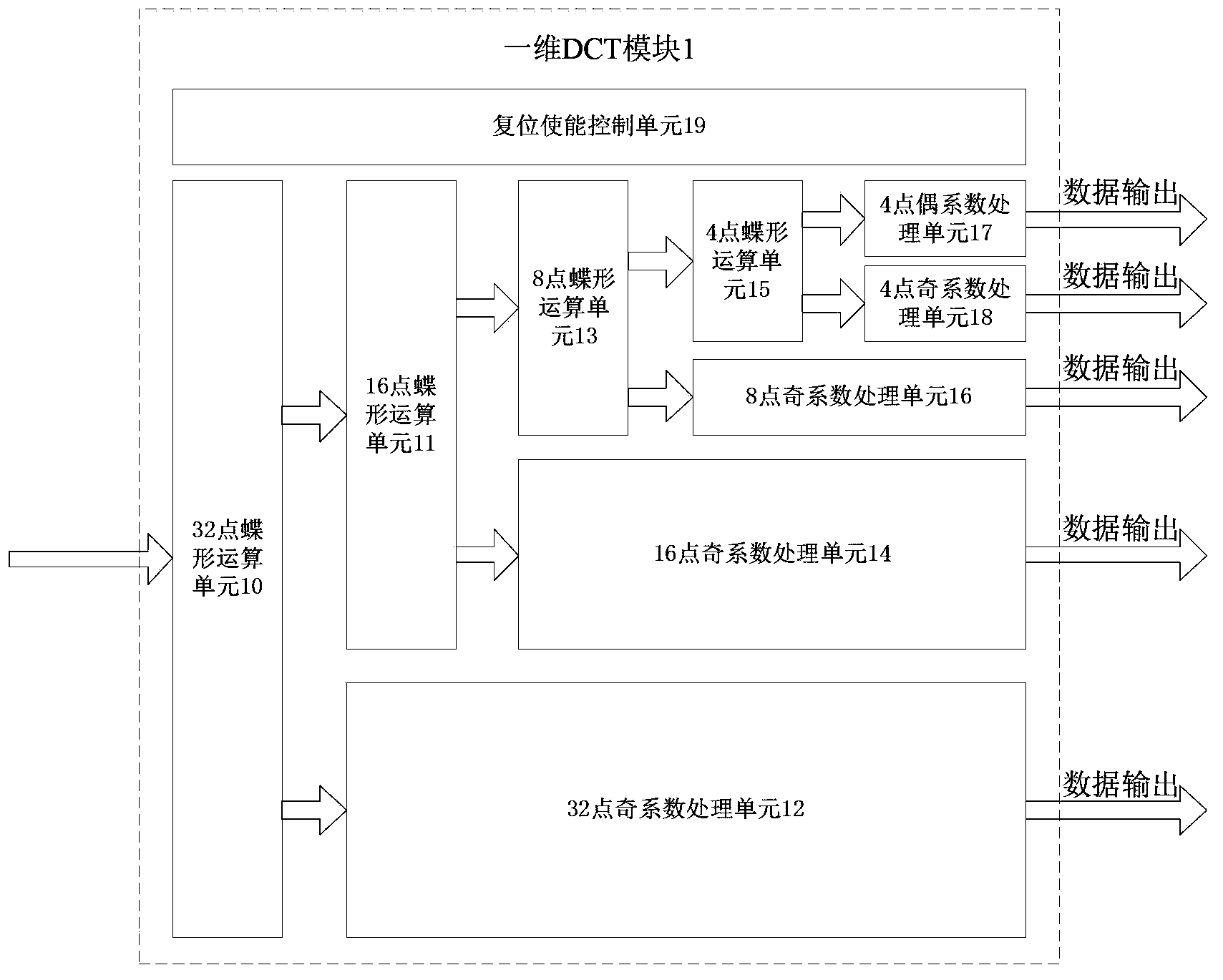

Transition coder applicable to HEVC ( high efficiency video coding) standards

The invention discloses a transition coder applicable to HEVC ( high efficiency video coding) standards and mainly solves the problems of multiple use of multipliers and a complicated circuit in the prior art. The transition coder comprises a one-dimensional DCT (discrete cosine transformation) module (1), a transposition buffer module (2) and a top layer control module (3), wherein the one-dimensional DCT module (1) adopts a plurality of butterfly computing units and a plurality of odd coefficient processing units for completing each DCT in the HEVC standards, the odd coefficient processing units resolve the complicated multiply operation into multistage circuits and adopt a shifter, an adding device and a subtracter, i.e. the multistage shifter, the adding device and the subtracter are used for replacing a matrix multiplier, and the circuit structure is simplified. The transition coder has the advantages that the structure is simple and regular, the reusability is high, the key route is short, the lock frequency is high, and the integration is easy. The transition coding on video residual data is efficiently realized under the condition of not using the multipliers.

Owner:XIDIAN UNIV

Systems and methods for programming large-scale field-programmable analog arrays

ActiveUS7439764B2Good flexibilitySolid-state devicesLogic circuits using elementary logic circuit componentsTransistor arrayCapacitance

Owner:GEORGIA TECH RES CORP

Matrix multiplication calculation method and device

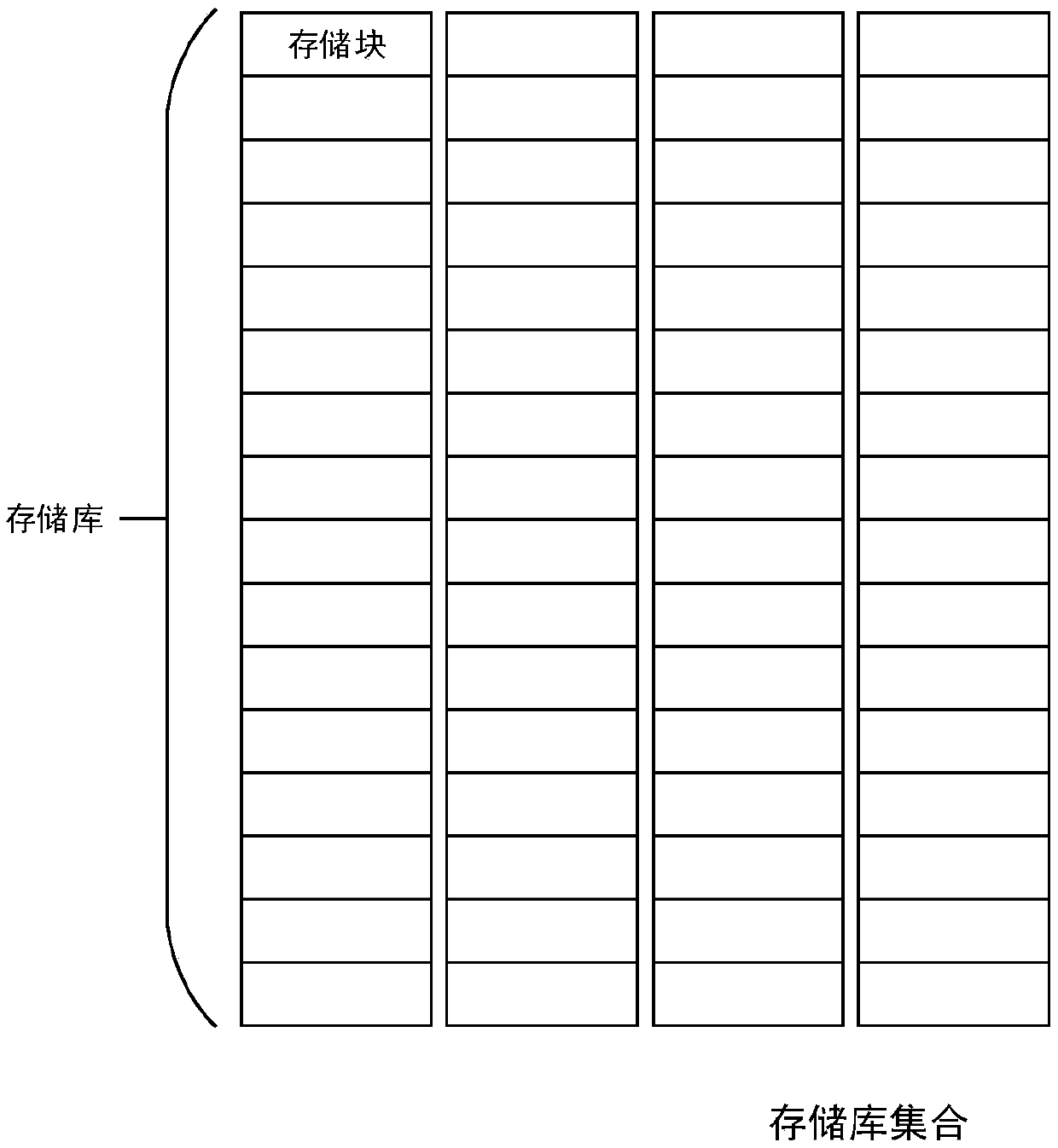

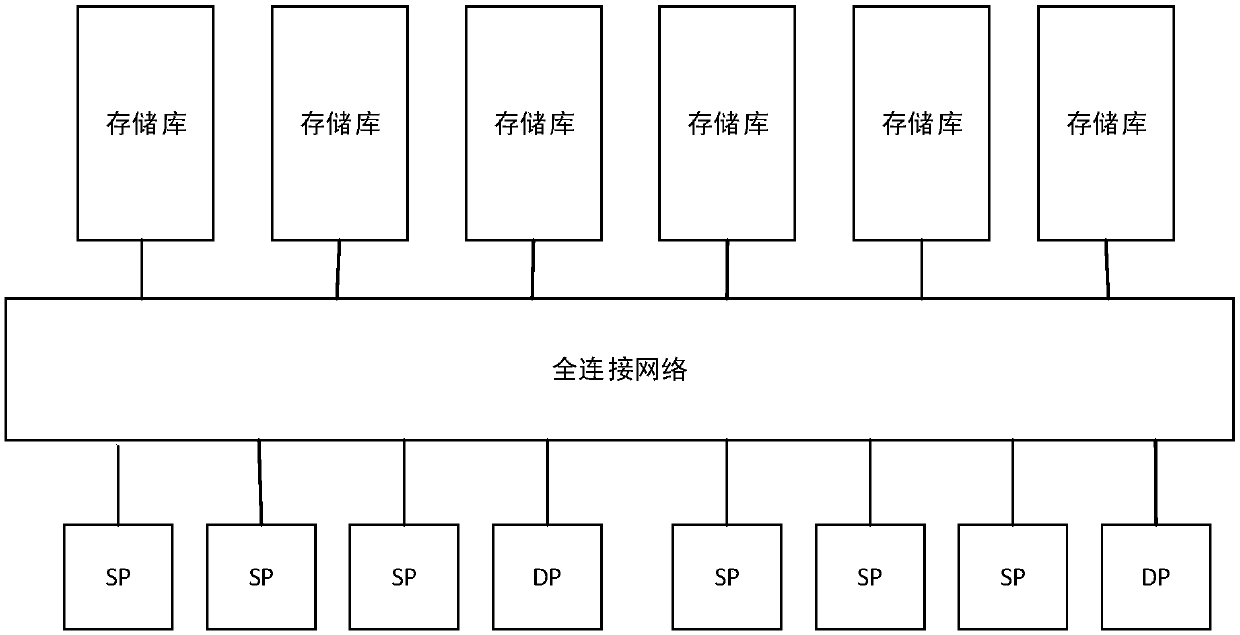

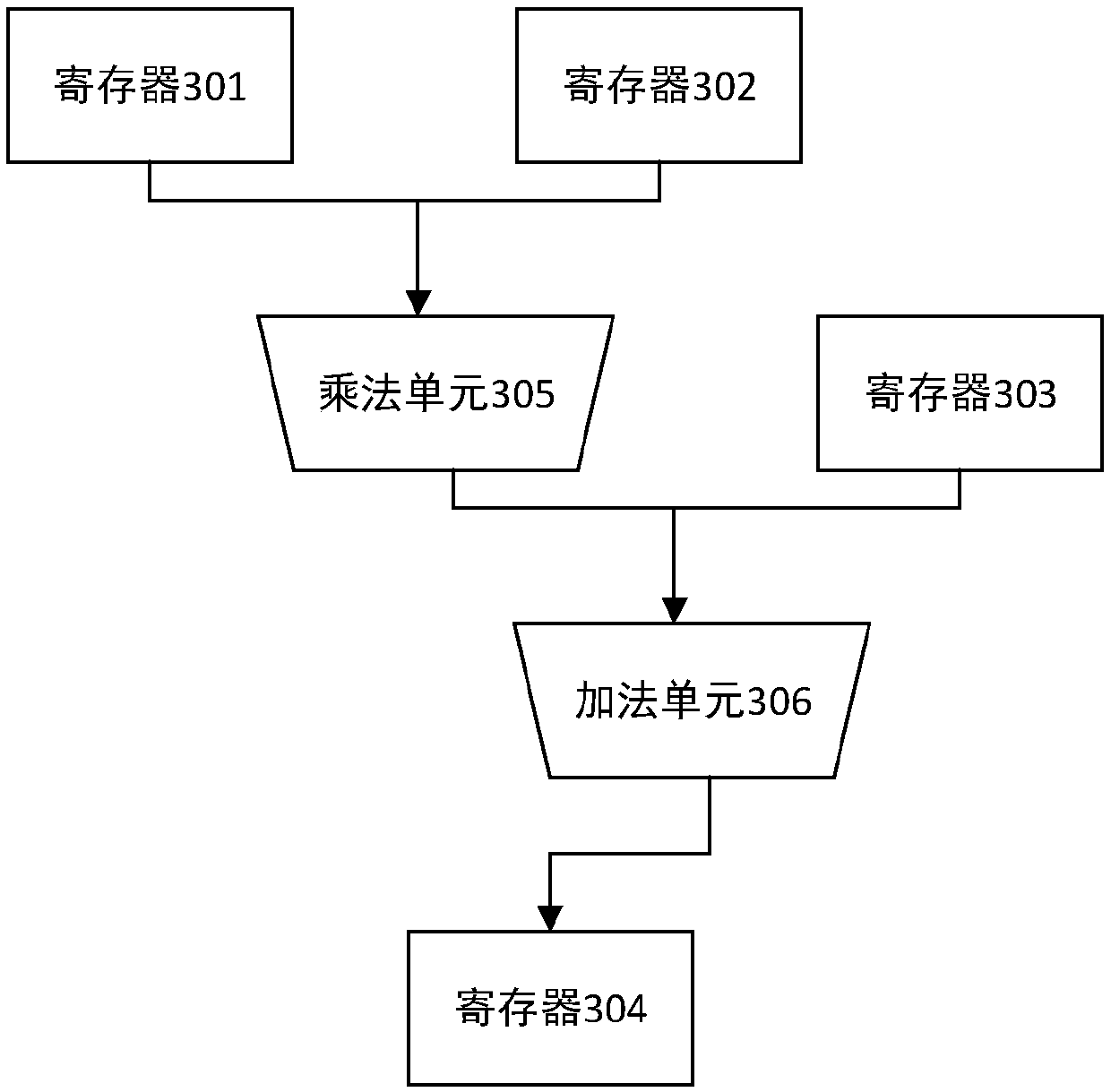

PendingCN110415157AImprove the efficiency of matrix multiplication calculationsFew stepsProcessor architectures/configurationComplex mathematical operationsGraphicsMemory bank

The invention provides a matrix multiplier. A full-connection network contained in an existing matrix multiplier occupies a large chip space, and a large number of storage accesses are needed during matrix multiplication calculation, so that the matrix multiplication calculation efficiency of a stream multiprocessor is low. The objective of the invention is to improve the matrix multiplication calculation efficiency of a graphics processor. According to the matrix multiplier provided by the invention, when matrix multiplication is carried out, by utilizing the characteristic that different groups of memory banks can be accessed at the same time, one row of elements of the matrix serving as the multiplicand and one column of elements of the matrix serving as the multiplier are loaded into corresponding calculation units each time, and calculation is carried out at the same time. By using the matrix multiplier, the steps required for completing matrix multiplication calculation can be reduced, and the frequency of storage access required to be performed is reduced, so that the matrix multiplication calculation efficiency of the graphics processor is improved.

Owner:HUAWEI TECH CO LTD

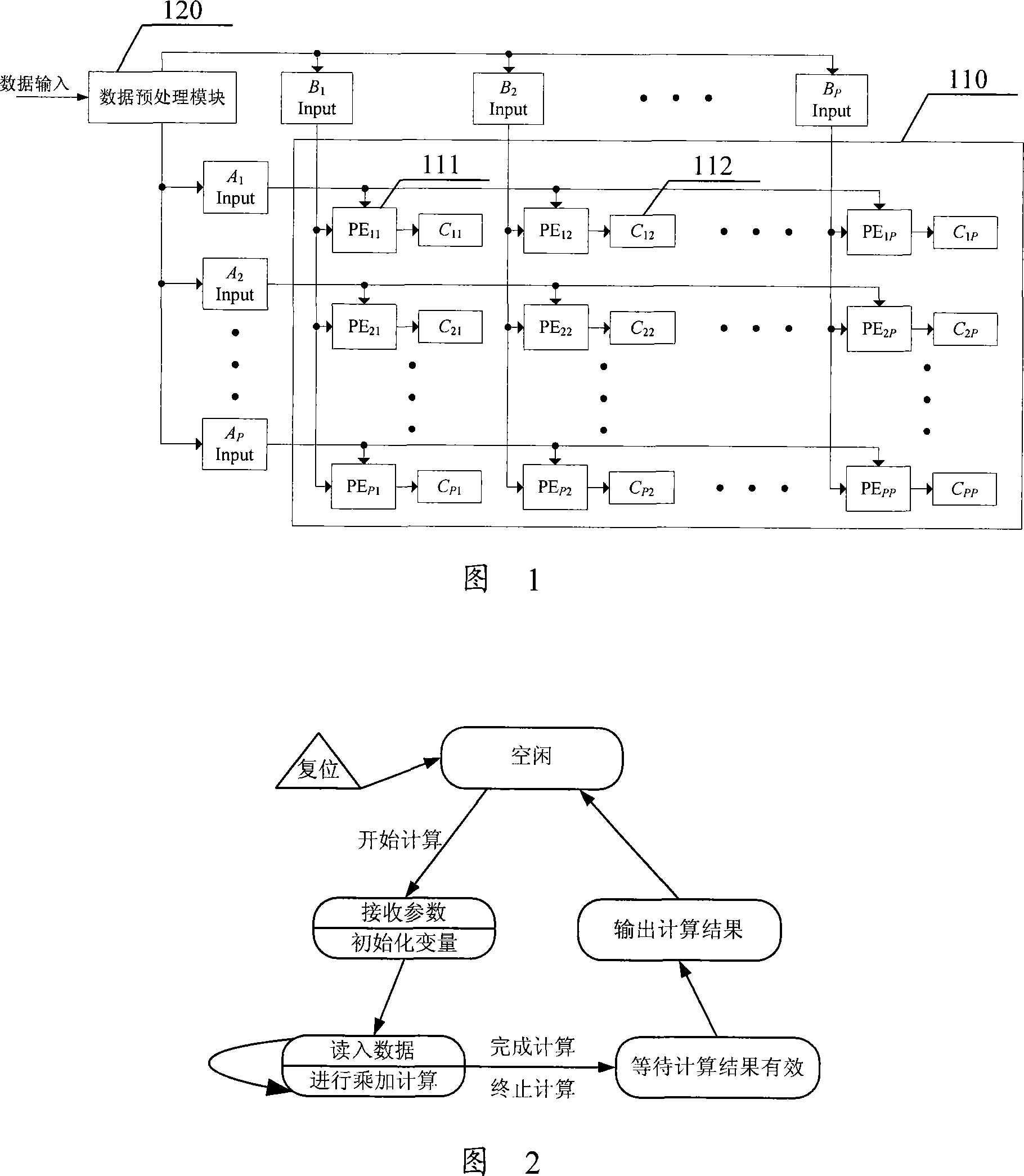

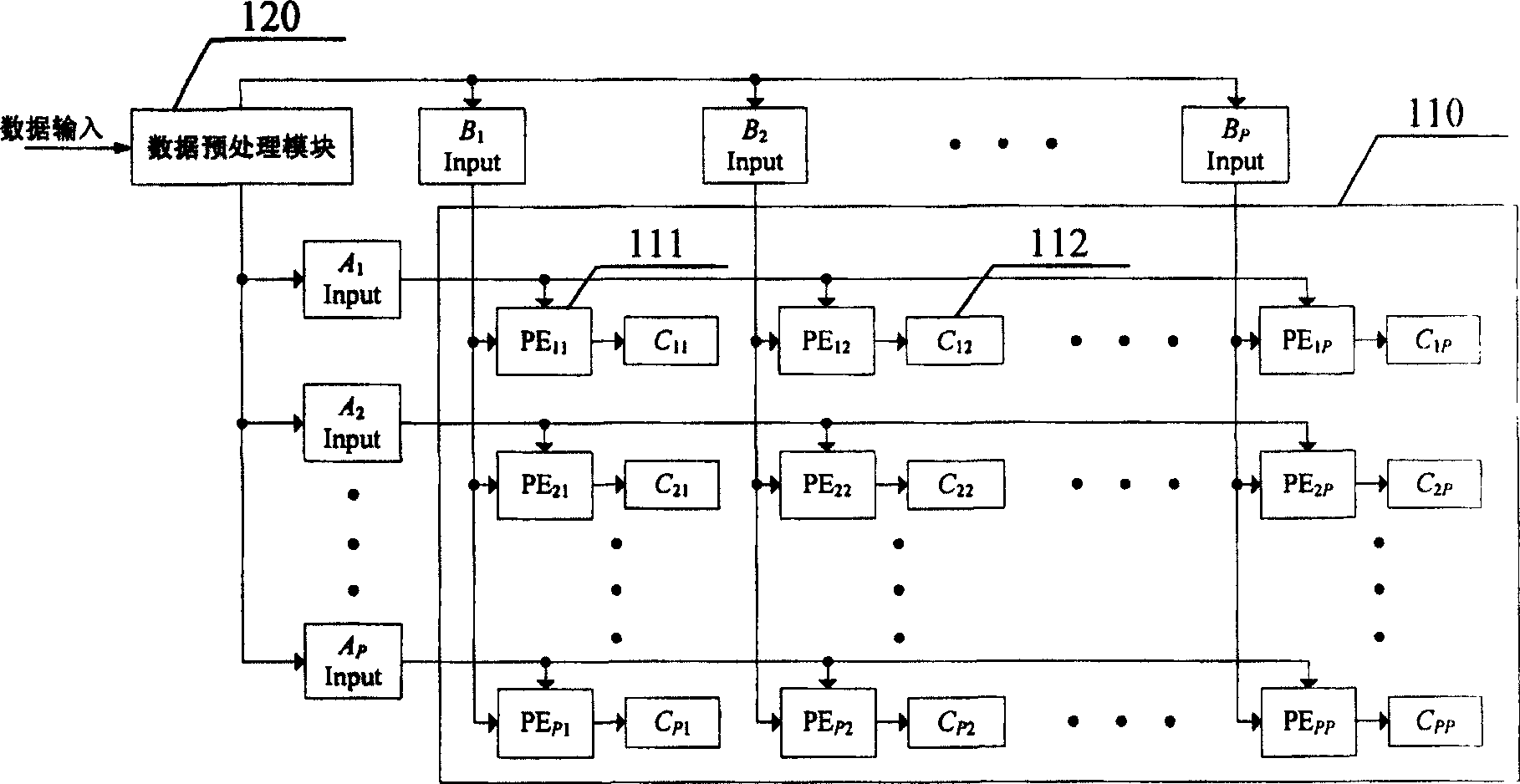

Matrix multiplier device based on single FPGA

The invention relates to a single FPGA matrix multiplication device that comprises P2 PEs formed in P row and P column matrix, data input and output interface and data pre processing unit. It can manage dense matrix and loose matrix multiplication with improvement in computing performance. It also relates to a matrix multiplication device based on FPGA.

Owner:ZHEJIANG UNIV

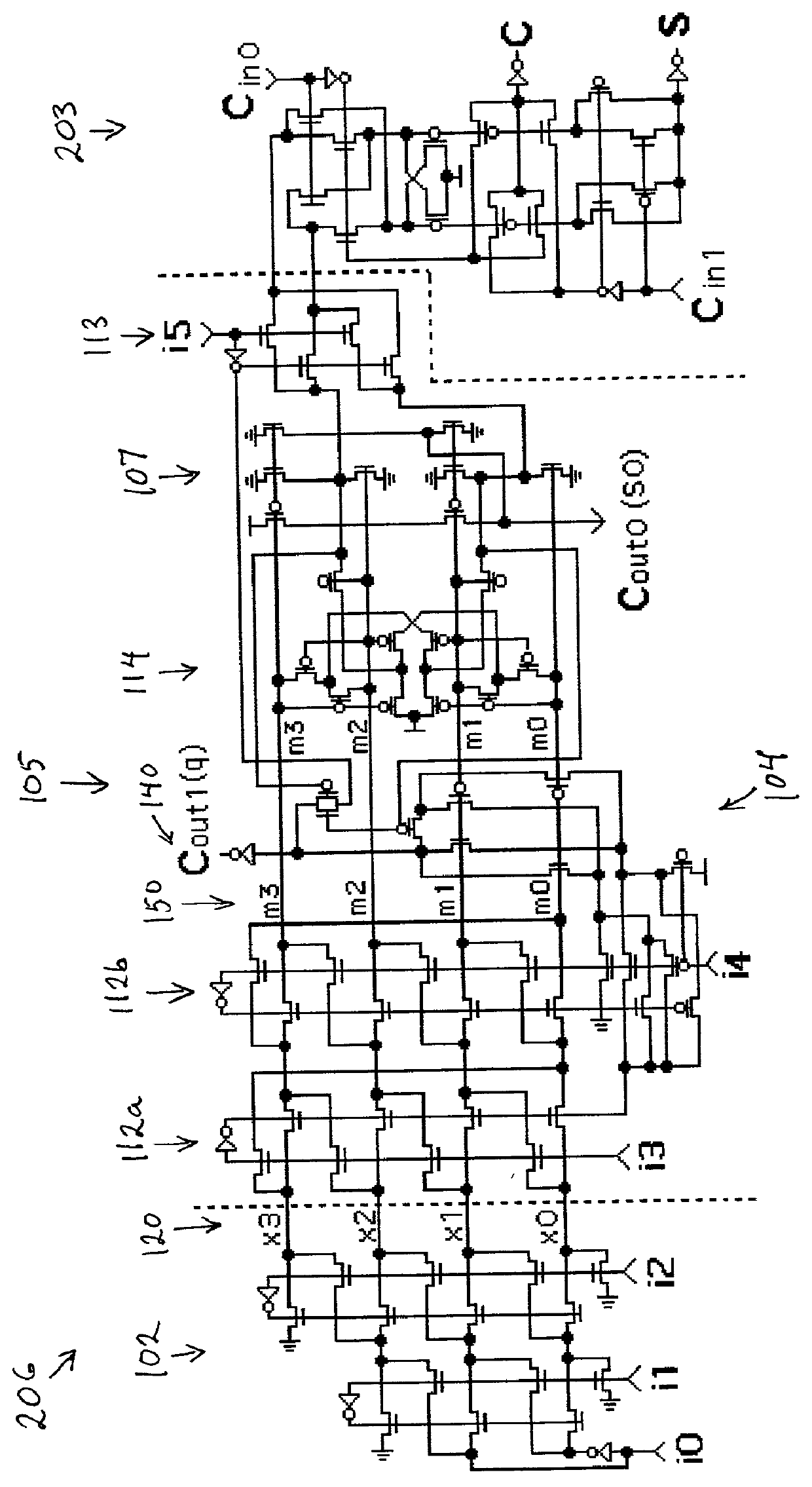

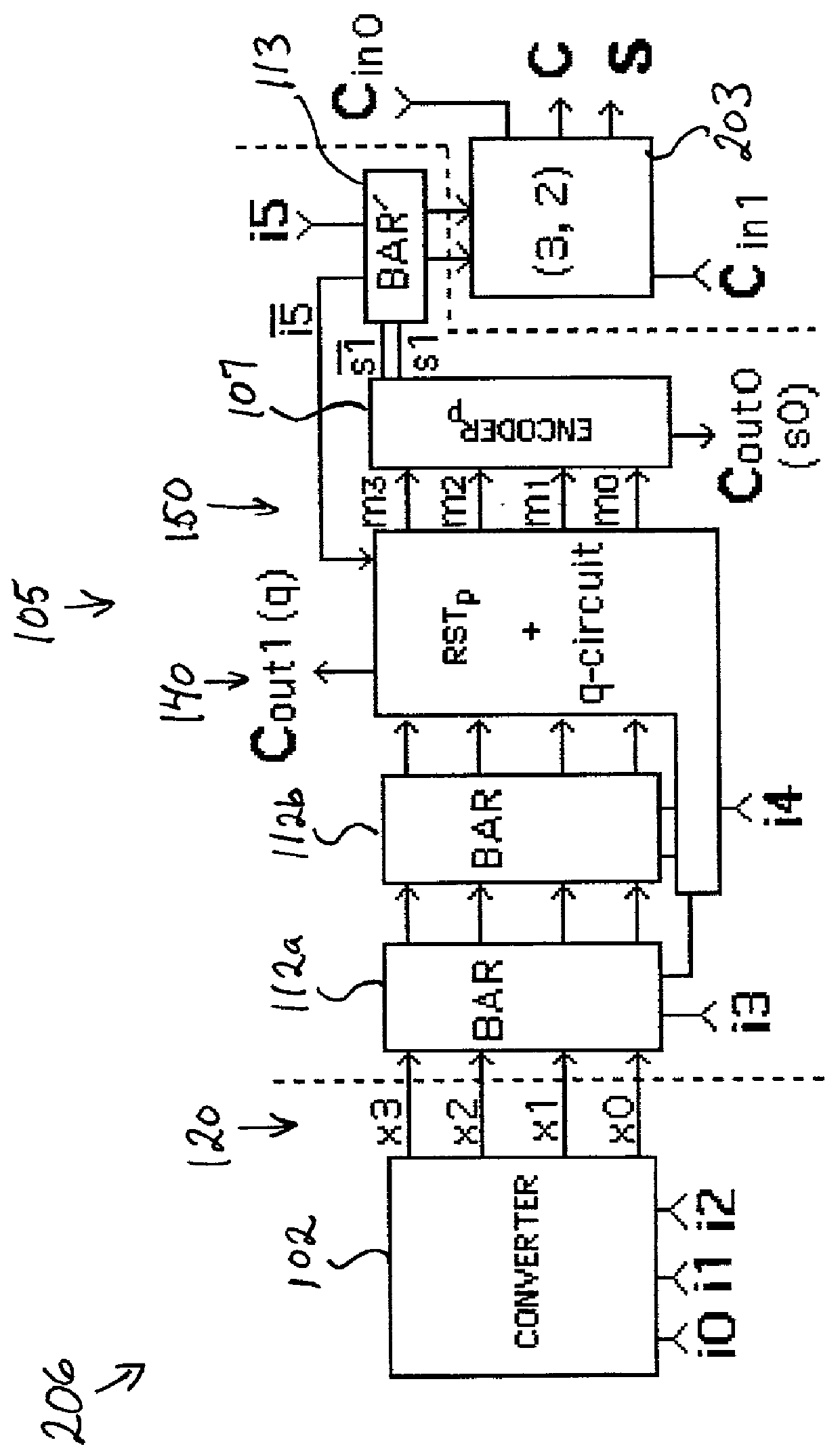

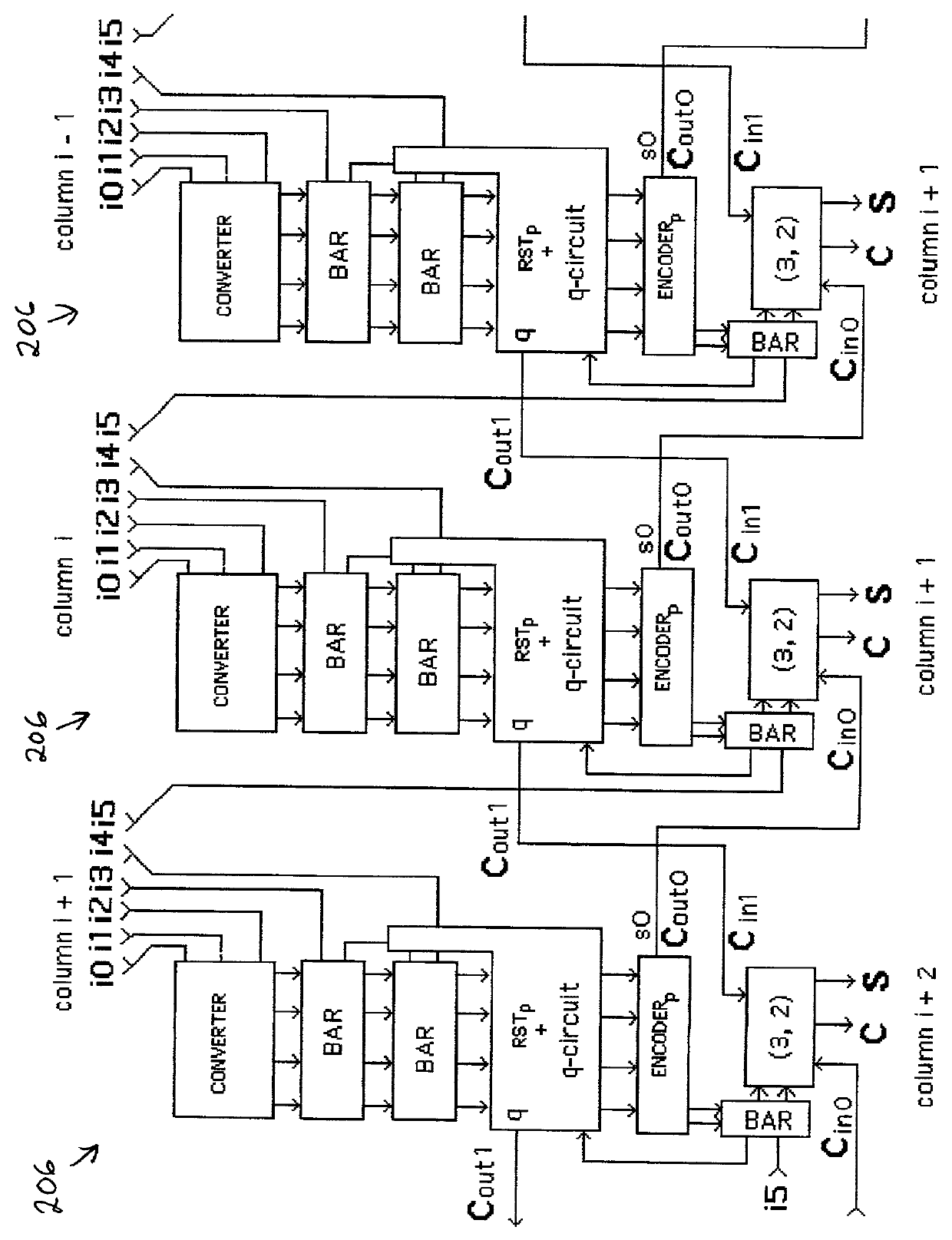

Family of low power, regularly structured multipliers and matrix multipliers

InactiveUS20010056455A1Computation using non-contact making devicesNumber-of-one countersCircuit complexityPartial product reduction

A family of embodiments of a new class of CMOS VLSI computer multiplier circuits that are simpler to fabricate, smaller, faster, more efficient in their use of power, and easier to scale in size than the prior art. The normal binary adder circuit unit is replaced by the innovative shift switch circuit unit. Use of the shift switch circuit sharply reduces fluctuations of power caused by plurality variations in the bit representations of the input, intermediate and output numbers. Reduced-scale devices are used in shift-switch pass-transistor signal restoration circuits, significantly reducing the size, power demand, and power dissipation of internal circuitry, in contrast to ordinary multiplier design. The simplicity of the circuit design allows multiplier partial-product reduction in fewer logic stages than existing comparable designs allow, showing speed improvement over such designs. The circuit design simplicity and the use of reduced-scale devices require less VLSI area than existing designs need, facilitating integration in VLSI microprocessors. Modular circuit organization simplifies scaling for larger operands without the circuit complications of existing designs. The design includes a critical flip of the physical layout of the partial-product matrix at each size level, simplifying the layout of traces in the circuit at all size scales. Finally, the application of reconfigurable design principles to the easily-scaled layout reduces significantly the mean demand for computing resources over a wide range of multiplication bit-width scales, as compared to existing designs. Overall, the orchestrated integration of these diverse design innovations makes possible the implementation of simpler, faster, smaller, more efficient, more flexible, and easier-to-build VLSI multiplication circuits than the current art reveals.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

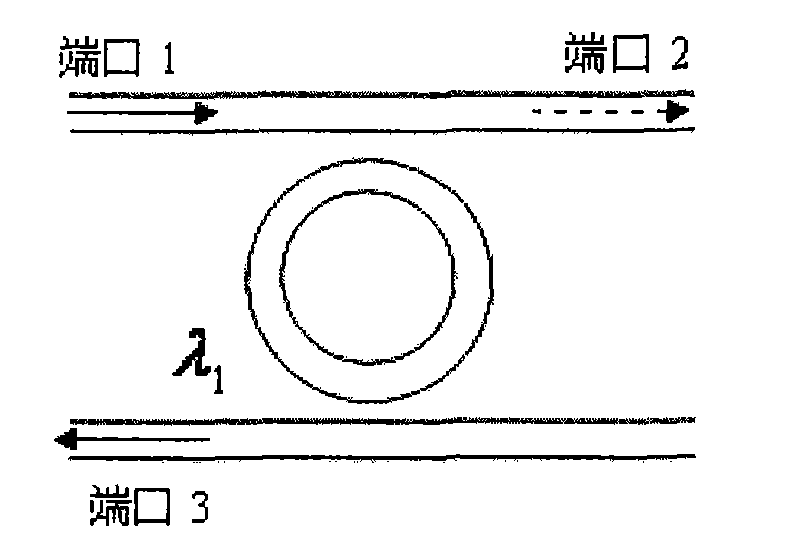

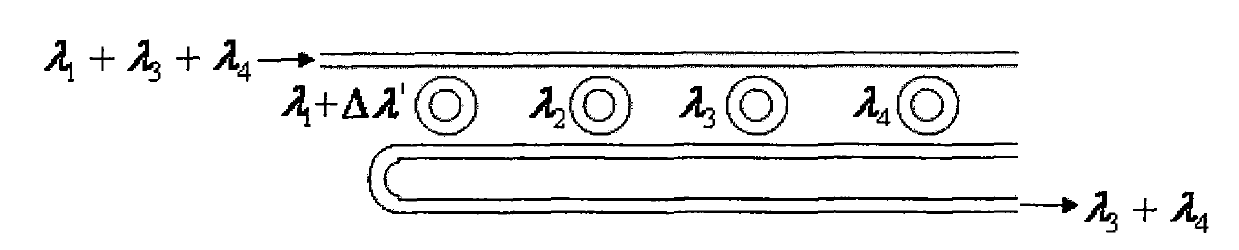

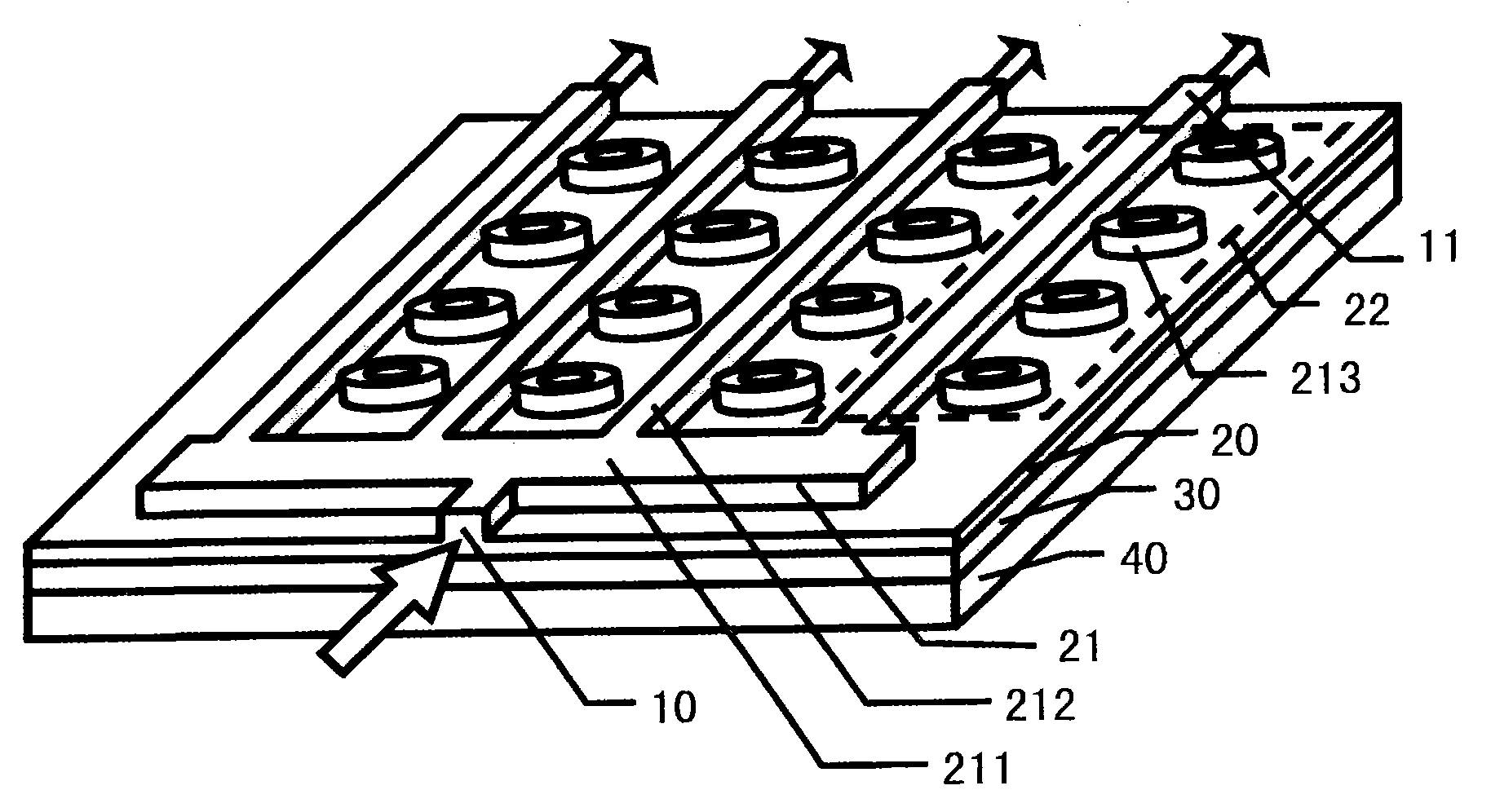

Optical vector-matrix multiplier based on single-waveguide coupling micro-ring resonant cavity

ActiveCN102147634AAvoid designSimple designLogic circuits using opto-electronic devicesComputation using denominational number representationResonant cavityMatrix multiplier

The invention discloses an optical vector-matrix multiplier based on a single-waveguide coupling micro-ring resonant cavity, which comprises a substrate, a buried layer and a top layer, wherein the buried layer is manufactured on the substrate; the top layer is manufactured on the buried layer; a comb structure is etched on the top layer; the comb structure comprises a back part and a tooth part; tunable micro-ring resonant cavities are etched in the side direction of the tooth part; each tooth of the tooth part is coupled with the plurality of adjacent tunable micro-ring resonant cavities to form a cascaded multi-wavelength modulator; an input end of an optical signal is formed in the centre of the back part of the comb structure; and an output end of the optical signal is formed at the tail part of the tooth part of the comb structure.

Owner:宏芯科技(泉州)有限公司

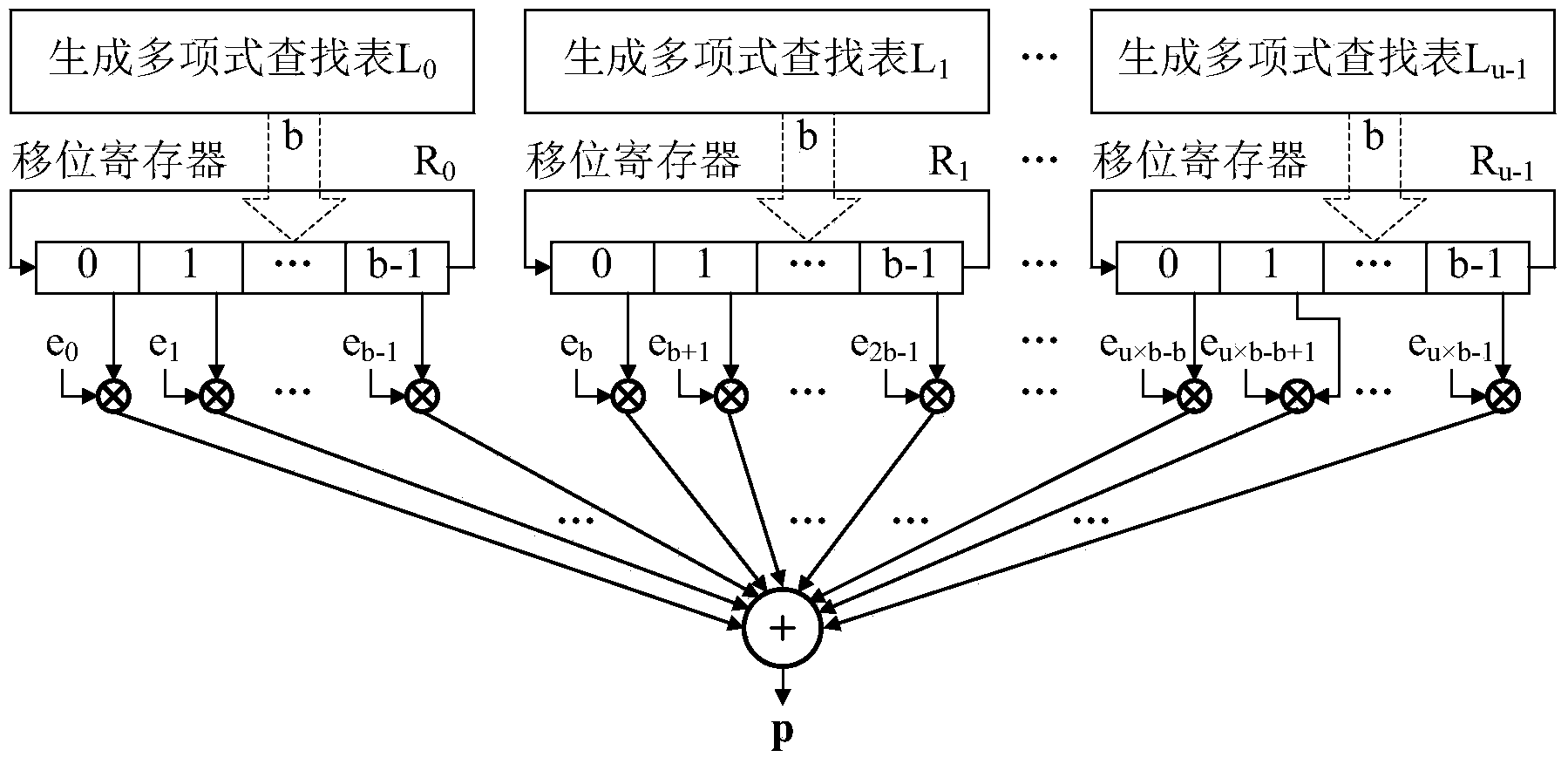

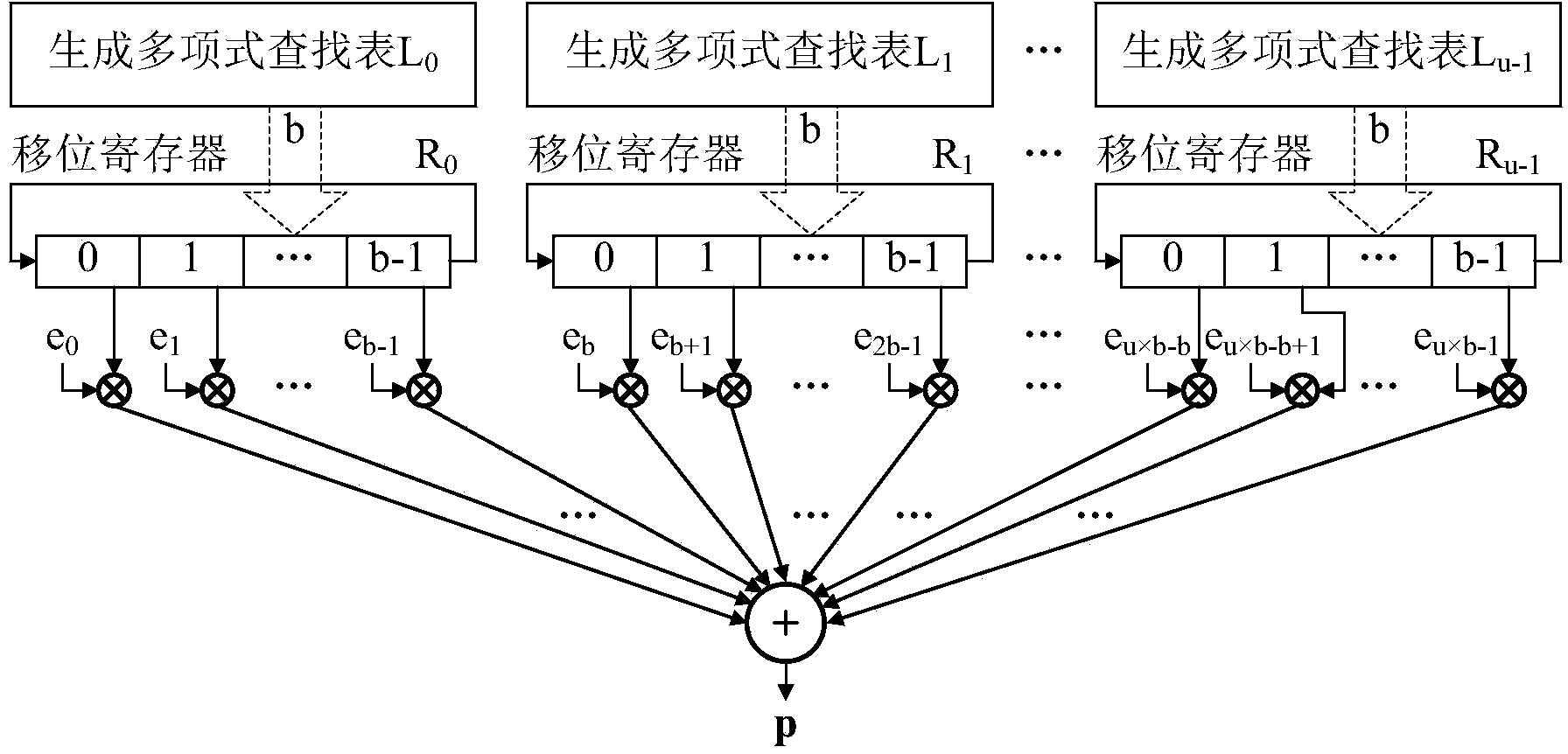

ROL quasi-cyclic matrix multiplier for full parallel input in WPAN

InactiveCN103902509ASimple structureReduce registerComputation using non-contact making devicesComplex mathematical operationsShift registerBinary multiplier

The invention provides an ROL quasi-cyclic matrix multiplier for full parallel input in a WPAN. The multiplier is used for multiplication of a vector m and a quasi-cyclic matrix F in standard QC-LDPC approximate triangle coding of the WPAN. The multiplier comprises two generating polynomial lookup tables for pre-storing all cyclic matrix cyclic generating polynomials in the matrix F, two 21-bit binary multipliers for performing scalar multiplication on the vector section and generating polynomial bits of the m, 21 three-bit binary adders for performing modulo-2 adding on content of a product sum shifting register and a 21-bit shifting register for storing the sum subjected to one-bit ROL. The multiplier for full parallel input is suitable for QC-LDPC codes in the WPAN standard and has the advantages of having fewer registers, being small in power consumption, low in cost, high in working frequency and large in throughput capacity, and the like.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

Error correction encoding method and error correction encoding device

ActiveUS20150188578A1Reduce the amount of calculationReduce the amount requiredError correction/detection using multiple parity bitsCode conversionParity-check matrixMatrix multiplier

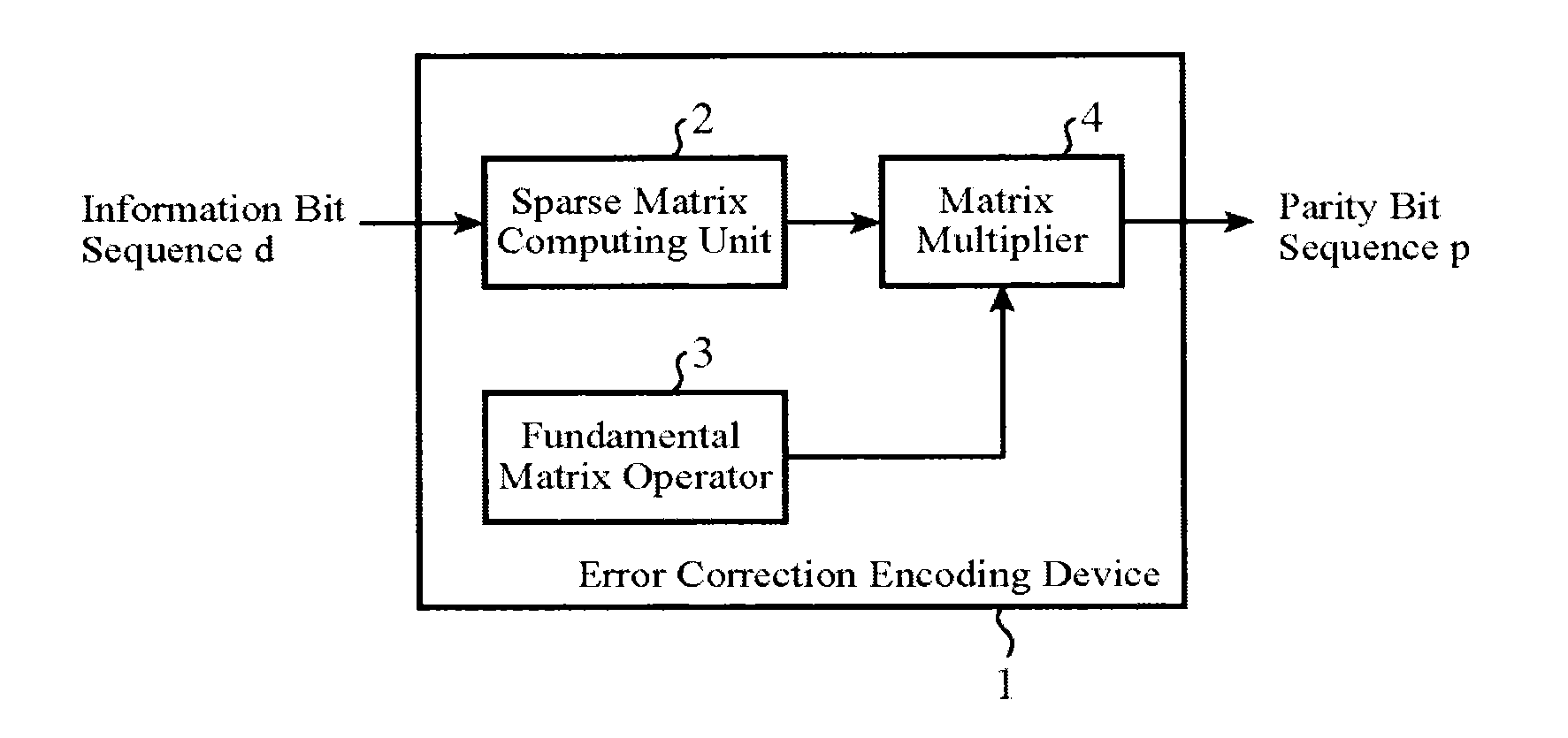

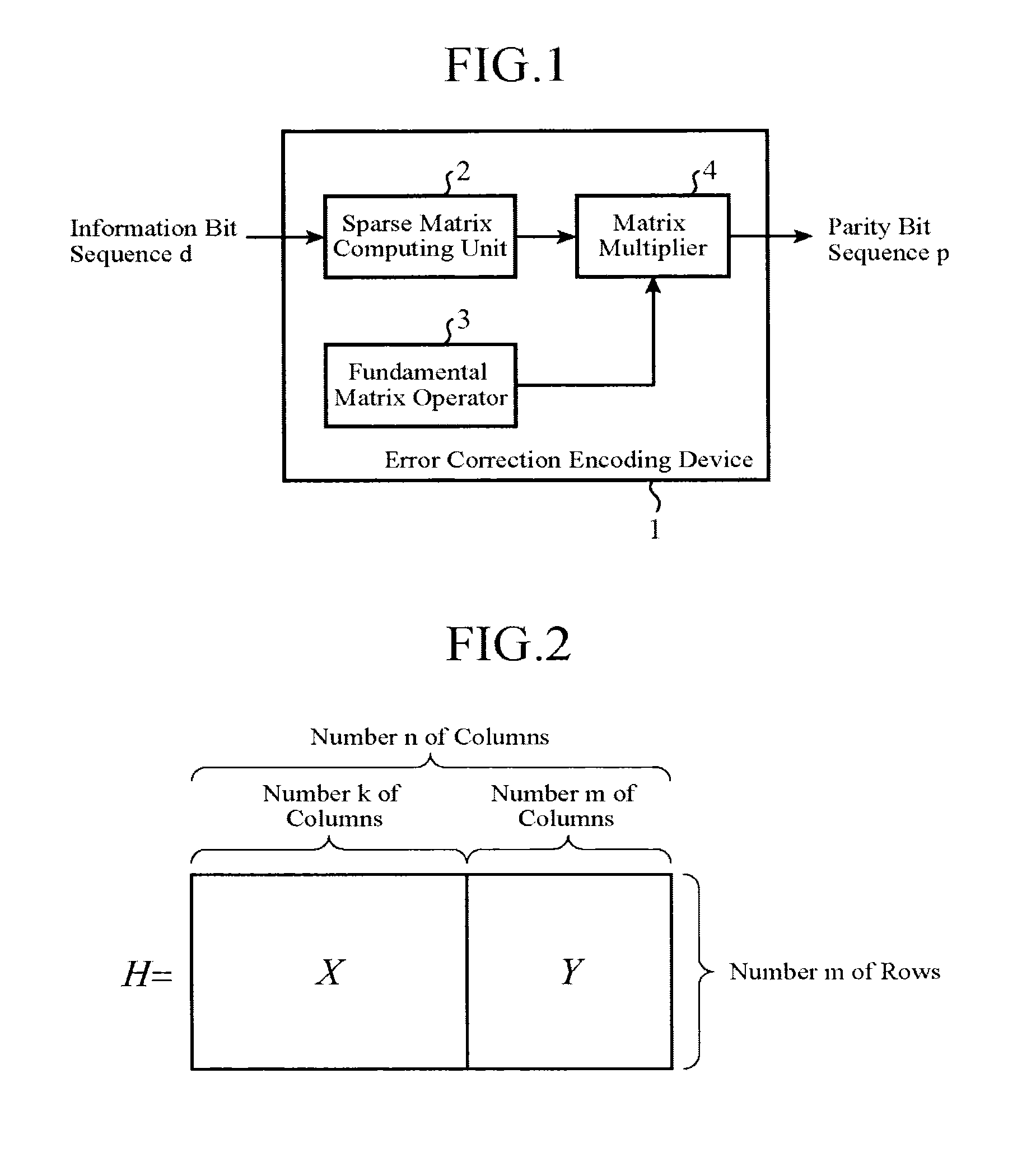

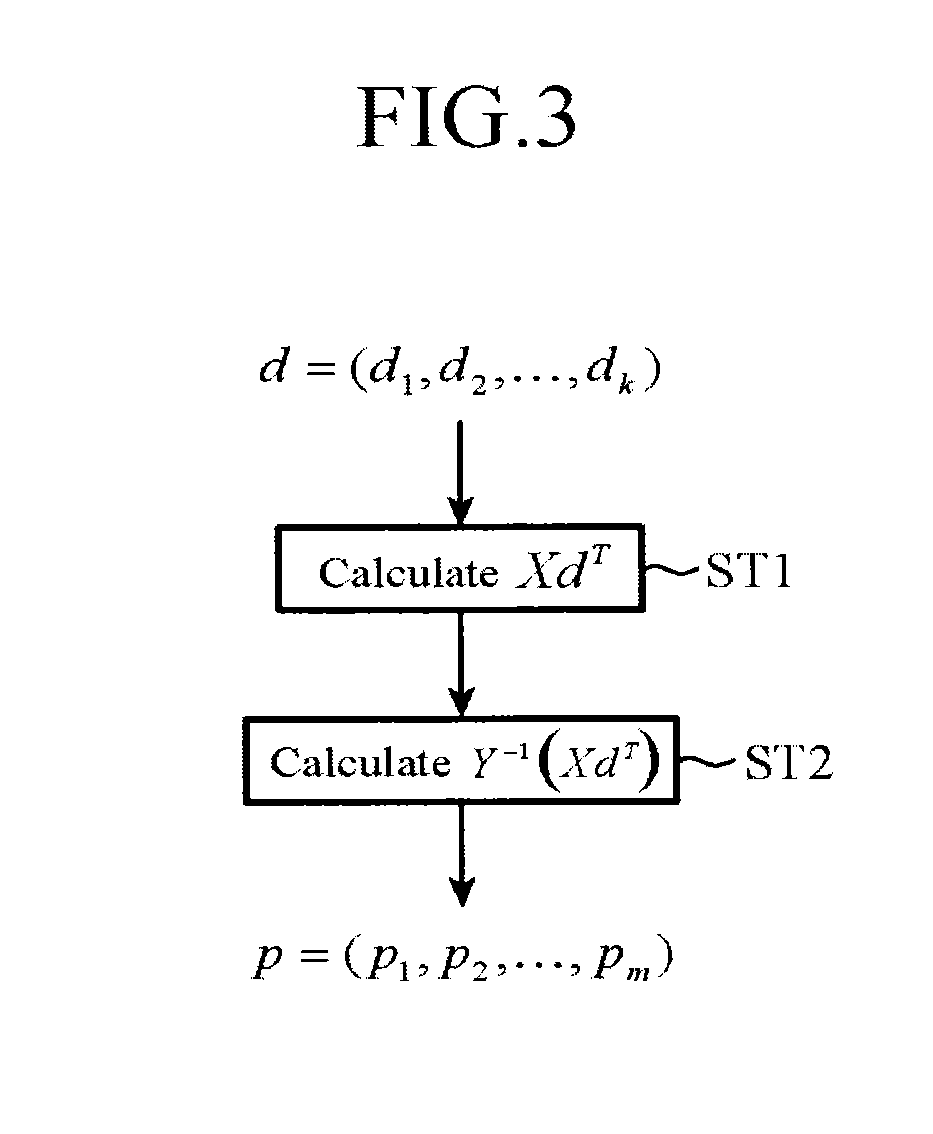

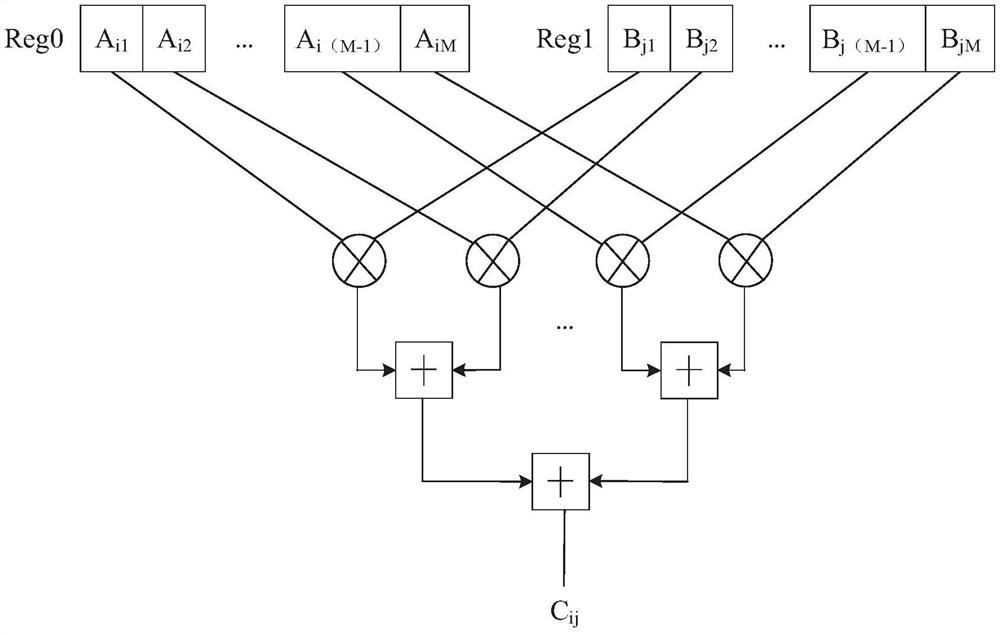

An error correction encoding device 1 includes a sparse matrix computing unit 2 that computes exclusive OR of a submatrix, in a parity-check matrix, corresponding to an information bit sequence, and the information bit sequence on the basis of the position of 1 in the submatrix to calculate a vector, a fundamental matrix operator 3 that calculates a predetermined matrix by performing a predetermined fundamental matrix operation on a submatrix, in the parity-check matrix, corresponding to a parity bit sequence, and a matrix multiplier 4 that calculates the parity bit sequence by multiplying the predetermined matrix which the fundamental matrix operator 3 calculates, and the vector which the sparse matrix computing unit 2 calculates.

Owner:MITSUBISHI ELECTRIC CORP

Matrix multiplier

PendingCN111859273AComputation using non-contact making devicesComplex mathematical operationsComputer hardwareBinary multiplier

The embodiment of the invention discloses a matrix-to-multiplier, relates to the technical field of data calculation, and aims to perform block calculation on two matrixes. The matrix multiplier comprises: a first memory, a second memory, an operational circuit and a controller, wherein the operational circuit can be in data communication with the first memory and the second memory through a bus;and the controller is used for controlling the first matrix and the second matrix to perform partitioning according to a preset program or instruction, and controlling the operational circuit to perform multiplication operation on corresponding partitions in the first memory and the second memory according to a partitioning result of the controller. The matrix multiplier may be used to multiply two matrices.

Owner:HUAWEI TECH CO LTD

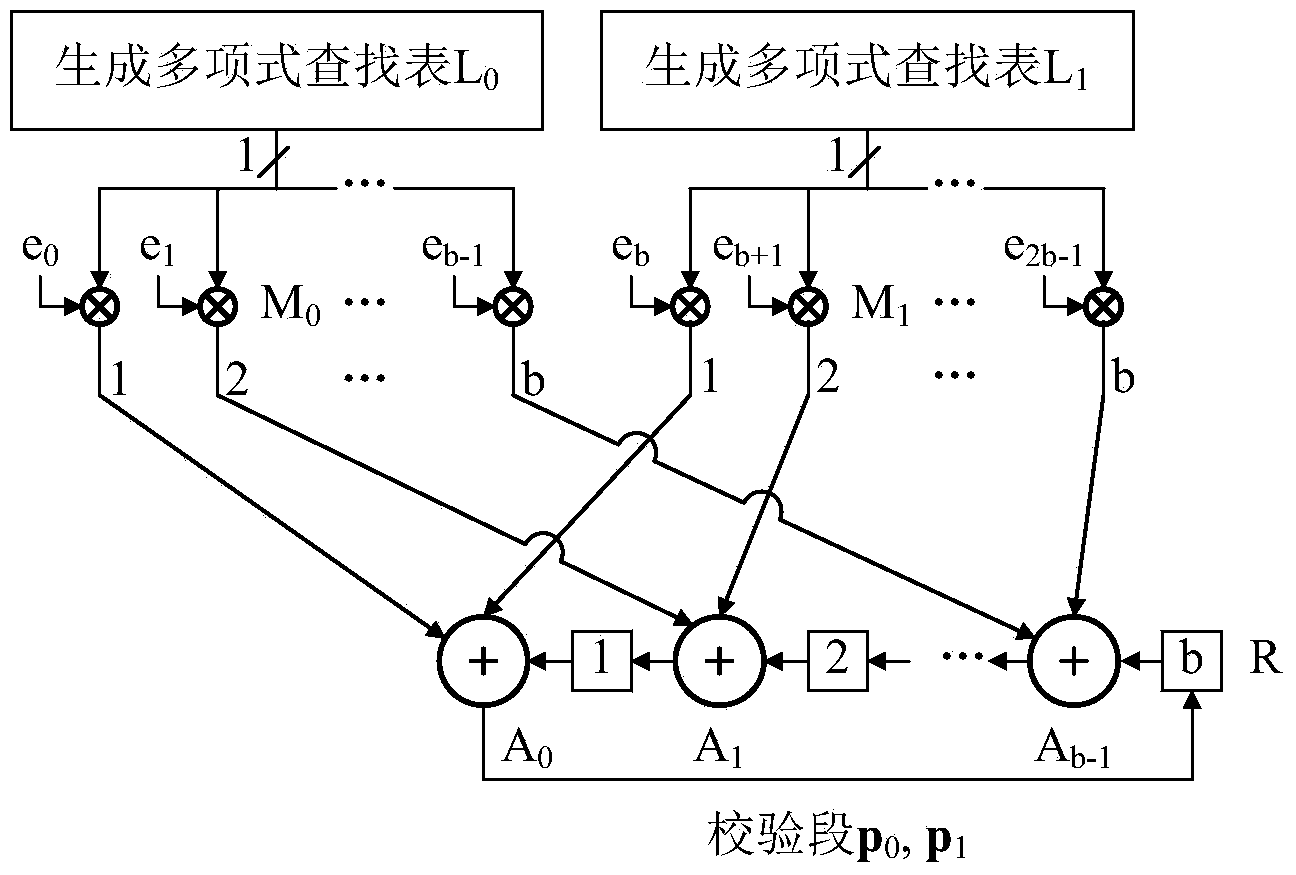

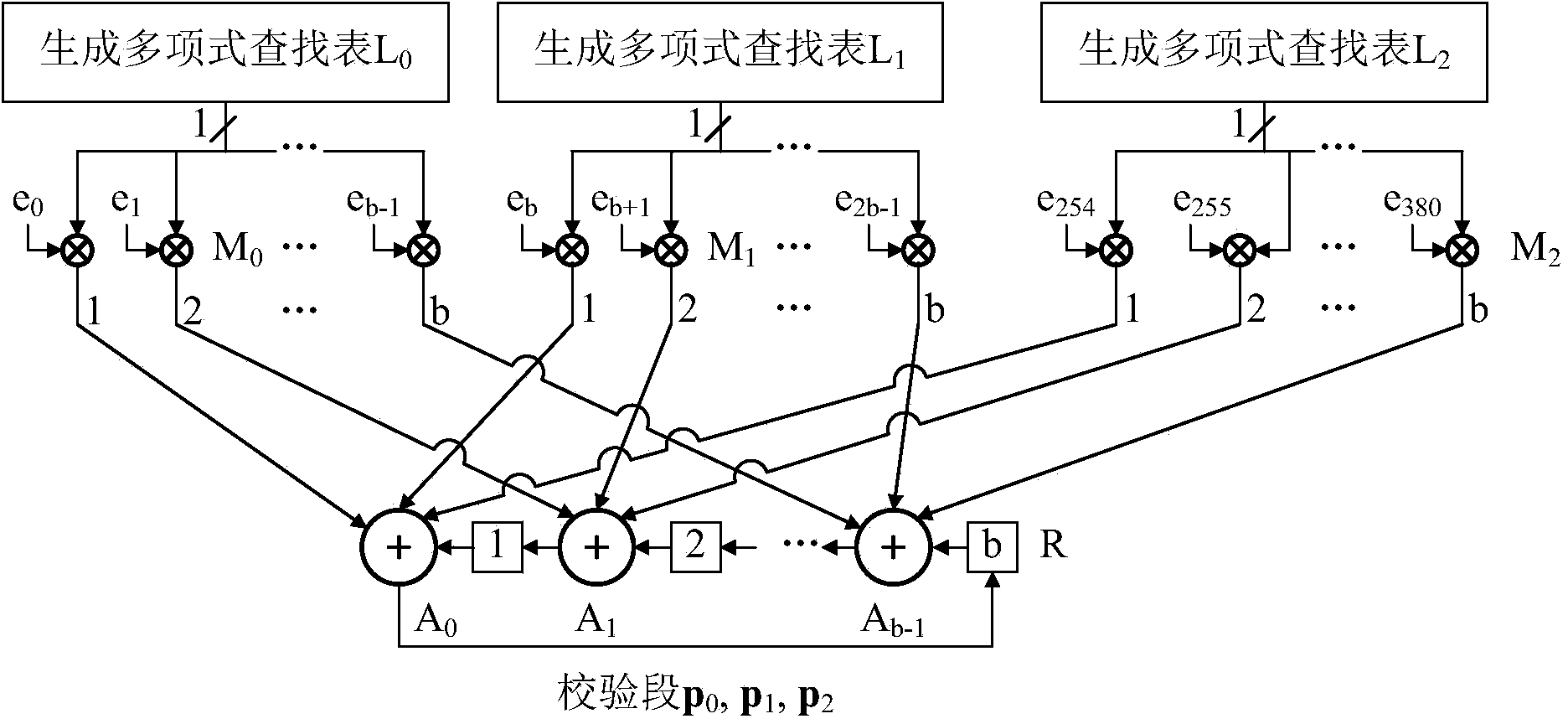

Full parallel input quasi-cyclic matrix multiplier based on ring shift left in DTMB

InactiveCN103929199ASimple structureReduce registerError correction/detection using multiple parity bitsShift registerBinary multiplier

The invention provides a full parallel input quasi-cyclic matrix multiplier based on ring shift left in a DTMB, wherein the multiplier is used for achieving multiplication of vectors m and quasi-cyclic matrixes F in DTMB standard multiple rate QC-LDPC approximate lower triangular codes. The multiplier comprises three generator polynomial lookup tables for prestoring all circulant matrix generator polynomials in the matrixes F, three 127-bit binary multipliers for carrying out scalar multiplying on vector fields of the m and generator polynomial bits, 127 4-bit binary adders for carrying out modulor-2 addition on products and shifting register content, and a 127-bit shifting register for storing the sum of results obtained after 1-bit ring shift left is carried out. The full parallel input multiplier is compatible with all code rates and has the advantages that the number of the registers is small, power consumption is little, cost is low, work frequency is high and the handling capacity is large.

Owner:RONGCHENG DINGTONG ELECTRONICS INFORMATION SCI & TECH CO LTD

Matrix multiplier device based on single FPGA

Owner:ZHEJIANG UNIV

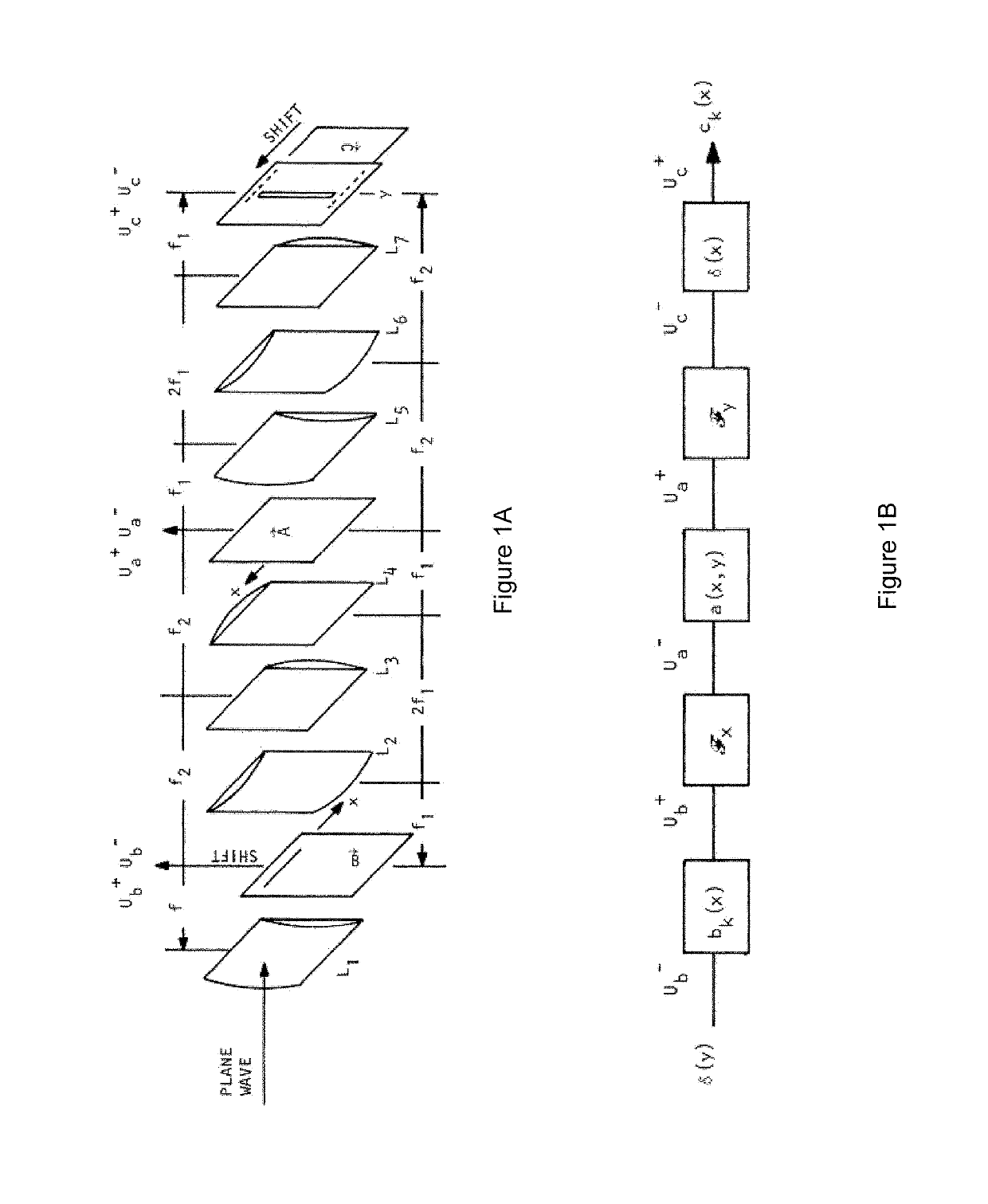

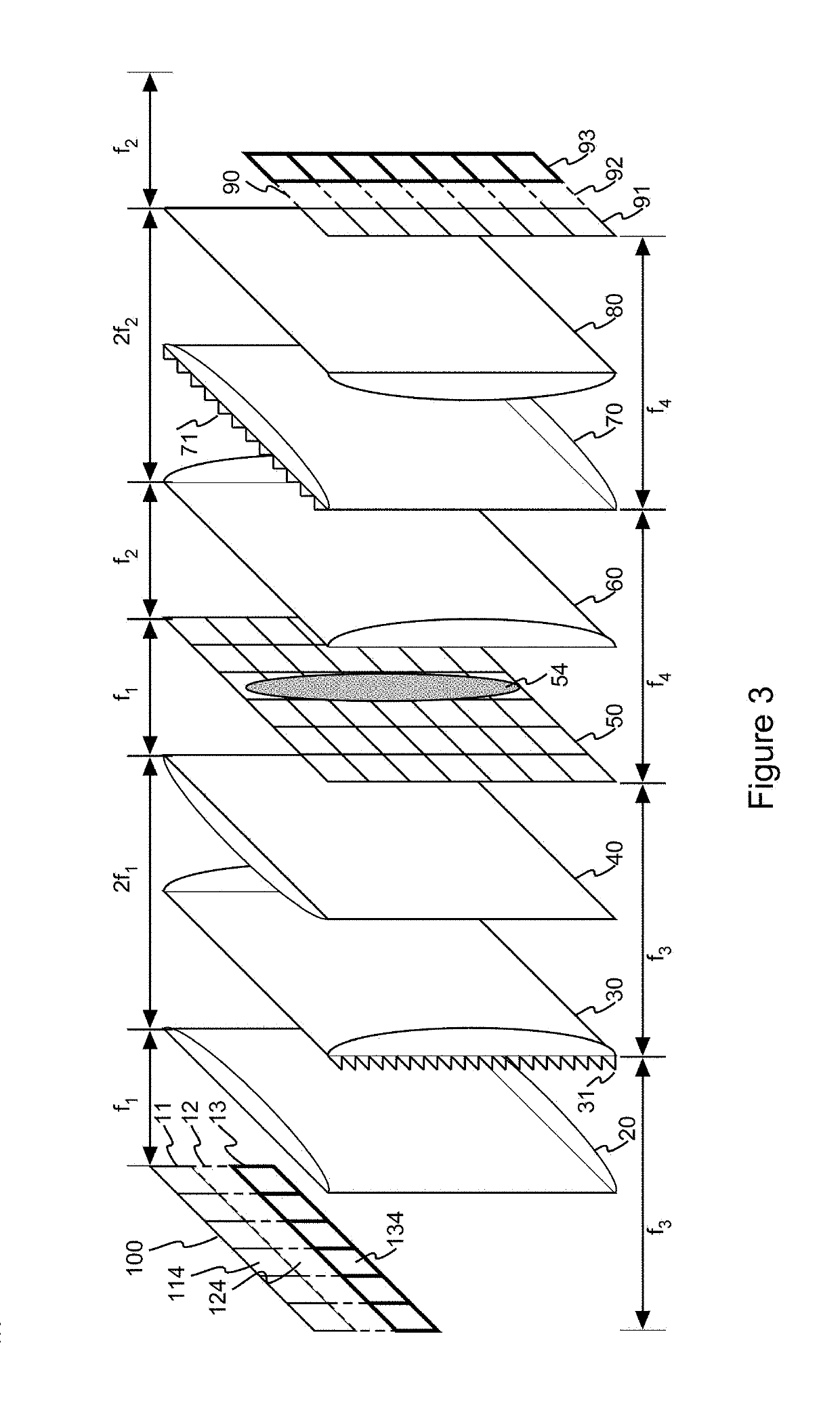

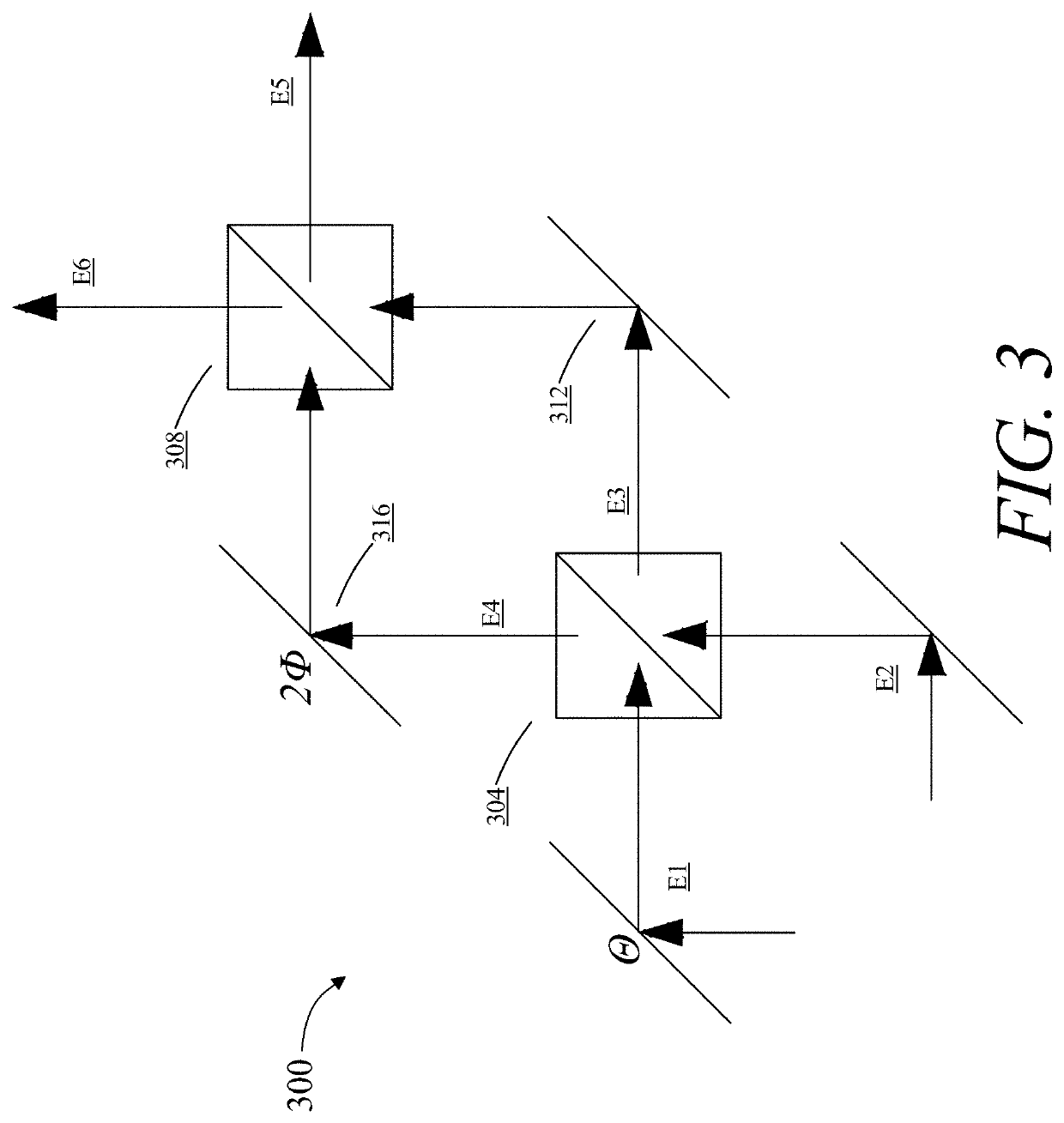

Wavelength multiplexed matrix-matrix multiplier

ActiveUS10274989B2Efficient collectionComputing operations for multiplication/divisionDigital dataMultiplexingMatrix multiplier

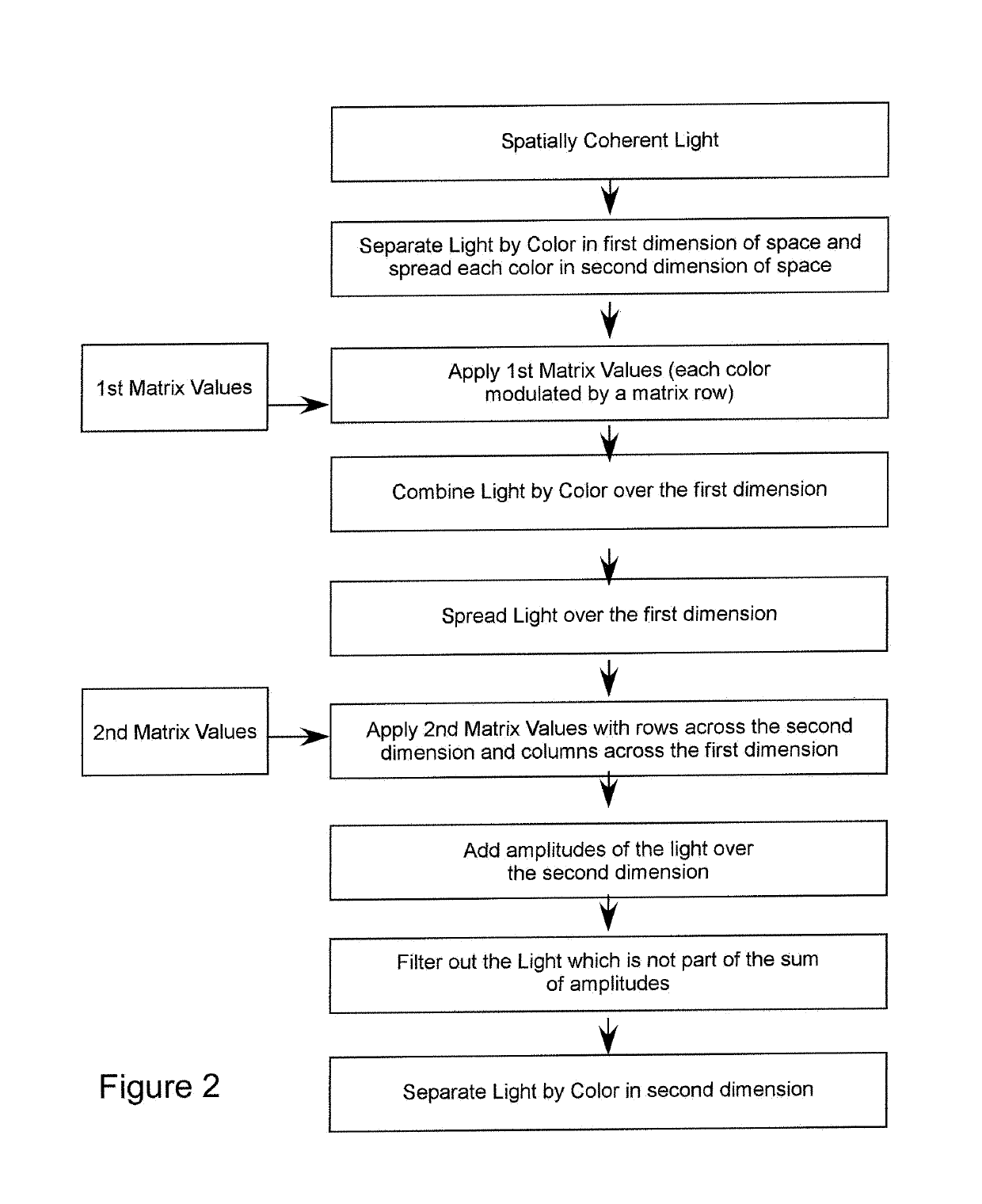

Optical systems for performing matrix-matrix multiplication in real time utilizing spatially coherent input light and wavelength multiplexing.

Owner:FATHOM RADIANT PBC

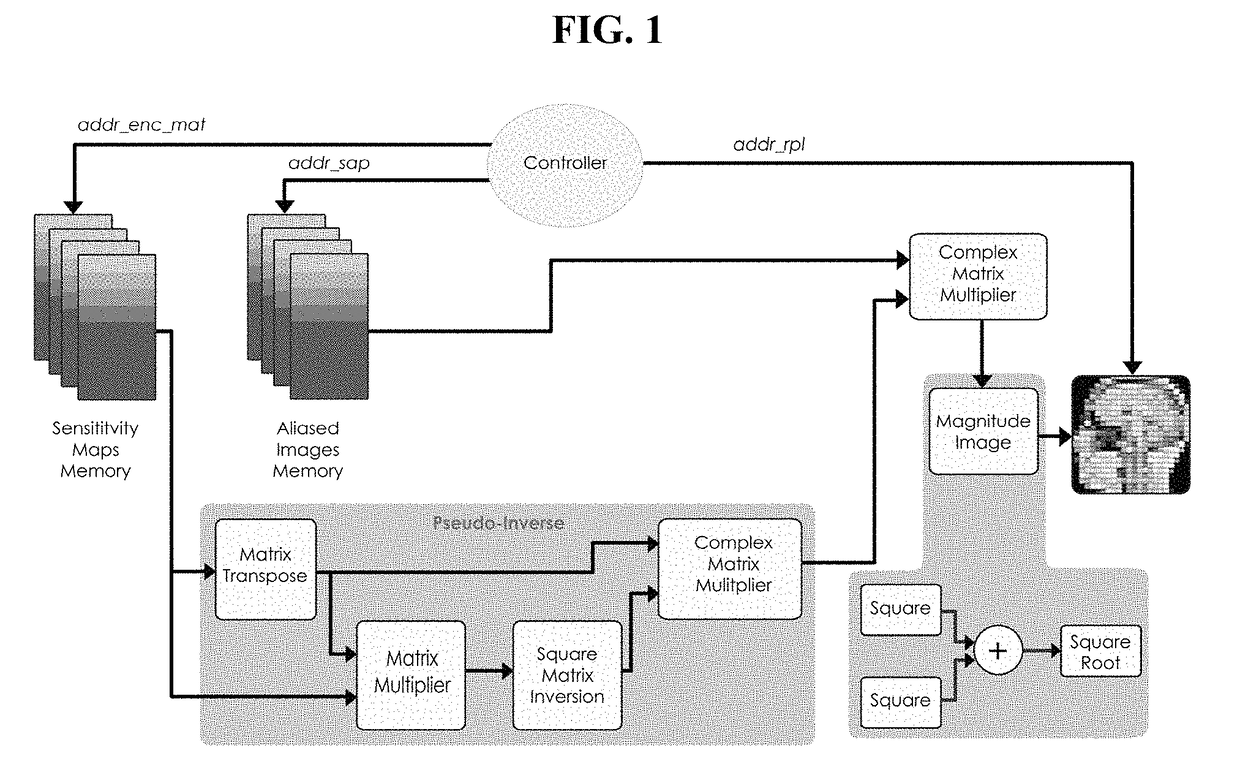

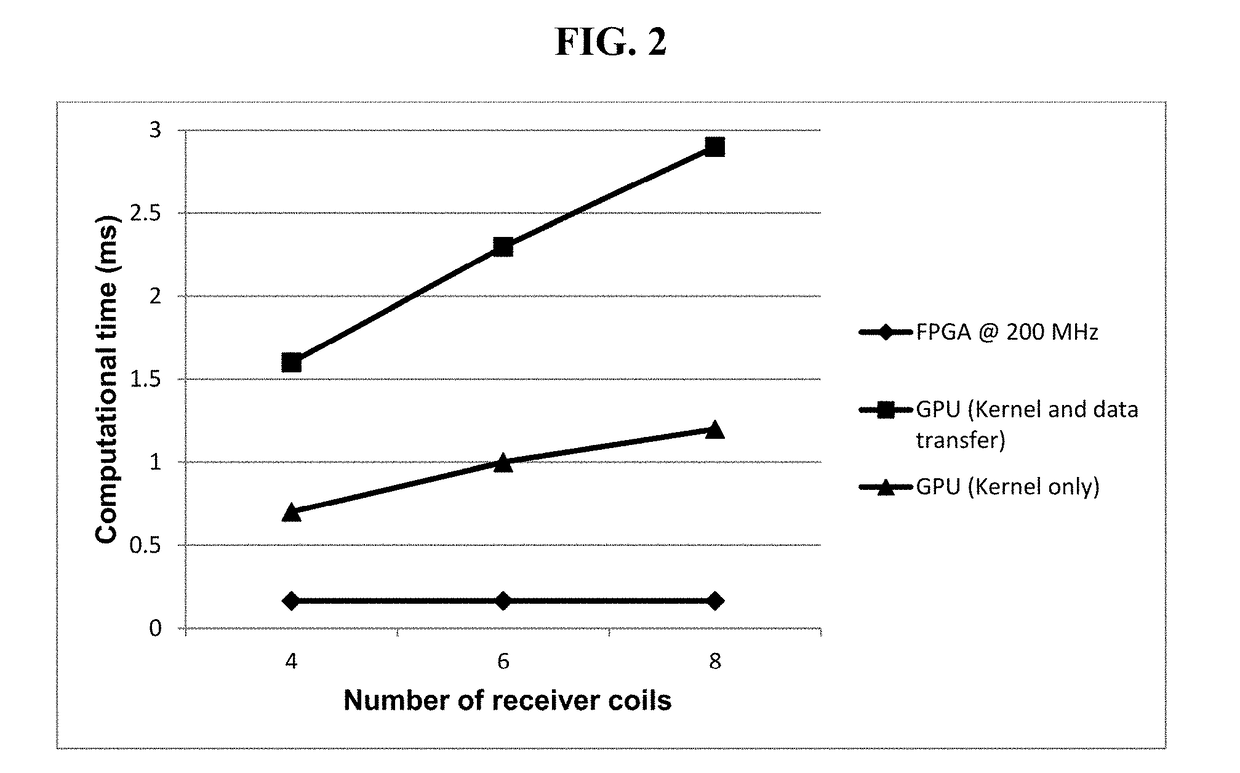

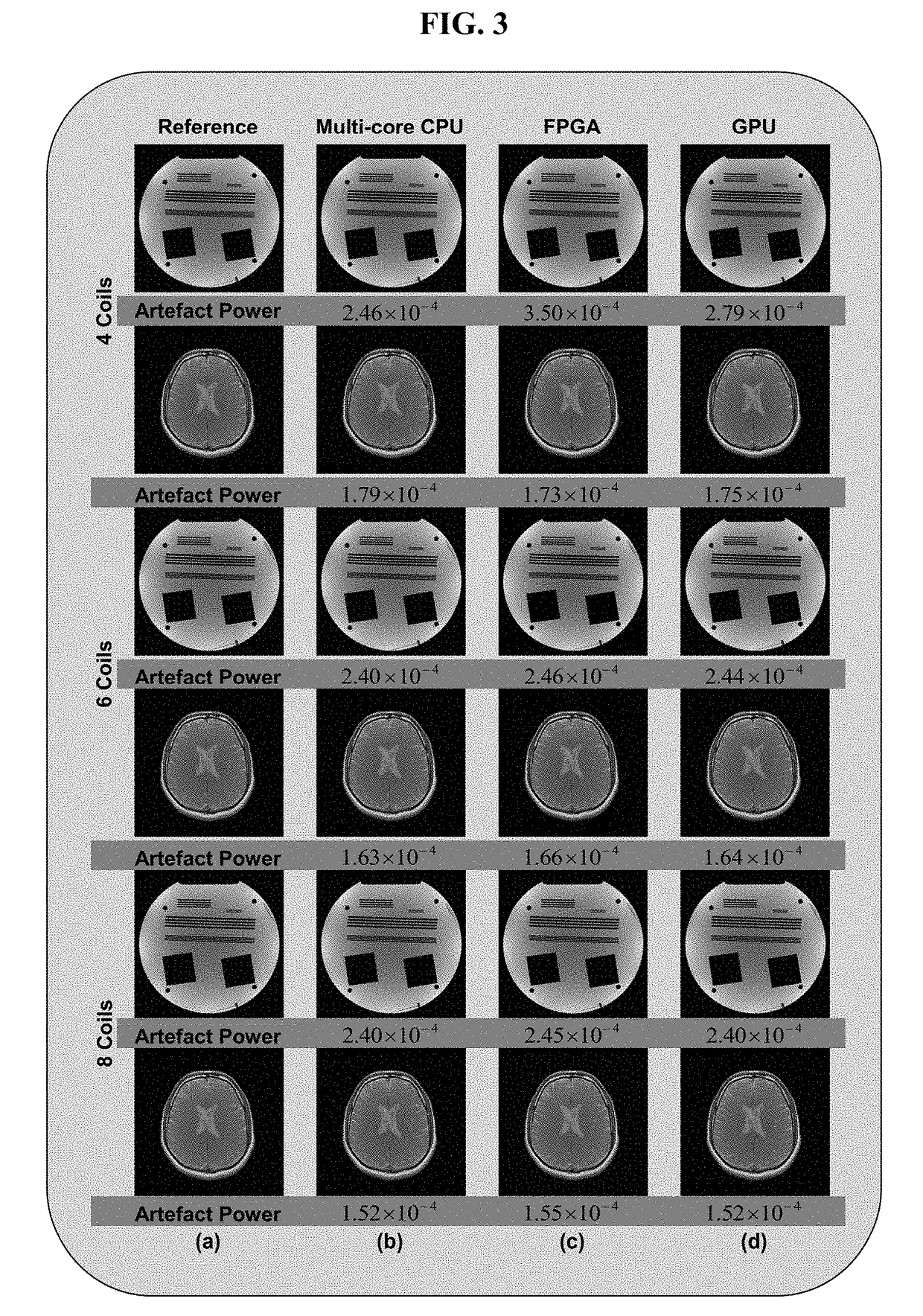

FPGA implementation of a real-time parallel MRI reconstruction

A system for parameterized FPGA (Field Programable Gate Array) implementation of real-time SENSE (SENSitivity Encoding) reconstruction including: a sensitivity maps memory configured to store sensitivity map data; an aliased image memory configured to store aliased image data acquired from a scanner; a reconstructed image memory configured to store reconstructed image data; a parameterized complex matrix multiplier; a pseudo-inverse calculator; a magnitude image block; and a controller; wherein sensitivity map data from the sensitivity maps memory is transferred to the pseudo-inverse calculator; wherein data from the pseudo-inverse calculator and the aliased image data from the aliased image memory is transferred to the complex matrix multiplier; wherein data from the complex matrix multiplier is transferred to the magnitude image block; wherein the controller is configured to generate an address of the sensitivity map memory and an address of the aliased image memory to access the encoding matrix and corresponding aliased image data and also configured to generate an address of the reconstructed image memory to store the reconstructed image data.

Owner:COMSATS INST OF INFORMATION TECH

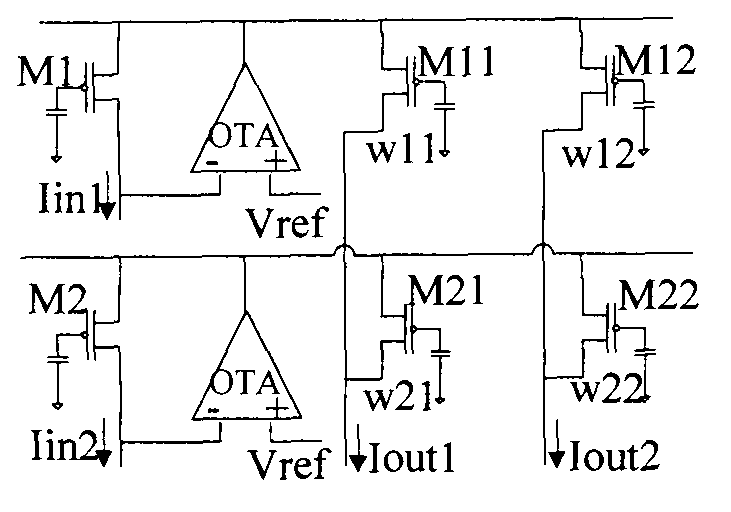

Design method for field programmable analog array (FPAA)-based reconfigurable vector-matrix multiplier

InactiveCN102929842AAchieving Variable Operation ScaleCoefficient adjustableComputation using non-contact making devicesComplex mathematical operationsAudio power amplifierMatrix multiplier

The invention discloses a design method for a field programmable analog array (FPAA)-based reconfigurable vector-matrix multiplier. According to the method, a novel FPAA based on a transconductance operational amplifier and a floating gate transistor is designed, then an analog vector-matrix multiplier principle circuit is designed, and a design process of adopting SIMULINK, Sim2Spice, GRASPER and RAT software tools to realize the reconfigurable analog vector-matrix multiplier is proposed. The configurable analog vector-matrix multiplier designed by the method can realize a variable operation scale and an adjustable matrix coefficient.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

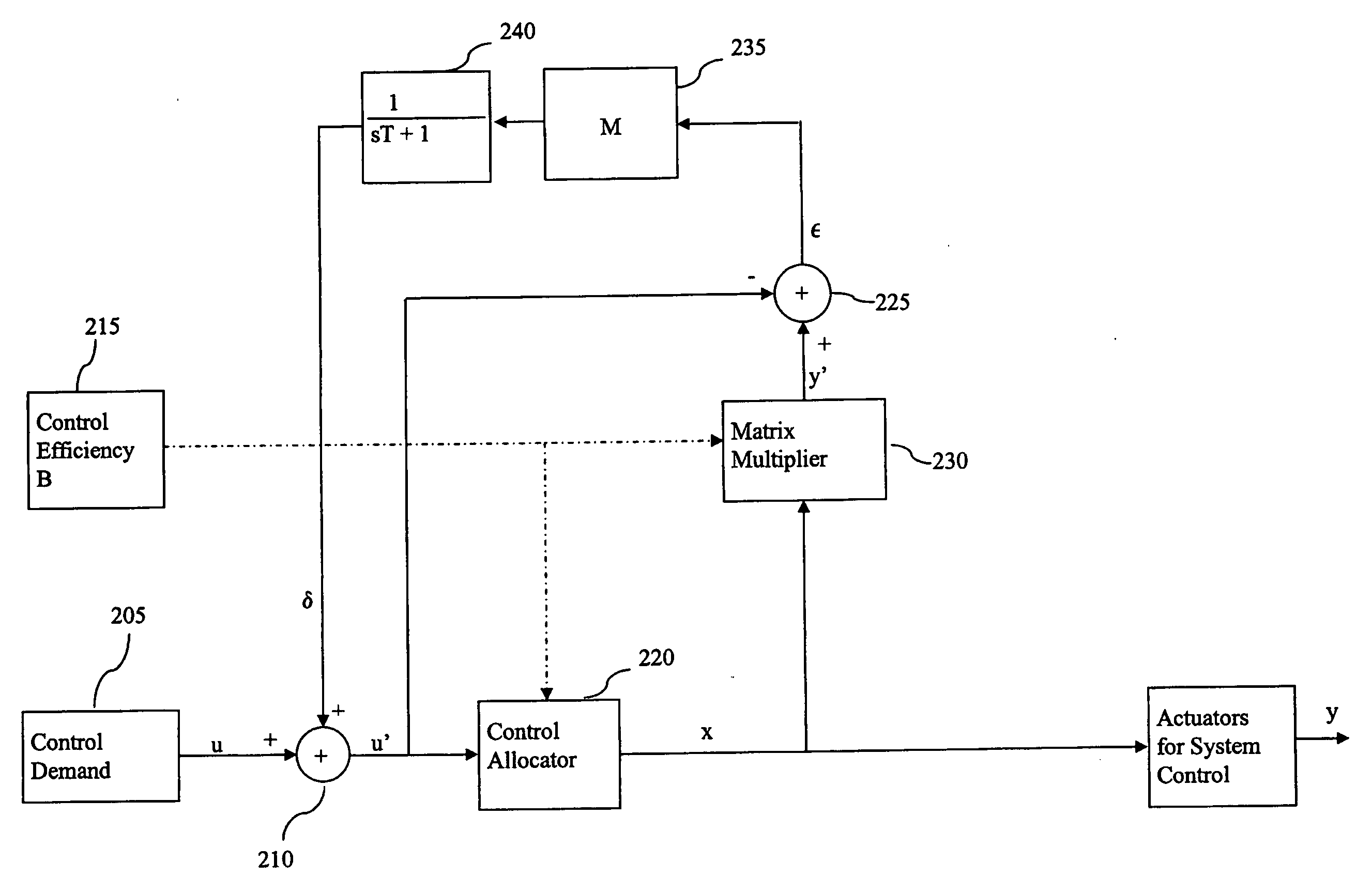

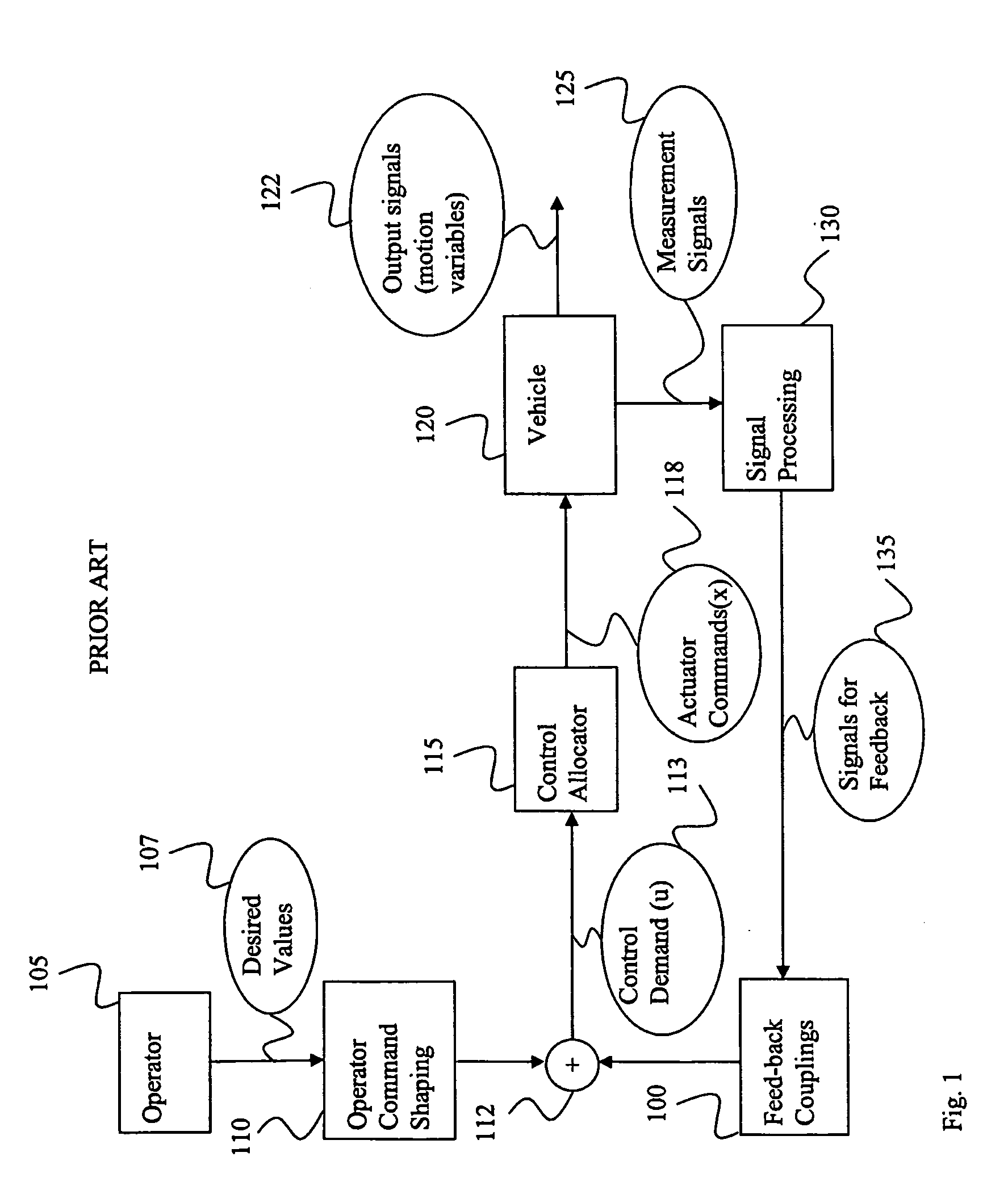

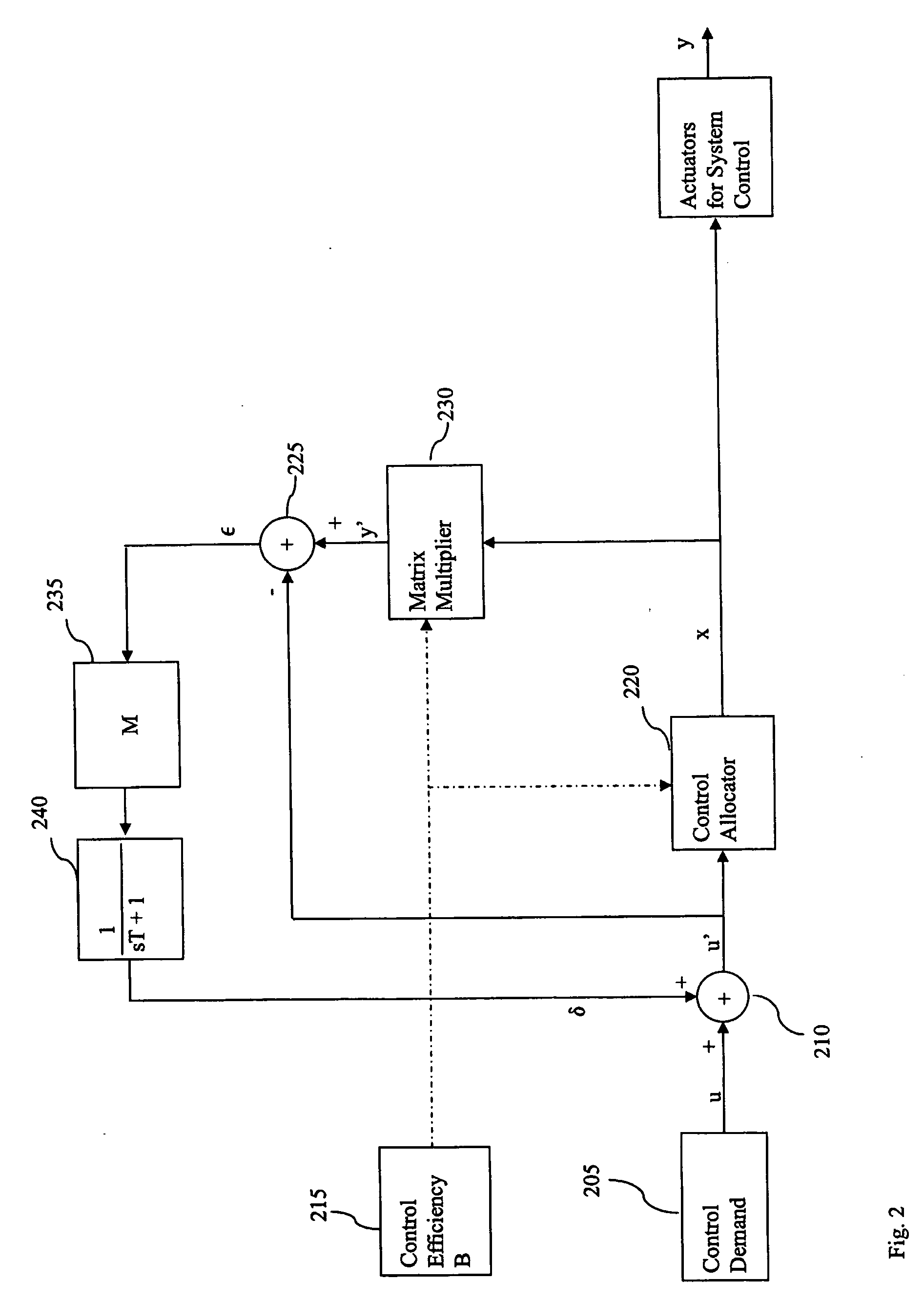

Vehicle control system and method using control allocation and phase compensation

InactiveUS20080215191A1Vehicle fittingsDigital data processing detailsControl systemMatrix multiplier

A vehicle control system and method combining control allocation and phase compensation for forming a phase compensated actuator command signal based on a control demand signal. A feedback unit includes a matrix multiplication unit for forming an estimated behaviour signal, from a control efficiency matrix and the actuator command signal. The estimated behaviour signal is fed to a second summation unit for forming a difference signal. The difference signal from the summation unit is processed by a filter unit for forming a feedback signal which is connected to a first summation unit for forming a modified control demand signal, such that the modified control demand signal is adjusted to always represent a control demand realisable by the vehicle. The modified control demand signal of the first summation unit is further connected to the second summation unit and to a control allocator which output is then connected to the matrix multiplier to form a feedback loop.

Owner:SAAB AB

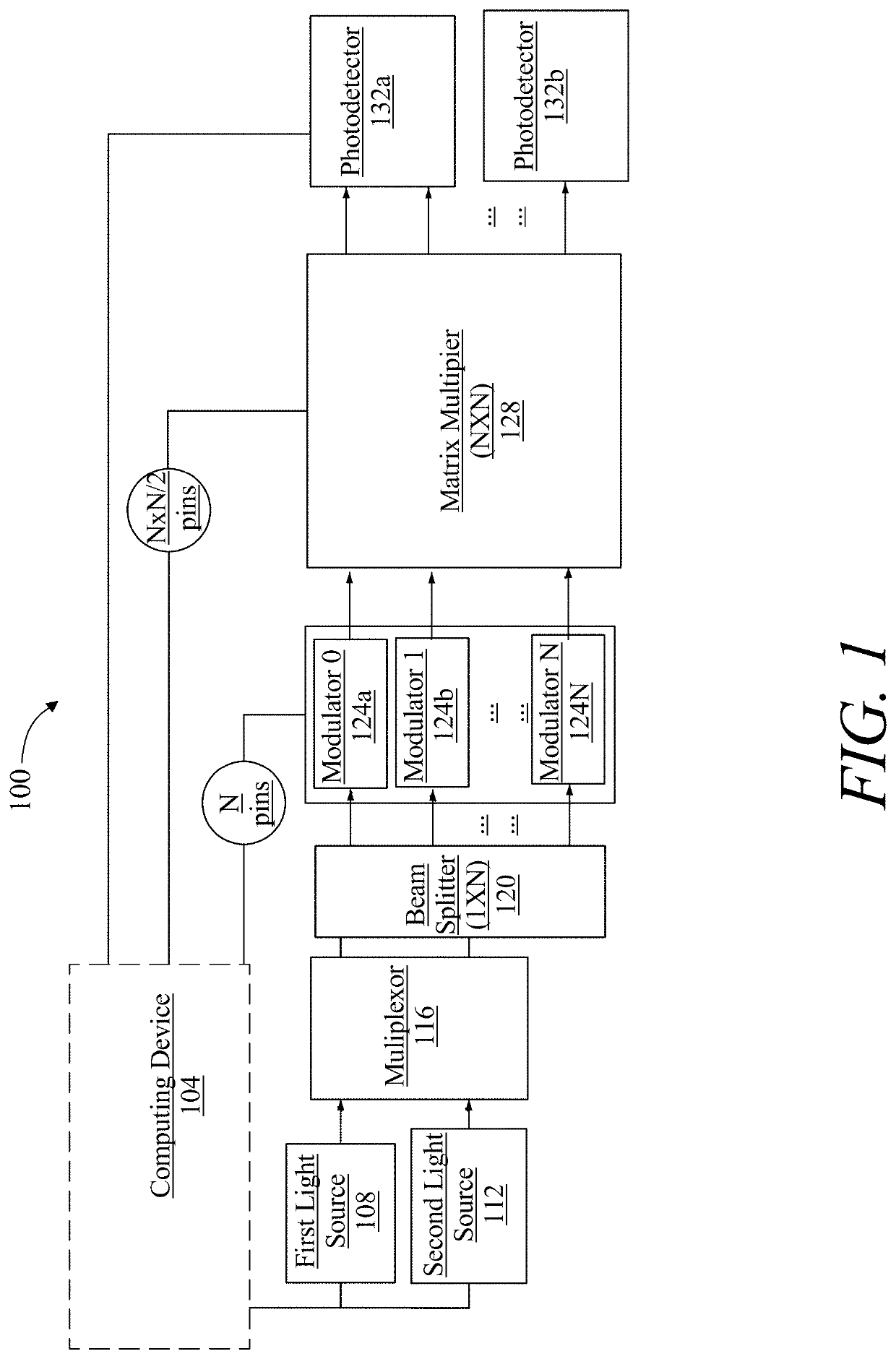

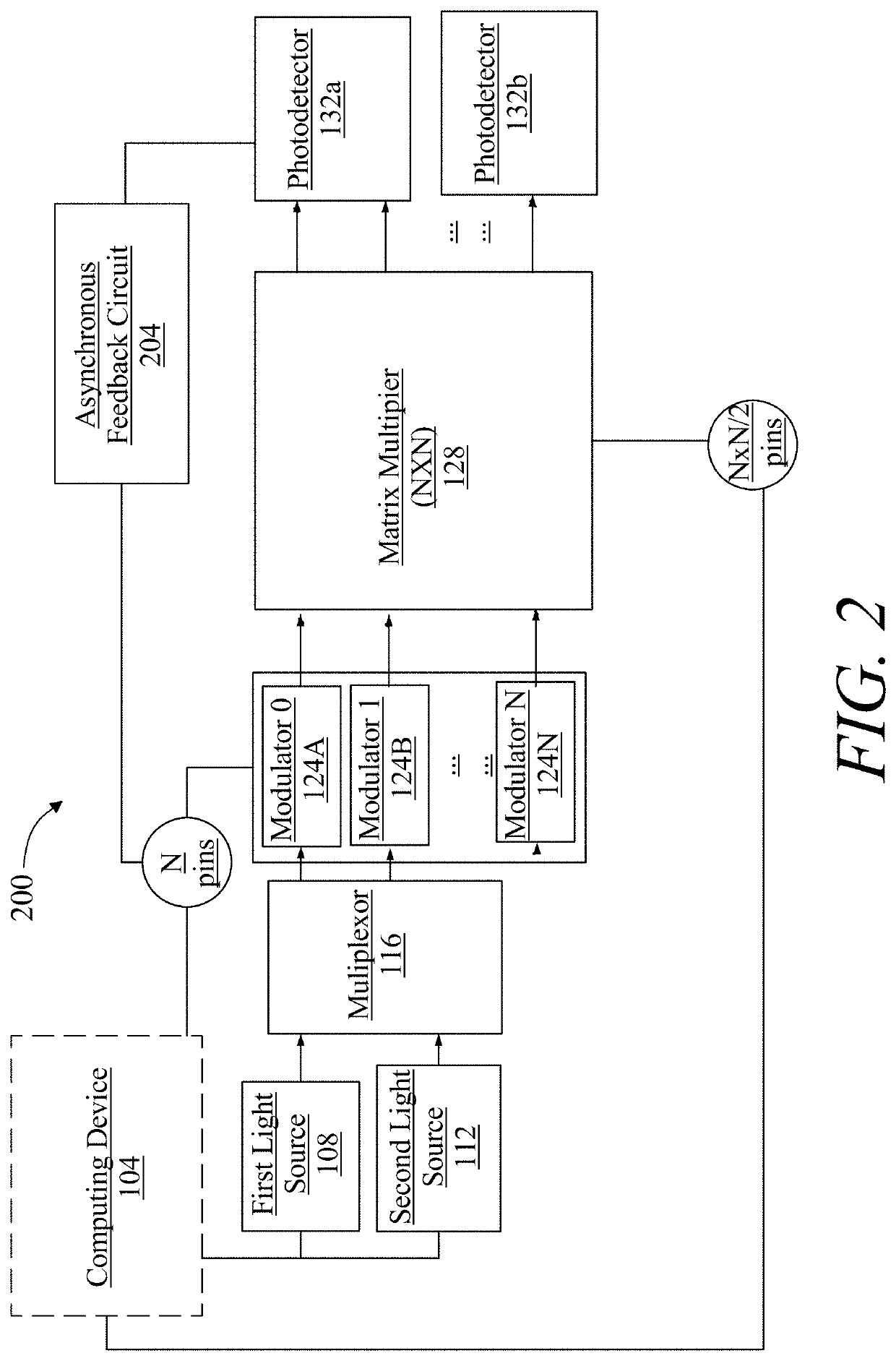

Methods and systems for optical matrix calculation

Aspects relate to methods and systems for optical matrix calculation. An exemplary system includes at least a first light source configured to output at least a first optical output having a first wavelength, at least a second light source configured to output at least a second optical output having a second wavelength substantially different from the first wavelength, at least an optical modulator configured to modulate the at least a first optical output, at least an optical matrix multiplier configured to perform at least two matrix multiplications, a first matrix multiplication as a function of the first optical output and a second matrix multiplication as a function of the second optical output, and at least a photodetector configured to measure the at least a first optical output and the at least a second optical output.

Owner:SIPHOX INC