Systolic structure matrix multiplier based on FPGA (Field Programmable Gate Array) and implementation method thereof

A technology of structure matrix and implementation method, which is applied in the direction of instruments, electrical digital data processing, and digital data processing components, etc., can solve the problems of high fan-out of matrix multiplier input modules, difficulty in achieving overall performance, and complex data input control. Achieve the effect of reducing overall power consumption, convenient reconfiguration, and low power consumption performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

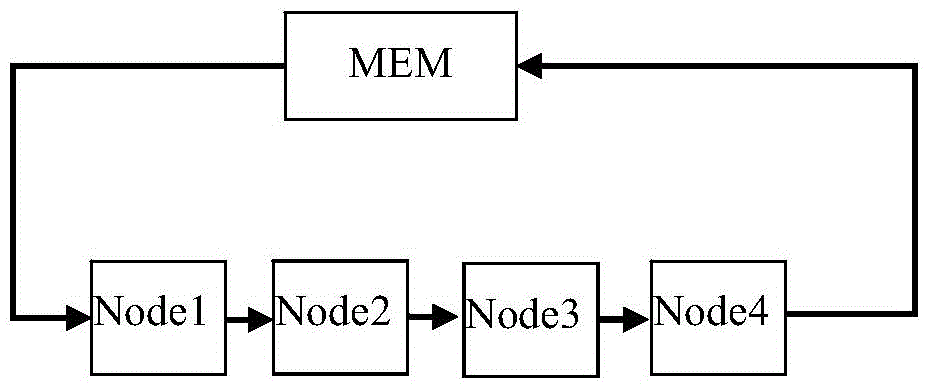

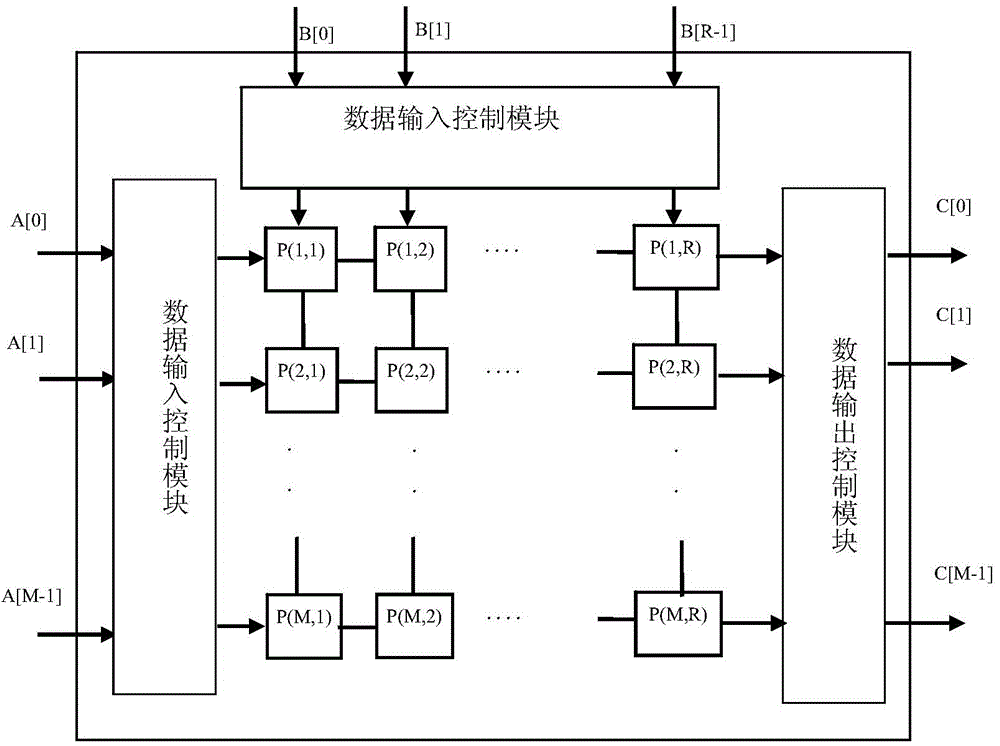

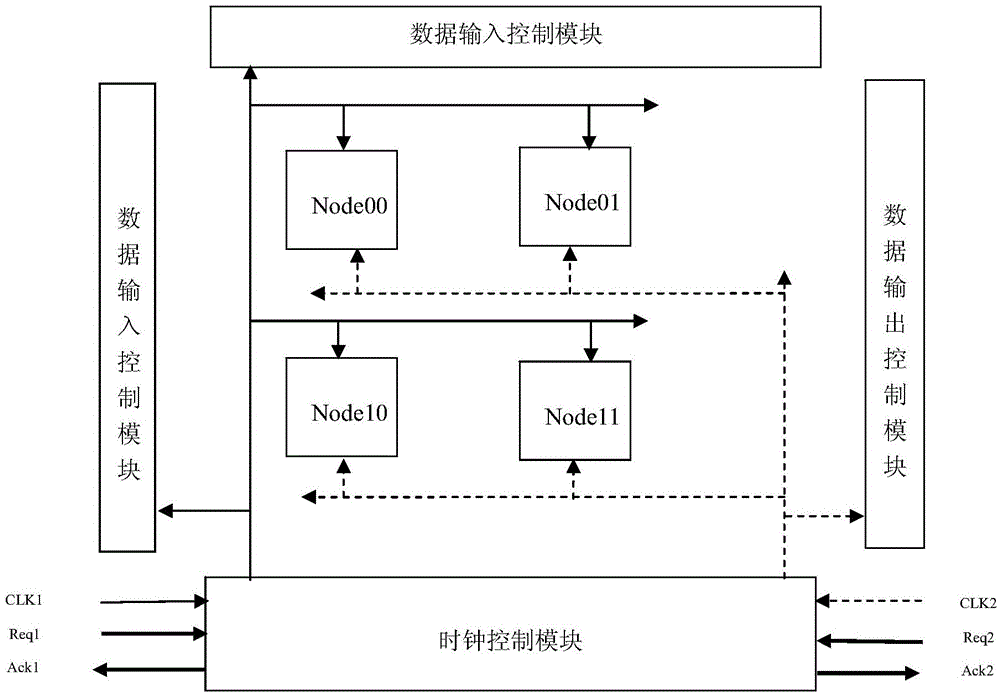

[0042] Such as figure 2Shown, a kind of pulsating structure matrix multiplier based on FPGA comprises: multiplier array, clock control module, data input control module, data output control module; Described multiplier array is the two-dimensional mesh array structure of M row R row , consisting of M×R node units, and adjacent node units are interconnected to realize the product operation of the input matrix A and matrix B; the clock control module is used to output two clocks, which are respectively provided to the data input A control module and a data output control module; the data input control module is used to input matrix A and matrix B in parallel under the control of the clock control module, wherein matrix A is M rows and N columns, and matrix B is N rows and R columns; The data output control module is used to output matrix C, wh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More