Matrix multiplier device based on single FPGA

A technology of matrix multiplier and matrix multiplication, applied in the field of FPGA technology and high-performance computing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

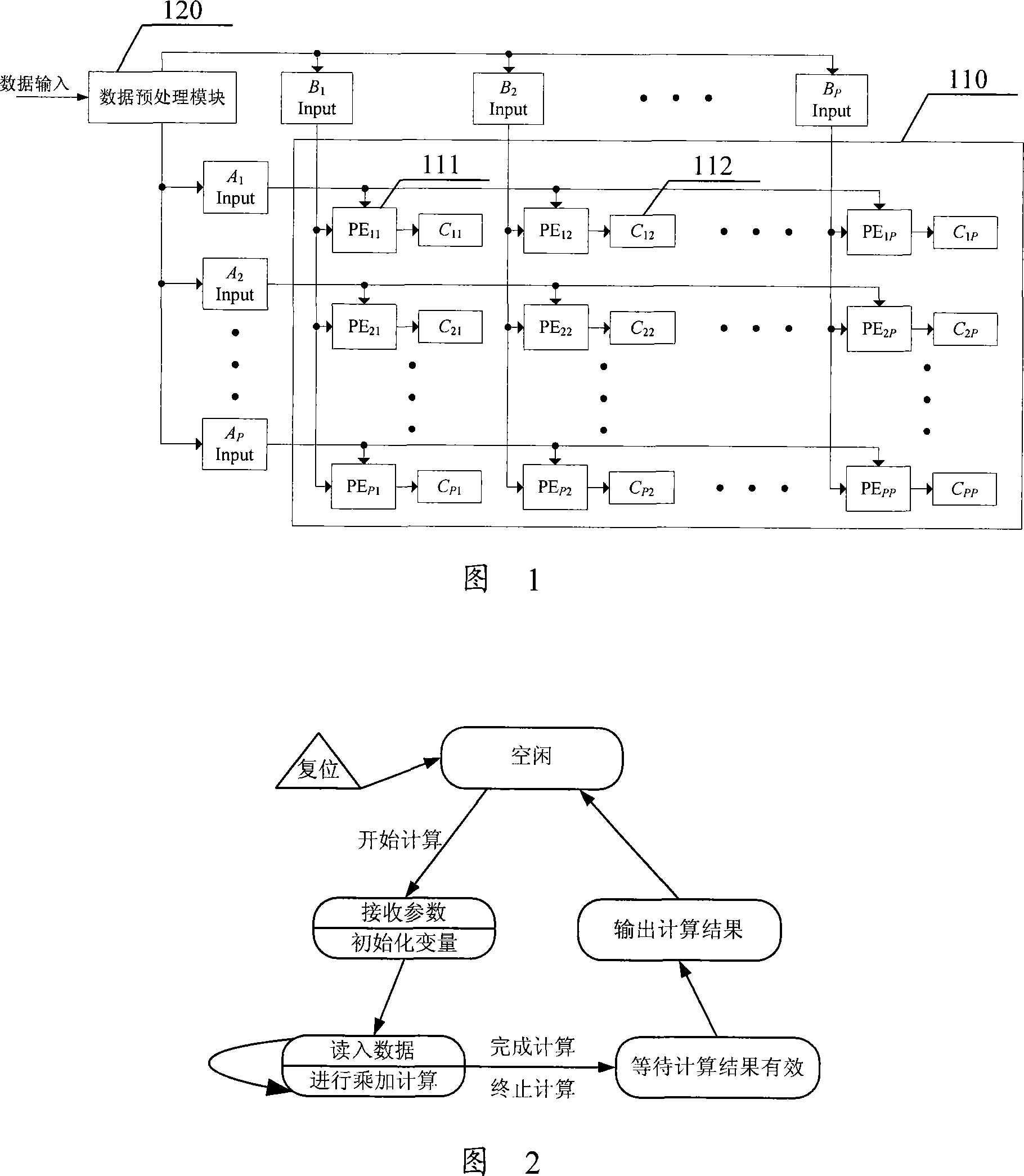

[0025] As shown in Figure 1, a matrix multiplier device based on a single FPGA specifically includes:

[0026] Realize P in a single FPGA chip by using FPGA internal DSP unit 2 A calculation unit PE (Processing Element) 111, which is used to perform multiplication and addition calculation operations on input data;

[0027] Each calculation unit PE 111 is configured with a storage unit 112 for storing calculation results;

[0028] Will P 2 A computing unit PE111 is arranged as a P×P PE array 110 for matrix multiplication calculation;

[0029] A data preprocessing module 120 is configured in front of the PE array 110 to analyze the values of the input matrix elements, so as to prevent the 0-element blocks in the sparse matrix from participating in the multiplication and addition calculation.

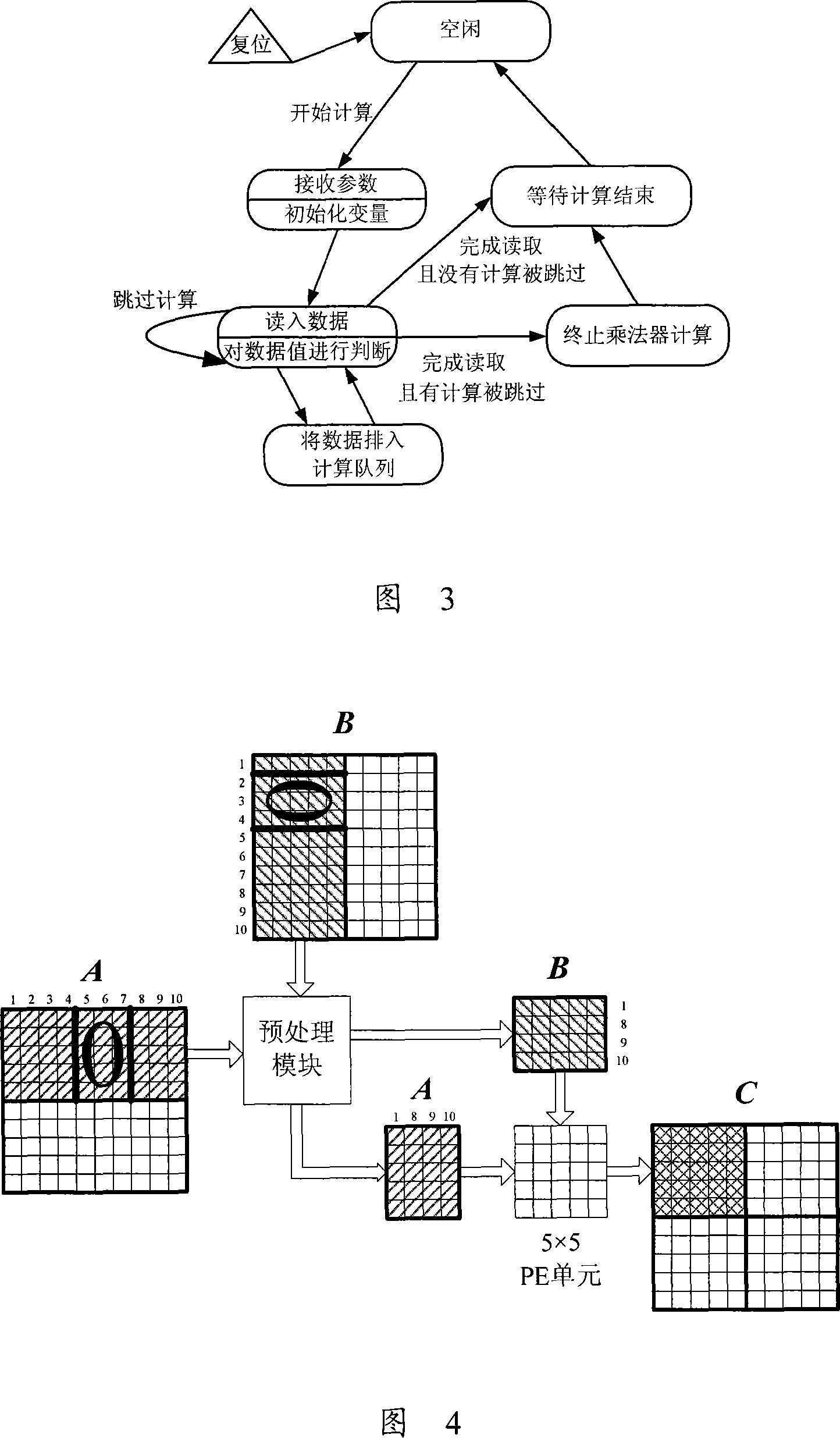

[0030] The working process of the PE array 110 is shown in Figure 2. After reset, the multiplier is in an idle state. After receiving the "start calculation" command, the multiplier i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More