Patents

Literature

132 results about "Formation matrix" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In statistics and information theory, the expected formation matrix of a likelihood function L(θ) is the matrix inverse of the Fisher information matrix of L(θ), while the observed formation matrix of L(θ) is the inverse of the observed information matrix of L(θ). Currently, no notation for dealing with formation matrices is widely used, but in books and articles by Ole E. Barndorff-Nielsen and Peter McCullagh, the symbol jⁱʲ is used to denote the element of the i-th line and j-th column of the observed formation matrix.

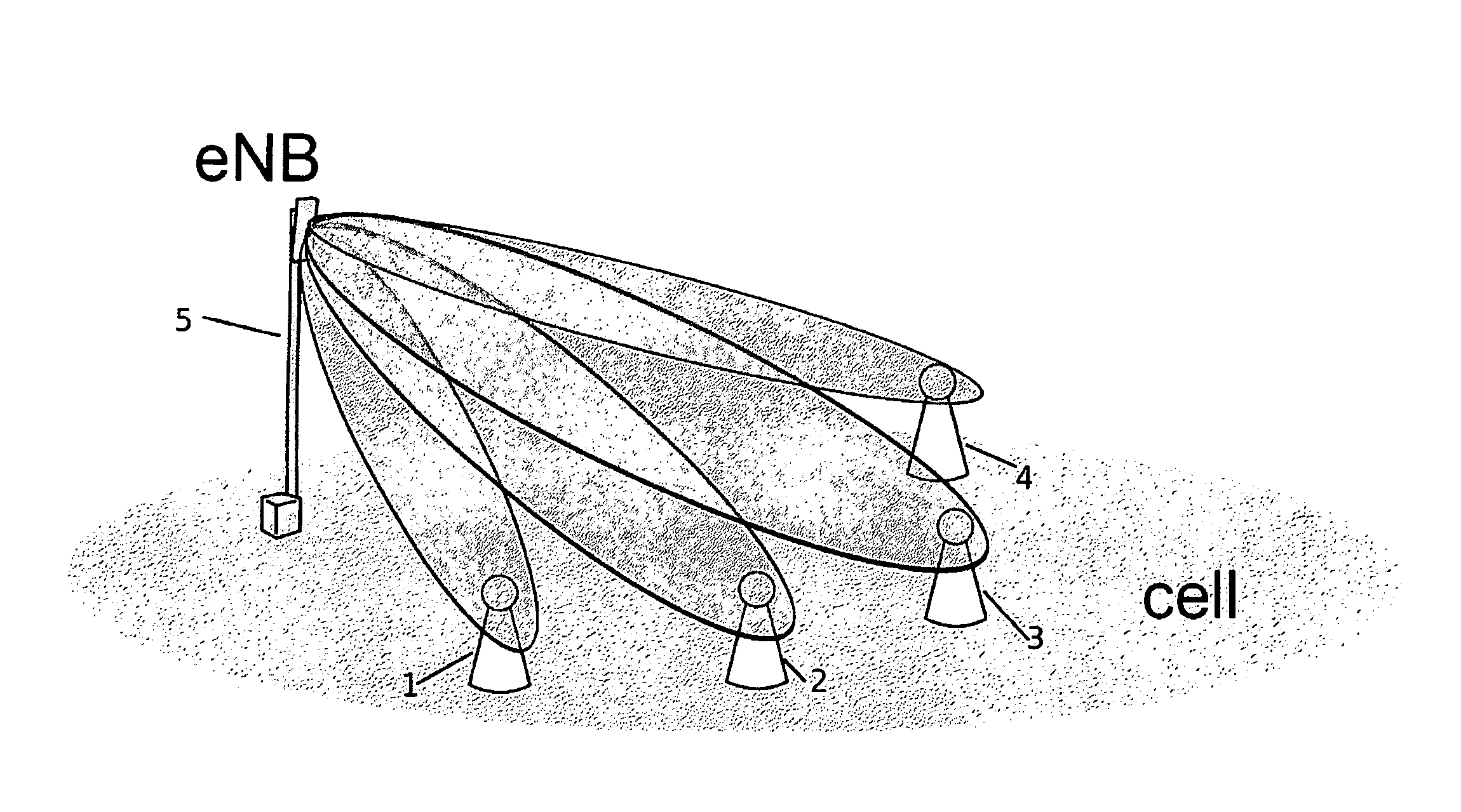

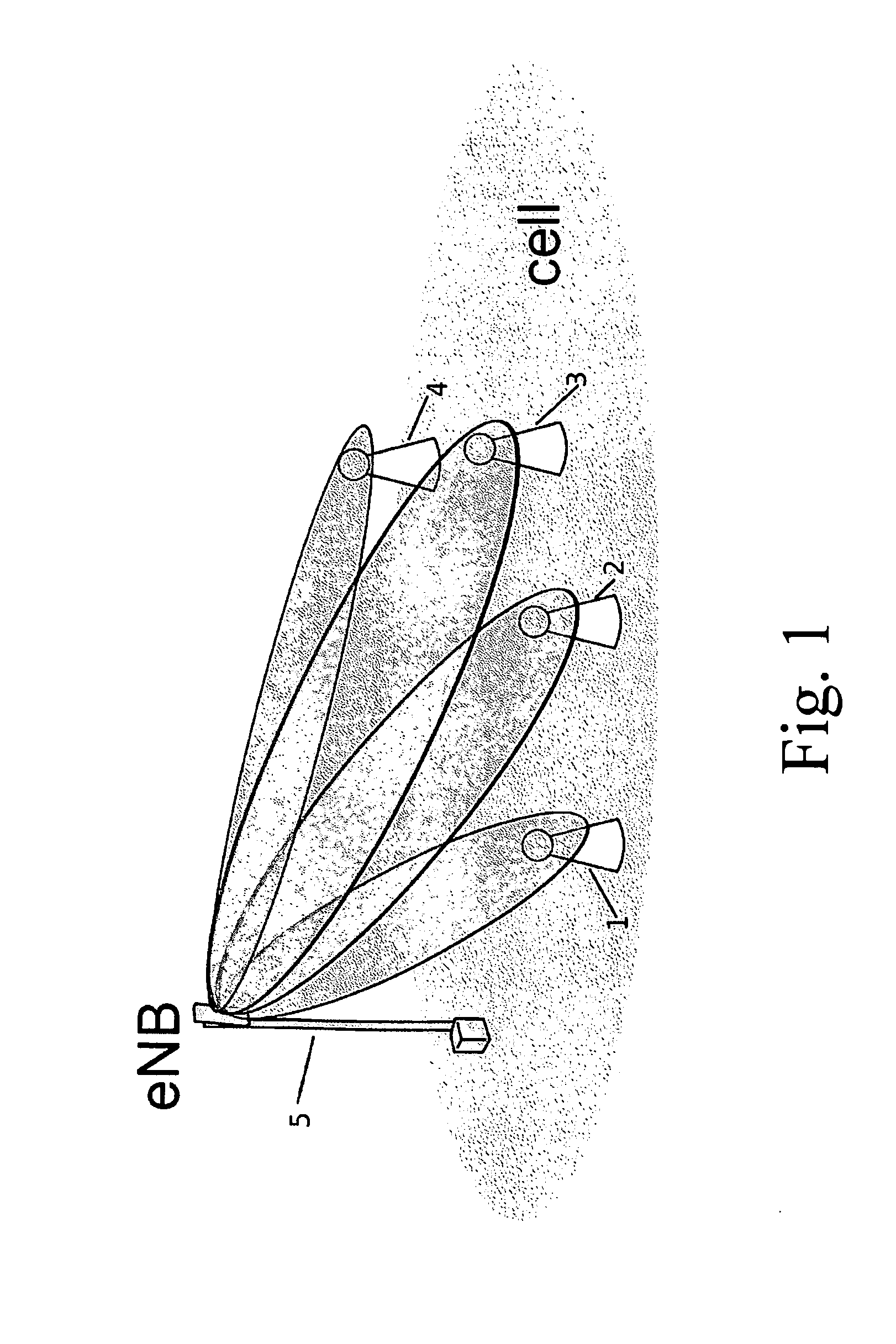

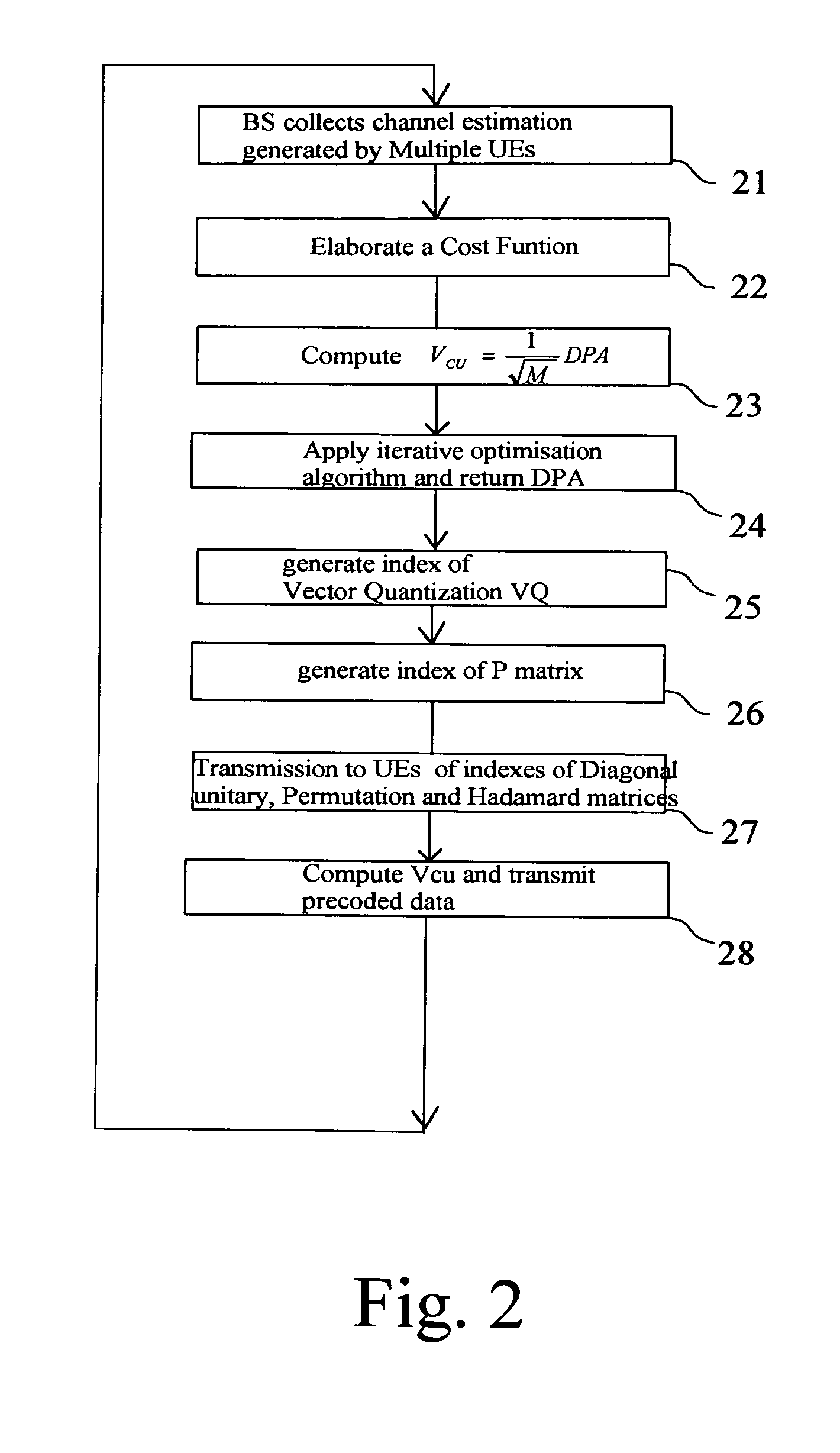

Process for Beamforming Data to be Transmitted by a Base Station in a MU-MIMO System and Apparatus for Performing the Same

InactiveUS20110299379A1Simple structureImprove performanceRadio transmissionOrthogonal multiplexFormation matrixUnitary matrix

A process for beamforming data to be transmitted in a MU-MIMO communication system comprising a base station and a selected set of User Equipments (UE) communicating with said base station; said data being precoded by said base station in accordance with a beamforming matrix complying with a precoding matrix under the form of: (formula 1) Where—M is the number of transmit antennas—D is a diagonal unitary matrix of the form D=diag (formula 2)—P is a permutation matrix interchanging only the last M−1 rows. —A is a general Hadamard matrix. and that the signaling information transmitted by the base station to the UE comprises at least a first and a second index which are representative of D, P and A.

Owner:ST ERICSSON FRANCE +1

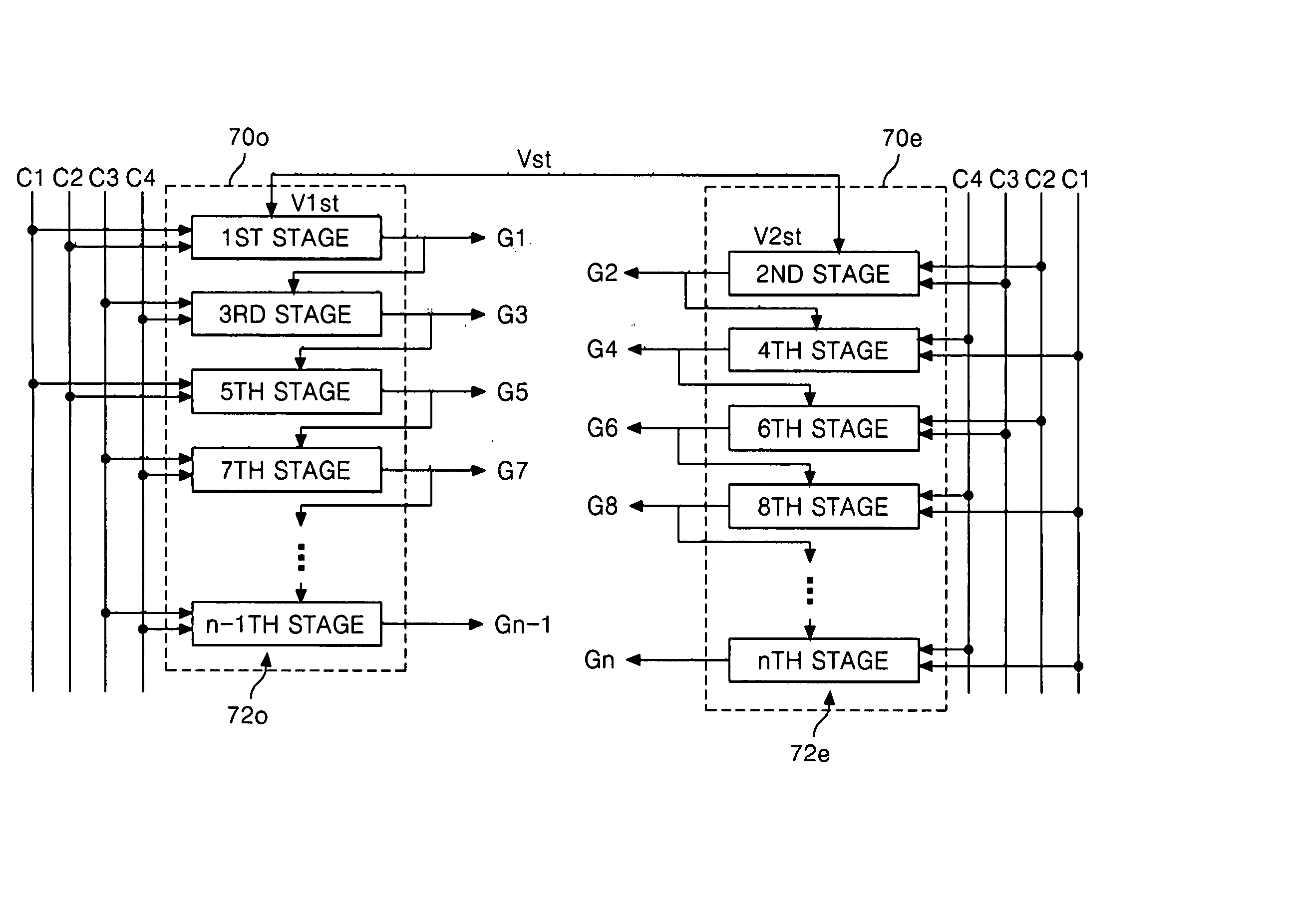

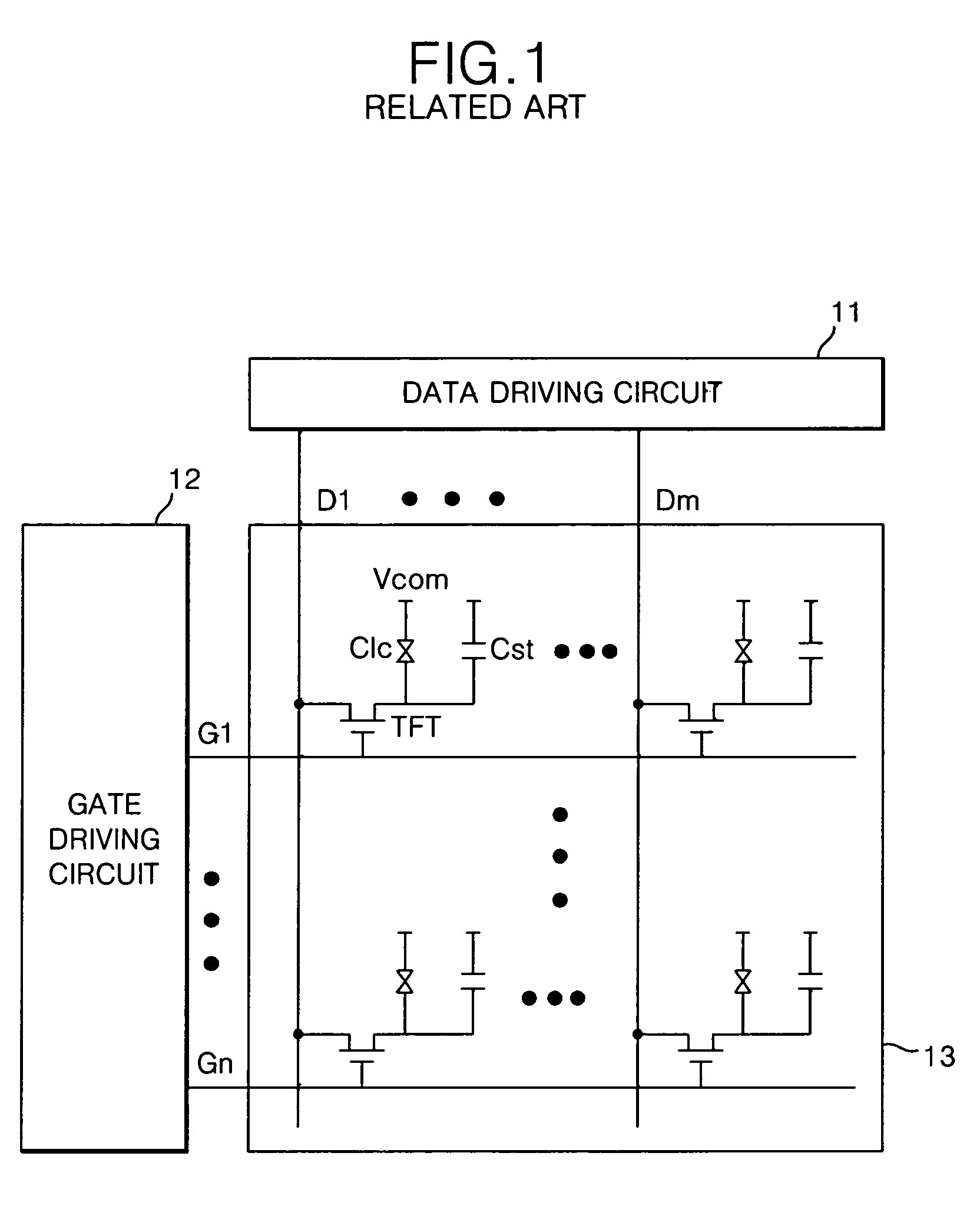

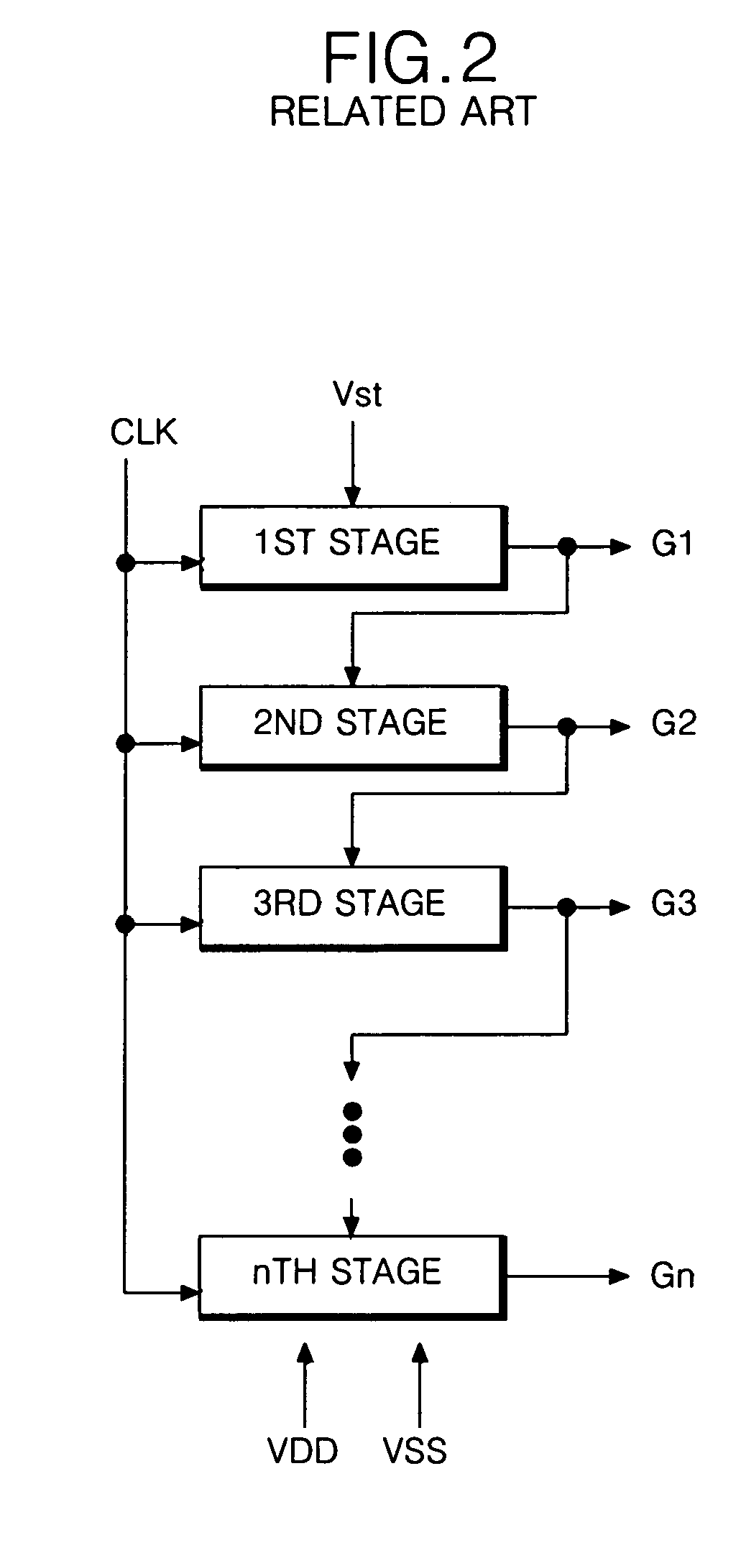

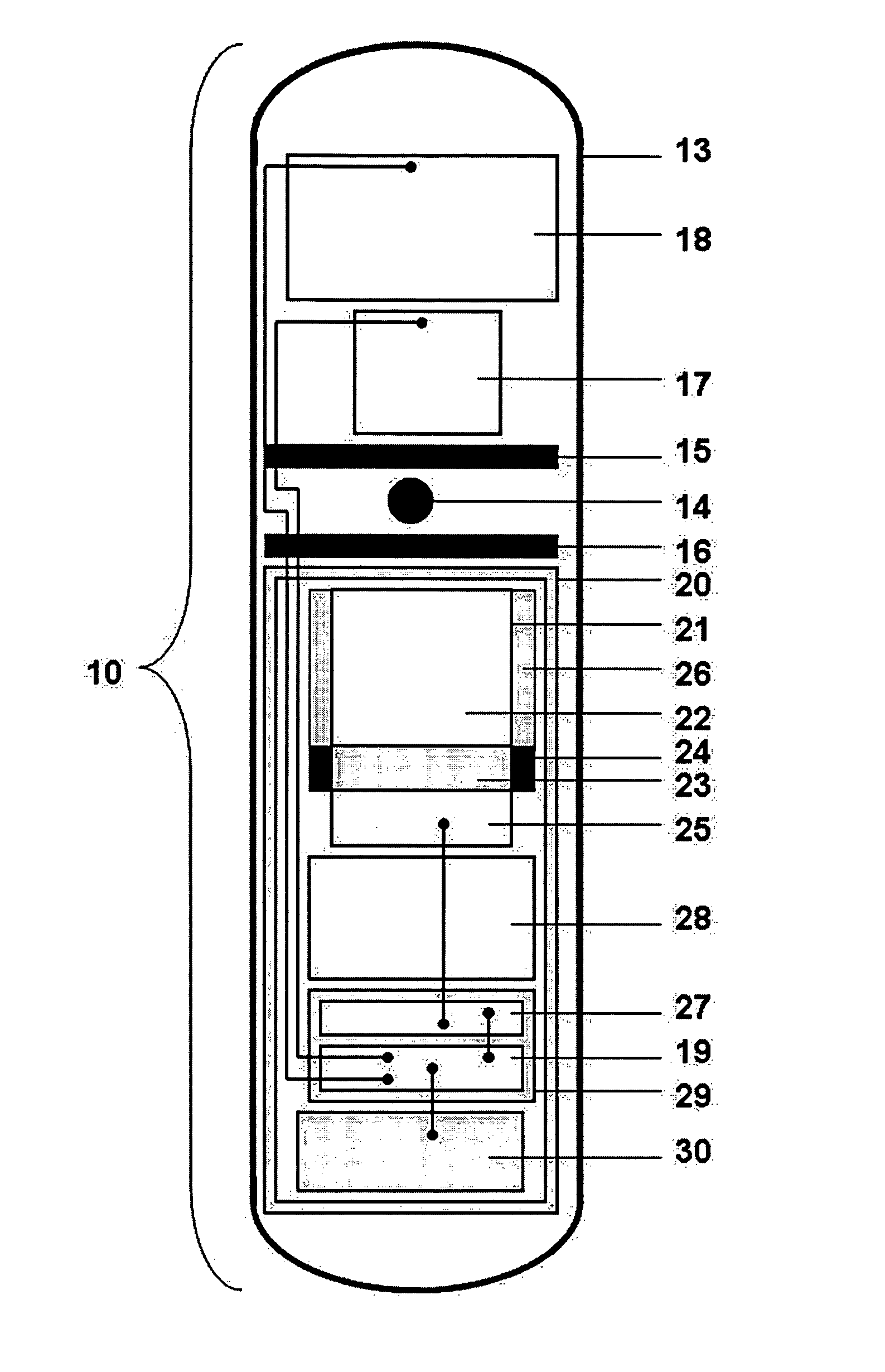

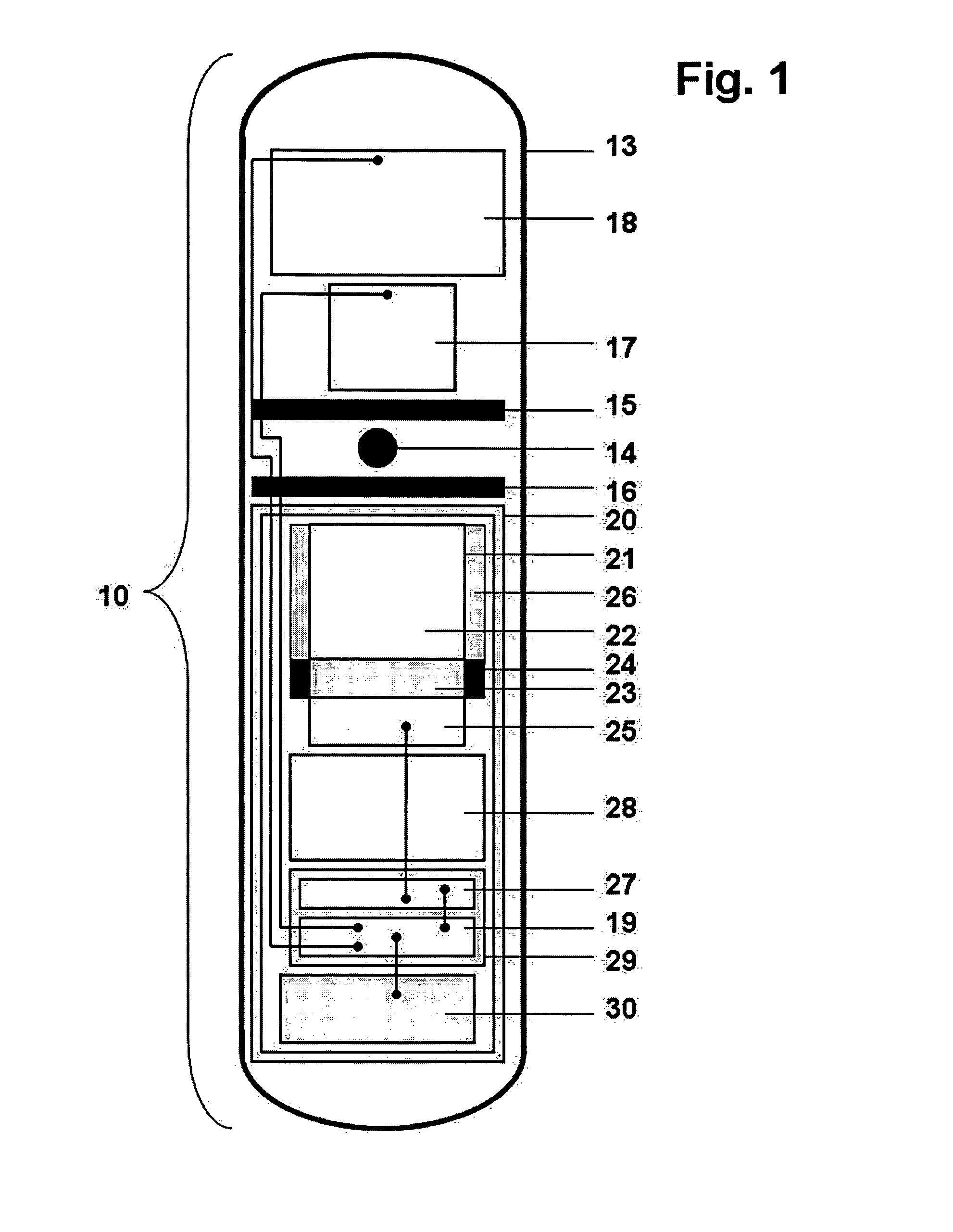

Liquid crystal display panel with built-in driving circuit

InactiveUS20060007085A1Reduce distortion problemsProlong lifeStatic indicating devicesDigital storageFormation matrixLiquid crystal cell

A liquid crystal display panel includes liquid crystal cells forming a matrix in a display area of the liquid crystal display panel; odd and even gate driving circuits provided at an outer area of the display area, the display area being positioned between the odd and even gate driving circuits, the odd driving circuit including a plurality of odd stages, the even driving circuit including a plurality of even stages; a plurality of gate lines, including even gate lines and odd gate lines in the liquid crystal cell matrix, the odd gate lines being driven by the odd driving circuit, and the even gate lines being driven by the even driving circuit, wherein a pitch of each of the odd stages and the even stages corresponds to size larger than a pitch of the liquid crystal cell.

Owner:LG DISPLAY CO LTD

Stereoscopic display apparatus

Owner:KK TOSHIBA

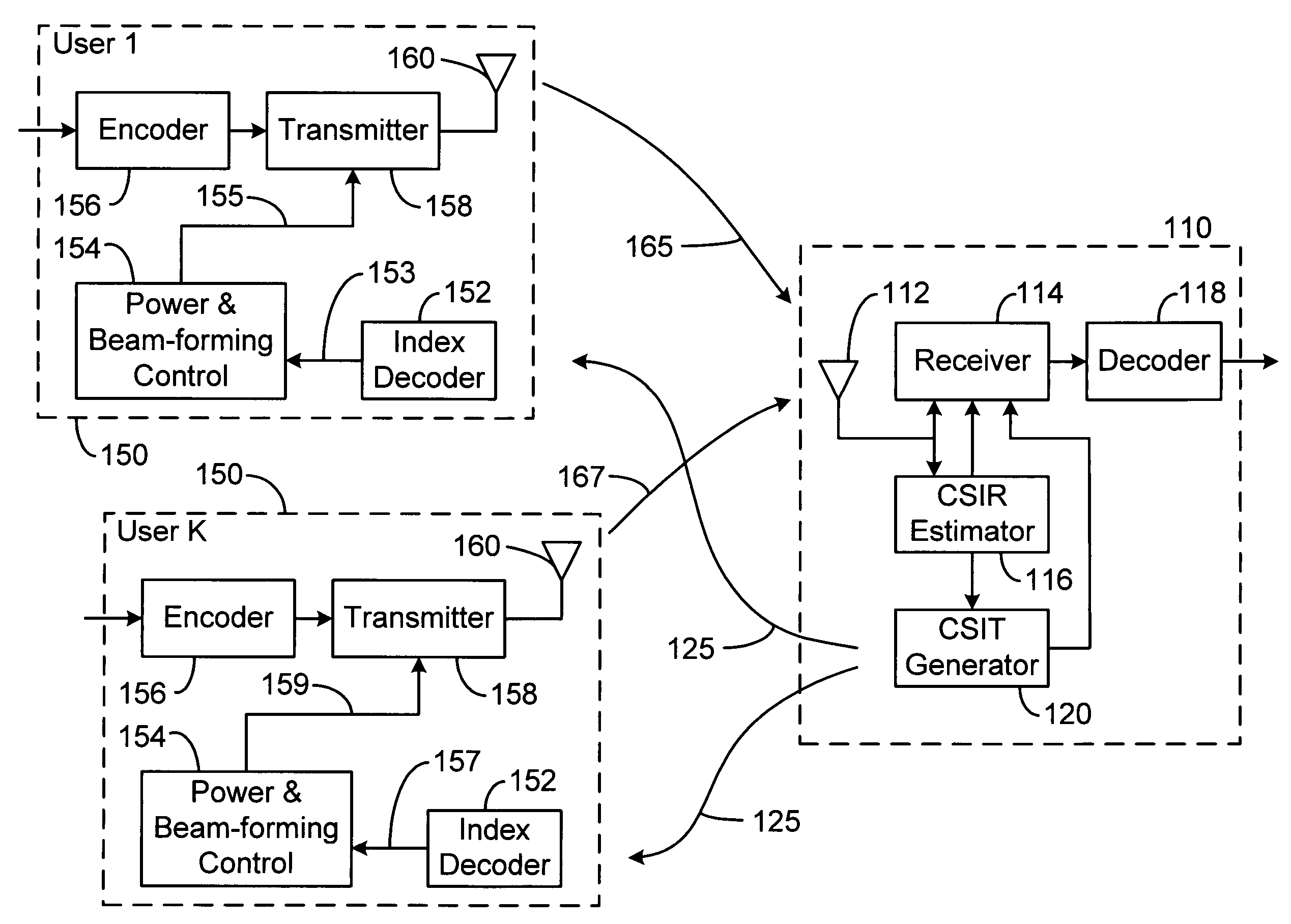

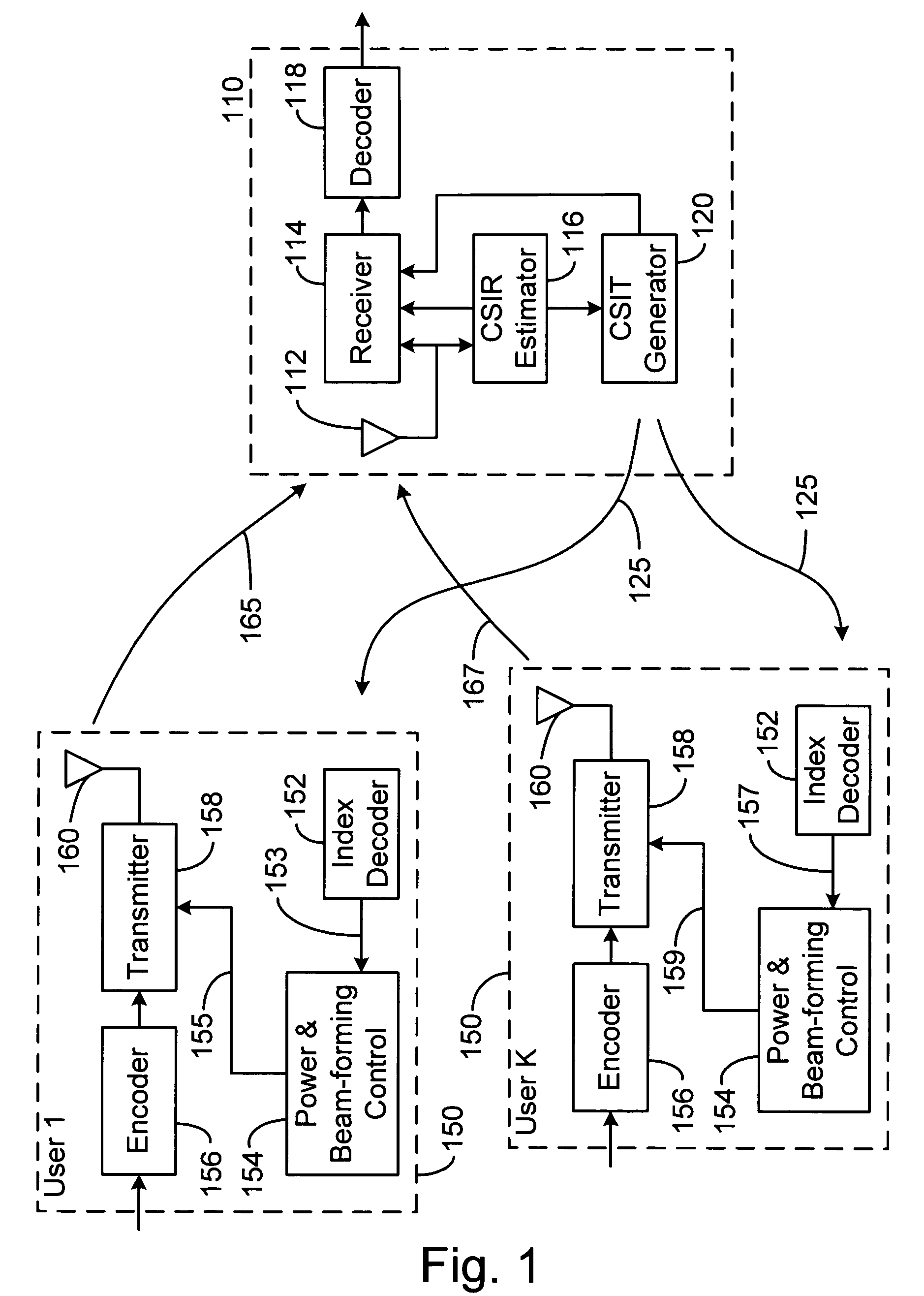

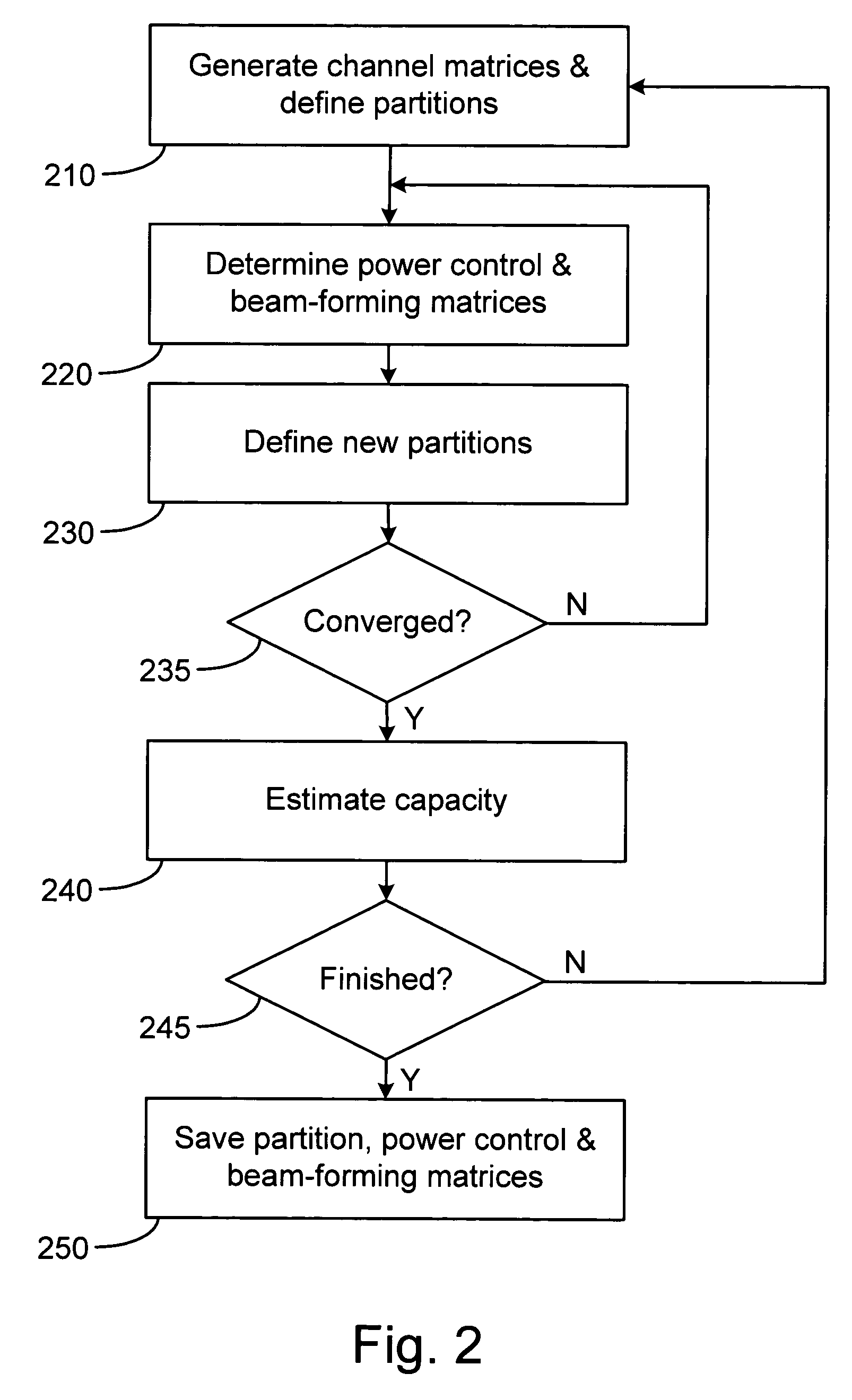

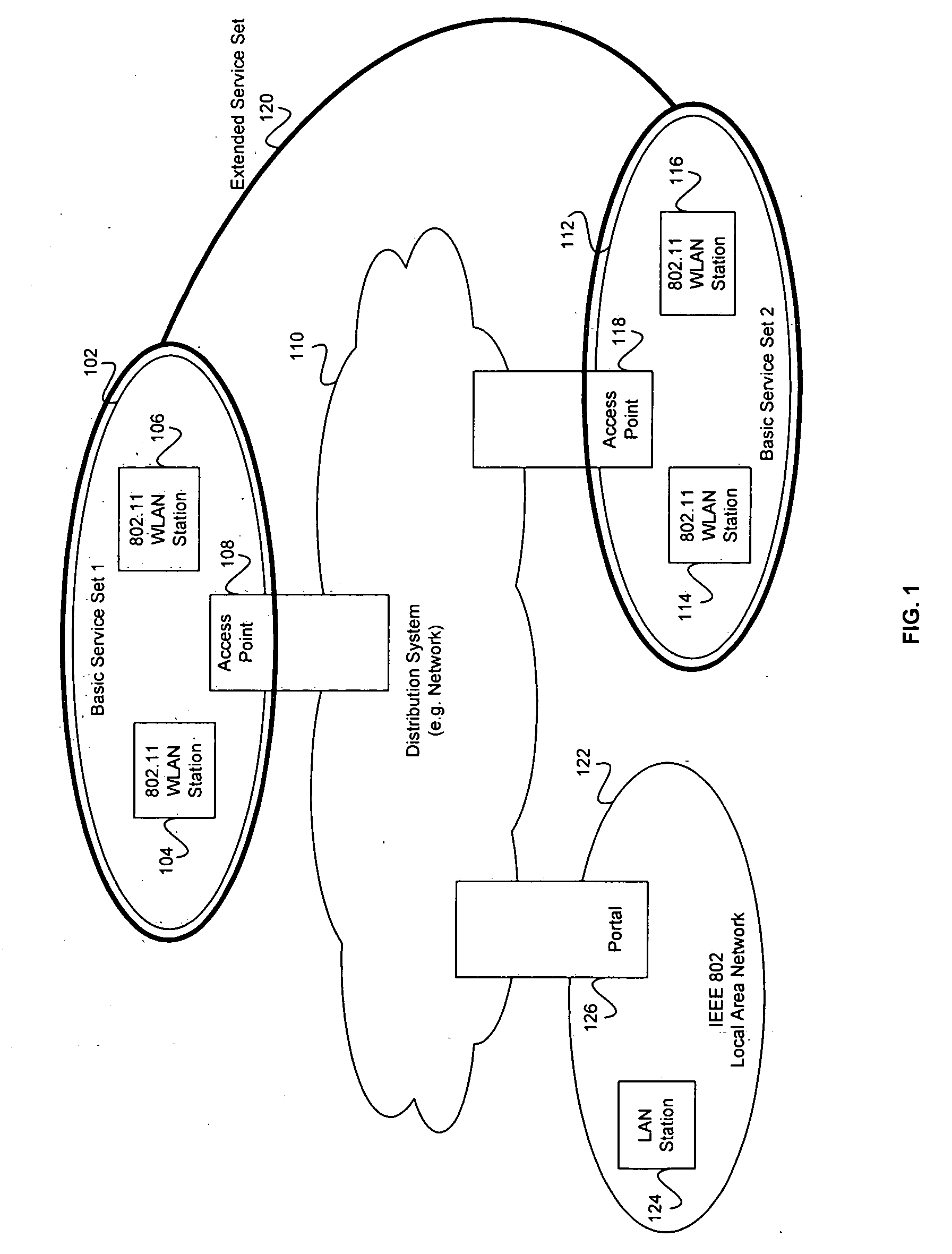

System and method for multi-access MIMO channels with feedback capacity constraint

ActiveUS7257167B2Radio wave direction/deviation determination systemsBaseband system detailsData streamFormation matrix

Systems and methods of MIMO wireless communication system with partial feedback are disclosed. In one embodiment, a base station estimates the channel matrices of the K mobile units and transmits an index value corresponding to each of the estimated channel matrix. Each mobile unit selects a power control matrix and beam-forming matrix based on the received index value and transmits its data stream to the base station using the selected power control and beam-forming matrix. A method for generating the sets of power control matrices, beam-forming matrices, and partitions of the channel matrix space is disclosed.

Owner:HFI INNOVATION INC

Method and system for quantization for a general beamforming matrix in feedback information

ActiveUS20070160011A1Radio/inductive link selection arrangementsRadio transmissionFormation matrixSignal-to-noise ratio (imaging)

Aspects of a method and system for utilizing Givens rotation expressions for quantization for a general beamforming matrix in feedback information. In one aspect of the invention, feedback information is computed at the receiving MIMO wireless device based on a geometric mean decomposition (GMD) method. The feedback information may include a matrix that describes a wireless medium. The matrix may represent a multiplicative product of at least one rotation matrix and at least one diagonal phase rotation matrix. Each of the rotation matrices may include at least one matrix element whose value is based on Givens rotation angle. The transmitting MIMO wireless device may subsequently transmit a plurality of signals via the wireless medium based on the received matrix information. The signal strength and / or signal to noise ratio (SNR) measurement (as measured in decibels, for example) associated with each of the transmitted plurality of signals may be about equal.

Owner:AVAGO TECH INT SALES PTE LTD

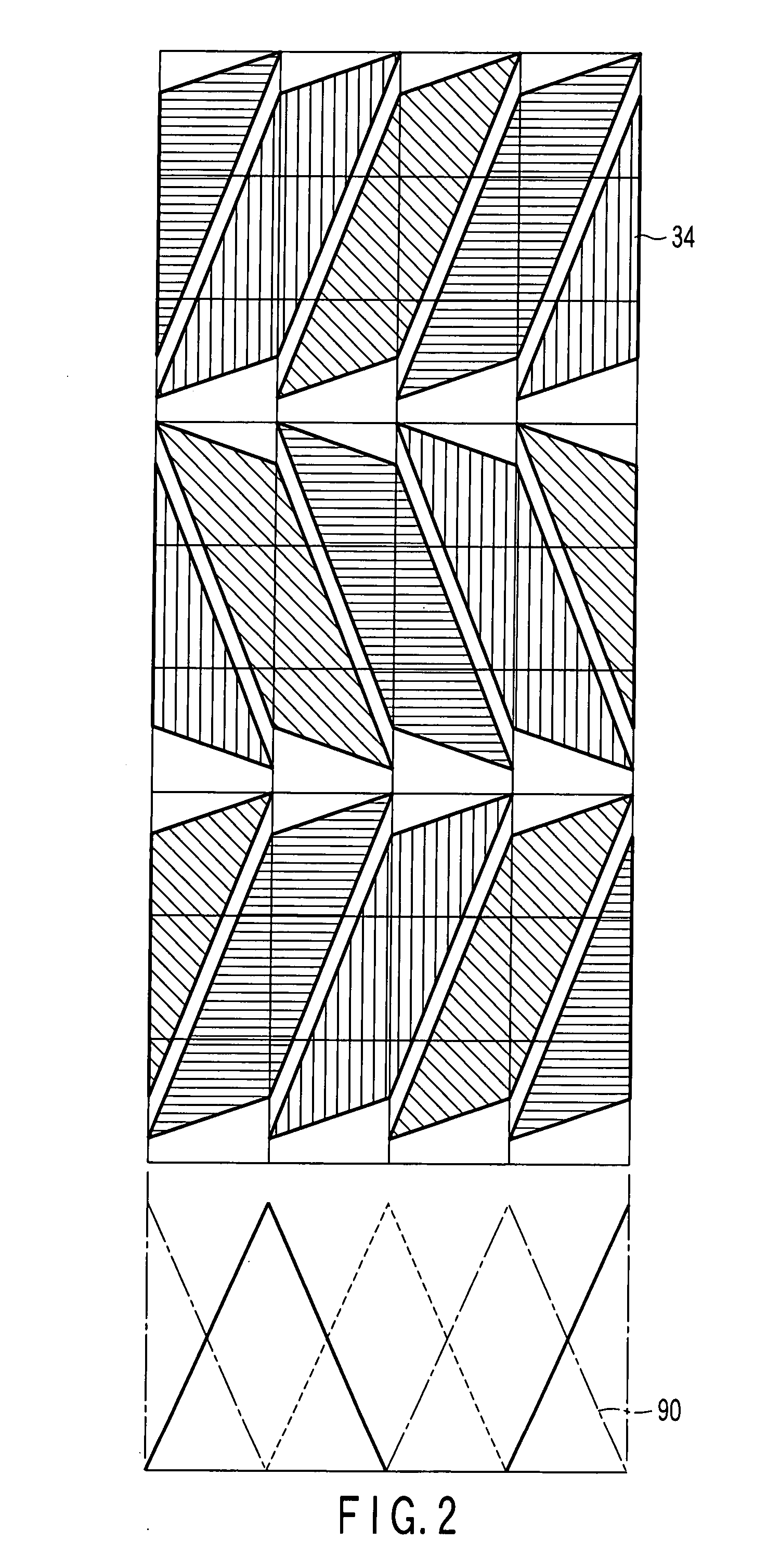

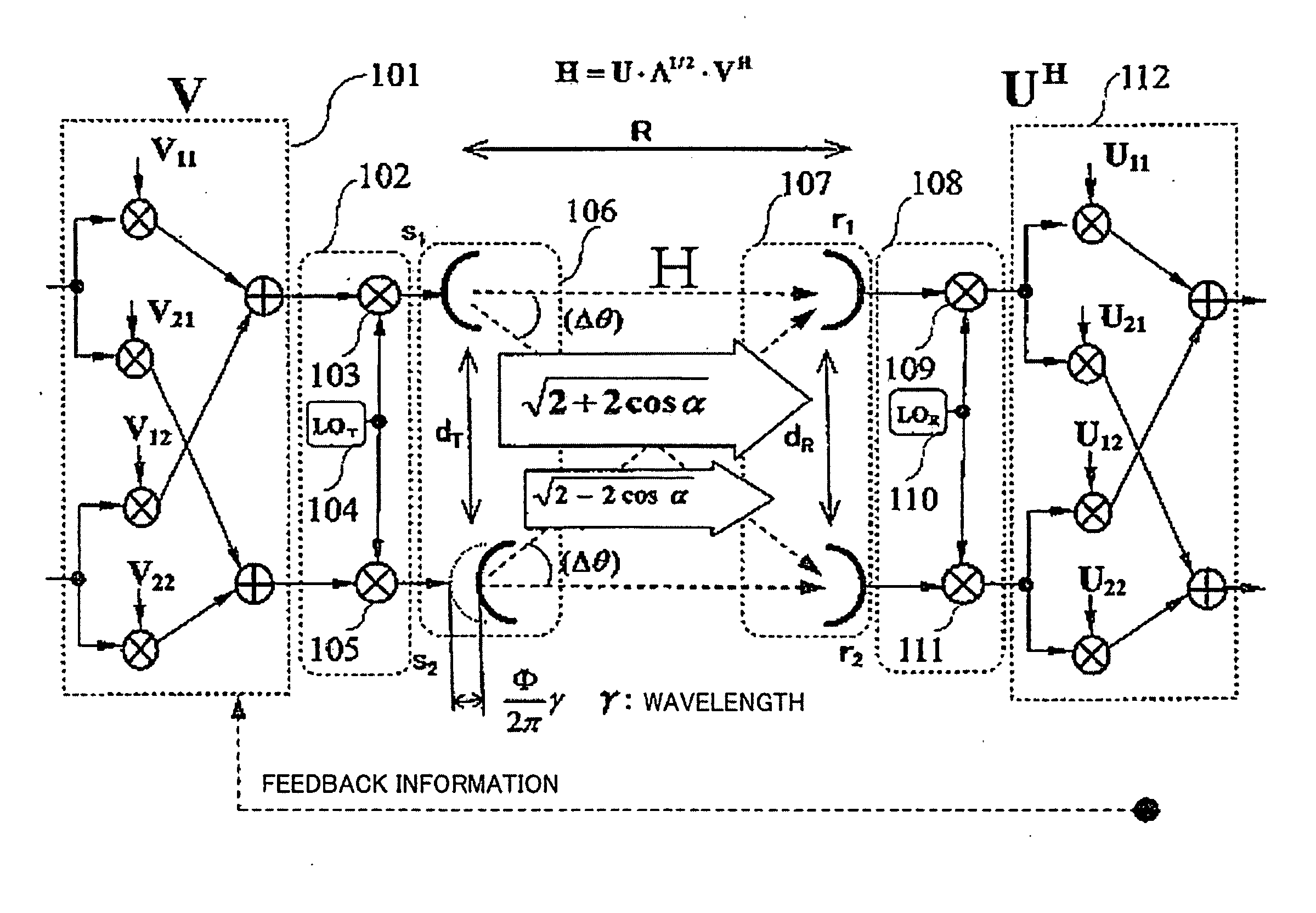

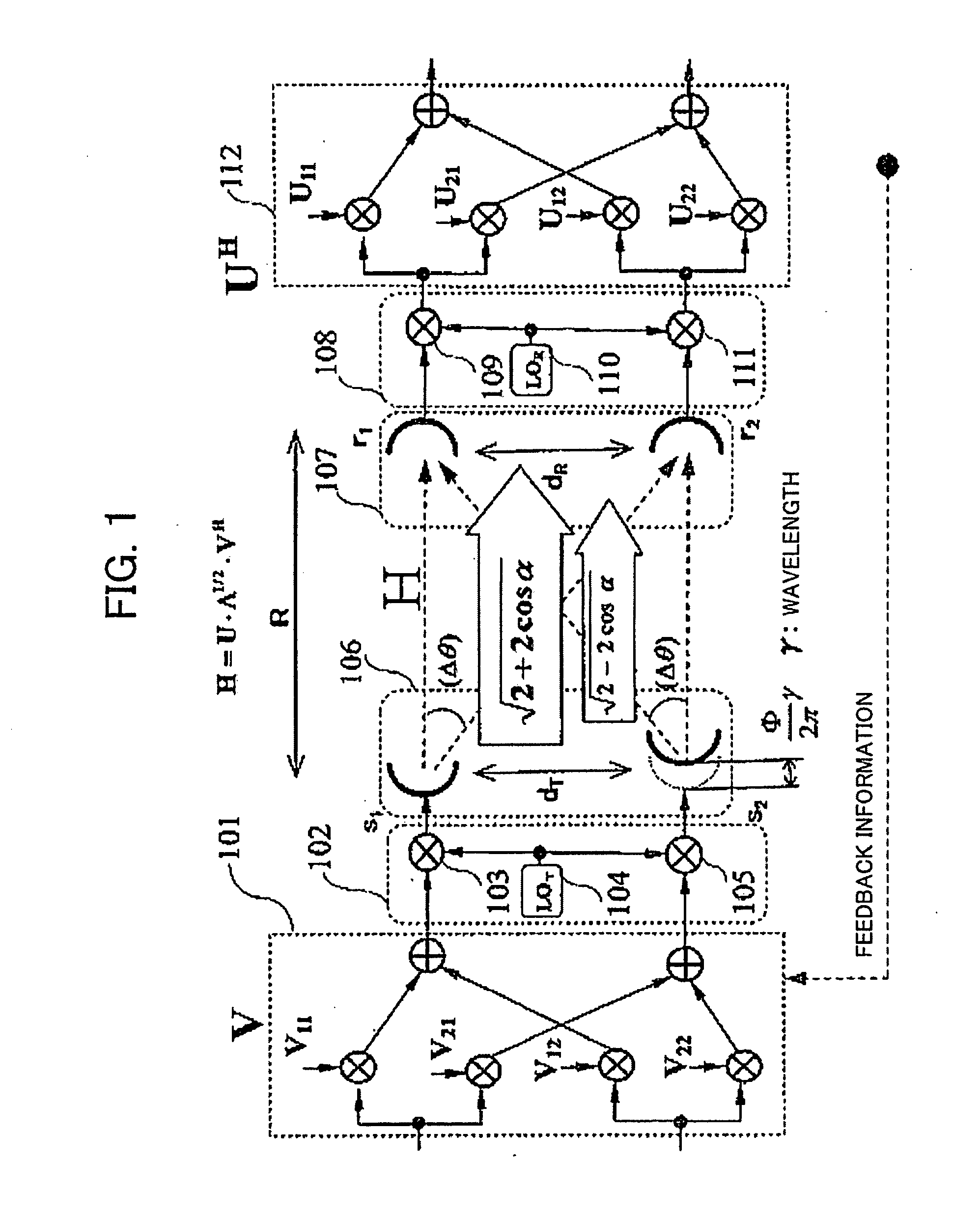

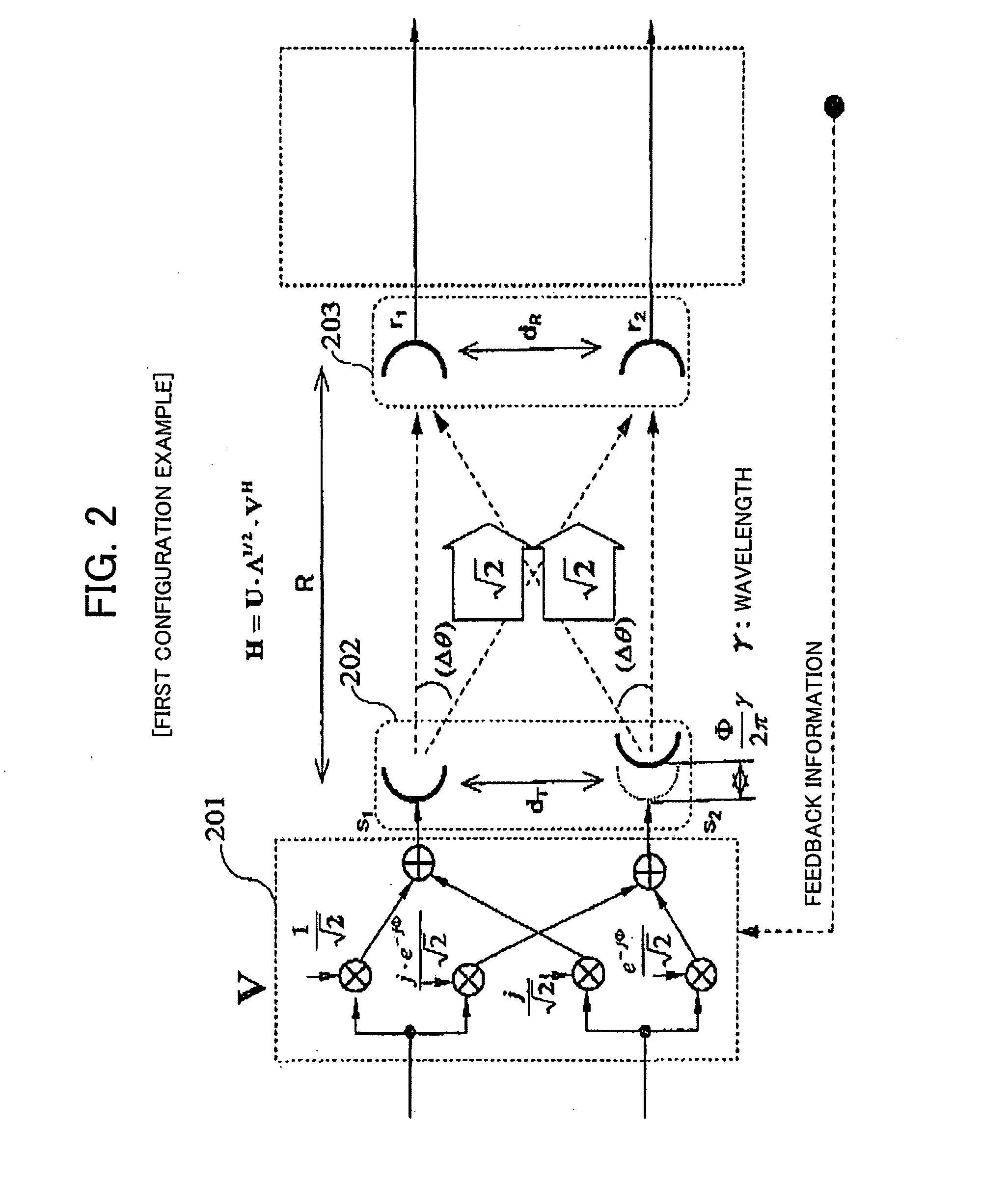

MIMO communication system having deterministic channels and method

InactiveUS20090296846A1Large communication capacityNone is problem freeMultiplex communicationDiversity/multi-antenna systemsFormation matrixChannel capacity

A MIMO communication system having deterministic channels wherein MIMO is applied to line-of-sight channels having a fixed geometrical positional relationship so as to increase the channel capacity. A line-of-sight MIMO communication system having a plurality of channels includes a channel matrix calculation processing section on a transmission or reception side or both of the transmission and reception sides. The channel matrix calculation processing section updates an orthogonal channel formation matrix in accordance with a fluctuation of a transmission antenna position or reception antenna position or a fluctuation of the channels.

Owner:NEC CORP

Method and system for utilizing givens rotation expressions for asymmetric beamforming matrices in explicit feedback information

Aspects of a method and system for utilizing Givens rotation expressions for asymmetric beamforming matrices in explicit feedback information are presented. In one aspect of the invention, Givens matrices may be utilized to reduce a quantity of information communicated in explicit feedback information via an uplink RF channel. The explicit feedback information may include specifications for a feedback beamforming matrix that may be utilized when transmitting signals via a corresponding downlink RF channel. The feedback beamforming matrix may represent a rotated version of an un-rotated matrix. The Givens matrices may be utilized to apply one or more Givens rotations to un-rotated matrix. The feedback beamforming matrix may be computed based on a matrix product of a plurality of Givens matrices. The feedback beamforming matrix may be encoded utilizing fewer bits than may be required to encode the un-rotated matrix.

Owner:AVAGO TECH INT SALES PTE LTD

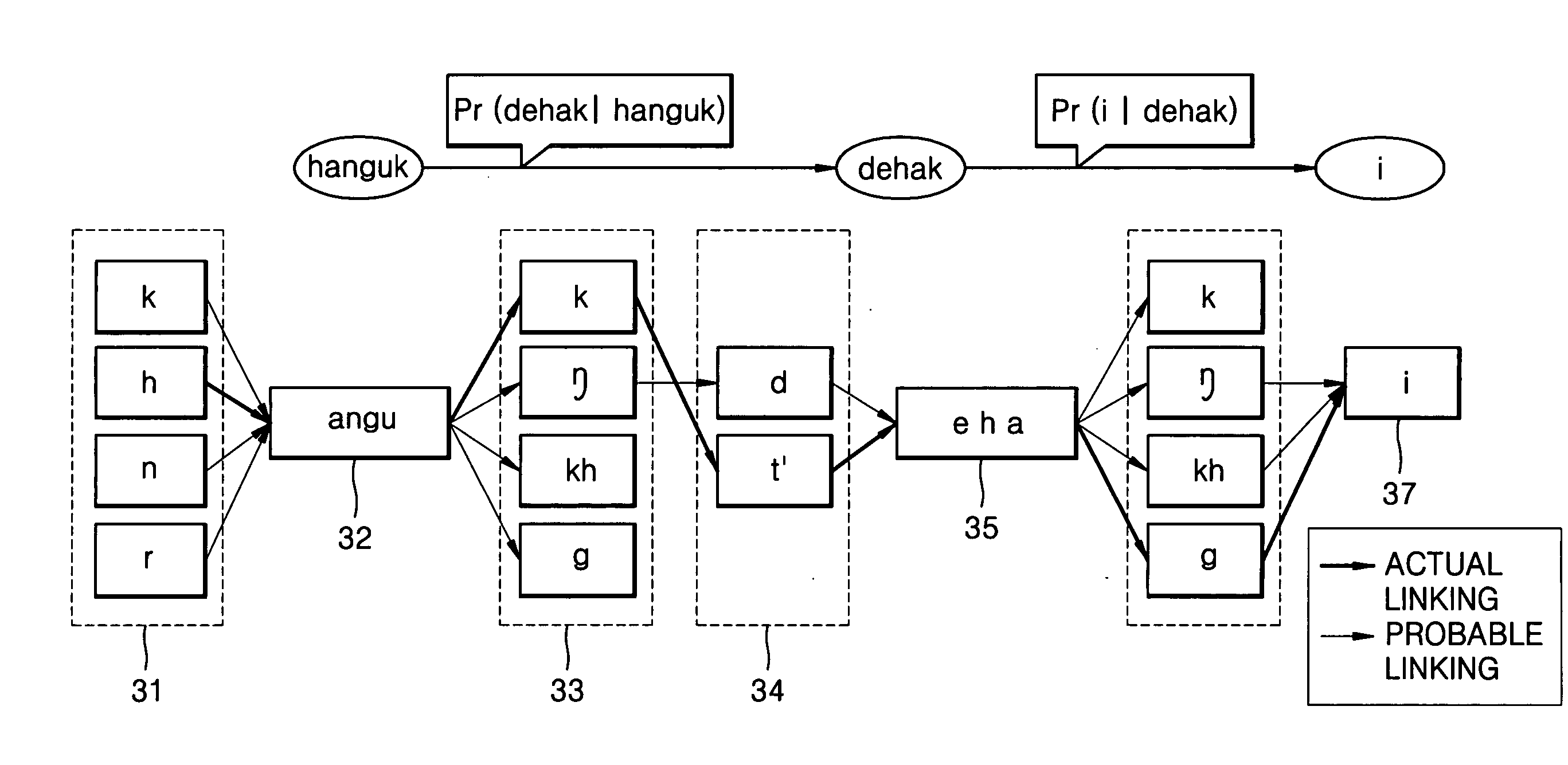

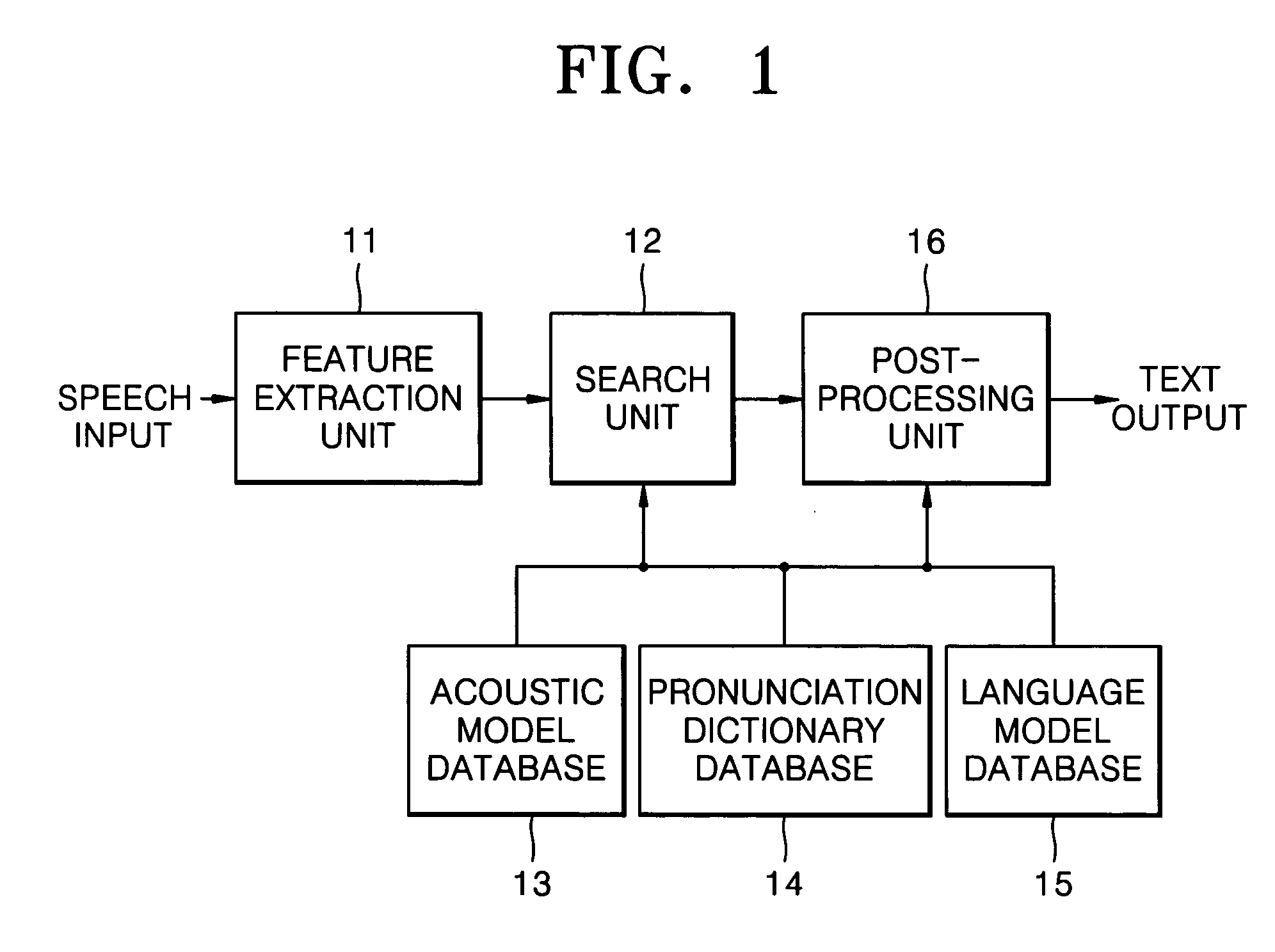

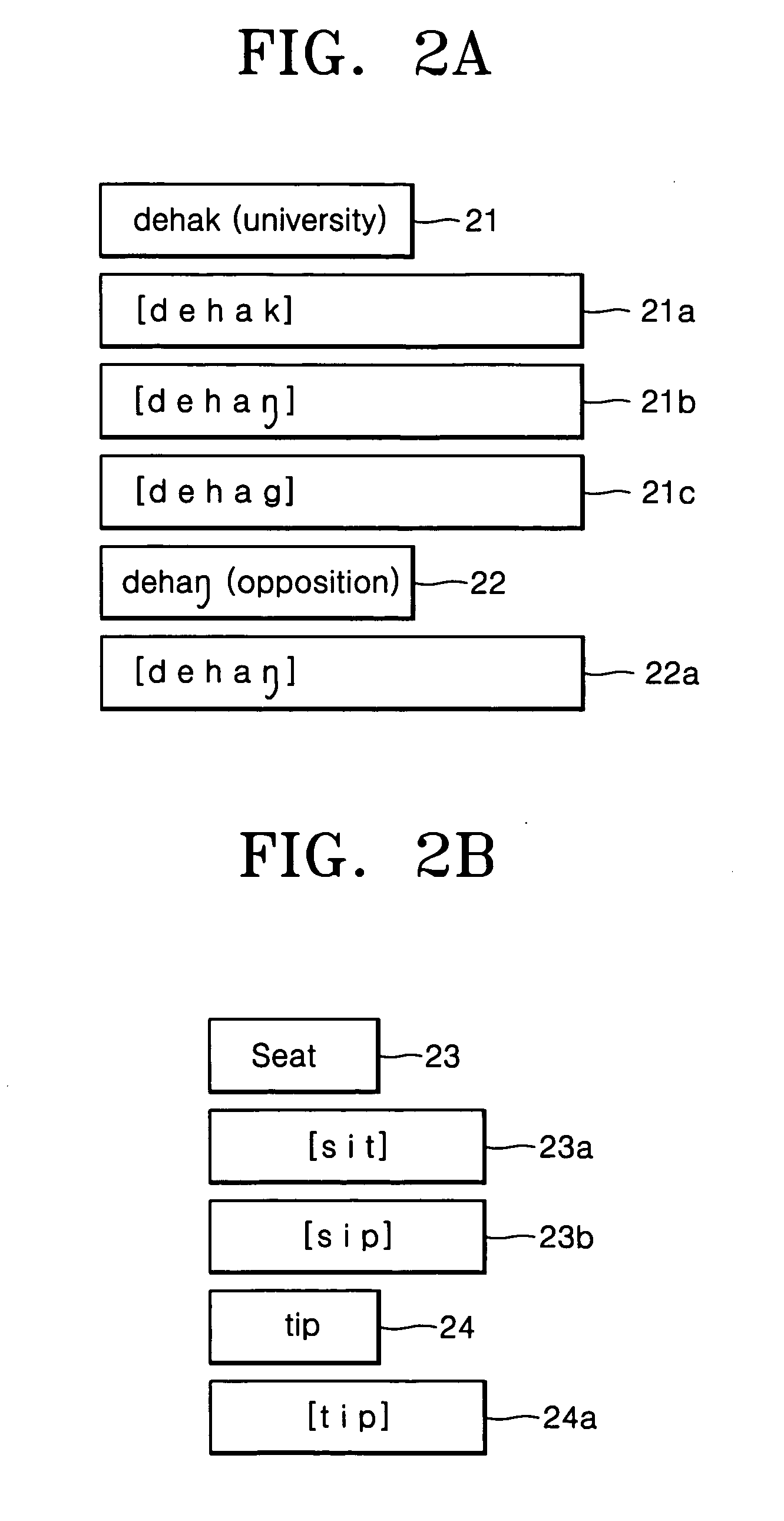

Continuous speech recognition method and system using inter-word phonetic information

A continuous speech recognition method and system are provided. The continuous speech recognition method includes constructing a pronunciation dictionary database including at least one pronunciation representation for each word which is influenced by applying phonological rules, wherein the pronunciation representation for the coda of a first word or the pronunciation representation for the onset of a second word following the first word is additionally indexed with an identifier if it does not match the phonetic pronunciation of its spelling, forming inter-word phonetic information in matrix form by combination of a number of all probable phonetic pairs, each of which is basically comprised of the coda of a first word and the onset of a second word following the first word, wherein the coda of the first word or the onset of the second word is indexed with an identifier if they undergo phonological changes and performing speech recognition on feature vectors extracted from an input speech signal with reference to the pronunciation dictionary database and the inter-word phonetic information.

Owner:SAMSUNG ELECTRONICS CO LTD

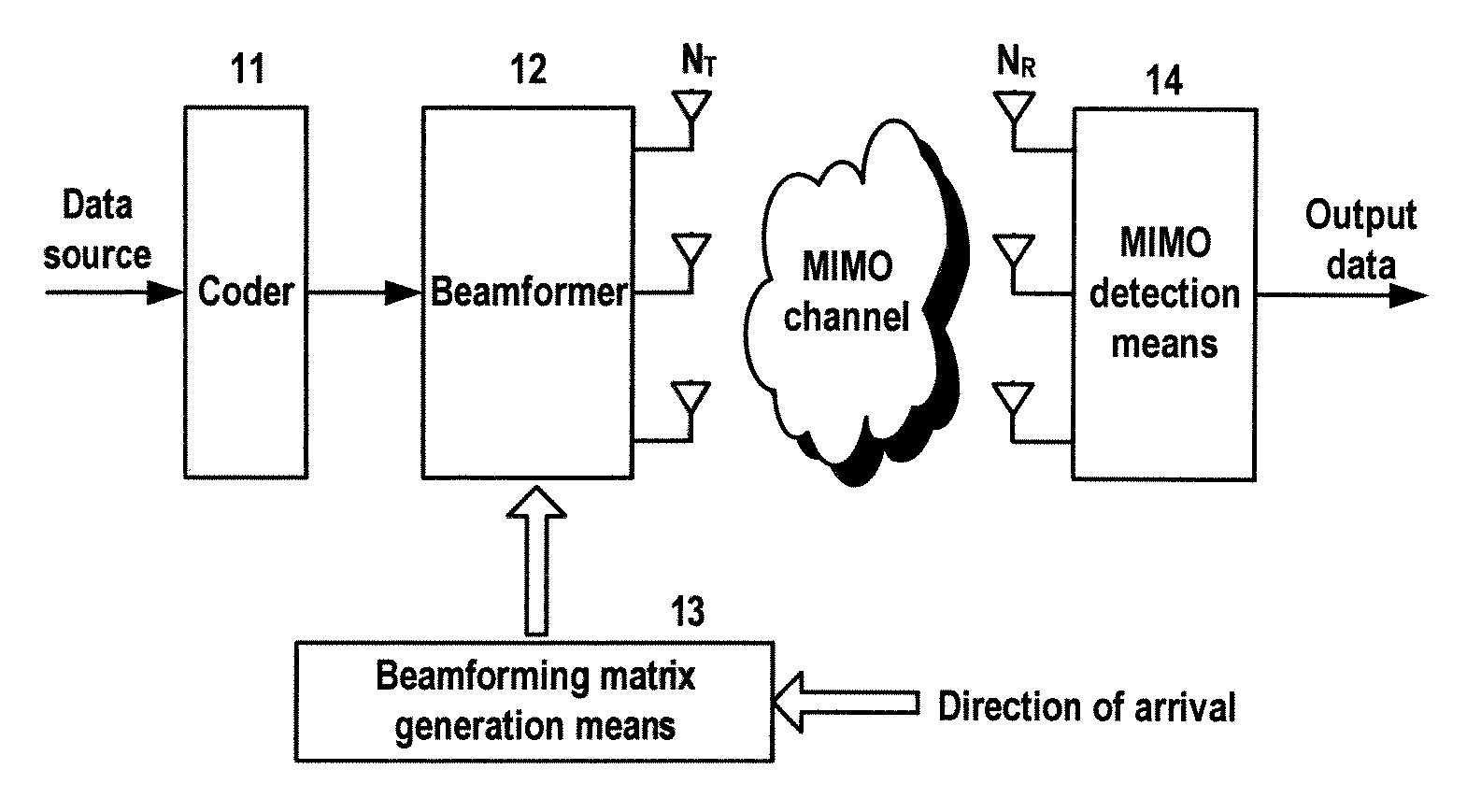

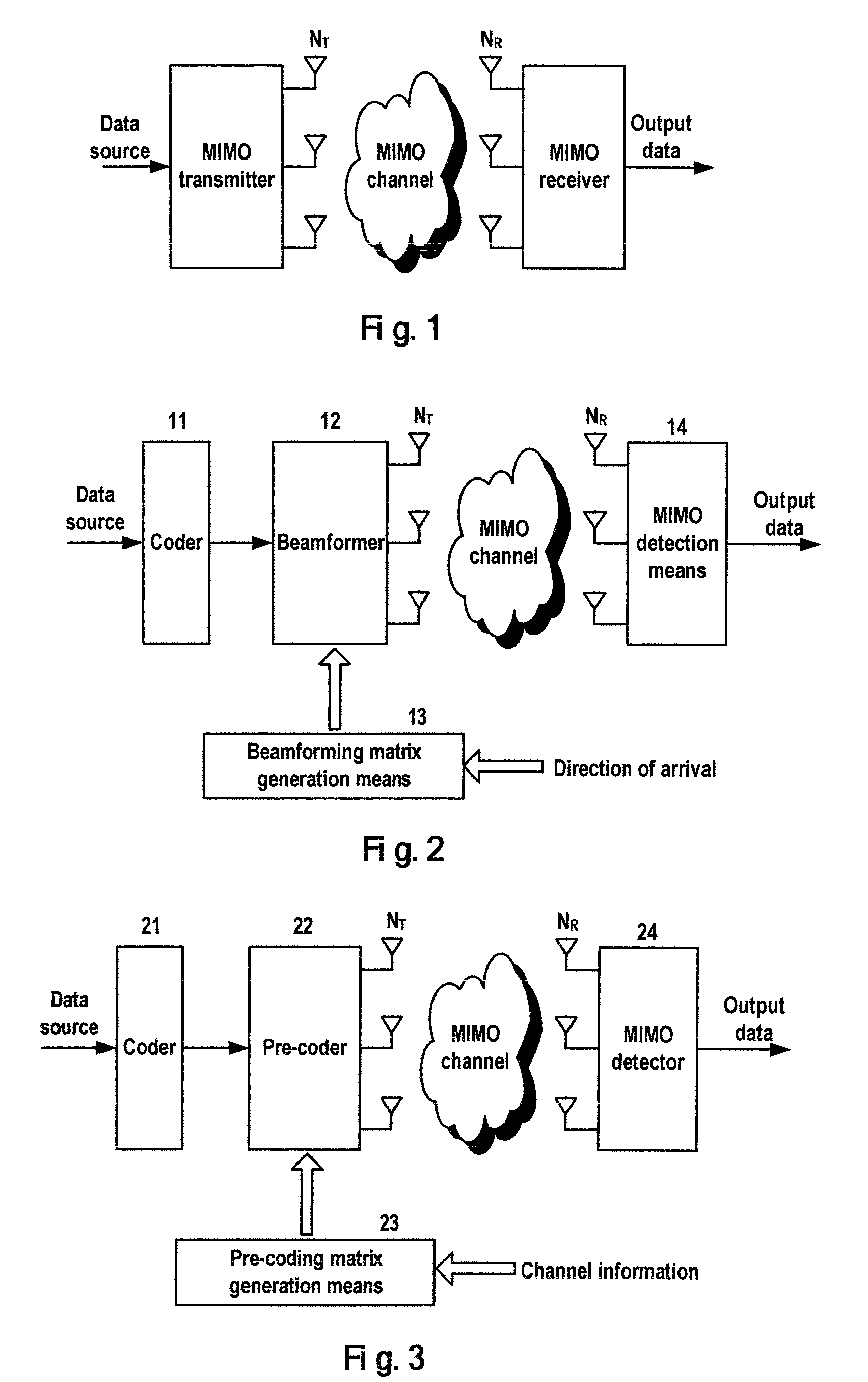

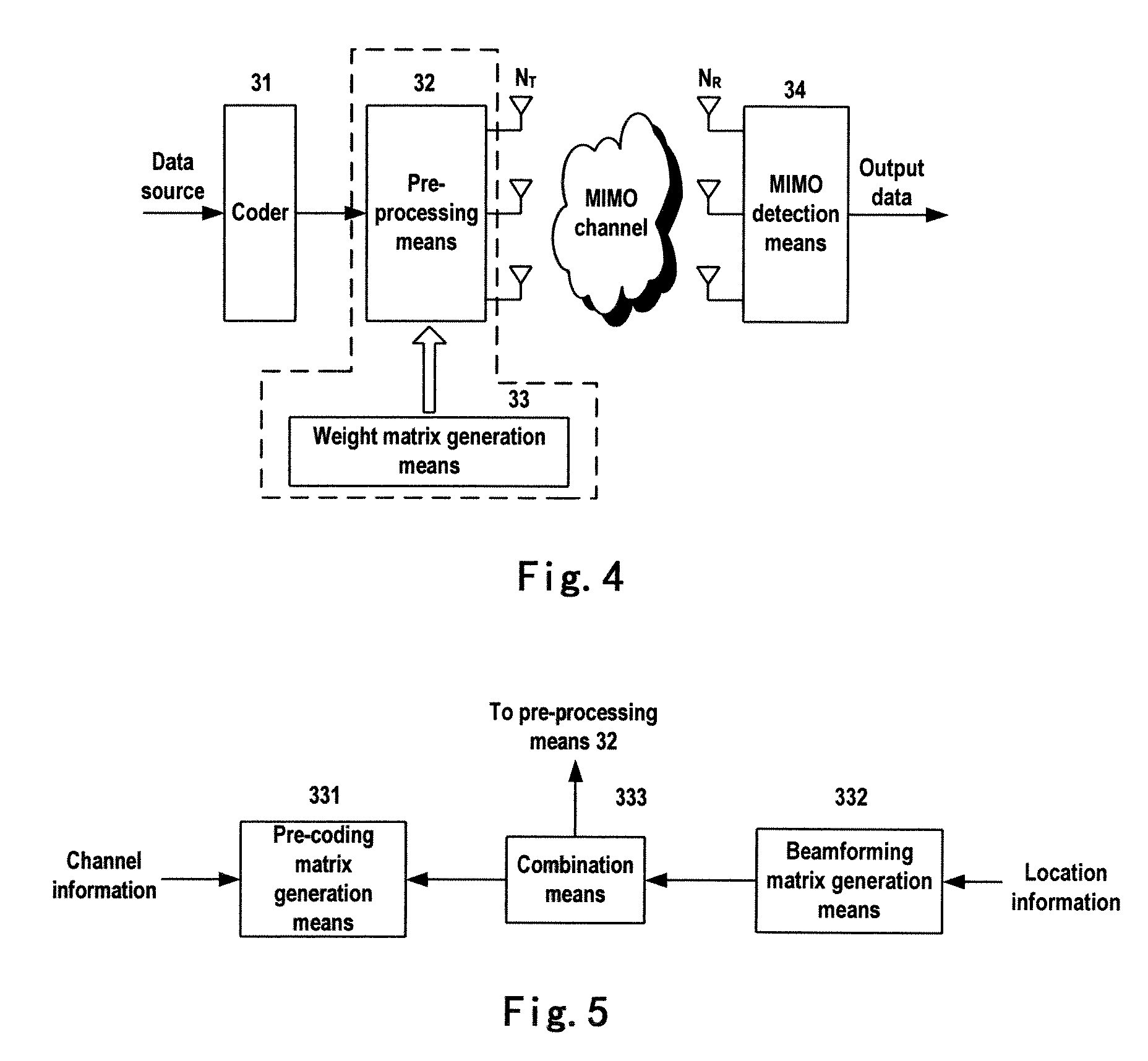

Method and apparatus for pre-processing data to be transmitted in multiple-input communication system

InactiveUS20100303170A1Improve performanceModulated-carrier systemsDiversity/multi-antenna systemsCommunications systemFormation matrix

A method for pre-processing data to be transmitted in a multiple-input communication system comprises the following steps: generating a beamforming matrix and a pre-coding matrix; combining the beamforming matrix and the pre-coding matrix to generate a weight matrix; and pre-processing the data by using the generated weight matrix. There are also provided a transmitter, a base station, and a communication system using the method.

Owner:ALCATEL LUCENT SAS

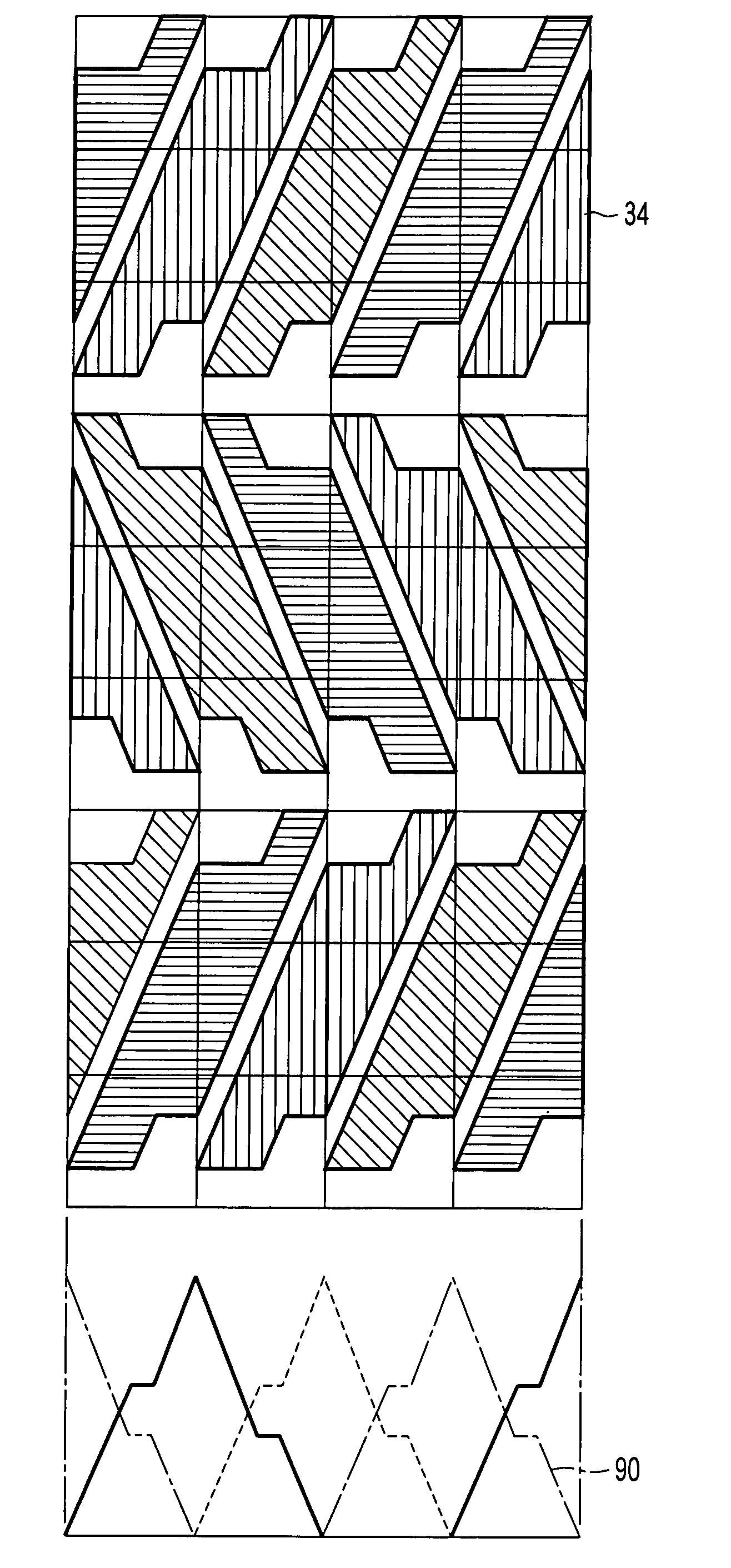

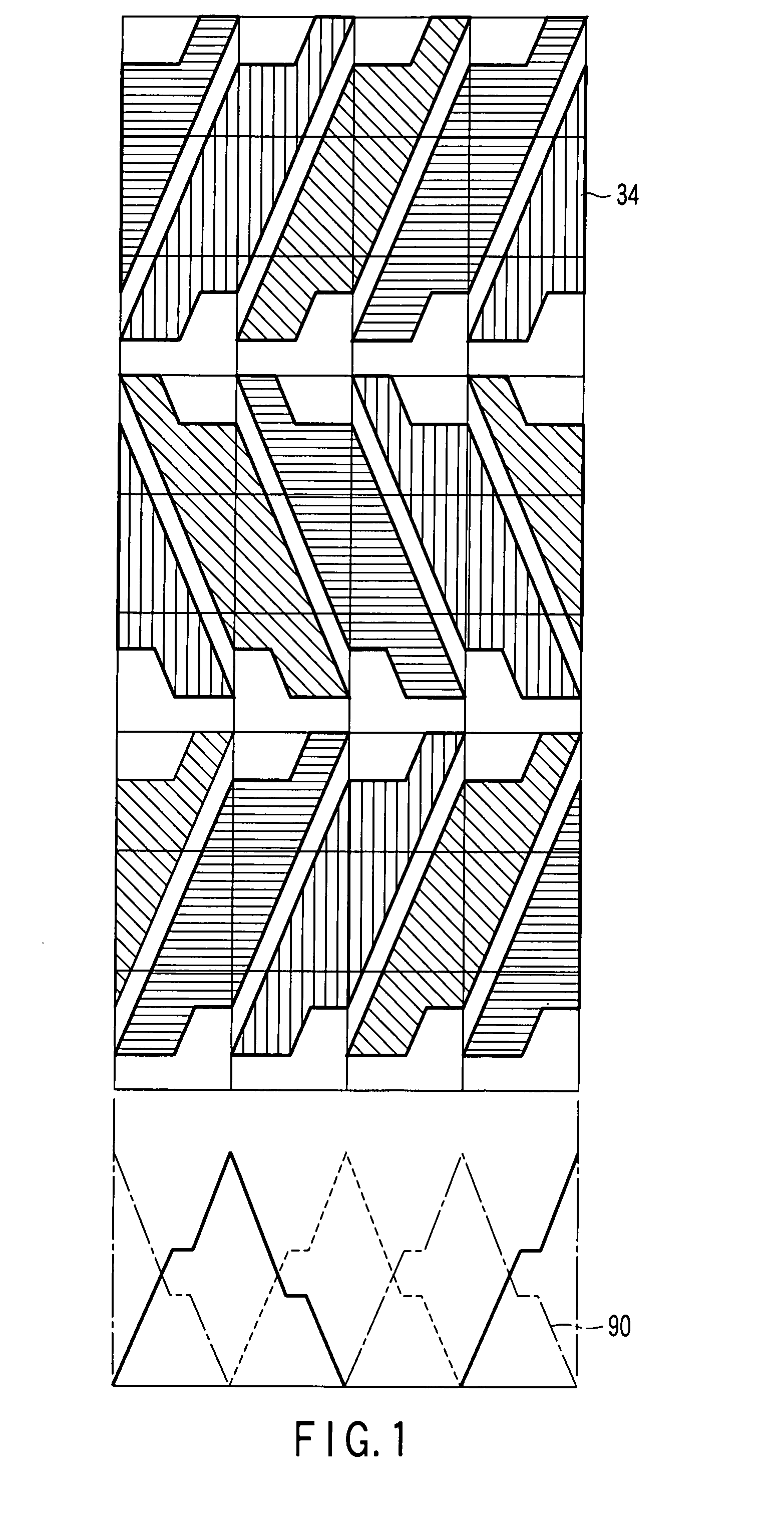

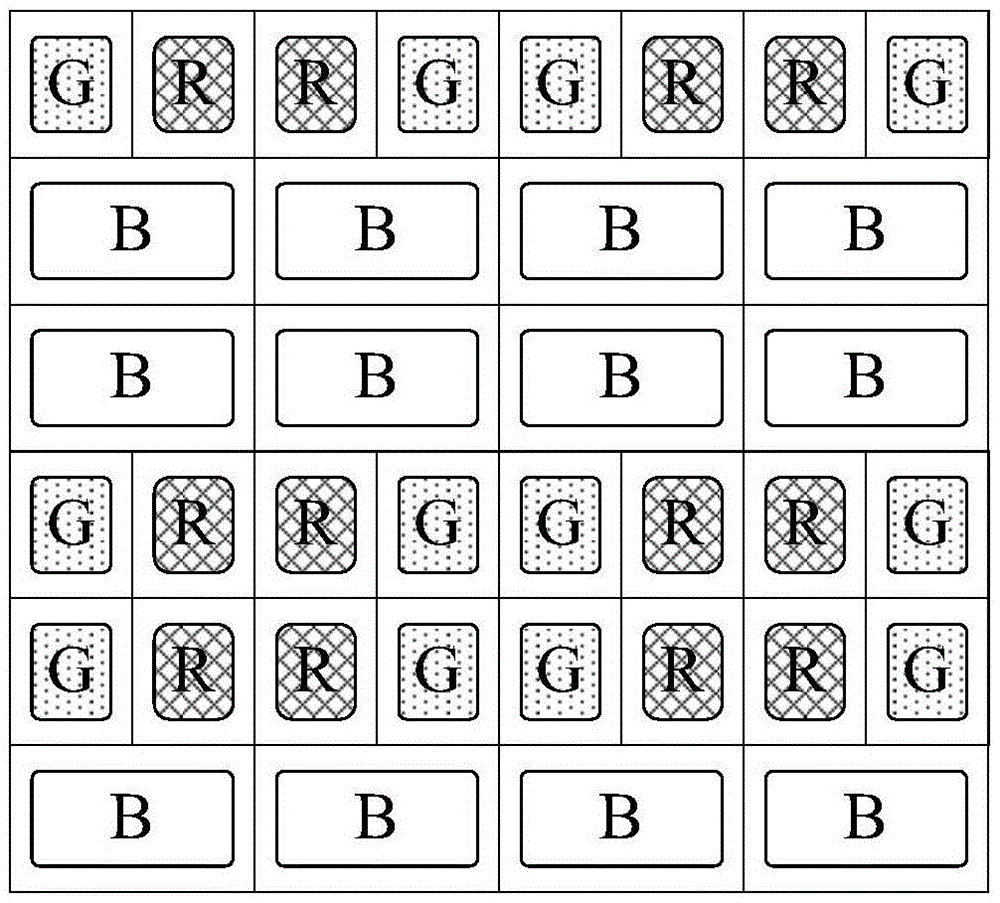

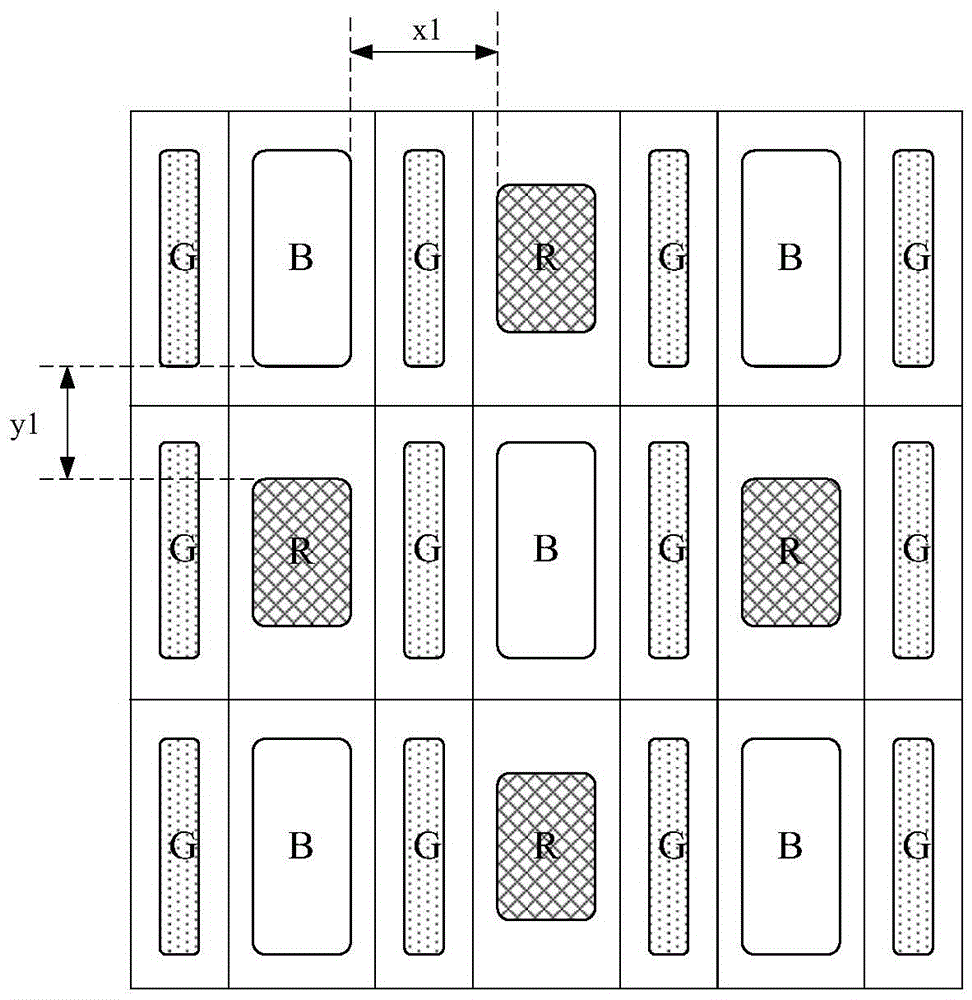

Pixel arrangement structure and manufacturing method thereof and display

ActiveCN105552102ASmall footprintIncrease display resolutionSolid-state devicesSemiconductor/solid-state device manufacturingFormation matrixComputer science

The invention relates to a pixel arrangement structure, which comprises a plurality of first repeating unit and second repeating units, wherein the first repeating units and the second repeating units alternately repeat in a row direction and a column direction in sequence to form a matrix arrangement; each first repeating unit comprises two green sub-pixels and a blue sub-pixel; each second repeating unit comprises two green sub-pixels and a red sub-pixel; and each red sub-pixel and each blue sub-pixel are shared by four green sub-pixels to form four pixel units. The invention further relates to a display employing the pixel arrangement structure and a manufacturing method of the pixel arrangement structure. The pixel arrangement structure and the display can provide relatively high display resolution.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

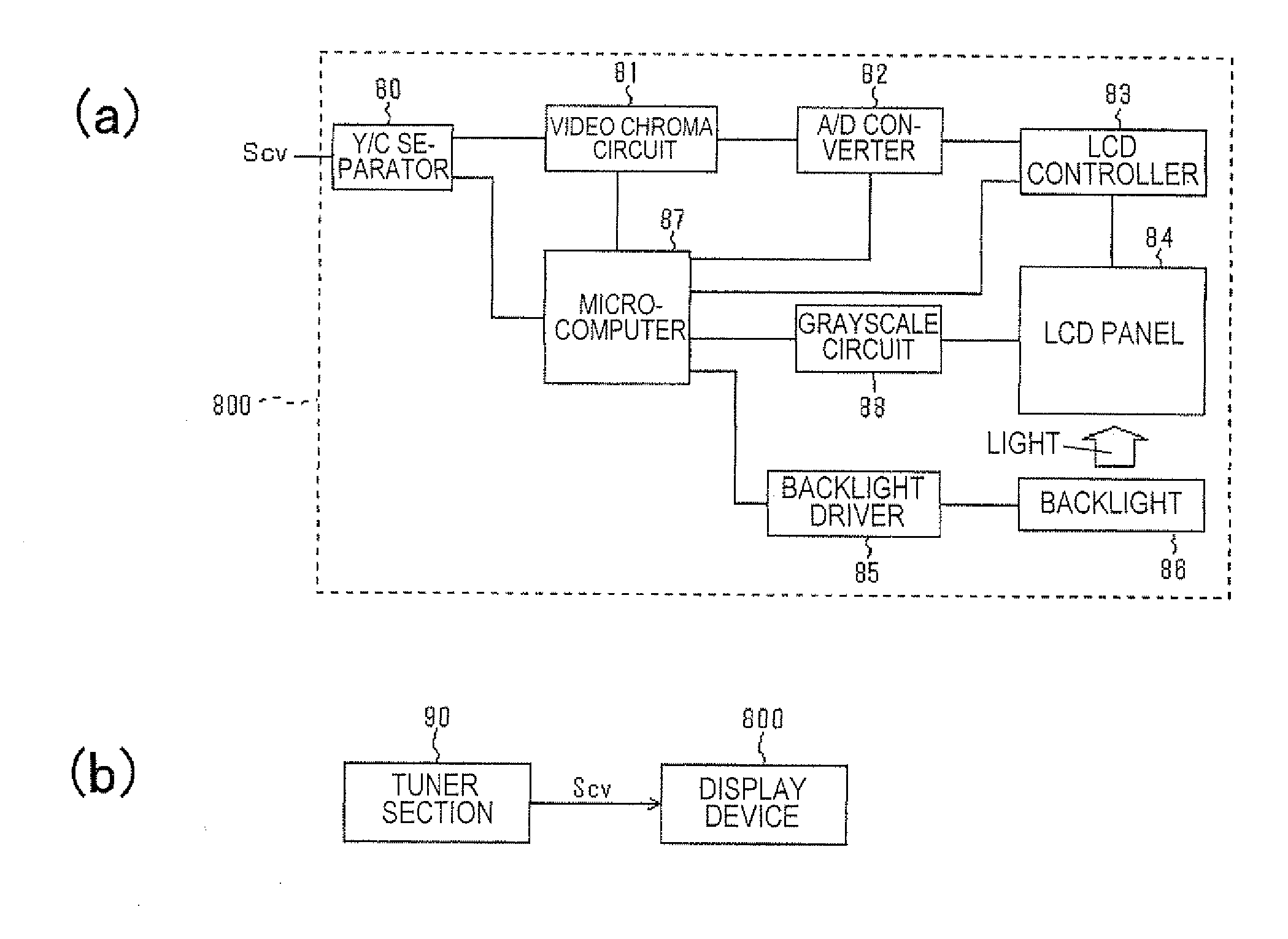

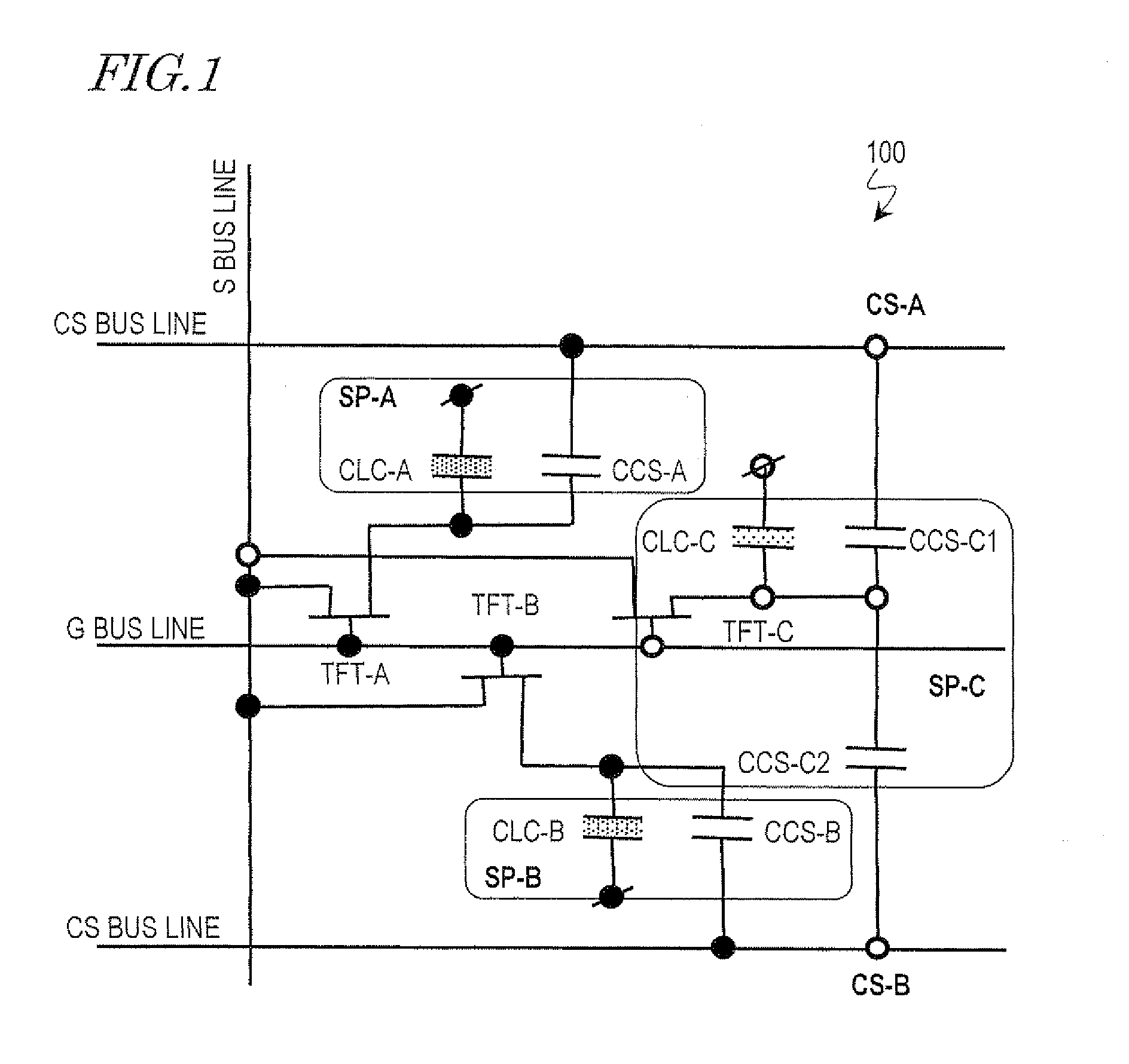

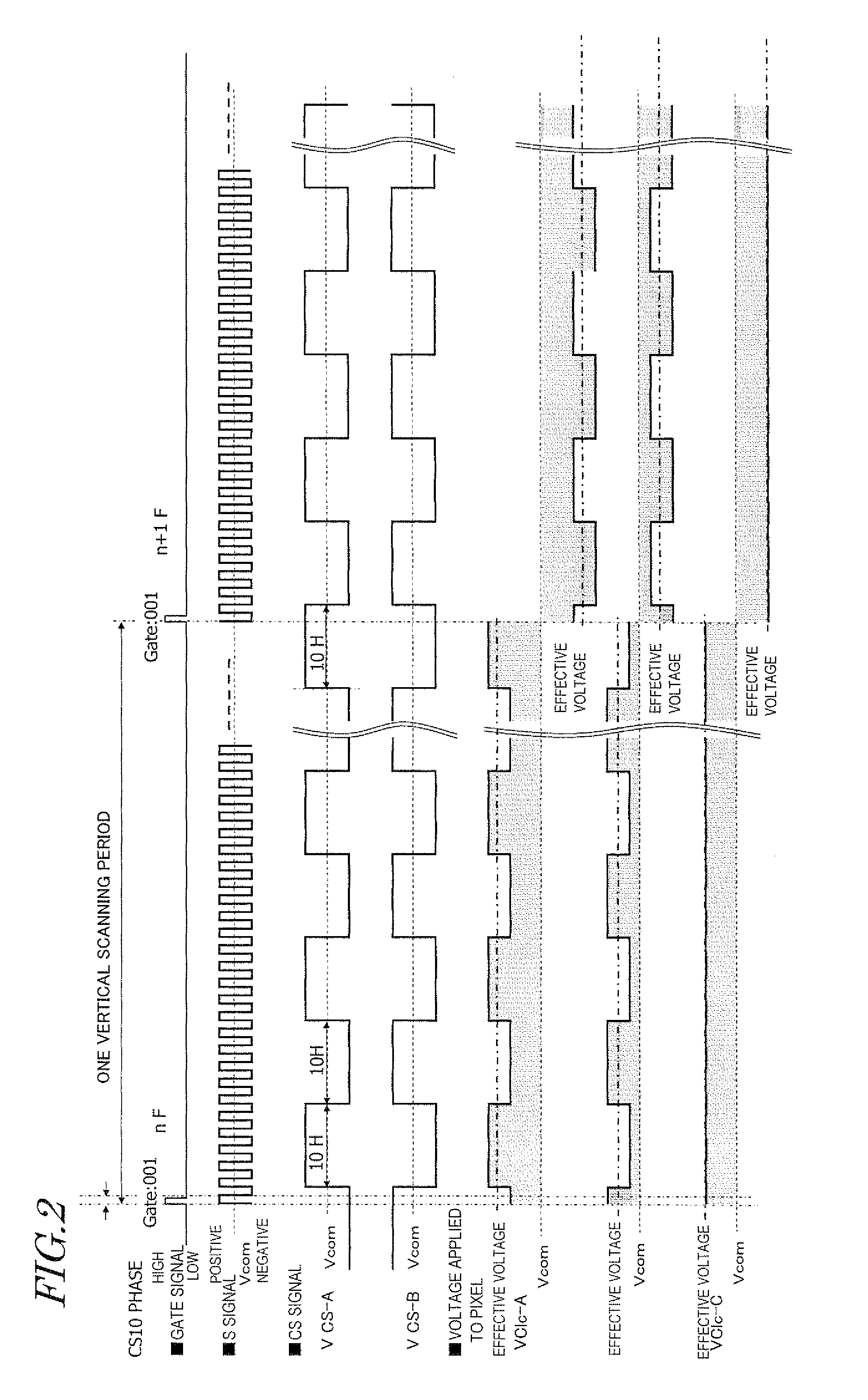

Liquid crystal display device

ActiveUS20100103339A1Improve display qualityLow costStatic indicating devicesNon-linear opticsFormation matrixLiquid-crystal display

A liquid crystal display device according to the present invention includes: a plurality of pixels that are arranged in rows and columns so as to form a matrix pattern; and TFTs (TFT-A, TFT-B and TFT-C), source bus lines, gate bus lines and CS bus lines (CS-A and CS-B), which are associated with the respective pixels. Each pixel includes at least three subpixels (SP-A, SP-B and SP-C) with liquid crystal capacitors that are able to retain mutually different voltages. By supplying a signal (CS-A or CS-B) that makes two of the at least three subpixels display mutually different luminances at least at a certain grayscale tone from the source, gate and CS bus lines to each pixel, the at least three subpixels are able to display mutually different luminances.

Owner:SHARP KK

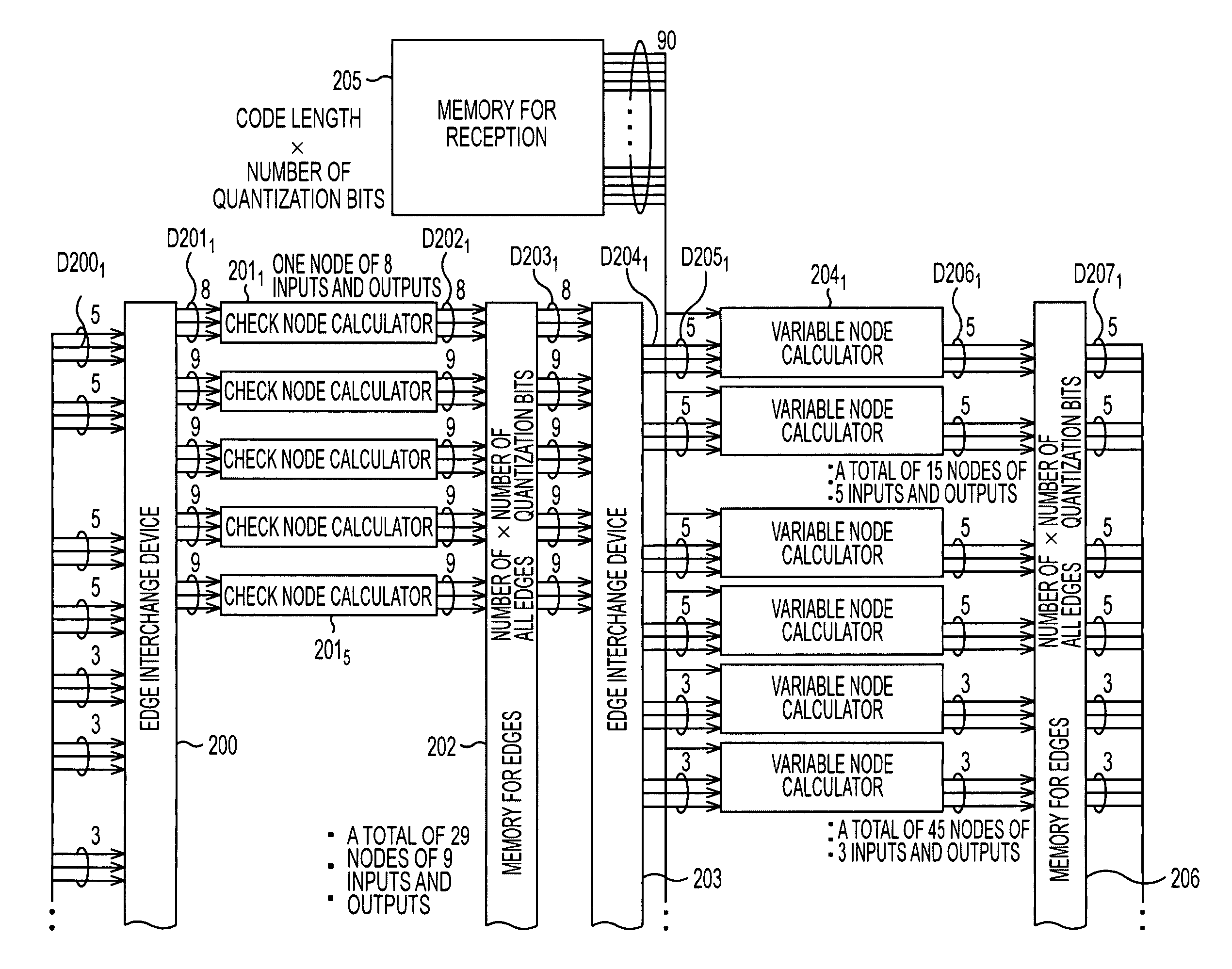

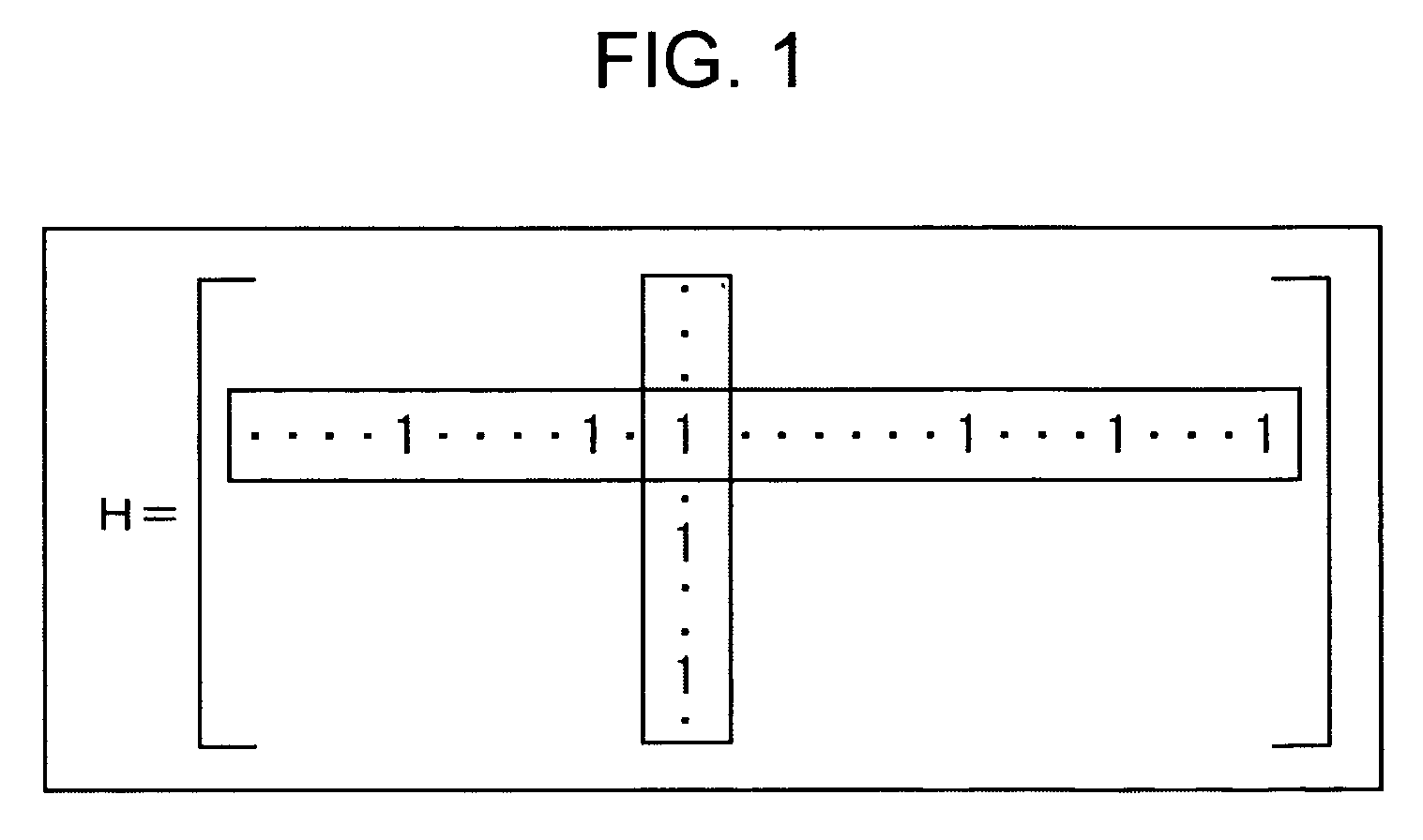

Decoding method, decoding apparatus, and program to decode low density parity check codes

ActiveUS7318186B2Easy to controlSuppression frequencyError correction/detection using multiple parity bitsCode conversionFormation matrixPartition of unity

Owner:SONY CORP

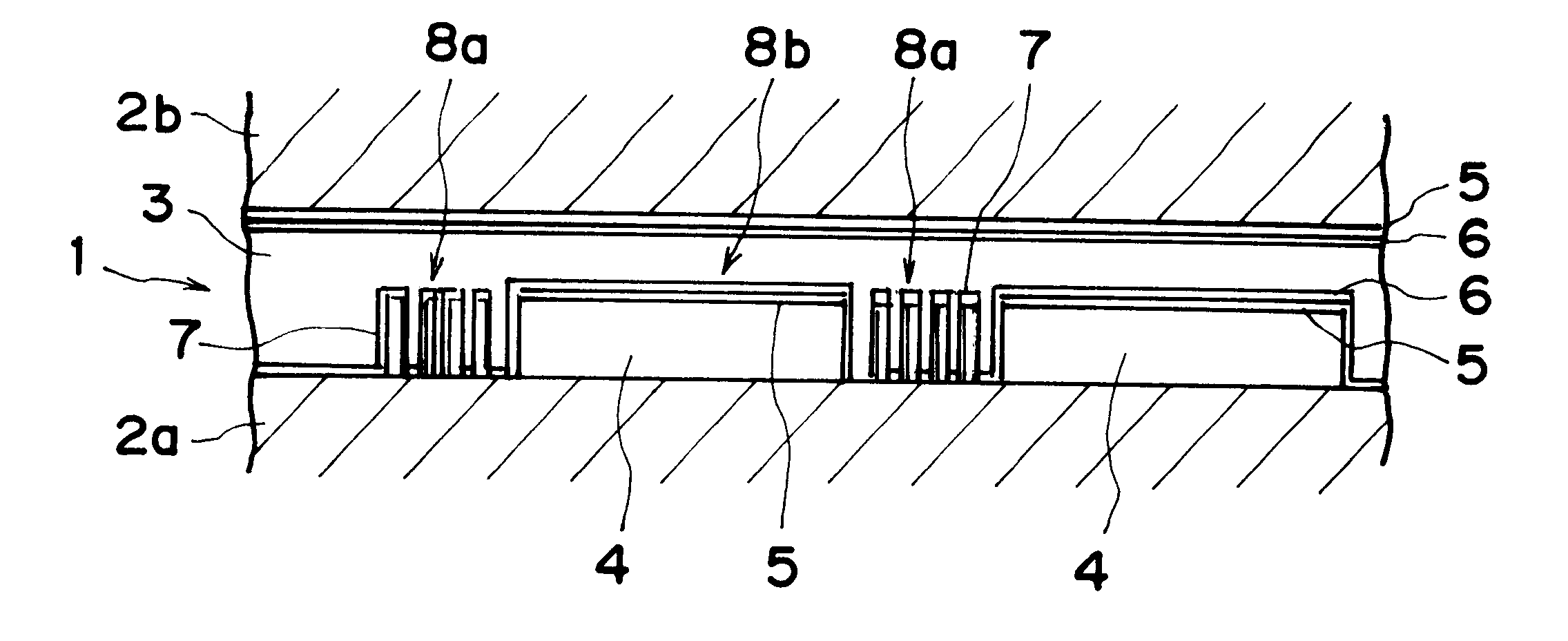

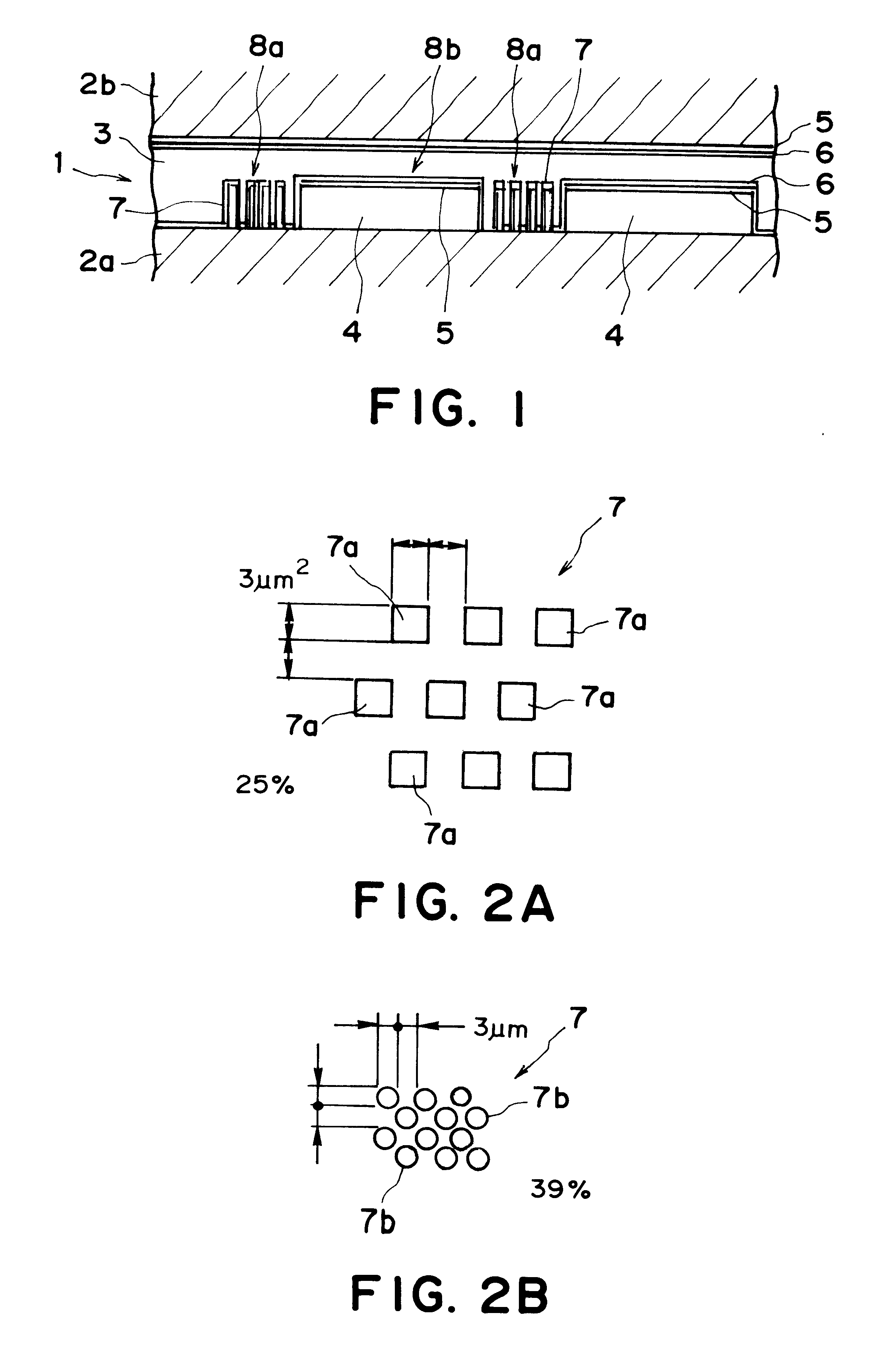

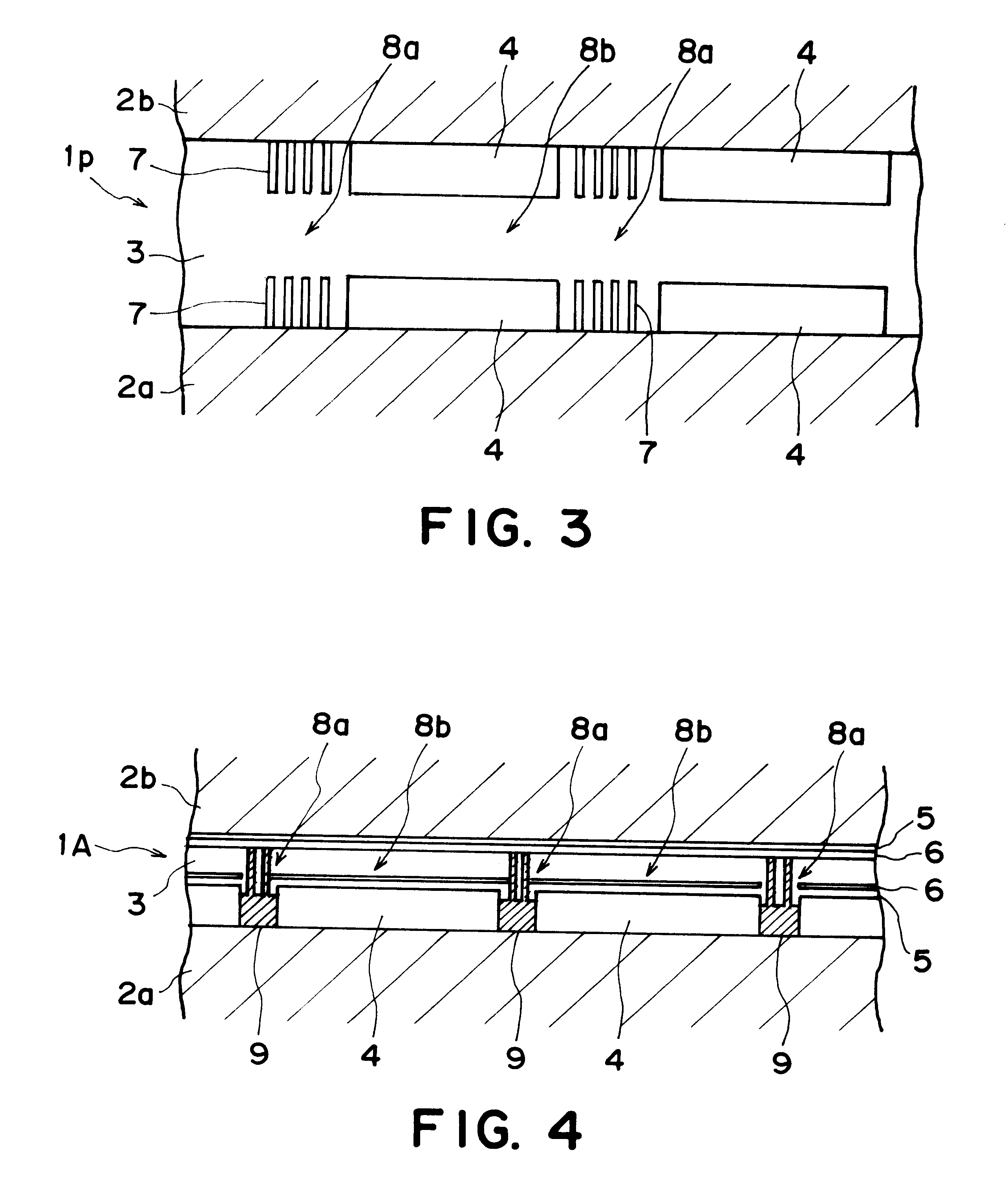

Liquid crystal device and process for production thereof

A matrix-type liquid crystal device is formed so as to have a matrix of pixels defined by and isolated from each other by an outside-pixel region. The liquid crystal in the outside-pixel region in placed in an alignment state, typically a homeotropic state or one close thereto, which is different from an alignment state, typically a homogeneous uniform alignment state, at the pixel region. As a result, the liquid crystal device is provided with improved display qualities due to suppression of irregularities at the outside-pixel region and / or a local pressure distribution.

Owner:CANON KK

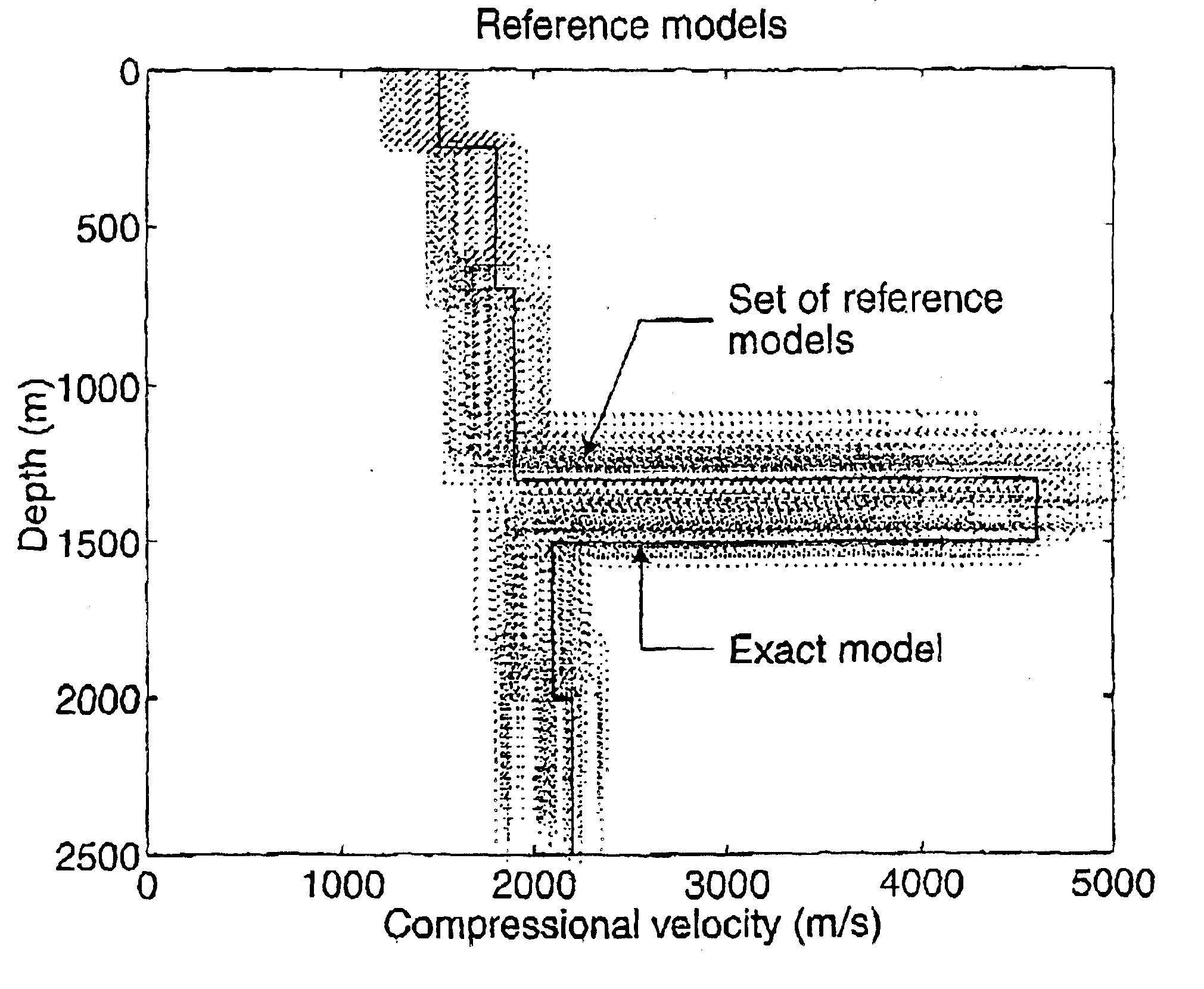

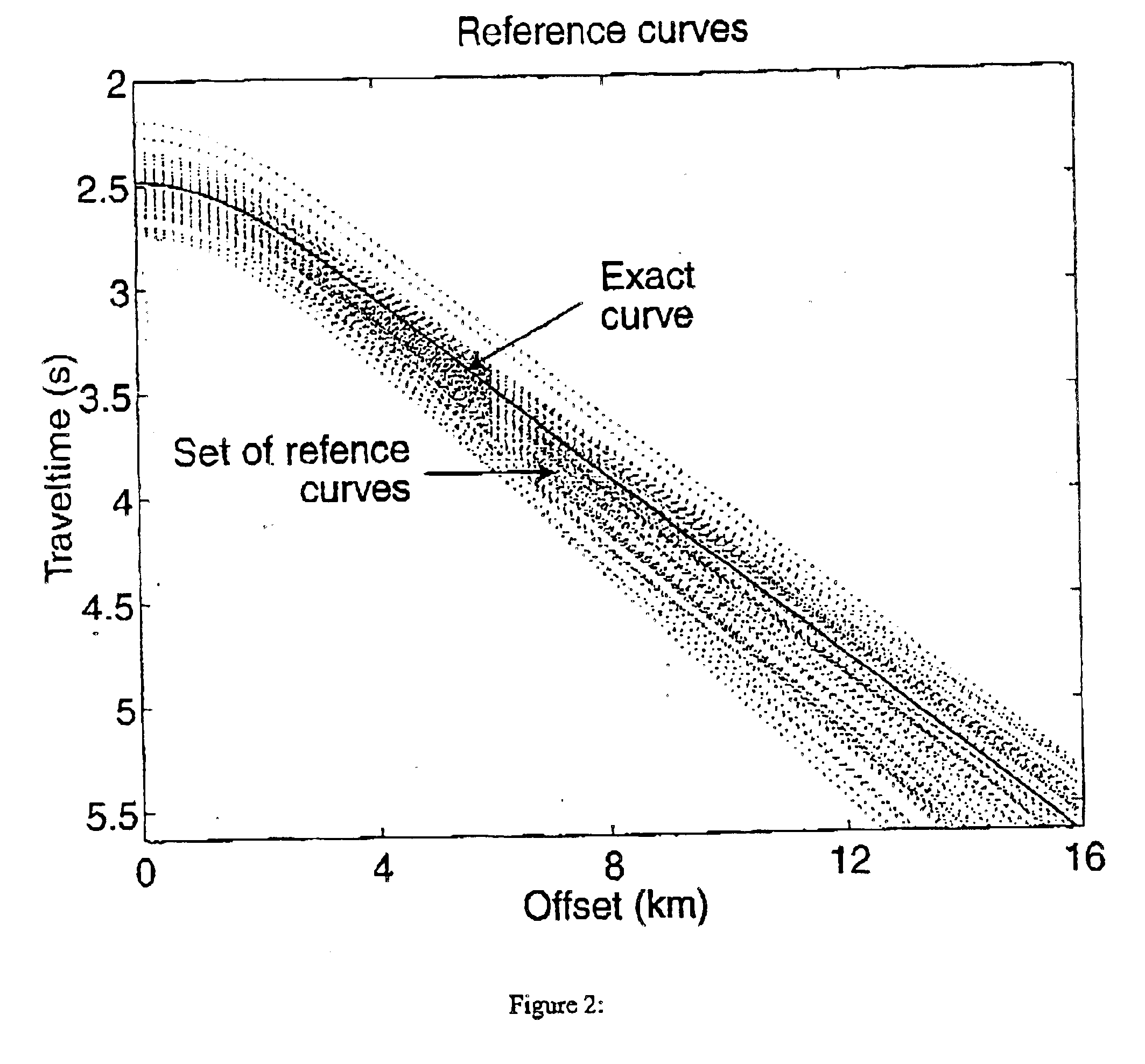

Seismic processing with general non-hyperbolic travel-time corrections

InactiveUS6839658B2Improve seismic traveltime approximationsImprove estimation accuracyDigital computer detailsNuclear monitoringSingular value decompositionFormation matrix

A method of constructing a basis of functions intended for the building of approximations of one-way or two-way seismic traveltime versus offset functions. The method is characterized by the combination of the following steps of (a) creating a distribution of reference one-way or two-way traveltime versus offset functions by traveltime modelling in a set of velocity models representing possible velocity distributions, (b) obtaining new reference functions by modifying these reference traveltime functions by applying an operator to them, (c) selecting a set of discrete offsets to make these new reference functions discrete, (d) arranging these discrete functions in columns to form a matrix, (e) applying a singular value decomposition to this matrix, with singular values sorted in decreasing order, to express its columns as linear combinations of the columns of an orthogonal matrix, and (f) building the basis functions by interpolating the columns of the orthogonal matrix.

Owner:SINTEF GASOLINEEUMSFORSKNING

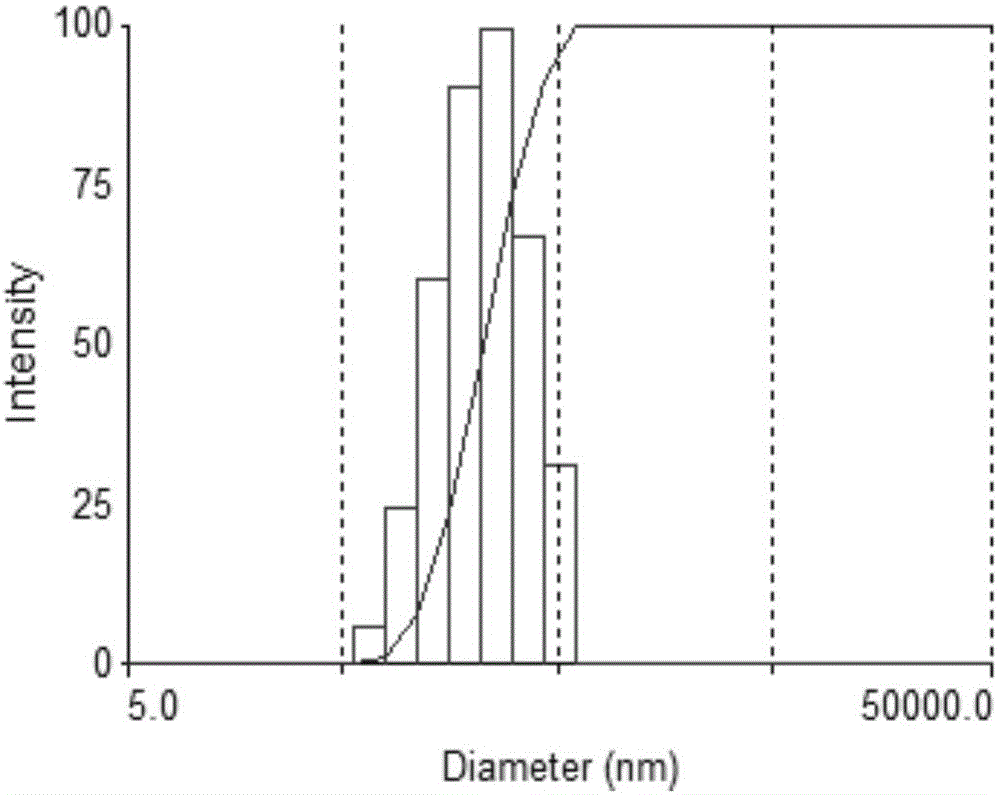

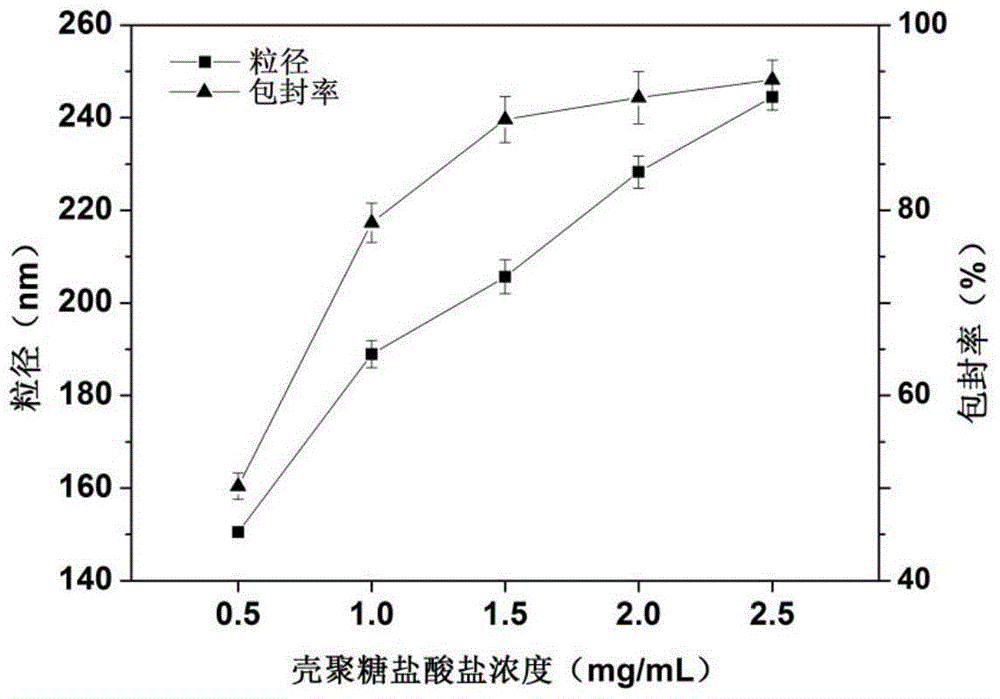

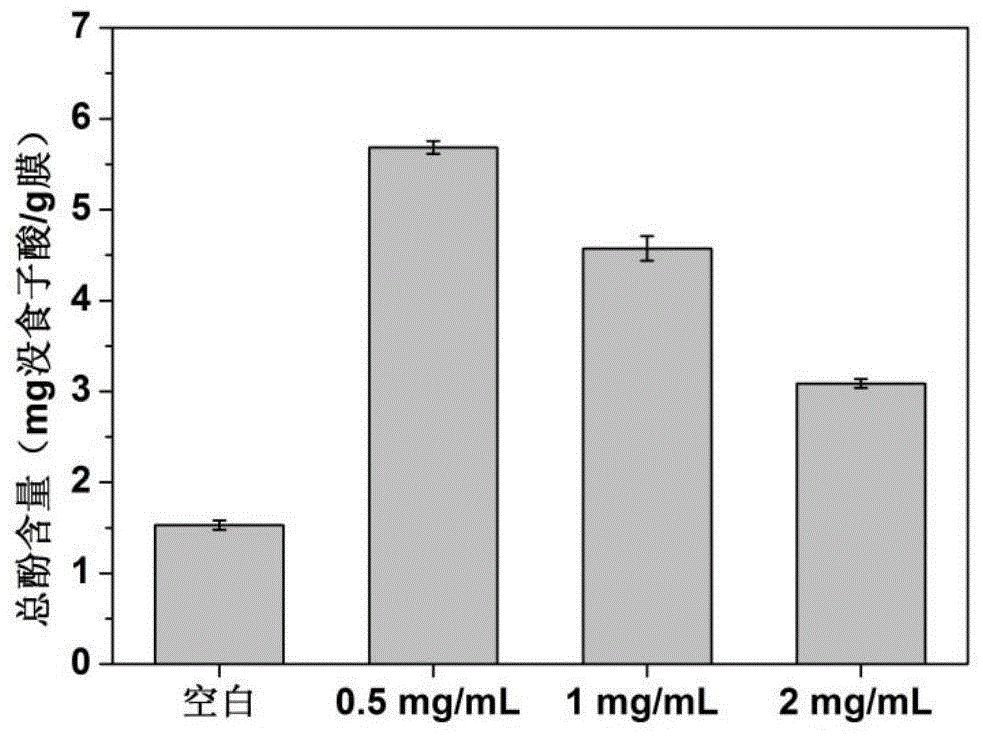

Edible film with continuous antioxidant function and preparation method and application thereof

ActiveCN104140568AAvoid the disadvantage of needing to be dissolved in acetic acid solutionAvoid Disadvantages of DissolutionFlexible coversWrappersFormation matrixNanoparticle

The invention discloses an edible film with a continuous antioxidant function and a preparation method and application thereof. Preparation parameters of tea polyphenol-chitosan hydrochloride nanoparticles are adjusted, and the prepared chitosan hydrochloride nanoparticles with different tea polyphenol encapsulation rates and particle sizes are added to a natural edible biological macromolecular film formation matrix so as to form the film. On one hand, the different encapsulation rates can change the proportion of free tea polyphenol to encapsulated tea polyphenol in the film; on the other hand, the nanoparticles in different sizes can adjust structure compactness of the film, and therefore release of the tea polyphenol in the film is coordinated and controlled. According to the edible film with the continuous antioxidant function and the preparation method and the application of the edible film, when the antioxidant film is prepared, release of active substances can be adjusted under the condition that the concentration of the active substances is definite, and the use rate of the active substances in the film is increased.

Owner:内蒙古秋实生物有限公司

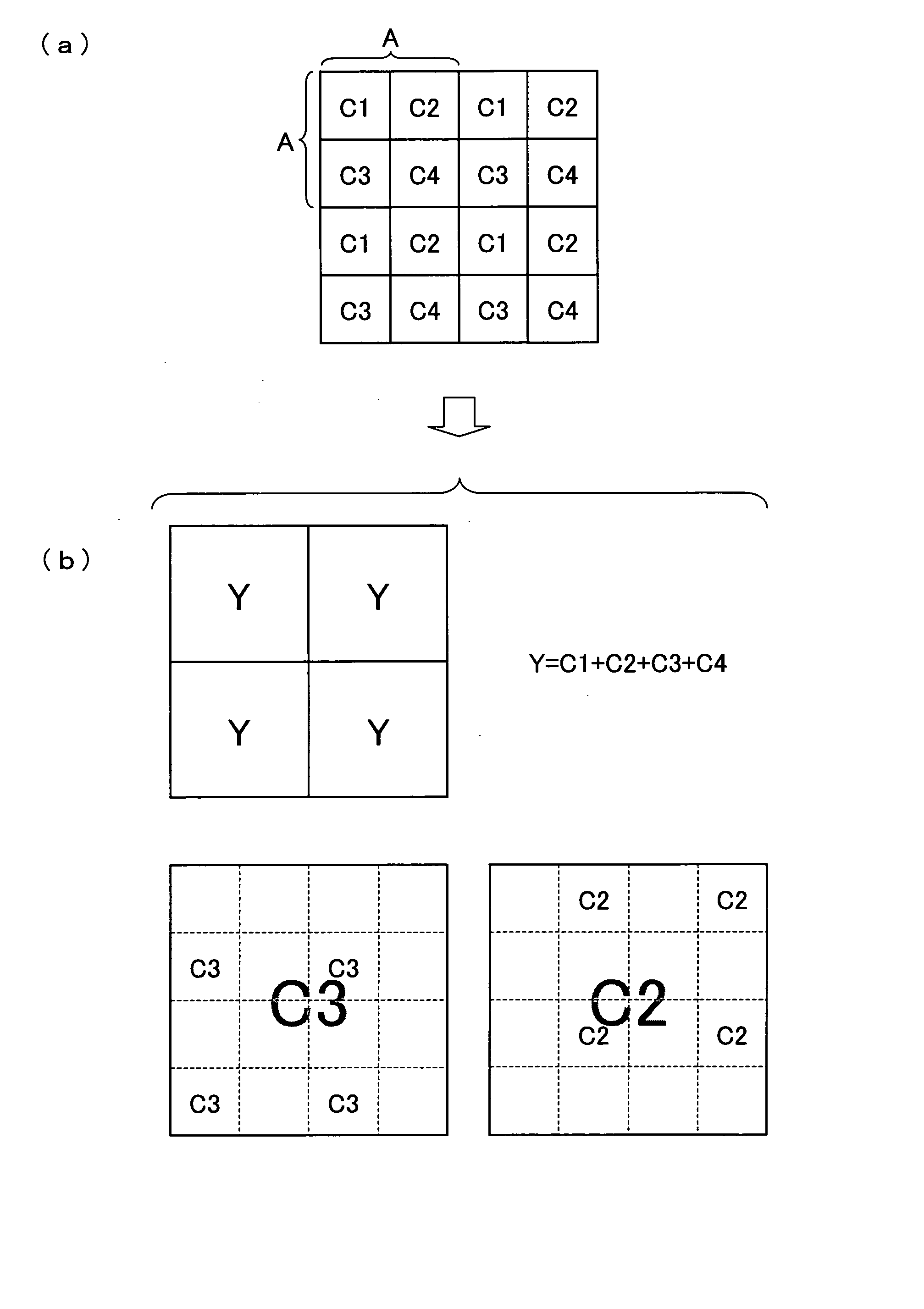

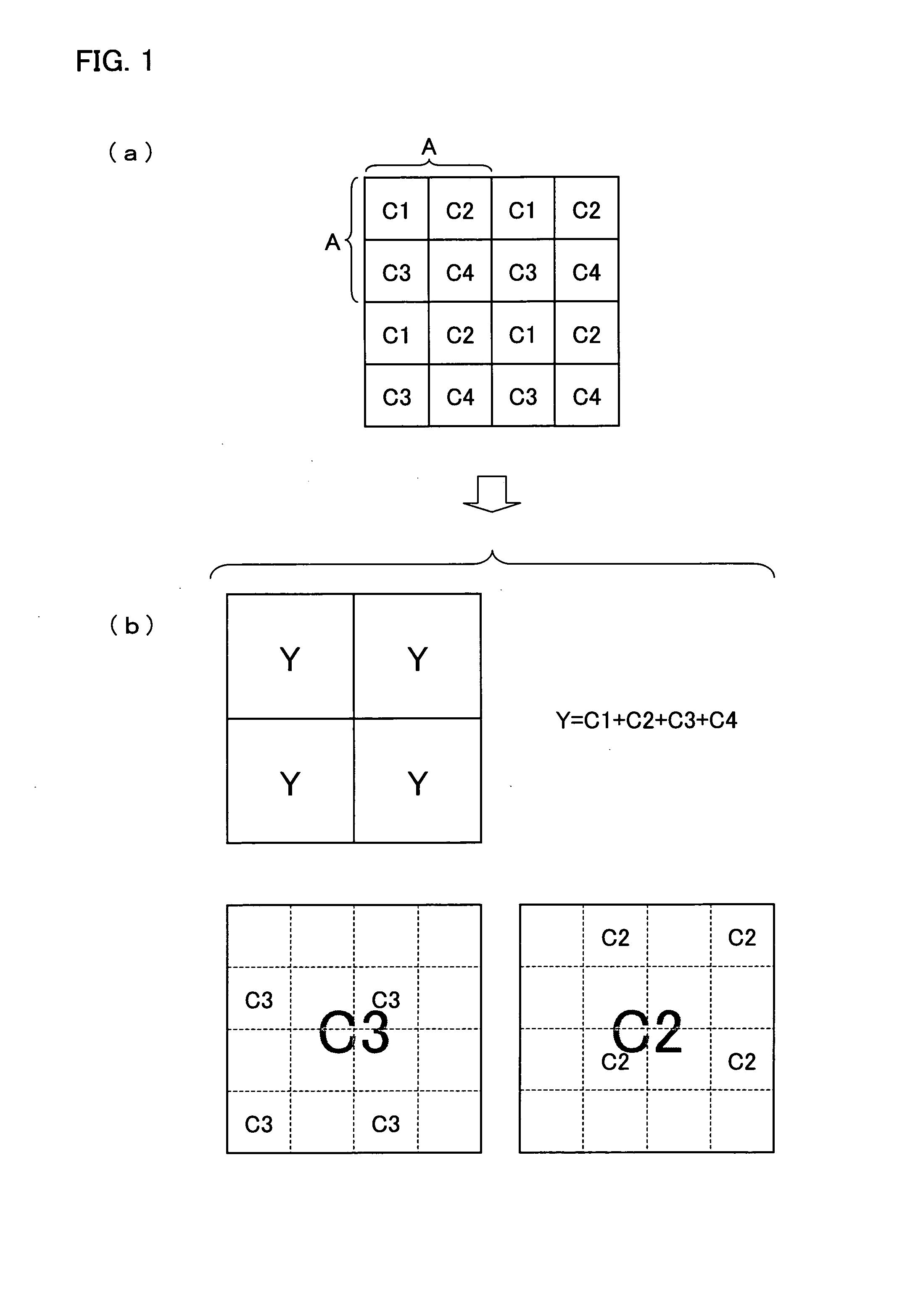

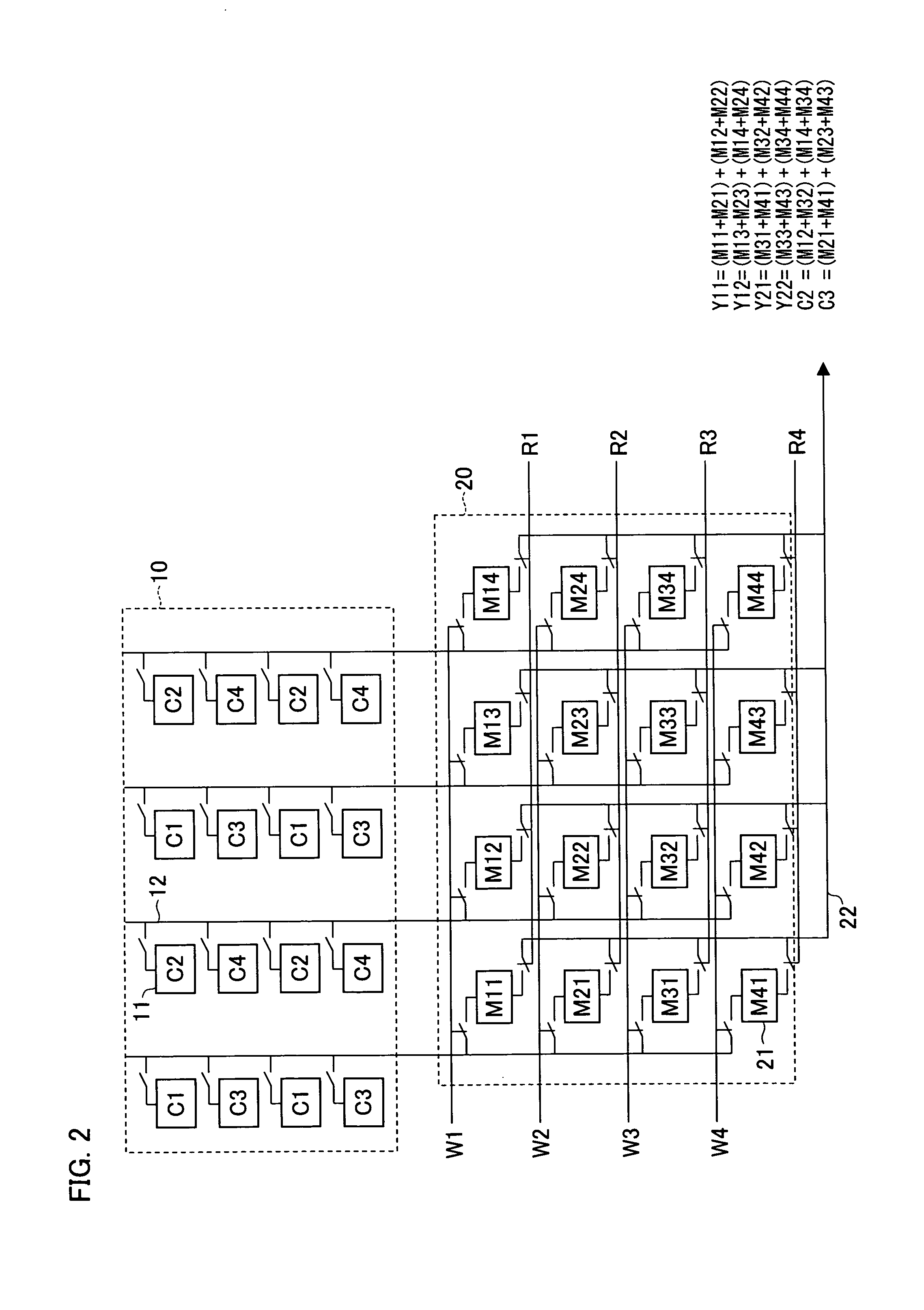

Color solid-state image pickup device and method for reading out pixel signals

InactiveUS20080316346A1High sensitivityHinder resolutionTelevision system detailsTelevision system scanning detailsFormation matrixImage resolution

A color solid-state image pickup device includes a pixel section having sets of a total of four adjacent pixels arrayed 2×2 in horizontal and vertical directions. Each of the sets consists of an first pixel serving as an upper left pixel and having a first spectral characteristic, a second pixel serving as an upper right pixel and having a second spectral characteristic, a third pixel serving as a lower left pixel and having a third spectral characteristic, and a fourth pixel serving as a lower right pixel and having a fourth spectral characteristic. The pixel section is formed by arraying the sets in the horizontal and vertical directions so that the sets form a matrix. The color solid-state image pickup device uses, as a unit of addition, a total of 16 pixels consisting of four adjacent sets arrayed 2×2 in the horizontal and vertical directions. The color solid-state image pickup device adds up and reads out respective pixel signals of the pixels. The color solid-state image pickup device creates a luminance signal by adding up and reading out respective pixel signals of the first, second, third, and fourth pixels constituting the set. This makes it possible to achieve both high sensitivity and high resolution by inhibiting the resolution from being reduced by adding up pixel signals.

Owner:SHARP KK

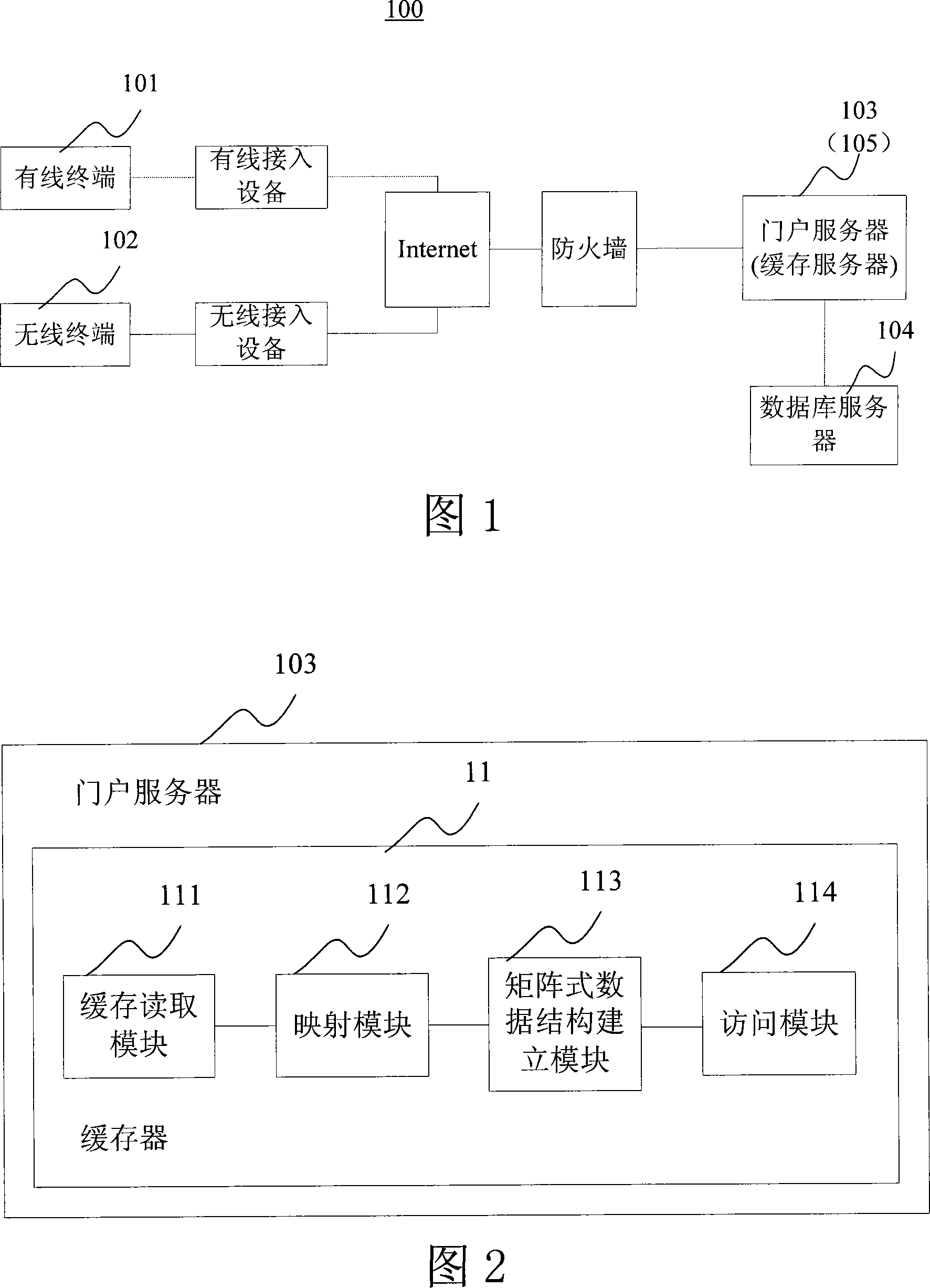

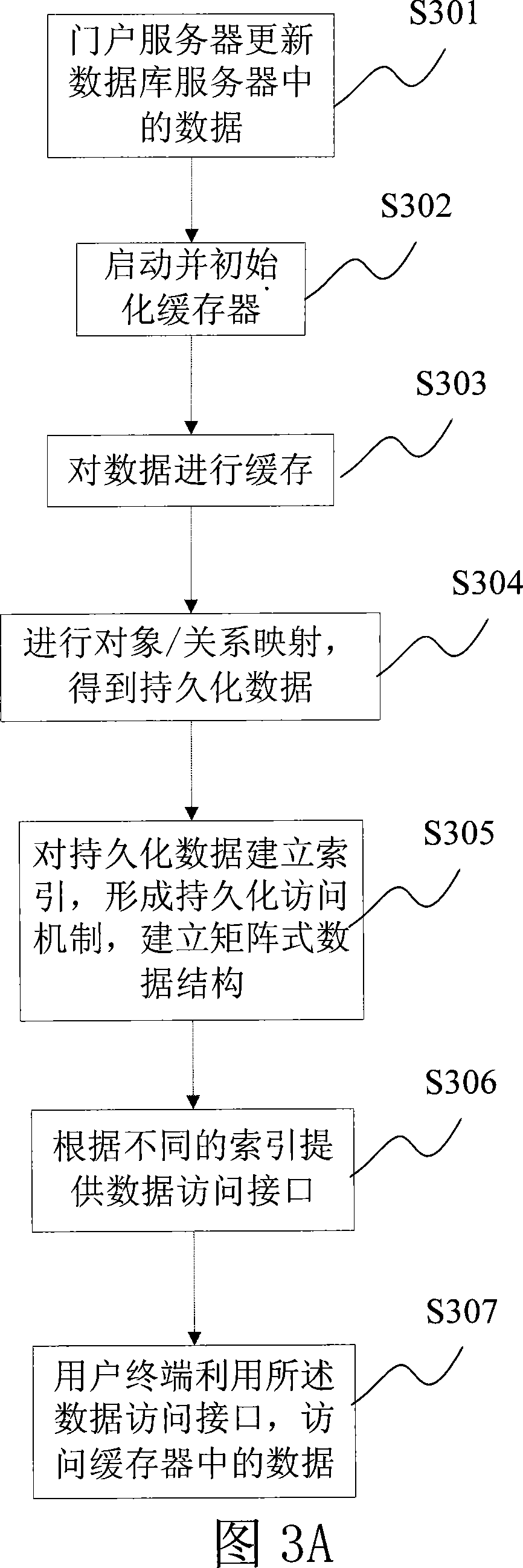

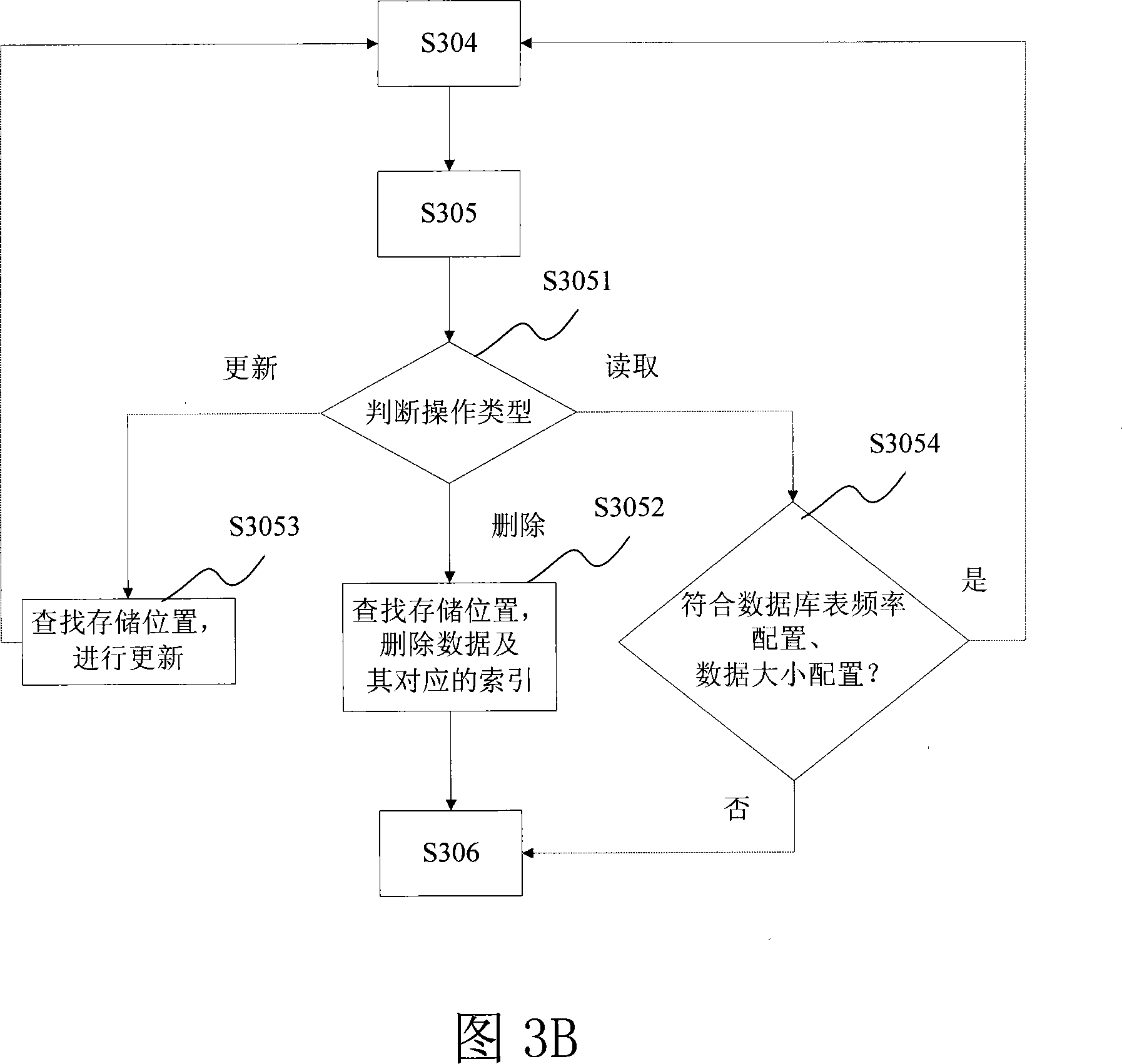

Matrix type data caching method and device based on WEB application

InactiveCN101169790AReduce trafficReduce the number of reads and writesSpecial data processing applicationsFormation matrixWeb application

The invention discloses a matrix form data caching method based on WEB application and a device thereof. The method comprises equipping a caching server for caching the read date from a database server according to a request from a portal server; performing object / relation mapping to the cached date to obtain persistent data; building indexes for the persistent data using Hash table to form a matrix form data structure; and providing access interface by the caching server according to the indexes. The invention obtains high efficiency with low cost, reduces the mutual communization of the WEB application server and database server, and reduces I / O read-write times of disk. The data is persistent. The invention enriches data searching manner, and provides very flexible interface and method for sequencing, accounting and other functions using these indexes.

Owner:ZTE CORP

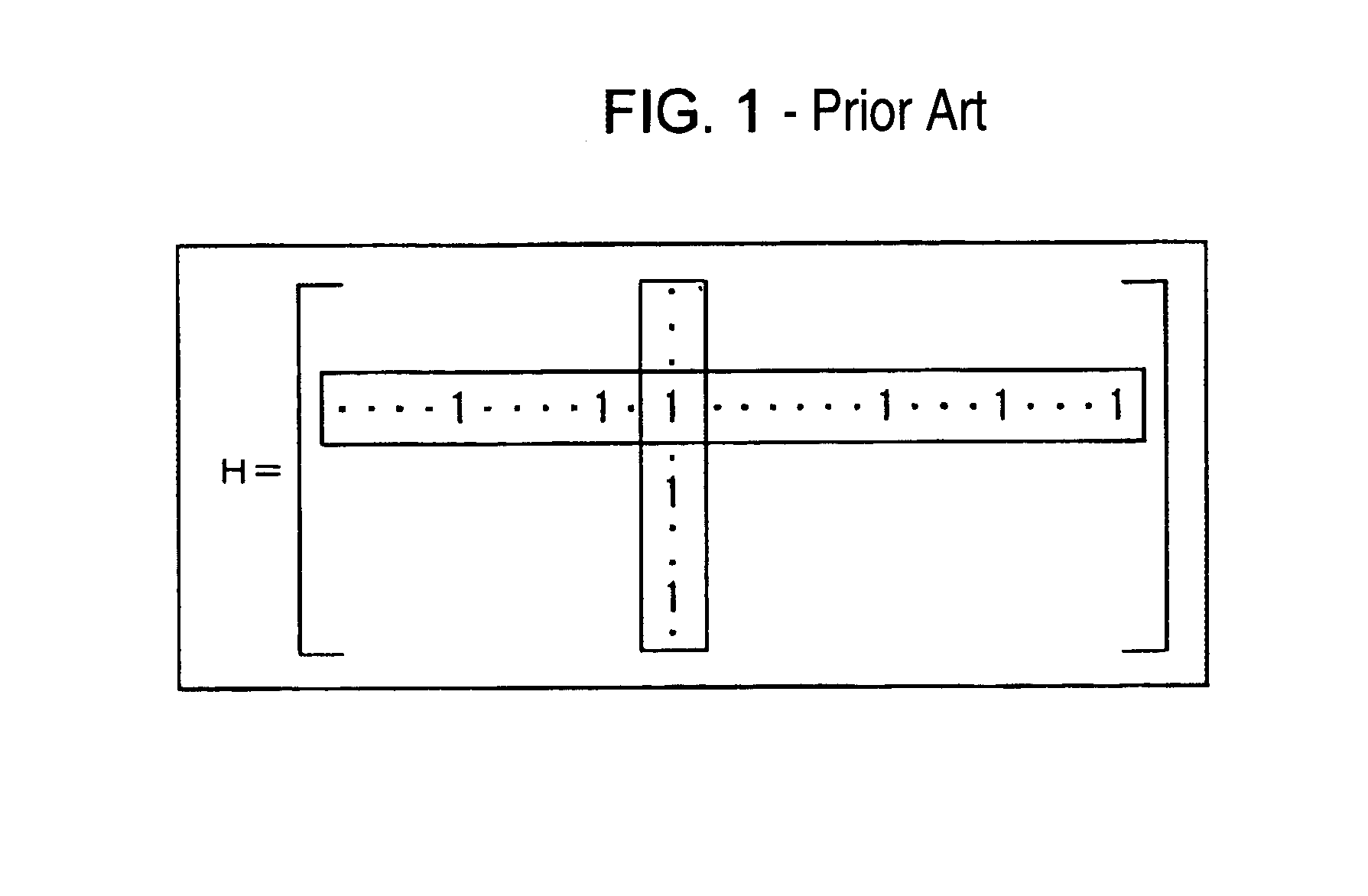

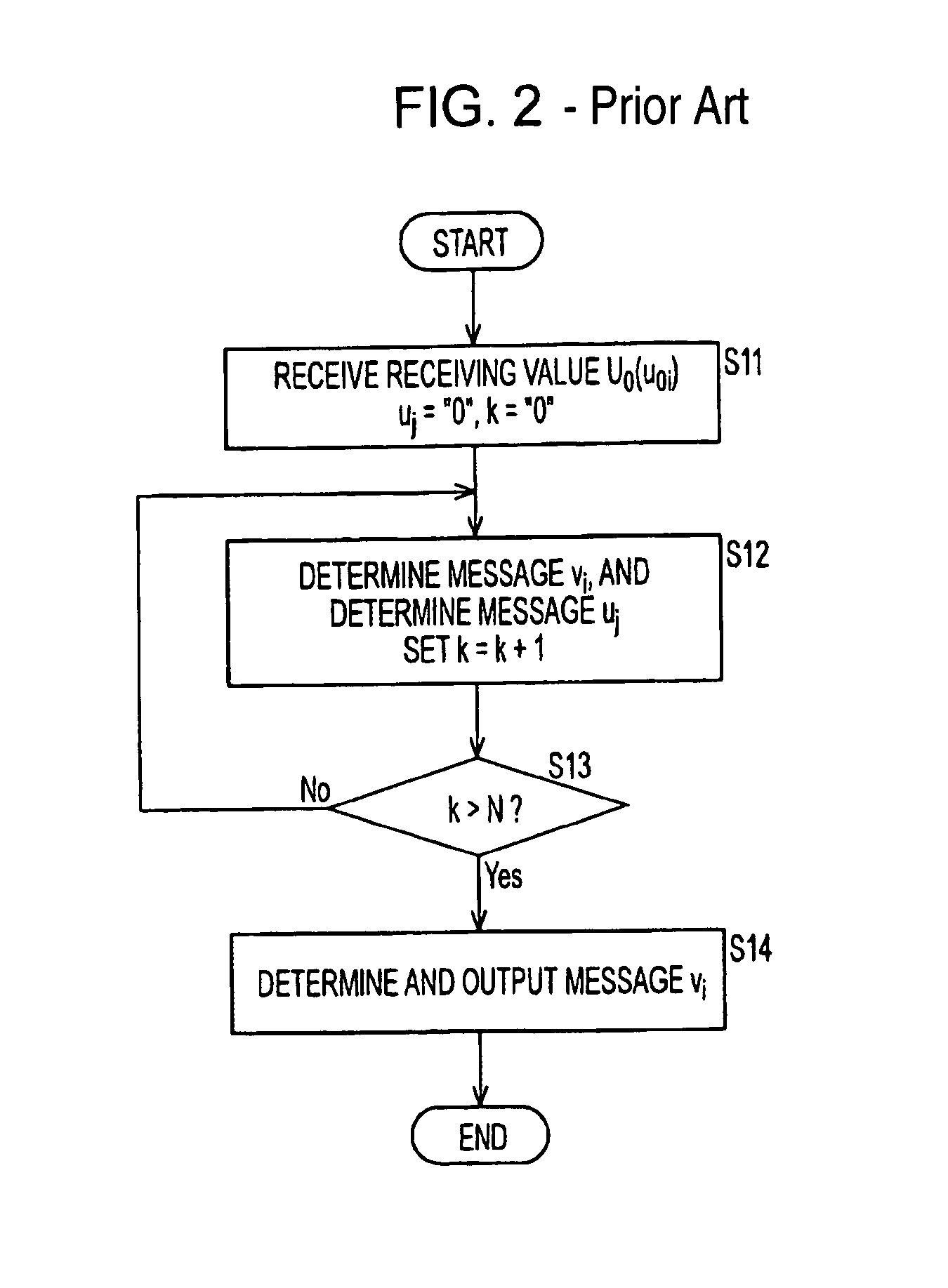

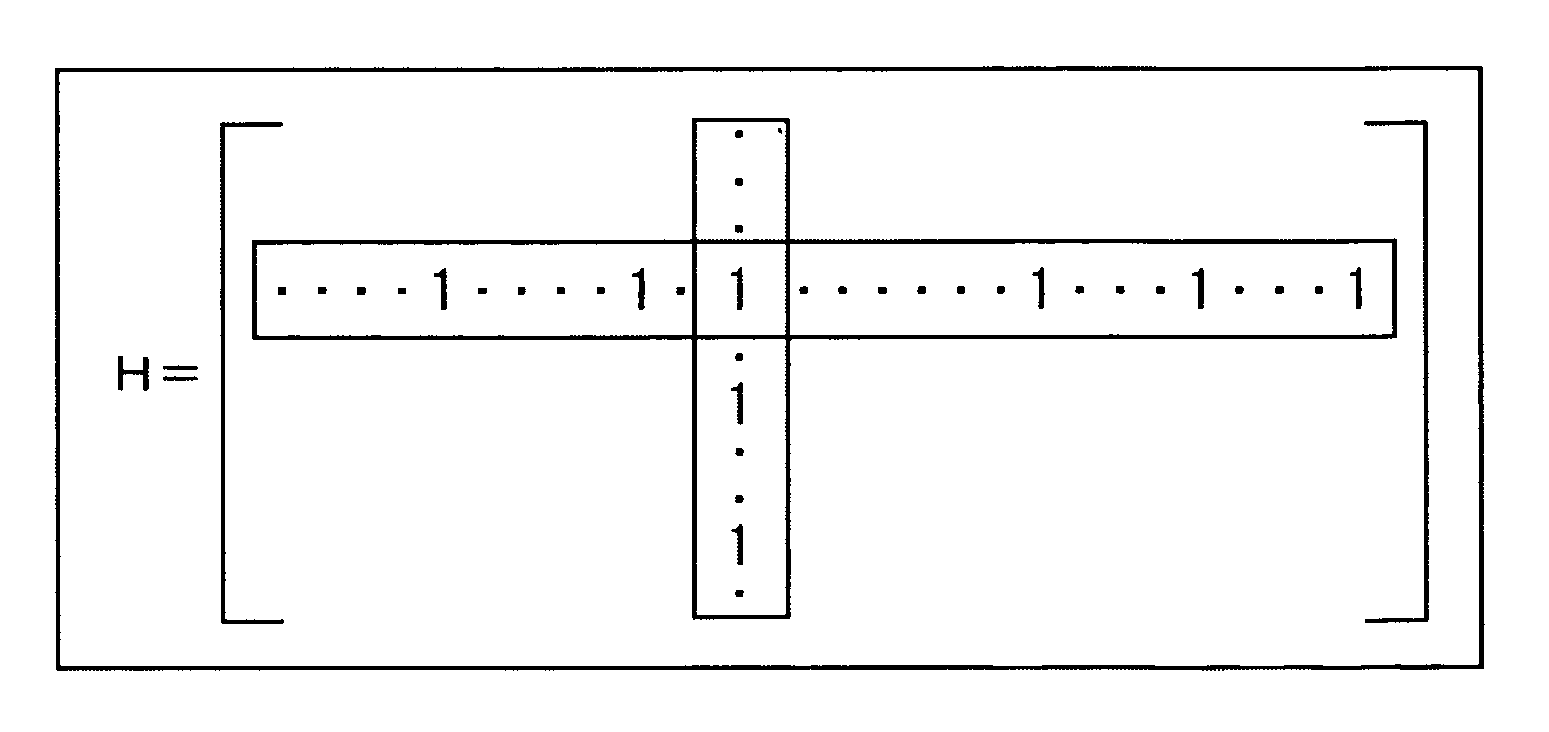

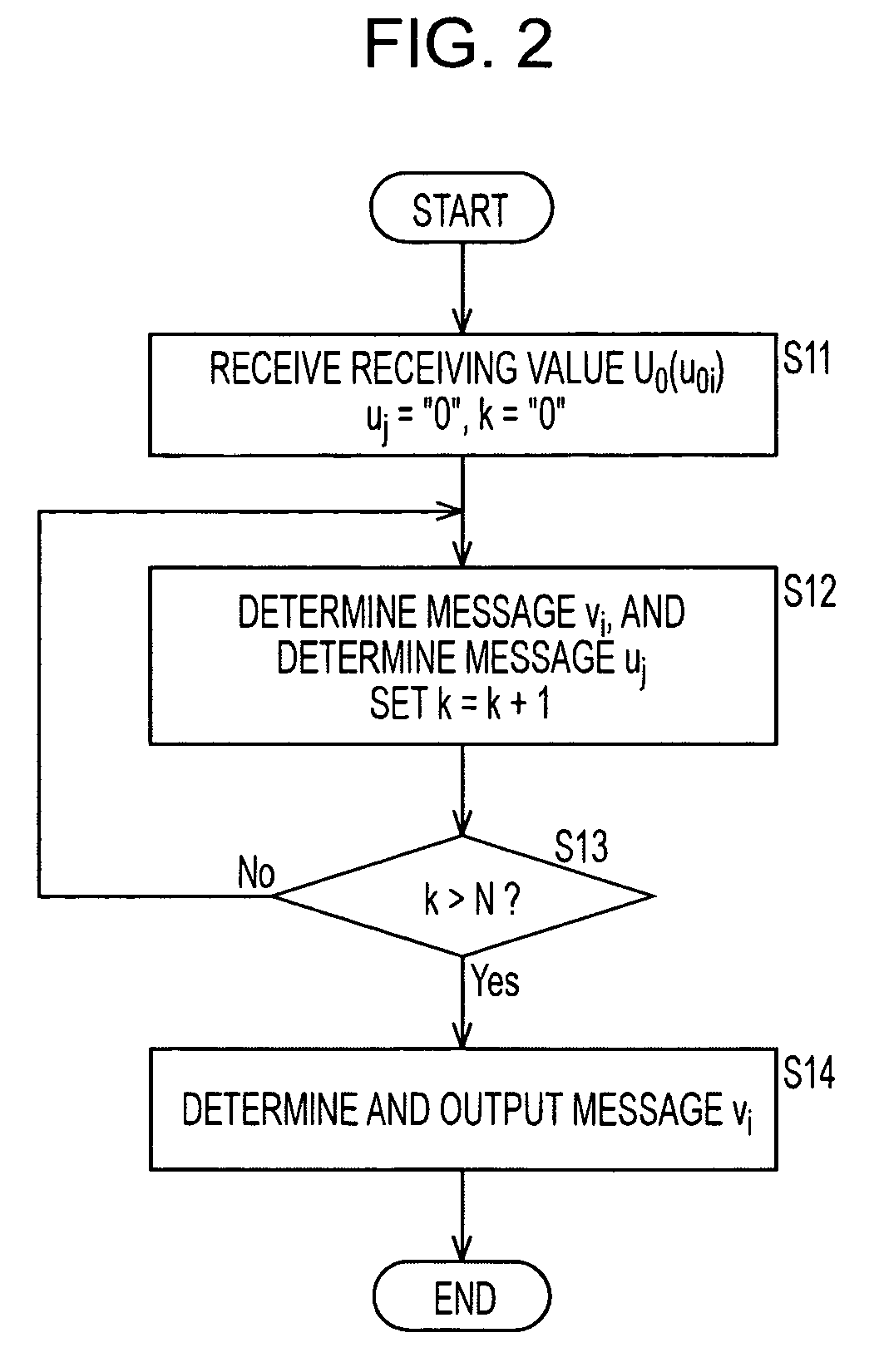

Decoding method, decoding device, and program

ActiveUS20050278604A1Suppress operating frequencyEasy to controlError correction/detection using multiple parity bitsCode conversionDecoding methodsFormation matrix

The present invention relates to a decoding method and a decoding apparatus in which, while the circuit scale is suppressed, the operating frequency can be suppressed within a sufficiently feasible range, and control of memory access can be performed easily, and to a program therefor. By using a transformation check matrix obtained by performing one of or both a row permutation and a column permutation on an original check matrix of LDPC (Low Density Parity Check) codes, the LDPC codes are decoded. In this case, by using, as a formation matrix, a P×P unit matrix, a quasi-unit matrix in which one or more is, which are elements of the unit matrix, are substituted with 0, a shift matrix in which the unit matrix or the quasi-unit matrix is cyclically shifted, a sum matrix, which is the sum of two or more of the unit matrix, the quasi-unit matrix, and the shift matrix, and a P×P 0-matrix, the transformation check matrix is represented by a combination of a plurality of the formation matrices. A check node calculator 302 simultaneously performs p check node calculations. A variable node calculator 304 simultaneously performs p variable node calculations.

Owner:SONY CORP

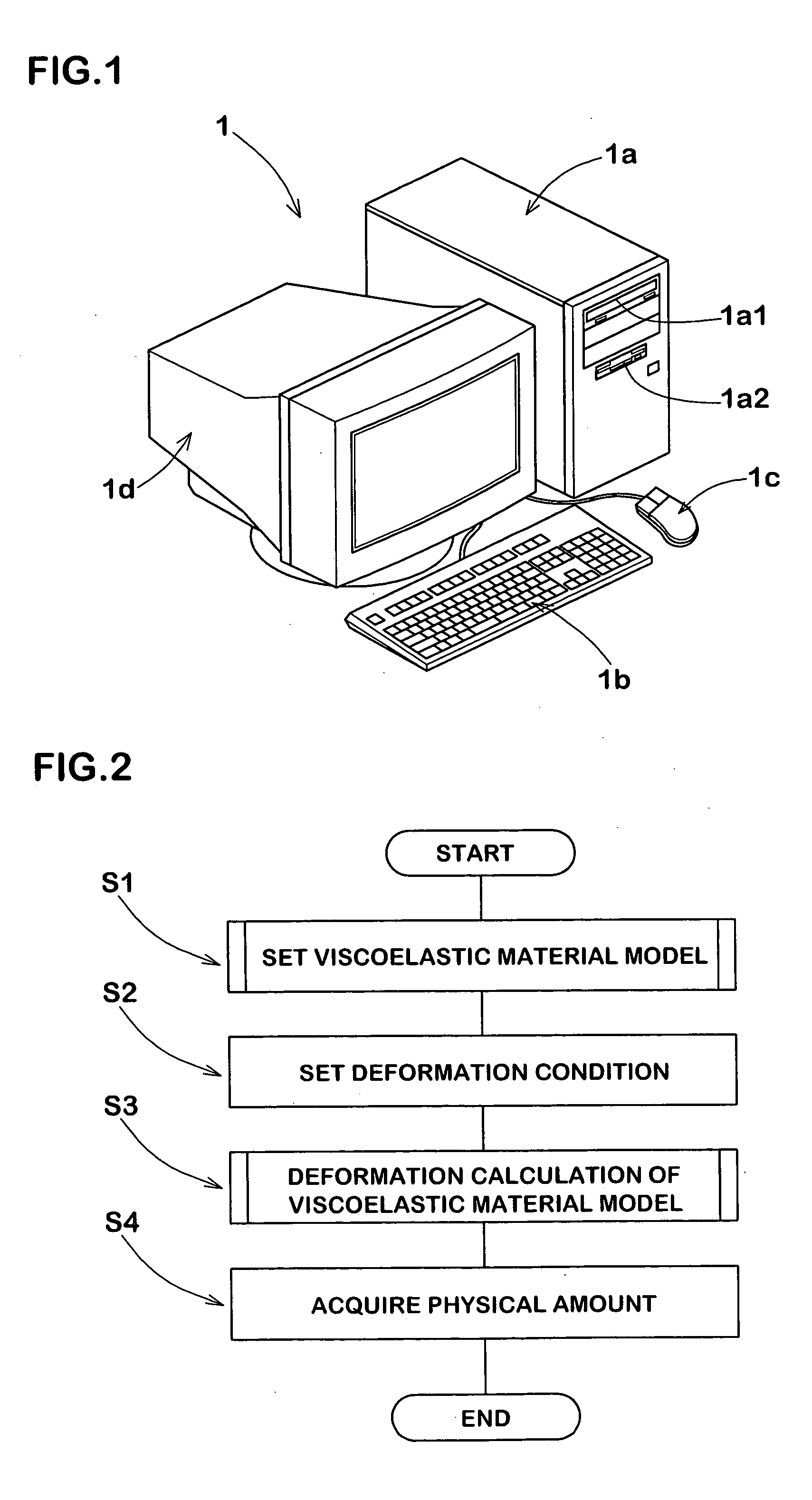

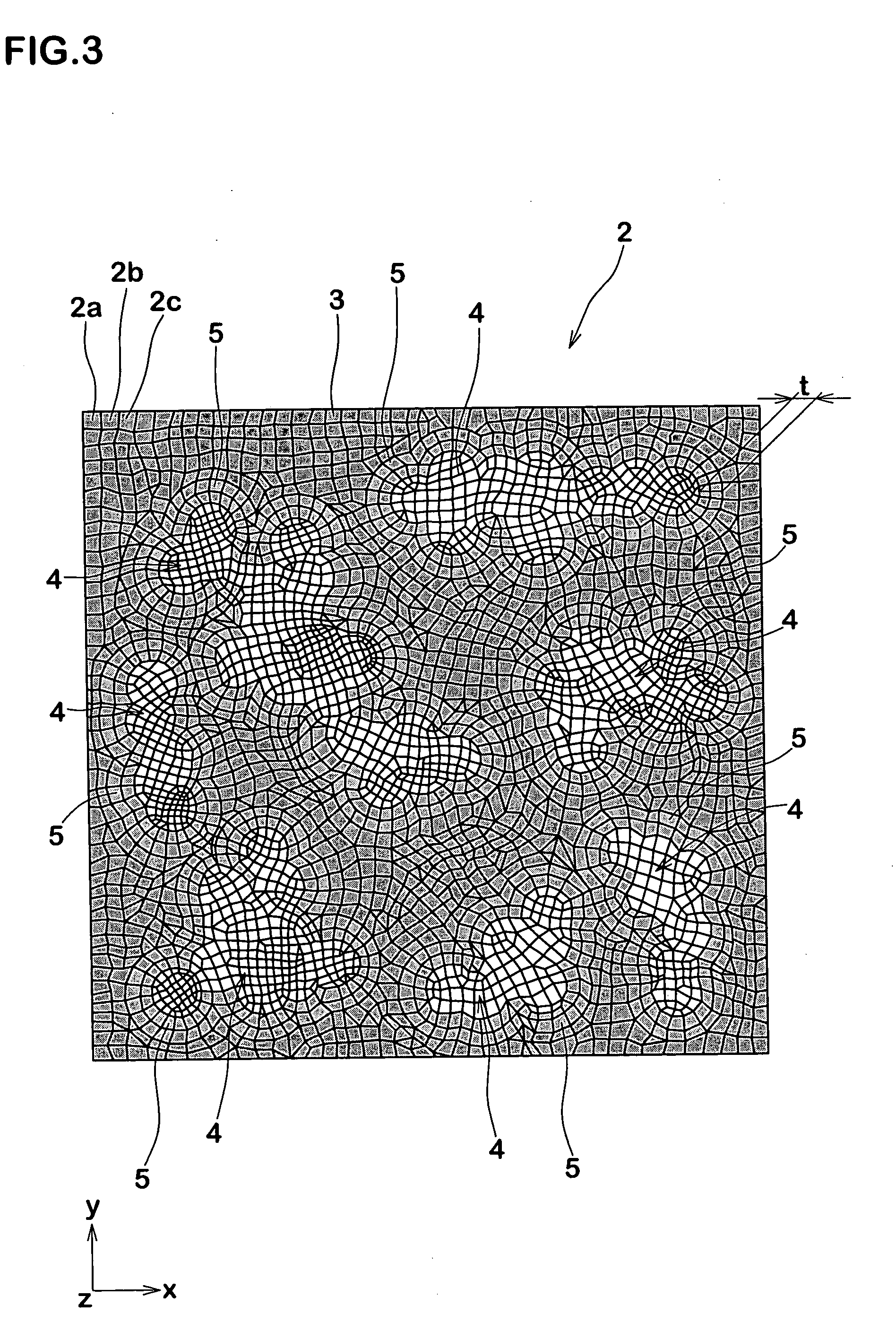

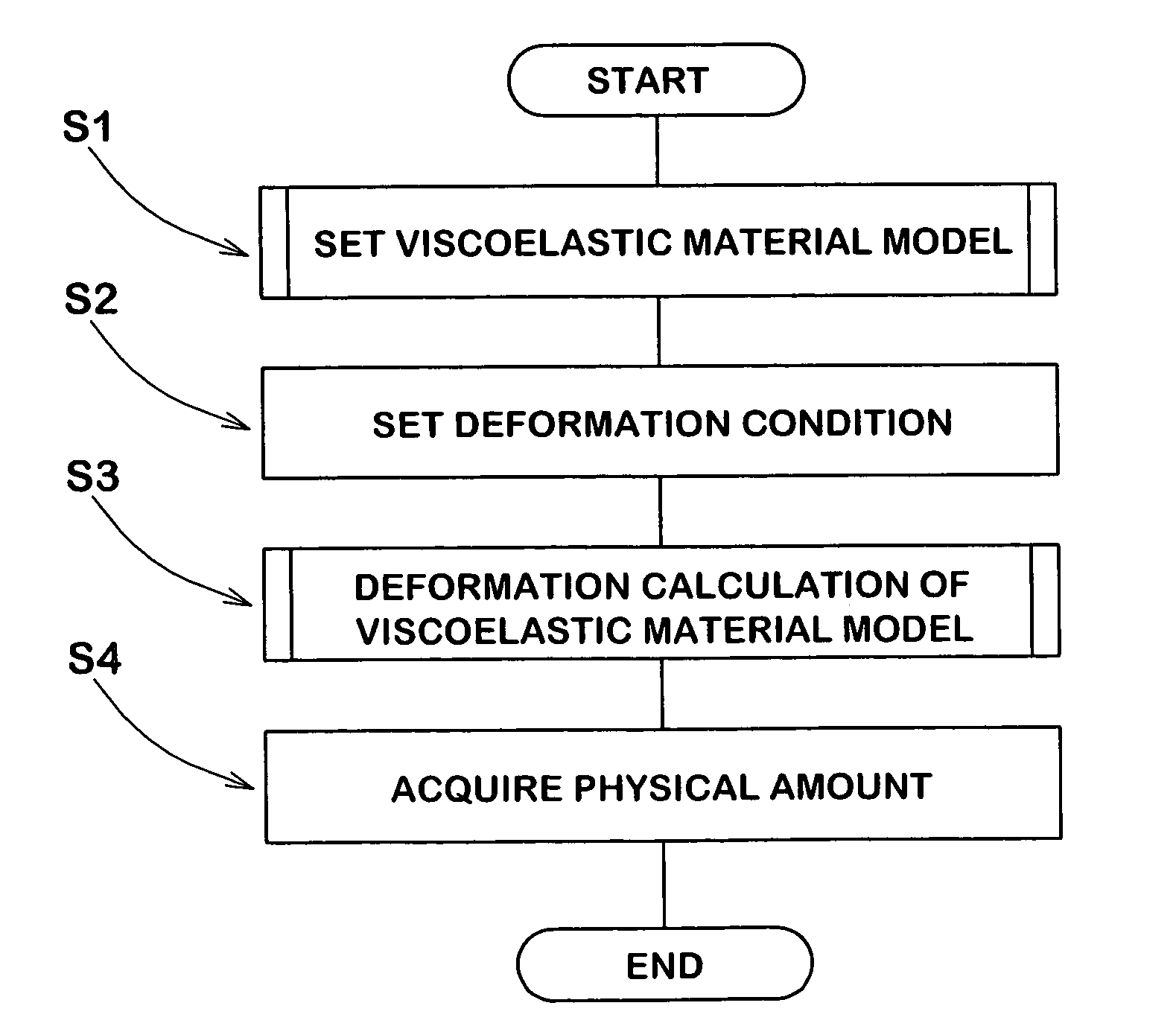

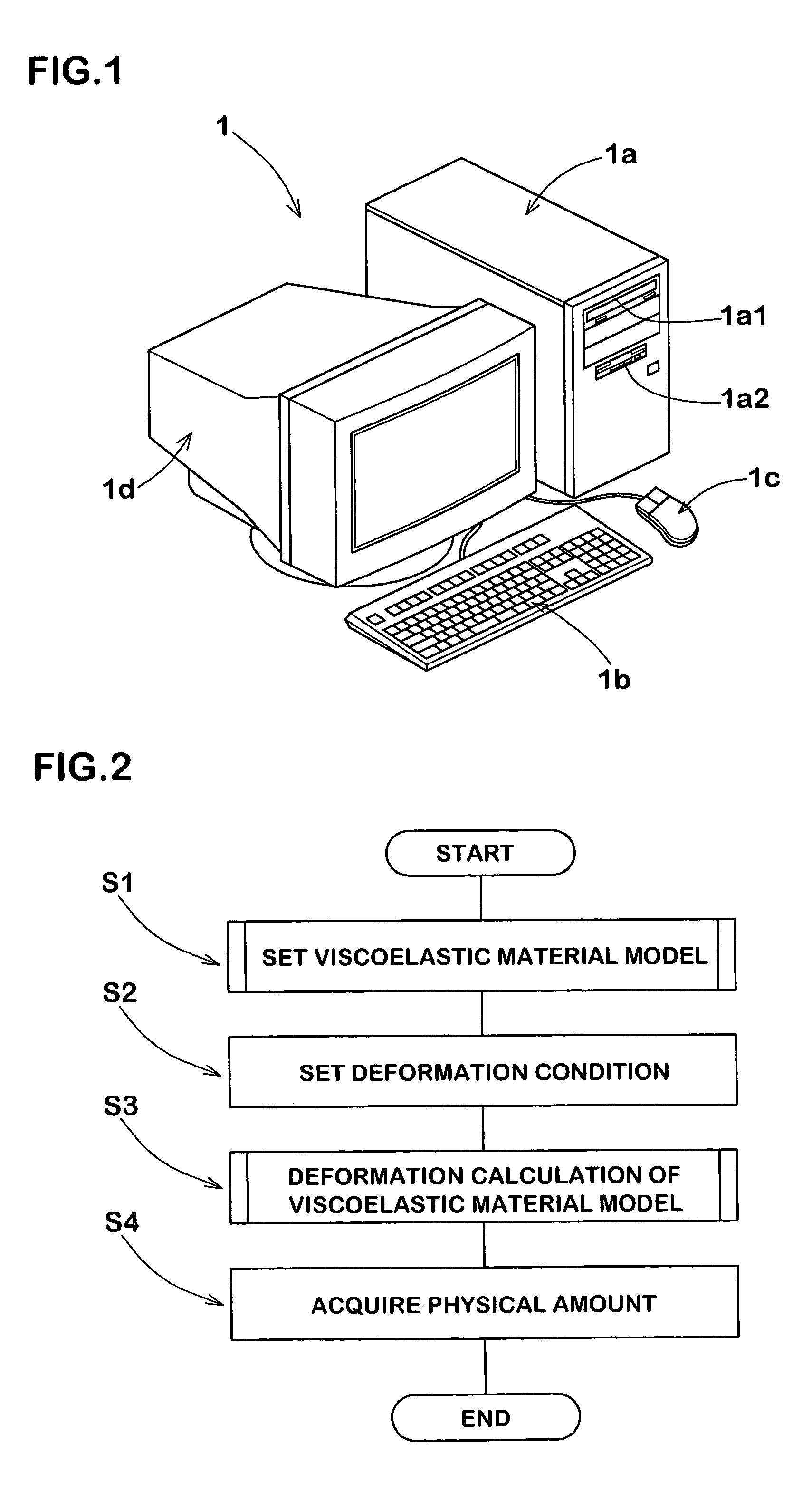

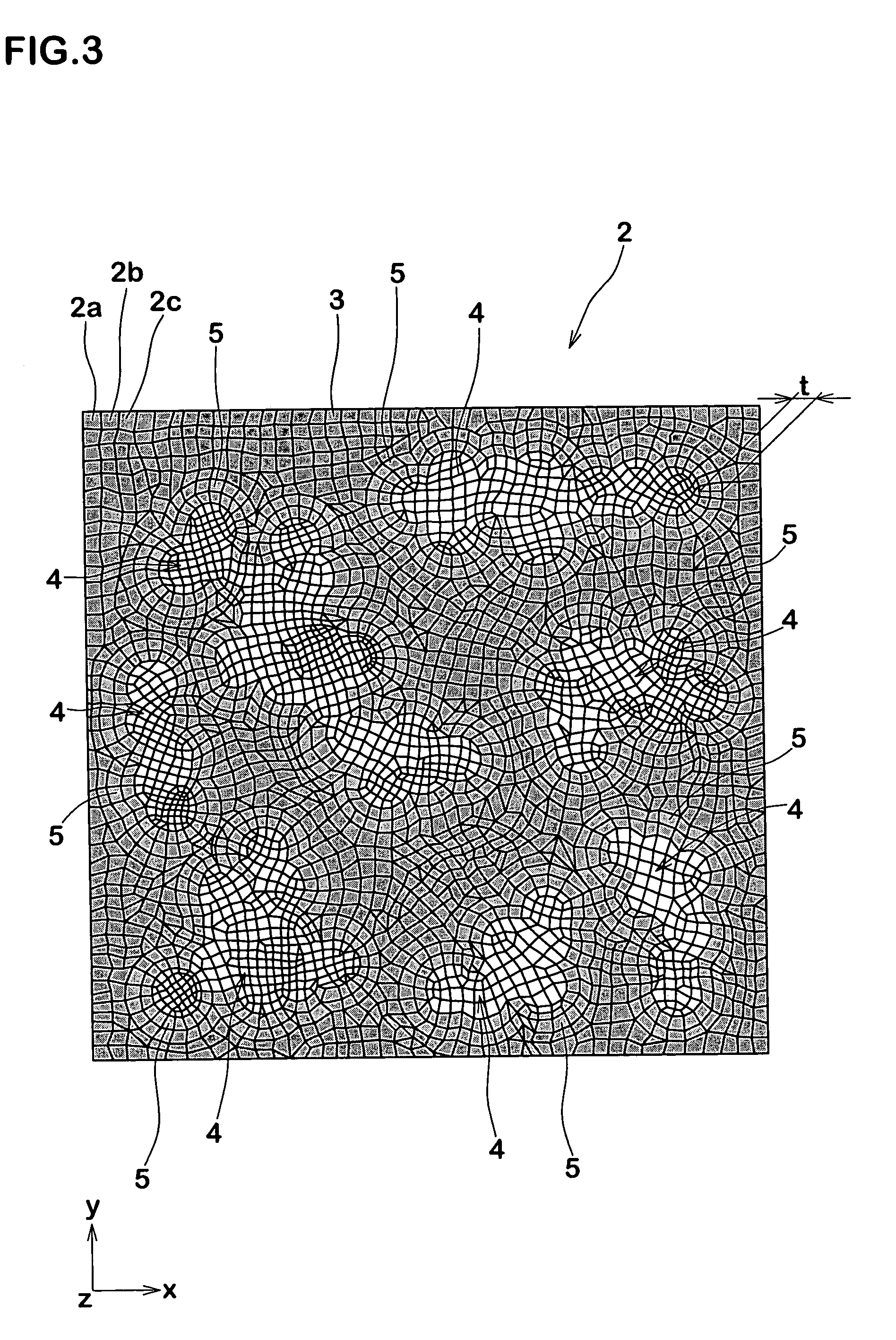

Method of simulating viscoelastic material

ActiveUS20050086034A1Improve accuracyFlow propertiesForce measurementFormation matrixMatrix partitioning

The present invention relates to a method of simulating the deformation of a viscoelastic material in which filler is blended to a matrix made of rubber or resin, the method including the steps of dividing the viscoelastic material into a finite number of elements to form a viscoelastic material model, a step of performing deformation calculation of the viscoelastic material model based on a predetermined condition, and a step of acquiring a necessary physical amount from the deformation calculation, where the step of dividing the viscoelastic material into a finite number of elements includes a step of dividing at least one filler into a finite number of elements to form a filler model, and a step of dividing the matrix into a finite number of elements to form a matrix model.

Owner:SUMITOMO RUBBER IND LTD

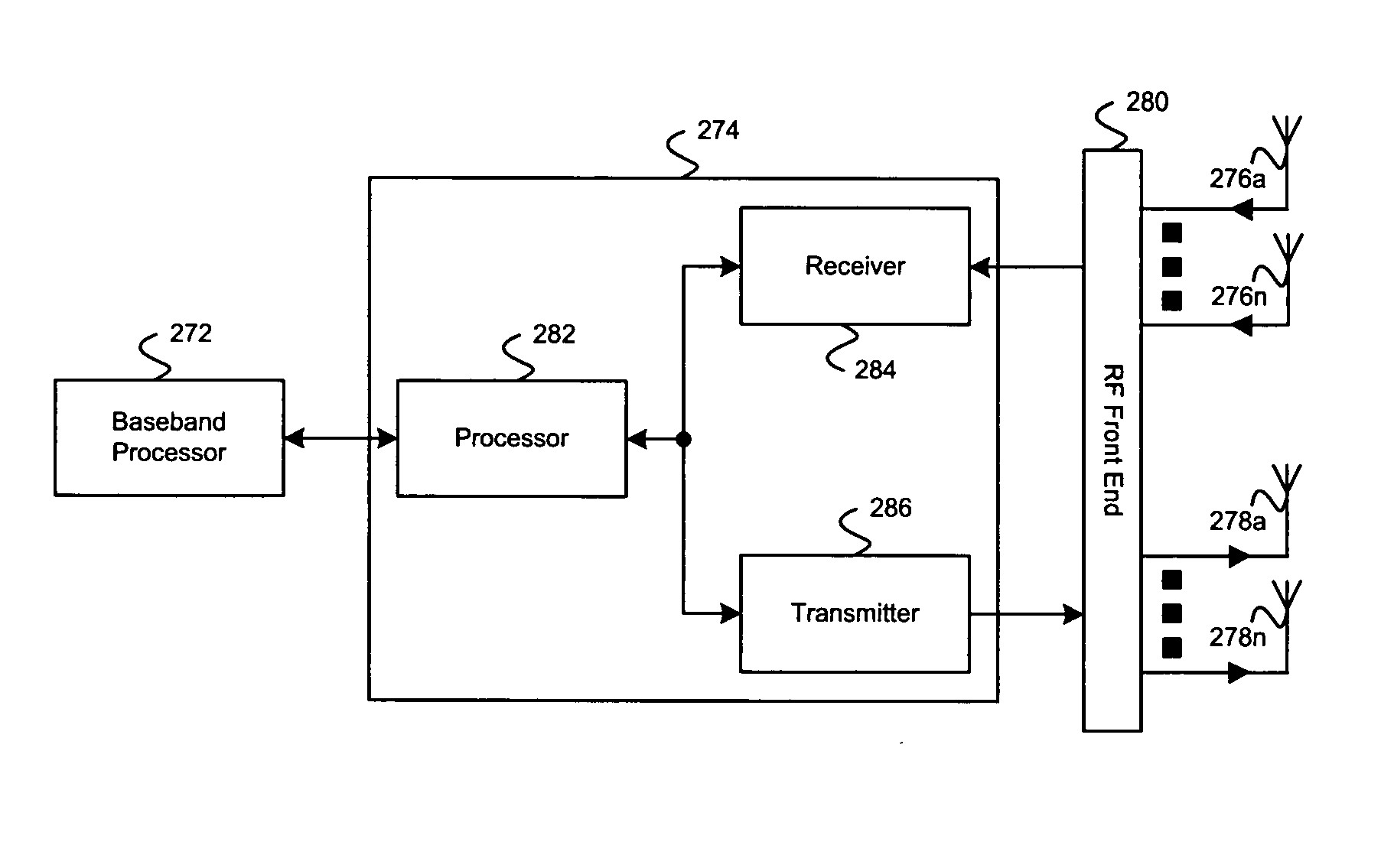

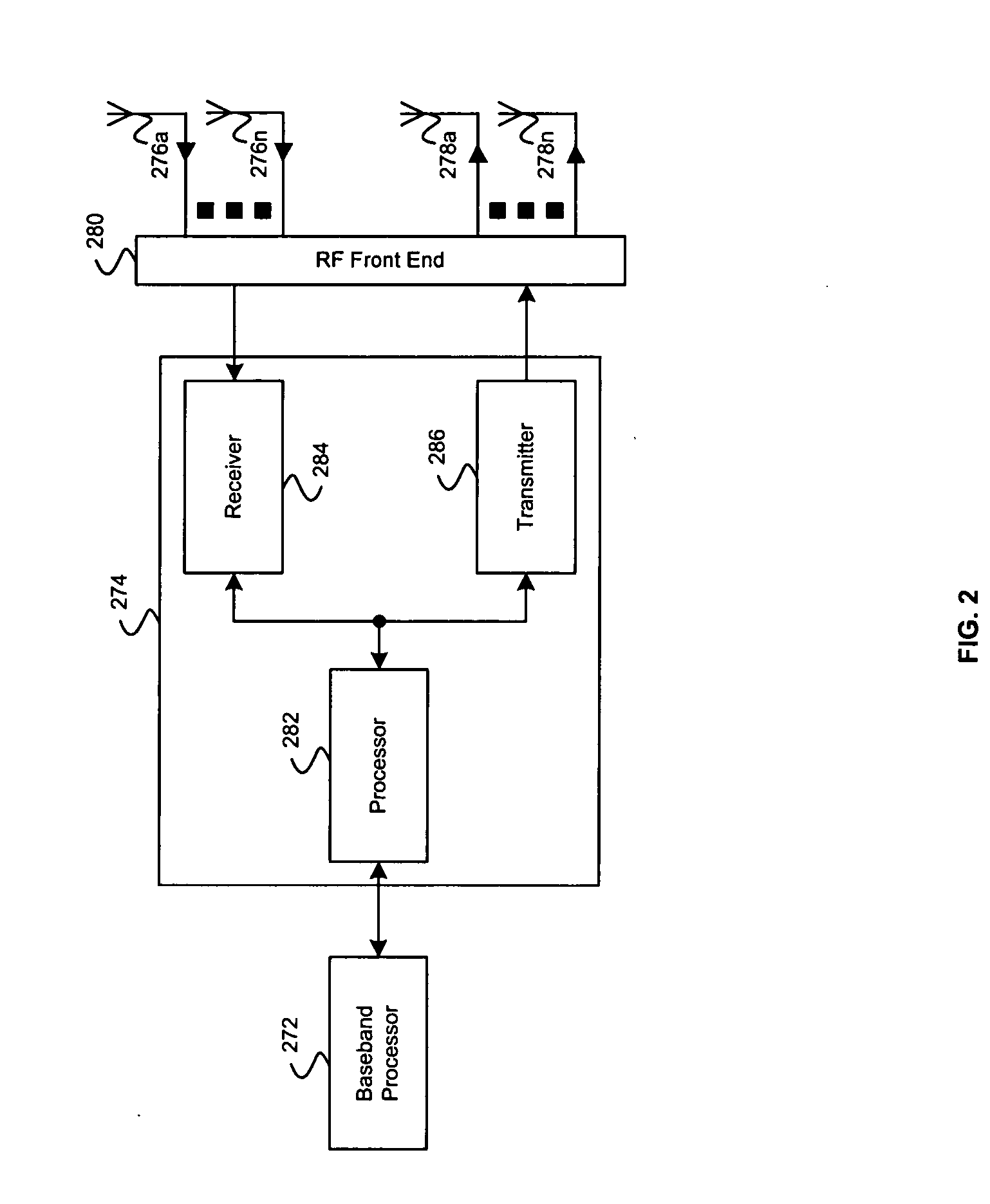

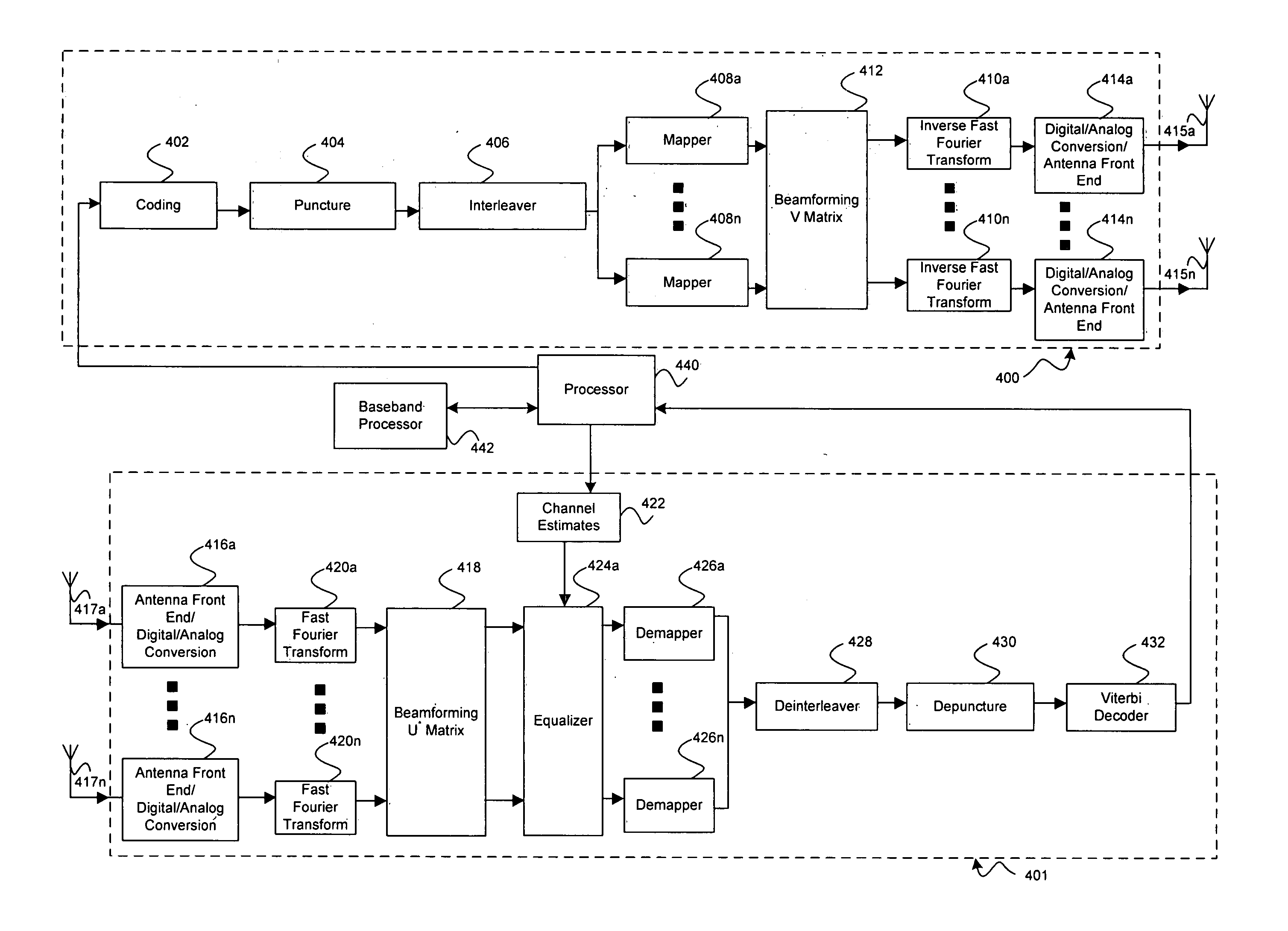

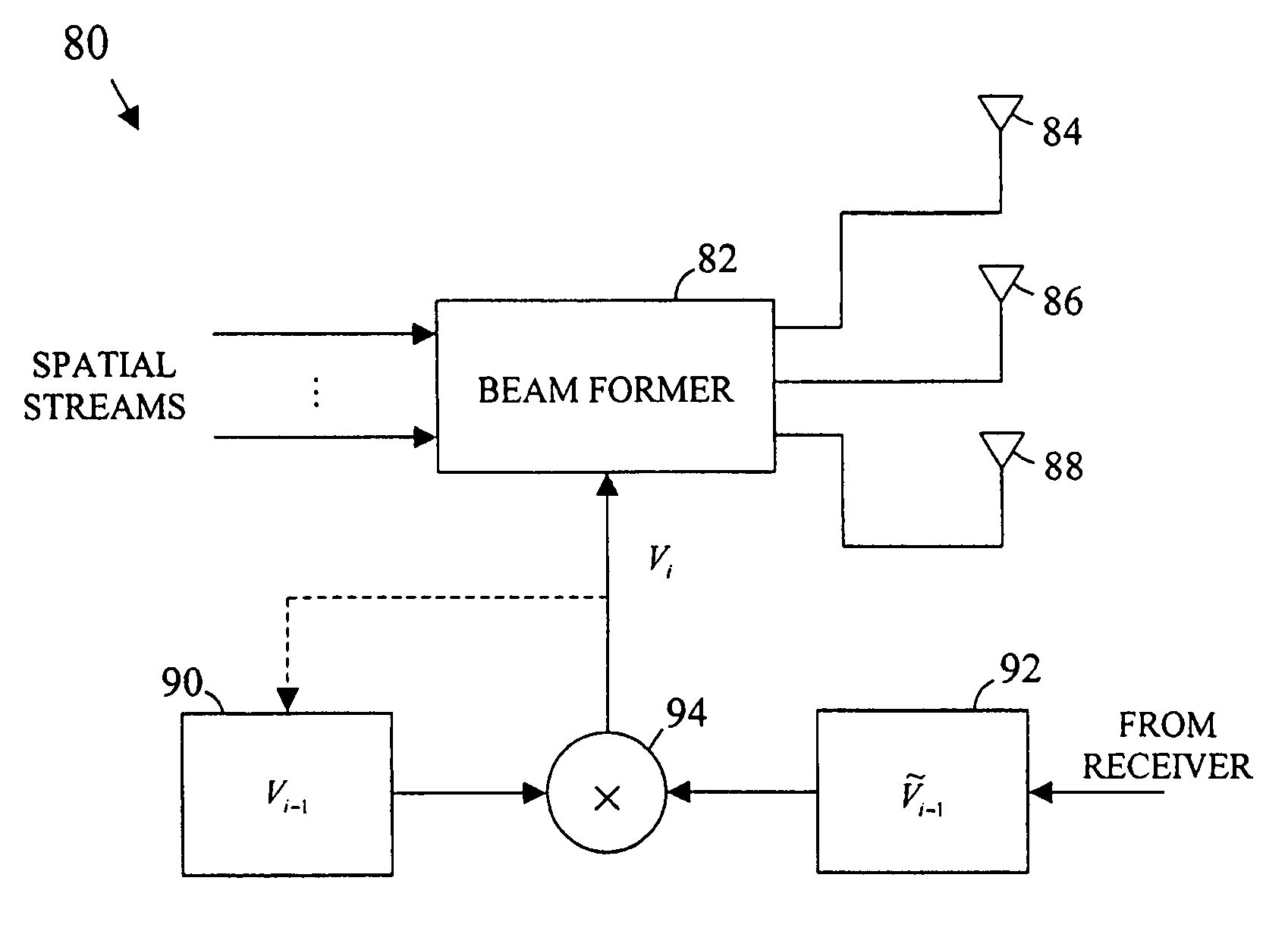

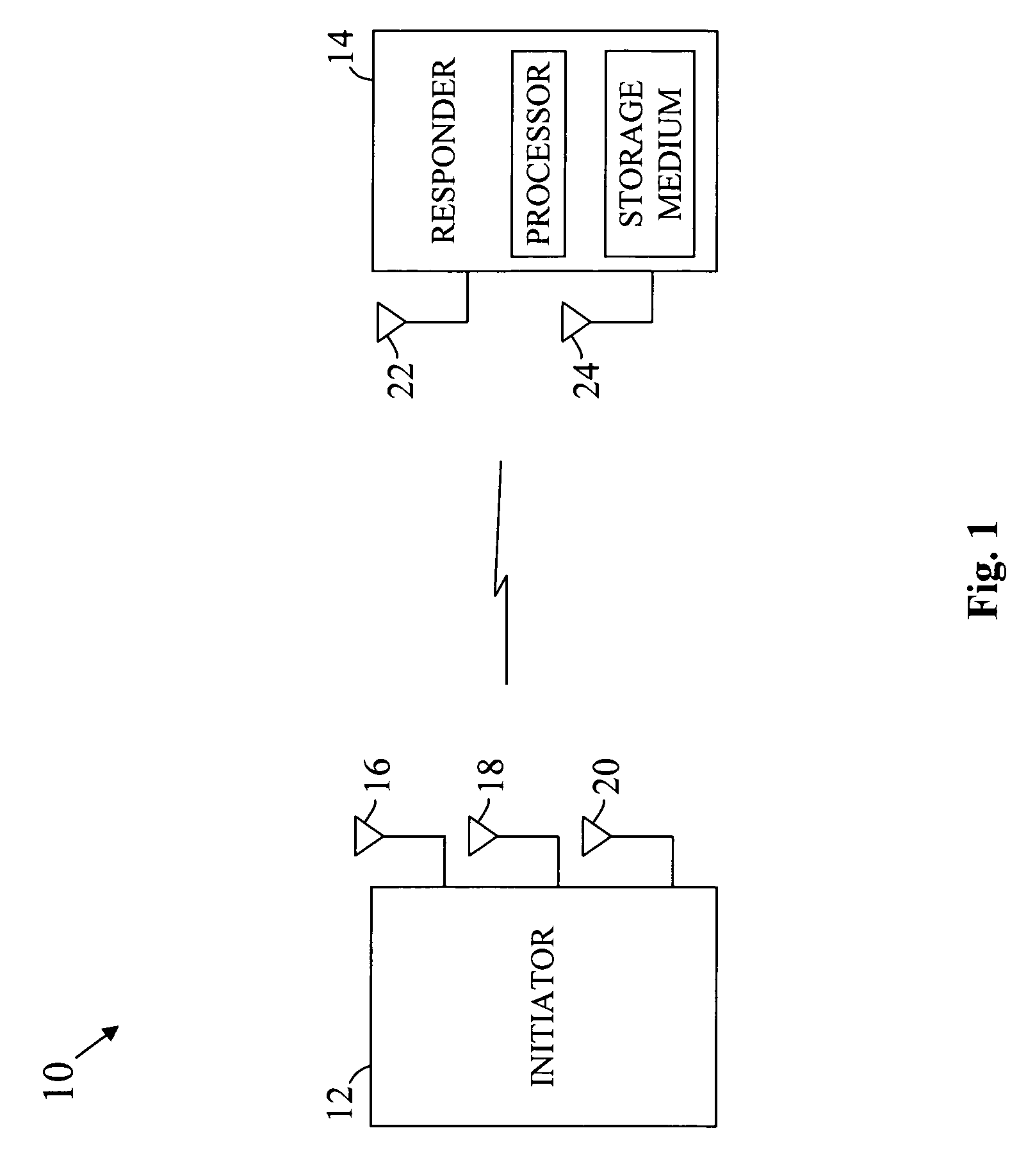

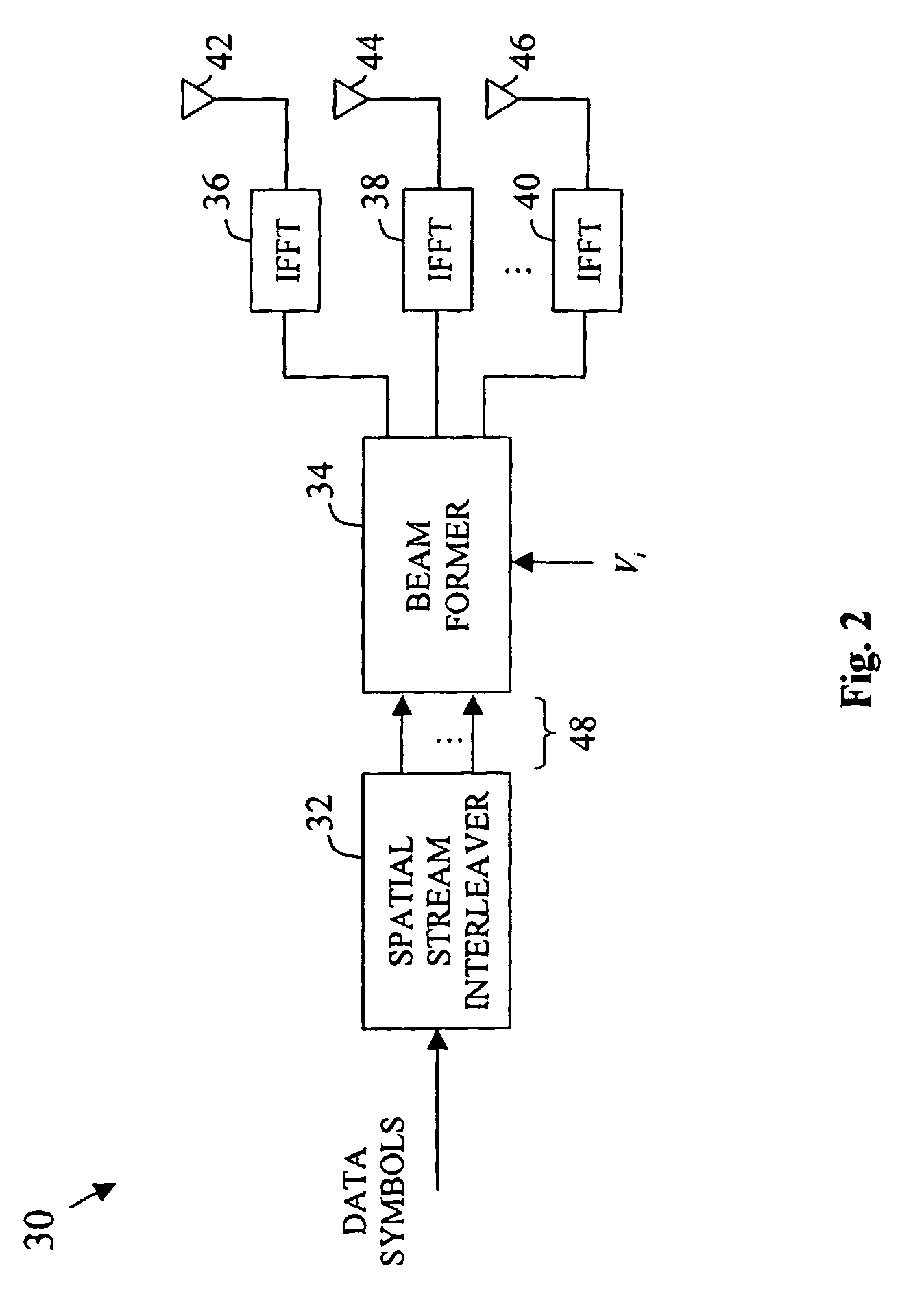

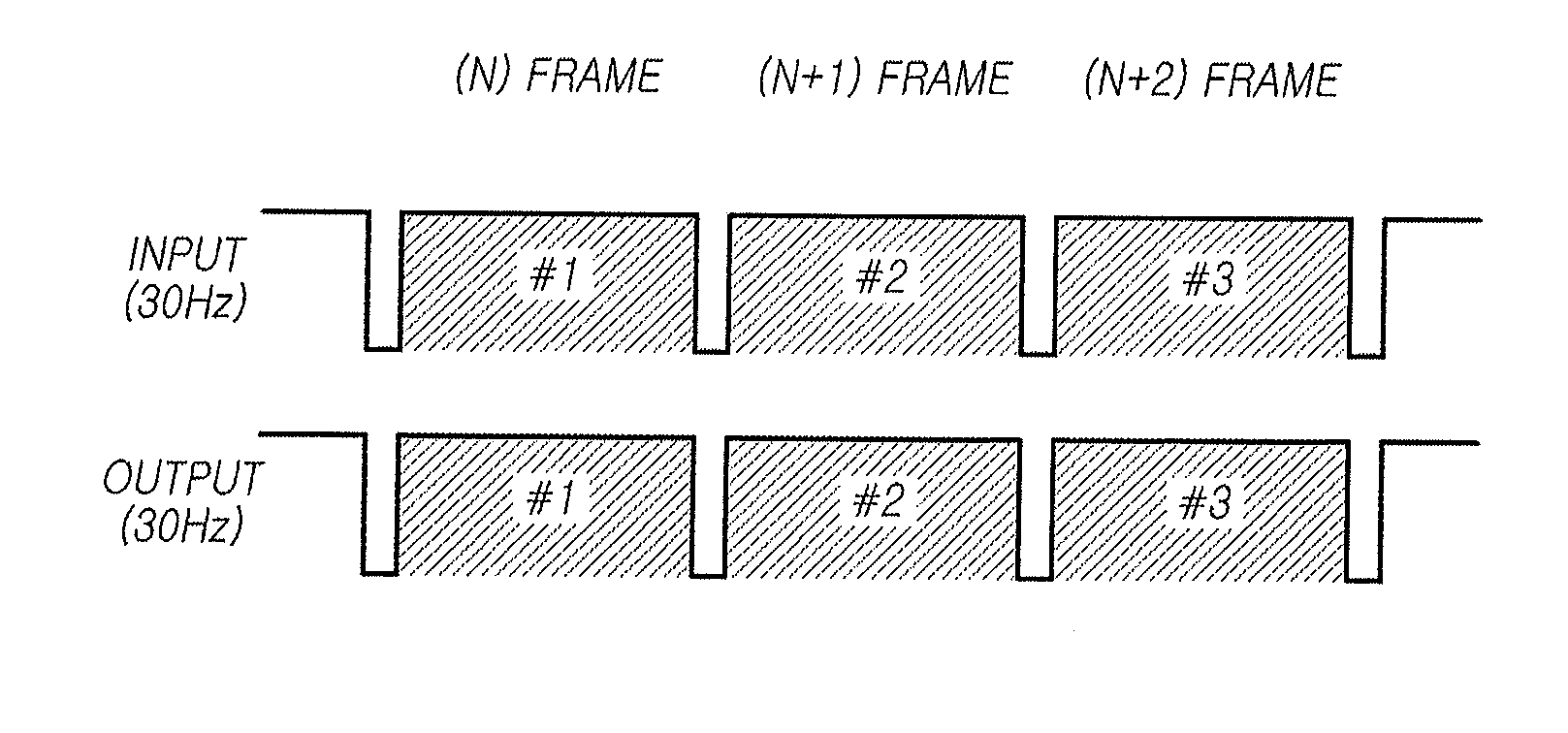

Method and apparatus for performing sequential closed loop multiple input multiple output (MIMO)

ActiveUS7609780B2Electric signal transmission systemsModulated-carrier systemsFormation matrixCommunications system

In a communication system using closed loop multiple input / multiple output MIMO, beam forming information may be fed back from a receiver to a transmitter sequentially over a number of frames. The beam forming matrices that are fed back may be quantized.

Owner:APPLE INC

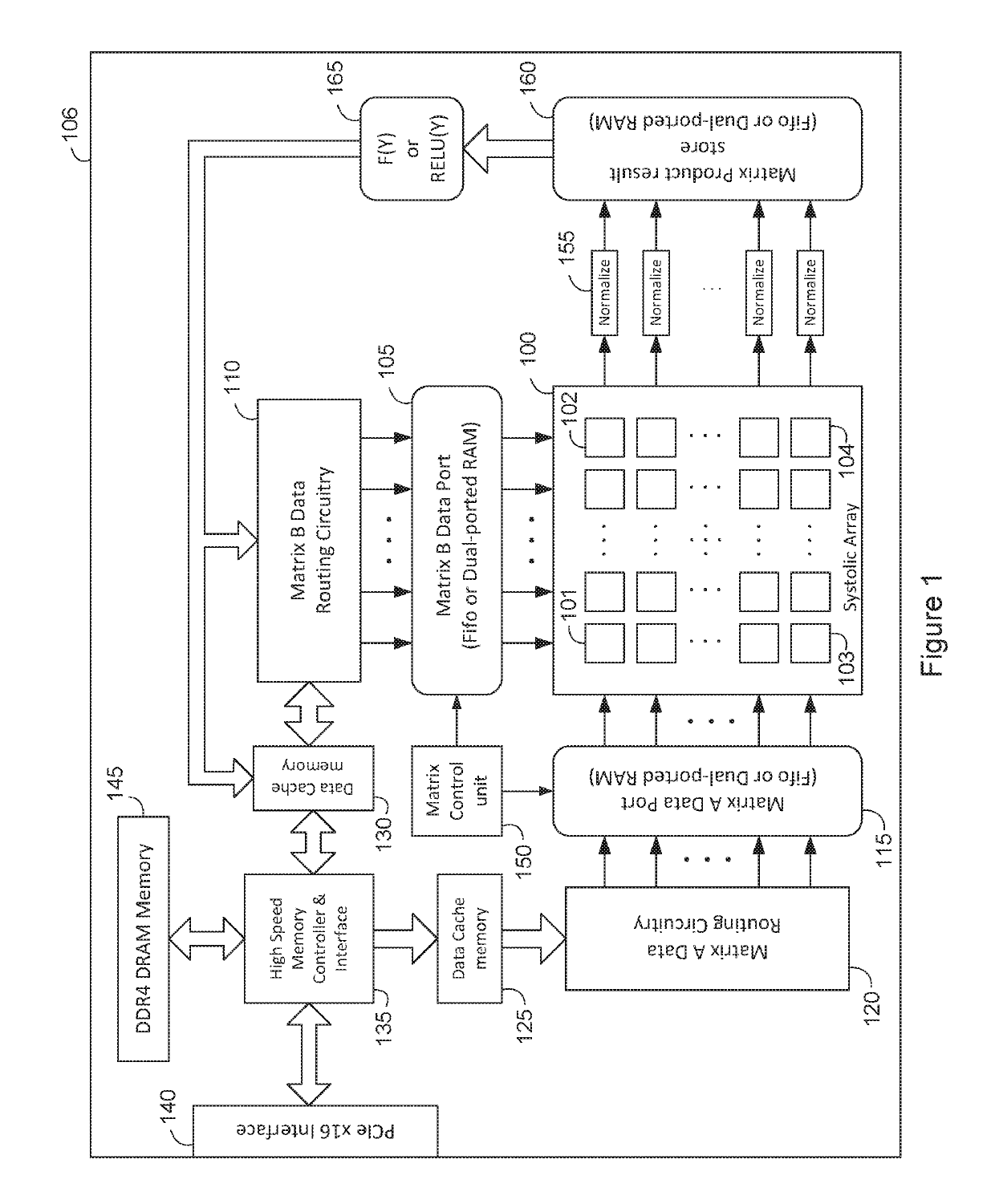

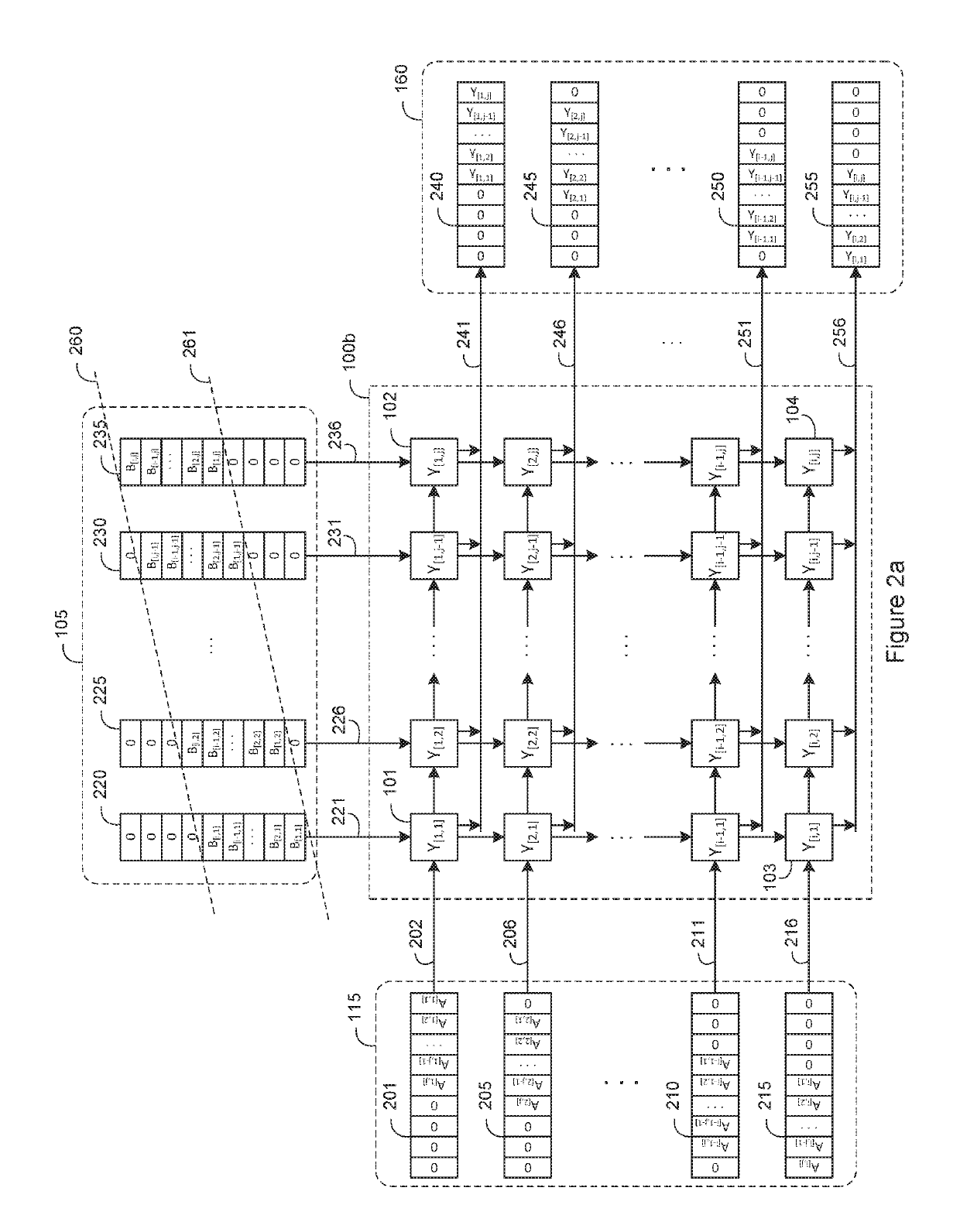

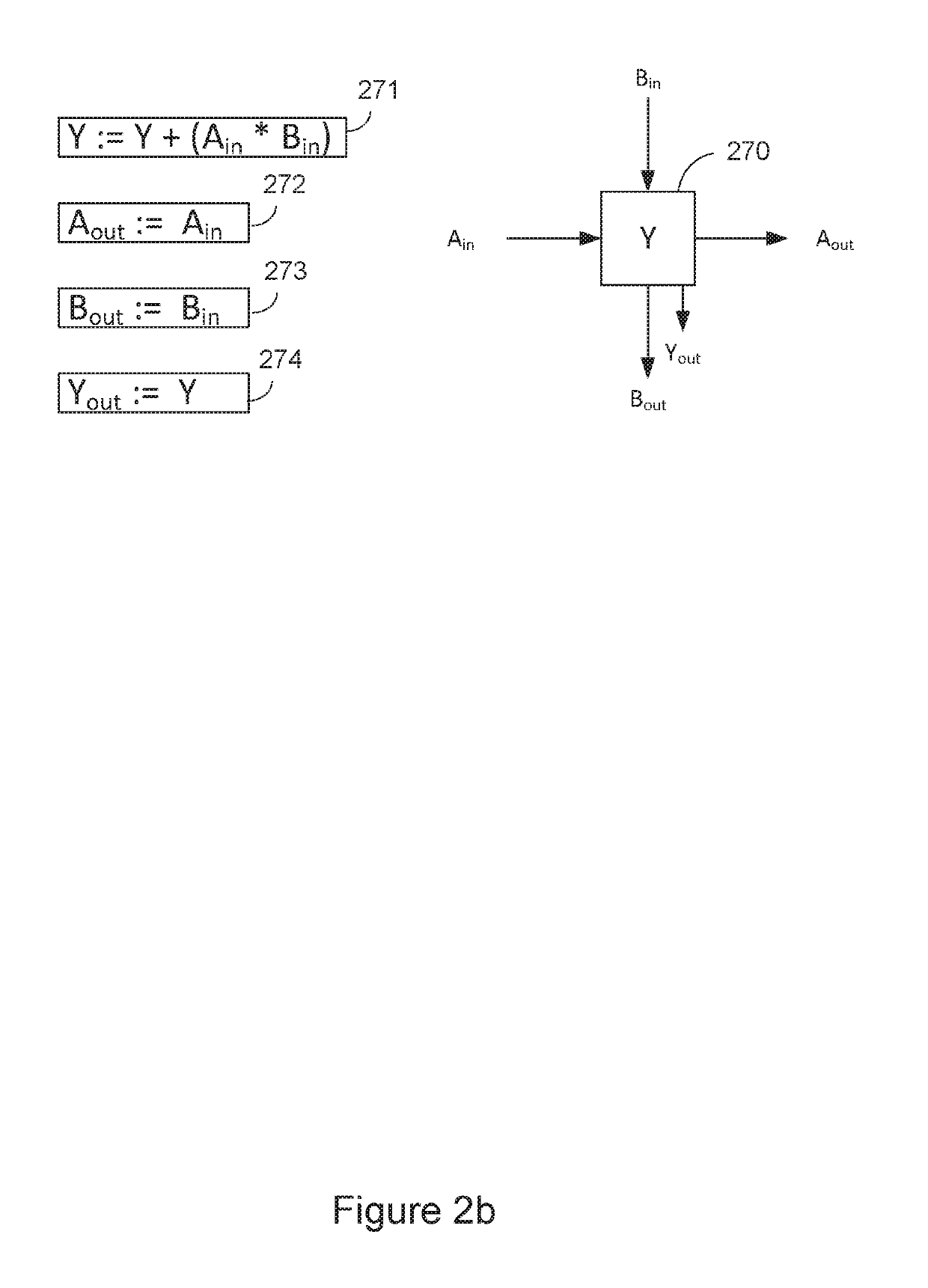

Residue number matrix multiplier

ActiveUS10387122B1Improve efficiencyIncrease speedComputations using residue arithmeticPhysical realisationFormation matrixAlgorithm

Arithmetic circuits and methods that perform efficient matrix multiplication for hardware acceleration of neural networks, machine learning, web search and other applications are disclosed herein. Various arrays of multiplier-accumulators may be coupled to form a matrix multiplier which processes data using high precision, fixed point residue number arithmetic.

Owner:OLSEN IP RESERVE

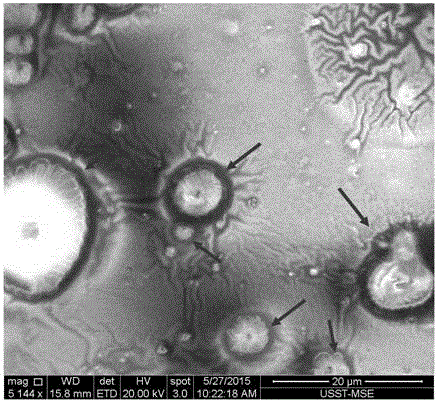

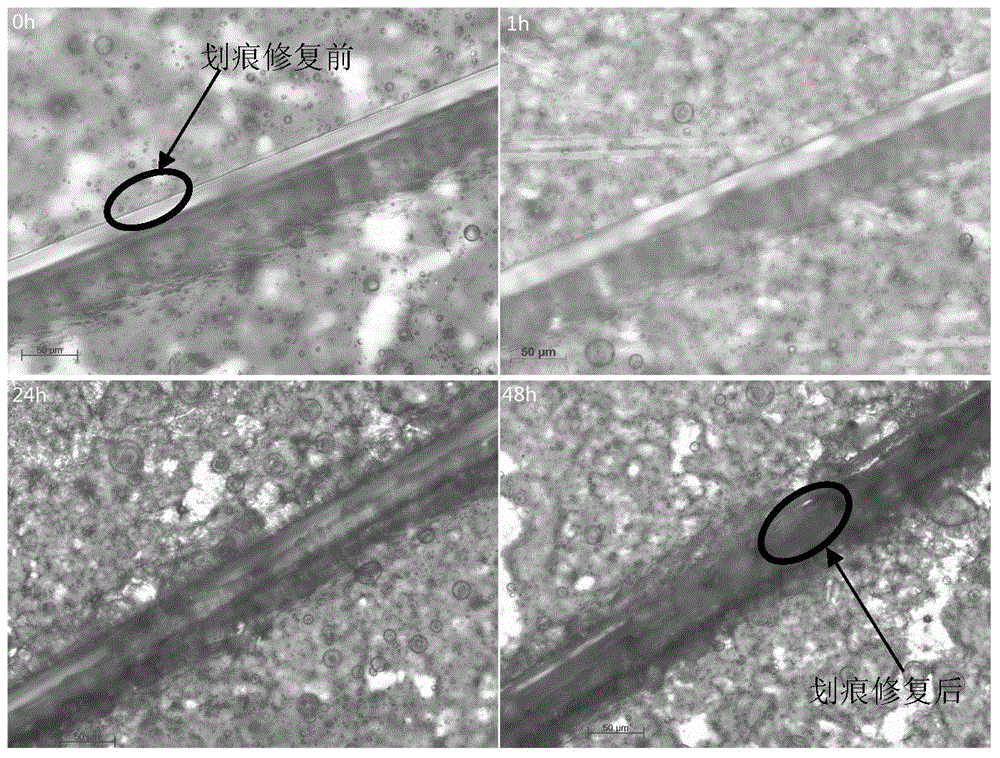

Metal surface anticorrosive coating comprising graphene and preparing method thereof

ActiveCN104946114AImprove barrier propertiesImprove mechanical propertiesAnti-corrosive paintsPolyurea/polyurethane coatingsFormation matrixCoating system

The invention discloses a metal surface anticorrosive coating comprising graphene and a preparing method thereof. The coating is formed by dried self-repairing microcapsules evenly dispersed in a film formation matrix. The self-repairing microcapsules are formed by wrapping organic repairing agents with the graphene, and the film formation matrix includes waterborne organic resin. According to the metal surface anticorrosive coating comprising graphene and the preparing method thereof, all the components of a coating system are in synergism to commonly form the self-repairing coating which is good in performance.

Owner:UNIV OF SHANGHAI FOR SCI & TECH

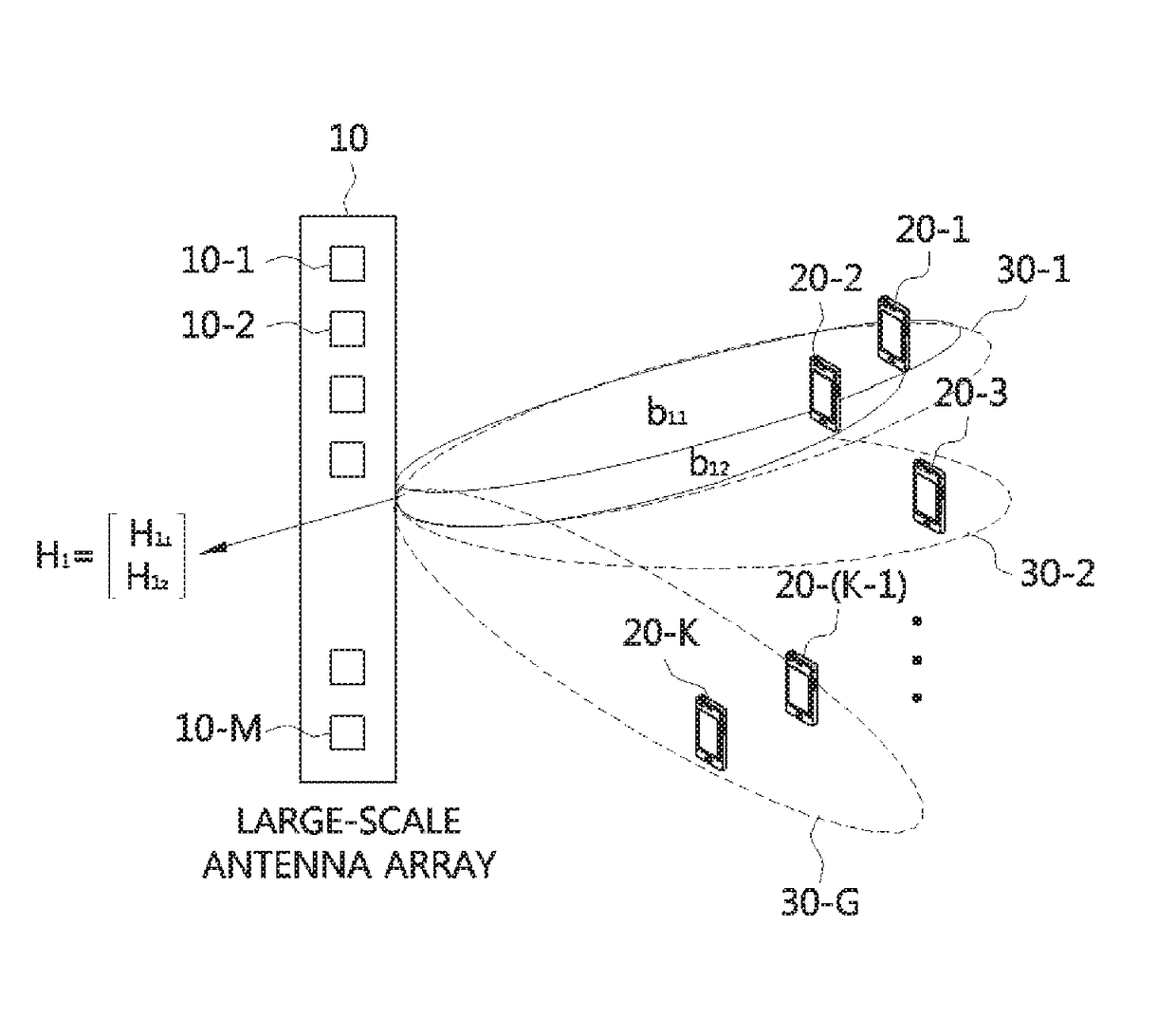

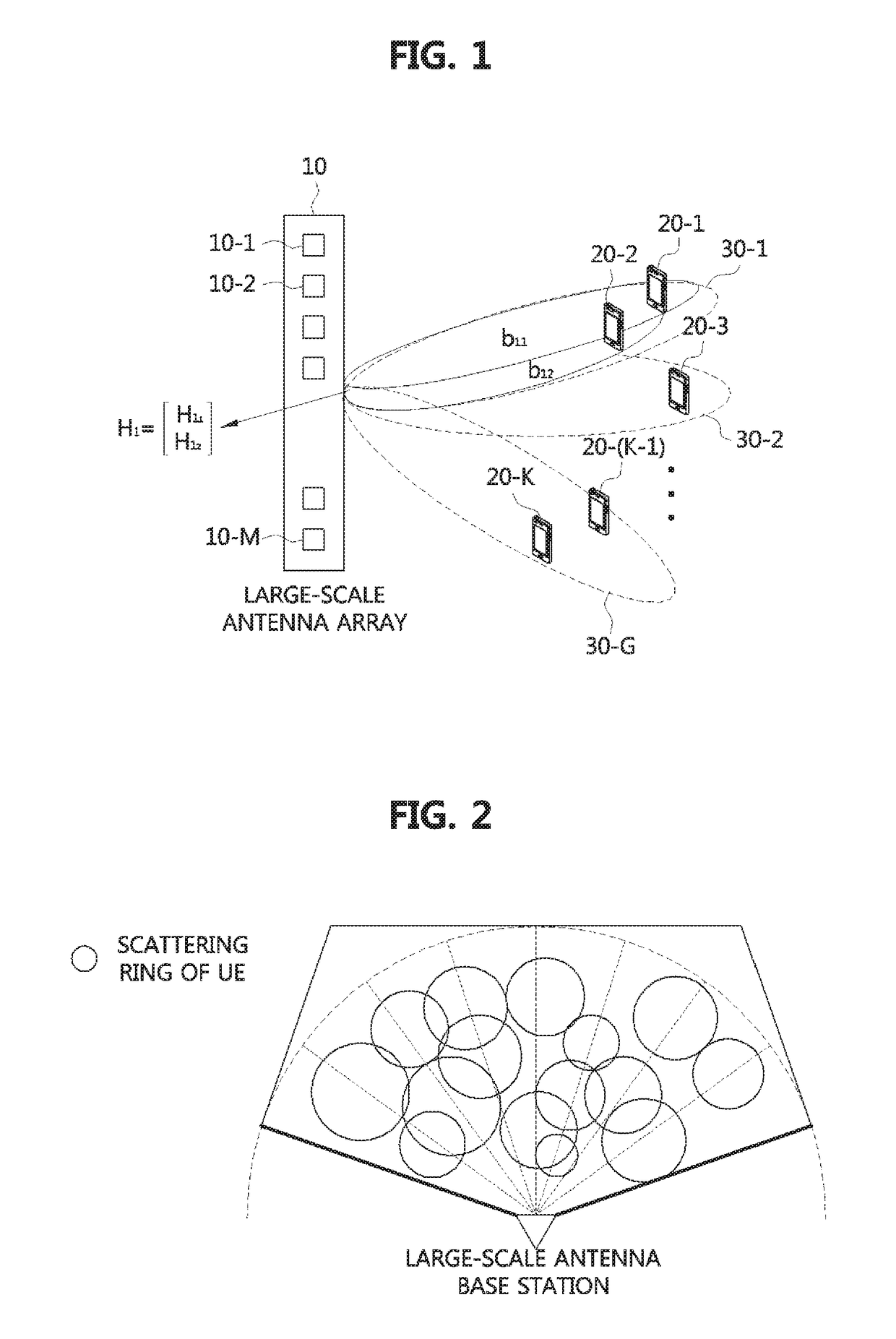

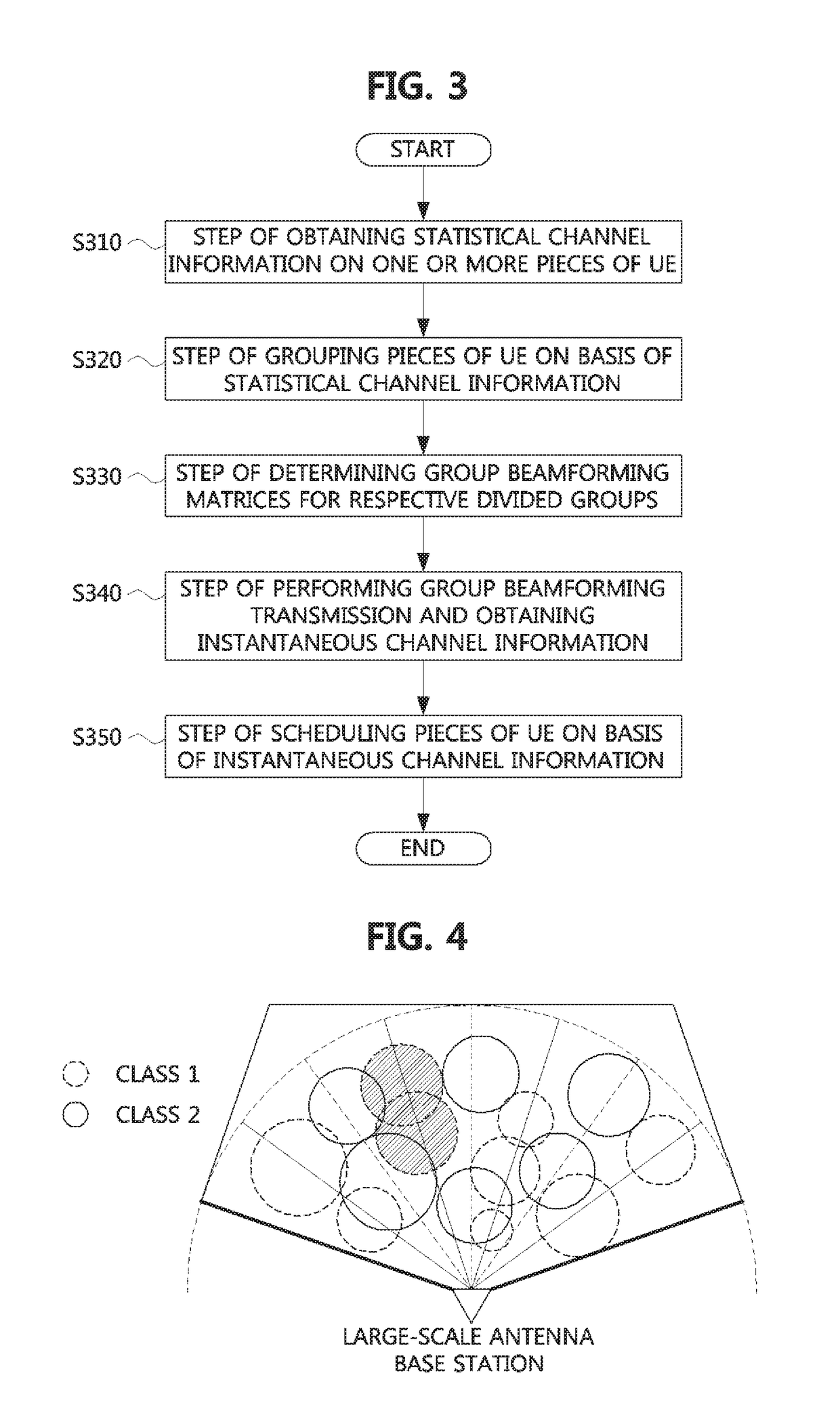

Multi-input and multi-output communication method in large-scale antenna system

ActiveUS20170208613A1Reduce system complexityEfficient executionSpatial transmit diversitySignalling characterisationChannel state informationMulti input

Owner:ELECTRONICS & TELECOMM RES INST

Method of simulating viscoelastic material

The present invention relates to a method of simulating the deformation of a viscoelastic material in which filler is blended to a matrix made of rubber or resin, the method including the steps of dividing the viscoelastic material into a finite number of elements to form a viscoelastic material model, a step of performing deformation calculation of the viscoelastic material model based on a predetermined condition, and a step of acquiring a necessary physical amount from the deformation calculation, where the step of dividing the viscoelastic material into a finite number of elements includes a step of dividing at least one filler into a finite number of elements to form a filler model, and a step of dividing the matrix into a finite number of elements to form a matrix model.

Owner:SUMITOMO RUBBER IND LTD

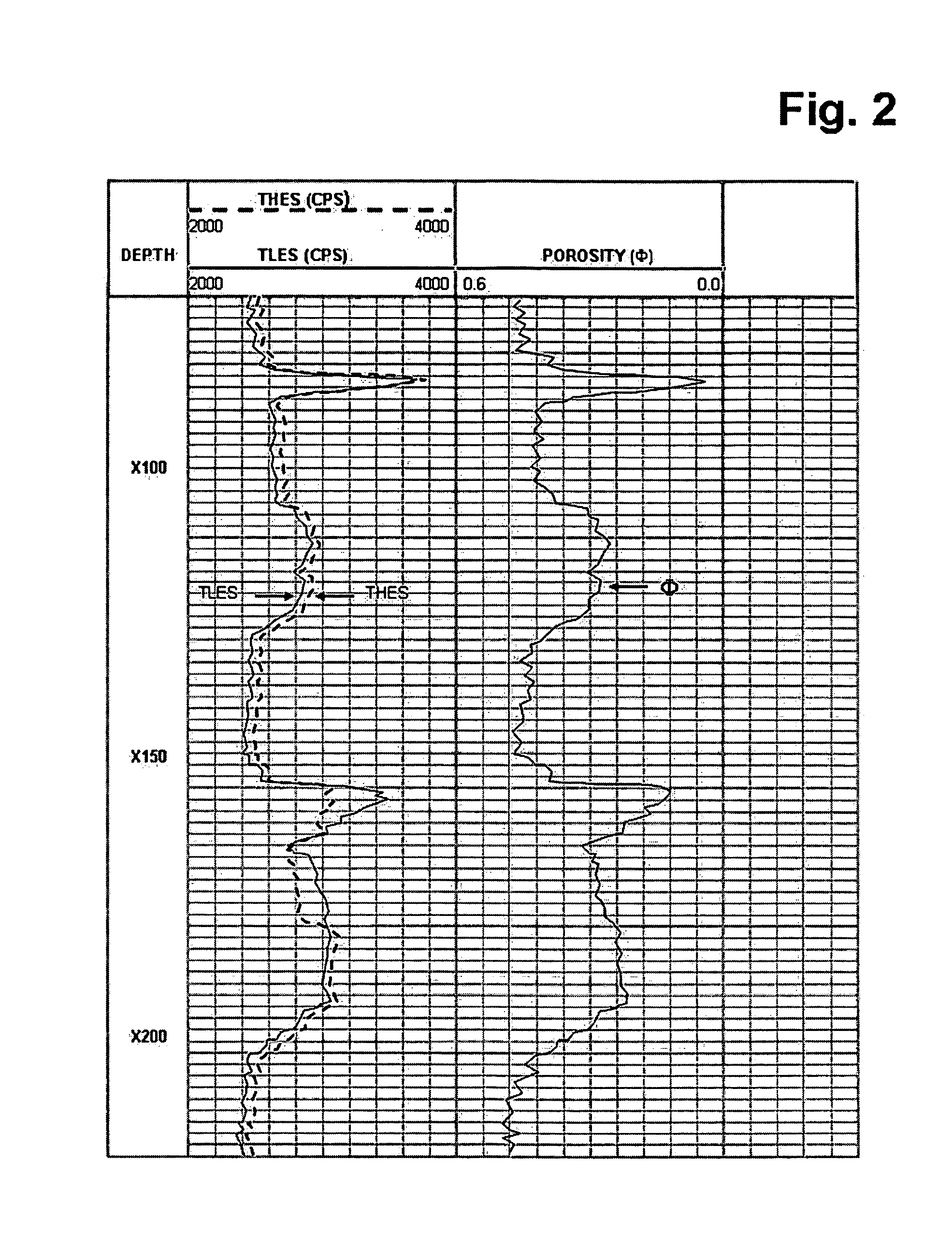

Irradiated formation tool (IFT) apparatus and method

InactiveUS7511266B1High capture cross-sectionAccurate water saturationNuclear radiation detectionFormation matrixWell logging

A well logging instrument that has a neutron source for irradiating earth formations traversing a borehole used in deriving useful information pertaining to said formations. Three detectors are mounted in a spaced-apart vertical relationship within a pressure-resistant housing. The detectors nearest and farthest from the neutron source detect thermal neutrons while the third detector from the neutron source detects a rare earth compensated aggregate capture gamma ray spectrum. By comparing the irradiated formations as detected by the three detectors, certain formation fluid, matrix, and pore volume parameters are derived. Also, by comparing the count rates of high and low energy ranges of the third detector in earth coal formation matrix, an ash volume is determined. From this value, a bulk density is derived from the corresponding earth coal formation.

Owner:NRC ENTERPRISES

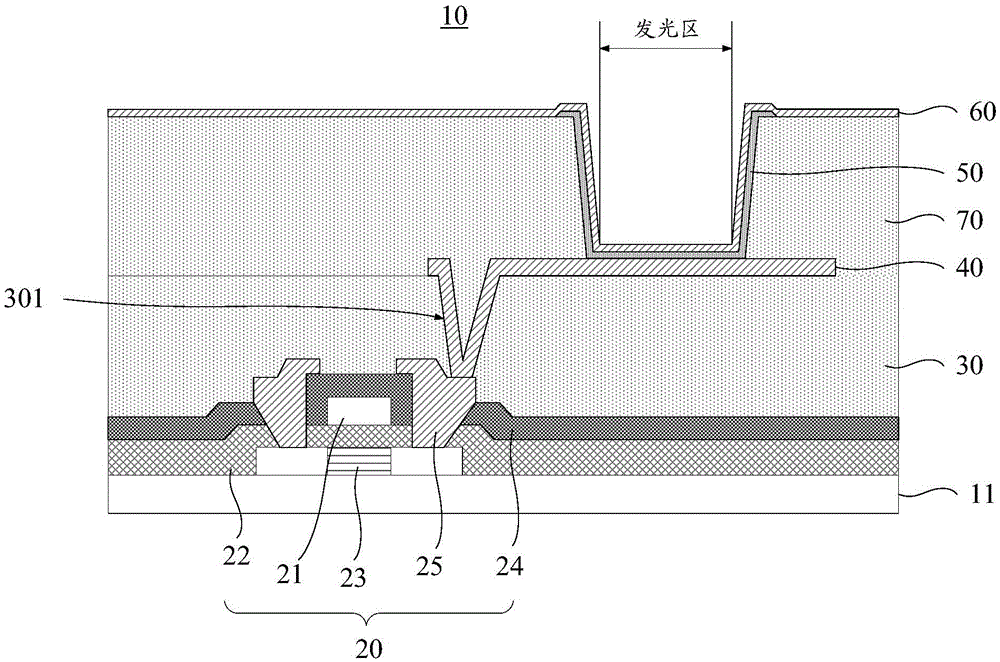

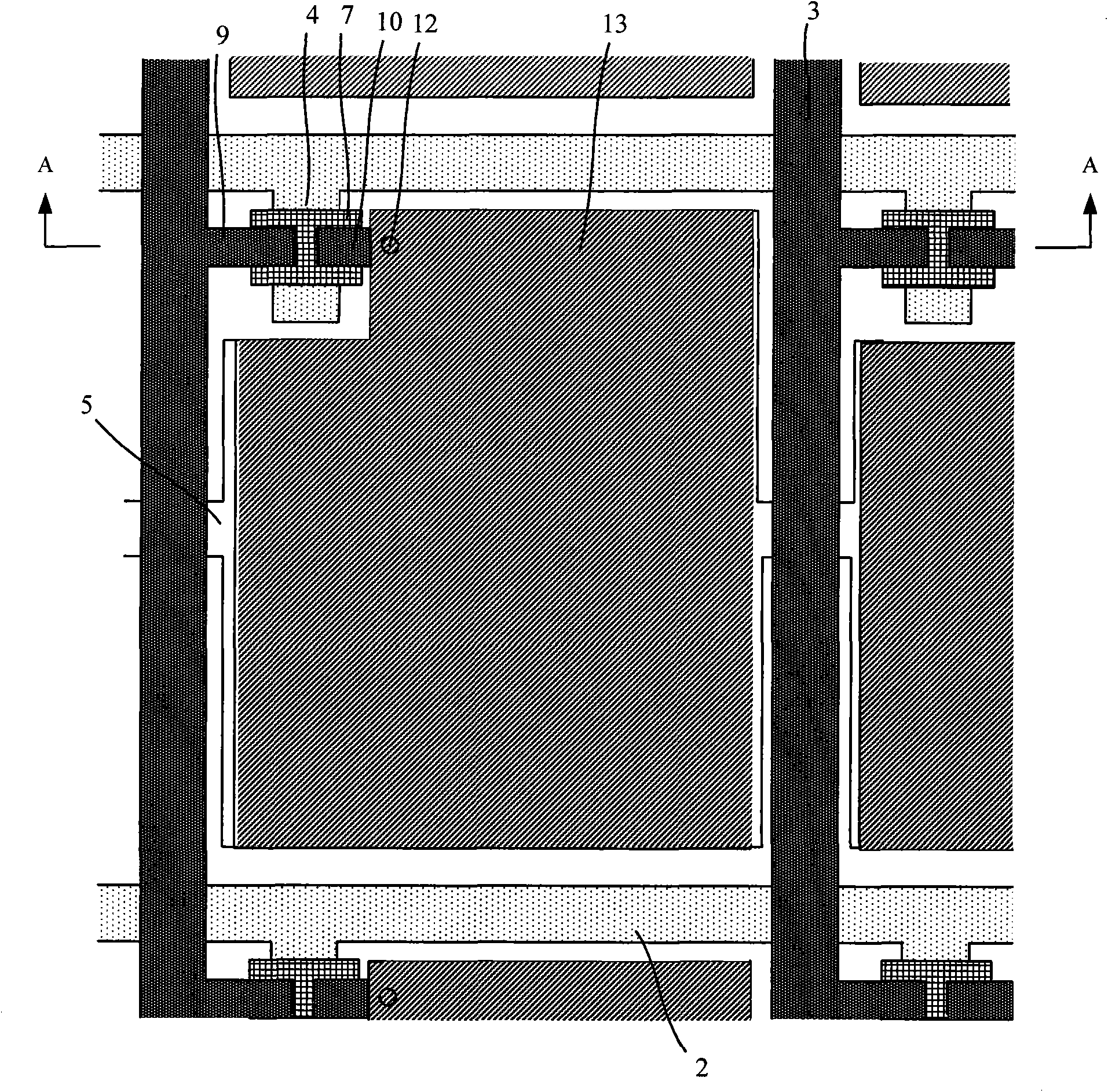

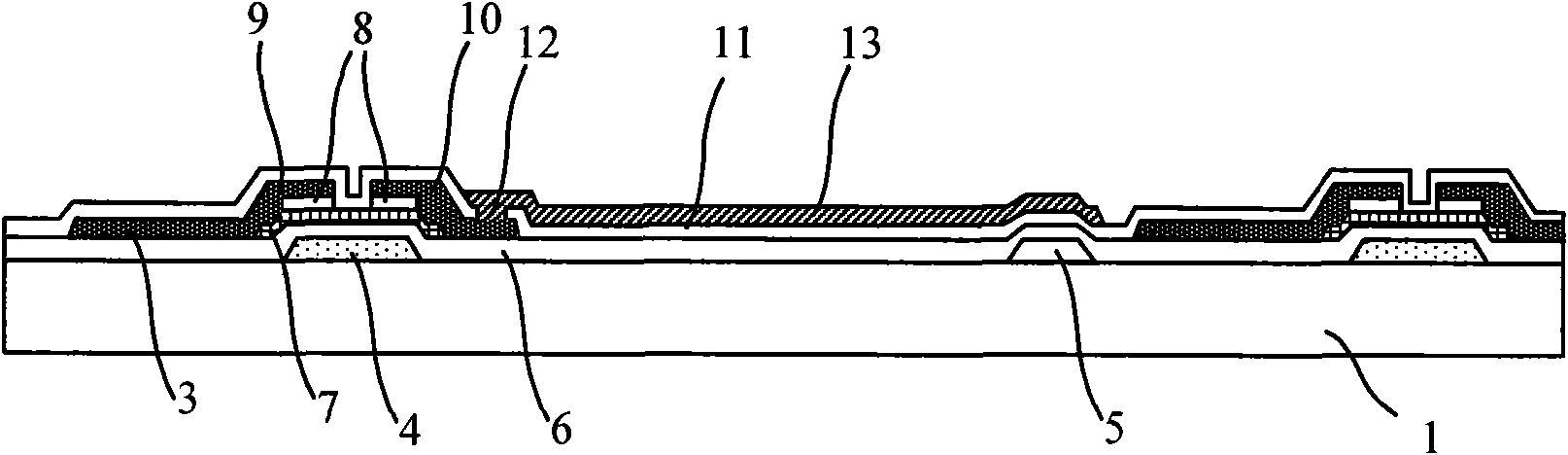

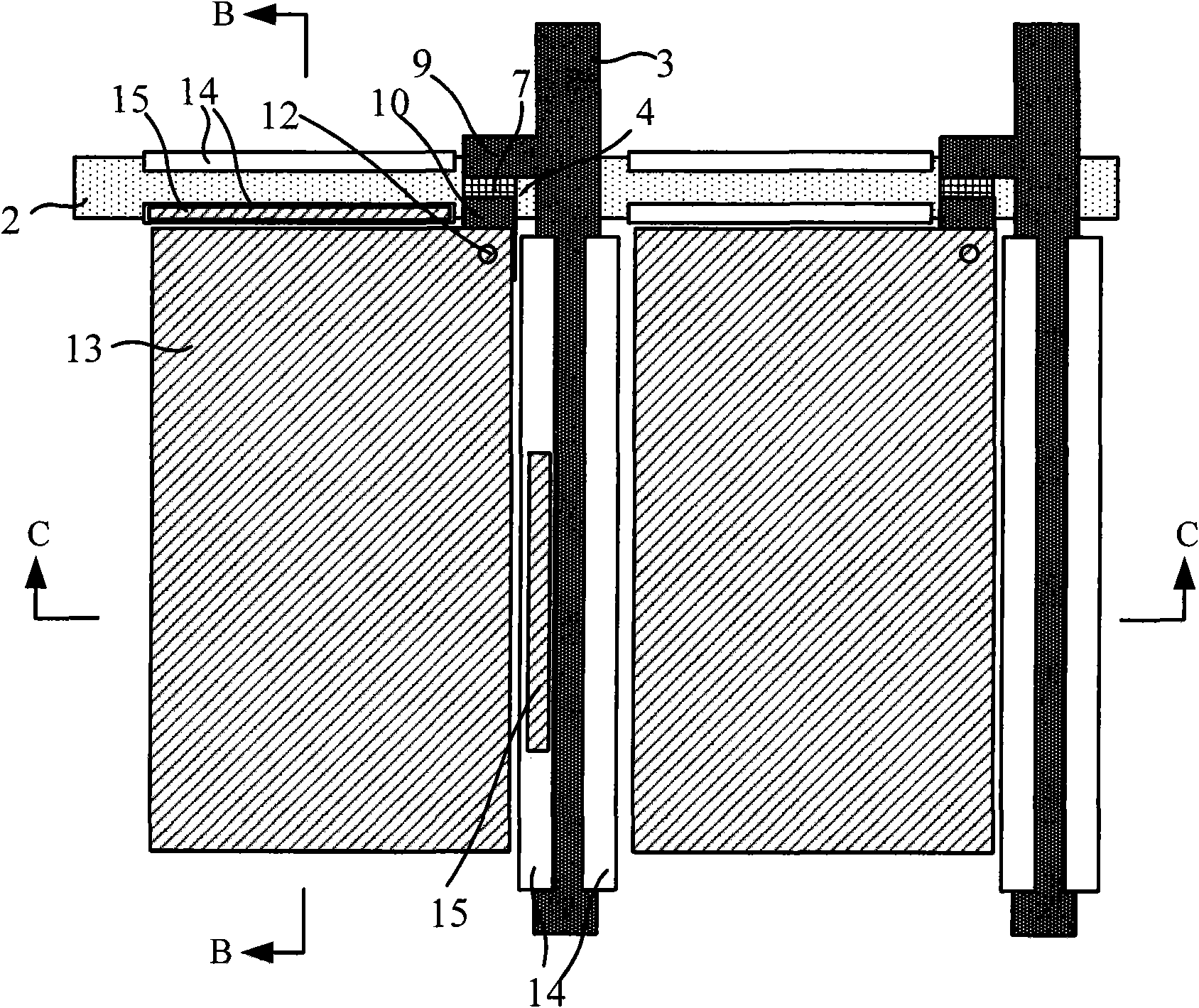

Array substrate as well as manufacturing method and liquid crystal display panel thereof

InactiveCN101833204AReduce or avoid short circuitImprove display qualitySemiconductor/solid-state device detailsSolid-state devicesLiquid-crystal displayFormation matrix

The invention relates to an array substrate as well as a manufacturing method and a liquid crystal display panel thereof. A groove is formed on a passivation layer of the array substrate and correspondingly formed between two adjacent pixel electrodes; and the depth of the groove is less than that of the passivation layer. The method comprises the following steps of: forming patterns with a plurality of film layers on the substrate; forming the passivation layer on the substrate with the plurality of film layers forming; forming a passivation layer through hole and the groove on the passivation layer; depositing a transparent conducting film layer on the passivation layer with the groove forming; and forming a plurality of pixel electrodes in a matrix mode by adopting a mapping process. The liquid crystal display panel comprises the array substrate. In the invention, the groove is formed on the passivation layer beyond the pixel electrode area, therefore, a pixel electrode material layer can form a faultage at the edge of the groove, and the connected short-circuit between the adjacent pixel electrodes is reduced or avoided, thereby improving the finished product ratio.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD

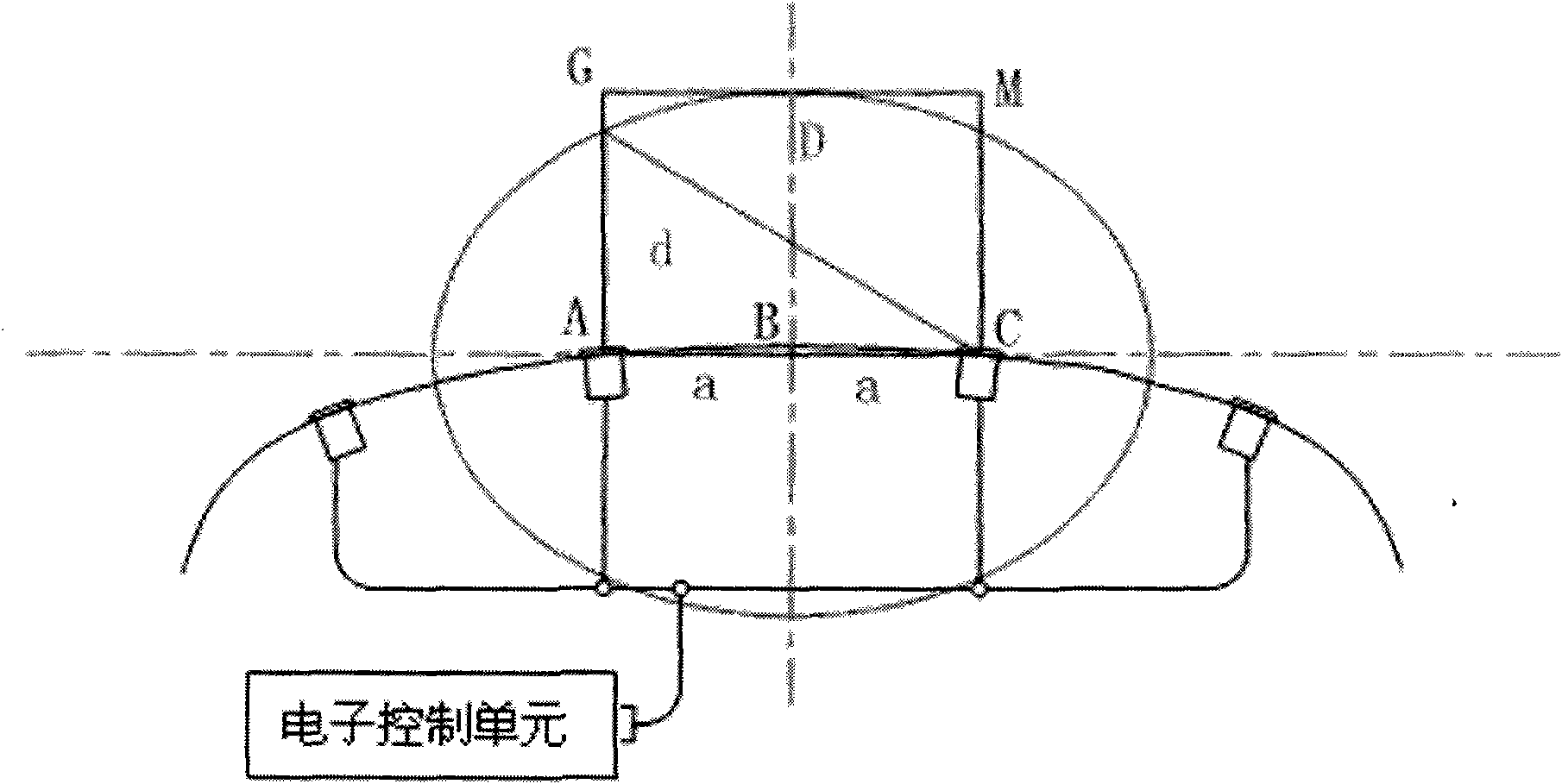

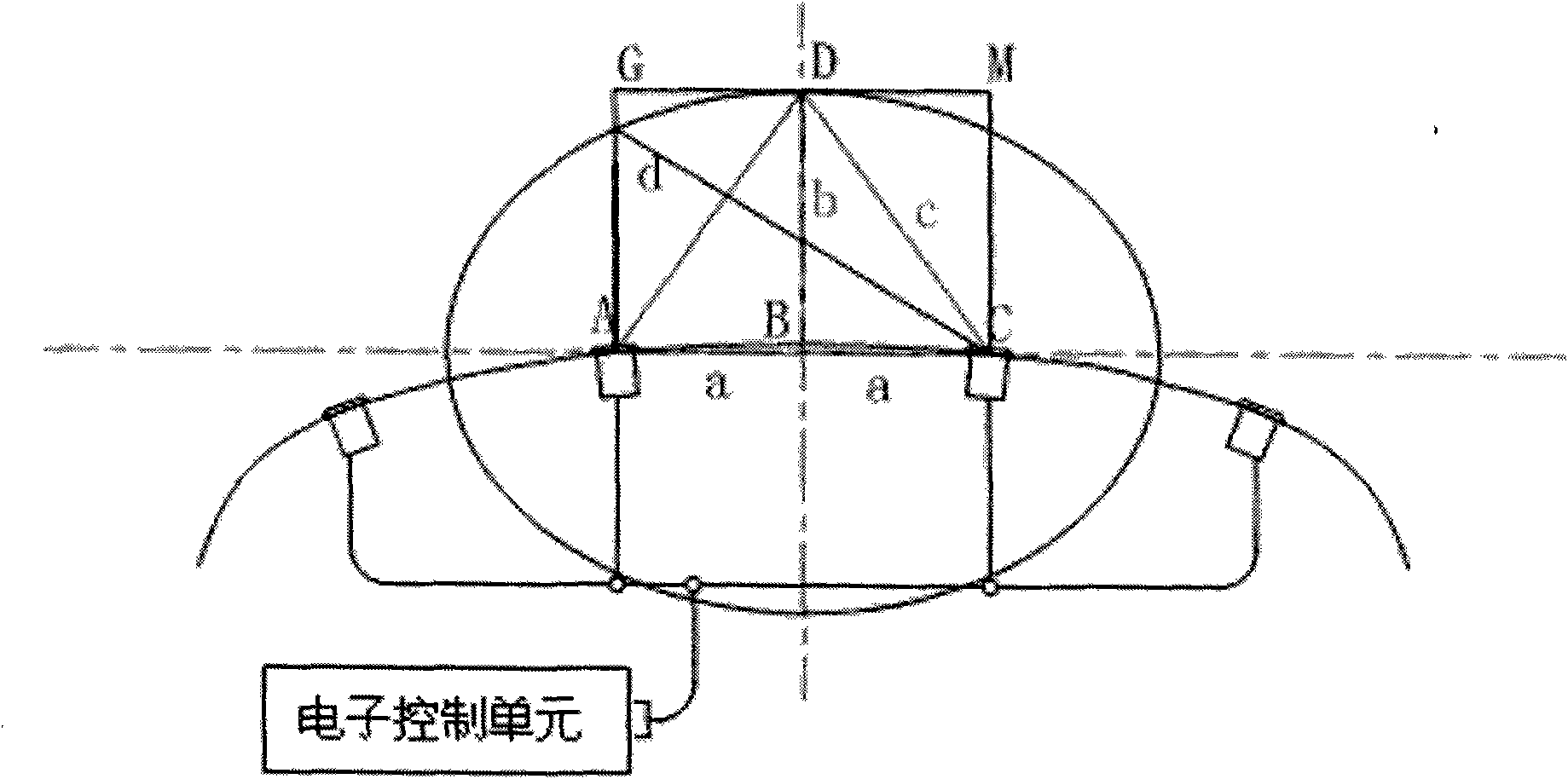

Reverse sensor range positioning method and system for assisting parking

ActiveCN101887125AAvoid misjudgmentHigh outputAcoustic wave reradiationFormation matrixDecision model

The invention relates to a reverse sensor range positioning method and a reverse sensor range positioning system for as assisting parkin. The method comprises the following steps of: performing matrix division on a detected area by establishing a mathematic model; establishing a decision model of each range grade in each detected area; externally calculating a judgment parameter of each matrix, and saving the judgment parameter in a calculation unit, or calculating the judgment parameter in real time by the calculation unit, wherein the judgment parameter is used for judging whether barriers exist in the matrix area or not. The method and the system have the advantages that: 1, the method and the system are applied to a plurality of barriers or barriers with special shapes in actual situations so as to avoid misjudgment; and 2, the detected area is divided horizontally, and the range grade is divided vertically to form the matrix, so that the position of the barrier can be clearly indicated, and is conveniently outputted to a prompt system, a video display and a sound alarm for visual prompt.

Owner:HANGZHOU AUTOMOTIVE TECH CO LTD

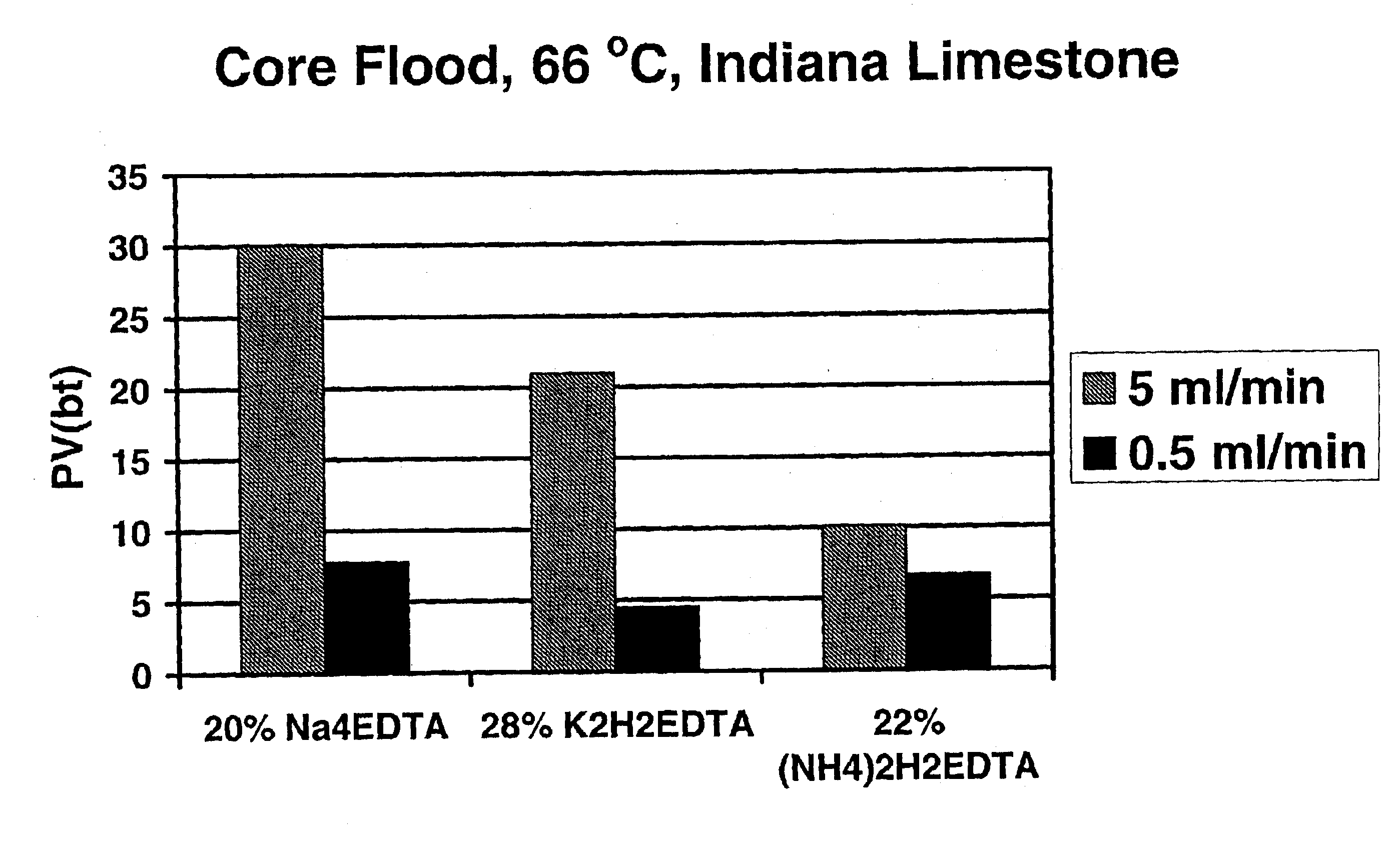

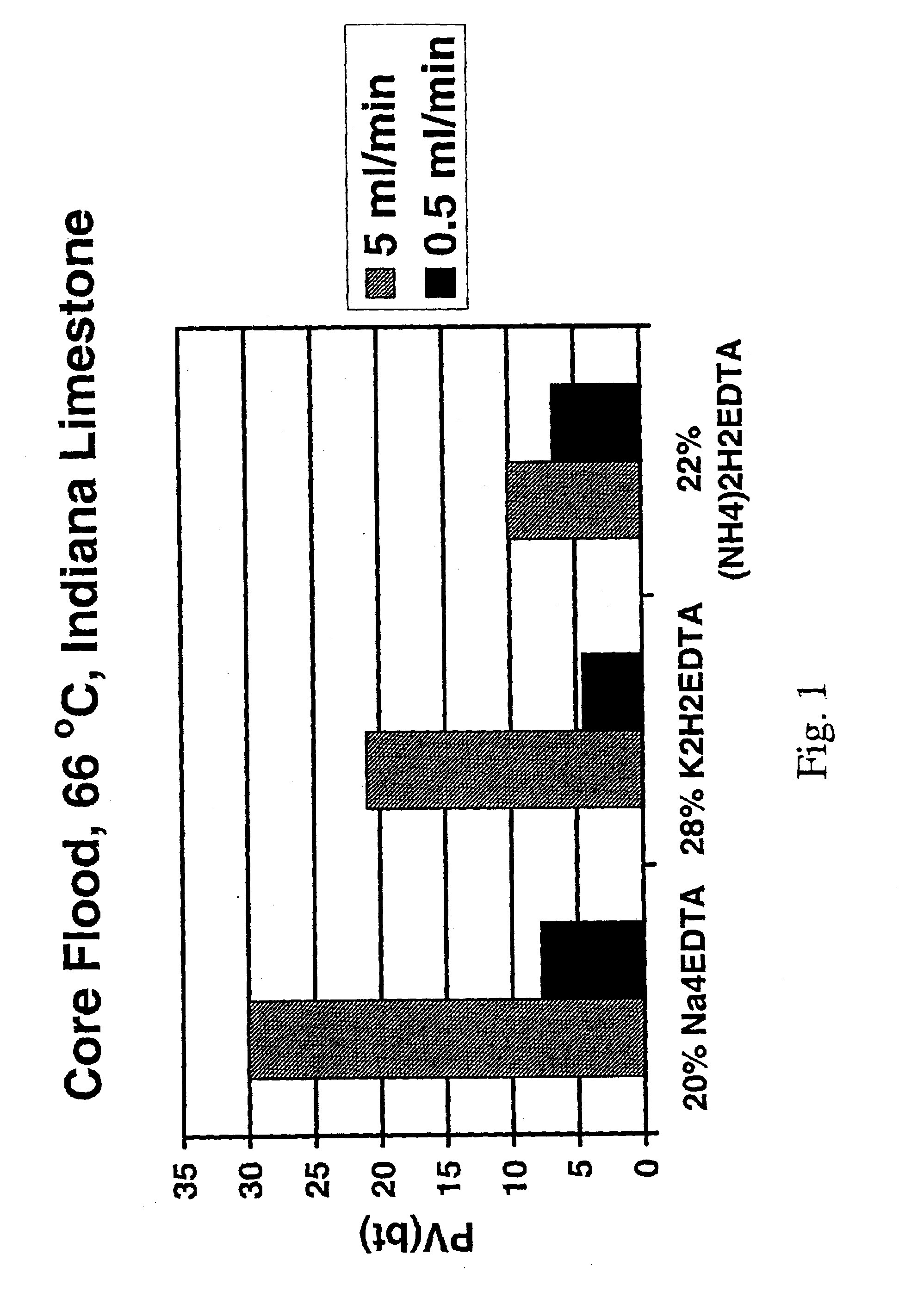

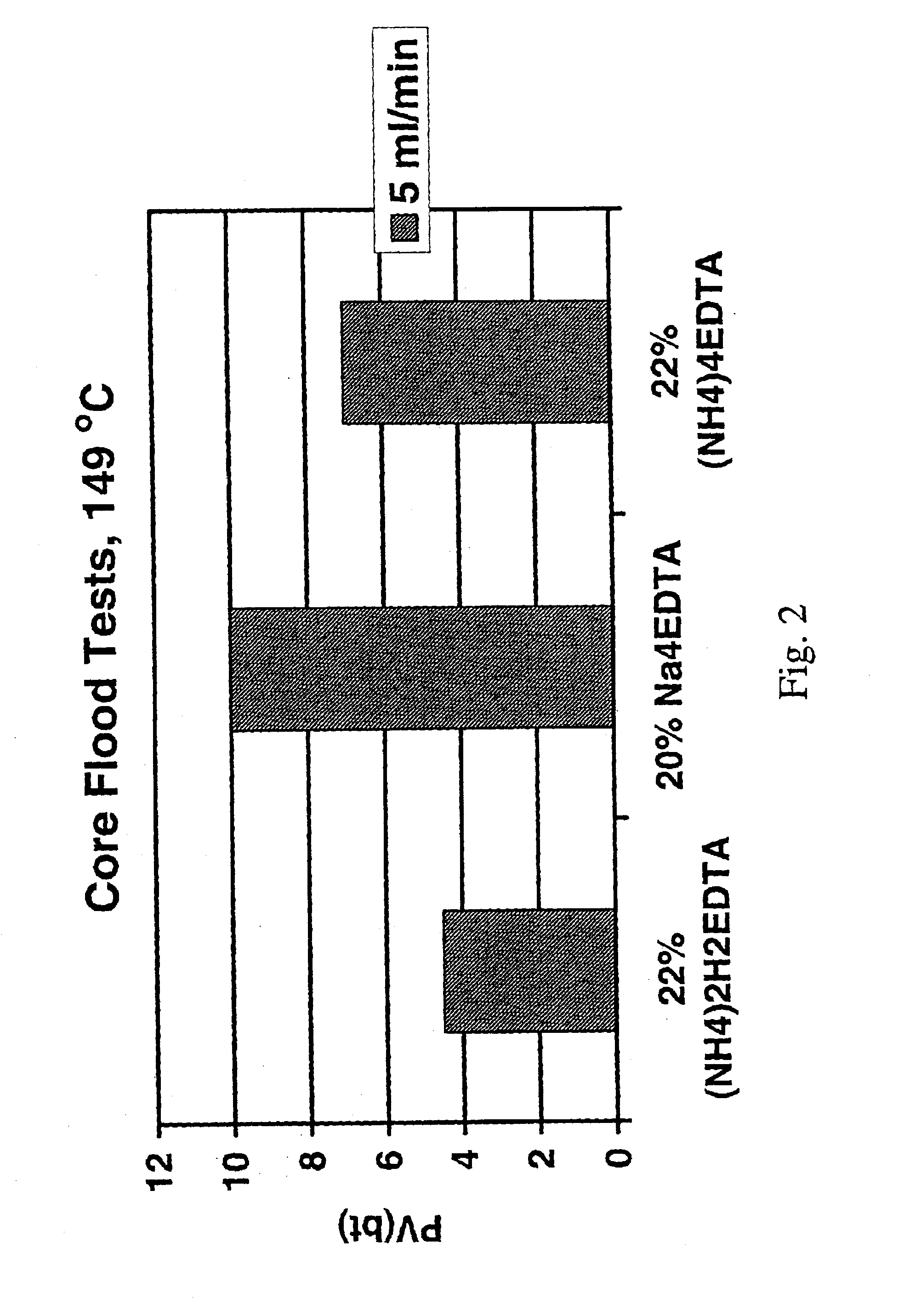

Method for treating a subterranean formation

InactiveUS6911418B2Improve breathabilityMinimized volumeOther chemical processesCleaning apparatusFormation matrixCarboxylic acid anion

A method for increasing the permeability of a subterranean formation is disclosed in which an amount of an aqueous mixture, sufficient to increase the permeability of the formation, comprising specified aminopolycarboxylic anionic species, and specified cationic species, is injected into the formation matrix.

Owner:SCHLUMBERGER TECH CORP

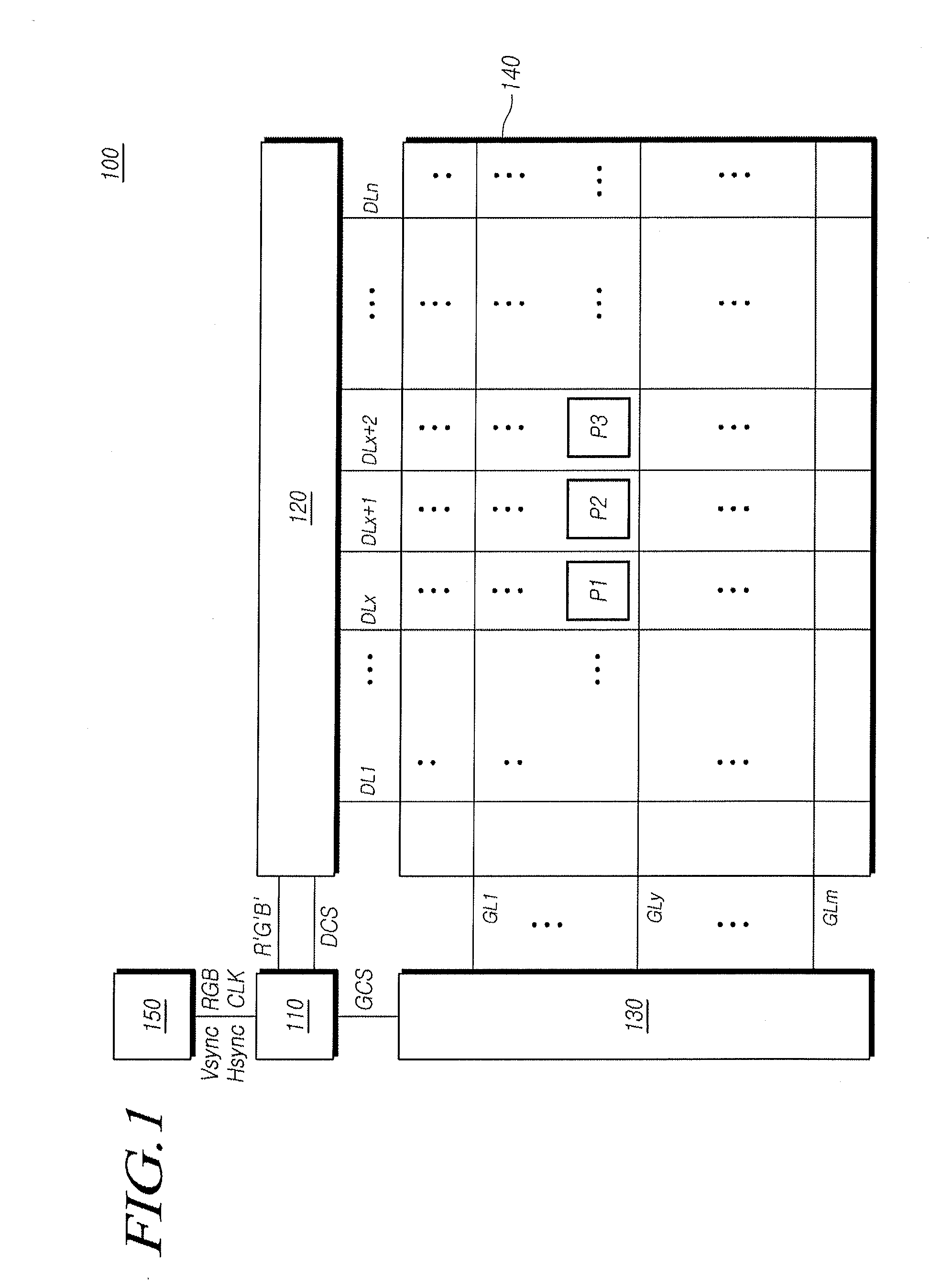

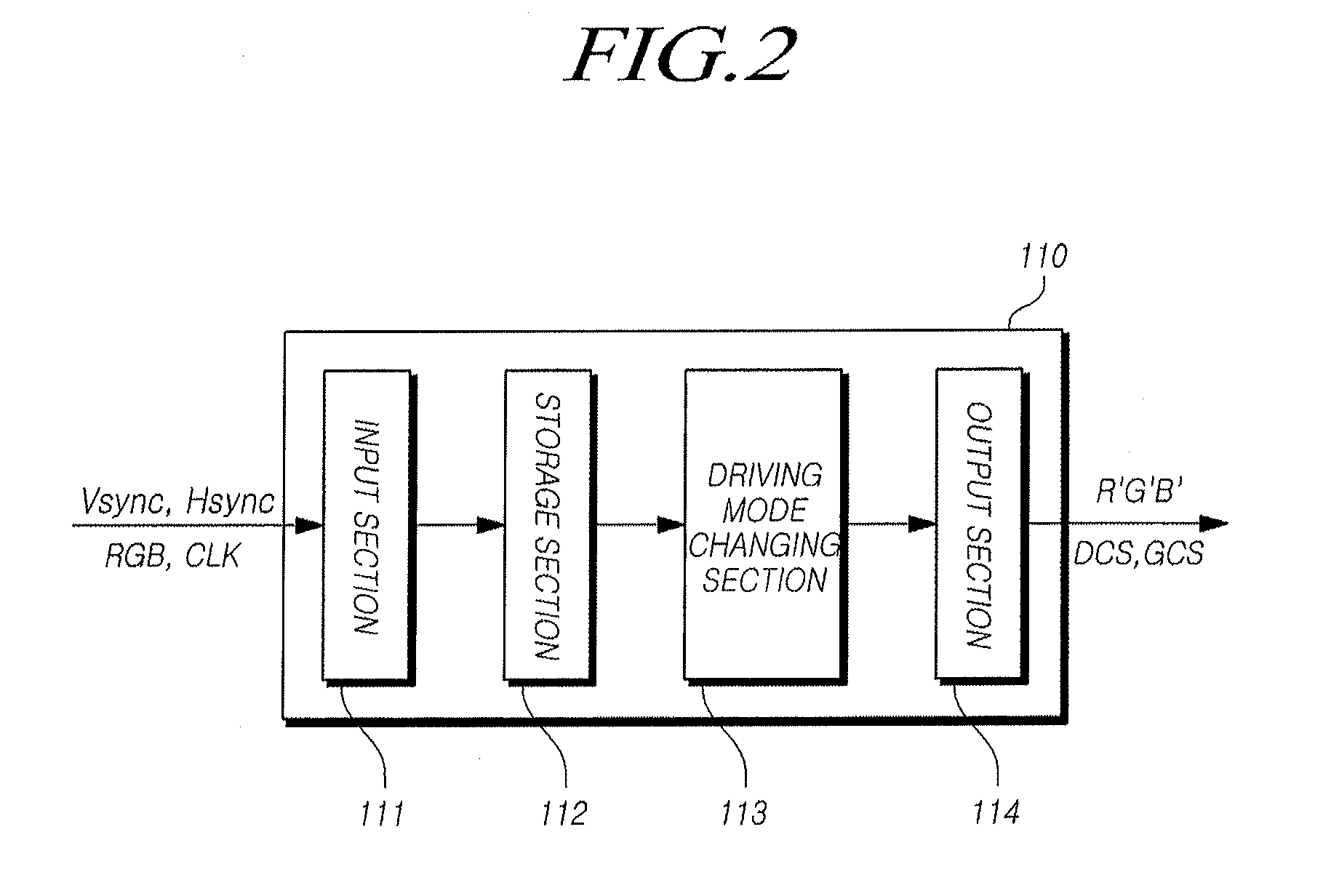

Display device and method of driving the same

ActiveUS20150145901A1Minimize power consumptionCathode-ray tube indicatorsInput/output processes for data processingFormation matrixDisplay device

A display device and a method of driving the same. The display device includes a display panel on which a plurality of data lines and a plurality of gate lines intersect each other to form a matrix, with a number of pixels being defined at intersections of the plurality of data lines and the plurality of gate lines. A data driver is connected to the plurality of data lines. A gate driver is connected to the plurality of gate lines. A timing controller controls the display panel to operate in a driving mode that changes depending on image signals.

Owner:LG DISPLAY CO LTD

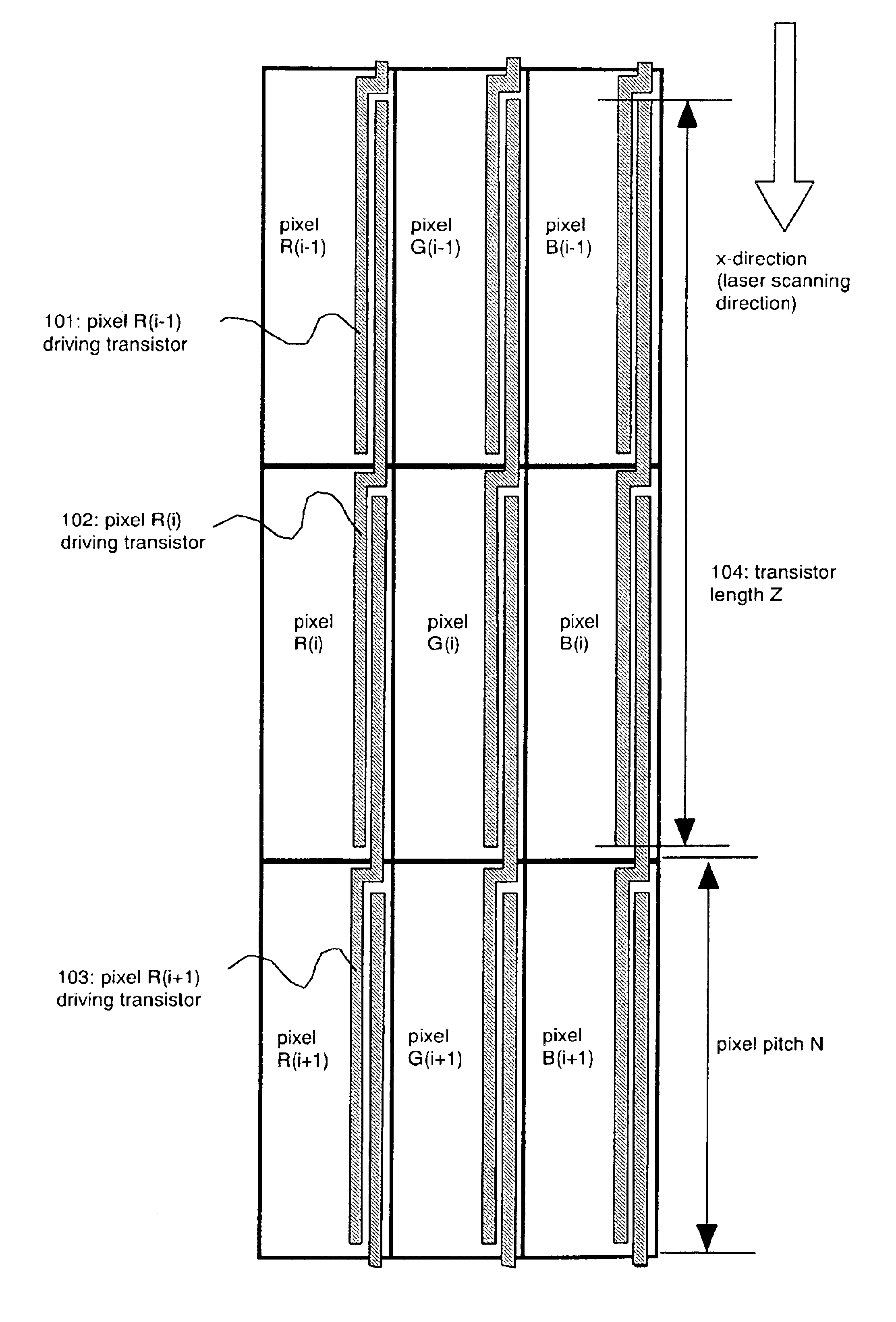

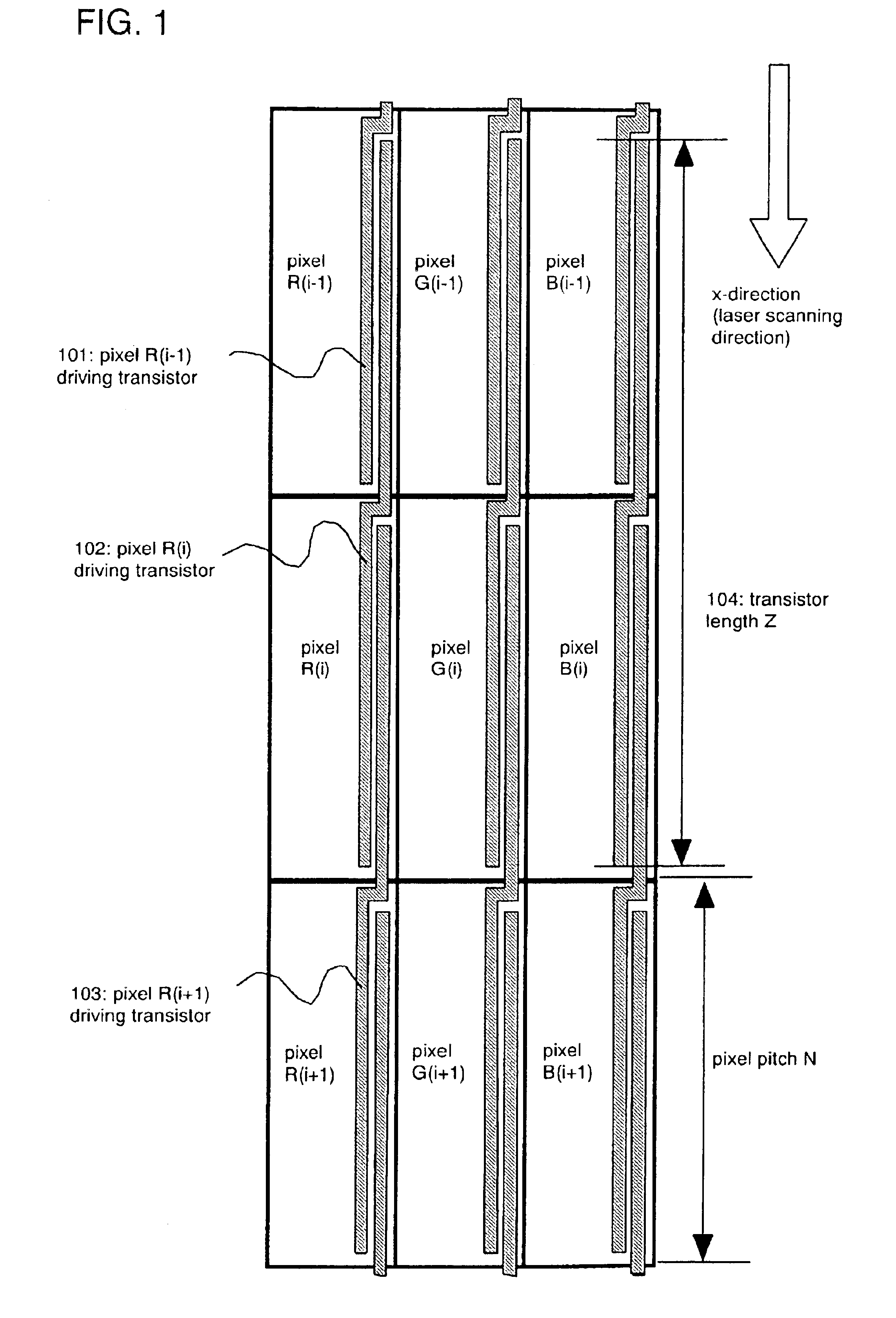

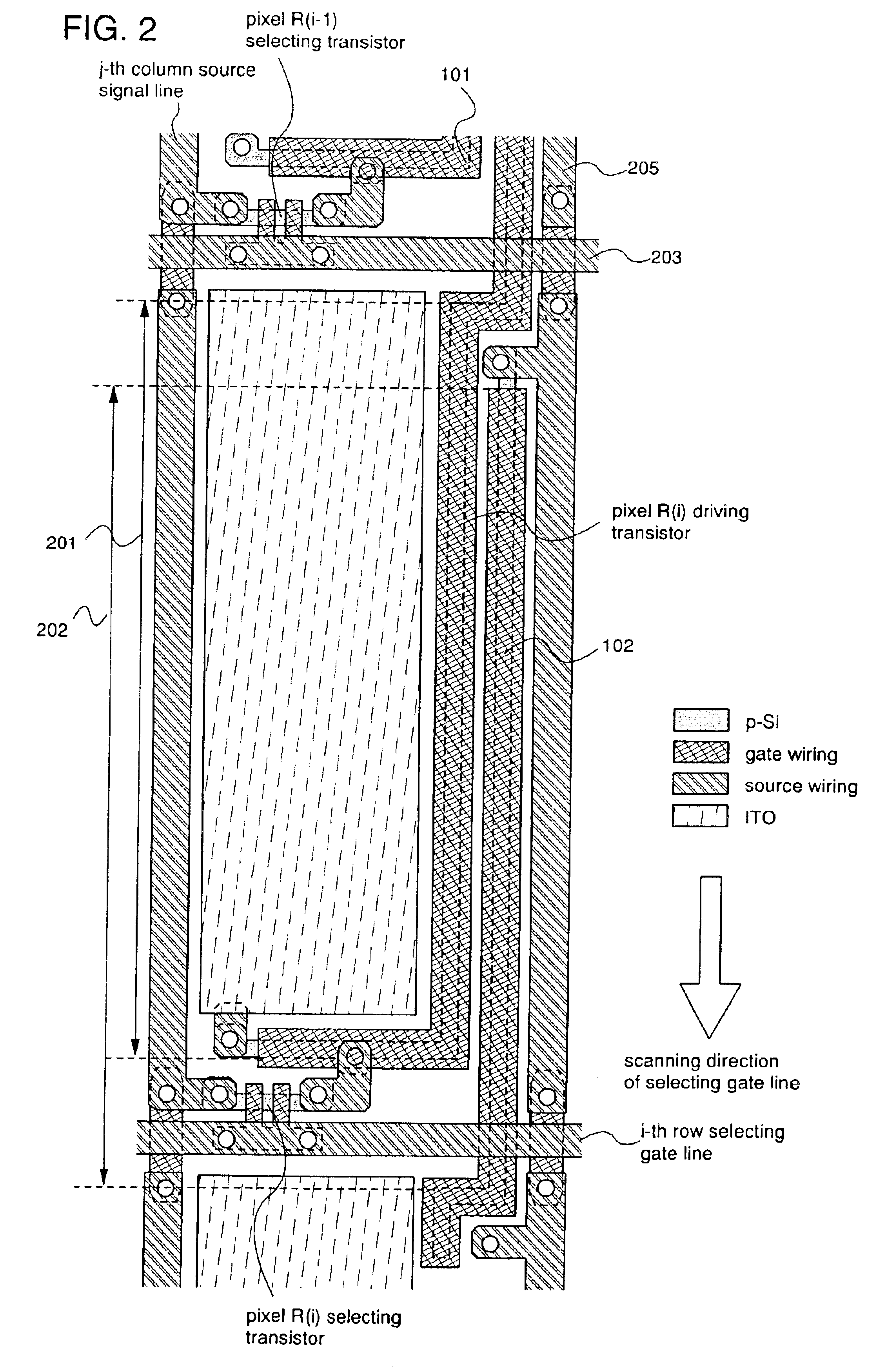

Semiconductor device and method of manufacturing the same

InactiveUS6930328B2Reduce the impact of volatilityLess laser fringeTransistorSolid-state devicesFormation matrixOptoelectronics

To obtain a semiconductor device and a method of manufacturing the same which can reduce influence of fluctuation in characteristic among transistors due to fluctuation in laser light irradiation number and laser light intensity on a semiconductor. There is provided a semiconductor device with plural pixels having transistors forming a matrix pattern, in which: the transistors have semiconductors crystallized by laser light irradiation; the semiconductors stretch over at least two pixels; the length of each of the semiconductors is longer than the pixel pitch of the pixels; and when the scan pitch of the laser light is given as M and the pixel pitch of the pixels is given as N, the semiconductors are irradiated with the laser light N / M times or more.

Owner:SEMICON ENERGY LAB CO LTD