System for unified configuration and management of FPGA chip in equipment

An in-device and chip technology, which is applied in the system field of unified configuration and management of FPGA chips in the device, can solve problems such as low configuration efficiency, and achieve the effect of improving efficiency and improving configuration efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

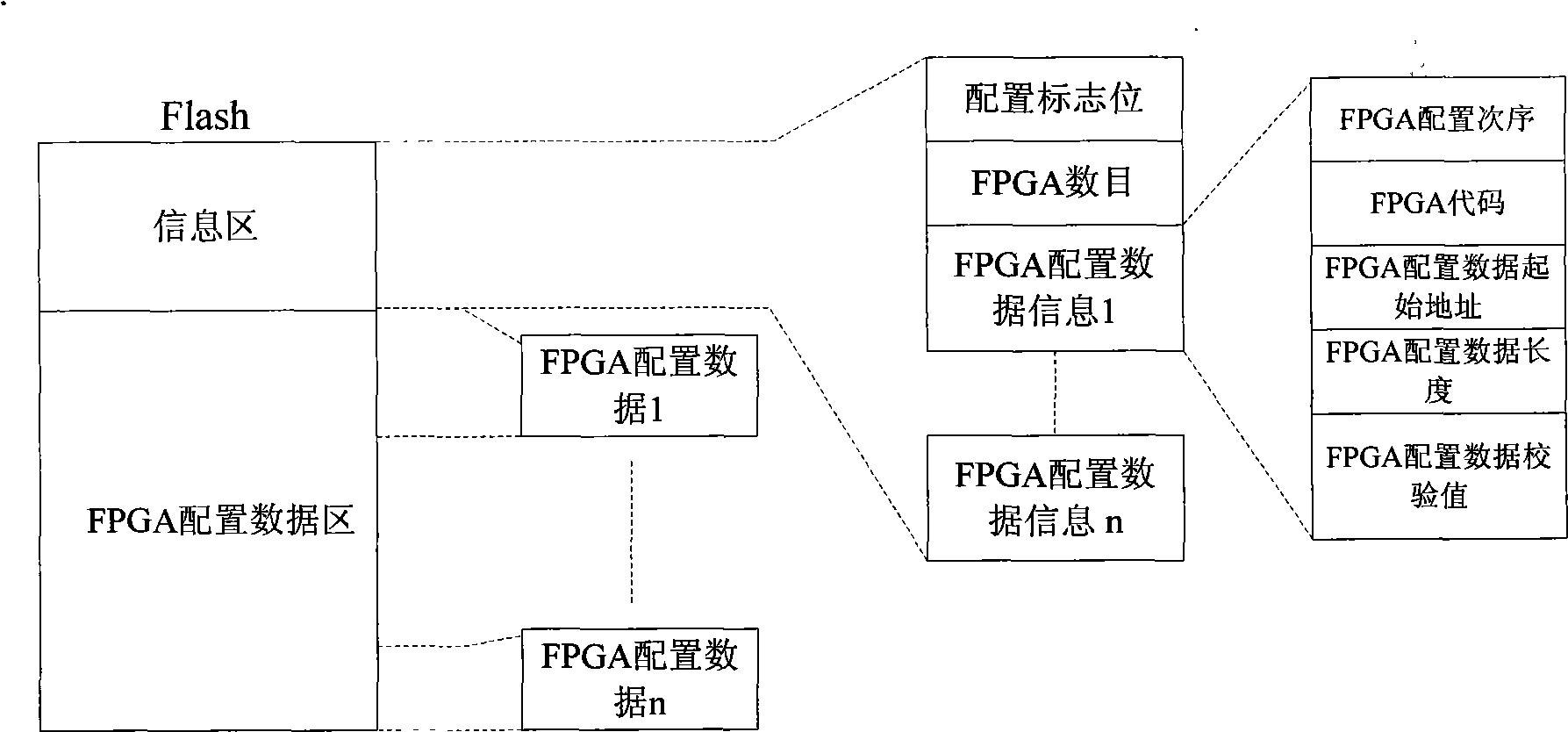

[0038] Flash

[0039] Such as figure 2As shown, the Flash is used to store configuration information of the FPGA chip and configuration data of the FPGA chip. Therefore, we divide the storage space of the Flash into two areas, one of which is used to store the configuration information of the FPGA chip, called the information area; the other area is used to store the configuration data of the FPGA chip, called the data area.

[0040] The beginning part of the information area stores the configuration flag bit, which is used to indicate whether the CPLD needs to wait for the command of the microprocessor before starting to configure the FPGA chip. If the configuration flag bit=0xAA, then the CPLD need not wait for the configuration command of the microprocessor, as long as it obtains the bus control right of the Flash, the configuration of the FPGA chip can be started; if the configuration flag bit=0x55, the CPLD must wait for the configuration command of the microprocessor ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More