Patents

Literature

96 results about "Subsystem design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Guidelines: Design Subsystem. A model element which has the semantics of a package (it can contain other model elements) and a class (it has behavior). The behavior of the subsystem is provided by classes or other subsystems it contains. A subsystem realizes one or more interfaces, which define the behavior it can perform.

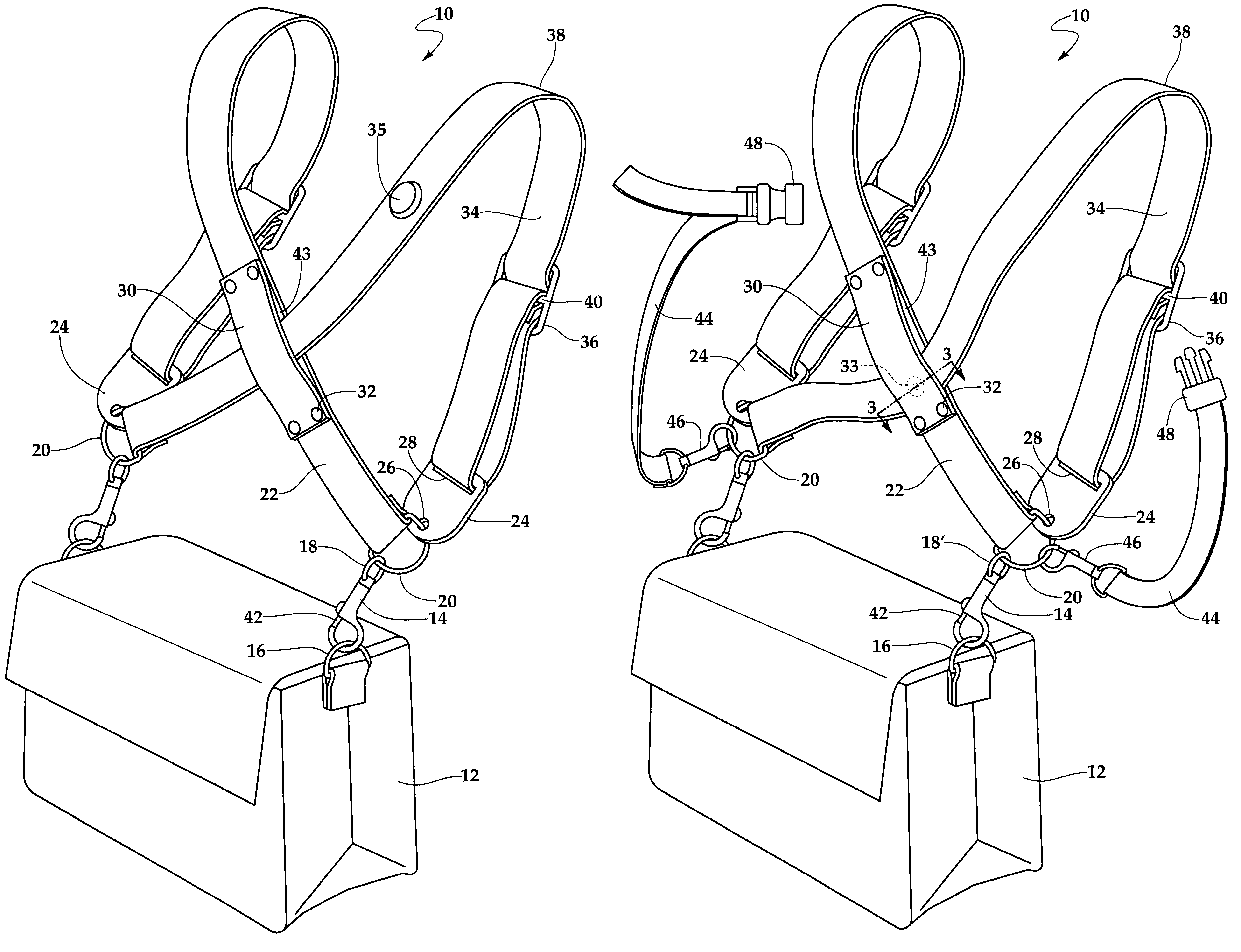

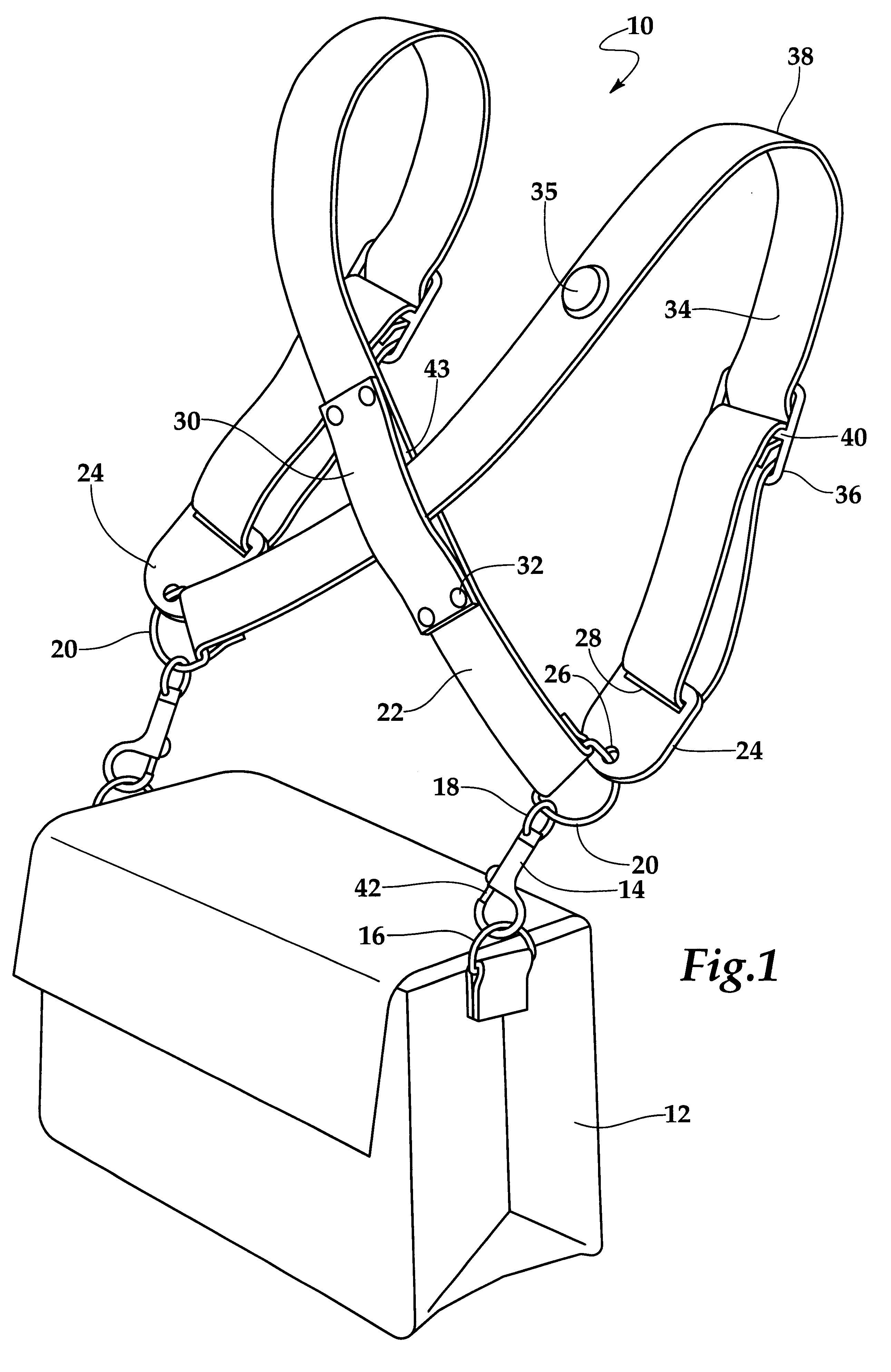

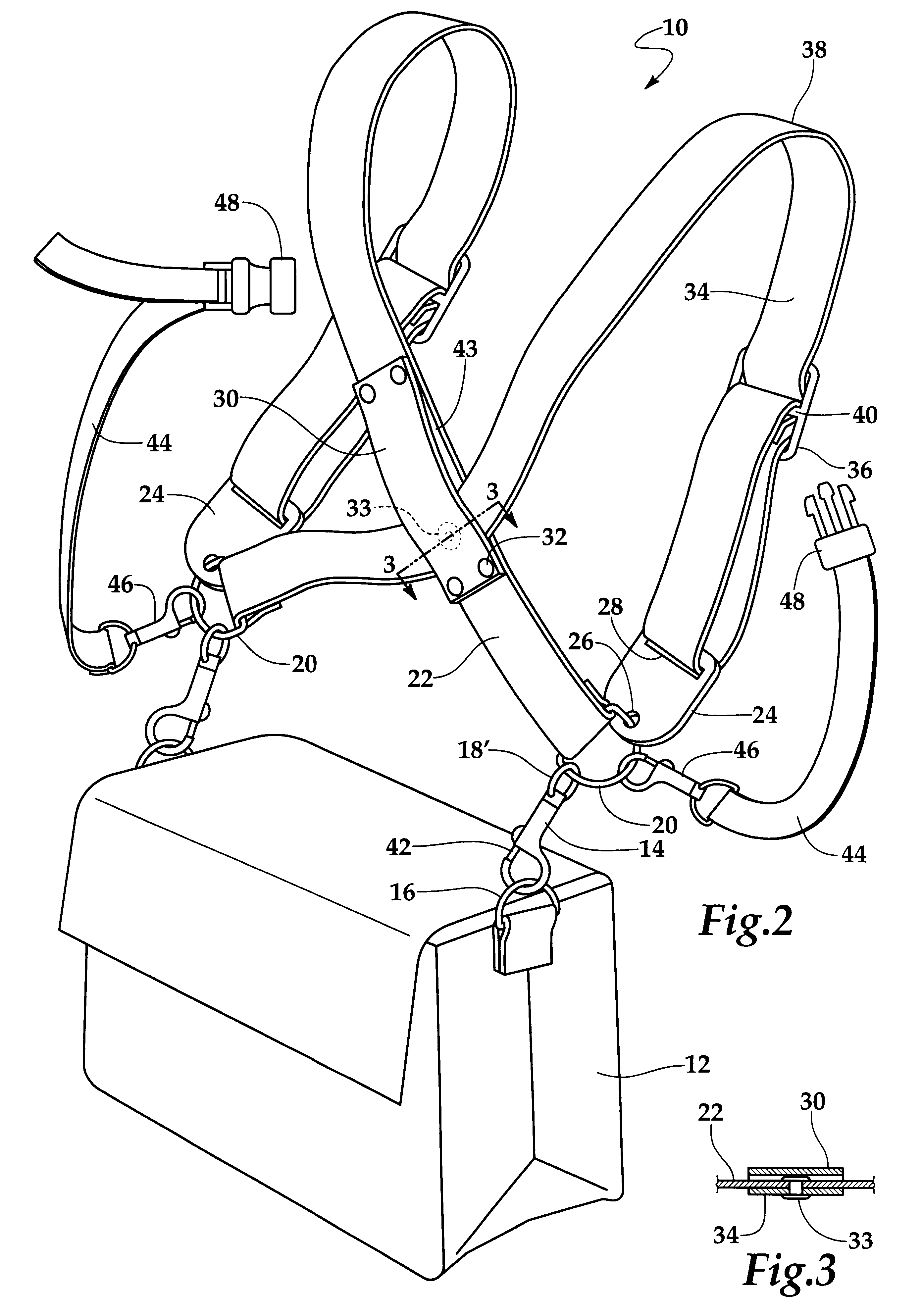

Dual strap system for conversion of bags to backpacks

The present invention discloses a dual strap system used for connection to a utility bag, such as a computer bag, by which the bag can be converted into a backpack, In a first embodiment, the dual straps of the system cross each other by means of a rigid member disposed at the crossing point to provide a twist resistant arrangement and properly center the present invention on the back of the user. One strap has a stop located thereon which helps position the straps with respect to the rigid member when the strap is off the bag and maintain the integrity of the device during the time the device is not installed on the bag. An attachment clip system is also provided which automatically positions the straps properly for use when the right hand grab technique is used to shoulder the device. Further, the clip system is designed to keep the straps from tangling when the device is off the bag. In a second embodiment, a swivel is provided for connection of the two straps which allows the rigid member to act as a cantilever-like member which helps provide a proper opening in the straps for shouldering the present invention.

Owner:JOHNSON JUSTIN

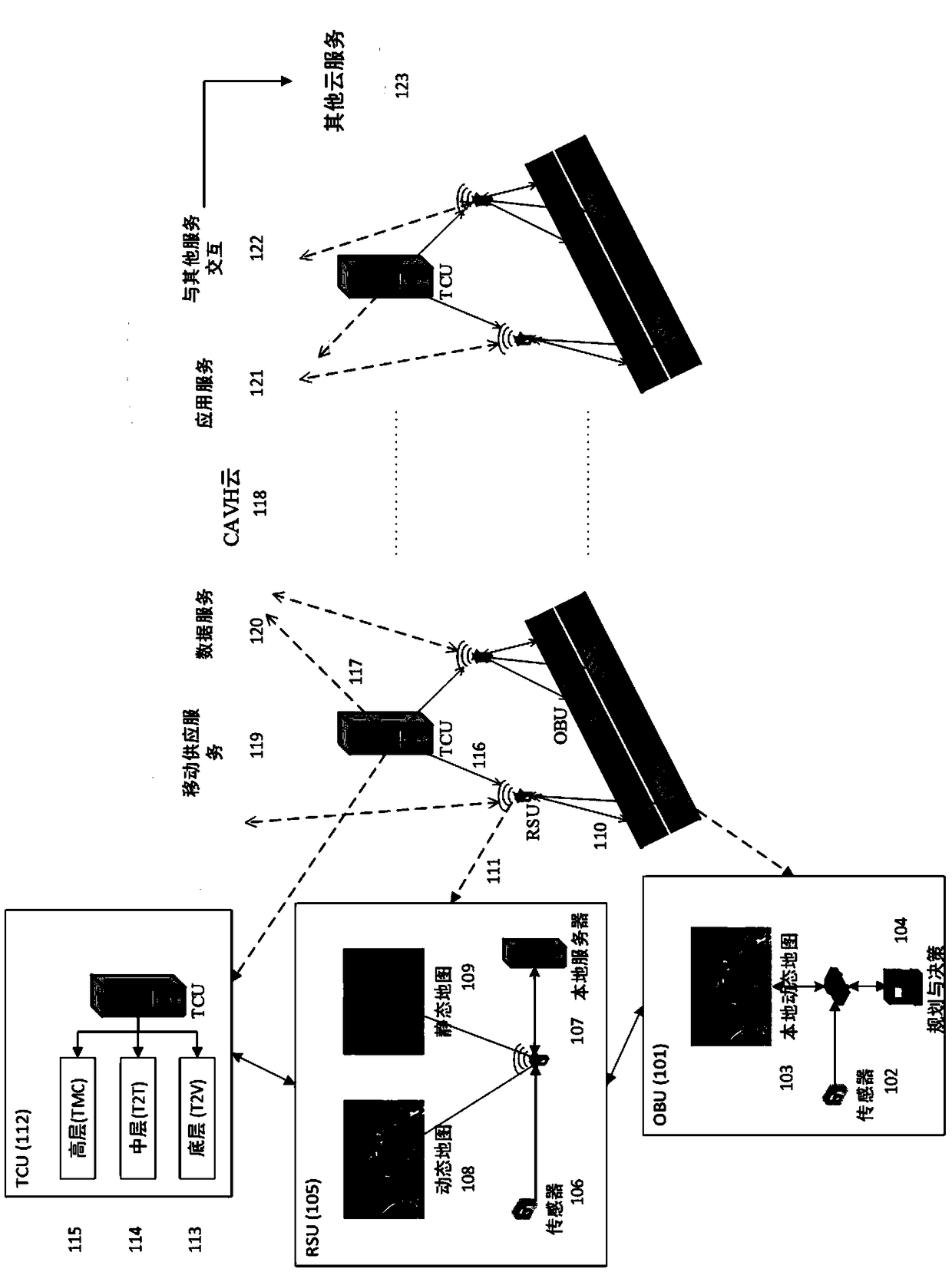

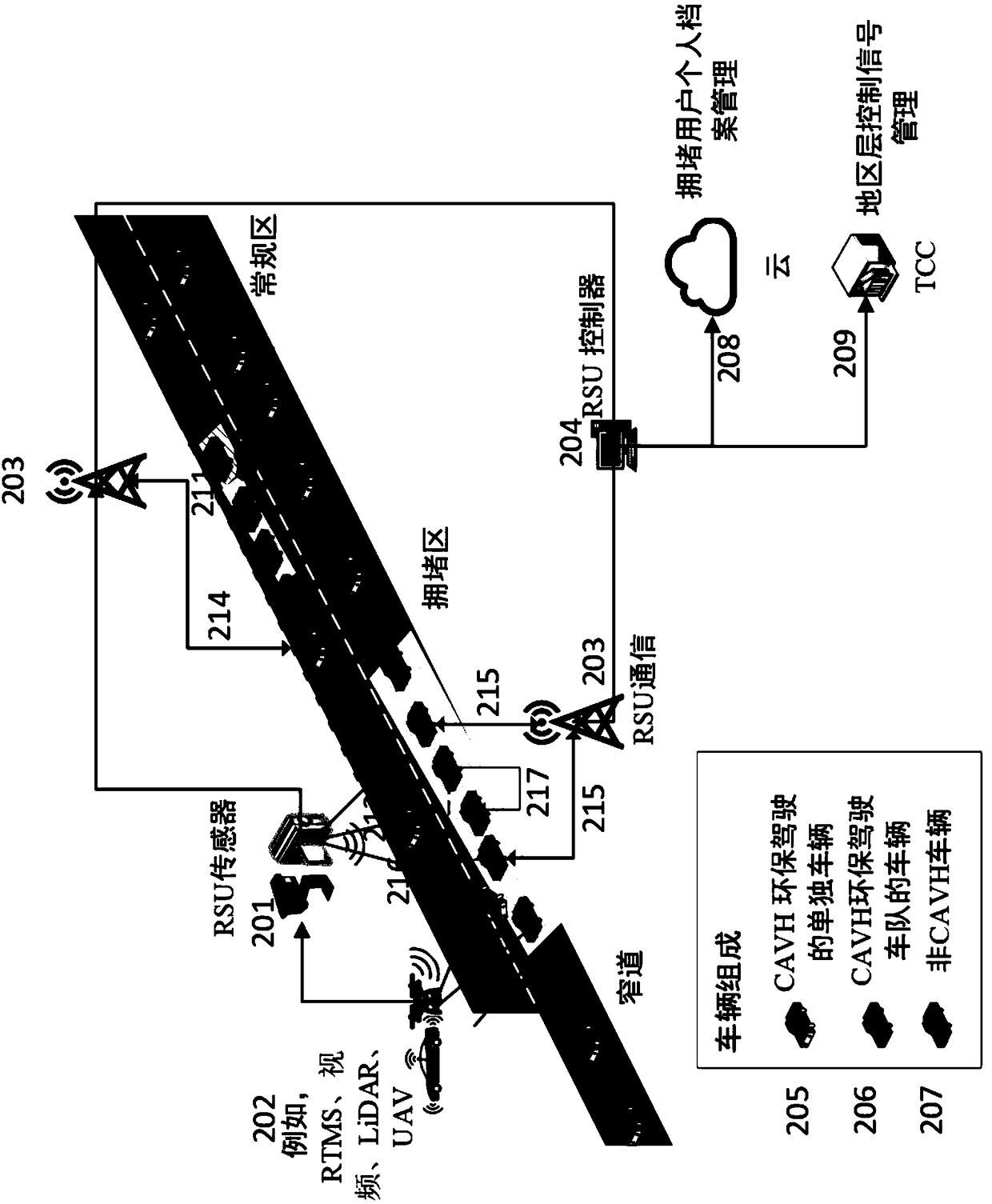

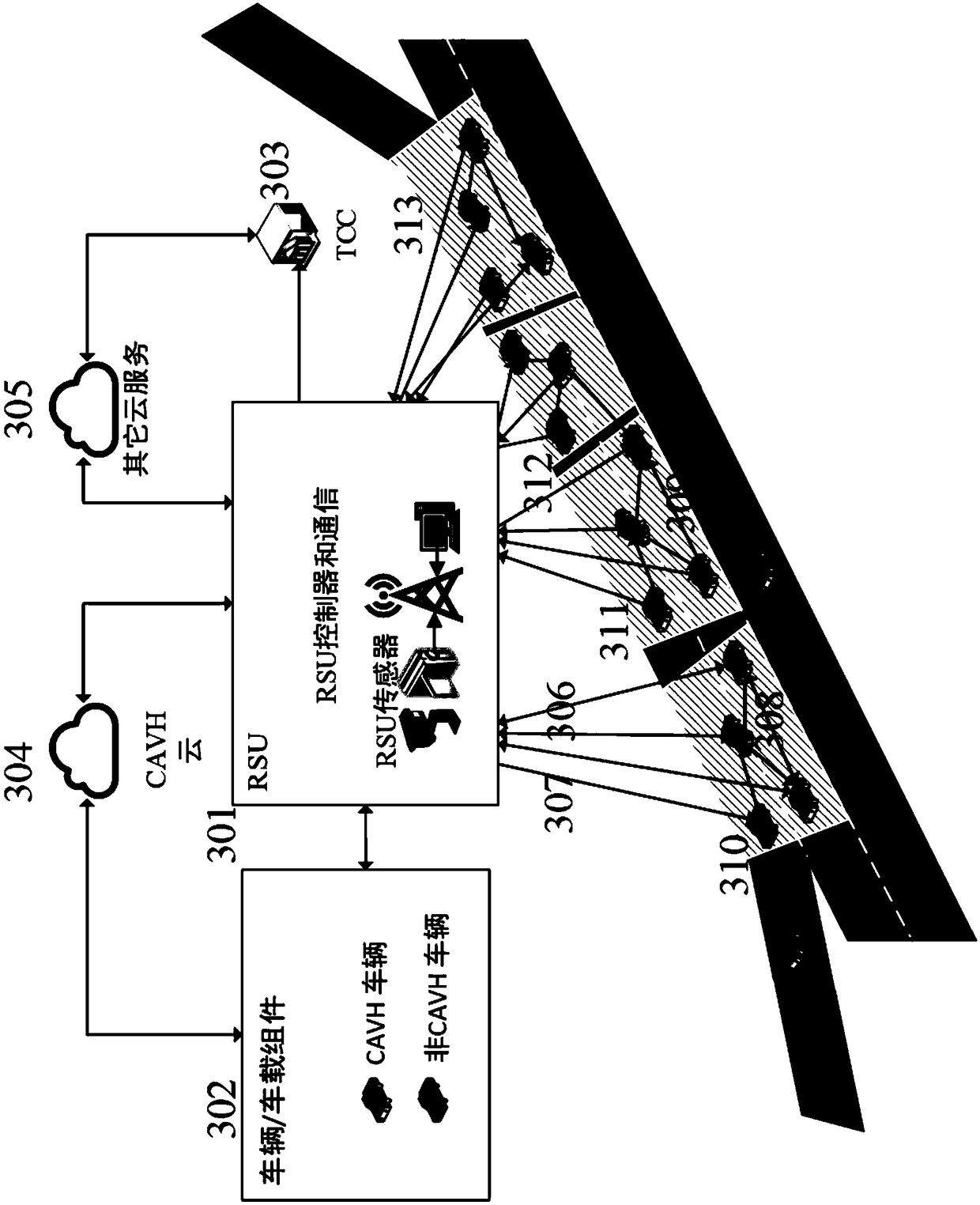

Intelligent networked transportation system for overall road network

The invention provides an intelligent networked transportation system for an overall road network. The intelligent networked transportation system comprises a sensing, communication and control modulefor managing the entire transportation system connected by road segments and nodes. When intelligent networked vehicles travel in a transportation network, they will route different types of road facilities such as basic road sections, highways, main roads, traffic bottleneck sections, interlaced and confluence sections, intersections, the start or last one kilometer if the road, parking areas, bridges, tunnels, multi-modal hubs, etc. These different sections and nodes in a transportation network have significant differences in geometric design and facility characteristics. The invention provides a specific intelligent networked system subsystem design to adapt to different types of road characteristics and achieve complete door-to-door travel.

Owner:上海丰豹商务咨询有限公司

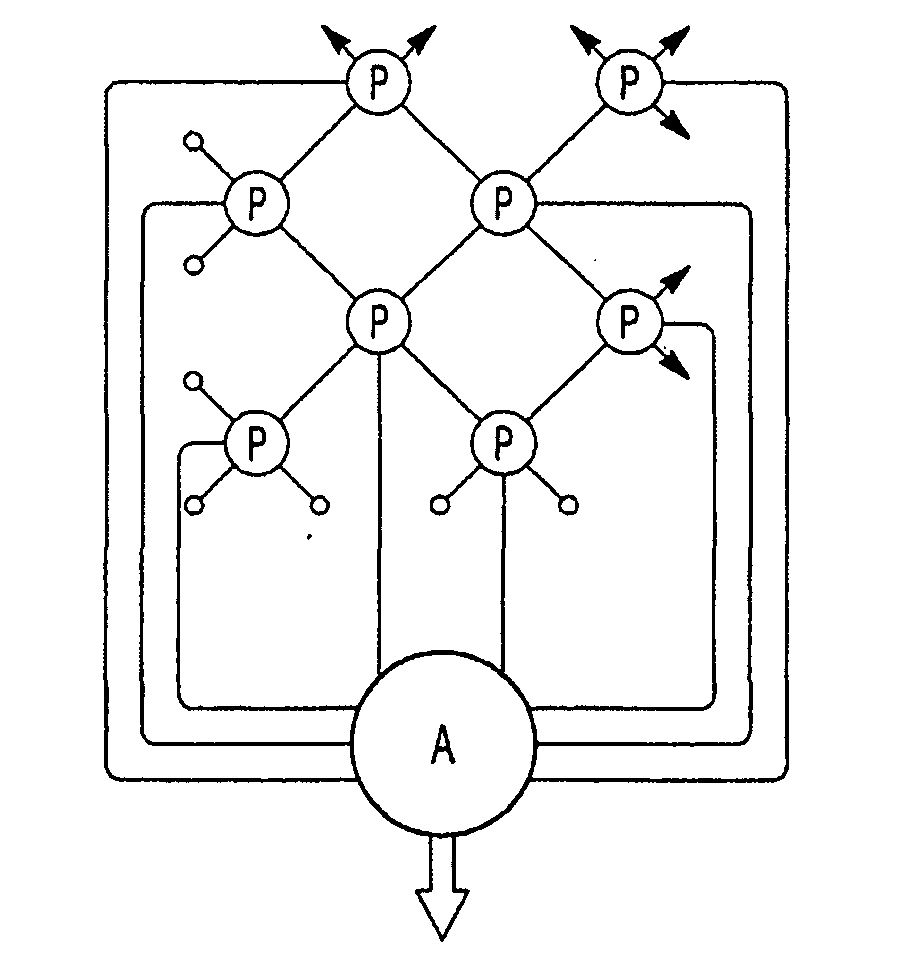

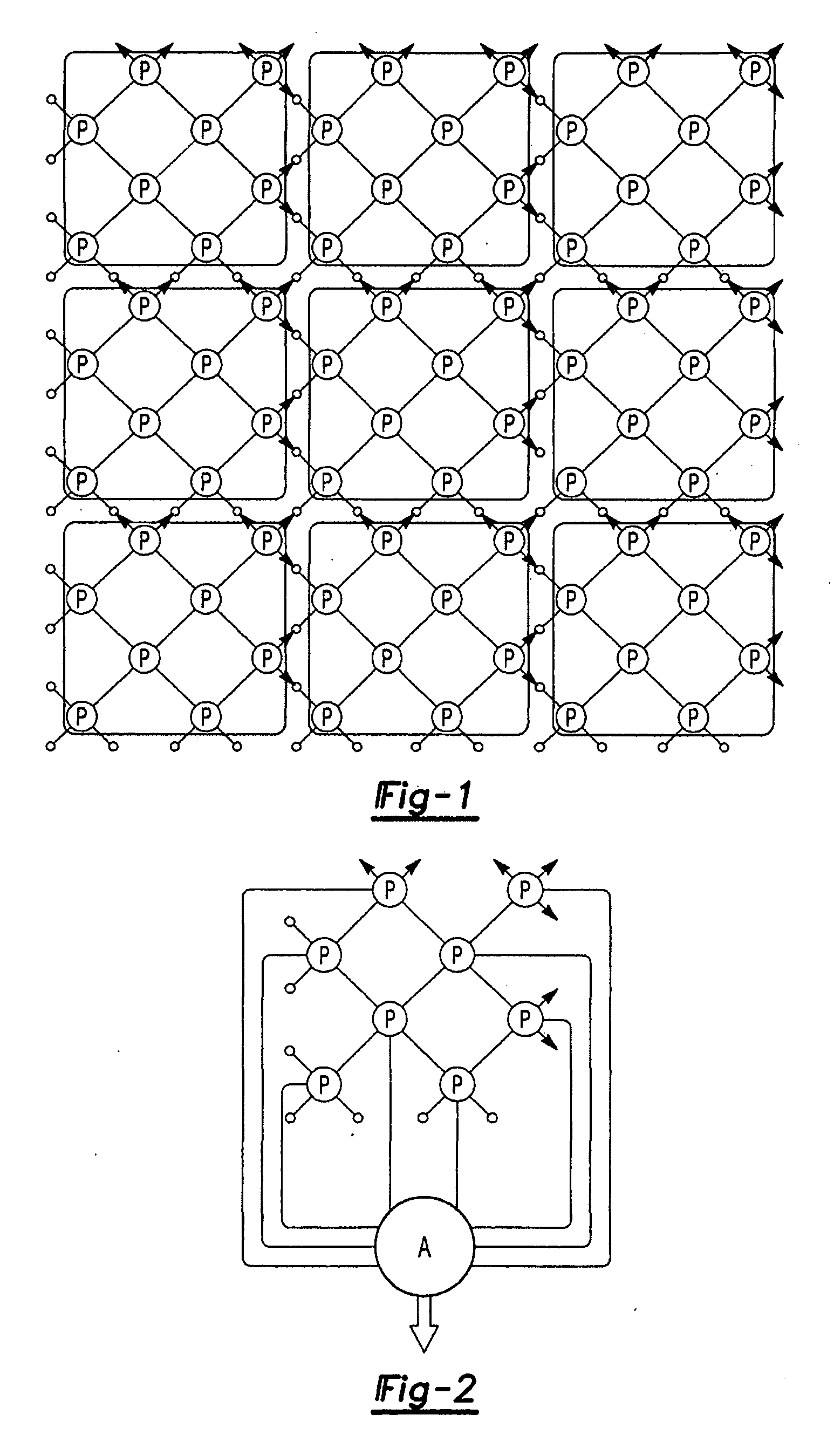

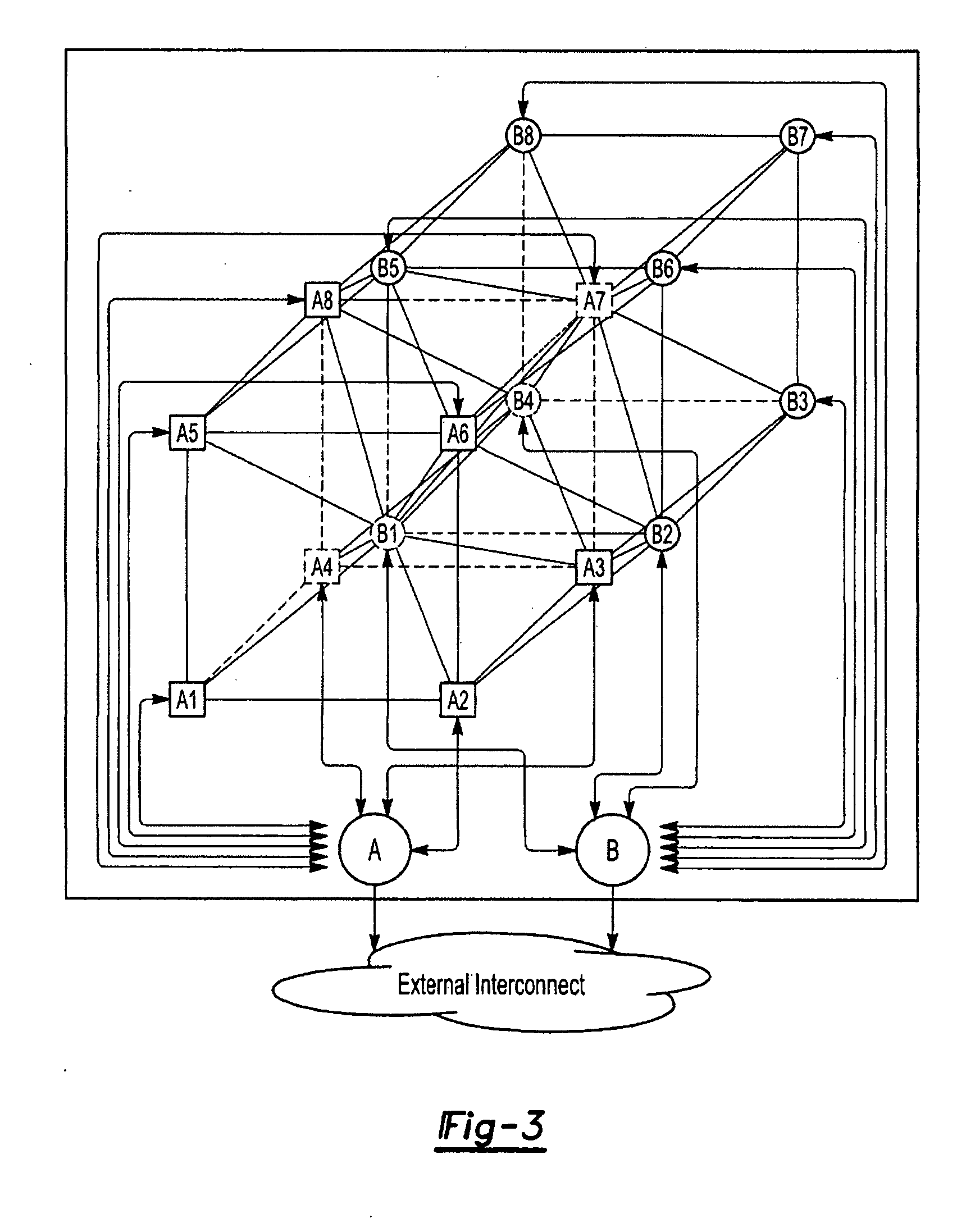

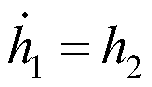

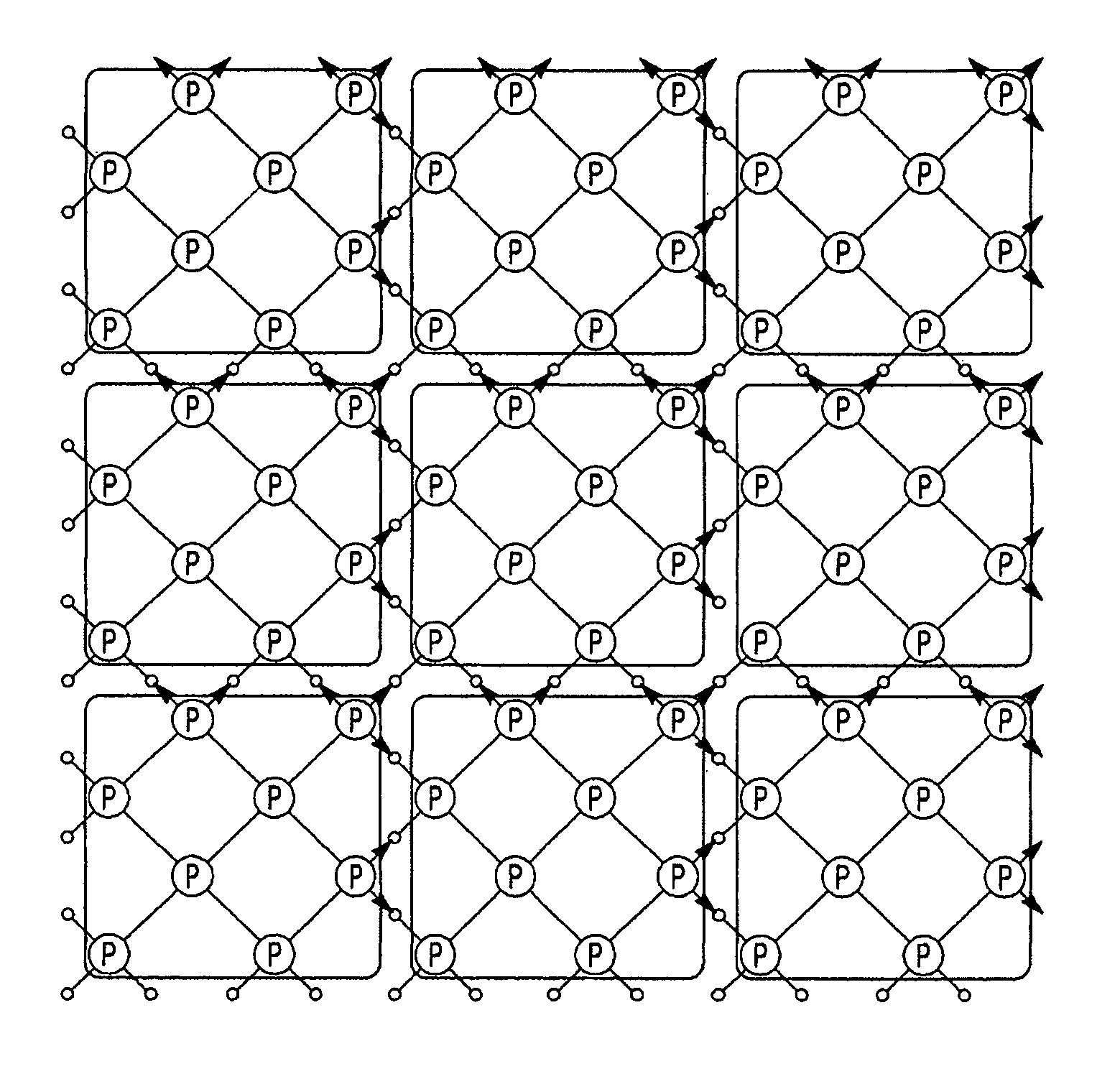

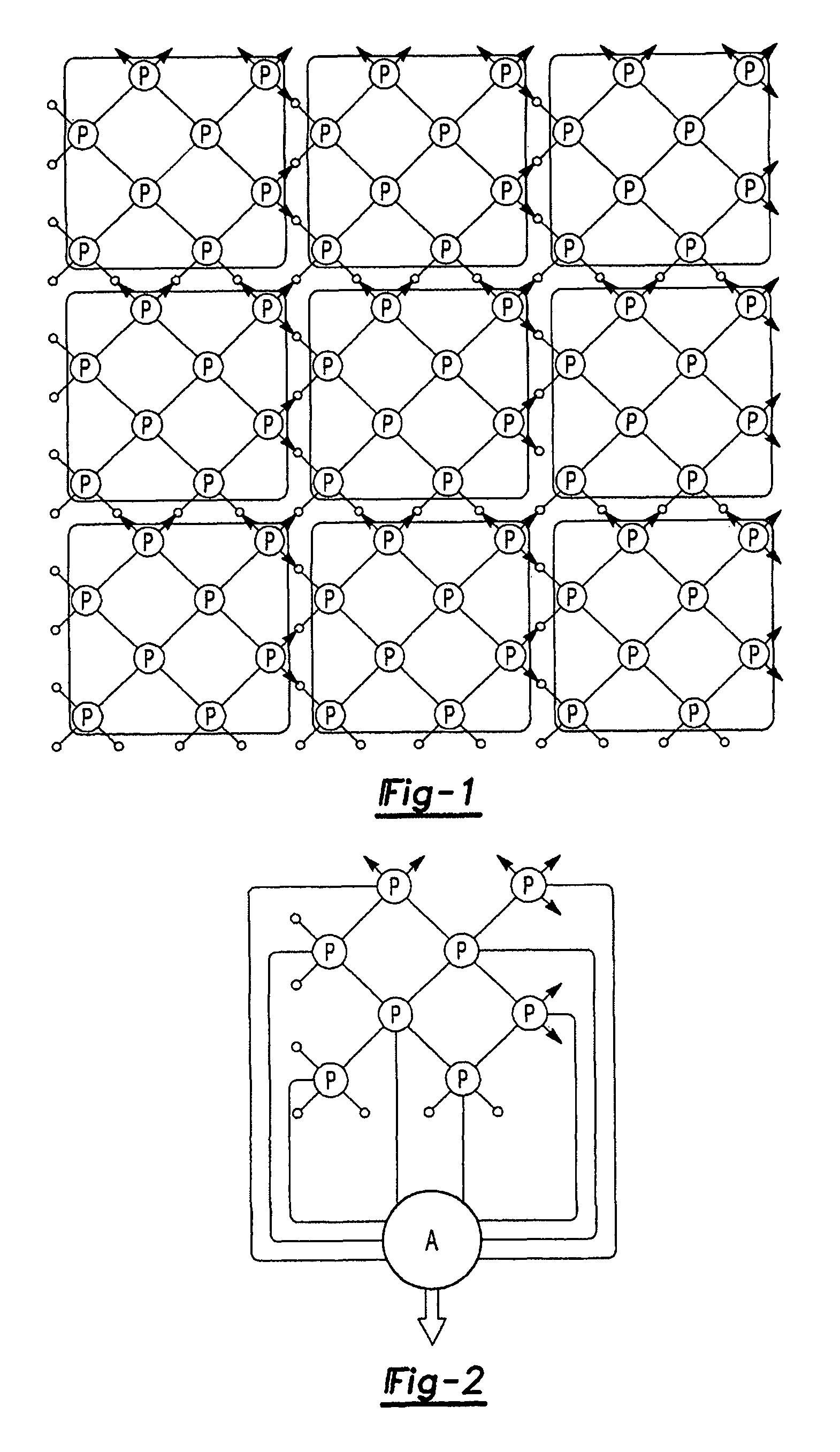

Ultra-scalable supercomputer based on mpu architecture

InactiveUS20090094436A1High-performance and sustained computing resourceHigh-performance and sustained computing resourcesProgram control using stored programsData switching by path configurationSupercomputerTraffic capacity

The invention provides an ultra-scalable supercomputer based on MPU architecture in achieving the well-balanced performance of hundreds of TFLOPS or PFLOPS range in applications. The supercomputer system design includes the interconnect topology and its corresponding routing strategies, the communication subsystem design and implementation, the software and hardware schematic implementations. The supercomputer comprises a plurality of processing nodes powering the parallel processing and Axon nodes connecting computing nodes while implementing the external interconnections. The interconnect topology can be based on MPU architecture and the communication routing logic as required by switching logics is implemented in the FPGA chips while some modular designs for accelerating particular traffic patterns from applications and meliorating the communication overhead are able to be deployed as well.

Owner:SHANGHAI REDNEURONS

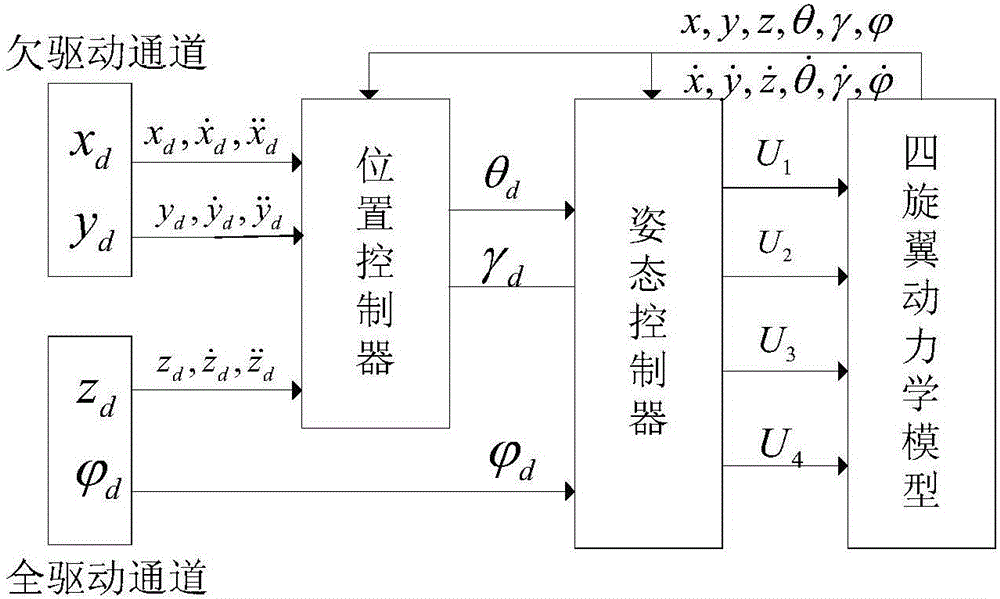

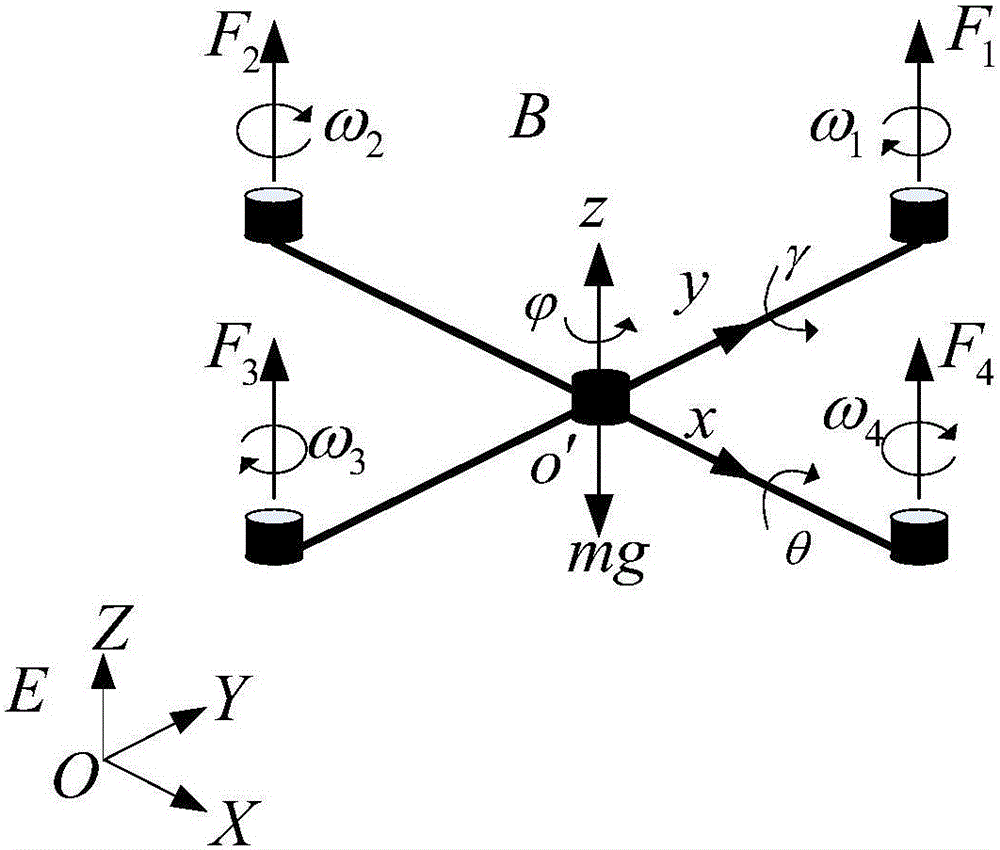

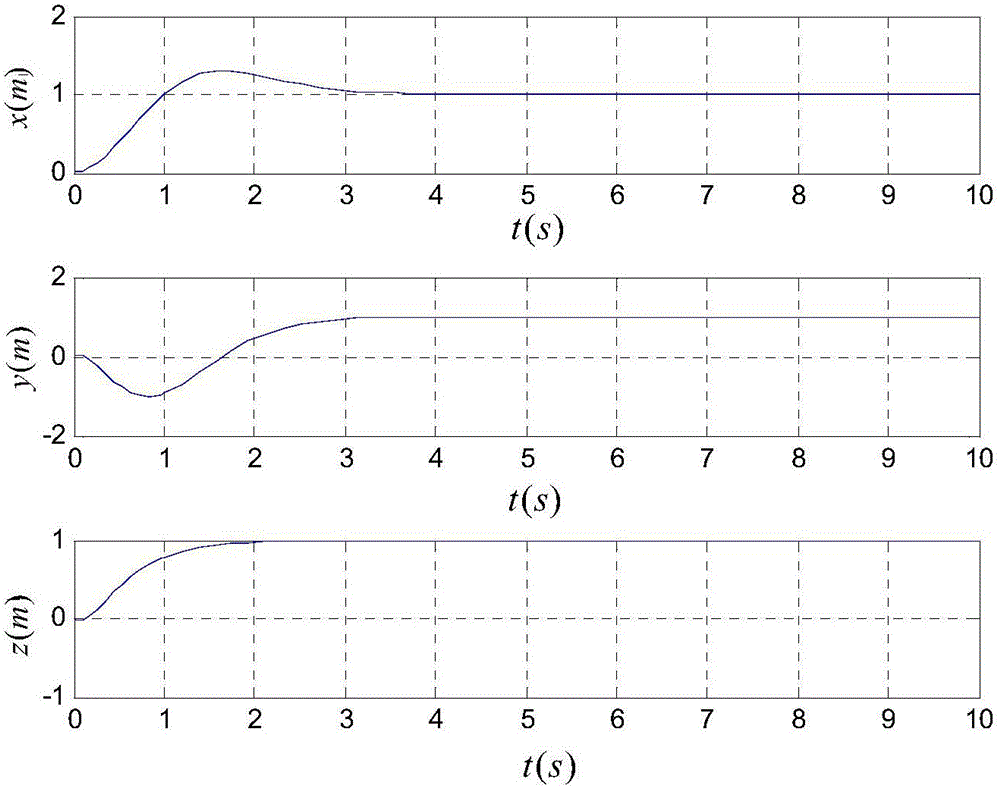

Four-rotor aircraft sliding mode variable structure control method based on inversion method

InactiveCN105759832AStrong targetingStrong decouplingAttitude controlPosition/course control in three dimensionsSubsystem designRotary wing

The invention discloses a four-rotor aircraft sliding mode variable structure control method based on an inversion method. The four-rotor aircraft sliding mode variable structure control method comprises the steps that firstly, a four-rotor aircraft kinetic model is analyzed and simplified and is systematically decomposed into an all-wheel-drive subsystem and an under-actuation subsystem; further, the inversion control method is utilized to derive a sliding mode control face with a sliding mode variable structure control theory as a basis, control laws are designed for the two subsystems, and the system stability is verified through a Lyapunov stability theory; finally, a controller of a four-rotor aircraft is designed out. The four-rotor aircraft sliding mode variable structure control method is integrated with the inversion method, is used for controlling spot hover and trajectory tracking control of the aircraft, analyzes the dynamic nature and the stability of the aircraft, effectively improves the response speed and control accuracy of the four-rotor aircraft and improves anti-interference performance of a system.

Owner:WUHAN UNIV OF SCI & TECH

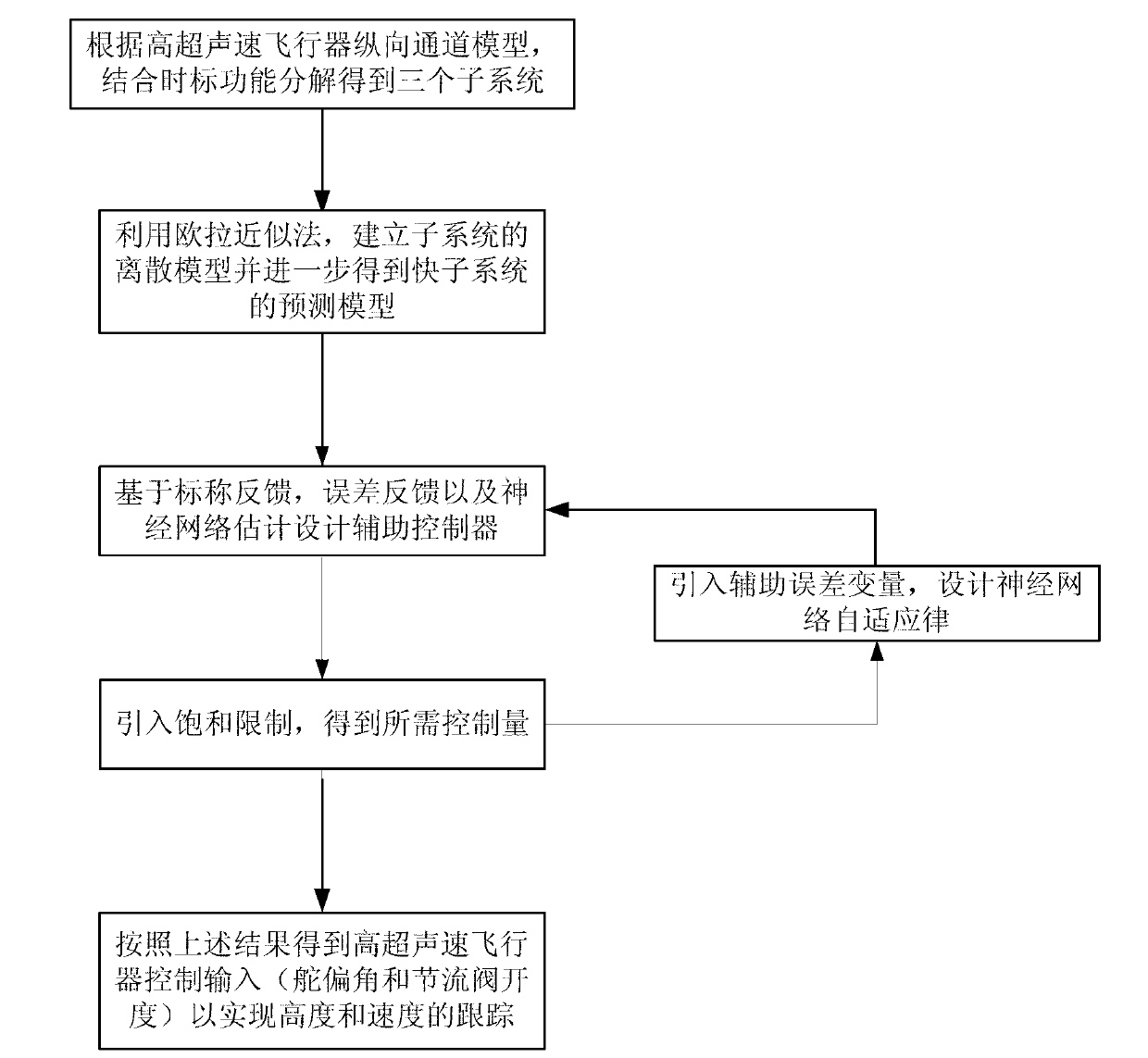

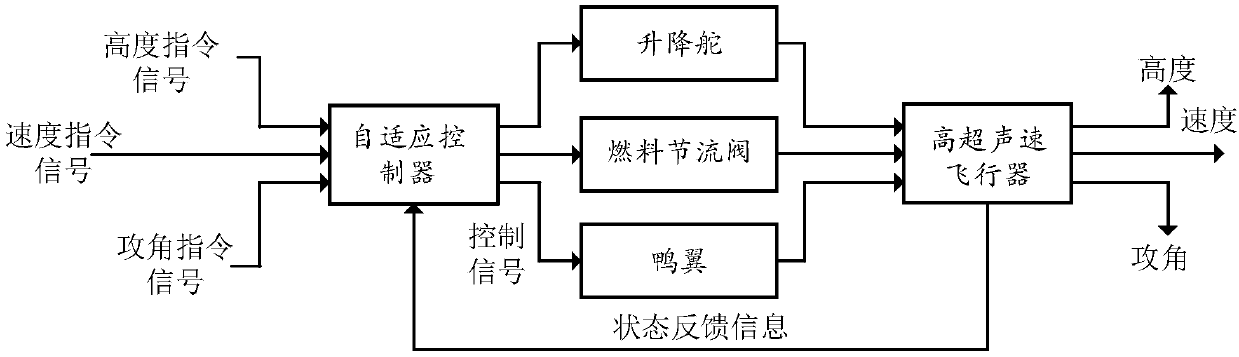

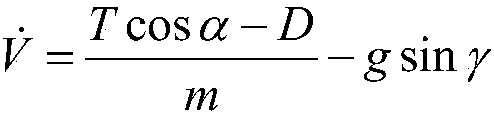

Time scale function decomposition based hypersonic aircraft actuator saturation control method

ActiveCN102880052ASimplify the number of variablesRealize the designVehicle position/course/altitude controlAdaptive controlDecompositionEulerian method

The invention discloses a time scale function decomposition based hypersonic aircraft actuator saturation control method. The method is used for solving the technical problem of difficulty in engineering realization under the existing hypersonic aircraft actuator saturation condition. The method includes: obtaining a high-speed slow variable subsystem, a speed slow variable subsystem and an attitude fast variable subsystem by time scale decomposition, and building a discrete form of an original system through an Eulerian method; regarding the height and the speed in a fast subsystem design process as constants so as to achieve model simplification; considering actuator saturation limitations, and importing auxiliary control variables to design throttling valve openness and the controlpiston deflexion angle; and designing an updating law of a neural network by importing an auxiliary error variable. The time scale function decomposition based hypersonic aircraft actuator saturation control method has the advantages that computer control characteristics are combined, a discrete model is built, the subsystems are designed according to time scale function decomposition, the actuator saturation condition is fully considered during controller design, and the method is suitable for engineering application.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

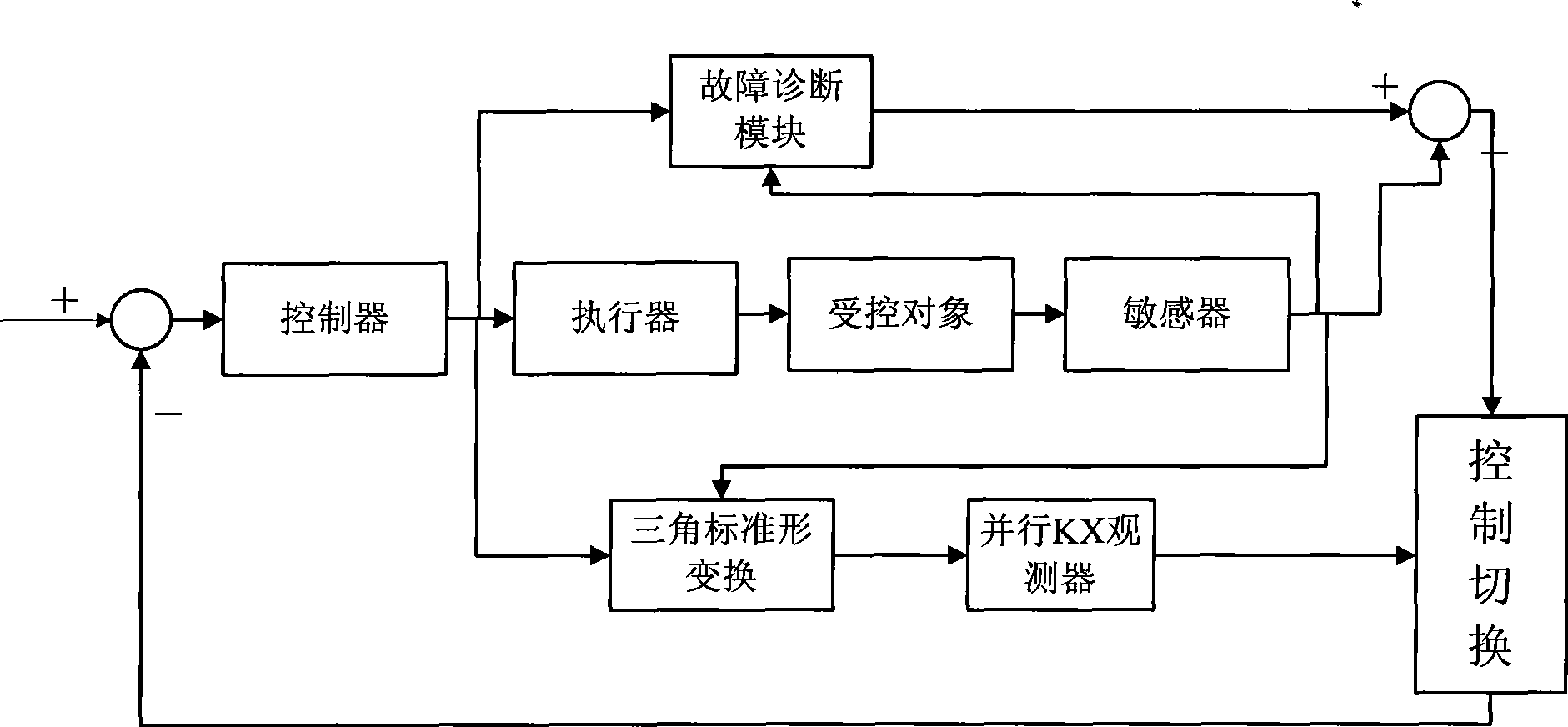

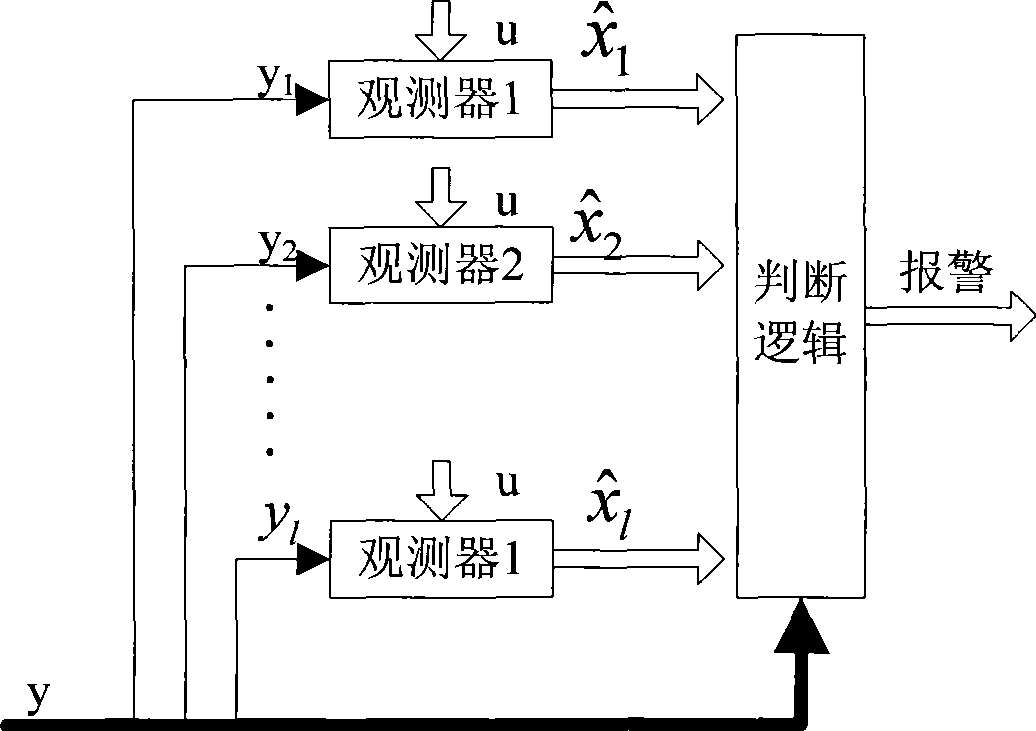

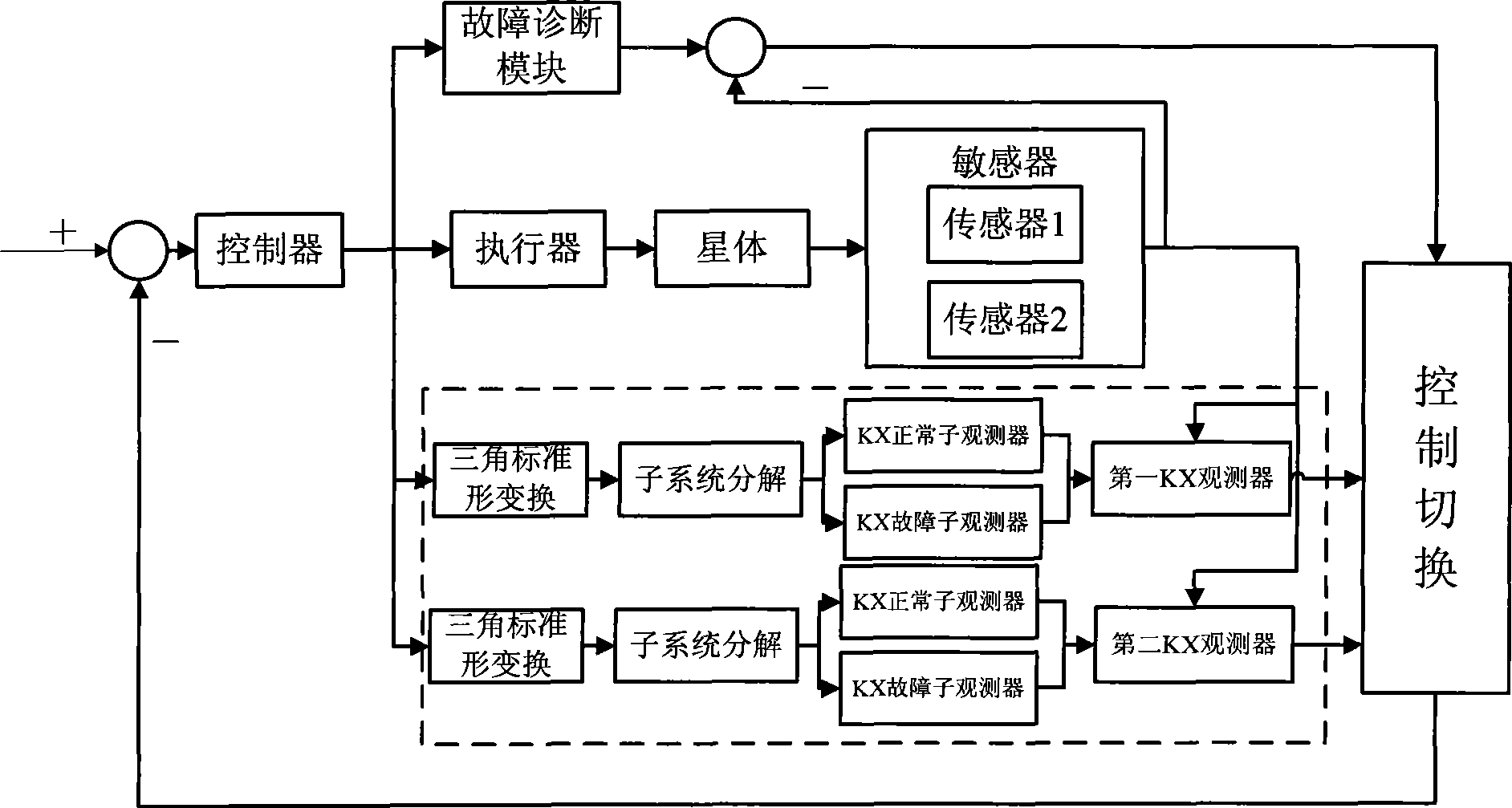

Fault tolerant observing method of sensor for satellite attitude control system

InactiveCN101481019AFault-tolerantState Observation Fault ToleranceElectric testing/monitoringSpacecraft guiding apparatusFault toleranceLoop control

The invention provides a sensor fault tolerance observing method for a satellite attitude control system. Firstly, the control system carries out the sensor fault detecting isolation; if a first sensor is judged to have faults according to an isolation result, a second KX observer is selected to observe; and if a second sensor is judged to have faults, a first KX observer is selected to observe. The first or second KX observer has the ensuring method that if the second or first sensor has faults, the control system is analyzed into a normal subsystem and a fault subsystem by using system feedback stable control as a target, and a low-dimension KX function observer is designed by respectively aiming at the two subsystems to combine and obtain a system KX observer with fault tolerance performance. The two parallel KX observers are designed and are fused into a controlling and switching flow; and when the partial sensor output is unreliable, the satellite attitude control system still can ensure the fault tolerance observation of system rest part observed quantity to ensure the closed loop control integrality of a failure system.

Owner:HUAZHONG UNIV OF SCI & TECH

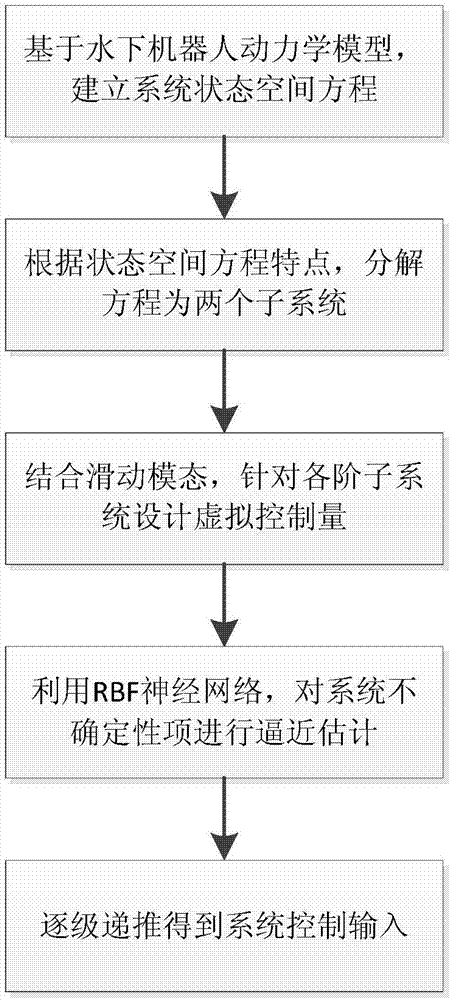

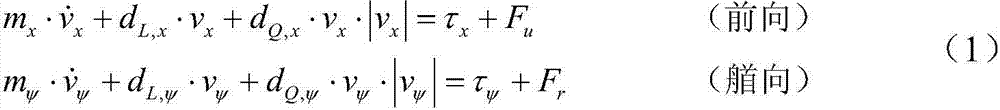

Underwater robot sliding mode control method based on adaptive backstepping

The invention discloses an underwater robot sliding mode control method based on adaptive backstepping in order to solve the technical problem that an existing underwater robot control method is poorin practicability. According to the technical scheme, the method comprises the steps that based on the decomposition of a complex nonlinear system, the controlling quantity of a total system is obtained by designing the virtual controlling quantity for a sub-system through the step-by-step recursion of a sliding mode; according to the buffeting problem caused when the system is not sure about theupper bound, and an RBF neural network is introduced into a controller so as to adoptively approach the internal indeterminacy and the external disturbance of the system. Finally, the control over thesystem buffeting is achieved, high-precision tracking control is achieved, the robustness of a closed-loop system is improved, the engineering requirements are met, and the practicability is high.

Owner:NORTHWESTERN POLYTECHNICAL UNIV +1

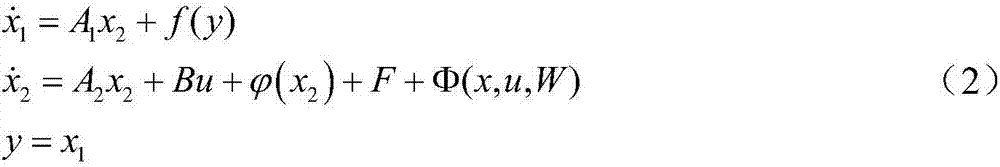

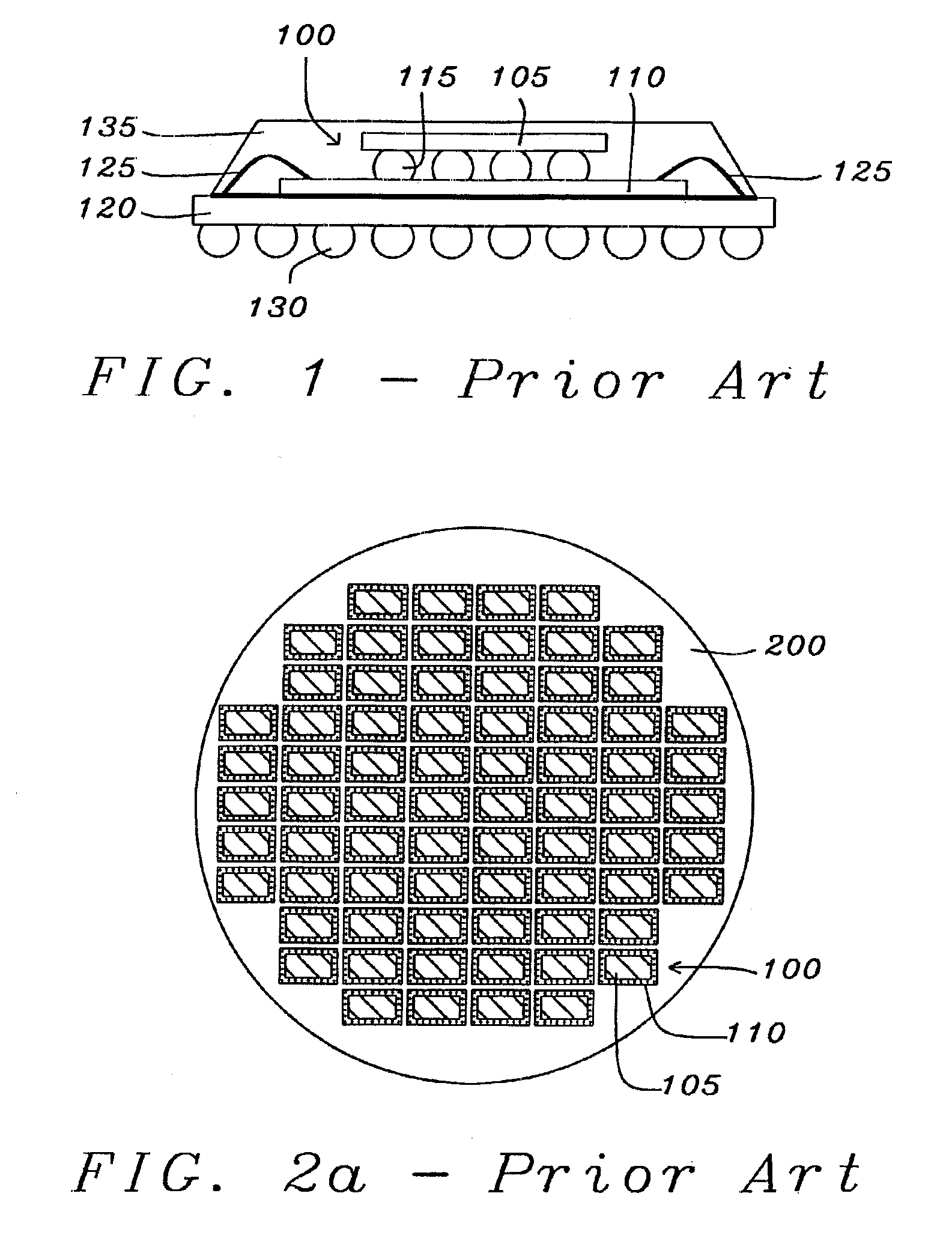

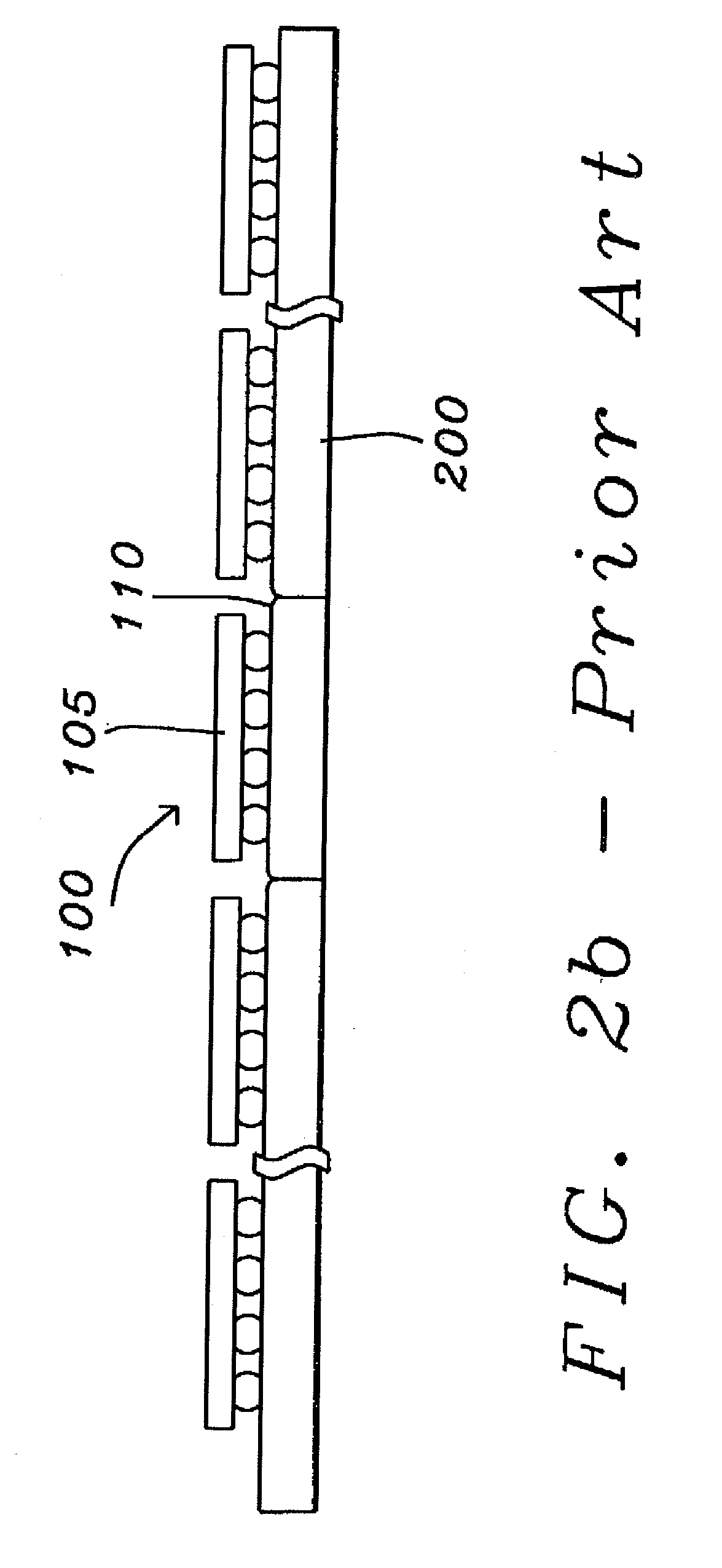

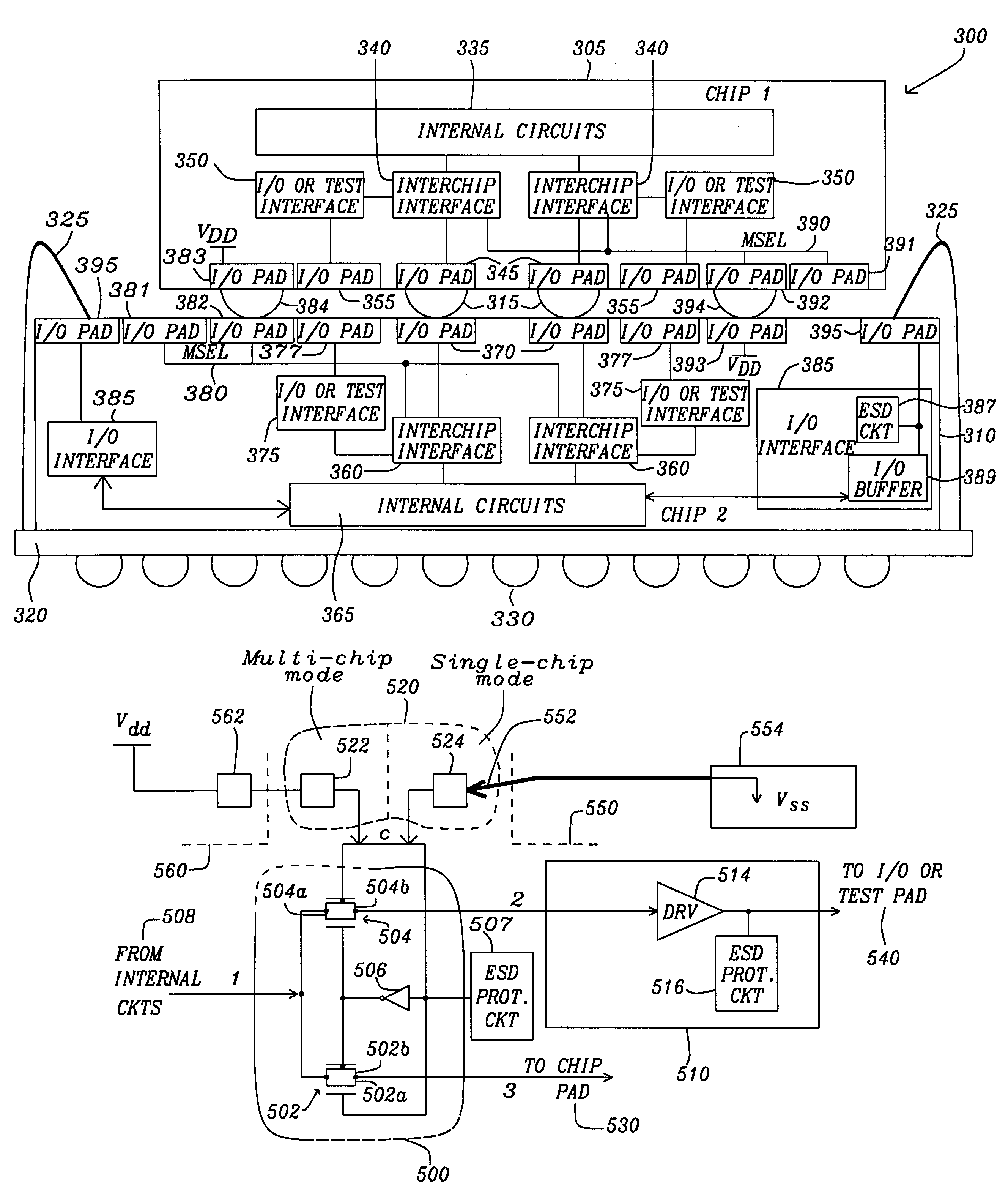

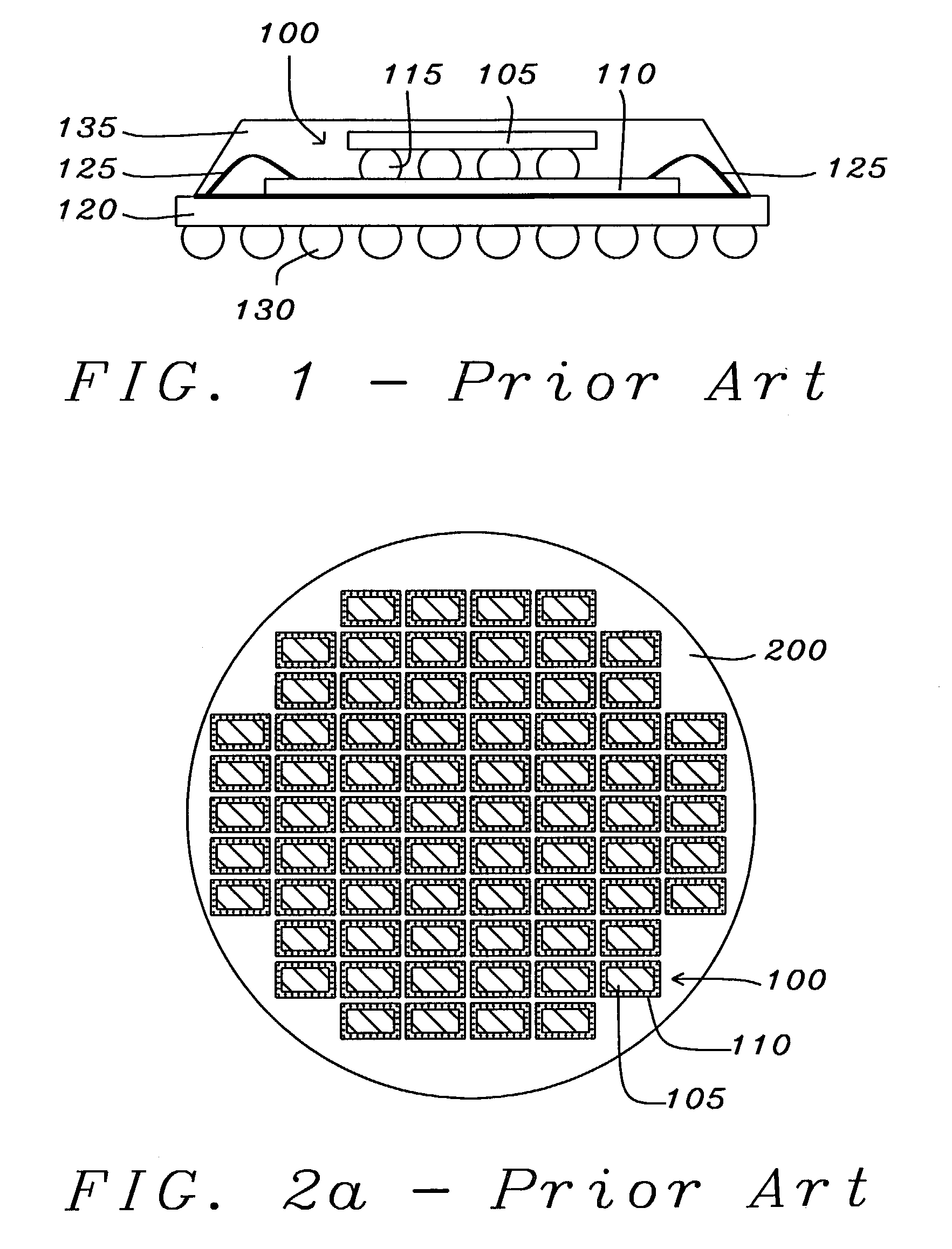

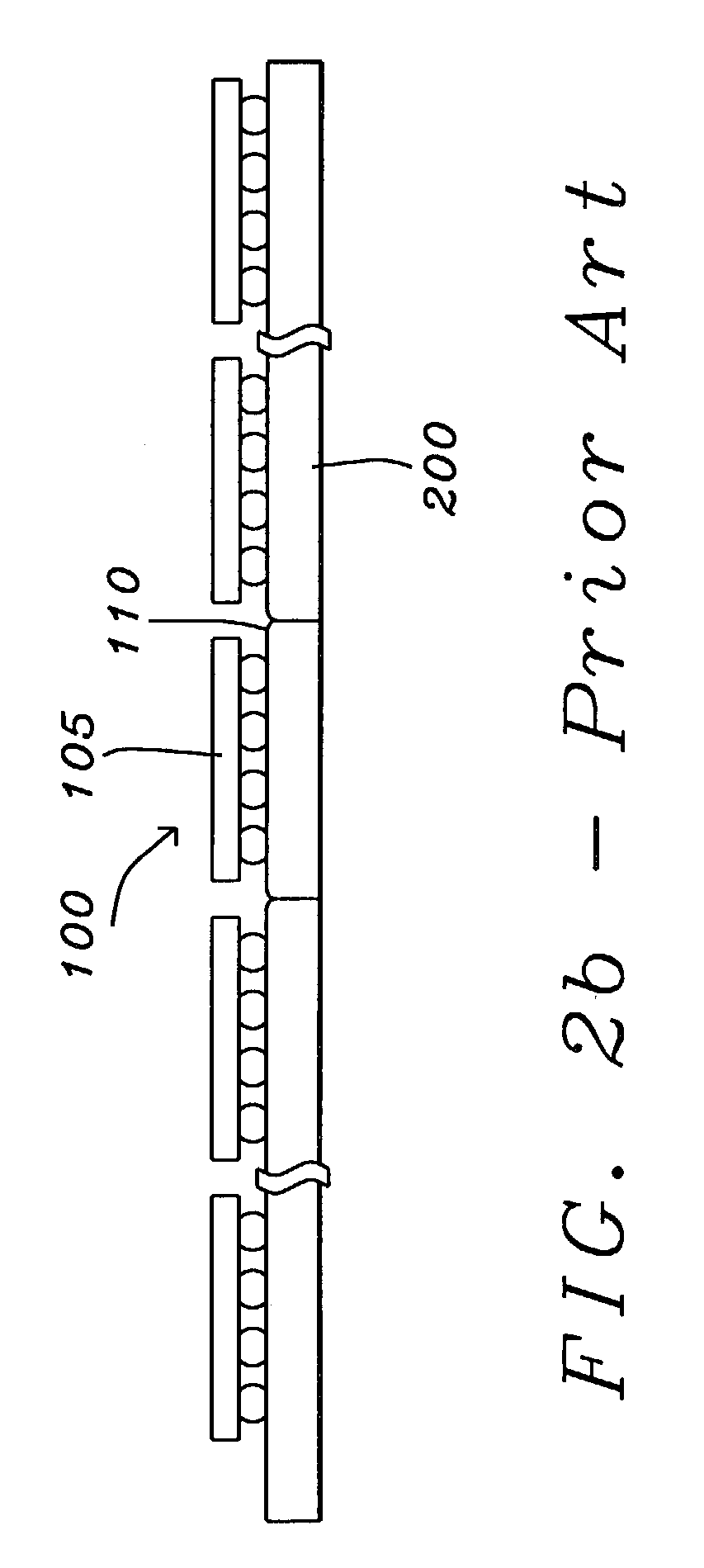

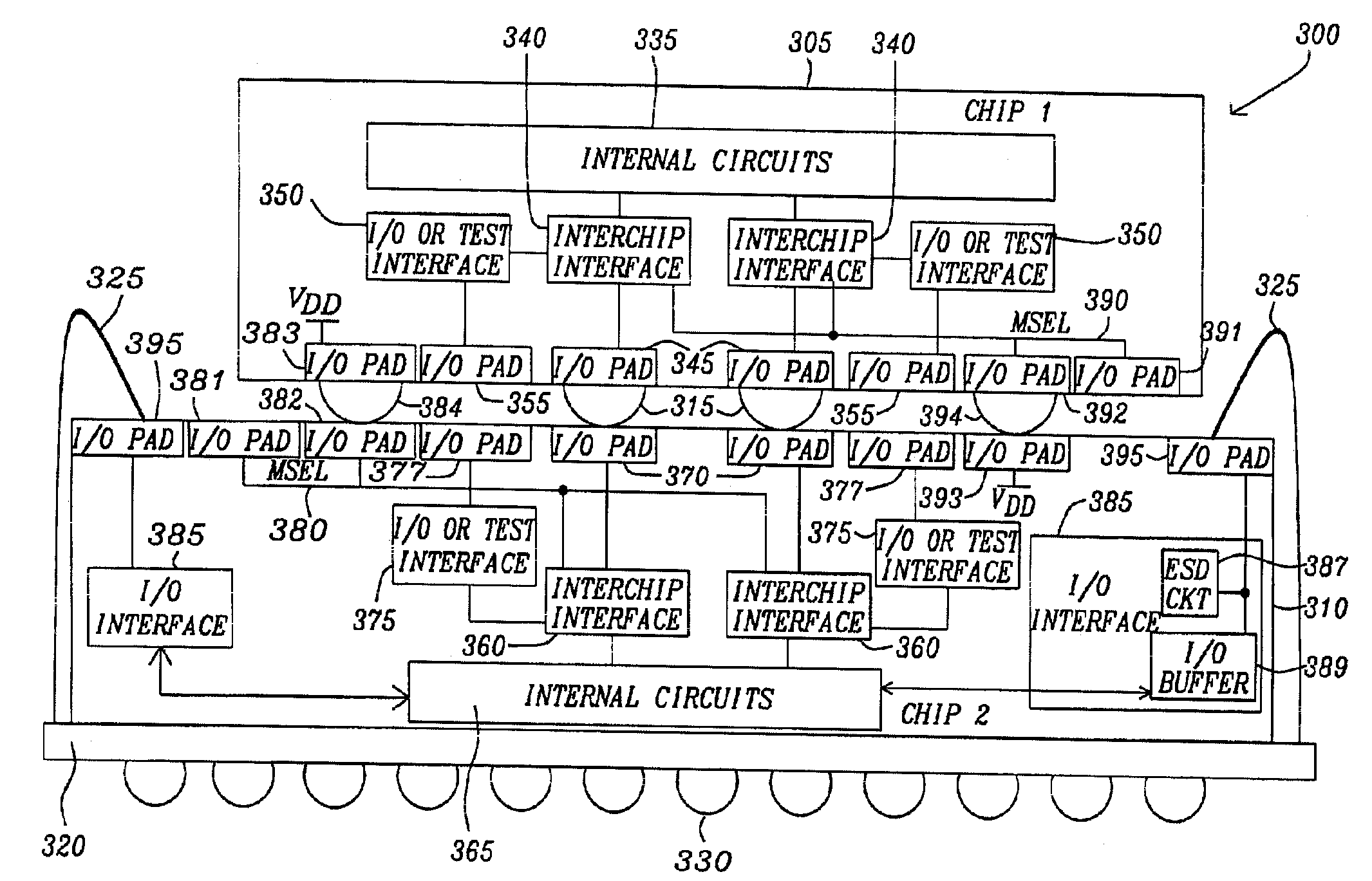

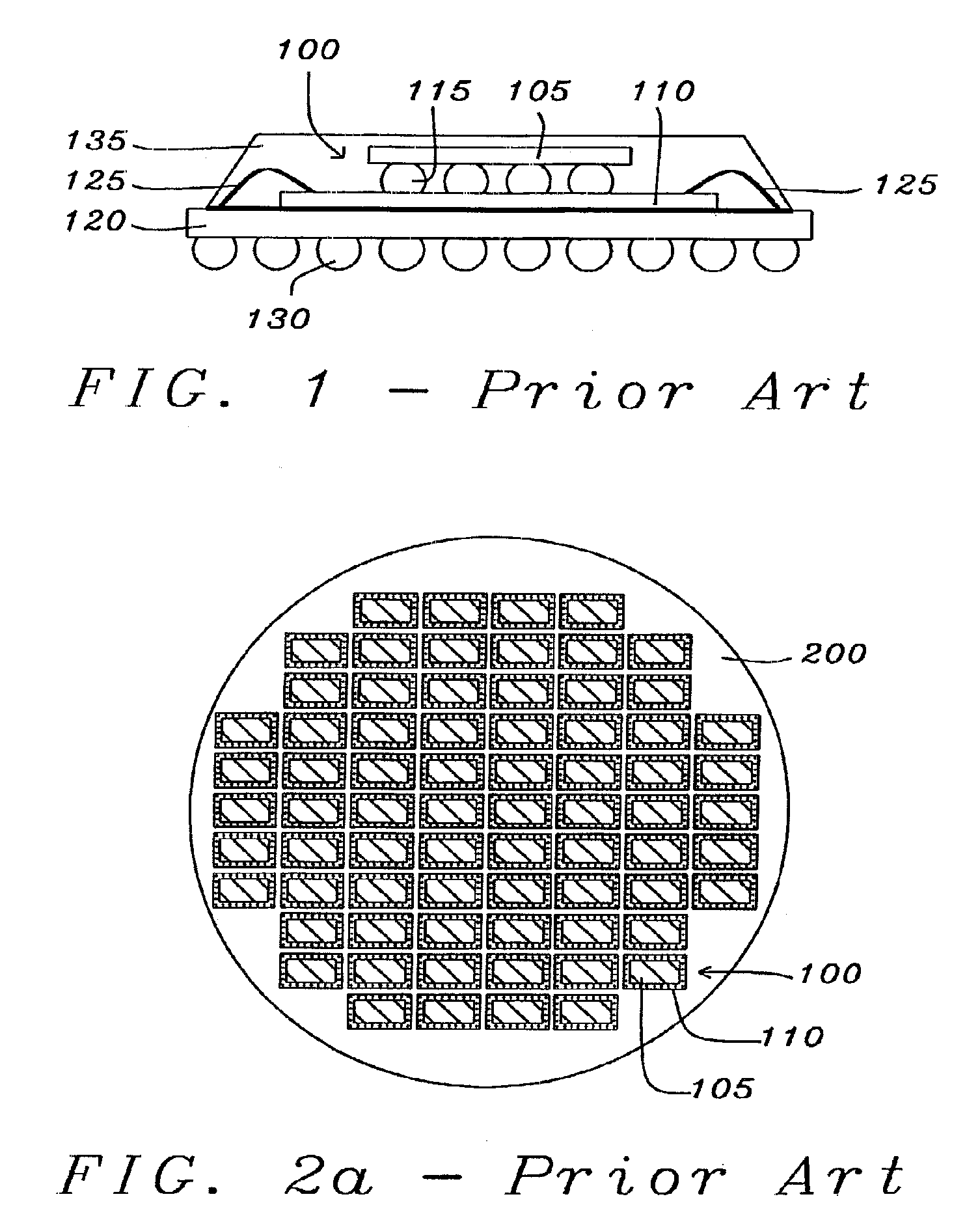

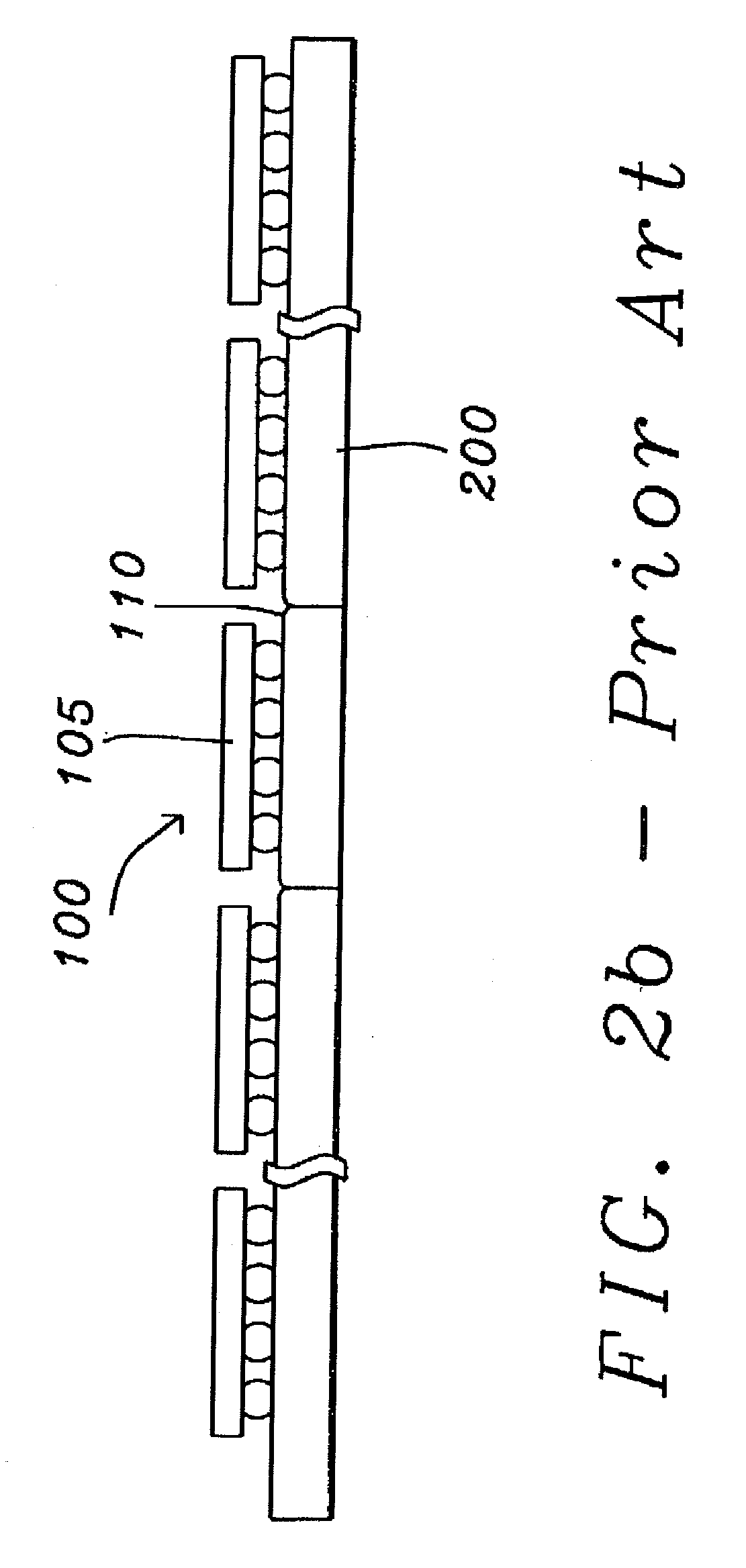

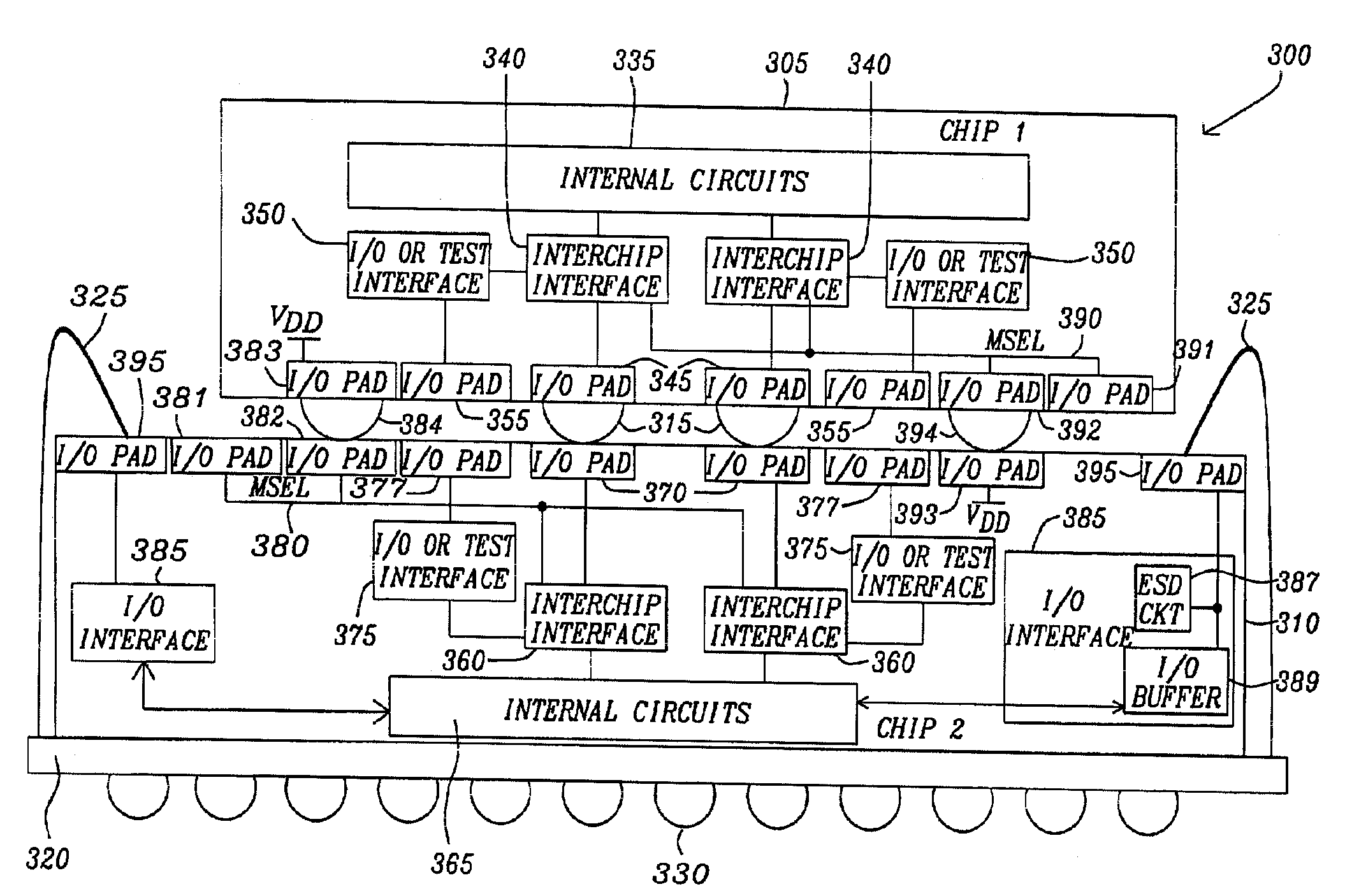

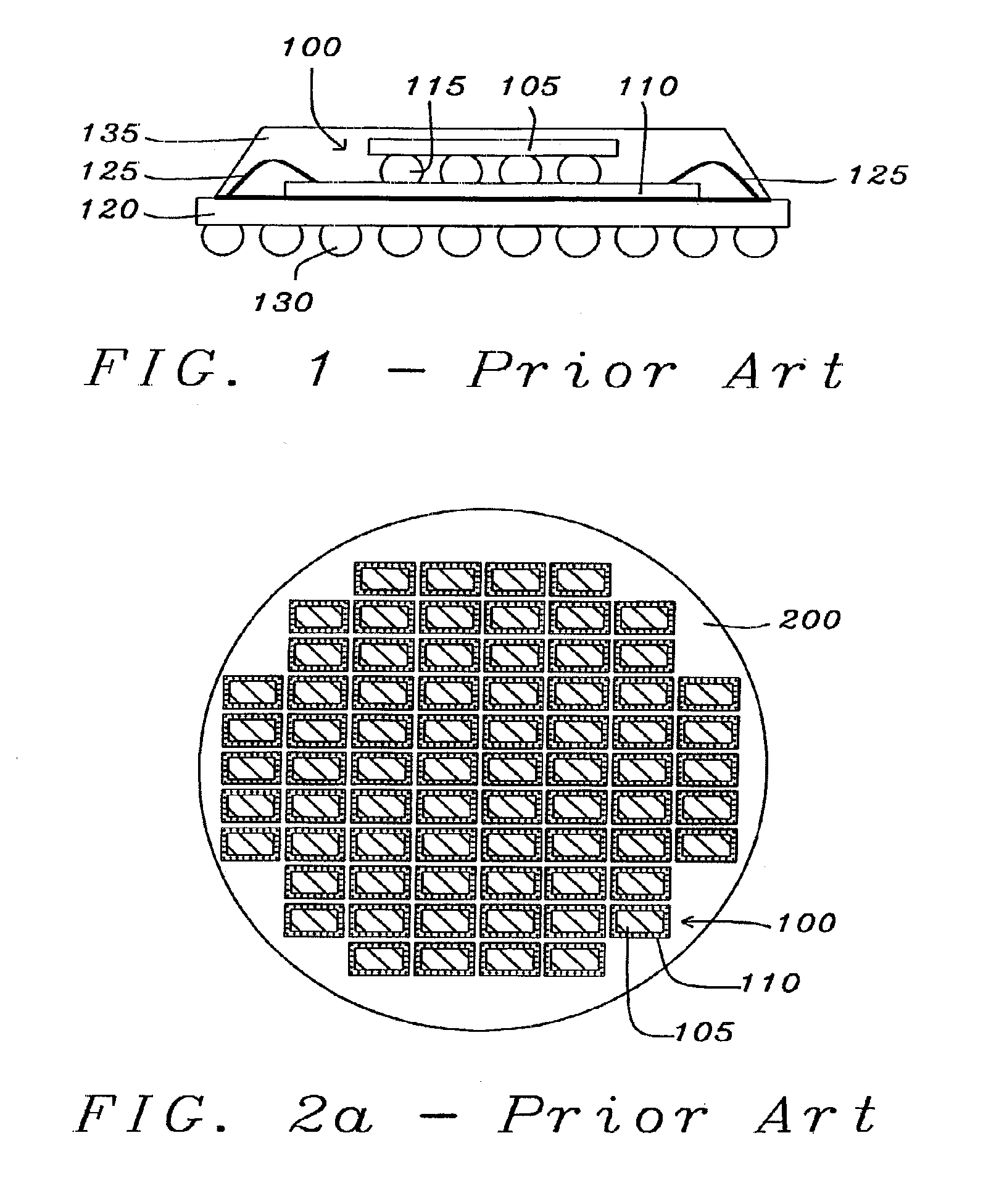

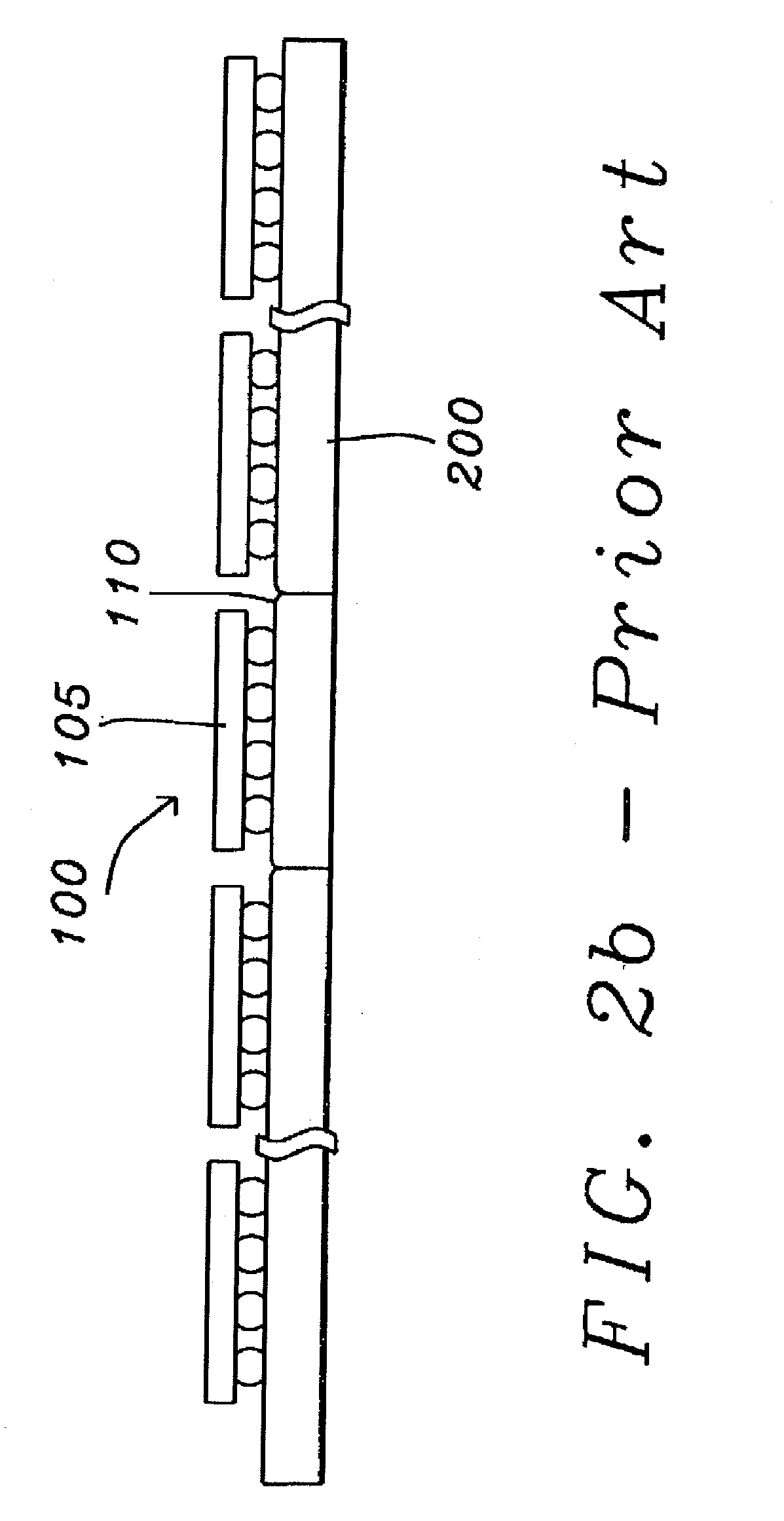

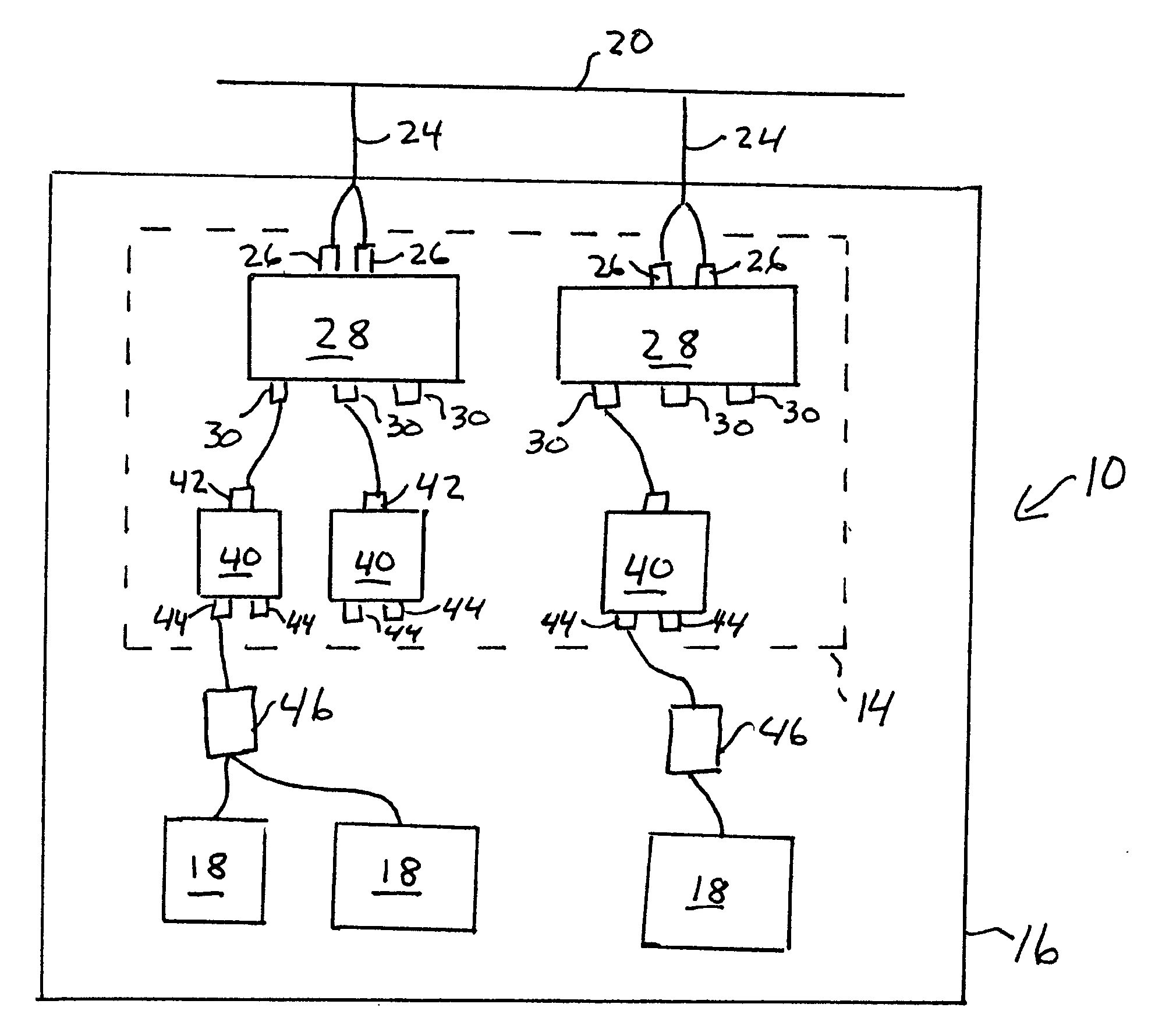

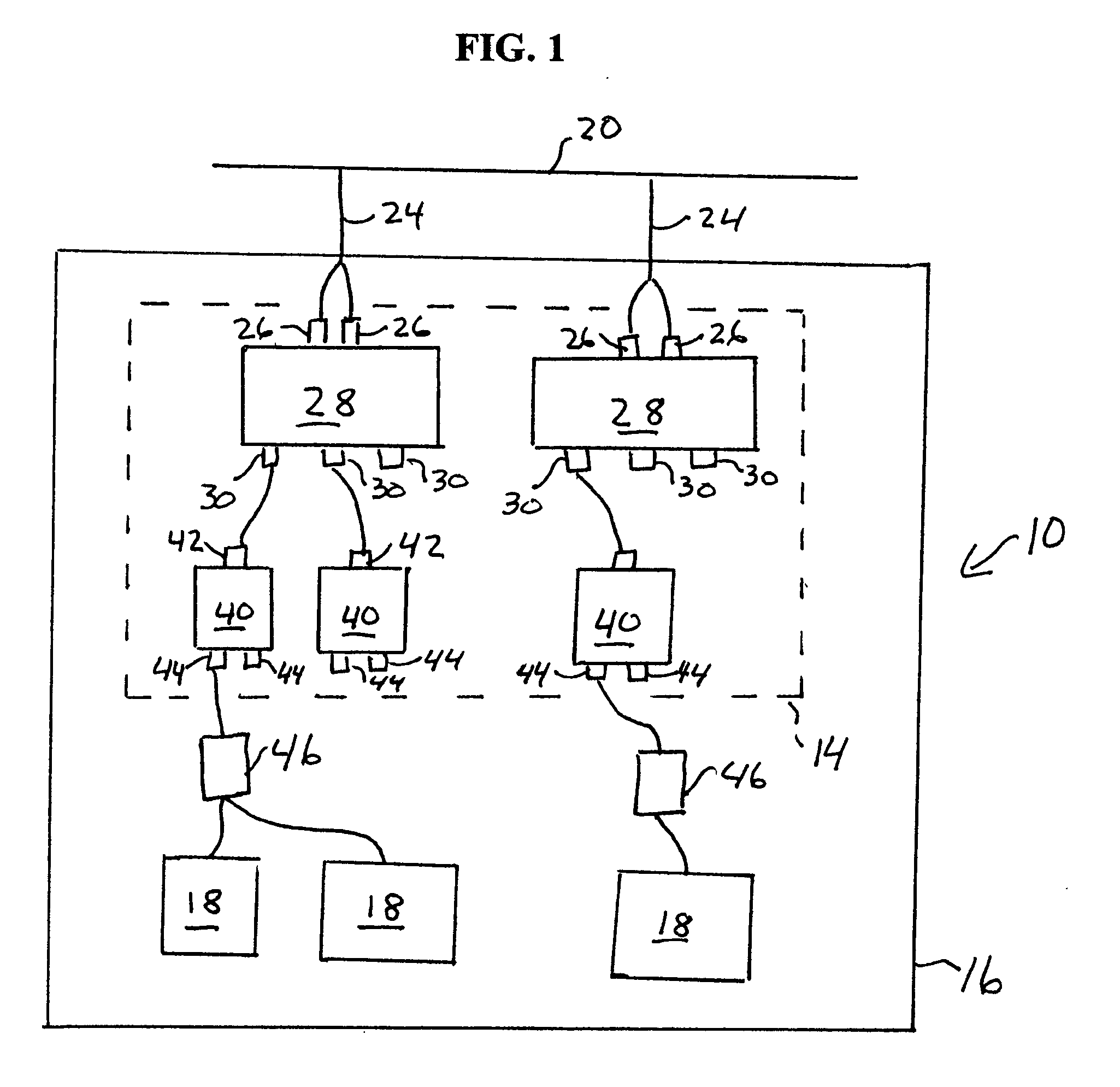

High performance sub-system design and assembly

InactiveUS20080185586A1Maximum performanceMinimal costEnergy efficient ICTDigital circuit testingSystems designEngineering

A multiple integrated circuit chip structure provides interchip communication between integrated circuit chips of the structure with no ESD protection circuits and no input / output circuitry. The interchip communication is between internal circuits of the integrated circuit chips. The multiple integrated circuit chip structure has an interchip interface circuit to selectively connect internal circuits of the integrated circuits to test interface circuits having ESD protection circuits and input / output circuitry designed to communicate with external test systems during test and burn-in procedures. The multiple interconnected integrated circuit chip structure has a first integrated circuit chip mounted to one or more second integrated circuit chips to physically and electrically connect the integrated circuit chips to one another. The first integrated circuit chips have interchip interface circuits connected each other to selectively communicate between internal circuits of the each other integrated circuit chips or test interface circuits, connected to the internal circuits of each integrated circuit chip to provide stimulus and response to said internal circuits during testing procedures. A mode selector receives a signal external to the chip to determine whether the communication is to be with one of the other connected integrated circuit chips or in single chip mode, such as with the test interface circuits. ESD protection is added to the mode selector circuitry.

Owner:QUALCOMM INC

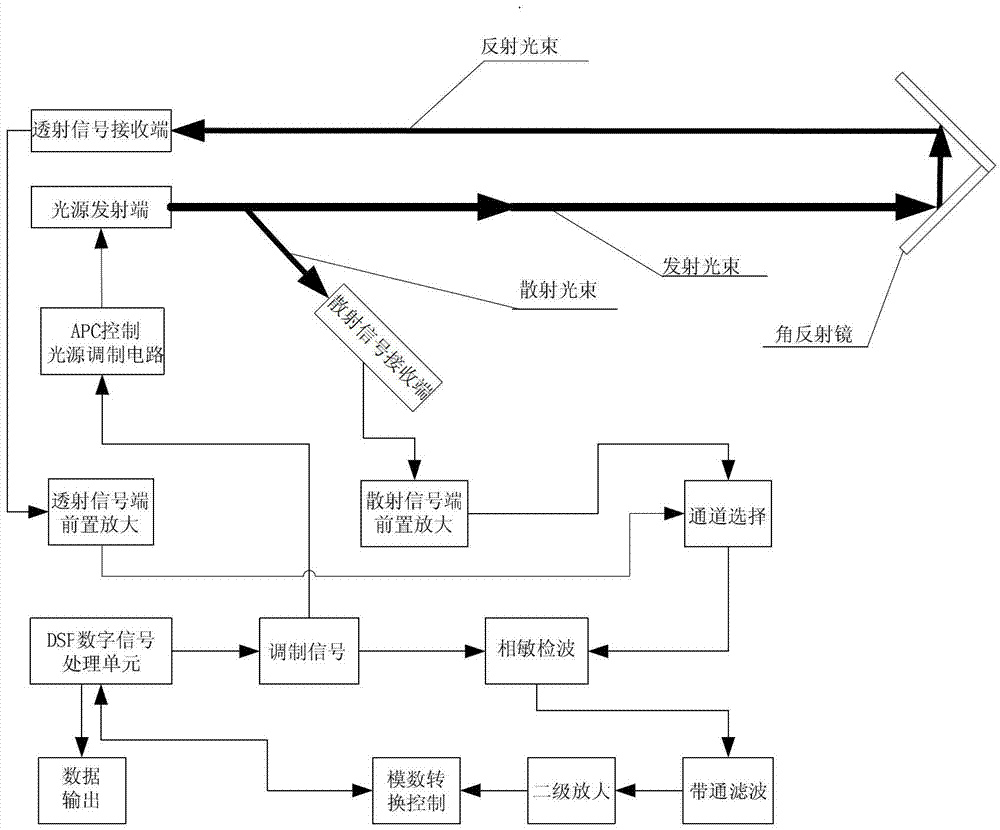

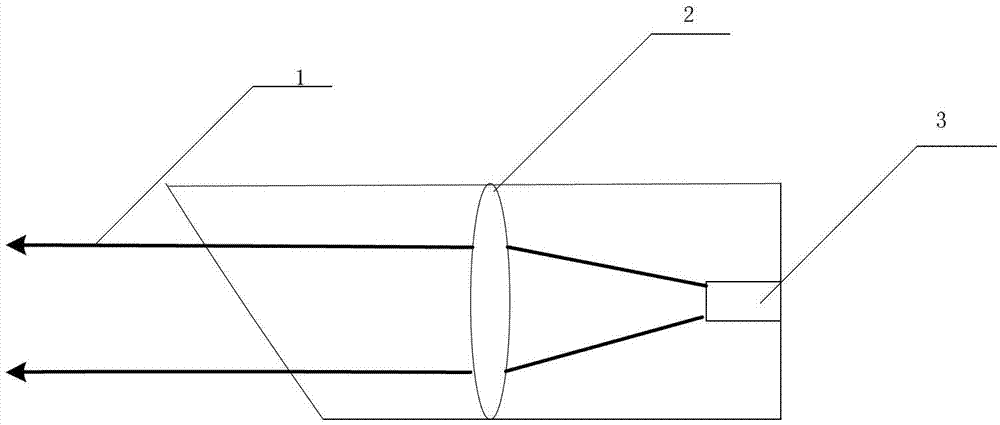

Atmospheric visibility measuring system

ActiveCN102879359AAccurate measurementUndisturbedScattering properties measurementsTransmissivity measurementsWhole bodyLaser light

An atmospheric visibility measuring system is characterized in that the system can realize full-scale precise measurement of atmospheric visibility. The system adopts a measurement structure with a single light source and double baselines; a light source transmitting terminal and two signal receiving terminals are integrated into a whole body, which reduces the complexity of optical path debugging and measurement electronic system design, reduces requirements for field installation, improves system practicality, and reduces equipment cost. Meanwhile, the laser light source is subject to high frequency modulation, and an optical filter is installed in the front of a detector, which improve the system capability of resisting background light and stray light influence. In the signal sampling part, synchronous demodulation weak signal detection technology is adopted, which improves the measurement precision and measurement range of the system. The atmospheric visibility measuring system of the invention is applicable to industries of meteorological stations, airports, highway, harbours, atmosphere environment monitoring, and the like.

Owner:HEFEI INSTITUTES OF PHYSICAL SCIENCE - CHINESE ACAD OF SCI

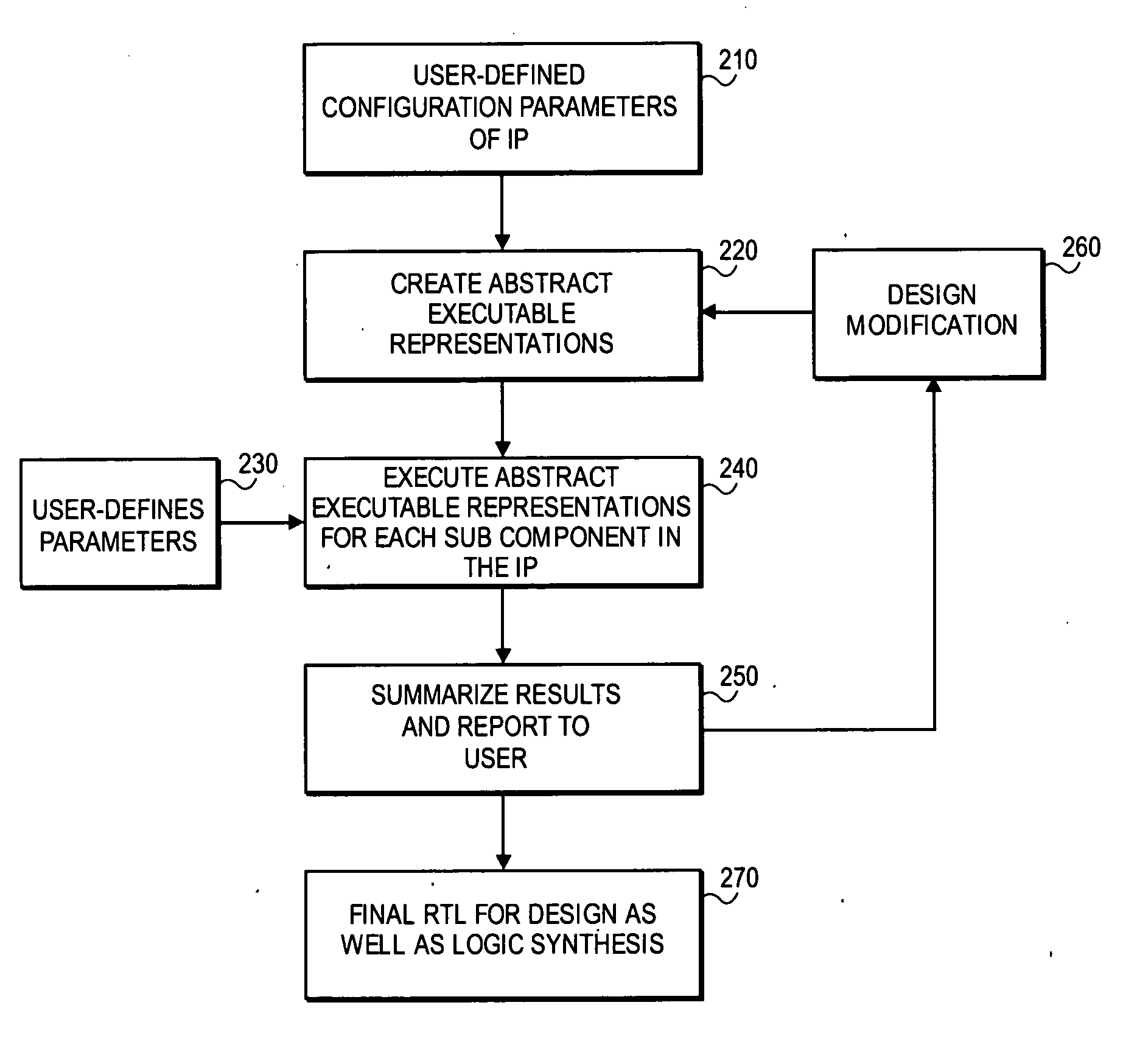

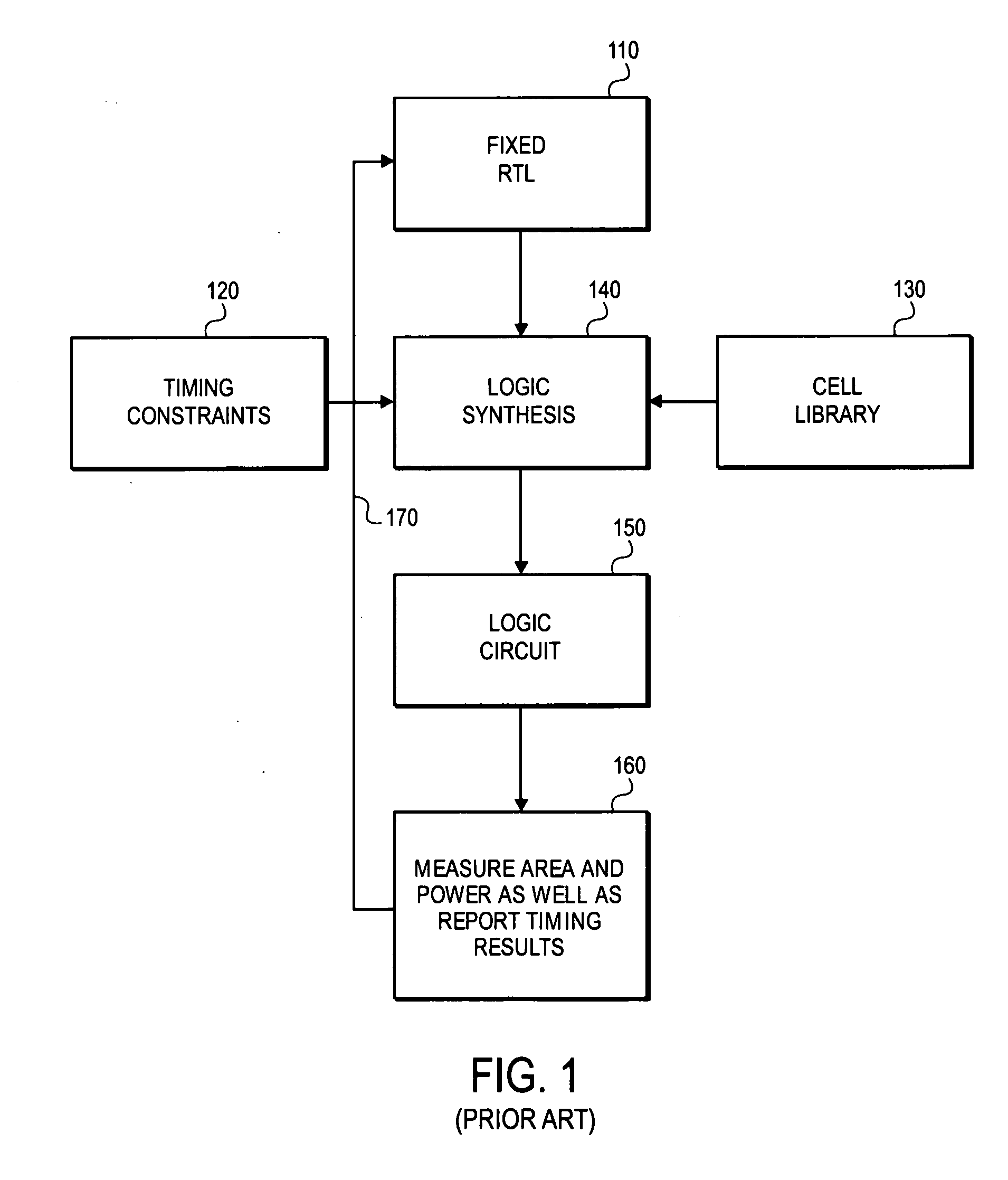

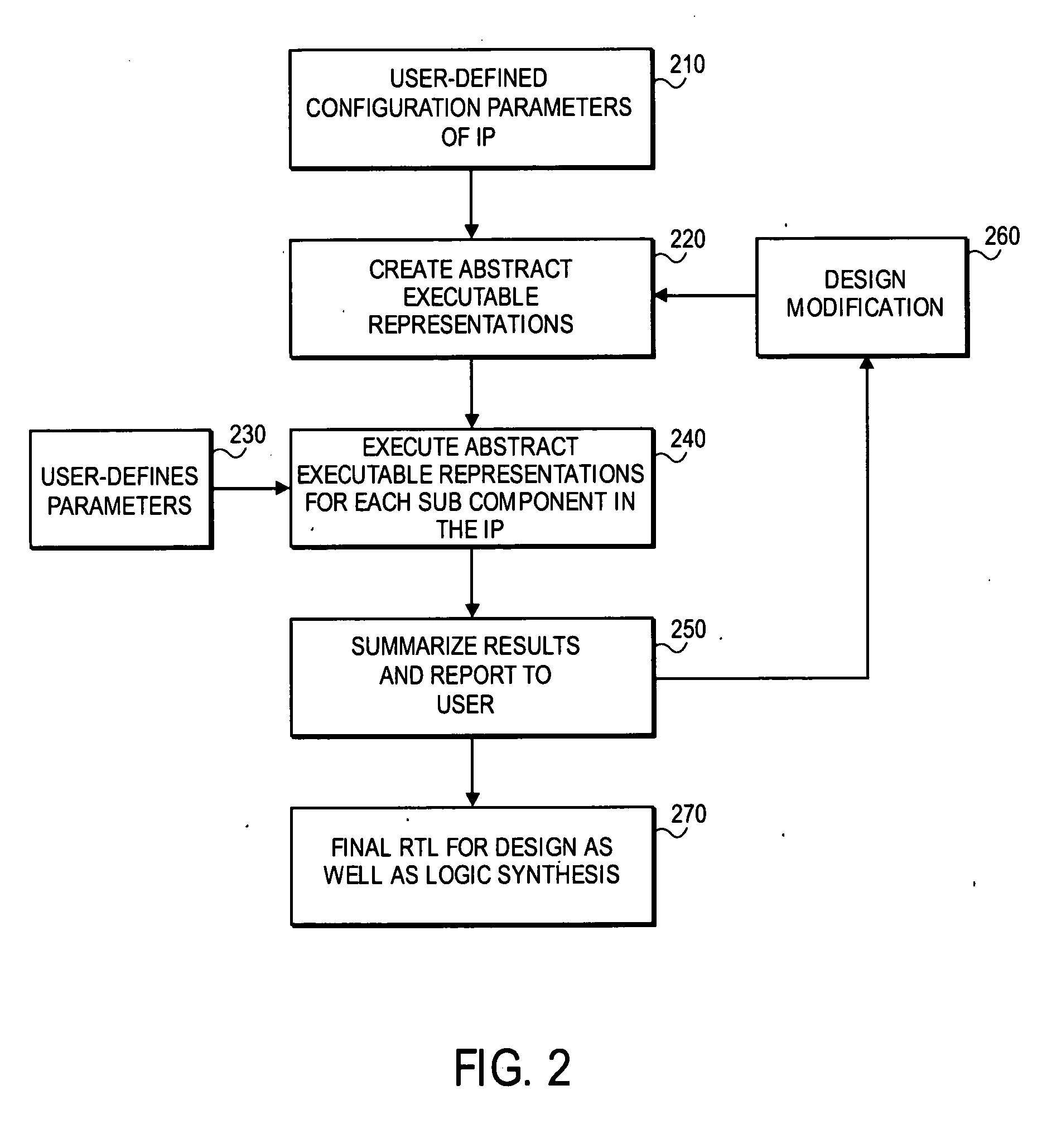

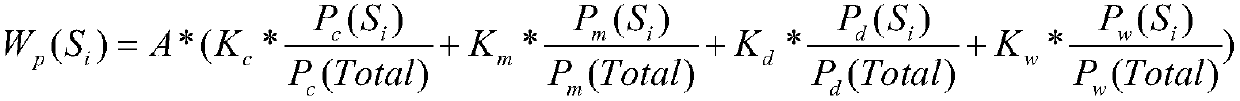

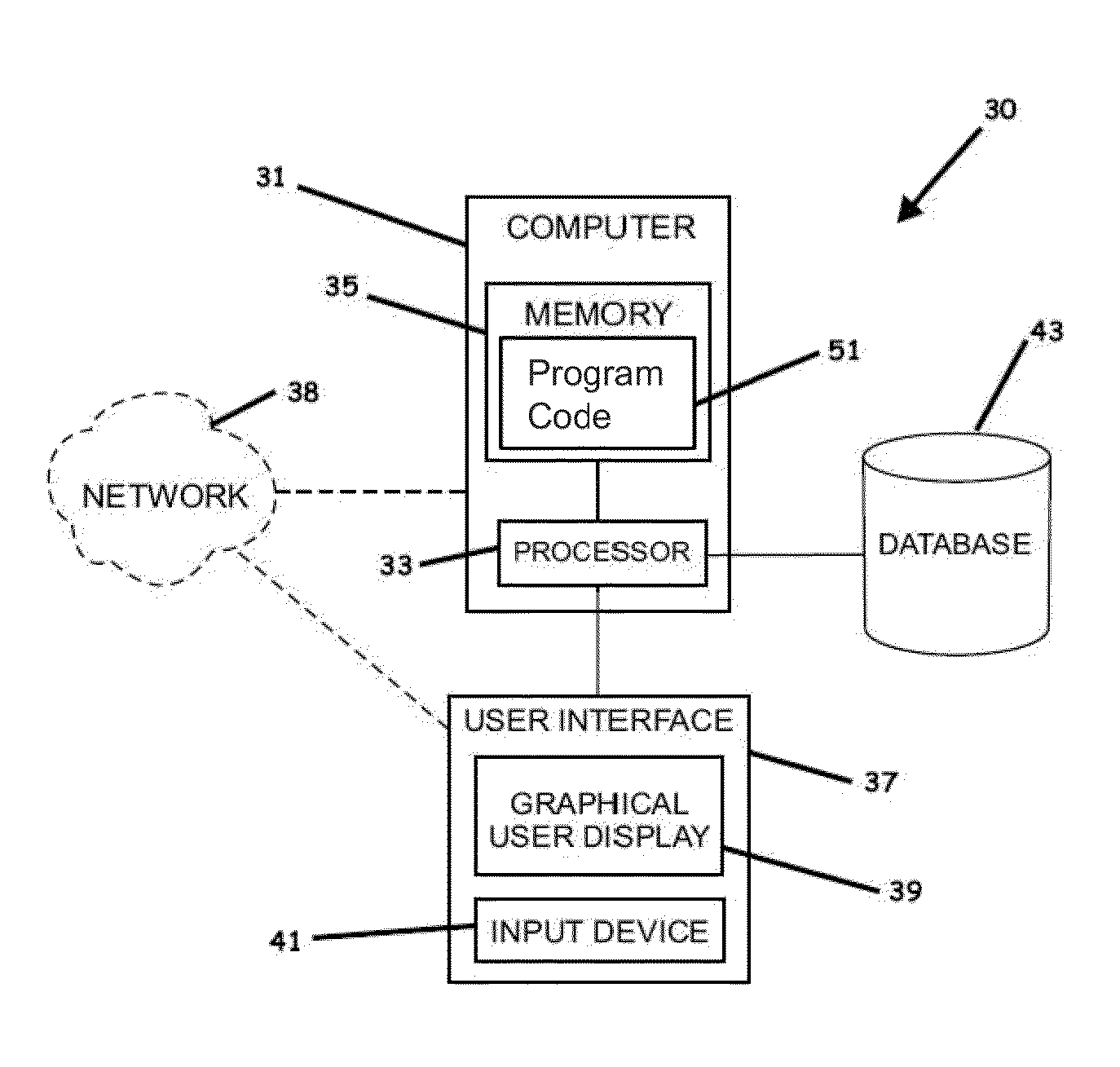

Various methods and apparatuses for estimating characteristics of an electronic system's design

Methods and apparatuses are described for an Intellectual Property (IP) Generator for estimating timing, area, and power characteristics of an electronic system design. The IP Generator receives a user-supplied file having data describing a configuration of an IP design having multiple levels of hierarchy. The IP Generator also receives user-supplied technology parameters and data-flow information. The IP generator correlates estimated timing, area, and power characteristics for each IP sub component based on the user supplied technology parameters, data-flow information and configuration parameters. The IP generator reports the timing, area, and power estimates to a user via a graphic user interface prior to a transformation of a Register Transfer Level (RTL) design into the gate-level circuit design.

Owner:META PLATFORMS TECH LLC

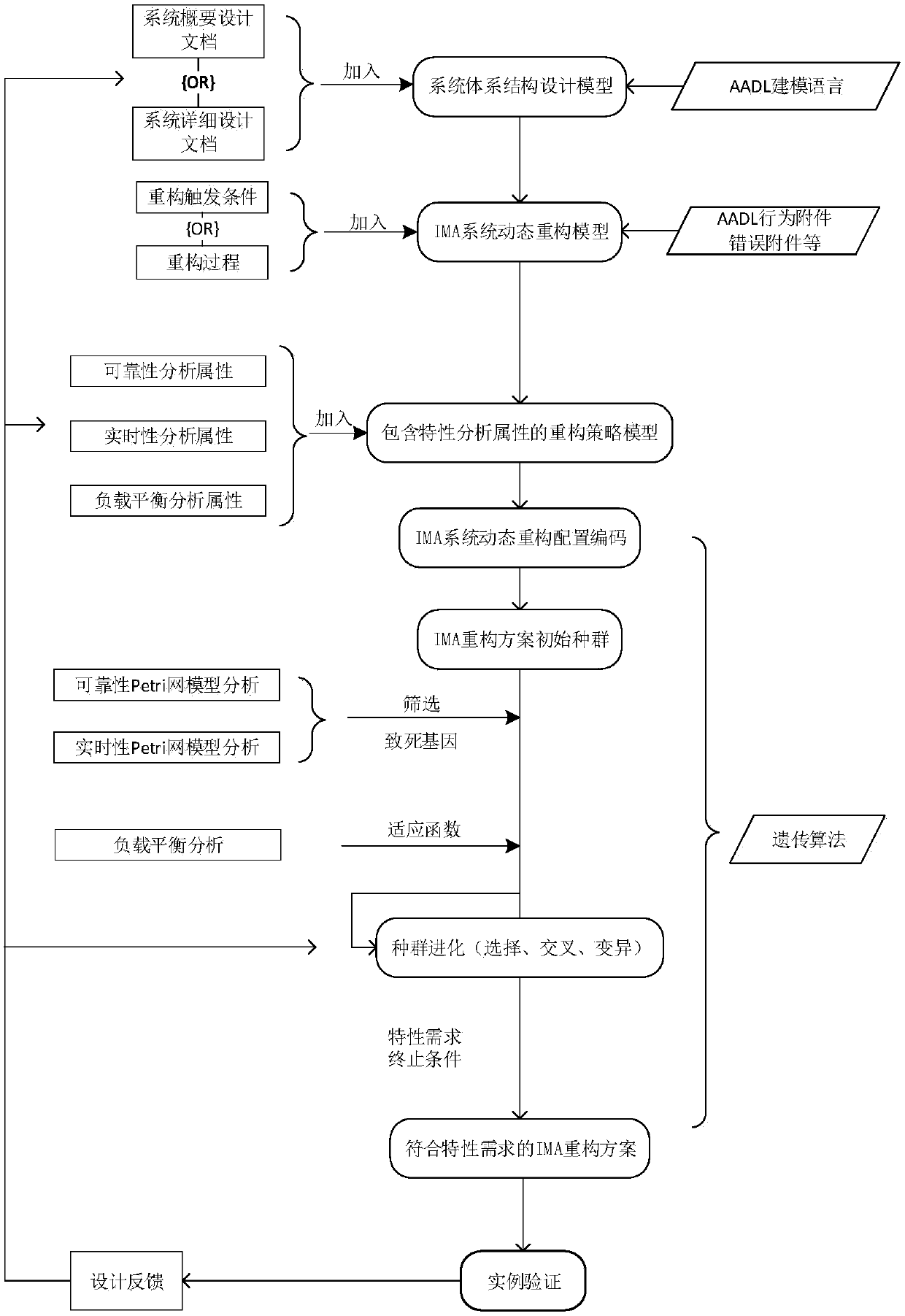

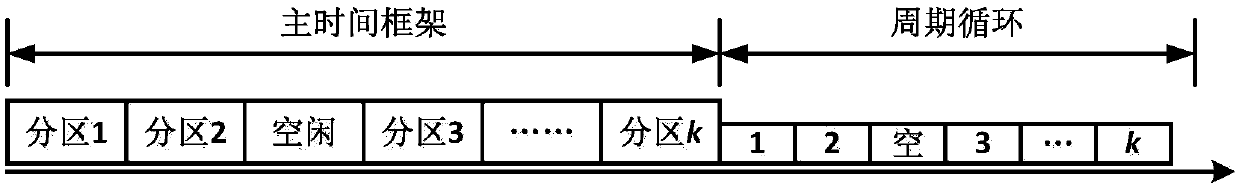

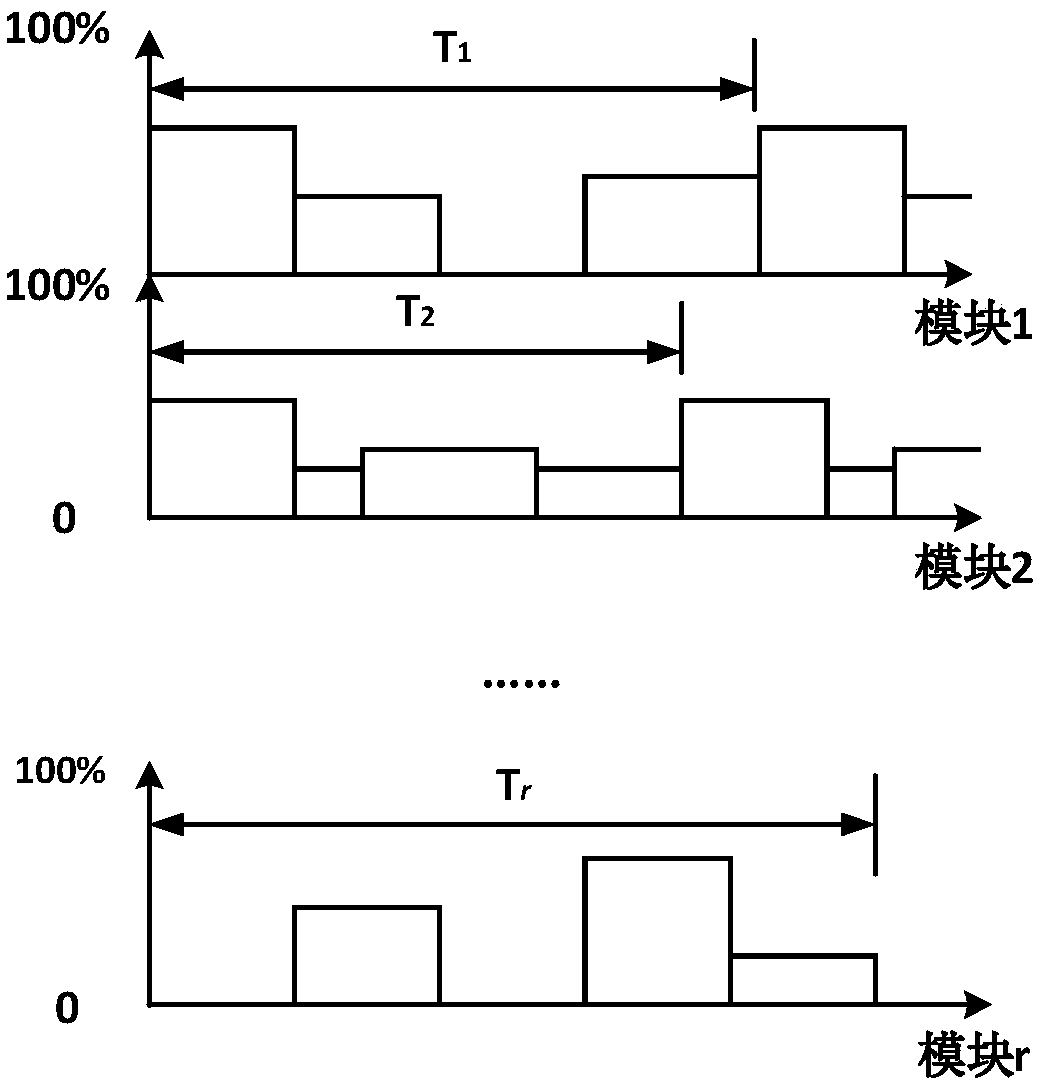

IMA system dynamic reconfiguration strategy optimization method based on genetic algorithm

ActiveCN108268710ASolving the state space explosion problemImprove reliabilityGeometric CADDesign optimisation/simulationElectronic systemsAlgorithm

The invention discloses an IMA system dynamic reconfiguration strategy optimization method based on a genetic algorithm and belongs to the field of integrated electronic system design. According to the method, the problem of configuration scheme state space explosion during dynamic reconfiguration of an IMA system is solved by use of the genetic algorithm technology, and an effective IMA system dynamic reconfiguration strategy model is obtained by adding an IMA system reliability, instantaneity and static load balance analysis method. By performing reconfiguration coding on software and hardware and time configuration of the IMA system, the model can be converted into an IMA system configuration scheme AADL model, the reliability, instantaneity constraint and multidimensional load balanceanalysis of the IMA system is performed through the AADL model, and a lethal gene and a fitness function in genetic algorithm analysis optimization can be obtained. Through genetic algorithm operation, an optimal IMA system dynamic reconfiguration scheme can be effectively found.

Owner:BEIHANG UNIV

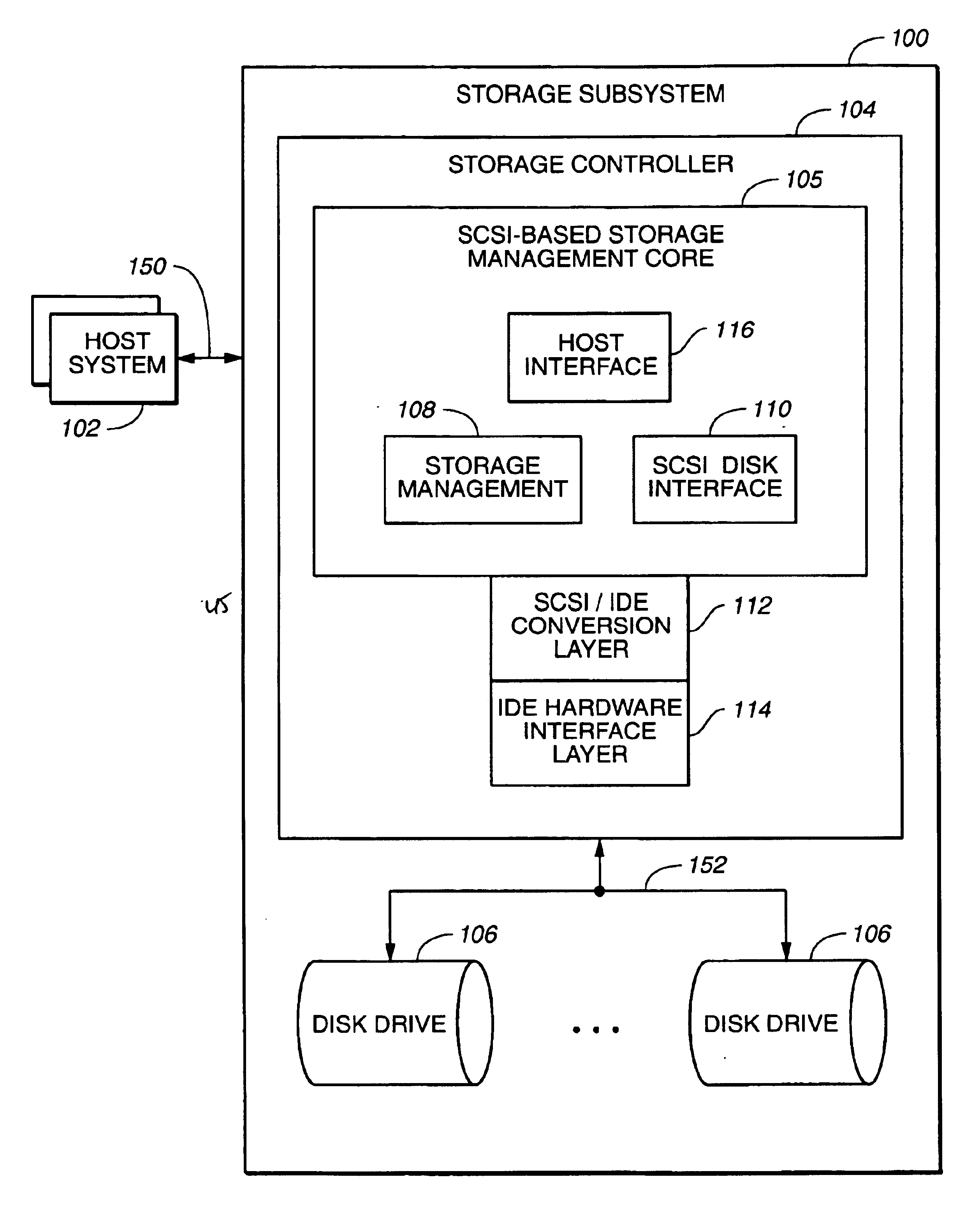

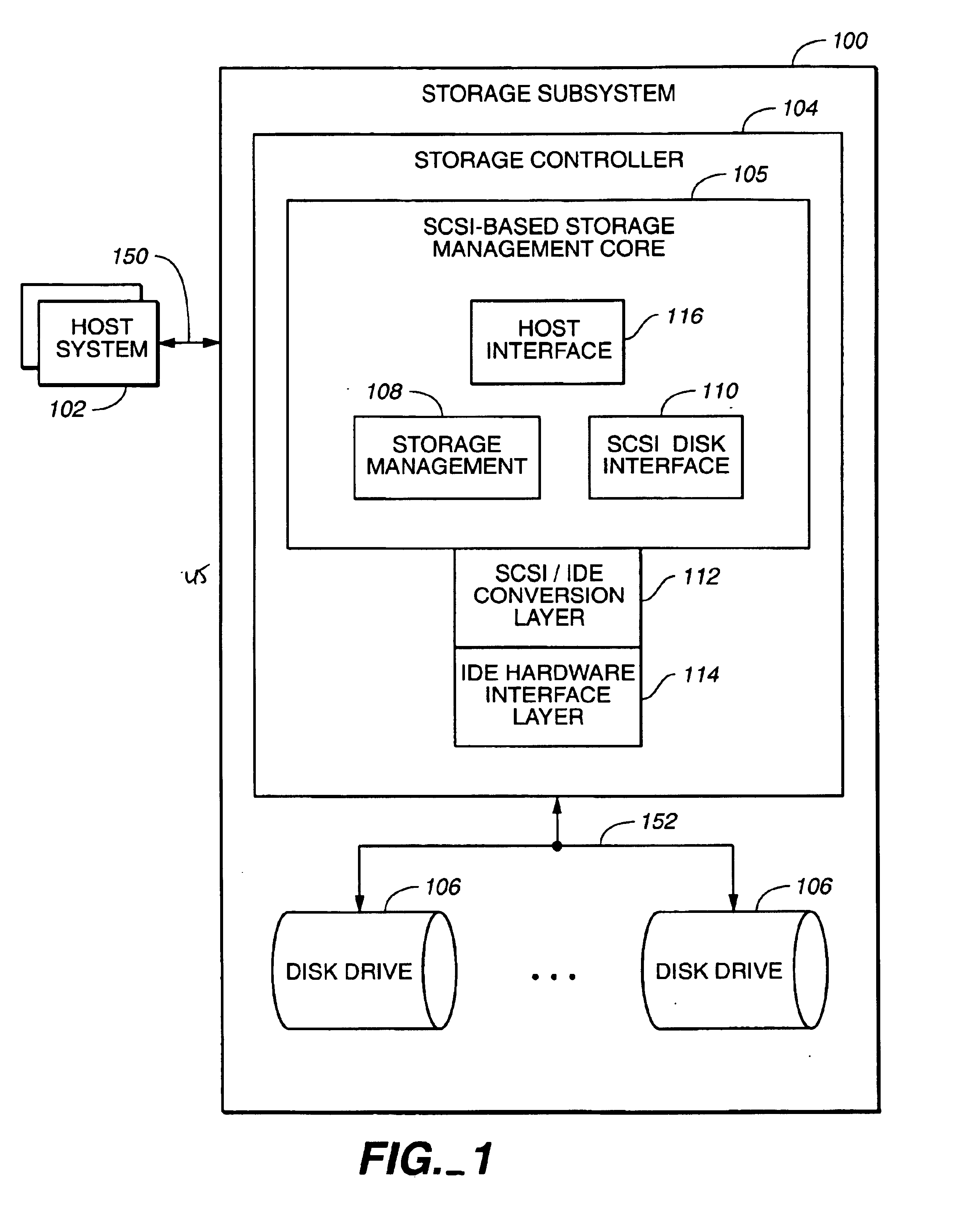

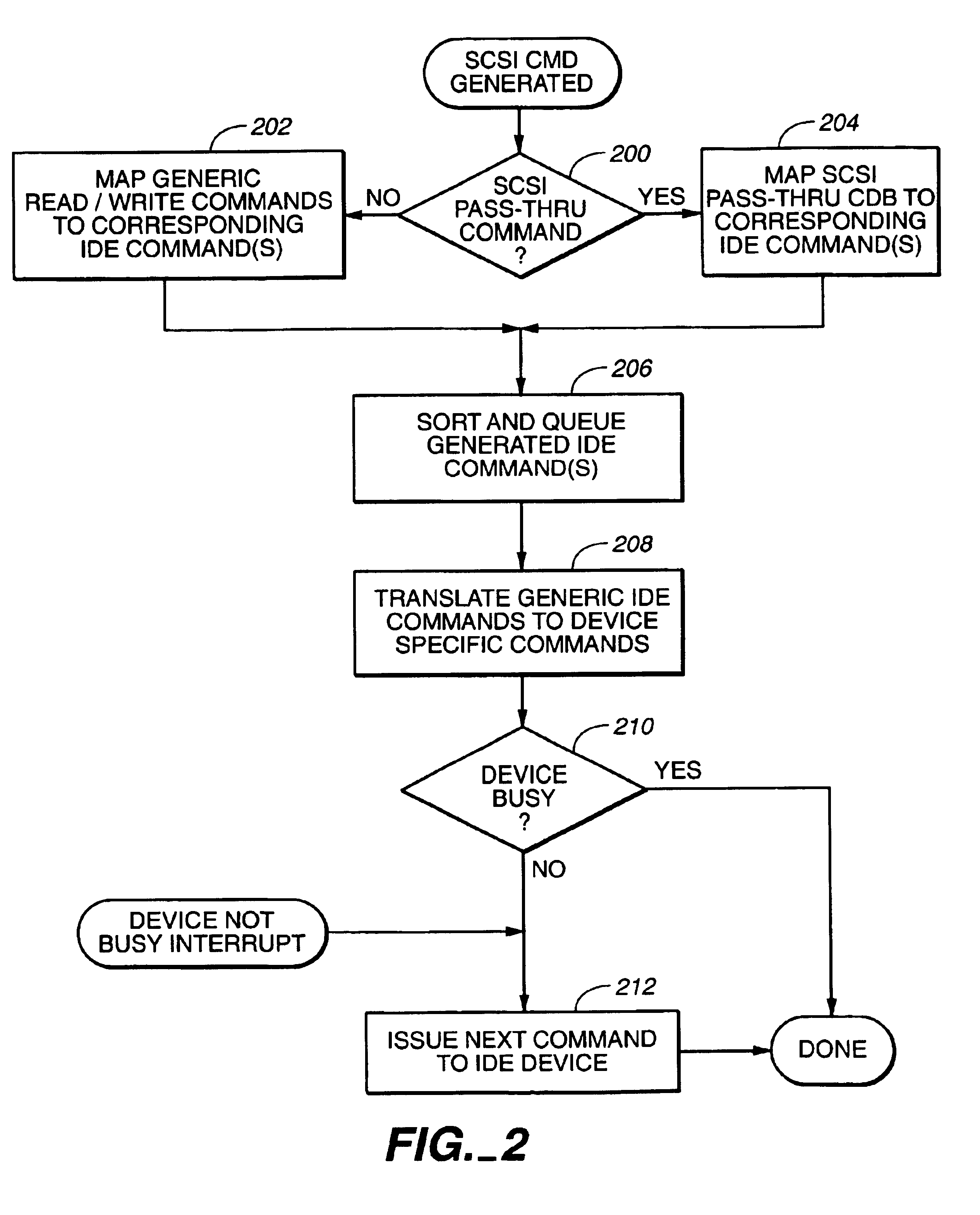

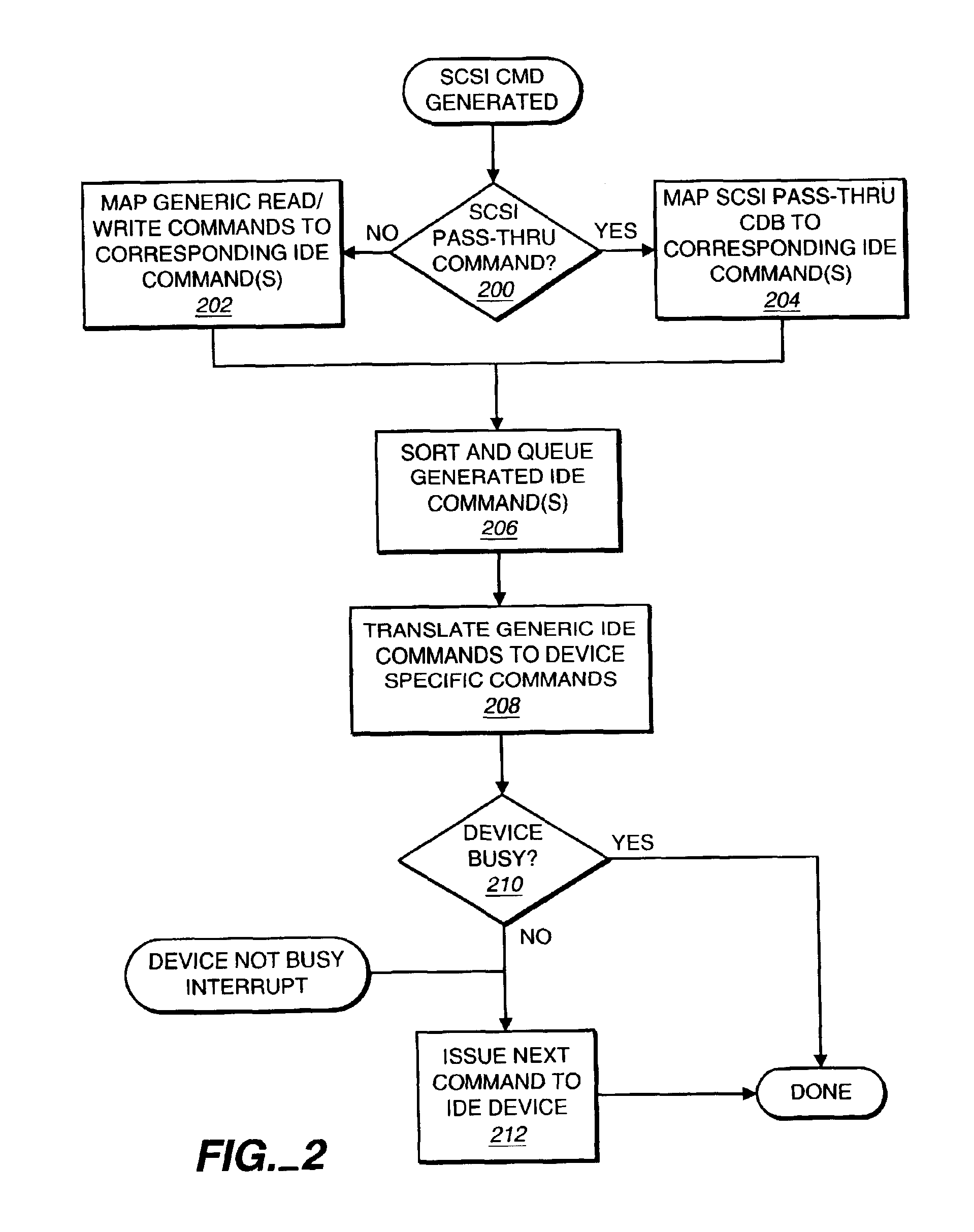

Methods and structure for SCSI/IDE translation in a storage subsystem

Methods and associated structure operable within a SCSI-based storage subsystem to adapt the storage controller for use with non-SCSI disk drives. A firmware layer of the present invention intercepts SCSI read / write requests and pass through command blocks (CDBs) generated by the storage management core of the controller and translates the requests and command structures into corresponding command structures for transmission to a non-SCSI disk drive. In like manner, the firmware layer of the present invention receives status information from non-SCSI disk drives and translates the status information into corresponding SCSI compatible status information. In one exemplary preferred embodiment, a storage subsystem designed for interaction with SCSI disk drives may be adapted in accordance with the present invention to utilize lower-cost, commodity disk drives such as IDE compatible disk drives.

Owner:AVAGO TECH INT SALES PTE LTD

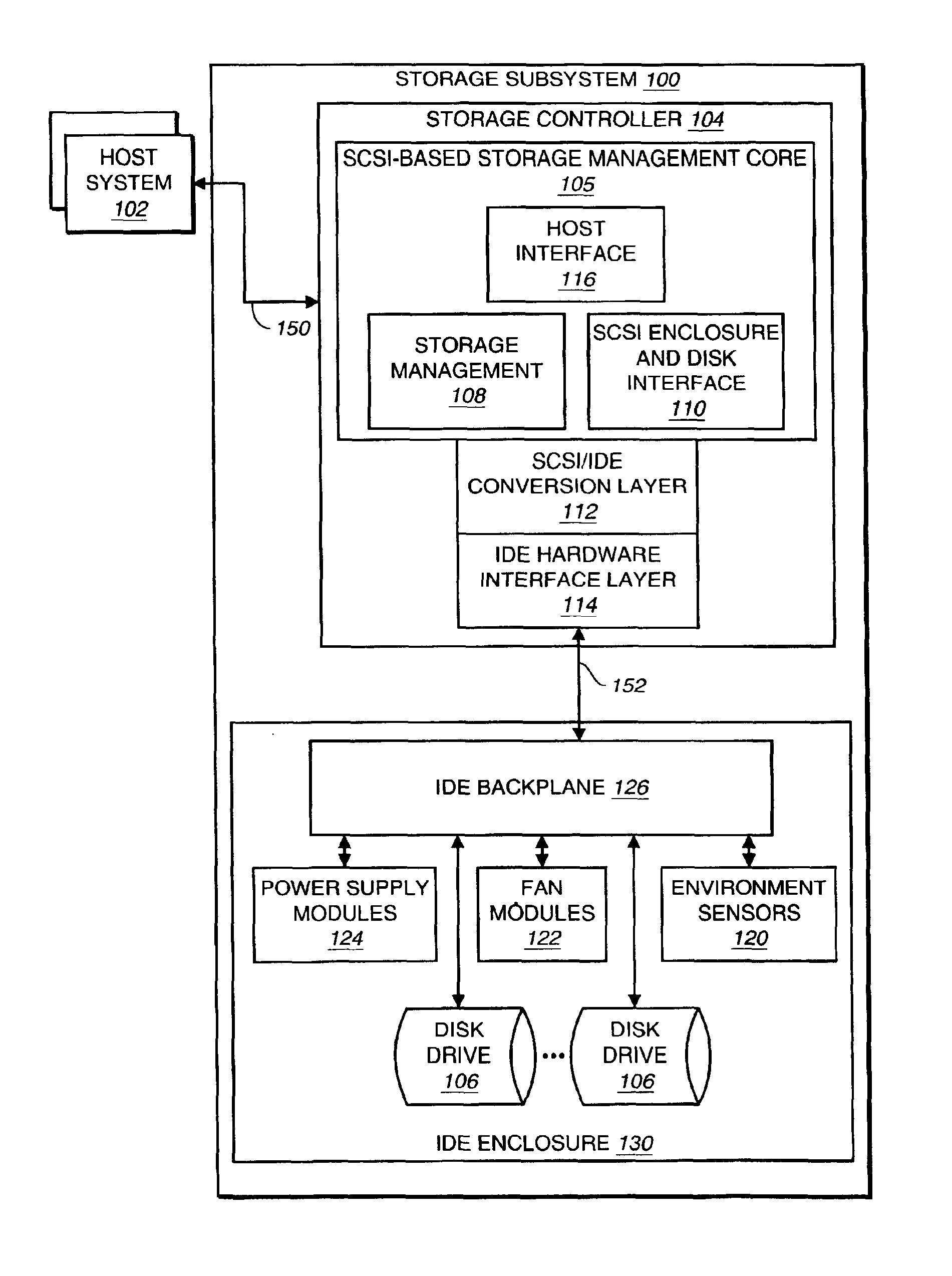

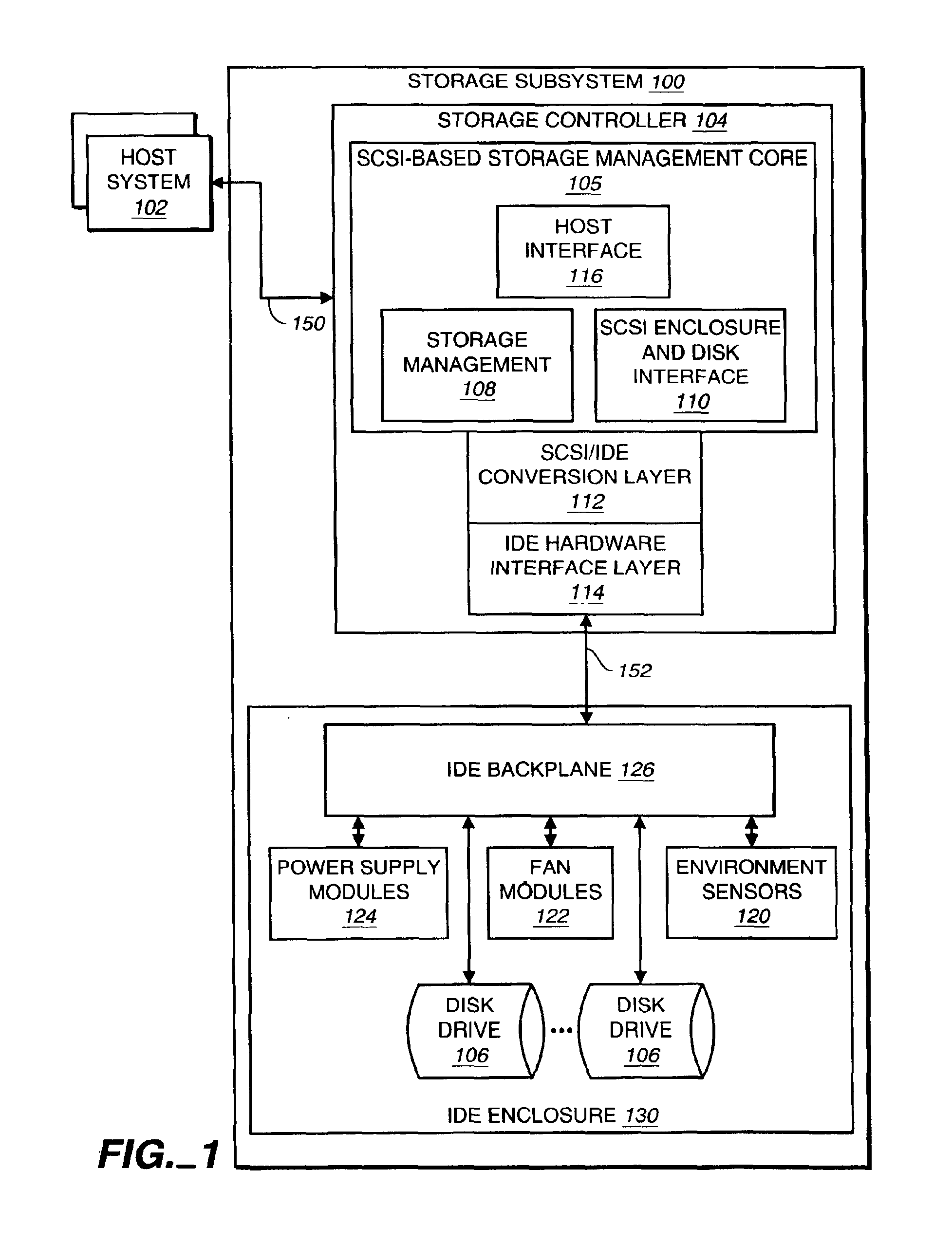

Methods and structure for SCSI/IDE translation for non-SCSI enclosures in a storage subsystem

Methods and associated structure operable within a SCSI-based storage subsystem are provided to adapt the storage controller for use with non-SCSI storage enclosures. A firmware layer of the present invention intercepts SCSI read / write requests and pass-through command blocks (CDBs) generated by the storage management core of the controller and translates the requests and command structures into corresponding command structures for transmission to a non-SCSI storage enclosure. In like manner, the firmware layer of the present invention receives status information from non-SCSI storage enclosures and translates the status information into corresponding SCSI compatible status information. In one exemplary preferred embodiment, a storage subsystem designed for interaction with SCSI storage enclosures may be adapted in accordance with the present invention to utilize lower-cost, IDE compatible storage enclosures.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

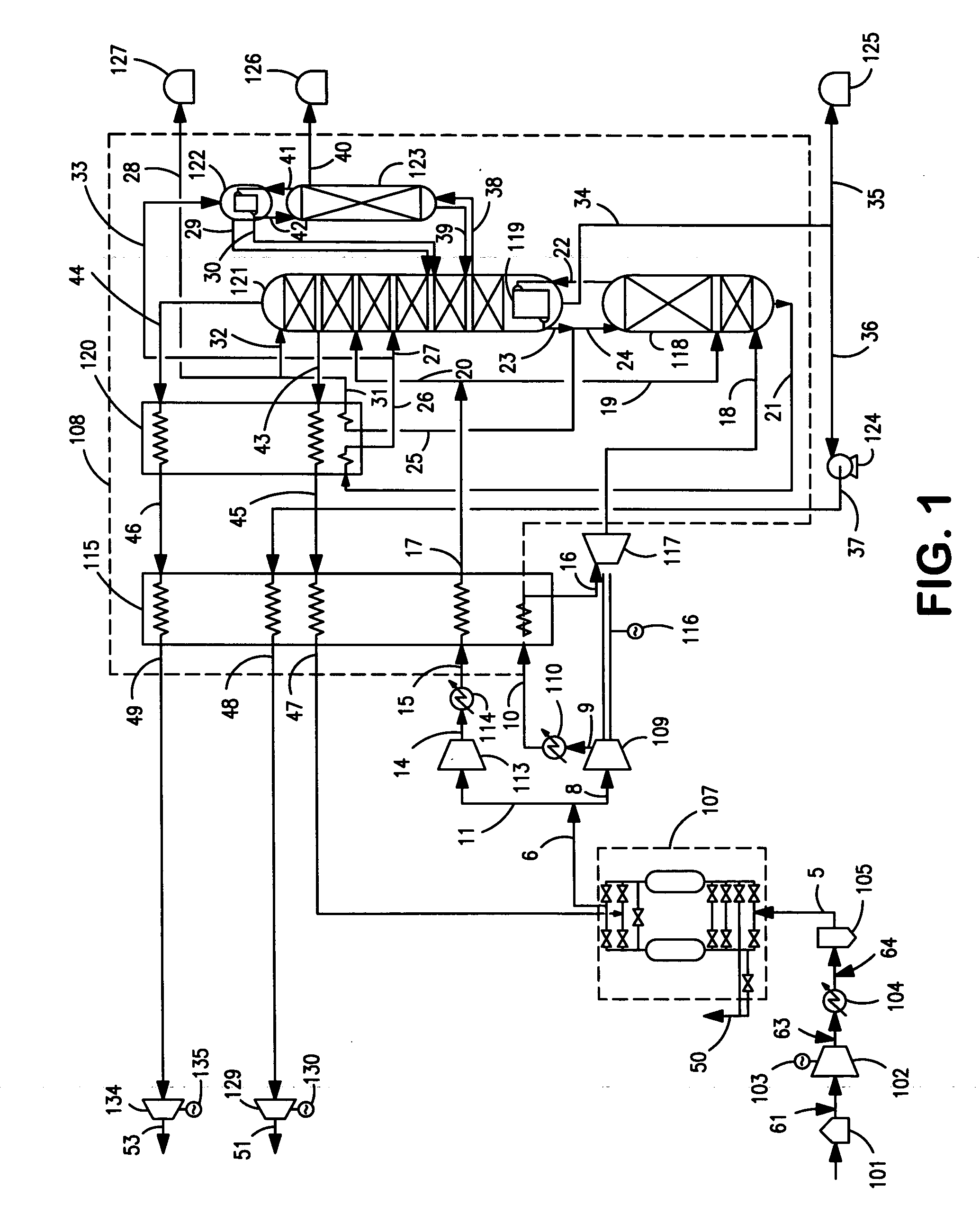

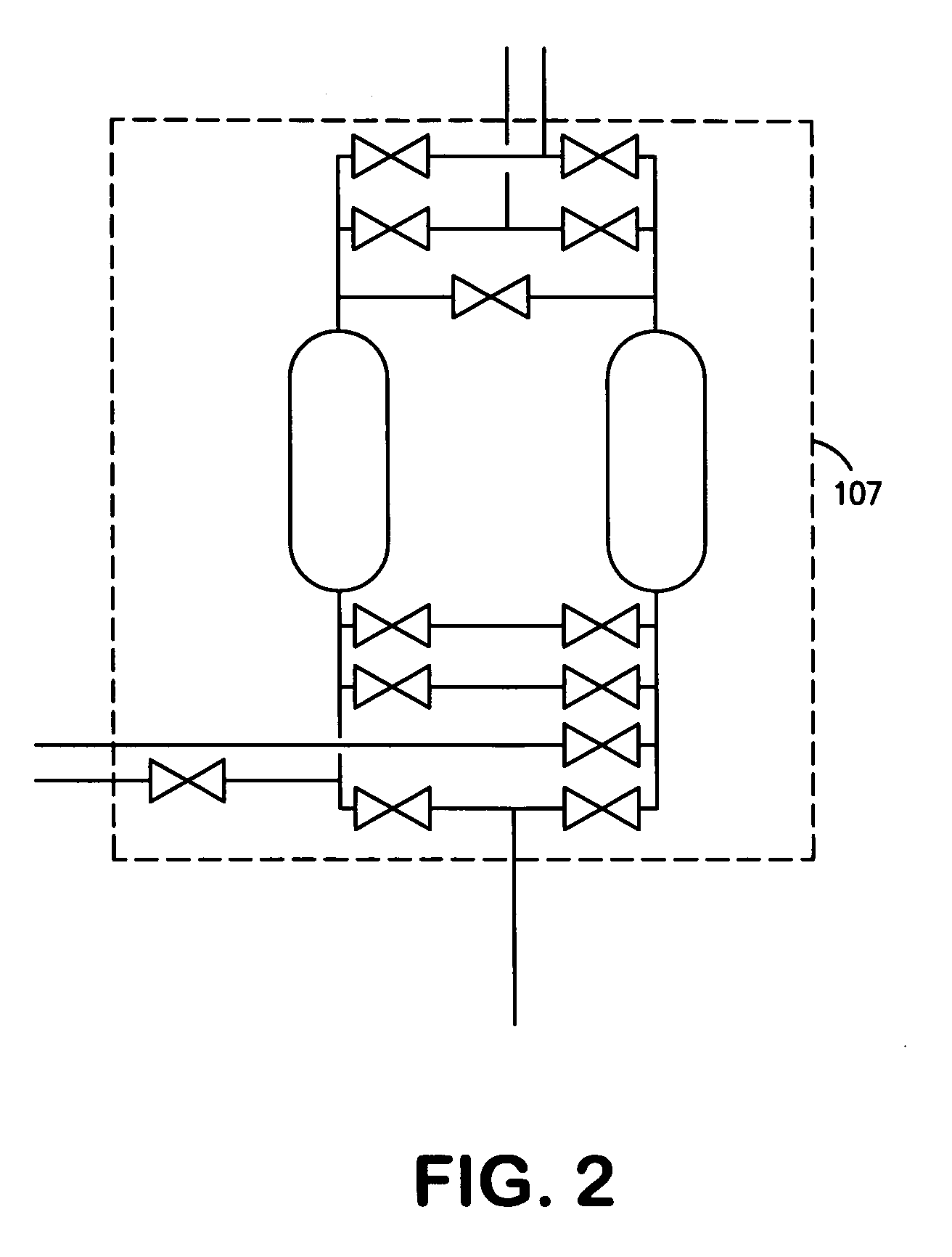

Method for designing a cryogenic air separation plant

A method for designing a cryogenic air separation plant wherein a particular plant which fits into a certain classification is designed by first employing at least one predesigned subsystem for that classification to form a base system and then completing the design by adding to the base system at least one auxiliary subsystem designed specifically for that particular plant.

Owner:PRAXAIR TECH INC

High performance sub-system design and assembly

InactiveUS7378735B2Maximum performanceMinimal costEnergy efficient ICTDigital circuit testingSystems designEngineering

A multiple integrated circuit chip structure provides interchip communication between integrated circuit chips of the structure with no ESD protection circuits and no input / output circuitry. The interchip communication is between internal circuits of the integrated circuit chips. The multiple integrated circuit chip structure has an interchip interface circuit to selectively connect internal circuits of the integrated circuits to test interface circuits having ESD protection circuits and input / output circuitry designed to communicate with external test systems during test and burn-in procedures. The multiple interconnected integrated circuit chip structure has a first integrated circuit chip mounted to one or more second integrated circuit chips to physically and electrically connect the integrated circuit chips to one another. The first integrated circuit chips have interchip interface circuits connected each other to selectively communicate between internal circuits of the each other integrated circuit chips or test interface circuits, connected to the internal circuits of each integrated circuit chip to provide stimulus and response to said internal circuits during testing procedures. A mode selector receives a signal external to the chip to determine whether the communication is to be with one of the other connected integrated circuit chips or in single chip mode, such as with the test interface circuits. ESD protection is added to the mode selector circuitry.

Owner:QUALCOMM INC

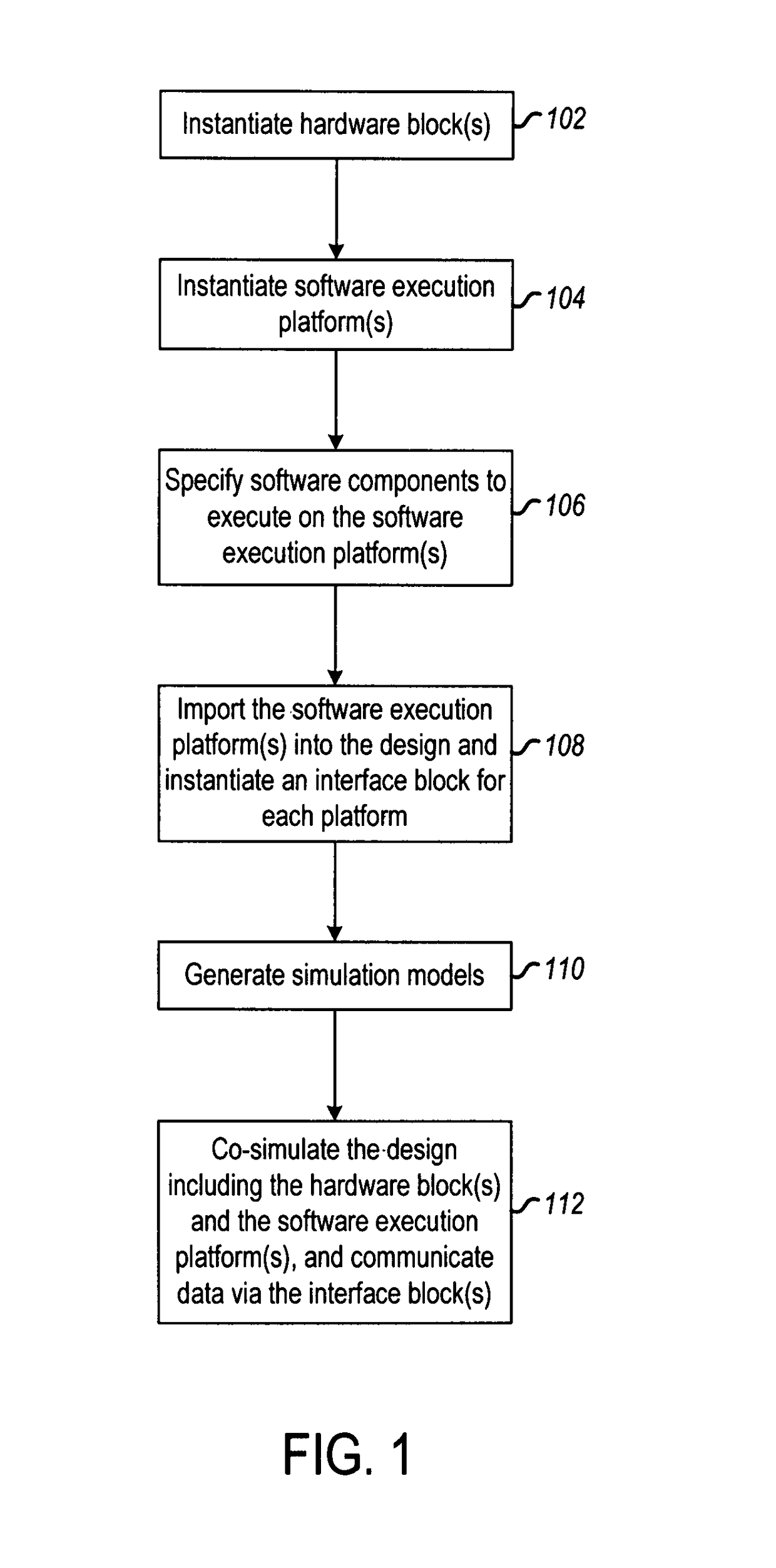

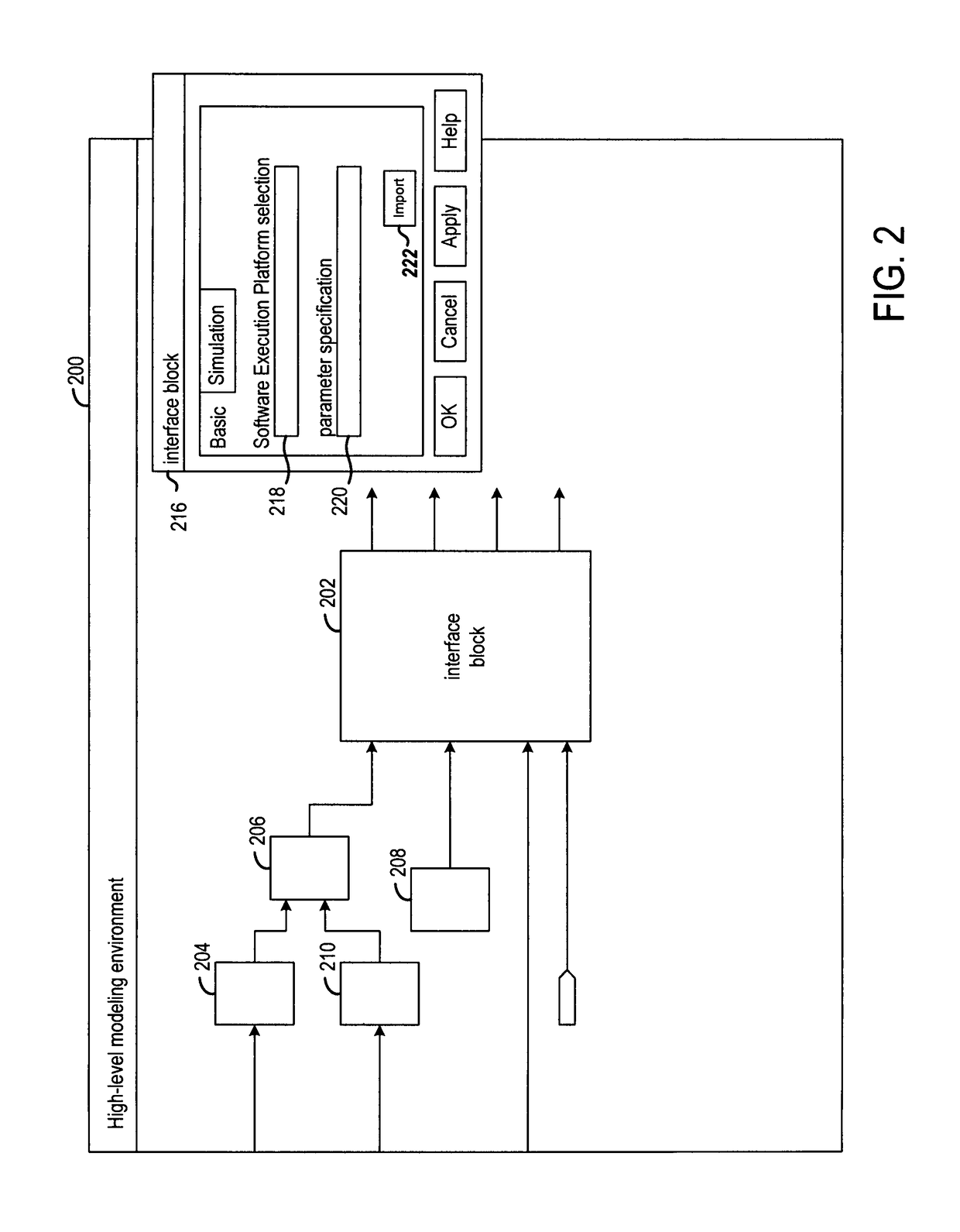

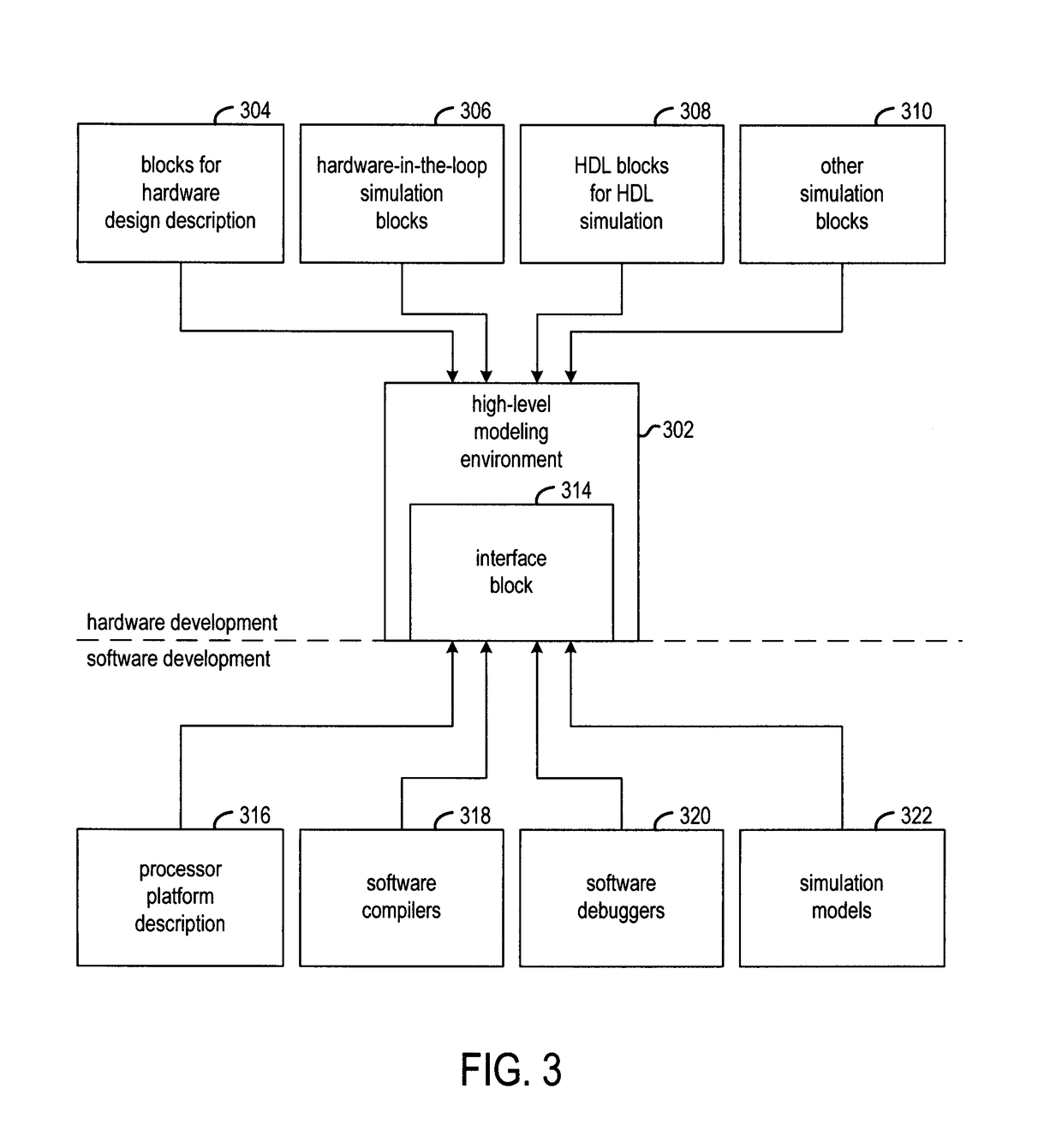

System-level hardware and software development and co-simulation system

ActiveUS8473269B1CAD circuit designSpecial data processing applicationsComputer hardwareSoftware development process

Various approaches for co-simulating an electronic system design are described. In one approach, a hardware design function block in the design is instantiated, along with a specification of a software execution platform including external ports and software to execute on the platform. In response to a user instruction to import the software execution platform into the design, a software execution platform interface block is automatically instantiated. A first simulation model is generated from the hardware design function block and the software execution platform interface block and a second simulation model is generated from the software execution platform. The design is co-simulated using the first and second simulation models. Data is communicated between the first simulation model and the second simulation model via the interface block.

Owner:XILINX INC

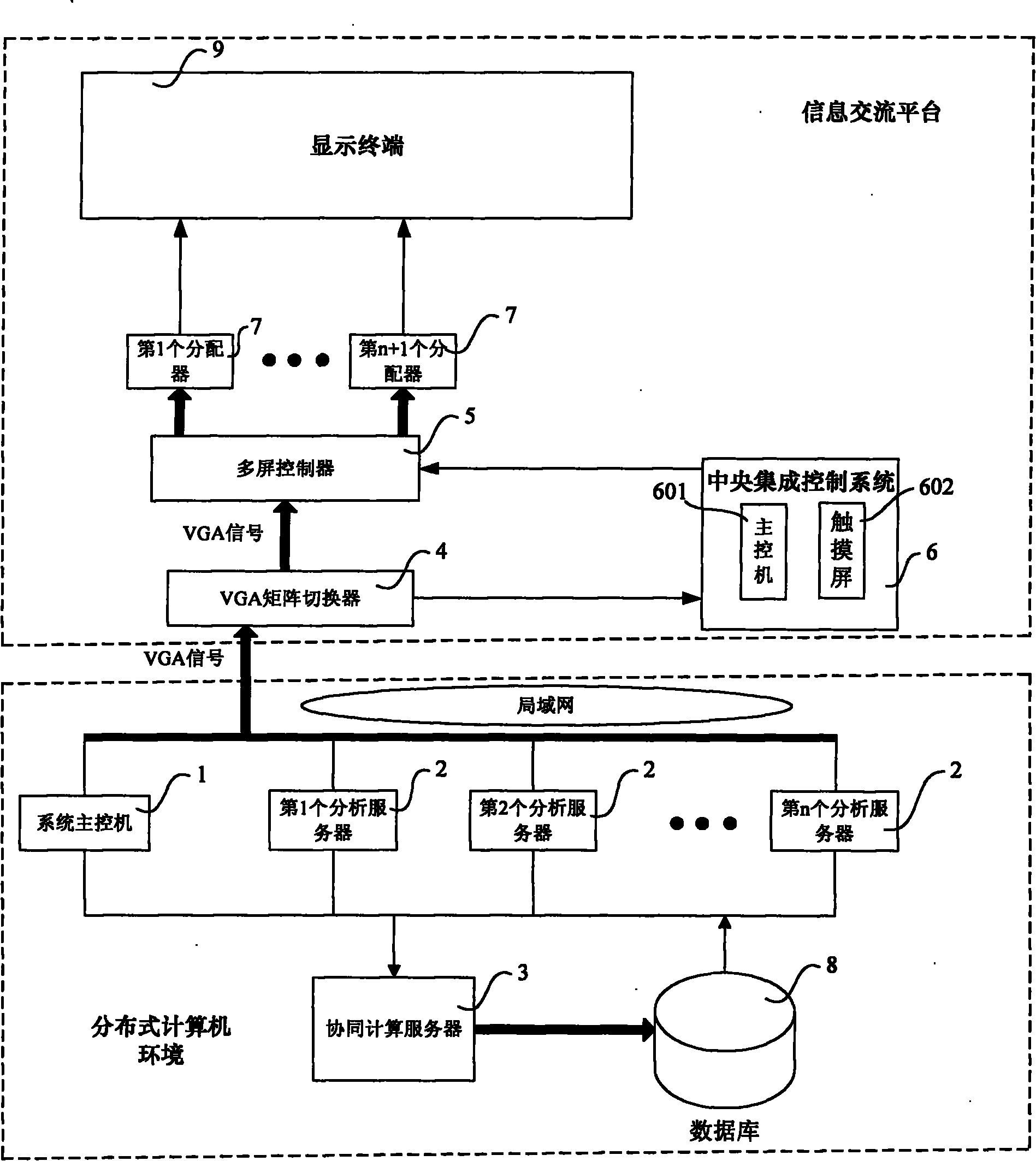

Multidisciplinary collaborative-design information communication platform

InactiveCN101854350AAchieve independenceImprove computing efficiencyTransmissionSpecial data processing applicationsSystems designControl system

The invention discloses a multidisciplinary collaborative-design information communication platform, which comprises a system main controller, n analysis servers, a collaborative computation server, a VGA matrix switcher, a multi-screen controller, a central integrated control system, n+1 distributors, a display terminal and a database; and the system main controller and the analysis servers carry out the system design to be finally displayed by a display terminal. Each sub-system design is independent, the collaborative computation server is used for adequately improving the computation efficiency, and the user can instantly monitor the design and optimization process of each sub-system, so the coordination of the sub-systems is convenient, and the design efficiency is improved; and the communication function of the central integration control system realizes the long-distance and isomerism design environment.

Owner:BEIHANG UNIV

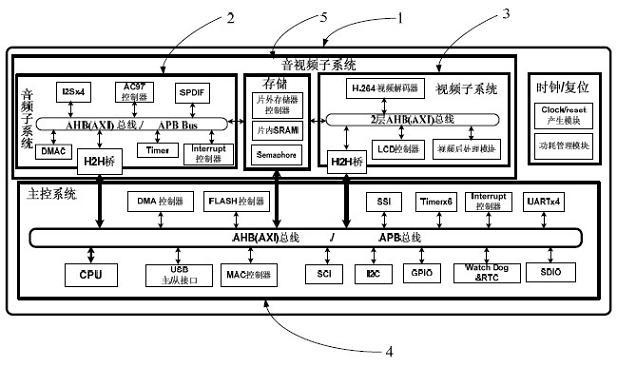

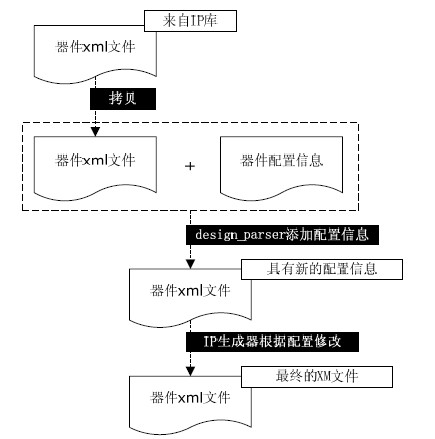

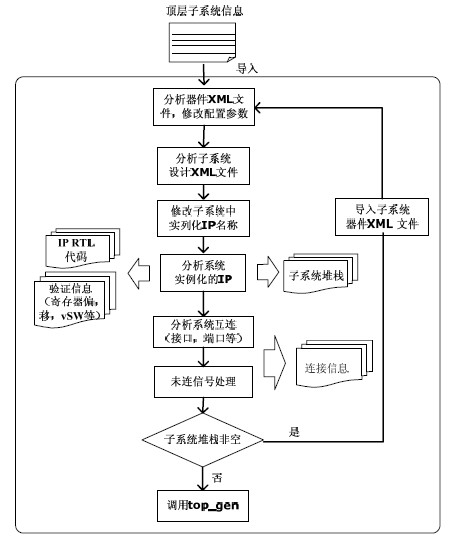

Subsystem integration method and subsystem integration system for integration design of system-on-chip

ActiveCN102012954AImprove compatibilityIncrease flexibilitySpecial data processing applicationsSubsystem designScripting language

The invention discloses a subsystem integration method for the integration design of a system-on-chip, which comprises the following steps of: 1) packaging a subsystem by adopting an IP-XACT standard, wherein the subsystem comprises a subsystem device extensible markup language (XML) file, a subsystem design XML file and a subsystem generator; 2) writing a subsystem XML file analysis tool by adopting a scripting language, analyzing instantiated devices in the subsystem, simultaneously iteratively analyzing other instantiated subsystems in the subsystem, making directories for each instantiated device, transferring working directories to the corresponding directories, calling a device generator to generate device register-transfer-level (RTL) codes and a test stimulus template, and generating a subsystem top-level code after finishing the iterative analyzing of the subsystem; 3) writing a code modifying tool by adopting the scripting language; and 4) writing a subsystem top level RTL code generation tool by adopting the scripting language. The invention also provides a subsystem integration system. The method and the system ensure high configurability, higher portability and high flexibility, and improve the integration efficiency.

Owner:C SKY MICROSYST CO LTD

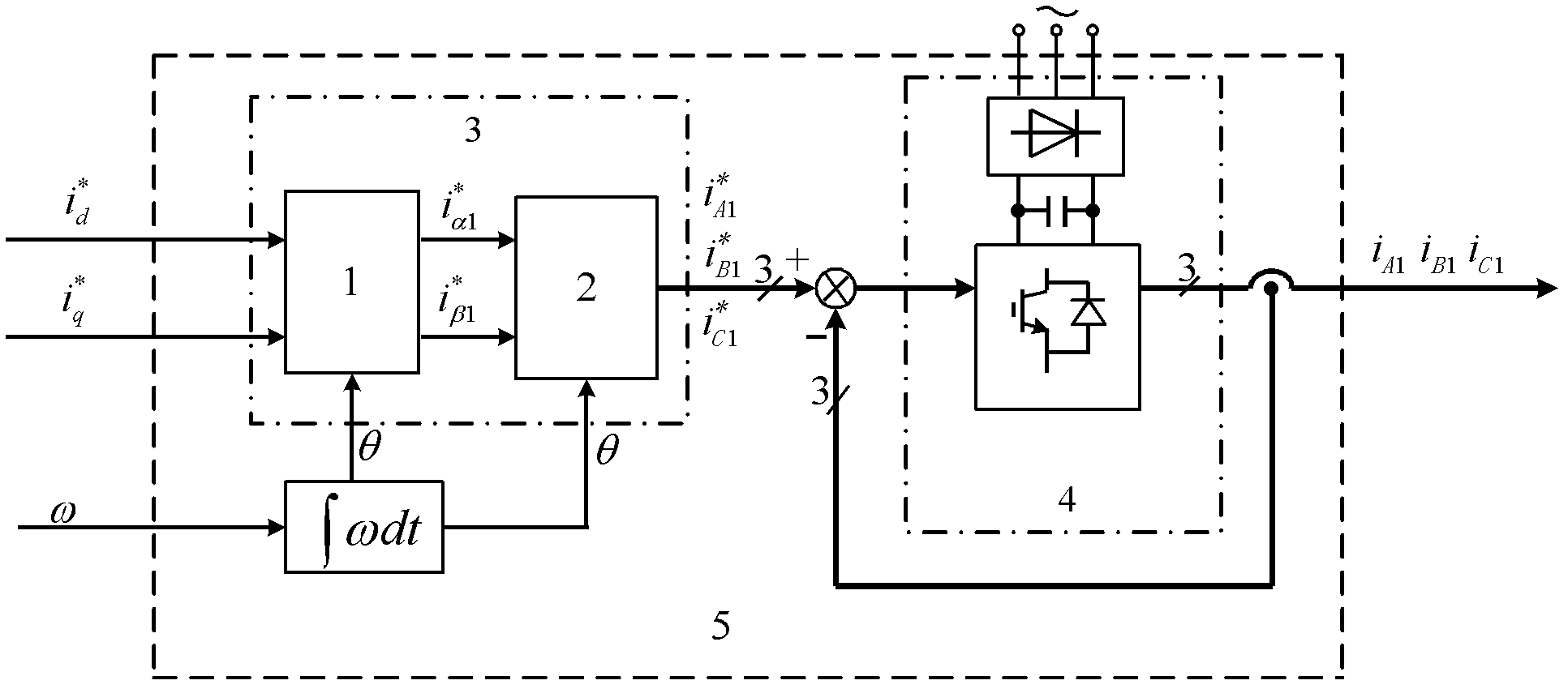

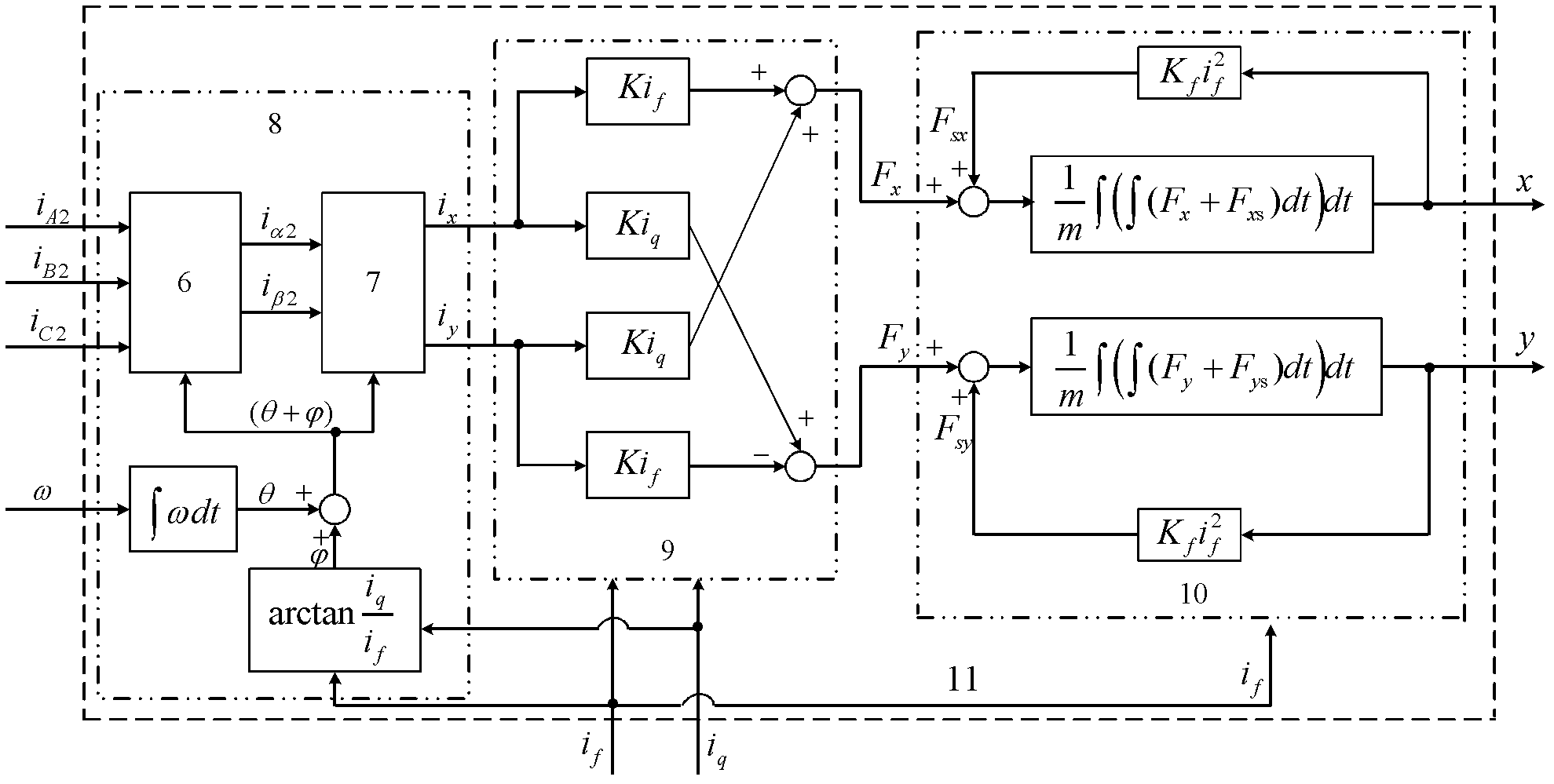

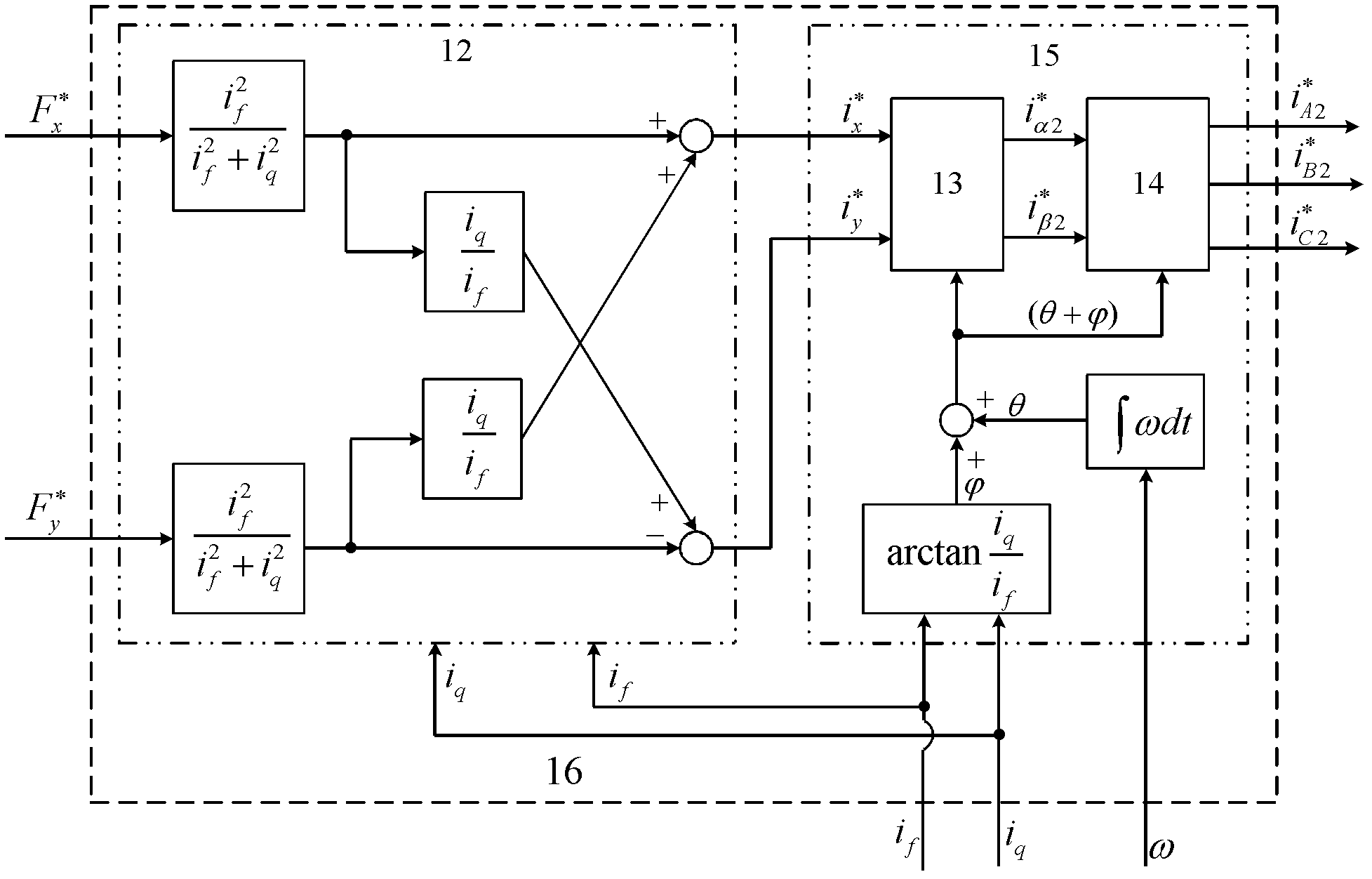

Decoupling method and control device for suspension force feed-forward compensation of bearingless permanent magnet synchronous motor

InactiveCN102299680AAchieving complete dynamic decouplingEasy to decoupleElectronic commutation motor controlVector control systemsHysteresisPhase currents

The invention discloses a suspension force feedforward compensation decoupling method and a control device of a bearingless permanent magnet synchronous motor. During control, it includes an expanded current hysteresis PWM inverter configured to supply power to the torque winding of the motor; the structure is expanded The coupled levitation force model; construct an extended feedforward compensation decoupling controller; the extended feedforward compensation decoupling controller takes two levitation force components, torque current components, permanent magnet equivalent excitation current and rotational speed as its input , the reference value of the three-phase current of the suspension winding is output, and the actual three-phase current is output after the first current hysteresis PWM inverter, which is used as the input of the extended coupling suspension force model, and the extended coupling suspension force model outputs the rotor displacement; finally, the two A decoupled suspension force subsystem and speed subsystem design a closed-loop regulator. By using the invention to control the bearingless permanent magnet synchronous motor, the stable suspension of the controlled motor can be realized, and the system has fast response, simple algorithm and excellent performance.

Owner:NANJING COLLEGE OF INFORMATION TECH

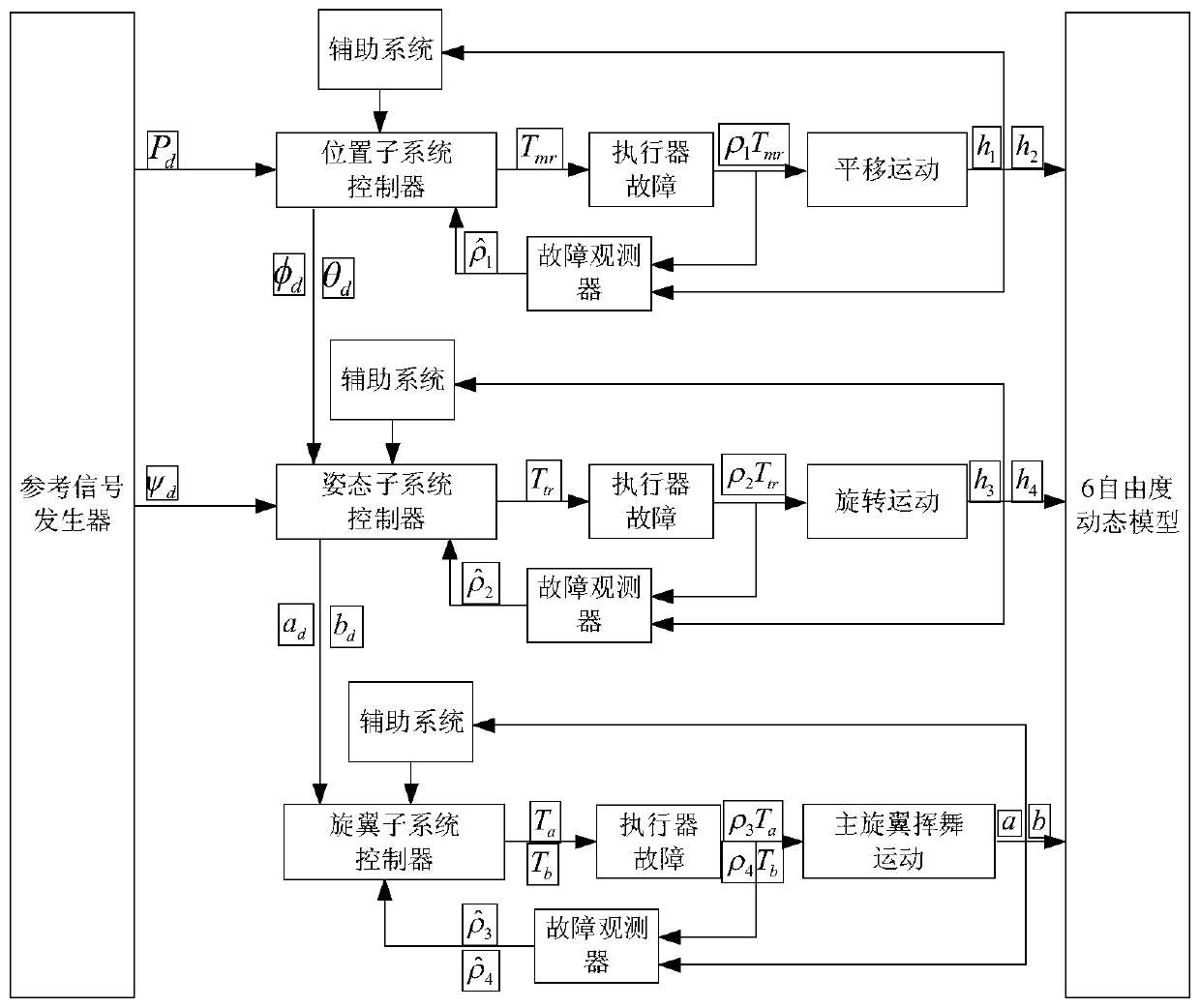

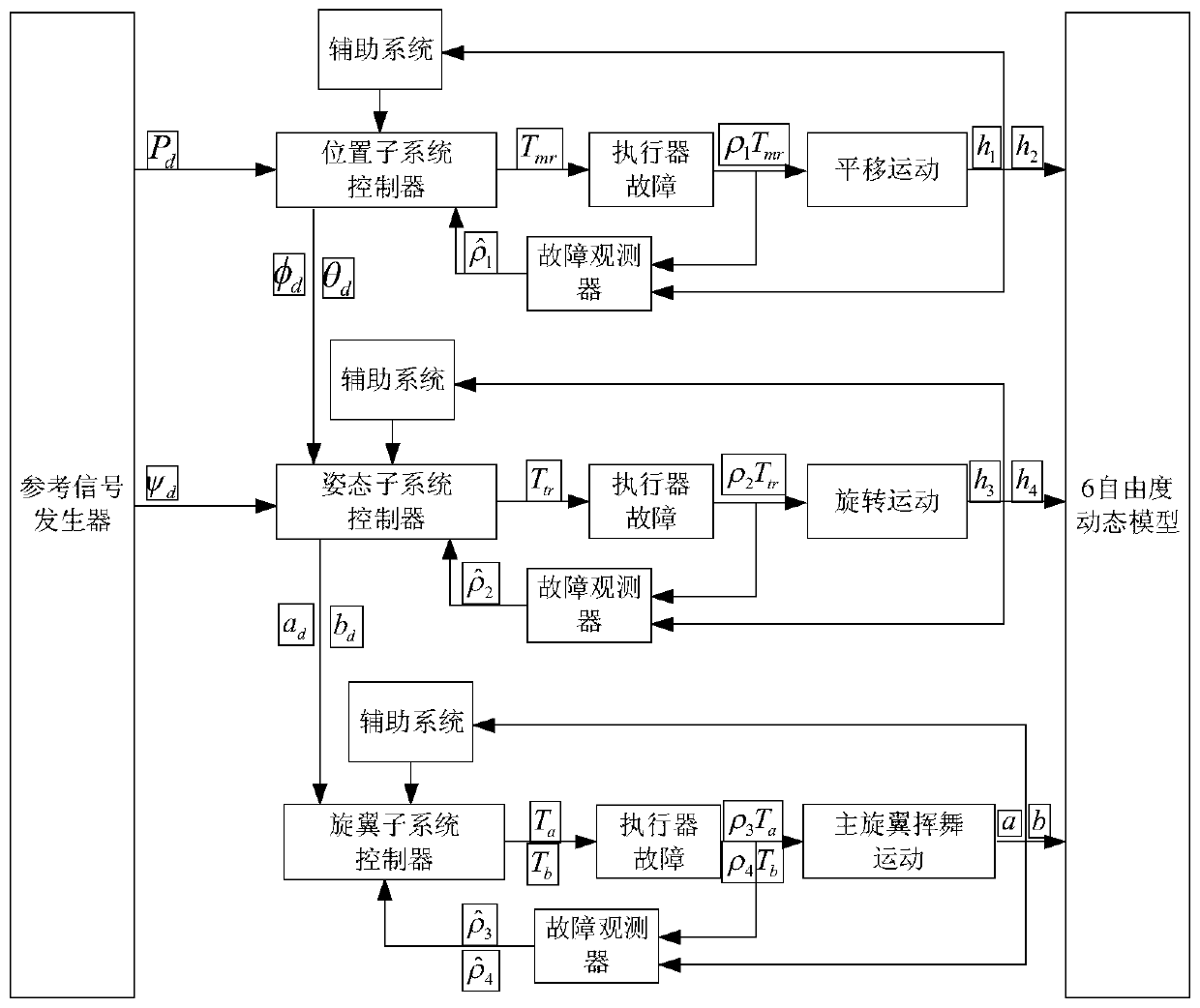

Robust fault-tolerant tracing method of unmanned helicopter

ActiveCN109991991AAttitude controlPosition/course control in three dimensionsState observerNon linear dynamic

The invention discloses a robust fault-tolerant tracing method of an unmanned helicopter. The robust fault-tolerant tracing method comprises the steps of building a six-freedom non-linear dynamic model, comprising main rotor dynamic waving and executor fault, of the unmanned helicopter; dividing a unmanned helicopter system into a position sub-system, a gesture sub-system and a waving sub-system,and designing an auxiliary state observer for each sub-system; and building a robust fault-tolerant controller to prevent influence of the fault on the system according to the designed auxiliary stateobservers of the three sub-systems. Stability can be maintained under considering influence of rotor dynamic waving and executor fault, and meanwhile, an expected reference track is traced.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Ultra-scalable supercomputer based on MPU architecture

InactiveUS8159973B2High-performance and sustained computing resourcesCostData switching by path configurationMultiple digital computer combinationsSupercomputerInterconnect topology

Owner:SHANGHAI REDNEURONS

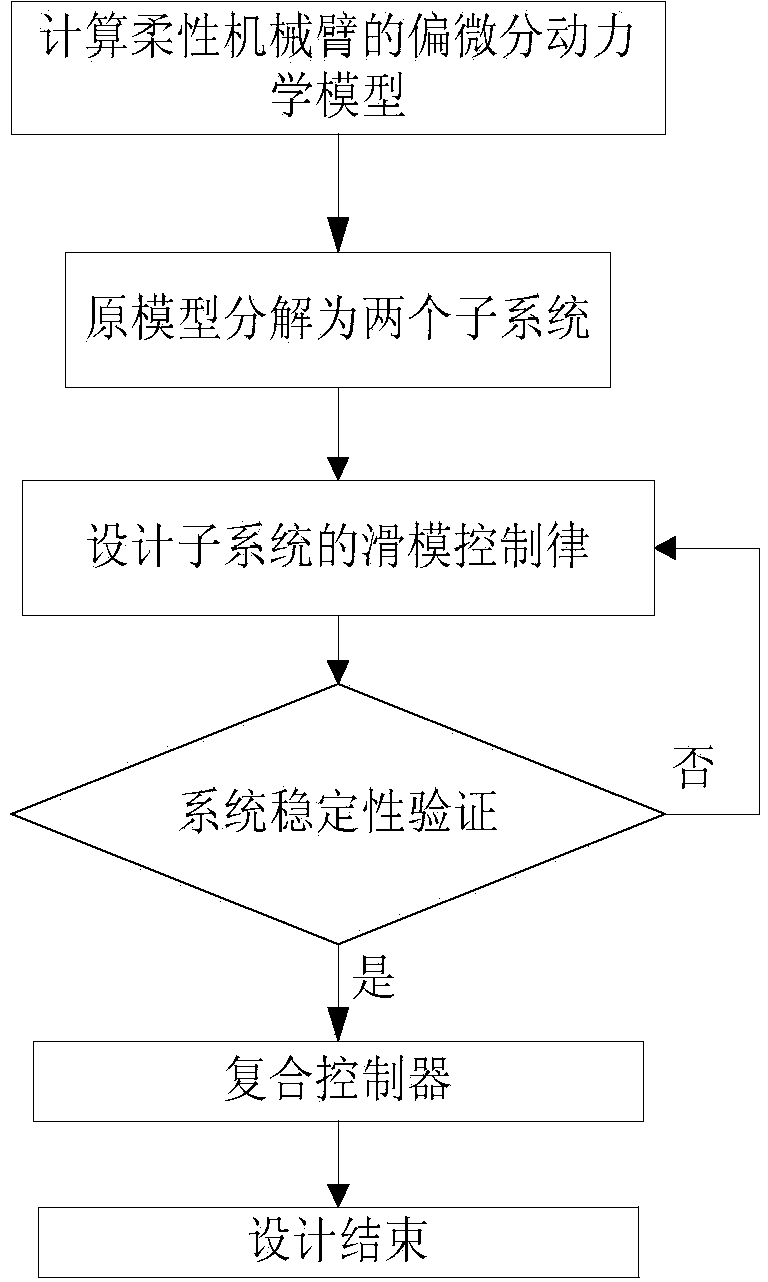

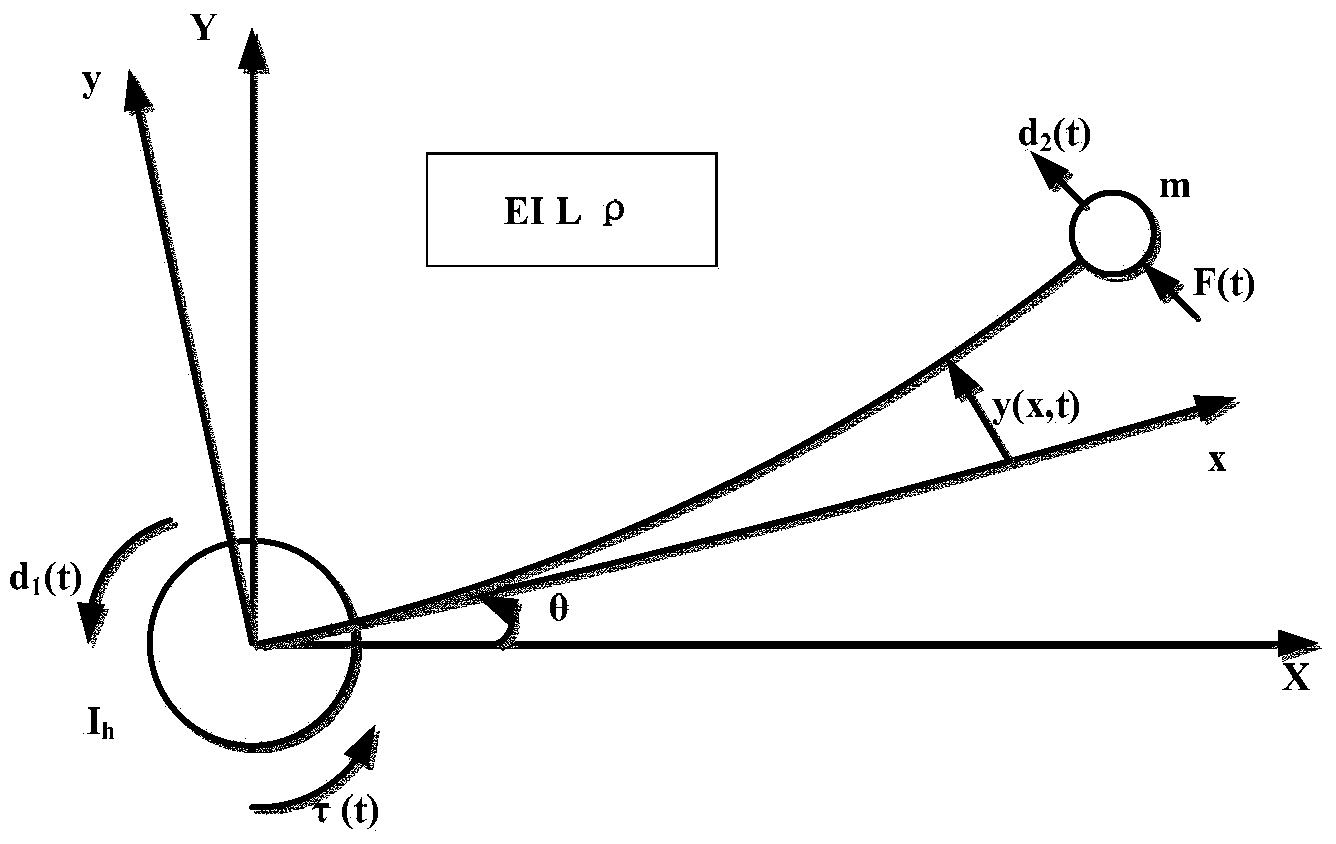

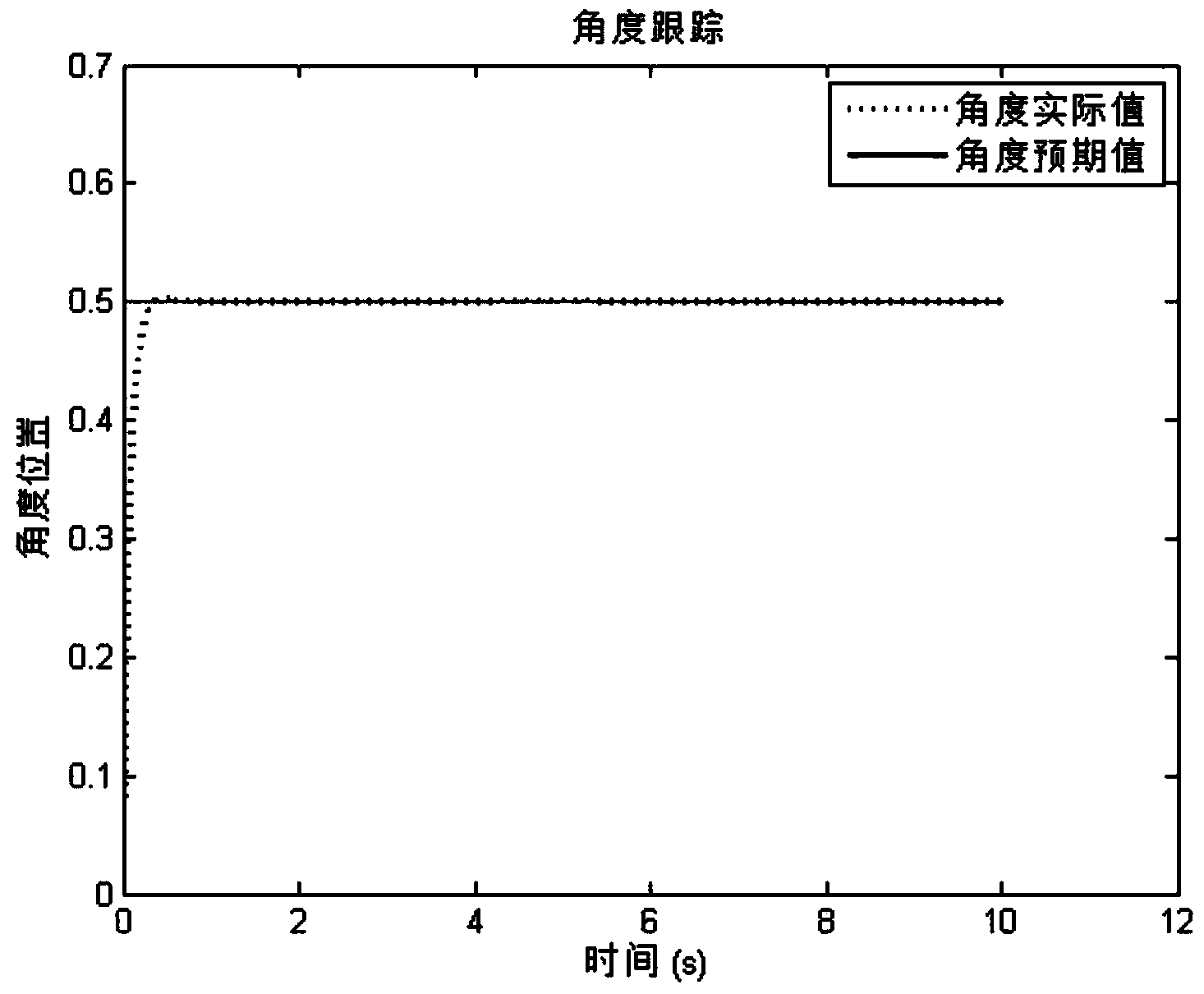

Flexible mechanical arm sliding-mode control designing method based on singular perturbation theory

ActiveCN104035337AWith anti-interference abilityReduce complexityAdaptive controlDesign controlPartial differential equation

The invention relates to a flexible mechanical arm sliding-mode control designing method based on a singular perturbation theory. The method includes four steps that (1) dynamics modeling of a flexible mechanical arm is performed; (2) partial differential equation (PDE) model decomposition is performed; (3) a control law is designed; (4) designing is finished. According to the flexible mechanical arm sliding-mode control designing method based on the singular perturbation theory, firstly, a Hamilton principle is utilized, and a PDE model of a whole system is determined; the original PDE model is decomposed into a concentrating slow subsystem which represents whole rigidity movement and a quick subsystem which describes system vibration by means of the singular perturbation theory; then a sliding-mode control law is designed by respectively aiming at the quick and slow subsystems, the designed control law is subjected to convergence analysis by the aid of a lyapunov function, and reasonability and stability of the control law are verified. Finally, a compound control law is obtained according to the singular perturbation theory.

Owner:GUODIAN SCI & TECH RES INST

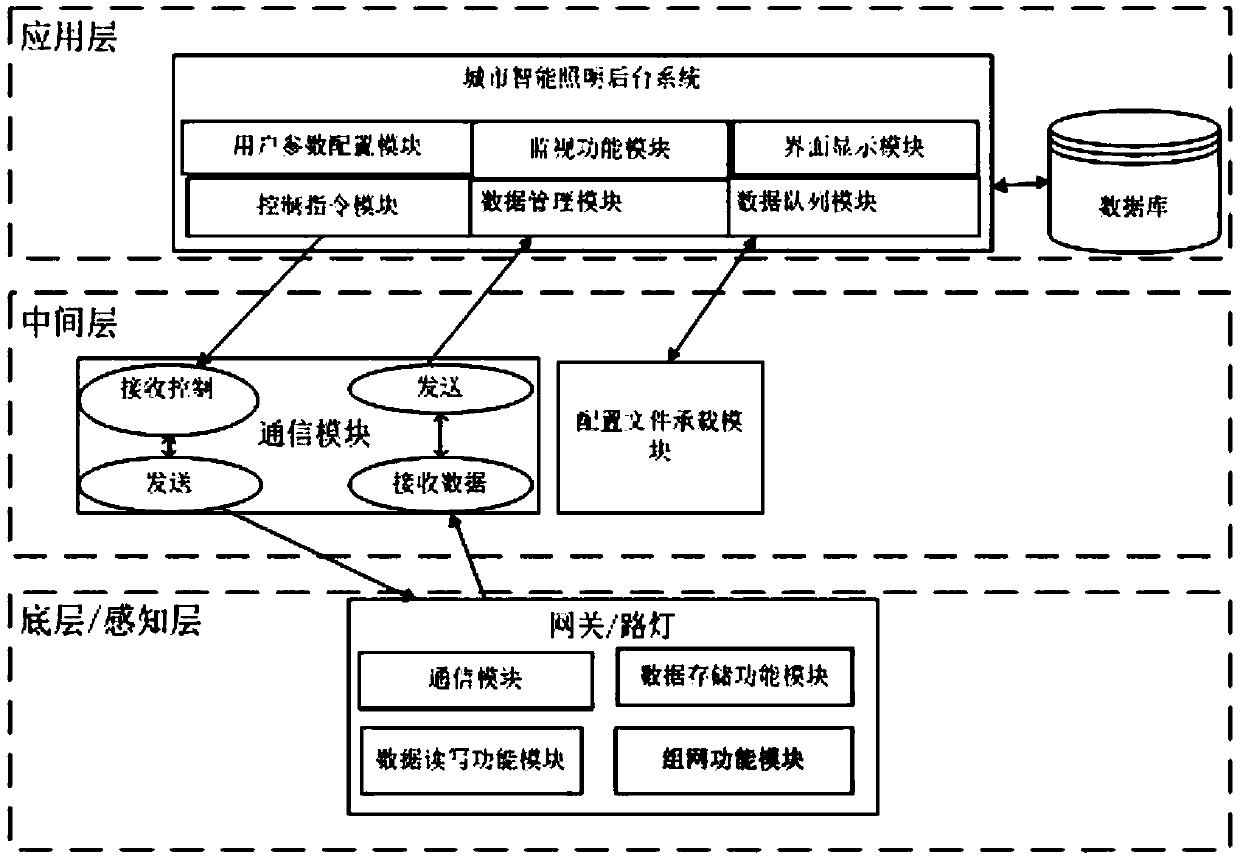

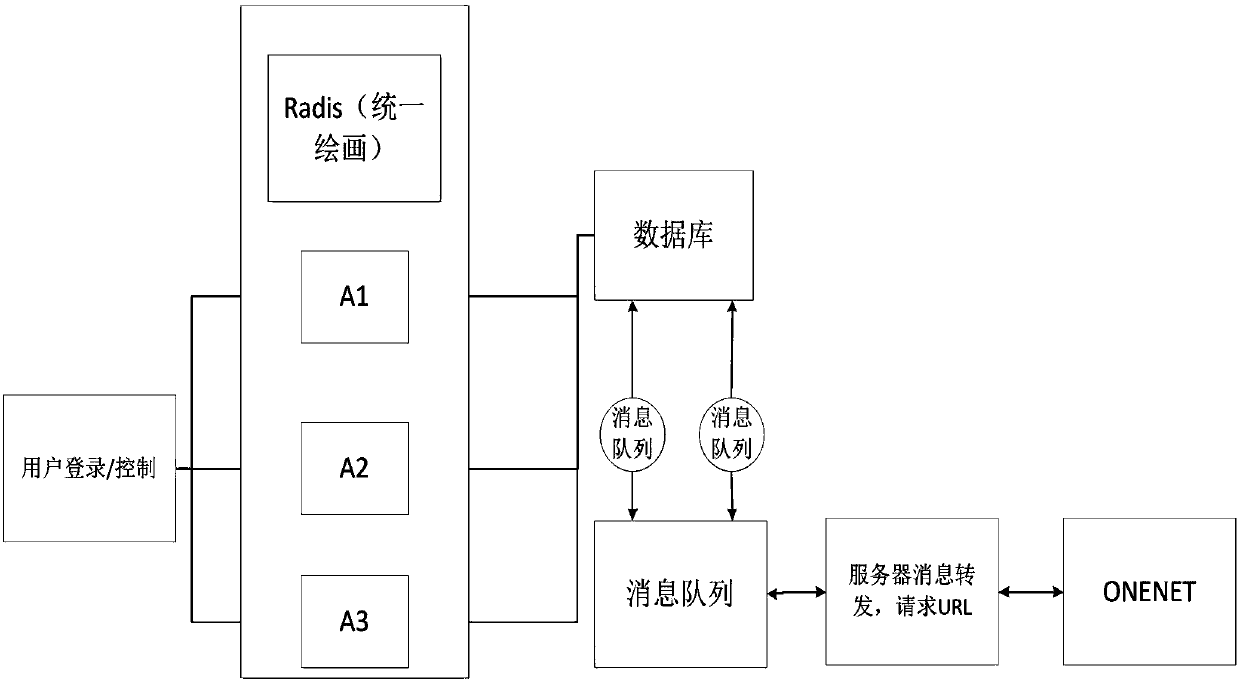

Intelligent lighting management and control system realization method

InactiveCN107800796AGuaranteed Access QuantityReliable transmissionElectric light circuit arrangementEnergy saving control techniquesIntelligent lightingSubsystem design

The invention provides an intelligent lighting management and control system realization method and belongs to the field of Internet of things application. The system is equipped with three layers ofarchitecture comprising terminal nodes in a sensing layer, a OneNET cloud platform in a network layer, and a device service subsystem and a user service subsystem in an application layer. In the sensing layer, the terminal nodes aggregate bottom layer information to a gateway device through a Zigbee protocol and the gateway device accesses a network through an upper computer. In the network layer,the OneNET cloud platform provides an ID number for the gateway device and the gateway device is connected with the OneNET through a TCP protocol family. In the application layer, for the particularity of a node communication mode, the device service subsystem designs a DSS communication protocol and operation process in order to analyze node information aggregated to the gateway, the problems such as service object identification and uplink and downlink data correspondence are solved, a function system for communicating with sensors, carrying out control and management, storing information and supporting operation of the user service subsystem is realized, and a user can monitor the operation condition of an urban lighting system in real time.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

High performance sub-system design and assembly

InactiveUS20090134391A1Maximum performanceMinimal costDigital circuit testingSemiconductor/solid-state device testing/measurementSystems designPattern selection

A multiple integrated circuit chip structure provides interchip communication between integrated circuit chips of the structure with no ESD protection circuits and no input / output circuitry. The interchip communication is between internal circuits of the integrated circuit chips. The multiple integrated circuit chip structure has an interchip interface circuit to selectively connect internal circuits of the integrated circuits to test interface circuits having ESD protection circuits and input / output circuitry designed to communicate with external test systems during test and burn-in procedures. The multiple interconnected integrated circuit chip structure has a first integrated circuit chip mounted to one or more second integrated circuit chips to physically and electrically connect the integrated circuit chips to one another. The first integrated circuit chips have interchip interface circuits connected each other to selectively communicate between internal circuits of the each other integrated circuit chips or test interface circuits, connected to the internal circuits of each integrated circuit chip to provide stimulus and response to said internal circuits during testing procedures. A mode selector receives a signal external to the chip to determine whether the communication is to be with one of the other connected integrated circuit chips or in single chip mode, such as with the test interface circuits. ESD protection is added to the mode selector circuitry.

Owner:QUALCOMM INC

High performance sub-system design and assembly

InactiveUS20090114914A1Maximum performanceMinimal costDigital circuit testingSemiconductor/solid-state device testing/measurementSystems designPattern selection

A multiple integrated circuit chip structure provides interchip communication between integrated circuit chips of the structure with no ESD protection circuits and no input / output circuitry. The interchip communication is between internal circuits of the integrated circuit chips. The multiple integrated circuit chip structure has an interchip interface circuit to selectively connect internal circuits of the integrated circuits to test interface circuits having ESD protection circuits and input / output circuitry designed to communicate with external test systems during test and burn-in procedures. The multiple interconnected integrated circuit chip structure has a first integrated circuit chip mounted to one or more second integrated circuit chips to physically and electrically connect the integrated circuit chips to one another. The first integrated circuit chips have interchip interface circuits connected each other to selectively communicate between internal circuits of the each other integrated circuit chips or test interface circuits, connected to the internal circuits of each integrated circuit chip to provide stimulus and response to said internal circuits during testing procedures. A mode selector receives a signal external to the chip to determine whether the communication is to be with one of the other connected integrated circuit chips or in single chip mode, such as with the test interface circuits. ESD protection is added to the mode selector circuitry.

Owner:QUALCOMM INC

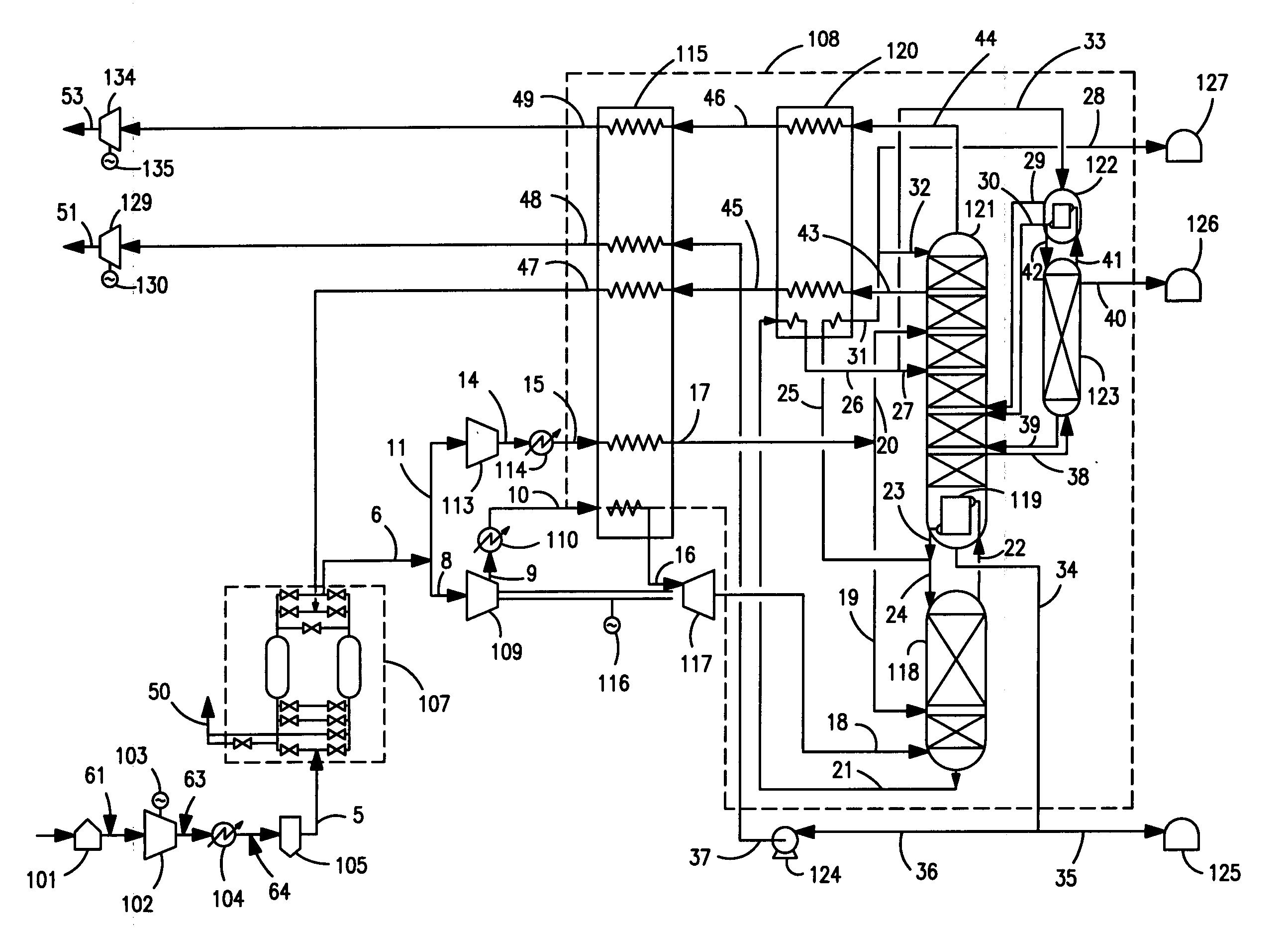

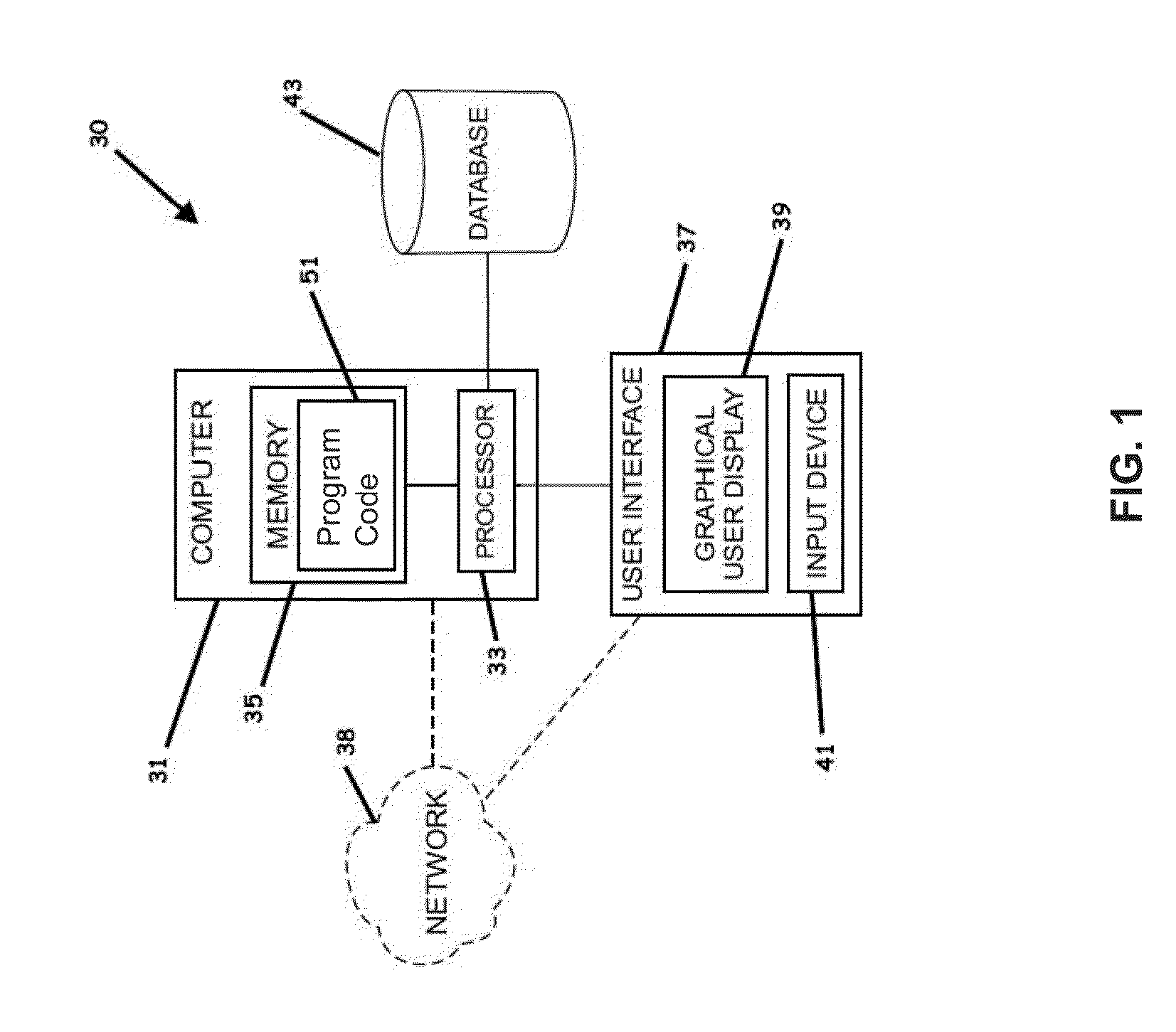

Methods For Simultaneous Process and Utility Systems Synthesis in Partially and Fully Decentralized Environments

Methods of providing a combined synthesis of cost-effective heat and power (CHP) utility systems and the key process systems are provided. An exemplary method includes process steps for identifying the best key subsystem design and operating conditions for both the process and the utility systems. The method can include the step of determining an optimal allocation of steam and power between both process and utility systems for one or more industrial process facilities in both partially and totally decentralized environments. This can include defining rigorously bounded decision variables as model input data, processing the model input data by a combined heat and power utility and process subsystem mathematical program model, and determining a plurality of at least substantially optimal process and utility subsystem conditions.

Owner:SAUDI ARABIAN OIL CO

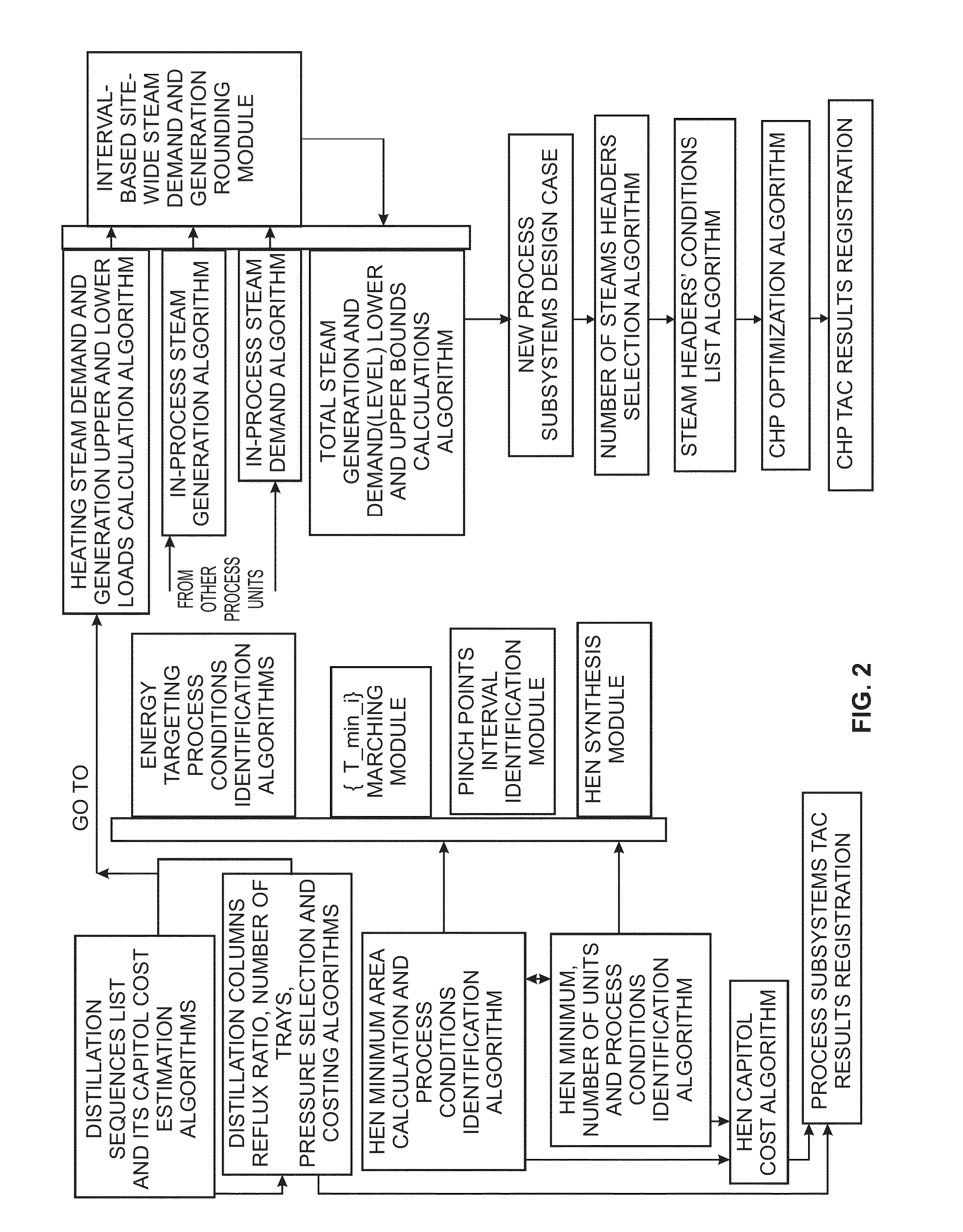

Adaptive fault tolerant control method considering input constraints of actuator for hypersonic flight vehicle

ActiveCN108919651ATroubleshooting Input Constraint PropertiesHigh precisionAdaptive controlBacksteppingLevel flight

The invention relates to an adaptive fault tolerant control method considering input constraints of an actuator for a hypersonic flight vehicle. The method comprises the following steps of firstly, establishing a standard longitudinal dynamics model of the hypersonic flight vehicle and decomposing the model into speed, height and attitude subsystems; secondly, establishing an air vehicle actuatorfault model with generality, and compensating input constraint characteristics of the actuator by constructing a smoothing function; and thirdly, respectively designing an adaptive compensation controller and an adaptive law for three subsystems through a dynamic inverse method, a backstepping method and a sliding mode control method. According to the method, the stability of longitudinal model parameters such as air vehicle speed, height and the like is guaranteed in a level flight working state when the hypersonic flight vehicle with the input constraint characteristics of the actuator has an actuator fault, and the method has the advantages of strong fault-tolerant capability and robustness to external disturbance and the like.

Owner:BEIHANG UNIV

Modular blade enclosure power subsystem disign

InactiveUS20080309160A1Coupling device connectionsDc network circuit arrangementsModularitySubsystem design

An apparatus for distributing power to computing modules in a multi module enclosure. The apparatus includes at least one power input module, a plurality of power input cables, a plurality of power conversion modules, and a plurality of computing modules. The at least one power input module is modularly arranged within the multi module enclosure. The plurality of power input cables are electrically connected to and provide power input to the at least one power input module. The plurality of power conversion modules are electrically connected to power outputs of the at least one power input module and are modularly arranged within the multi module enclosure. The plurality of computing modules are electrically connected to power outputs of the power conversion modules and are arranged within the multi module enclosure.

Owner:HEWLETT PACKARD DEV CO LP

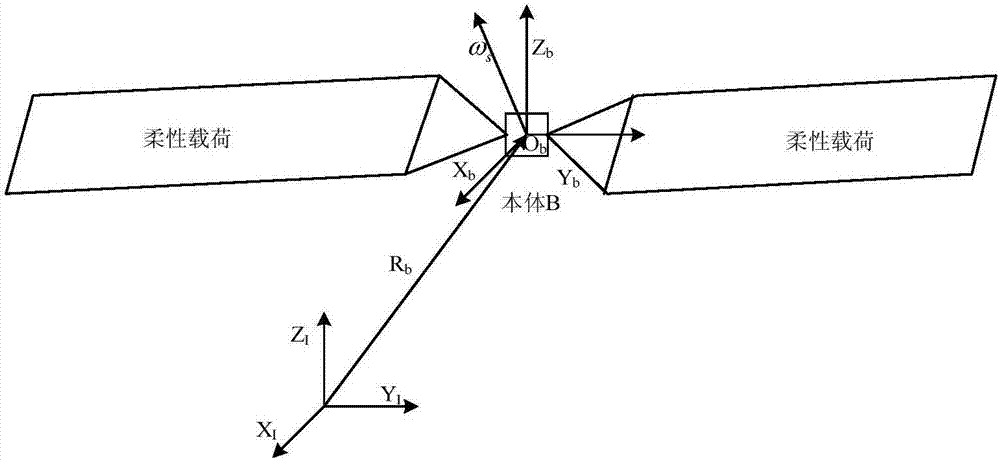

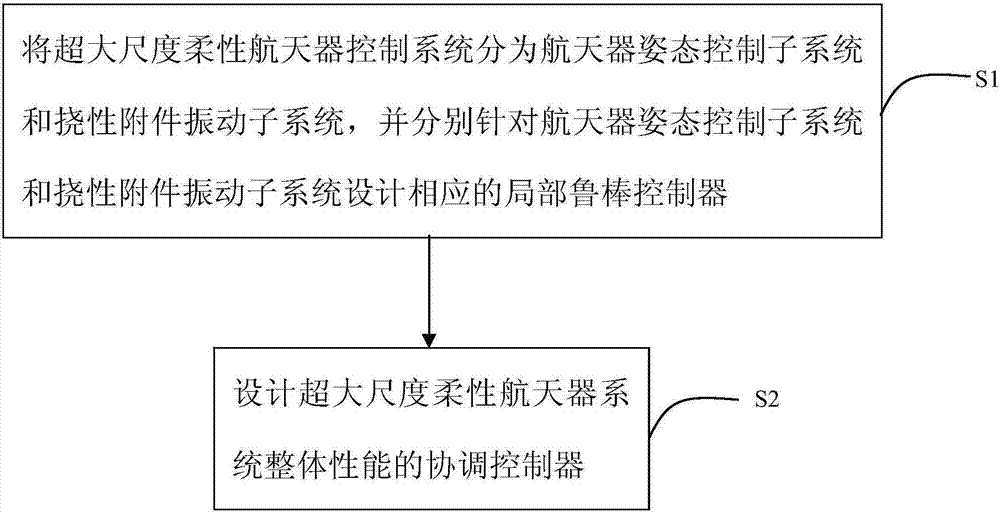

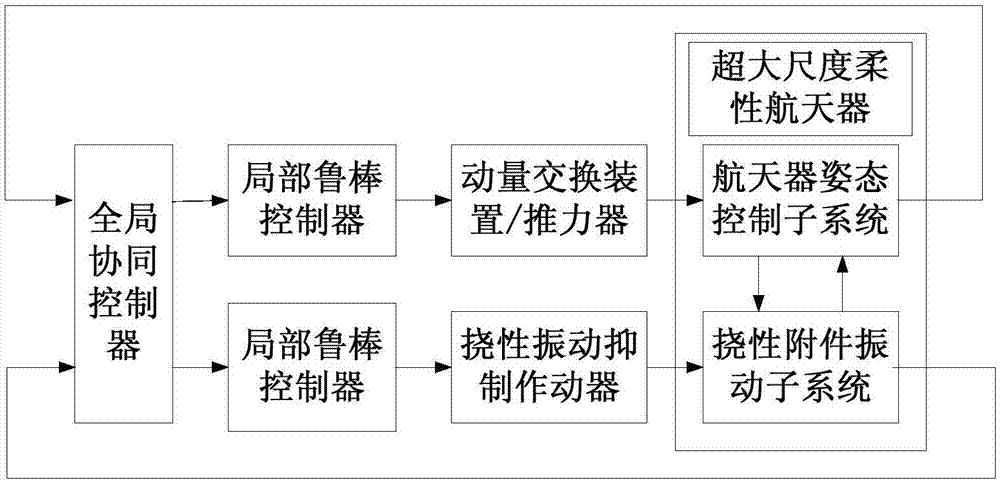

Super-size flexible spacecraft dispersion cooperative control method

ActiveCN107015567AHigh deformation control precisionImprove pointing accuracyAttitude controlDispersion stabilitySpacecraft attitude control

The invention discloses a super-size flexible spacecraft dispersion cooperative control method, and aims to achieve high stability and vibration inhibition control on a super-size flexible spacecraft. The method comprises the following steps: S1, dividing a super-size flexible spacecraft control system into a spacecraft posture control subsystem and a flexible attachment vibration subsystem, and designing corresponding partial robust controllers for the spacecraft posture control subsystem and the flexible attachment vibration subsystem respectively; and S2, designing a coordinate controller for overall properties of the super-size flexible spacecraft control system. The method has the advantages that according to the dynamic characteristics of the super-size flexible spacecraft, a dispersion cooperative control method is adopted, a partial structure is stably controlled through dispersion stability, overall high-precision performance indexes are achieved through the cooperative controller, high appointing precision and stability of postures and deformation control precision of a flexible component are achieved, and the method is widely applied to high-precision high-stability appointing control on a large-size flexible structure.

Owner:SHANGHAI AEROSPACE CONTROL TECH INST

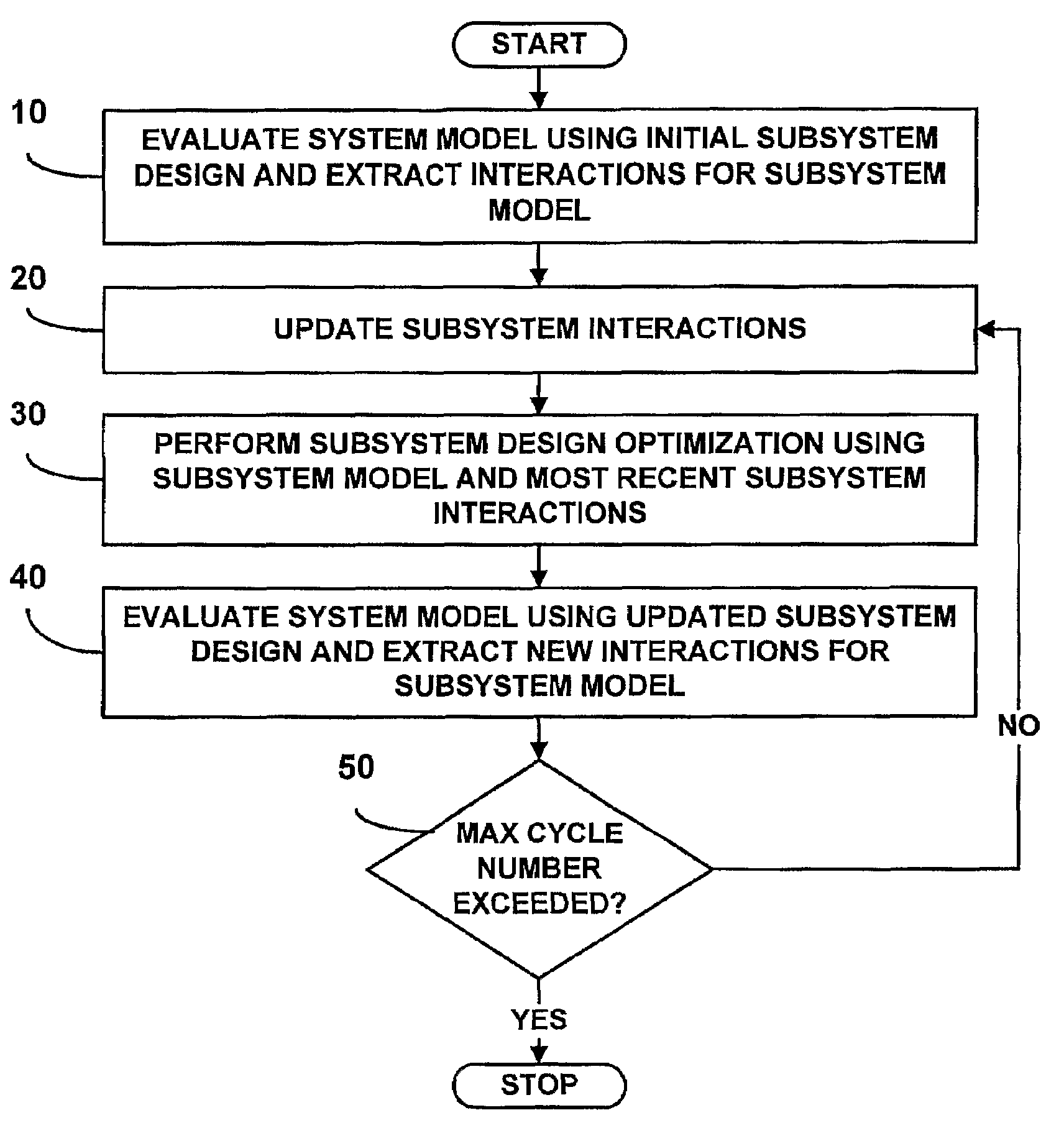

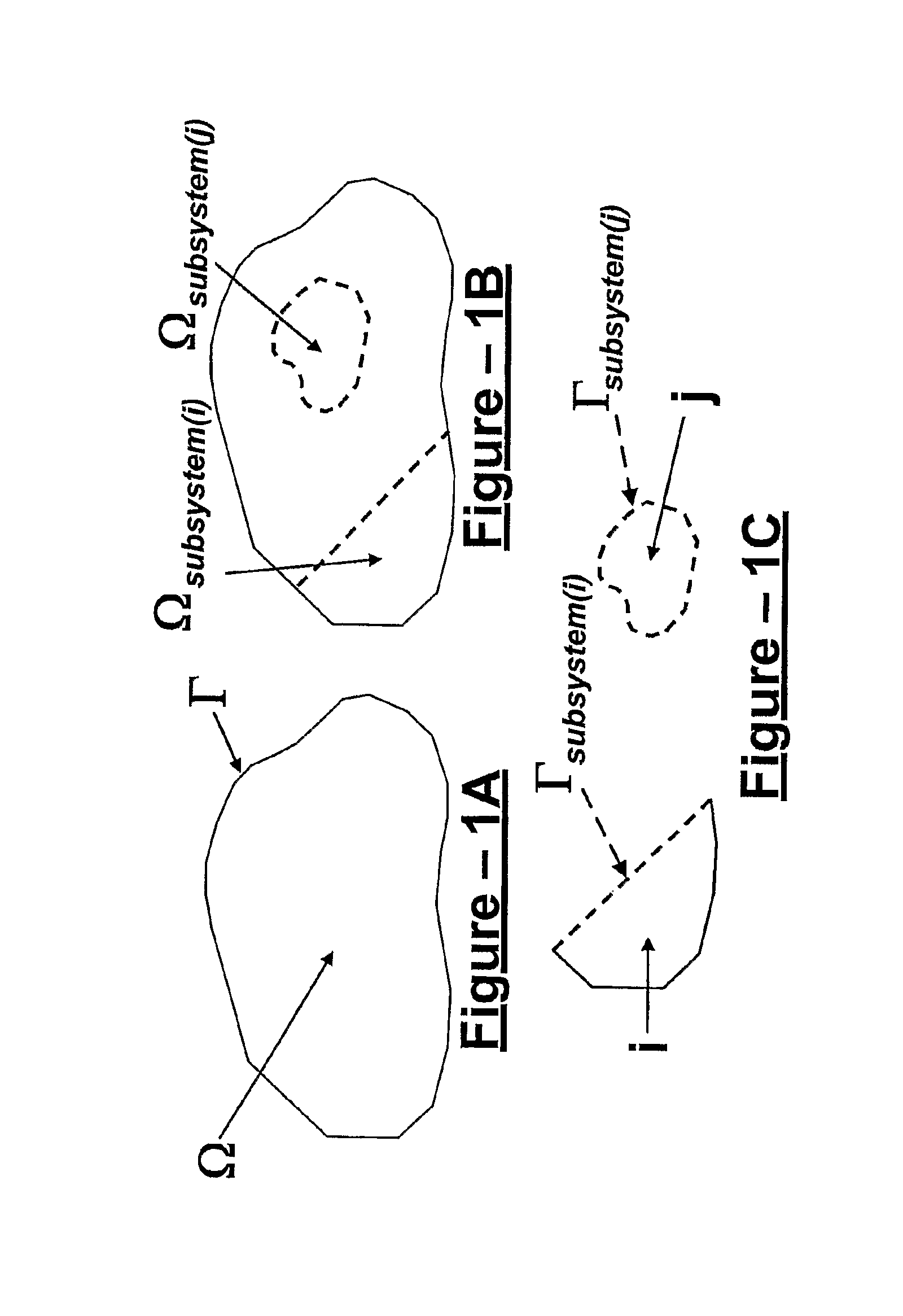

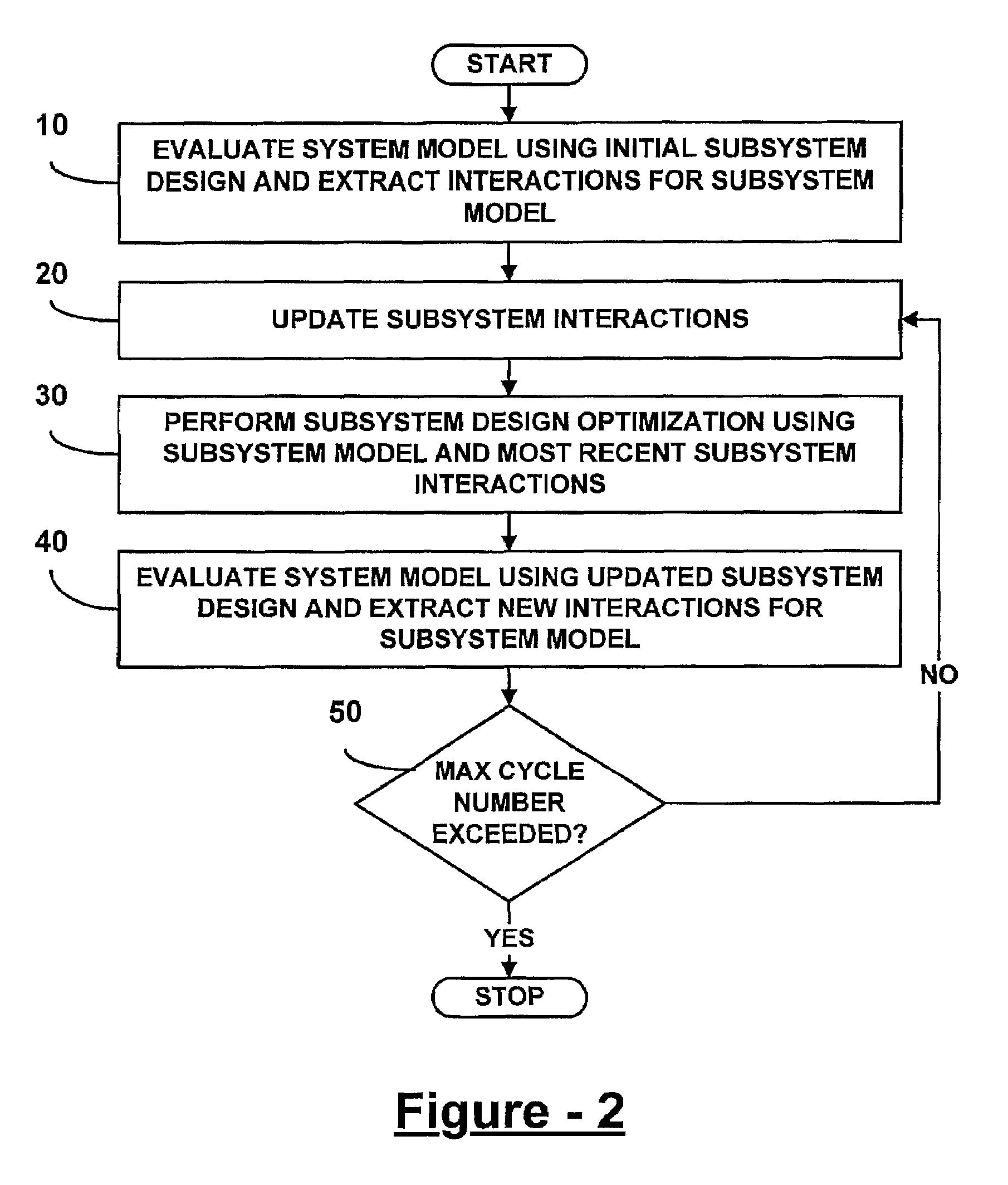

Design optimization system and method

ActiveUS7756688B2Improve performanceImprove robustnessForecastingComputation using non-denominational number representationSubsystem designEvaluation system

Owner:BOARD OF TRUSTEES OPERATING MICHIGAN STATE UNIV