Patents

Literature

48 results about "Interconnect topology" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

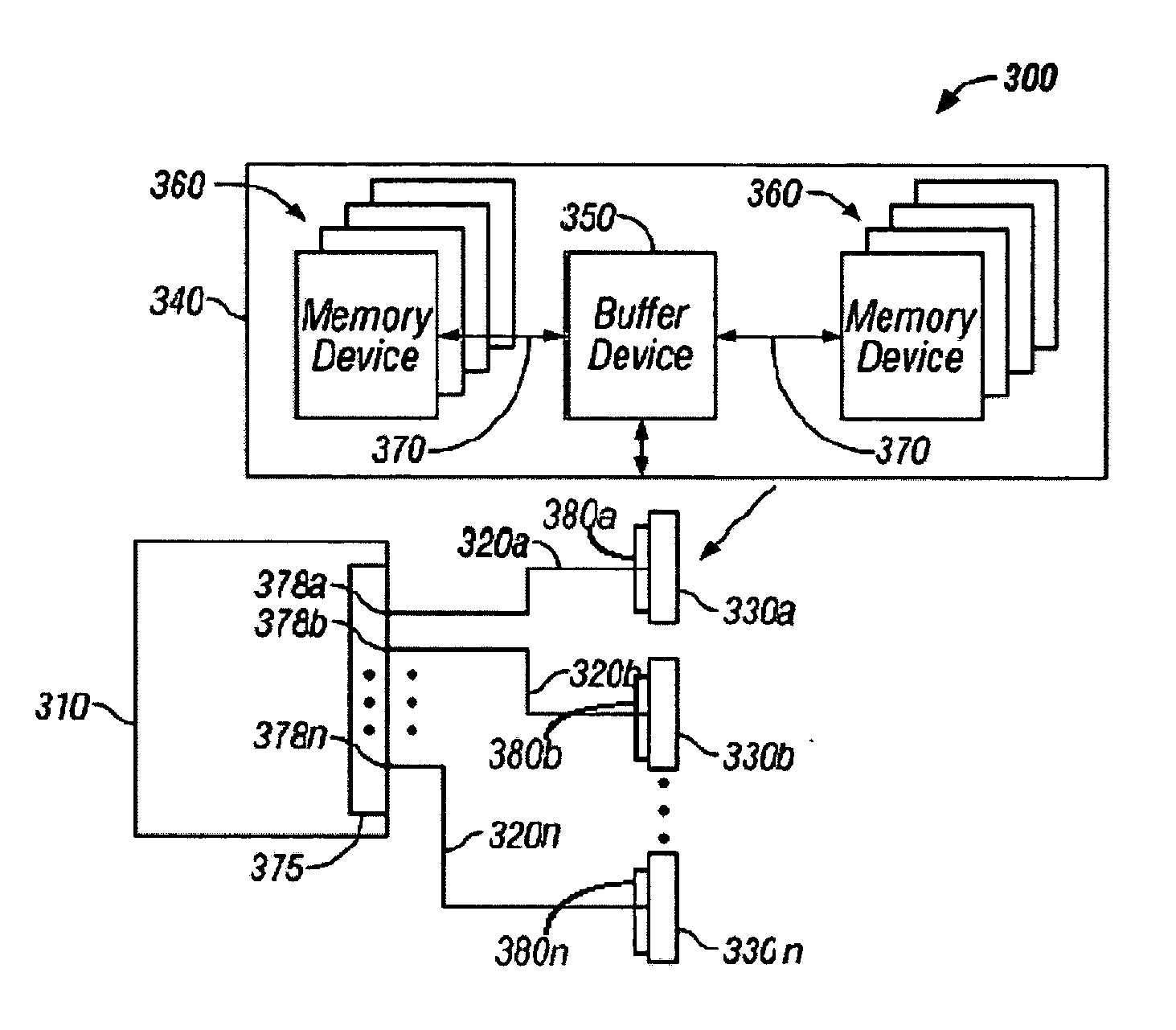

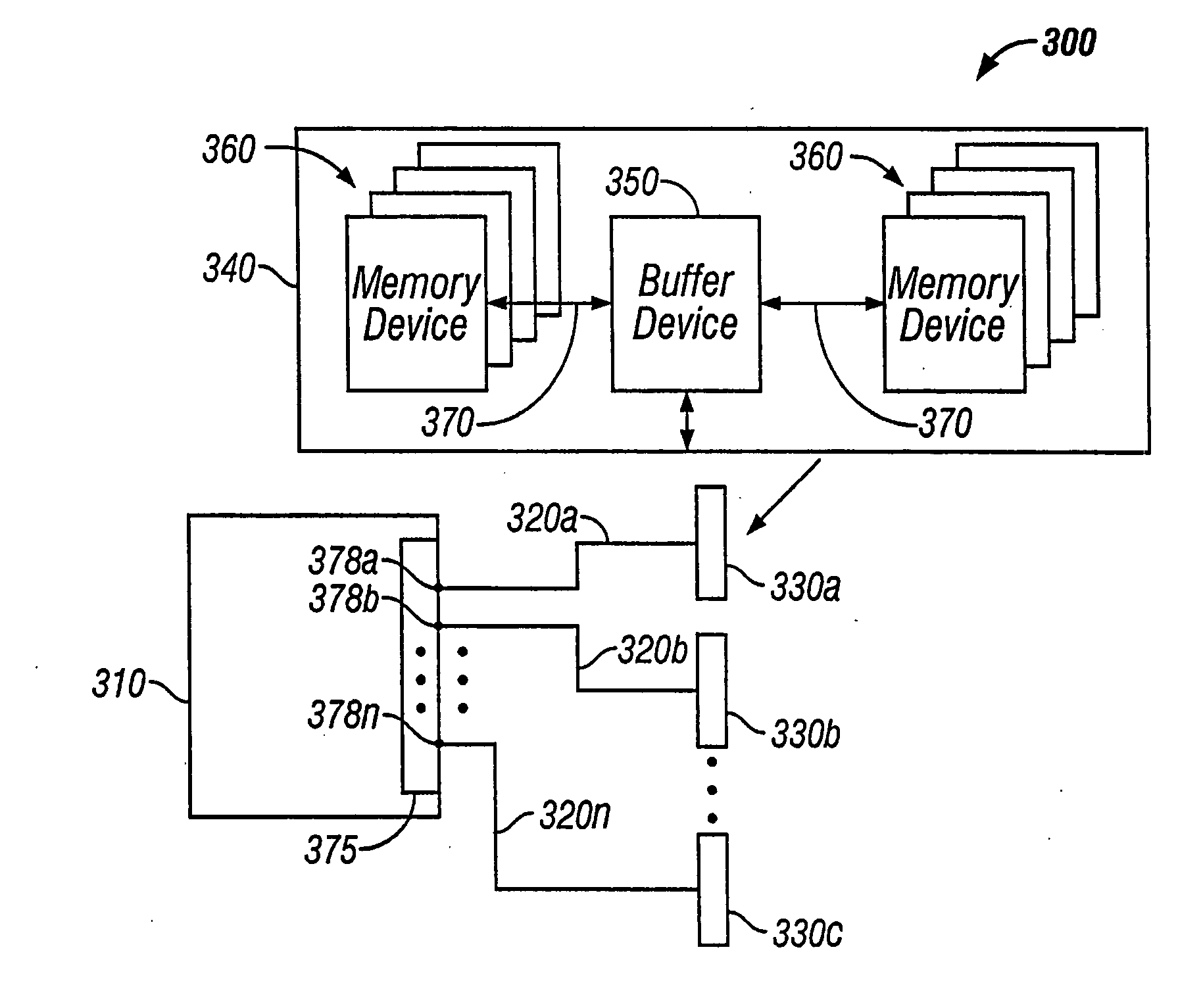

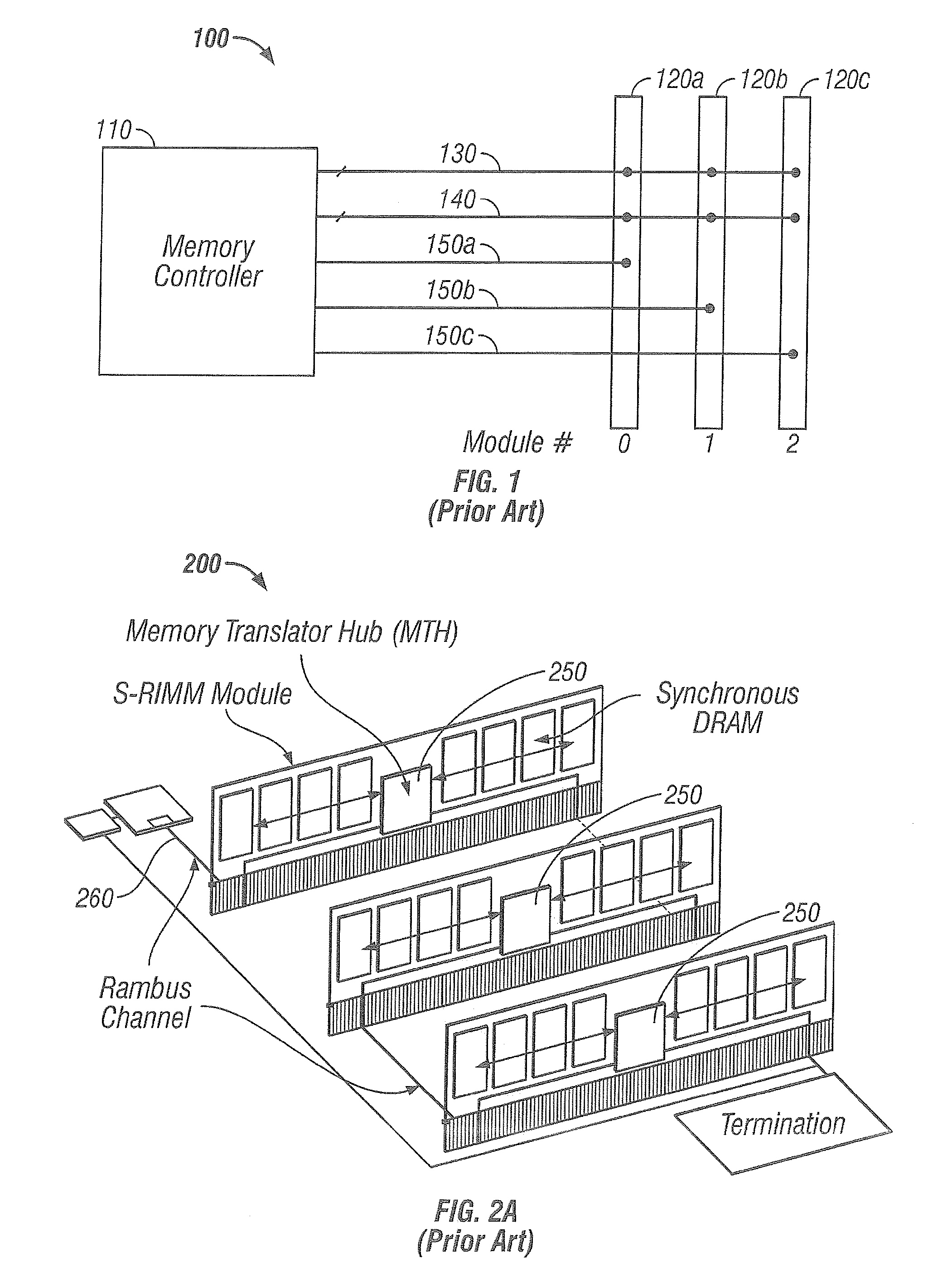

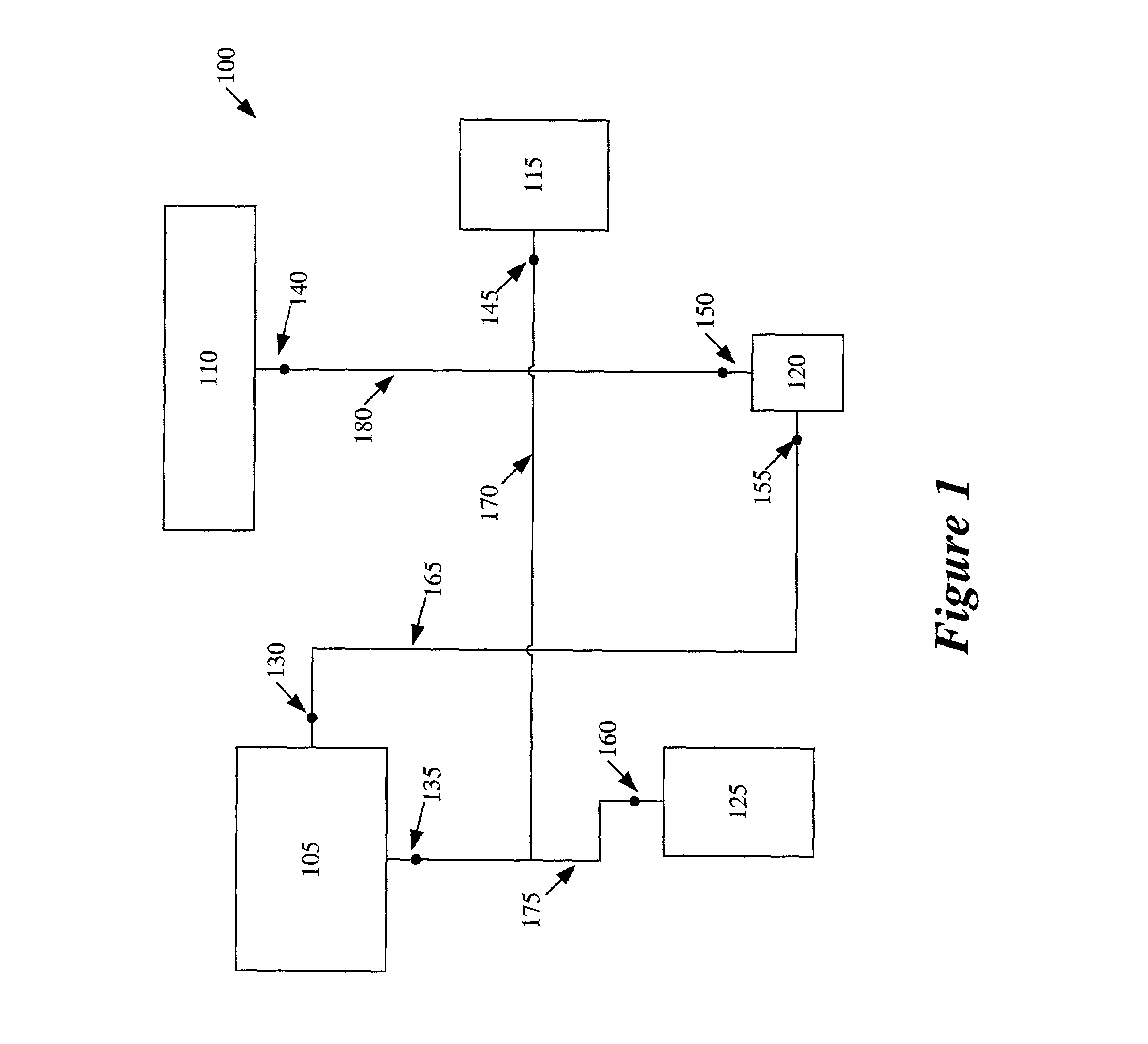

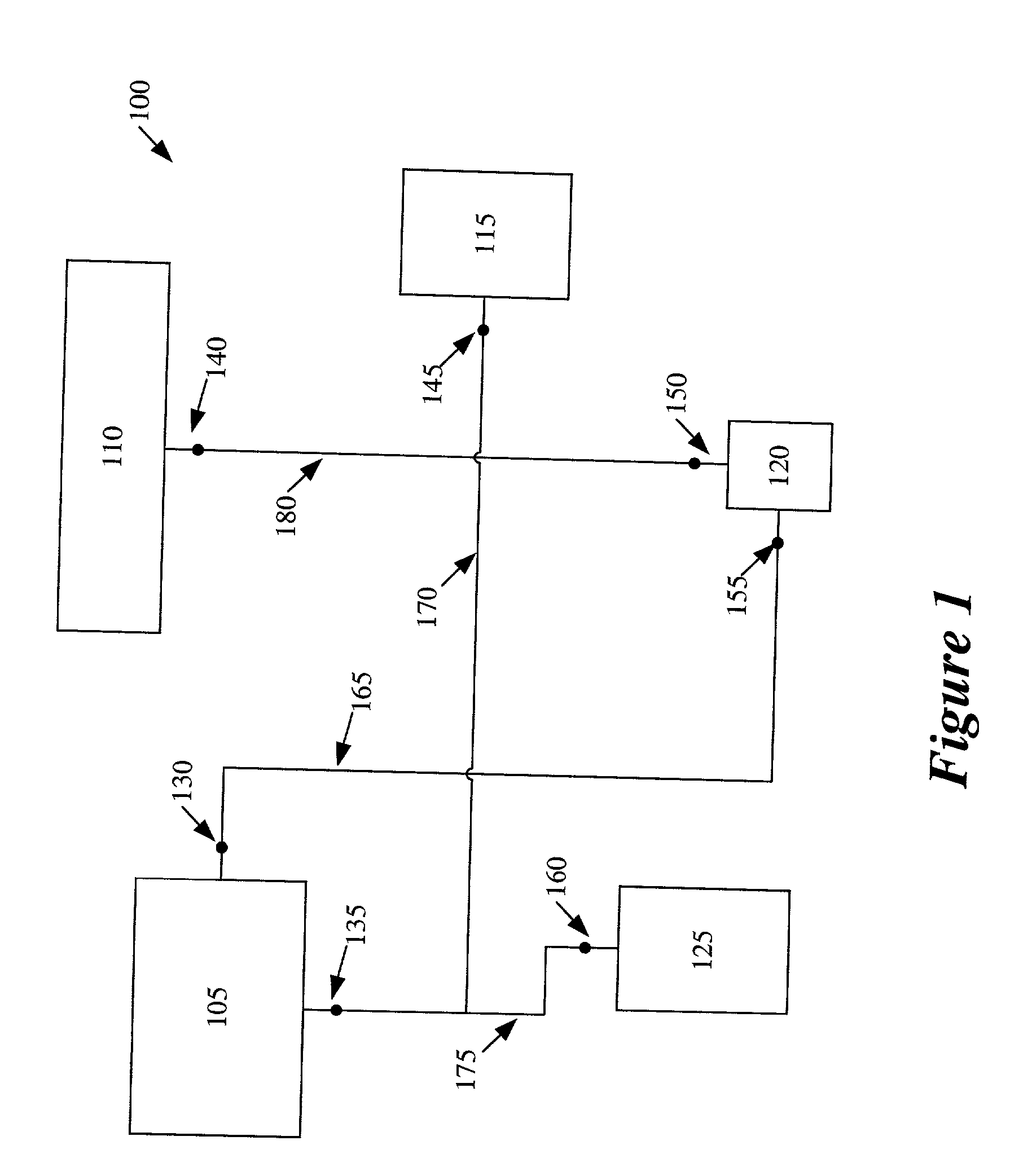

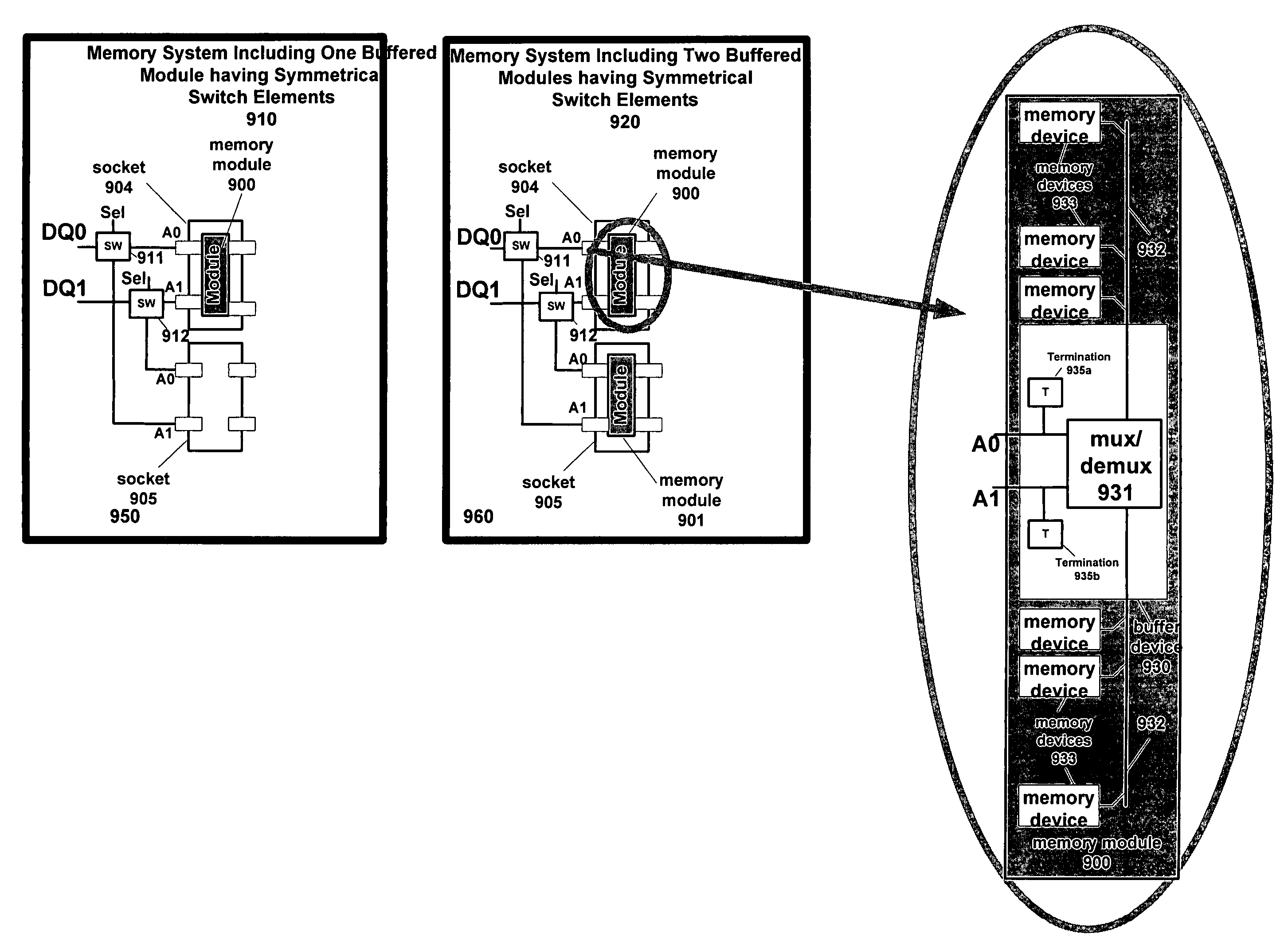

Configurable width buffered module having switch elements

A memory system architecture / interconnect topology includes a configurable width buffered memory module having a configurable width buffer device with at least one switch element. A buffer device, such as a configurable width buffer device, is positioned between or with at least one integrated circuit memory device positioned on a substrate surface of a memory module, such as a DIMM. A switch element is positioned on or off a memory module and includes two transistors in embodiments of the invention. One or more switch elements are coupled to one or more channels to allow for upgrades of memory modules in a memory system. An asymmetrical switch topology allows for increasing the number of memory modules to more than two memory modules without adding switch elements serially on each channel. Switch elements allow for increasing the number of ranks of memory modules in a system, while also achieving many of the benefits associated with point-to-point topology.

Owner:RAMBUS INC

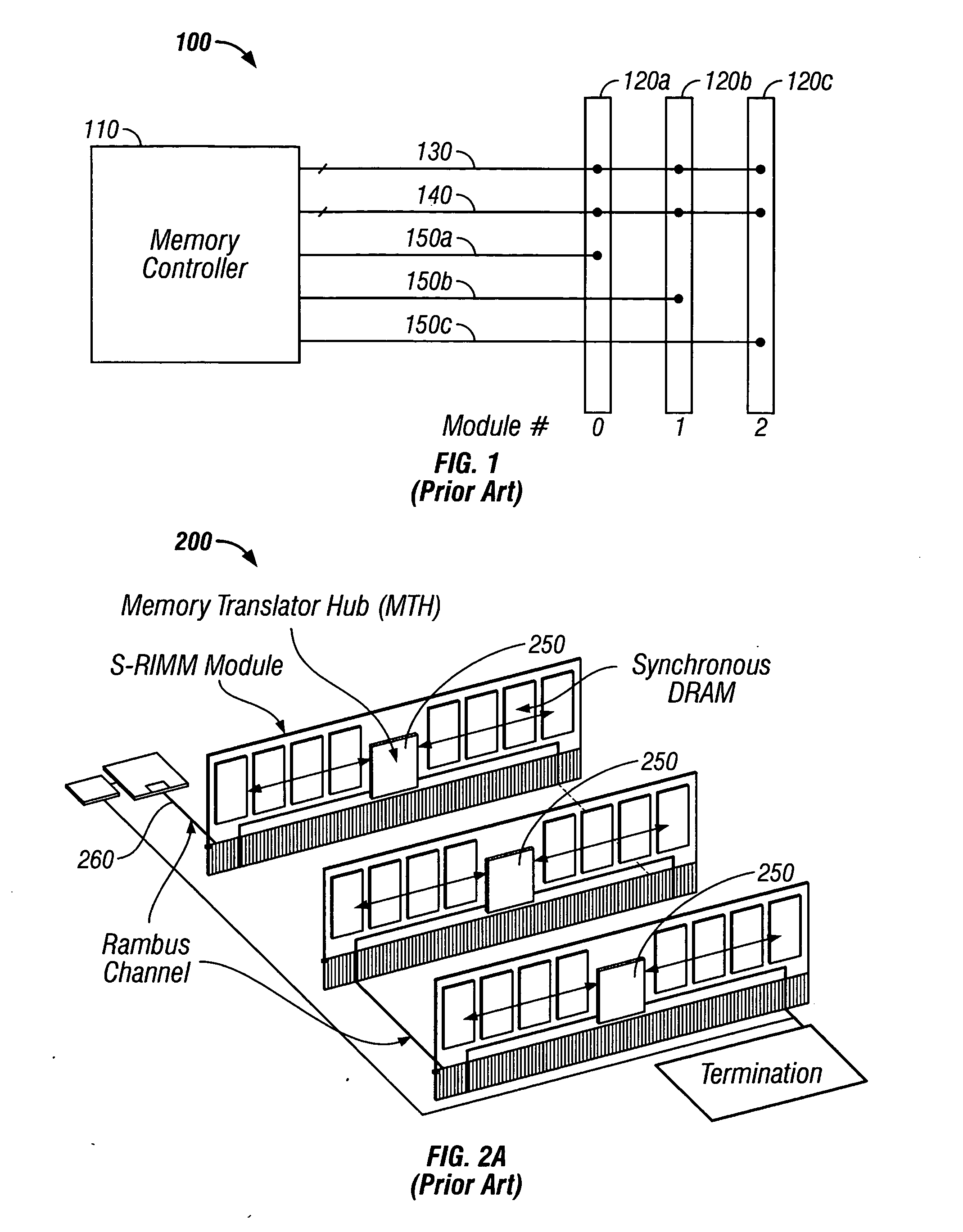

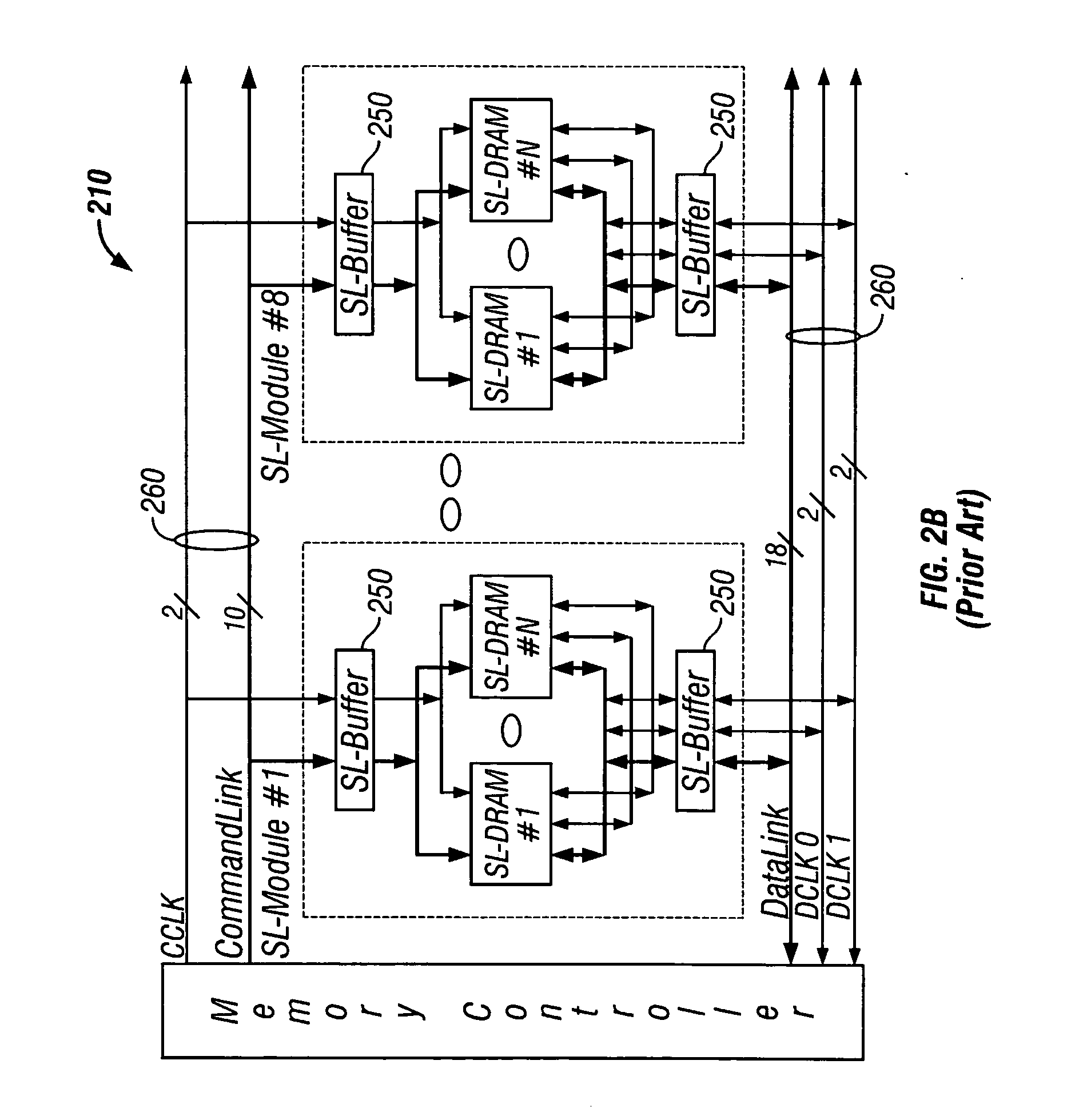

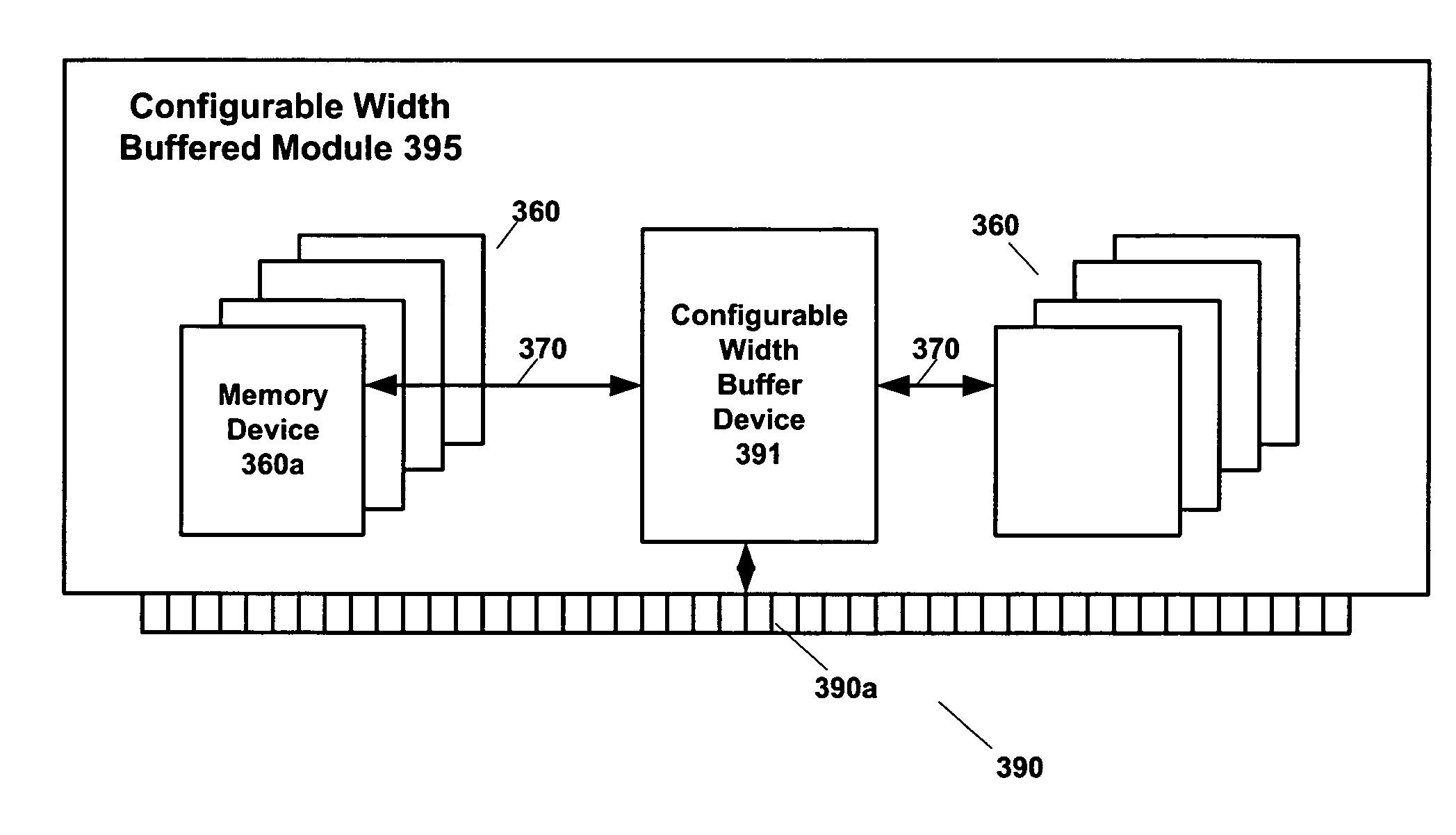

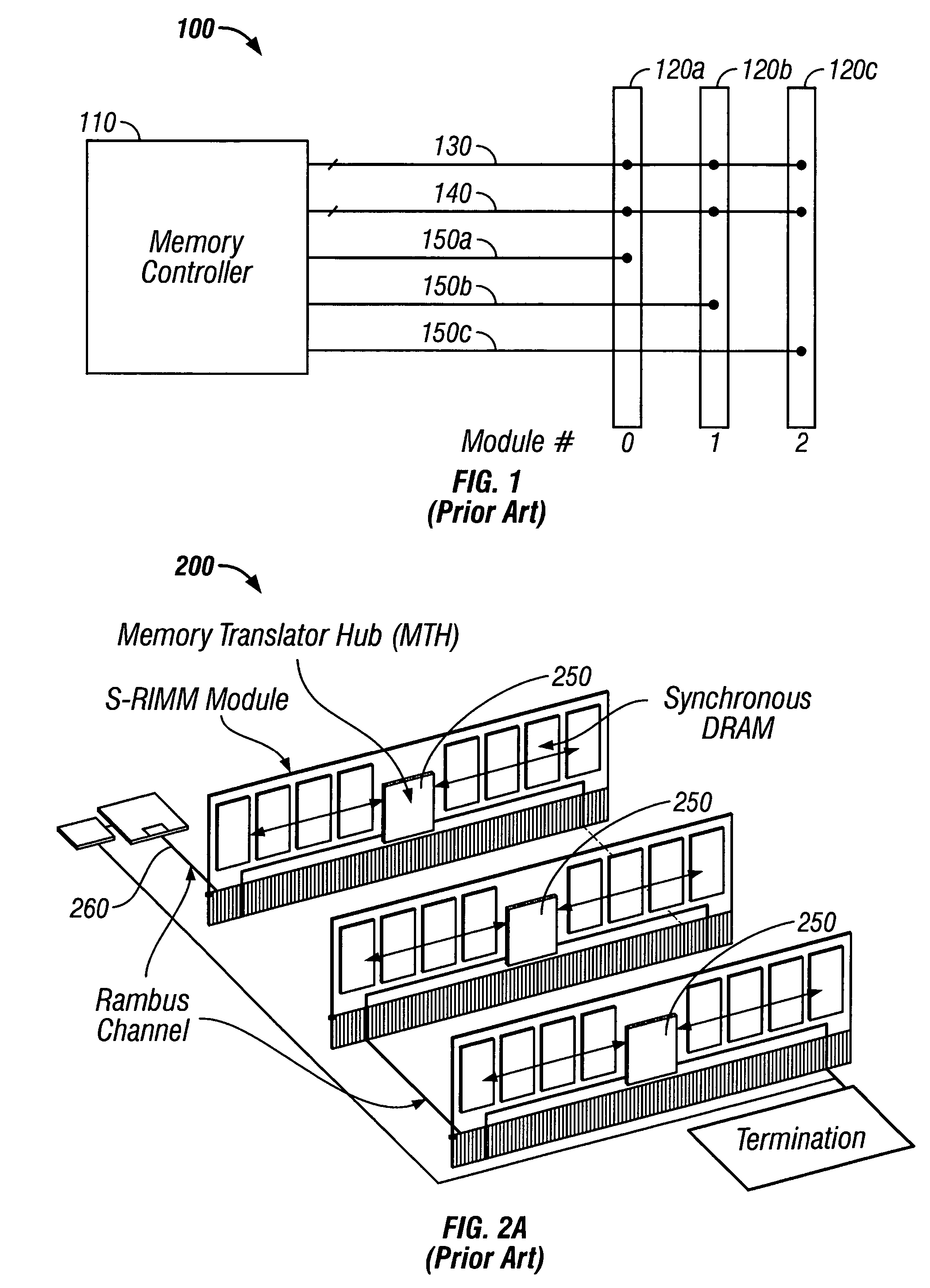

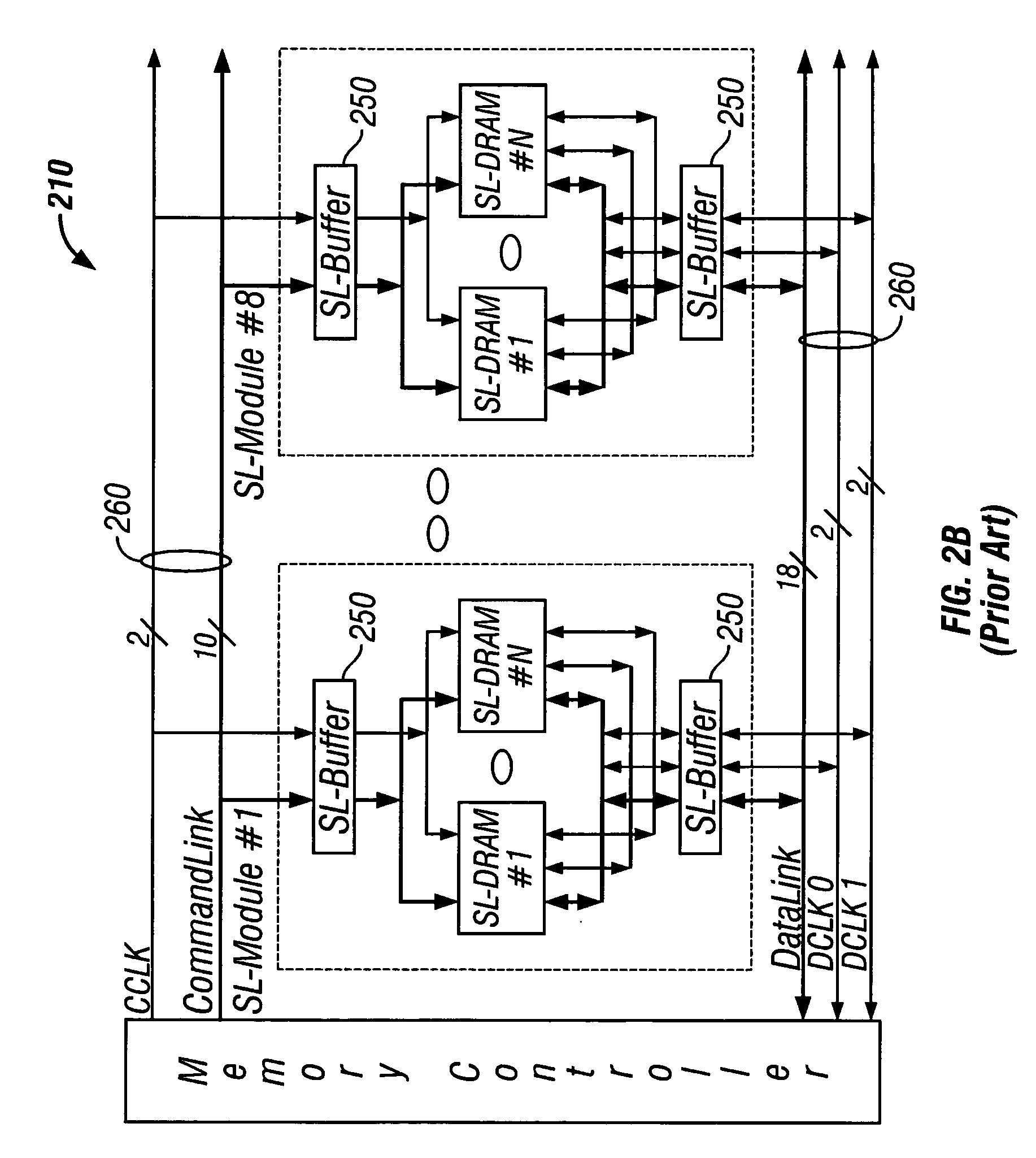

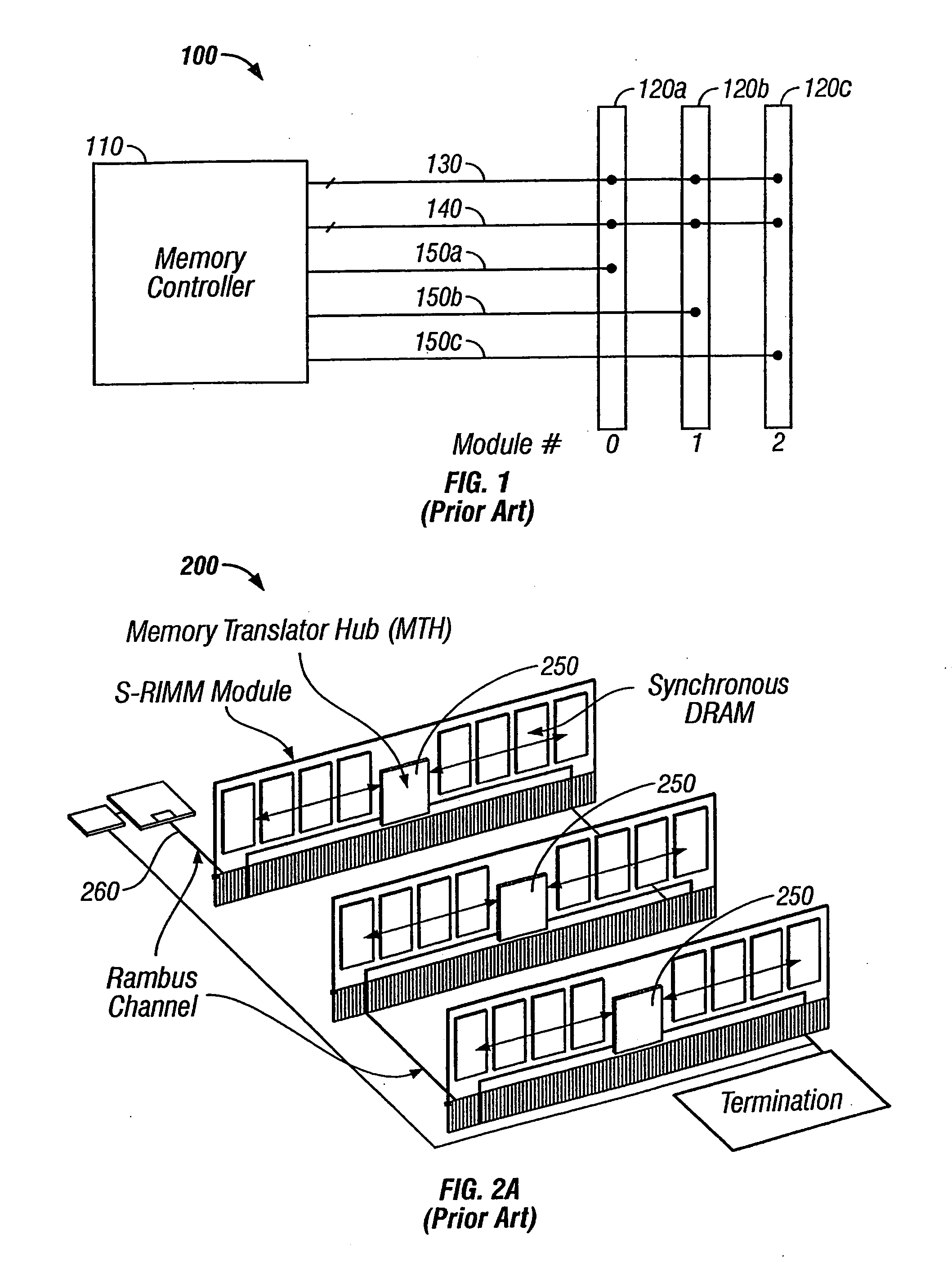

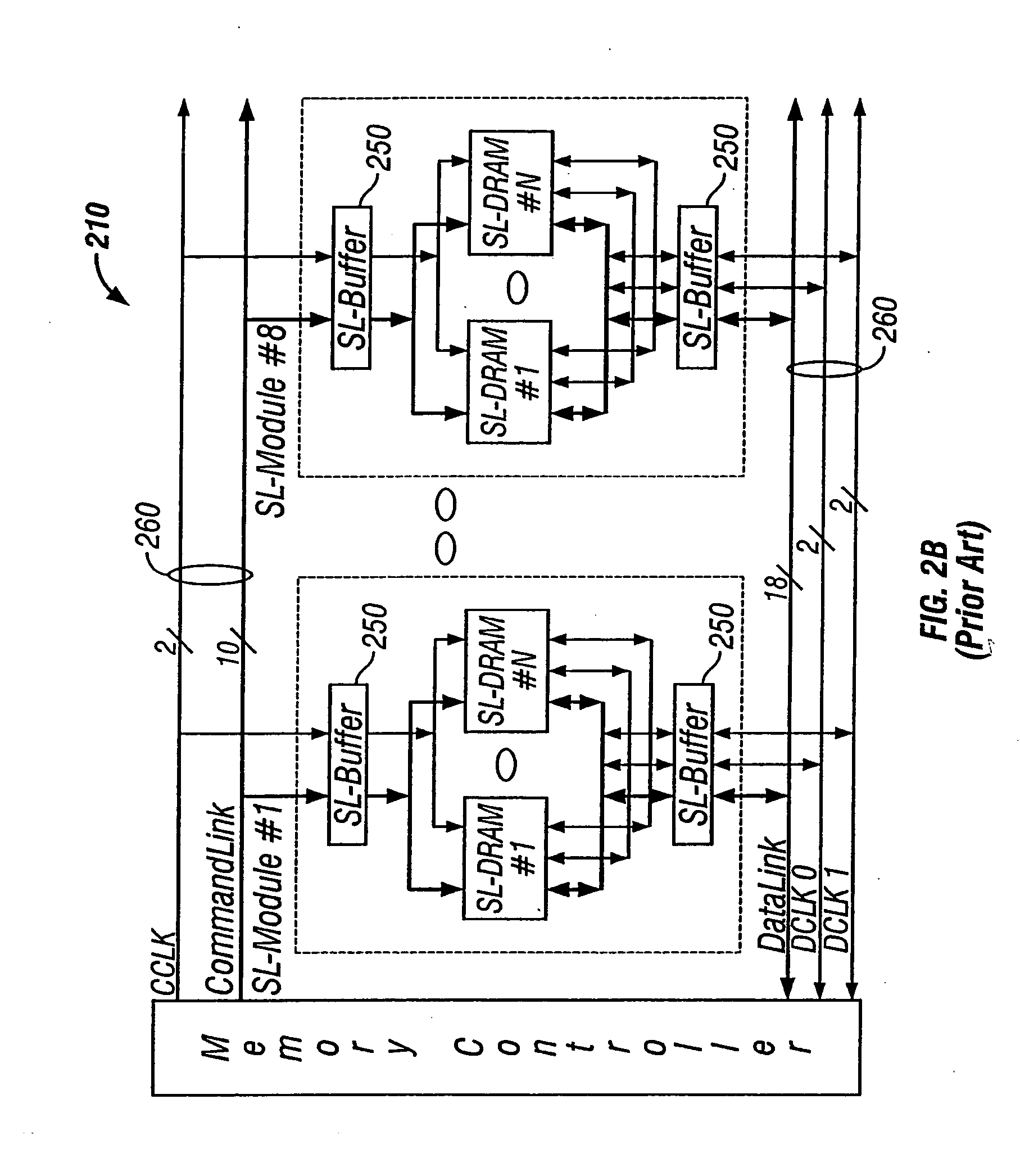

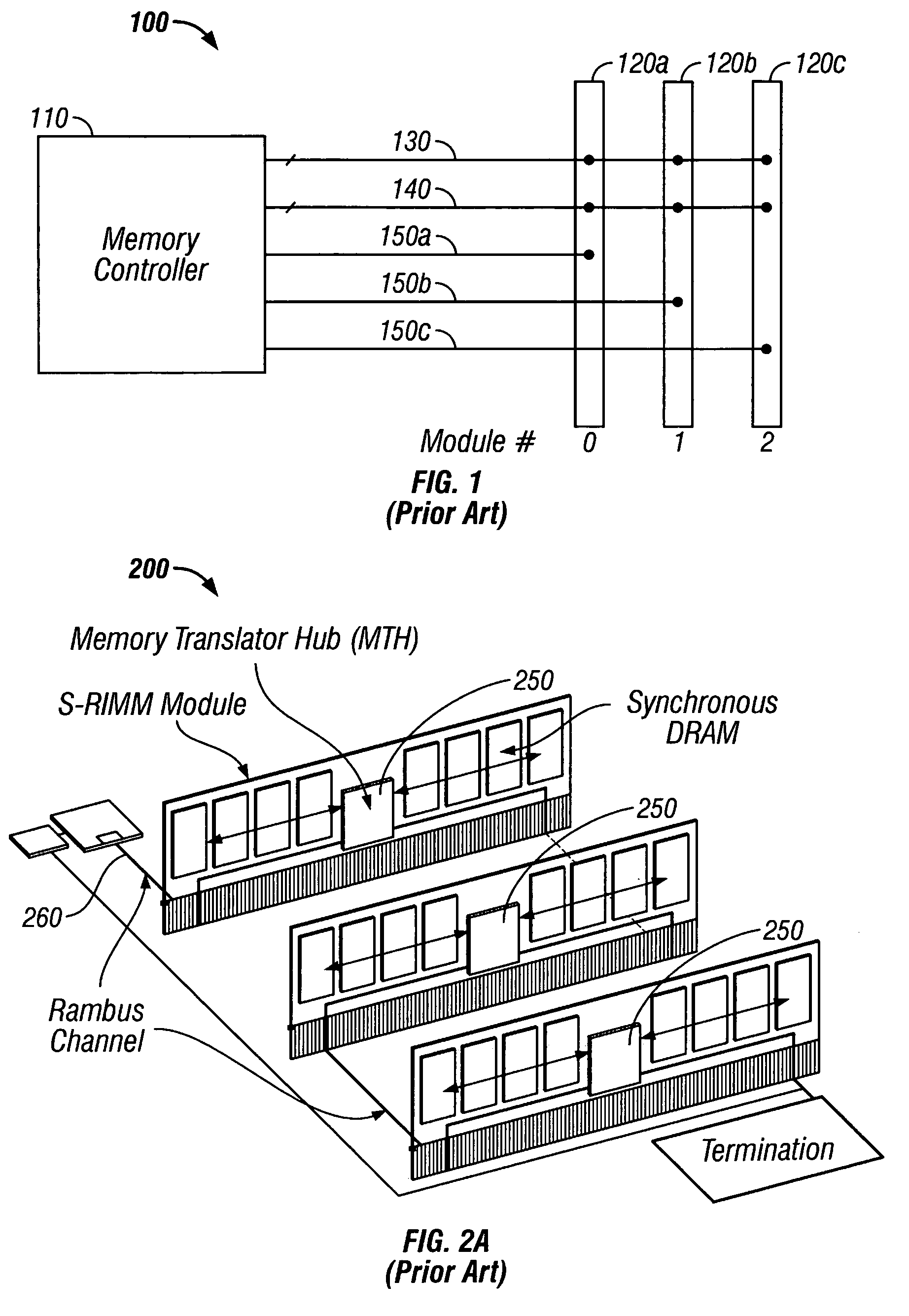

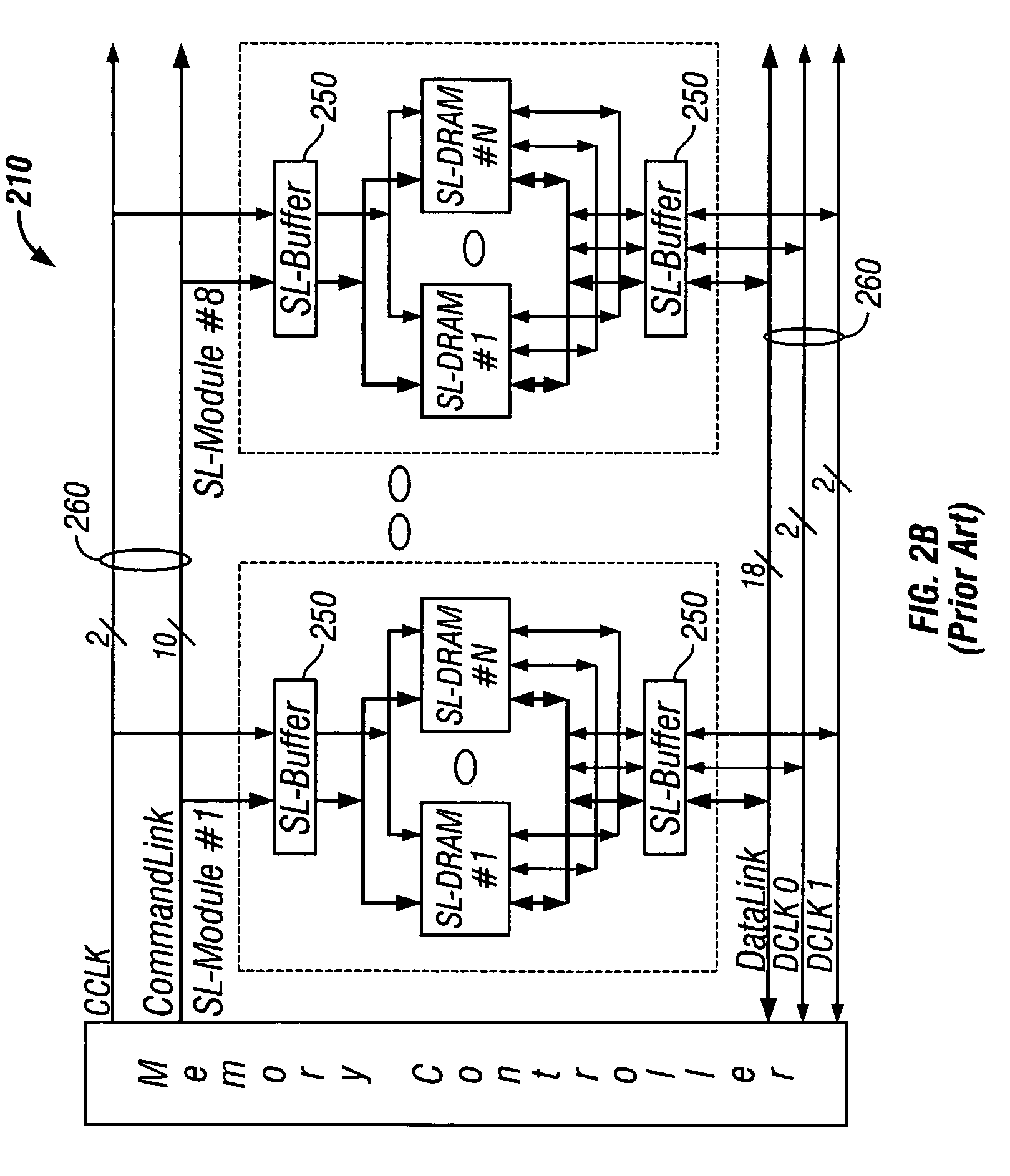

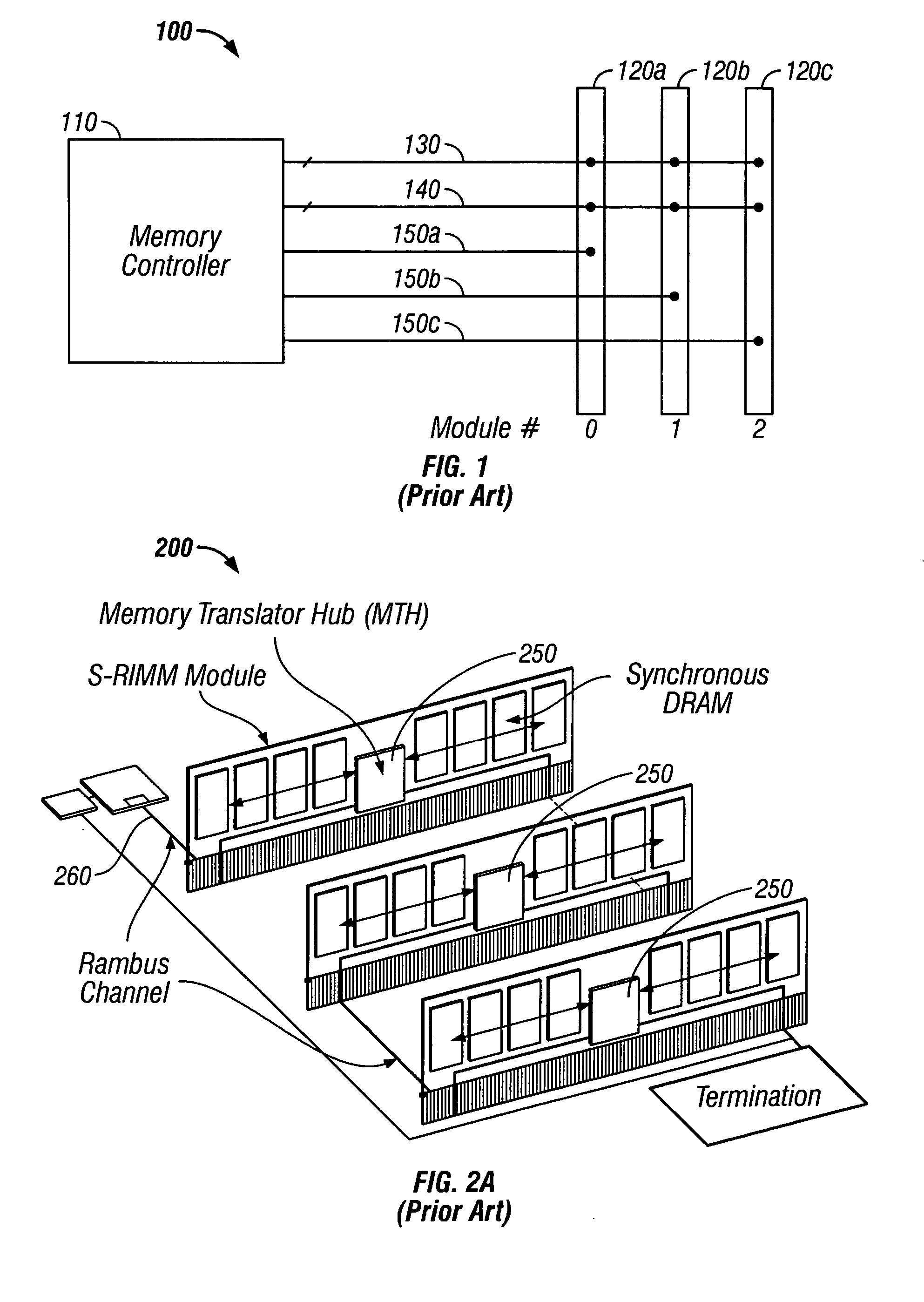

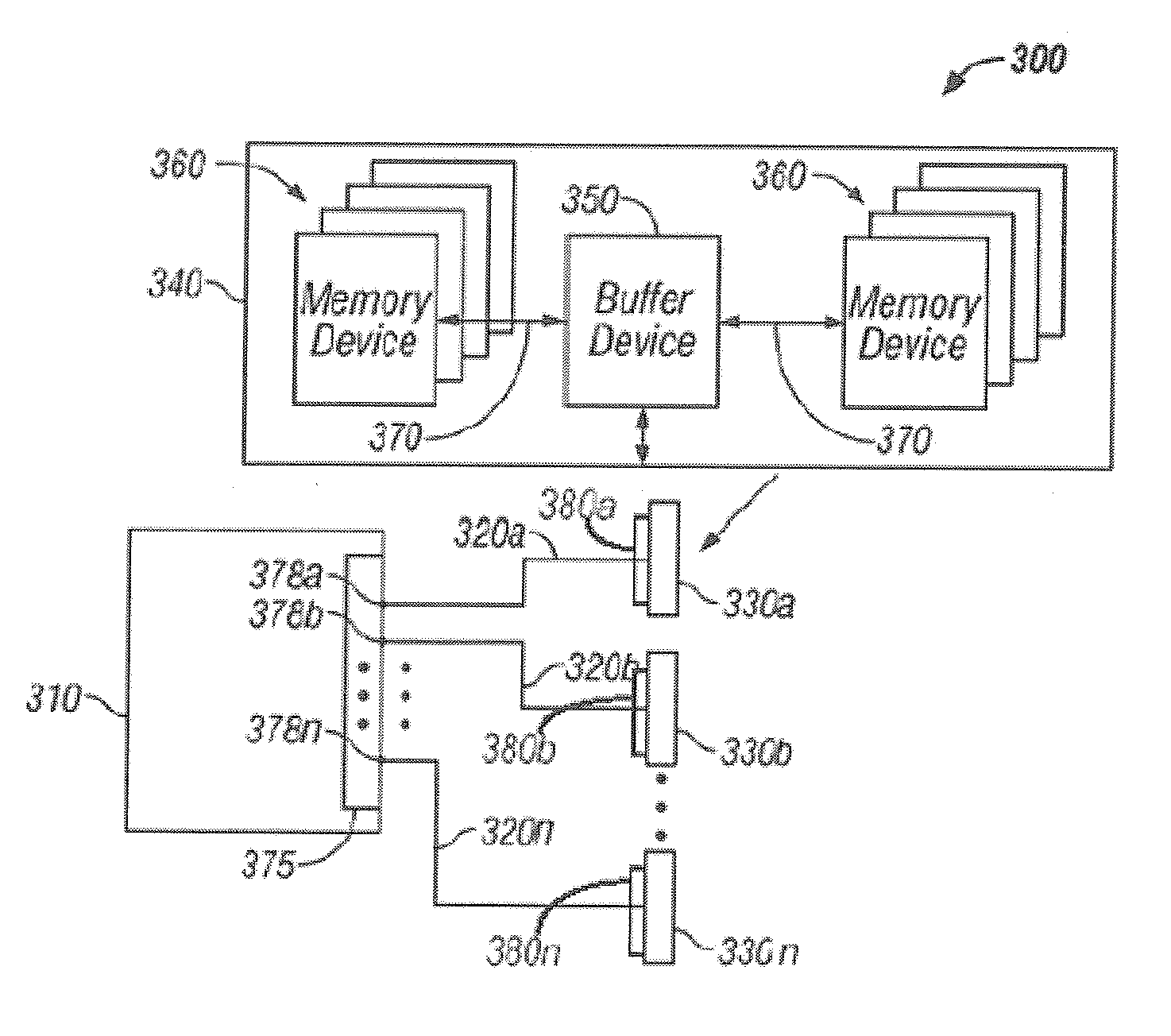

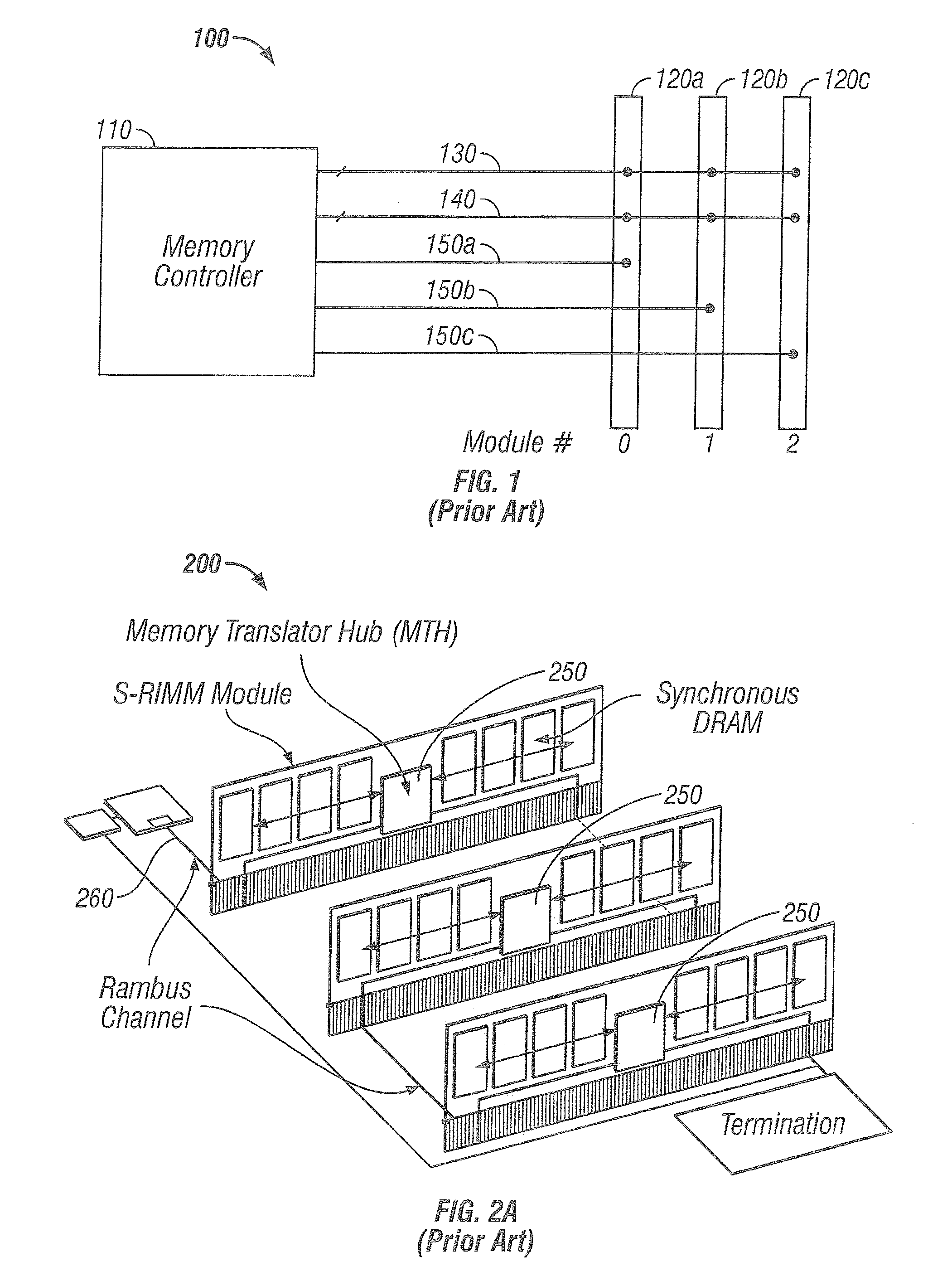

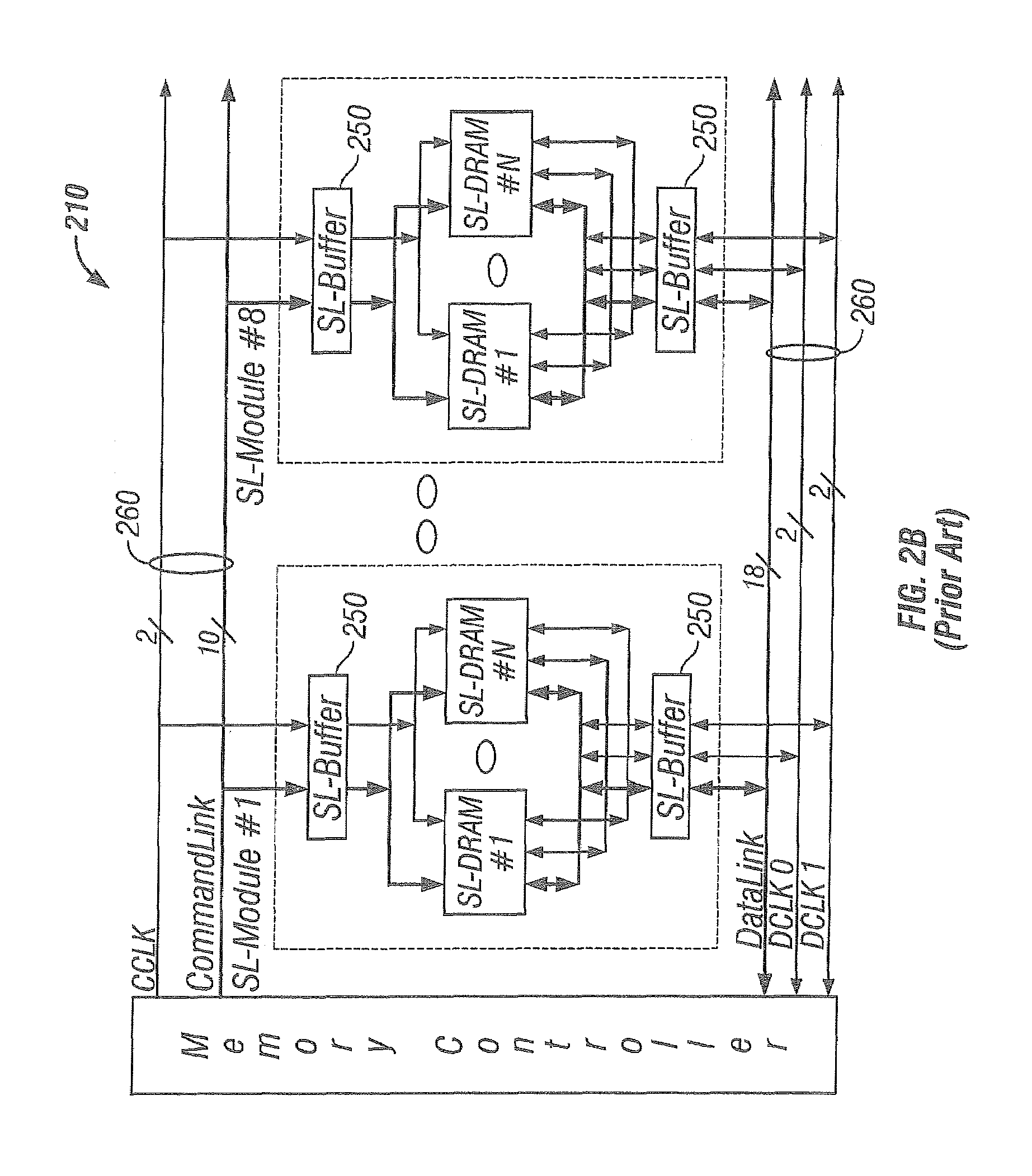

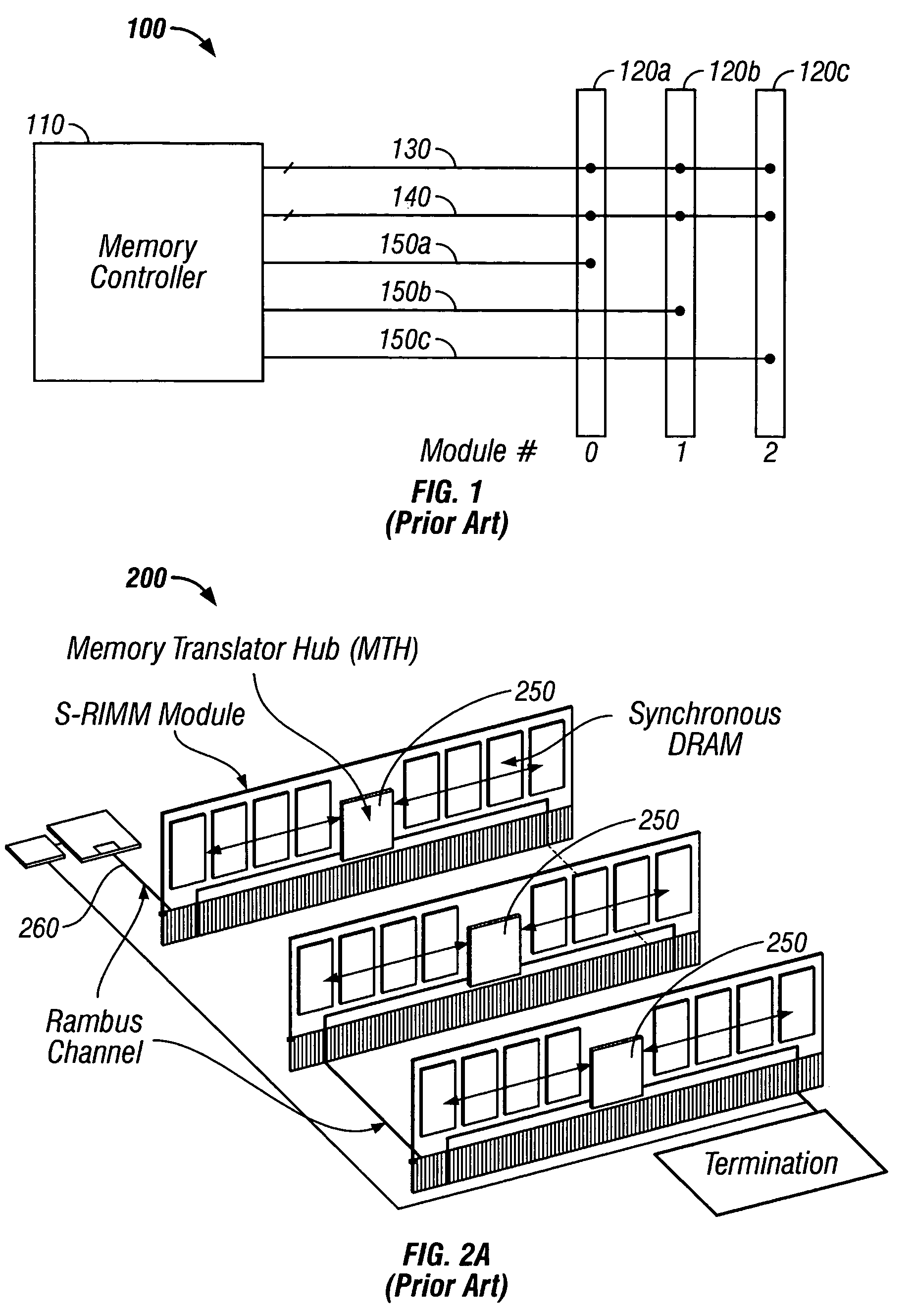

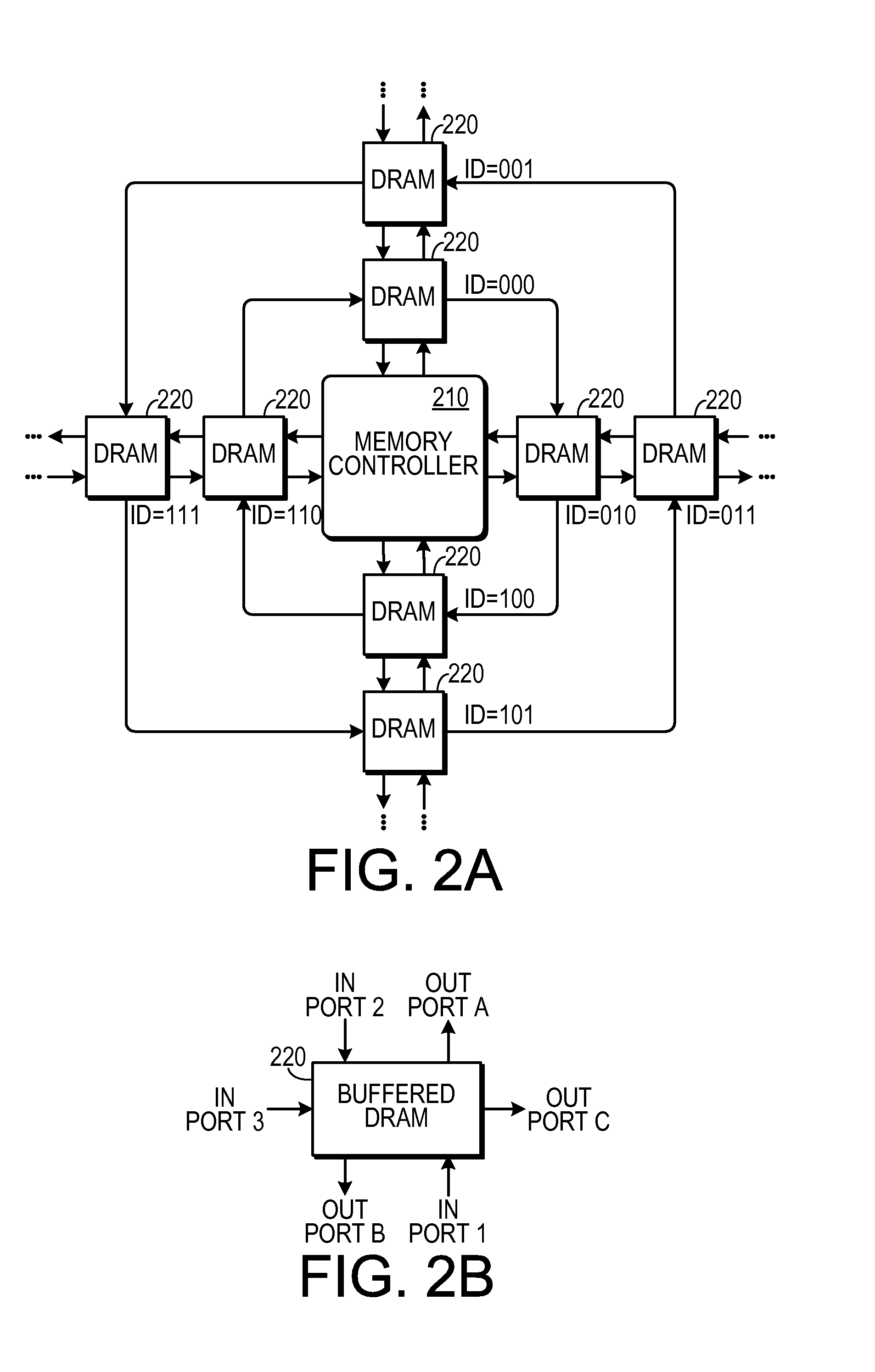

Memory system including an integrated circuit buffer device

InactiveUS20050044303A1Eliminate physical inter-dependenceMemory adressing/allocation/relocationDigital storageComputer hardwareInterconnect topology

A memory system architecture / interconnect topology that includes at least one point-to-point link between a master, and at least one memory subsystem. The memory subsystem includes a buffer device coupled to a plurality of memory devices. The memory system may be upgraded through dedicated point-to-point links and corresponding memory subsystems. The master communicates to the plurality of memory devices in each memory subsystem through the respective buffer device via each point-to-point link

Owner:RAMBUS INC

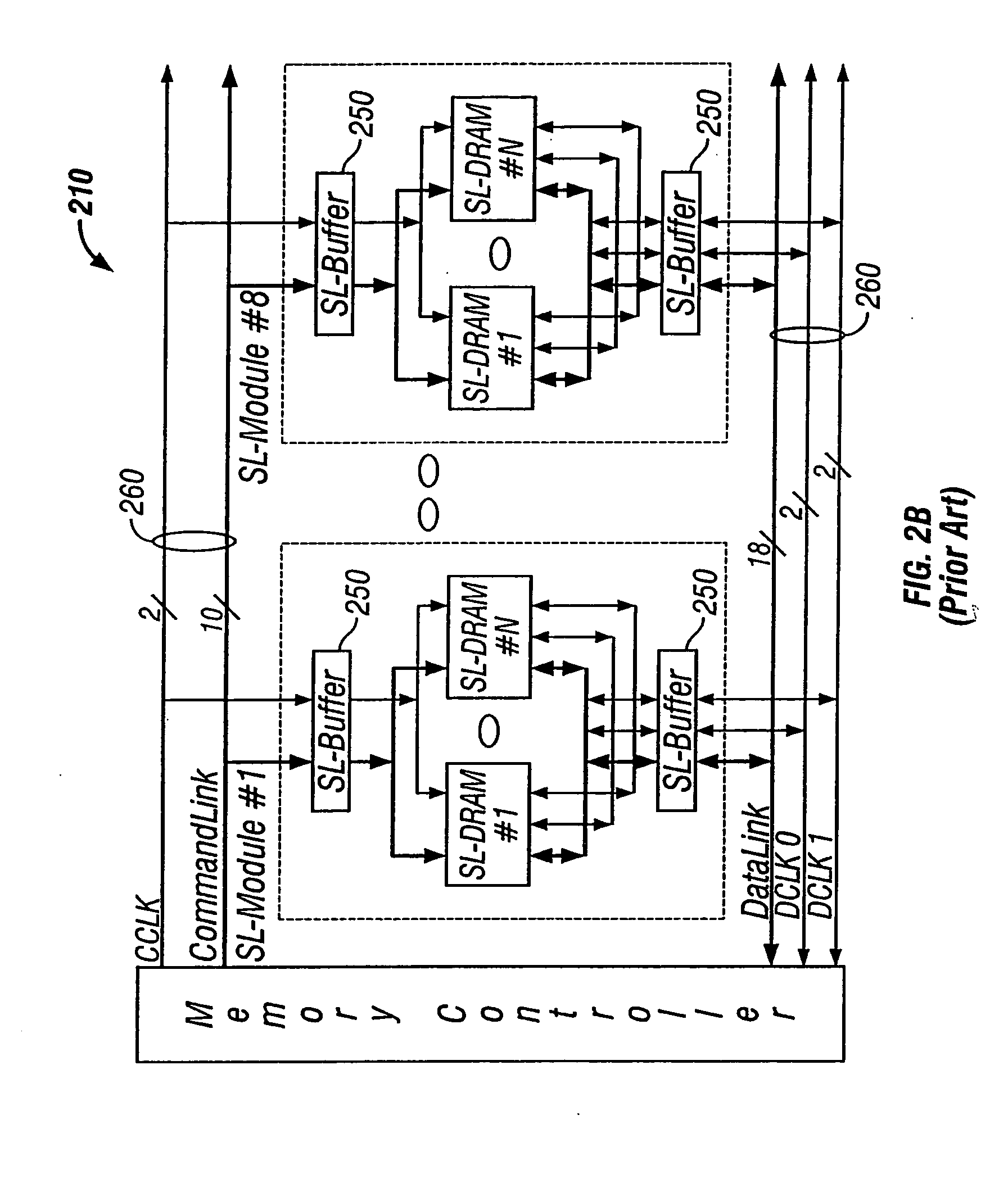

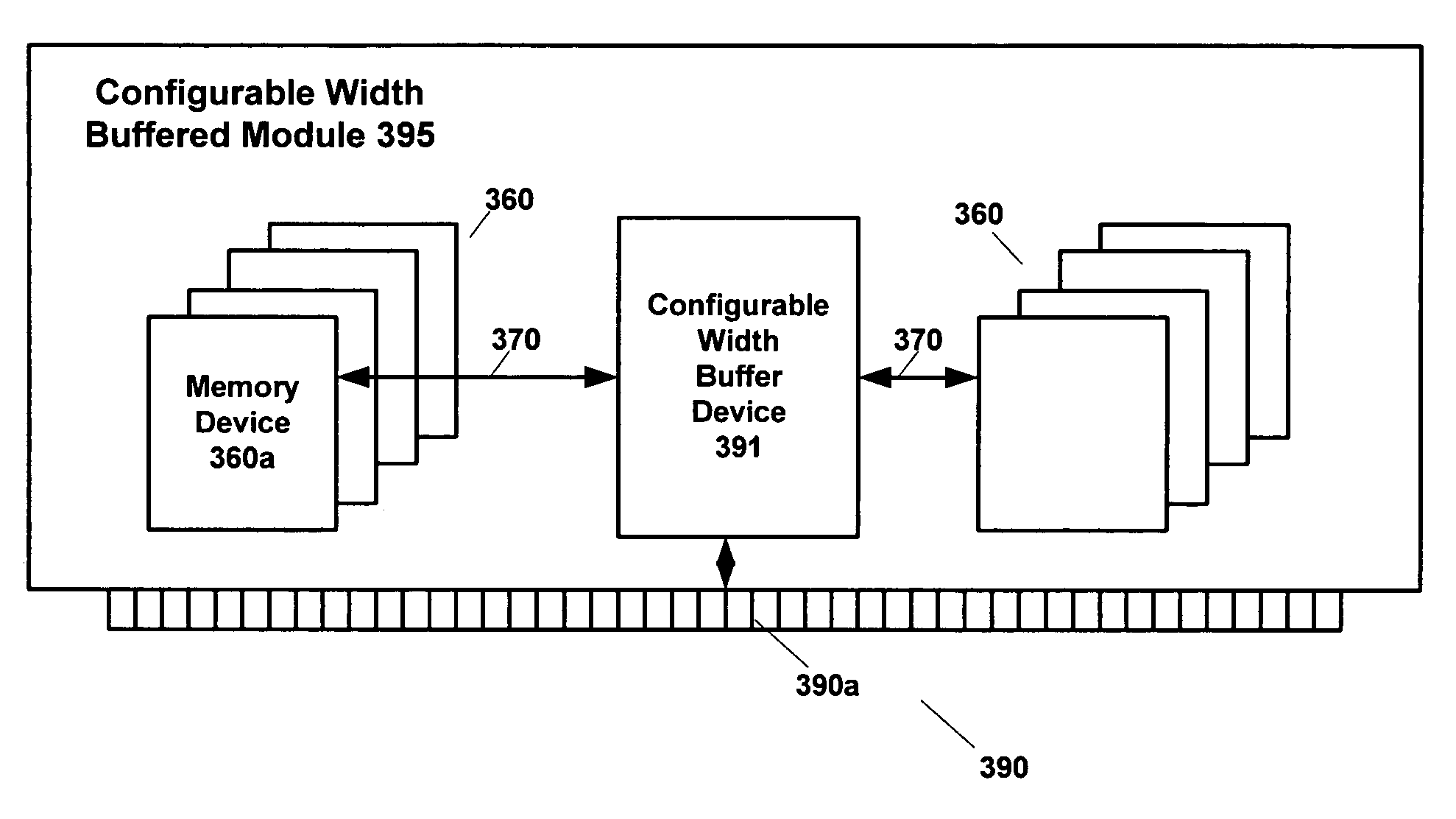

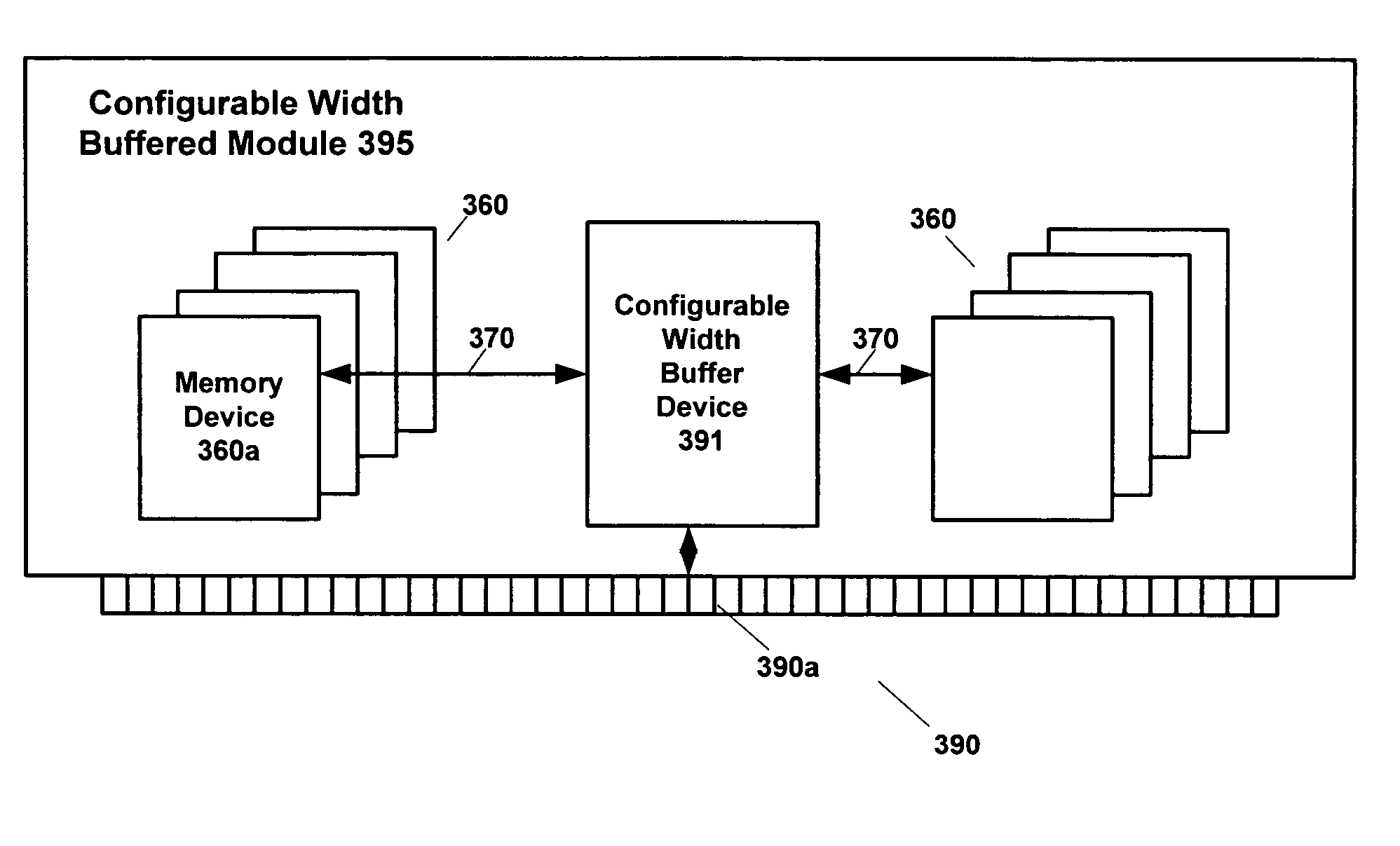

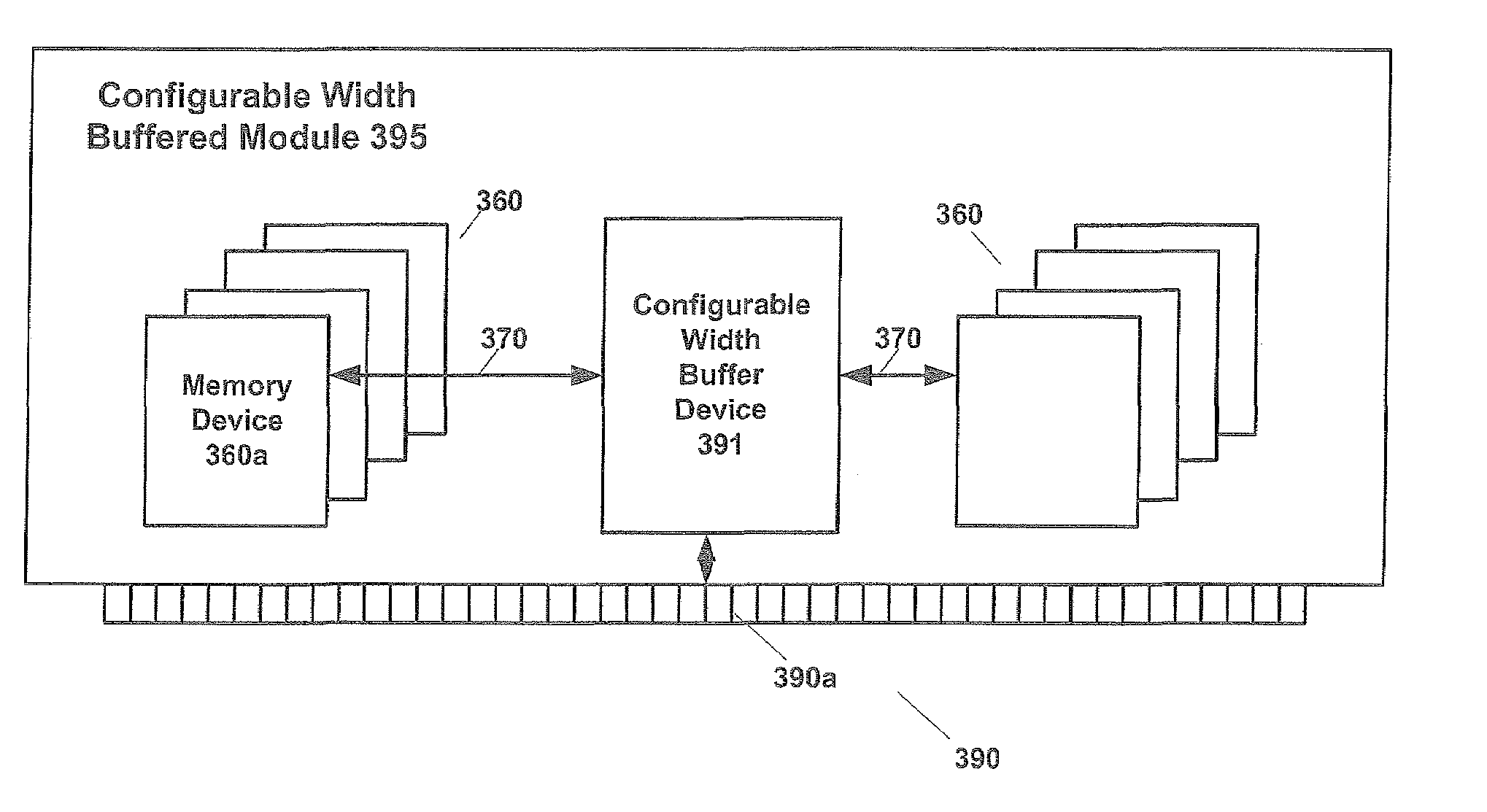

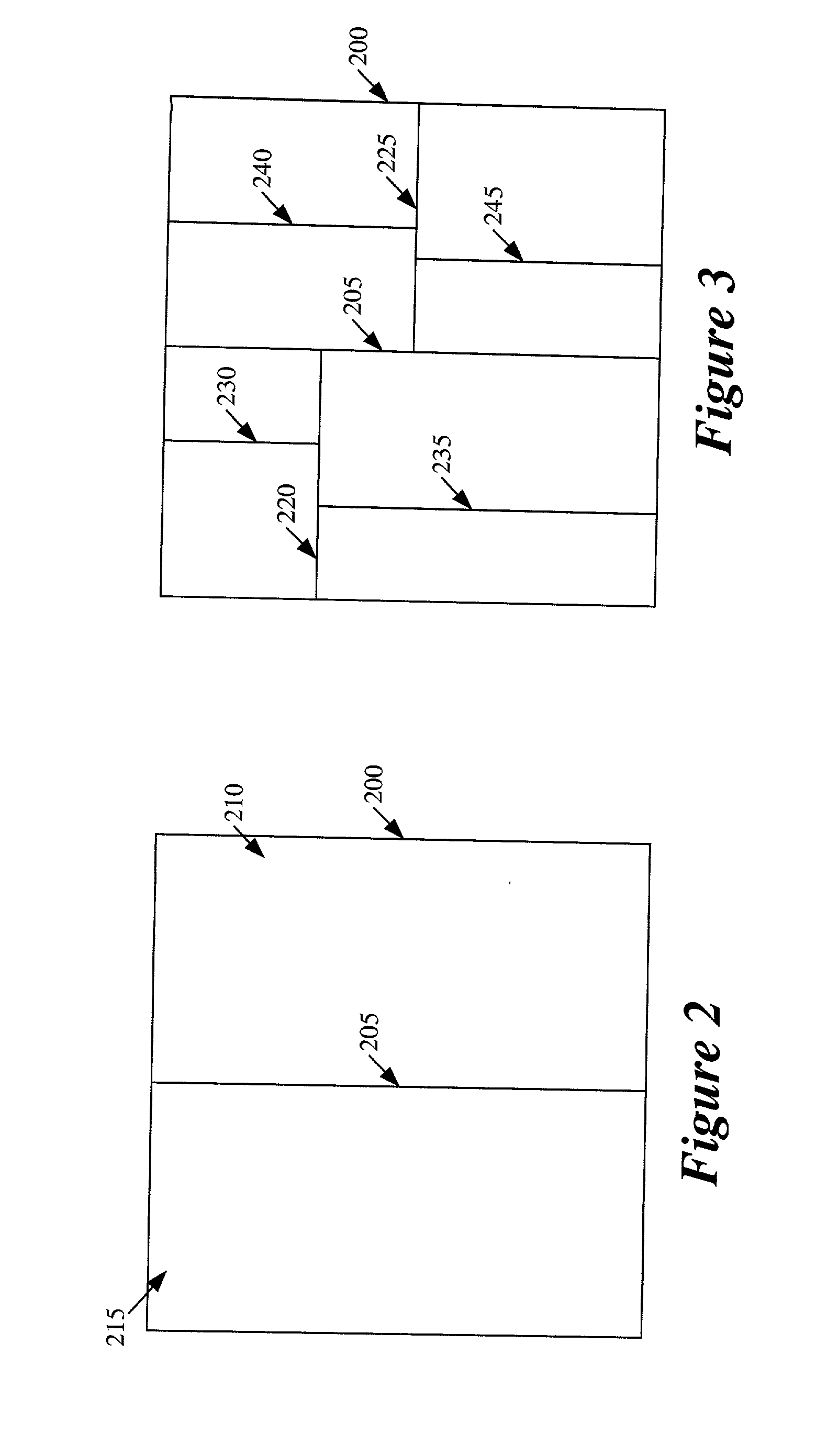

Configurable width buffered module

A memory system architecture / interconnect topology includes a configurable width buffered module having a configurable width buffer device. The configurable width buffer device is coupled to at least one memory device on the configurable width memory module. The configurable width buffer device includes an interface and a configurable serialization circuit capable of varying a data path width or a number of contacts used at the interface of the configurable width buffer device in accessing the at least one memory device. In an alternate embodiment of the present invention, a multiplexer / demultiplexer circuit is provided. A state storage provides a data width for the configurable width buffer and a SPD provides the configurable width buffer and / or module capabilities to the memory system.

Owner:RAMBUS INC

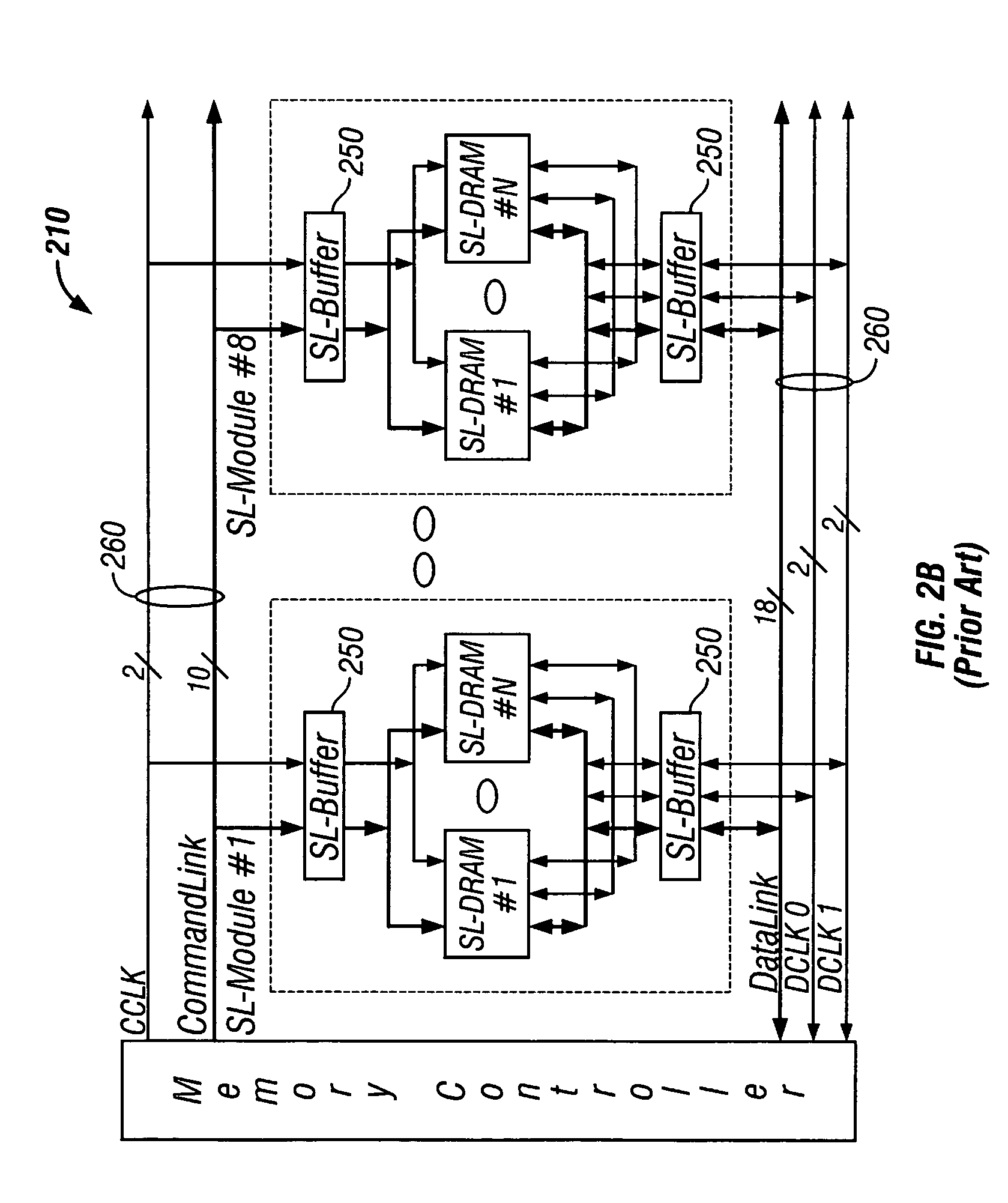

Method of operating a memory system including an integrated circuit buffer device

InactiveUS20050041504A1Eliminate physical inter-dependenceMemory adressing/allocation/relocationDigital storageComputer hardwareInterconnect topology

A memory system architecture / interconnect topology that includes at least one point-to-point link between a master, and at least one memory subsystem. The memory subsystem includes a buffer device coupled to a plurality of memory devices. The memory system may be upgraded through dedicated point-to-point links and corresponding memory subsystems. The master communicates to the plurality of memory devices in each memory subsystem through the respective buffer device via each point-to-point link

Owner:RAMBUS INC

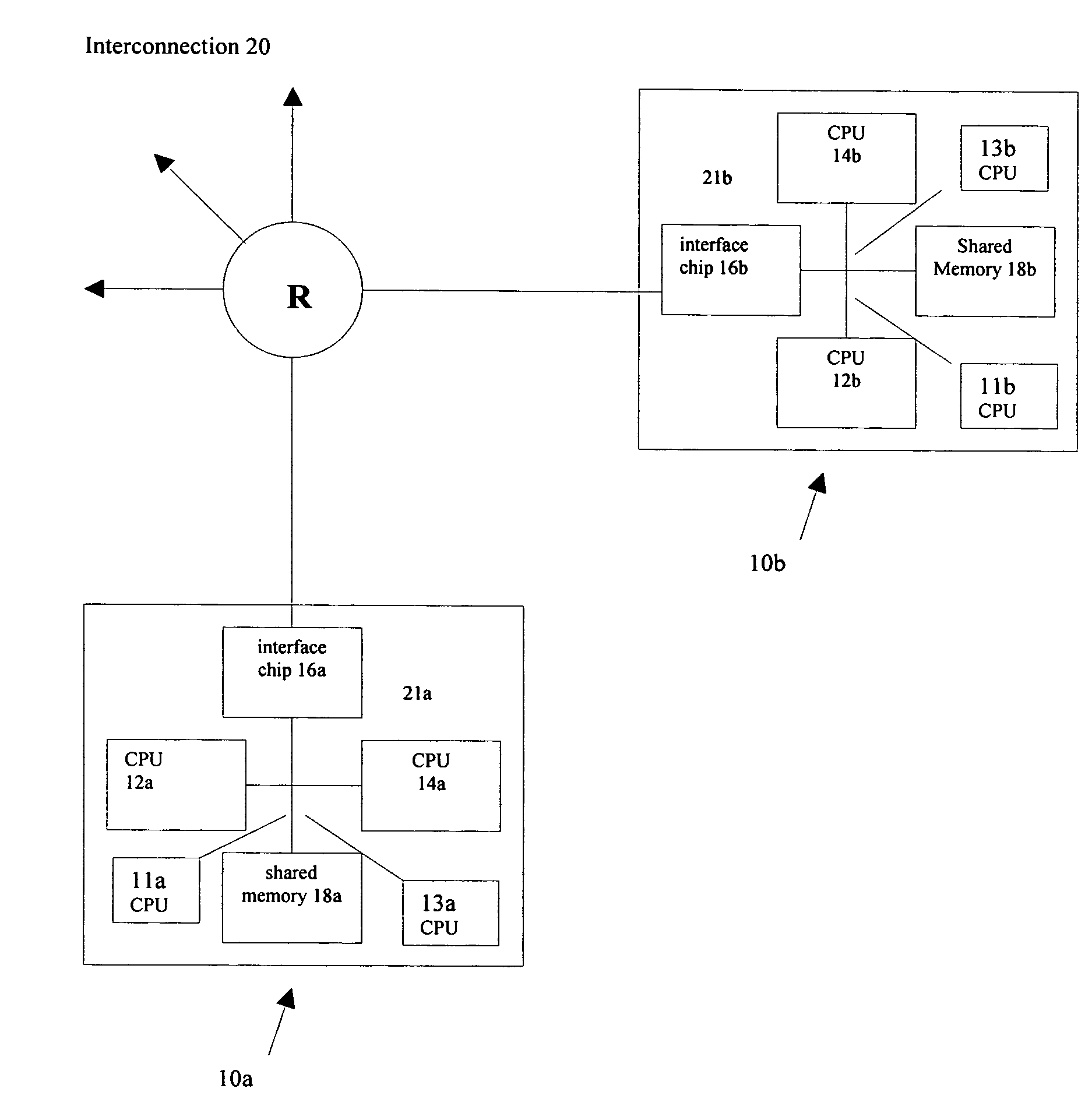

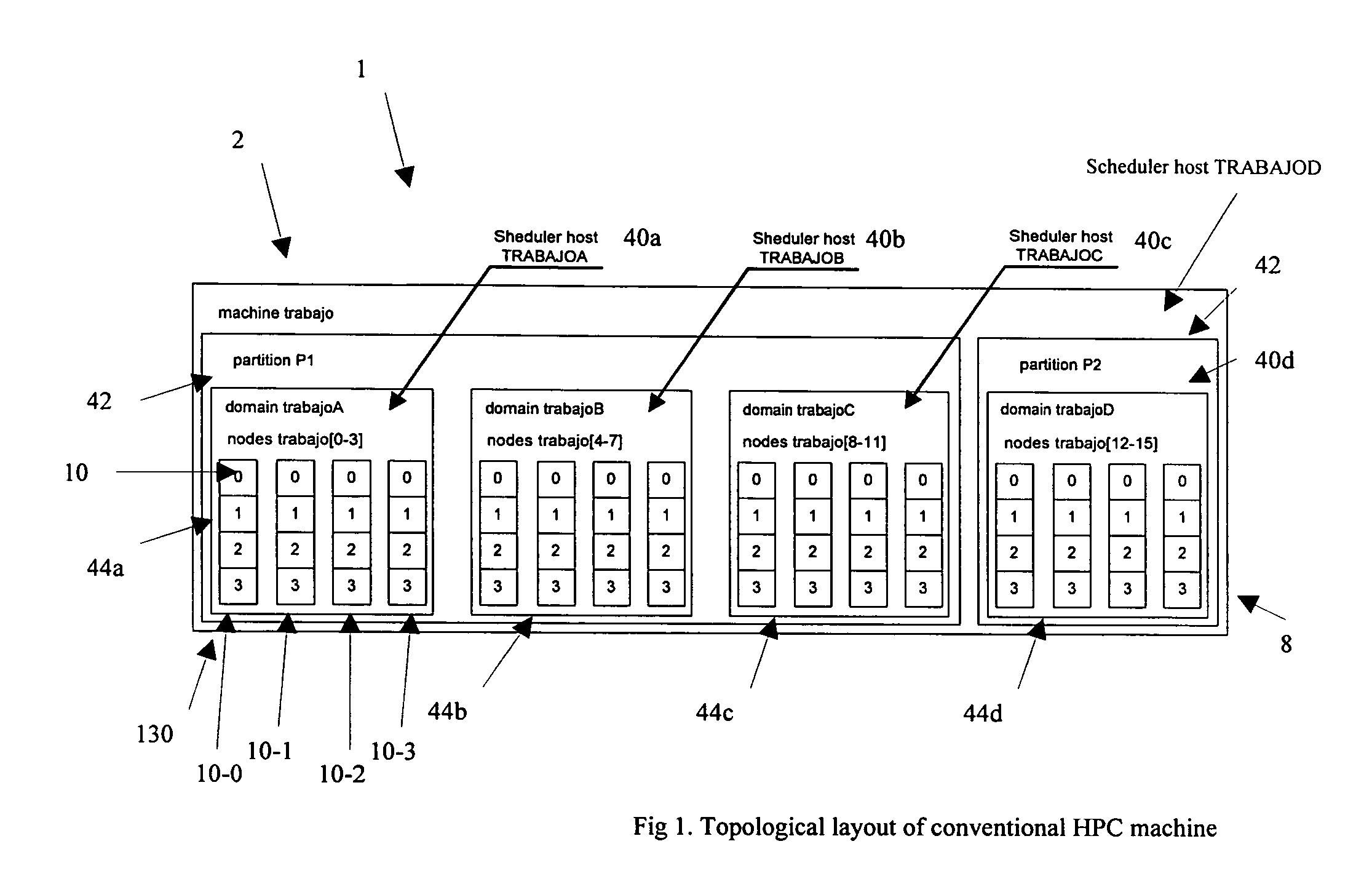

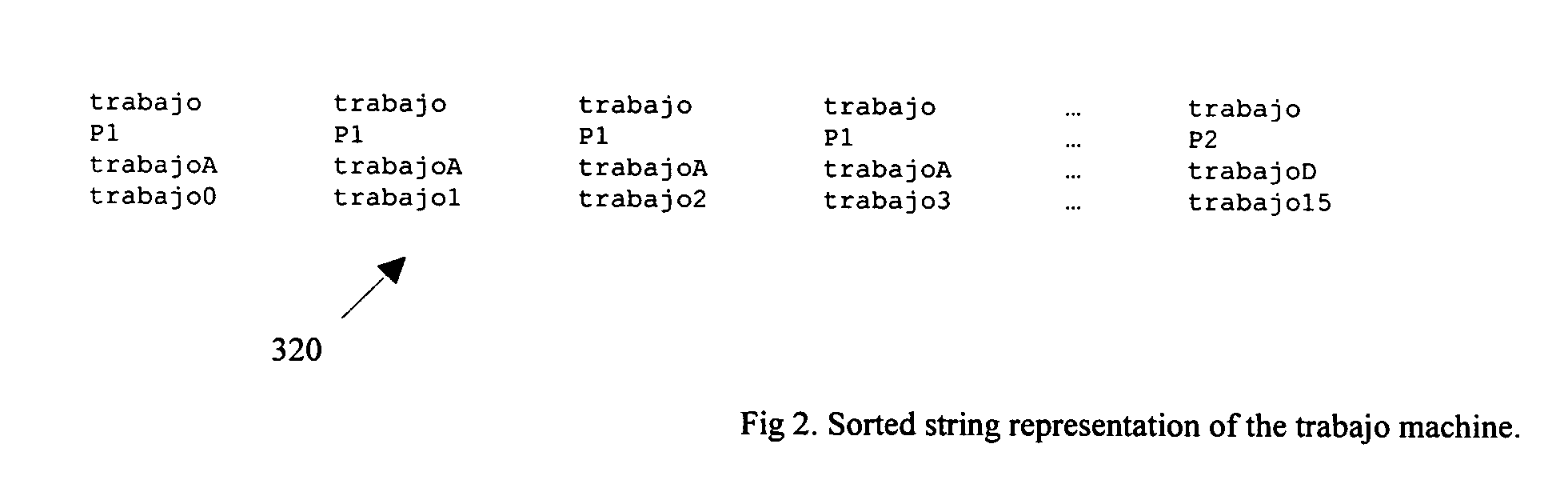

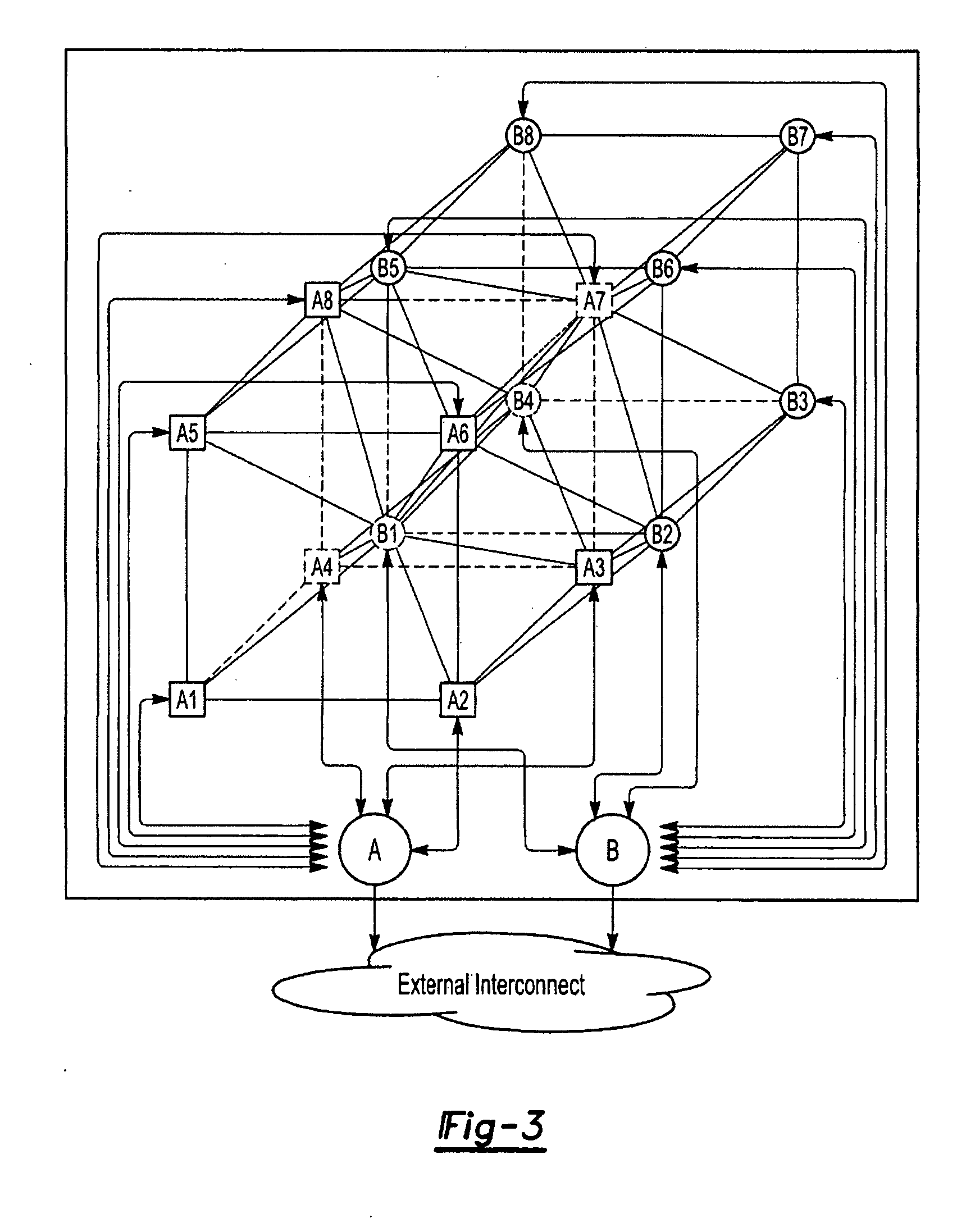

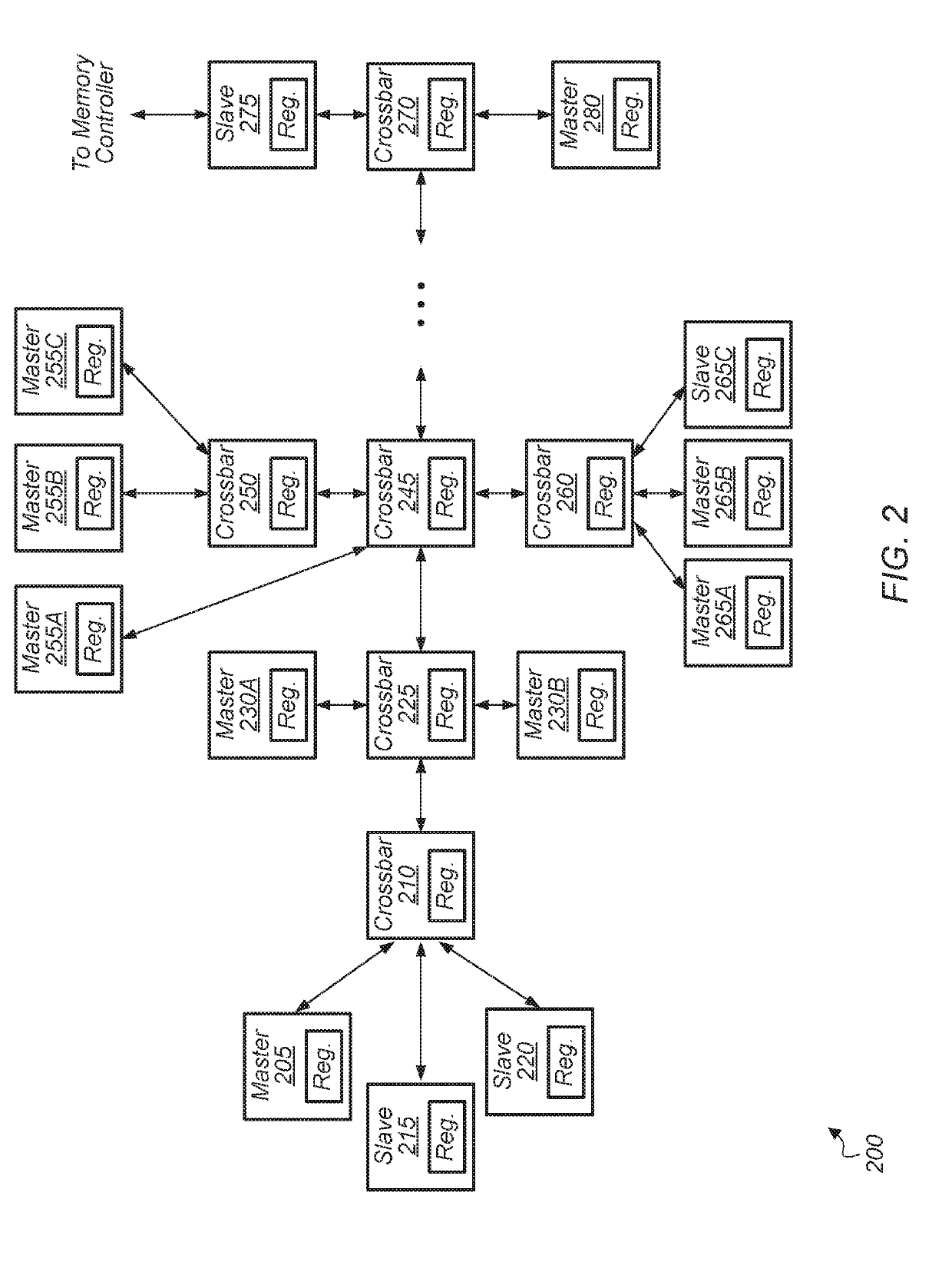

Support of non-trivial scheduling policies along with topological properties

InactiveUS7596788B1Fulfil requirementsMaximize efficiencyMemory architecture accessing/allocationResource allocationMulti processorTopological order

Systems and methods for scheduling jobs in a multiprocessor machine are disclosed. The status of resources in the multiprocessor machine is periodically determined. The status indicates the resources available to execute jobs. This information is accumulated by the topology-monitoring unit and provided to the topology library. The topology library also receives a candidate host list which lists all resources available to execute the job being scheduled based on non-trivial scheduling. The topology library unit generates a free map F indicating the interconnection of the resources available to execute the job. The topology monitoring unit matches jobs to the resources available to execute the jobs, based on resource requirements including shape requirements indicative of interconnections of resources required to execute the job. The topology monitoring unit dispatches the job to the portion of the free map F which matches the shape requirements of the job.

Owner:IBM CORP

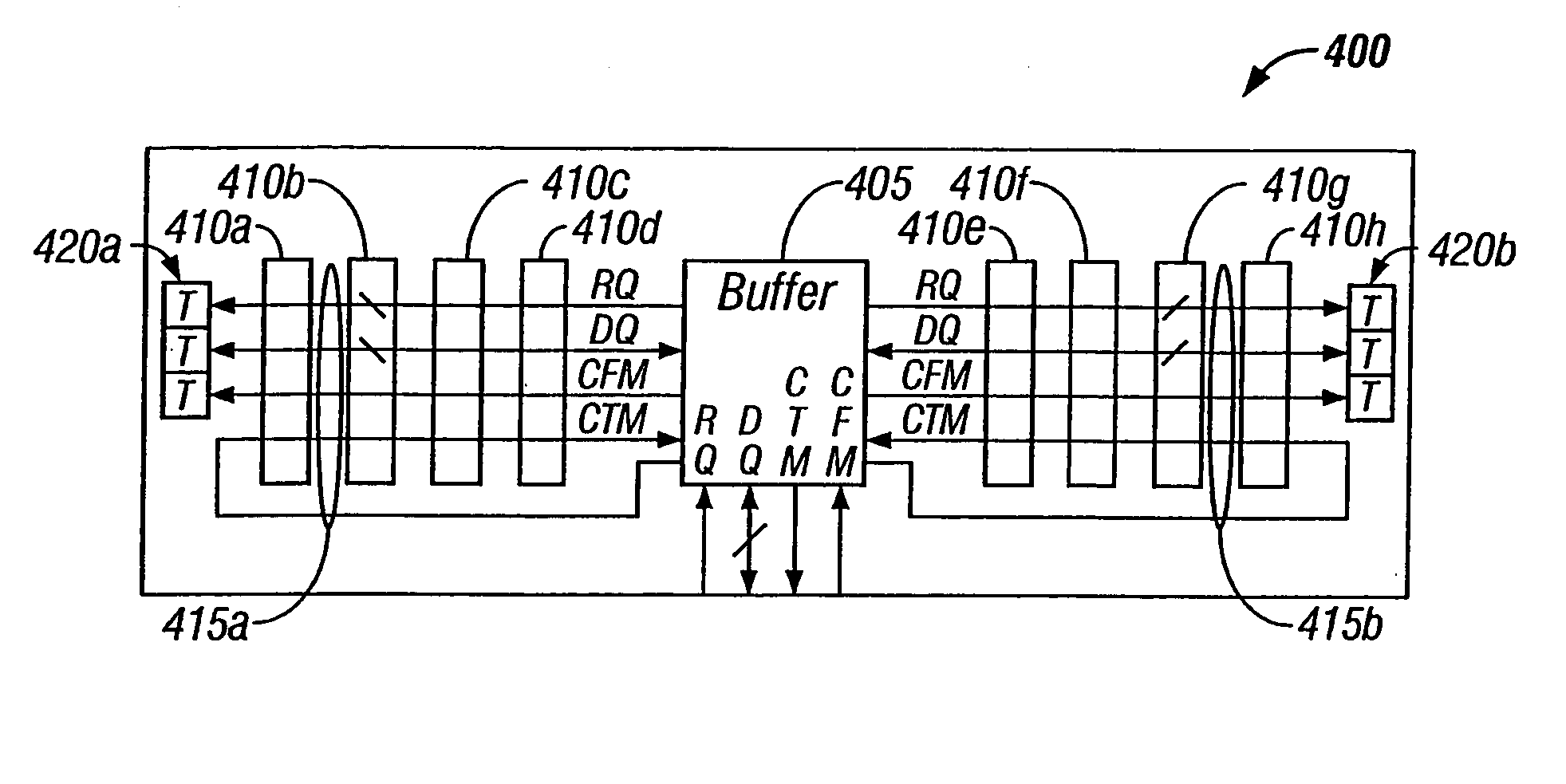

Configurable width buffered module having a bypass circuit

InactiveUS7356639B2Semiconductor/solid-state device manufacturingStatic storageInterconnect topologyDIMM

A memory system architecture / interconnect topology includes a configurable width buffered memory module having a configurable width buffer device with at least one bypass circuit. A buffer device, such as a configurable width buffer device, is positioned between or with at least one integrated circuit memory device positioned on a substrate surface of a memory module, such as a DIMM. The configurable width buffer device is coupled to at least one memory device (by way of an internal channel), entry pin and exit pin on the memory module. The configurable width buffer device includes a multiplexer / demultiplexer circuit coupled to the entry pin and the internal channel for accessing the memory device. A bypass circuit is coupled to the entry pin and the exit pin in order to allow information to be transferred through the memory module to another coupled memory module in the memory system by way of an external channel. In an alternate embodiment of the present invention, two bypass circuits are coupled to a pair of entry and exit pins. In an embodiment of the present invention, a memory system may include at least four interfaces, or sockets, for respective memory modules having configurable width buffer devices with bypass circuits that enable additional upgrade options while reducing memory system access delays.

Owner:RAMBUS INC

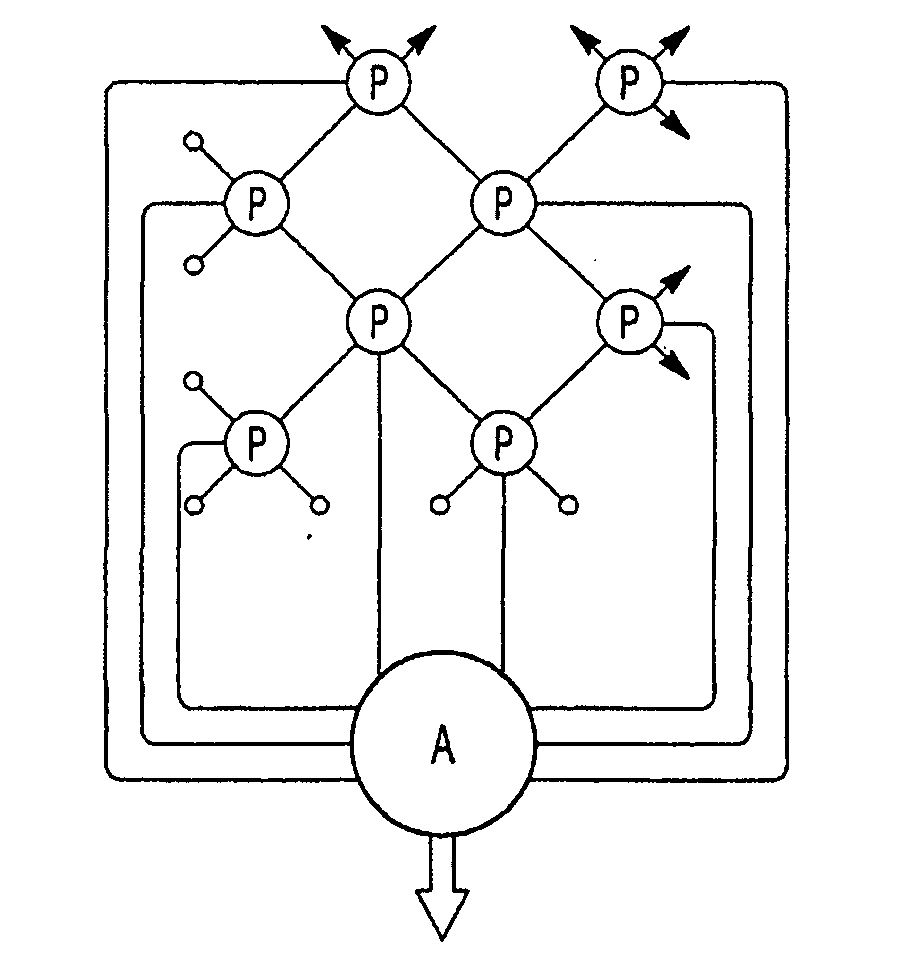

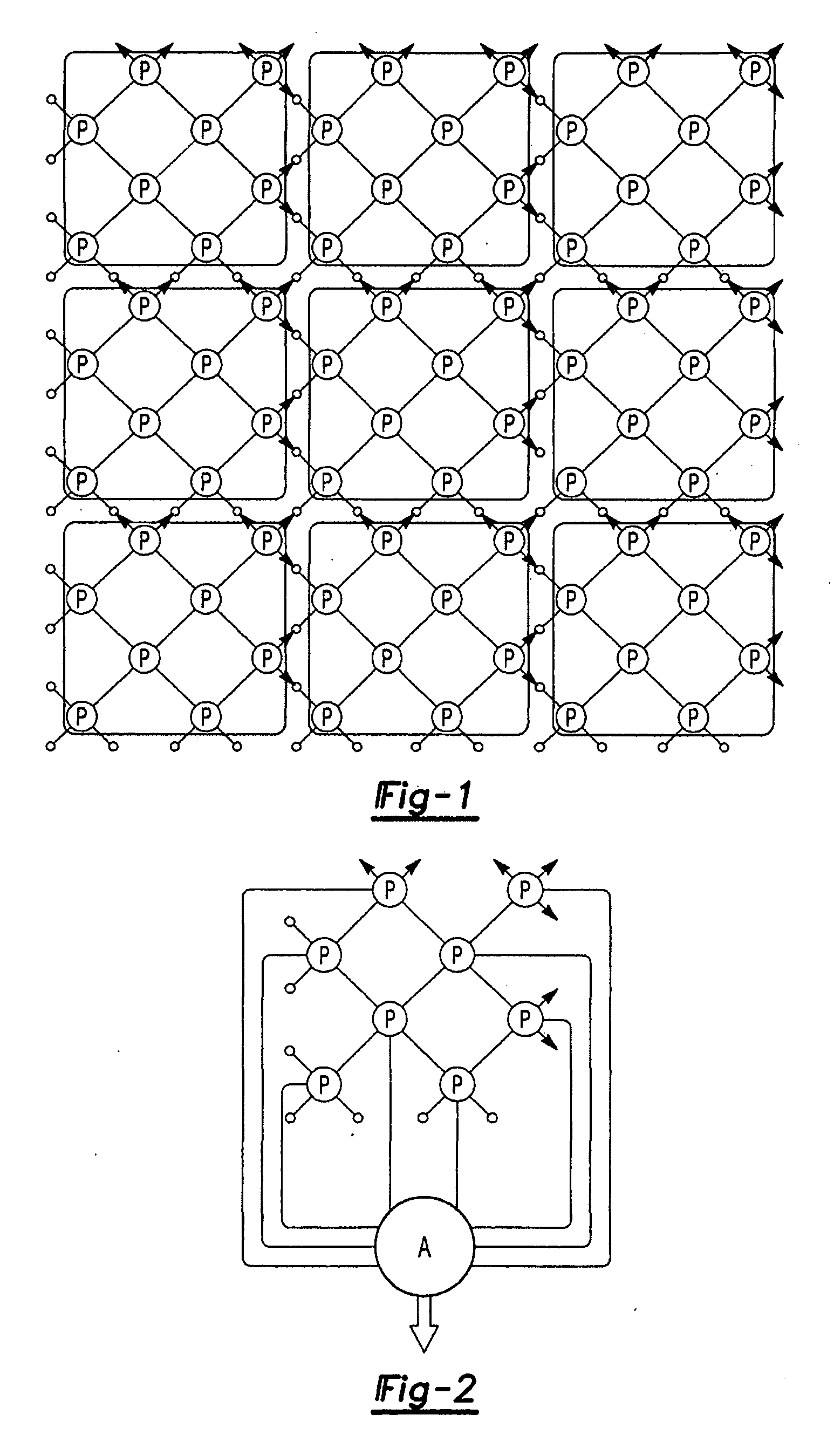

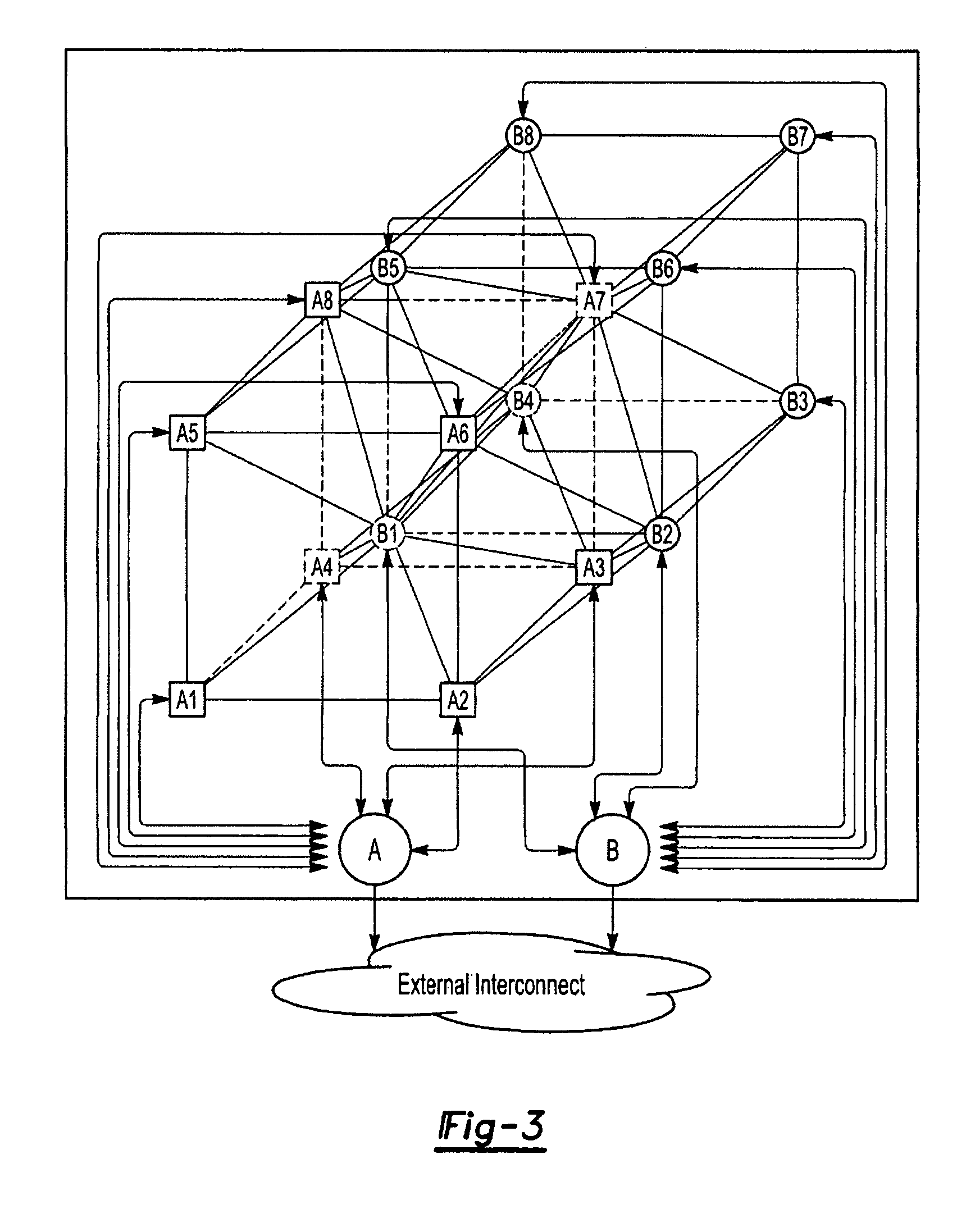

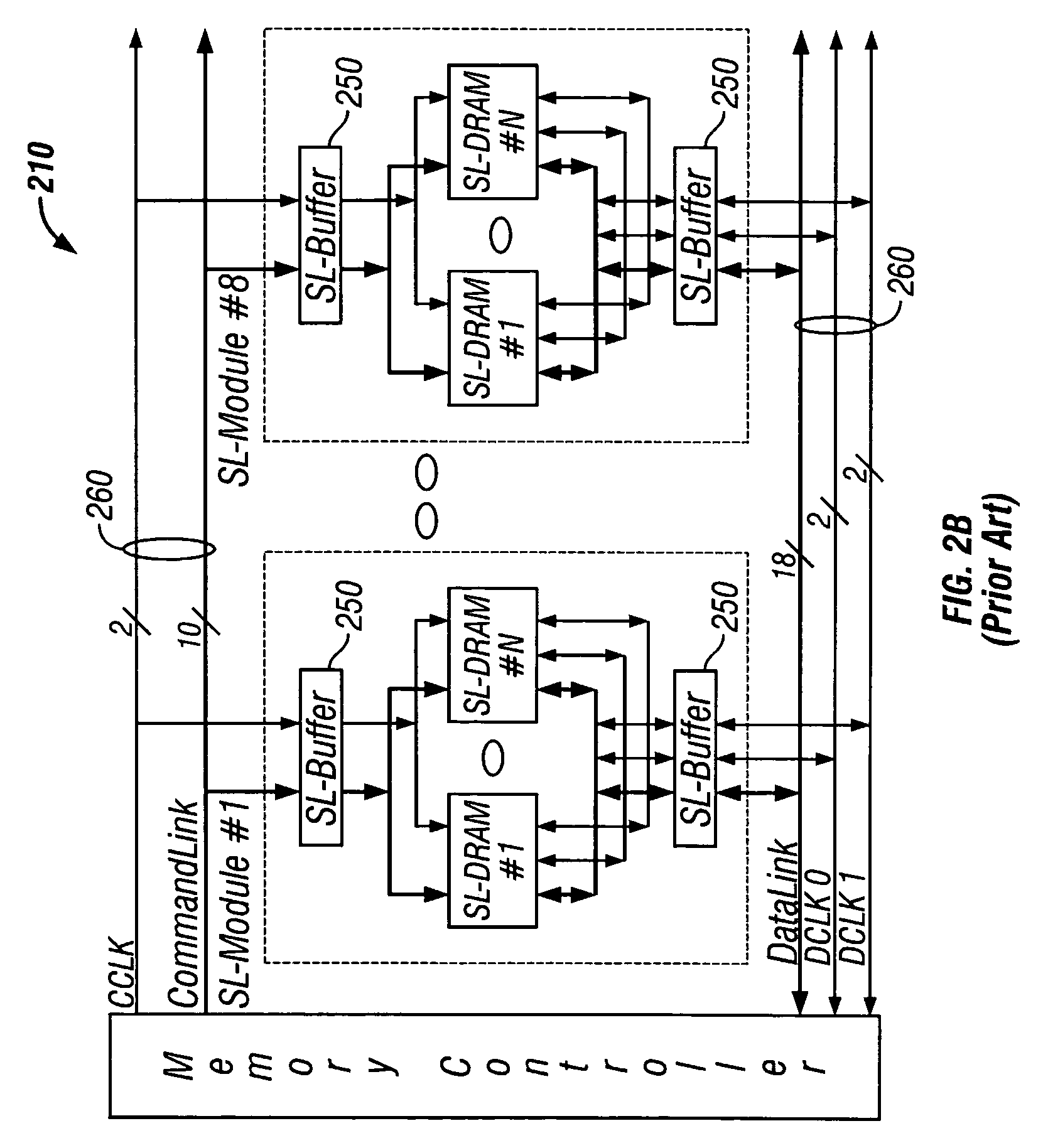

Ultra-scalable supercomputer based on mpu architecture

InactiveUS20090094436A1High-performance and sustained computing resourceHigh-performance and sustained computing resourcesProgram control using stored programsData switching by path configurationSupercomputerTraffic capacity

The invention provides an ultra-scalable supercomputer based on MPU architecture in achieving the well-balanced performance of hundreds of TFLOPS or PFLOPS range in applications. The supercomputer system design includes the interconnect topology and its corresponding routing strategies, the communication subsystem design and implementation, the software and hardware schematic implementations. The supercomputer comprises a plurality of processing nodes powering the parallel processing and Axon nodes connecting computing nodes while implementing the external interconnections. The interconnect topology can be based on MPU architecture and the communication routing logic as required by switching logics is implemented in the FPGA chips while some modular designs for accelerating particular traffic patterns from applications and meliorating the communication overhead are able to be deployed as well.

Owner:SHANGHAI REDNEURONS

Configurable width buffered module having flyby elements

A memory system architecture / interconnect topology includes a configurable width buffered memory module having a configurable width buffer device and at least one flyby element. A buffer device, such as a configurable width buffer device, is positioned between or with at least one integrated circuit memory device positioned on a substrate surface of a memory module, such as a DIMM. A flyby element is positioned on a memory module and / or in the buffer device and includes conductive element or signal line in embodiments of the invention. One or more flyby elements are coupled to one or more memory modules to allow for upgrades of memory modules in a memory system. An asymmetrical flyby topology allows for increasing the number of memory modules to more than two memory modules without increasing any more delay than is present in with two memory modules.

Owner:RAMBUS INC

Buffered Memory Having A Control Bus And Dedicated Data Lines

InactiveUS20080034130A1Memory adressing/allocation/relocationDigital storageInterconnect topologyMultiplexer

A memory system architecture / interconnect topology includes a configurable width buffered module having a configurable width buffer device. The configurable width buffer device is coupled to at least one memory device on the configurable width memory module. The configurable width buffer device includes an interface and a configurable serialization circuit capable of varying a data path width or a number of contacts used at the interface of the configurable width buffer device in accessing the at least one memory device. In an alternate embodiment of the present invention, a multiplexer / demultiplexer circuit is provided. A state storage provides a data width for the configurable width buffer and a SPD provides the configurable width buffer and / or module capabilities to the memory system.

Owner:RAMBUS INC

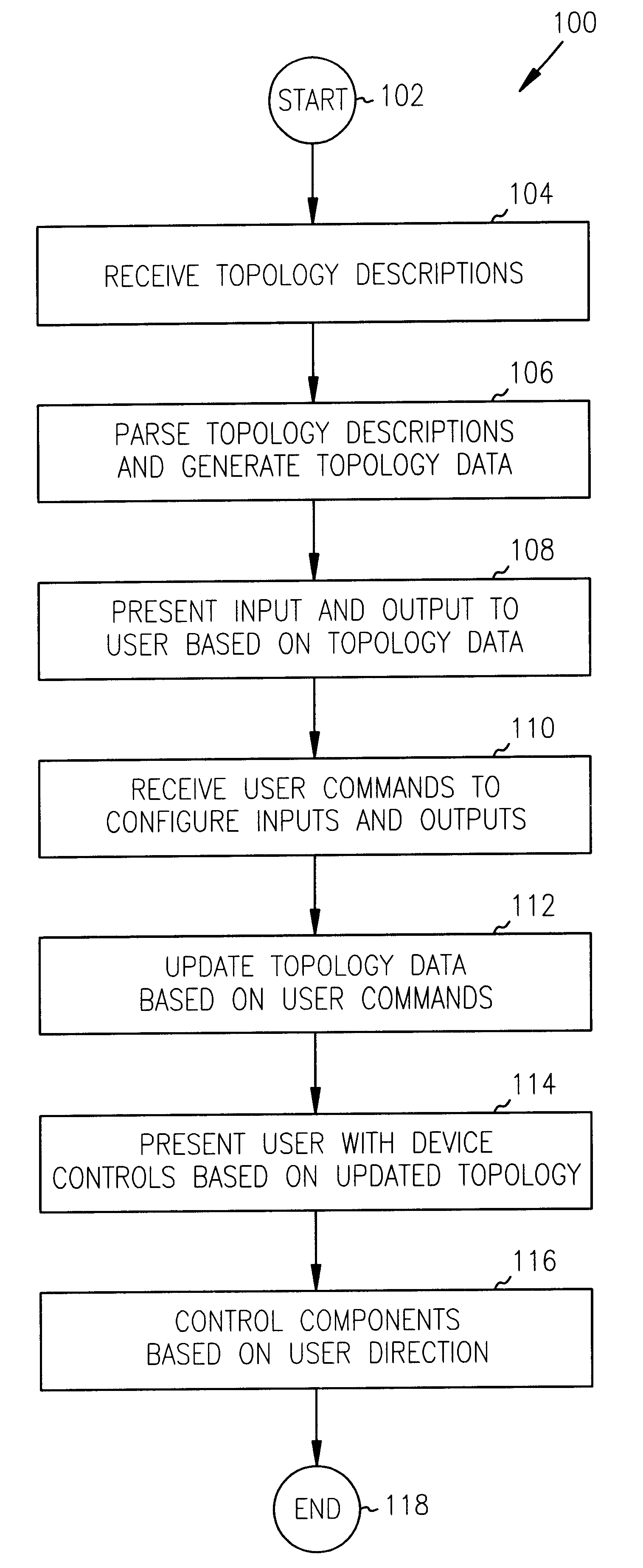

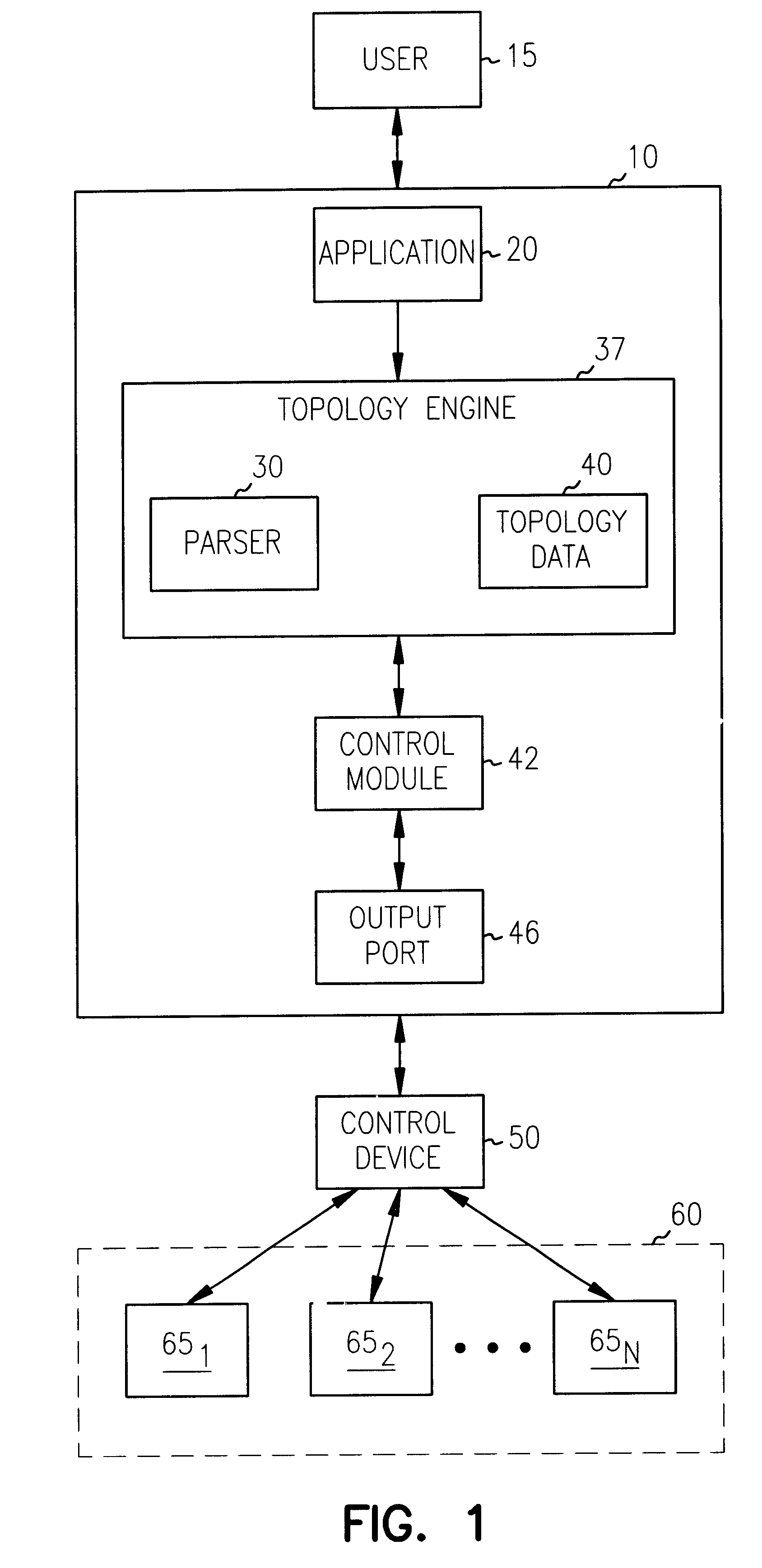

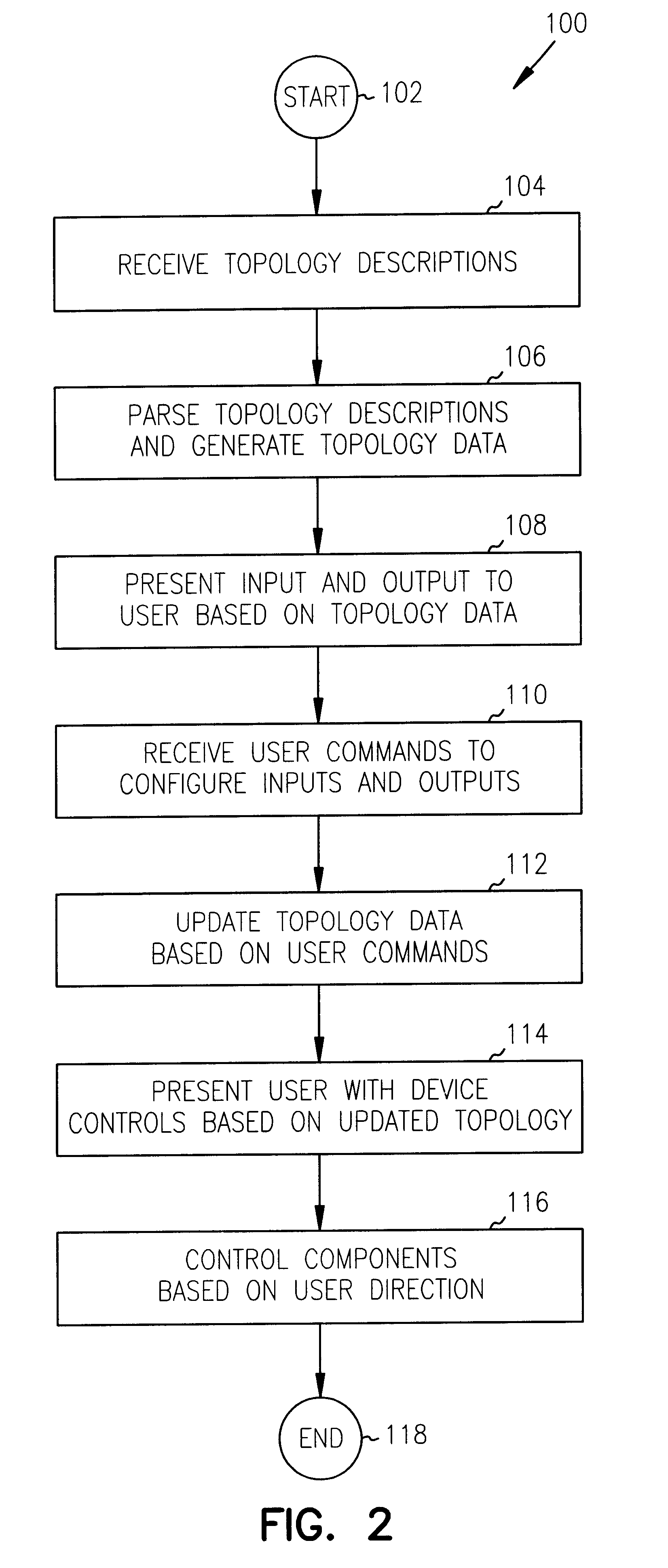

Computer processable interconnect topology

InactiveUS6430526B1Television system detailsRecord information storageVideocassette recorderCassette recorder

A computing system for processing a topology description language that describes an electronic environment having one or more electronic components such as a video cassette recorder (VCR), a television, a compact disc player, and an audio / video receiver. The computing system processes the description language in order to display suitable configurations, monitor usage, and even directly control the electronic components. The computing system includes a topology engine that processes the unique topology description language and generates topology data as a function of the topology descriptions. The topology engine provides an application programming interface (API) by which applications, such as a user interface, configure and control the electronic components.

Owner:INTEL CORP

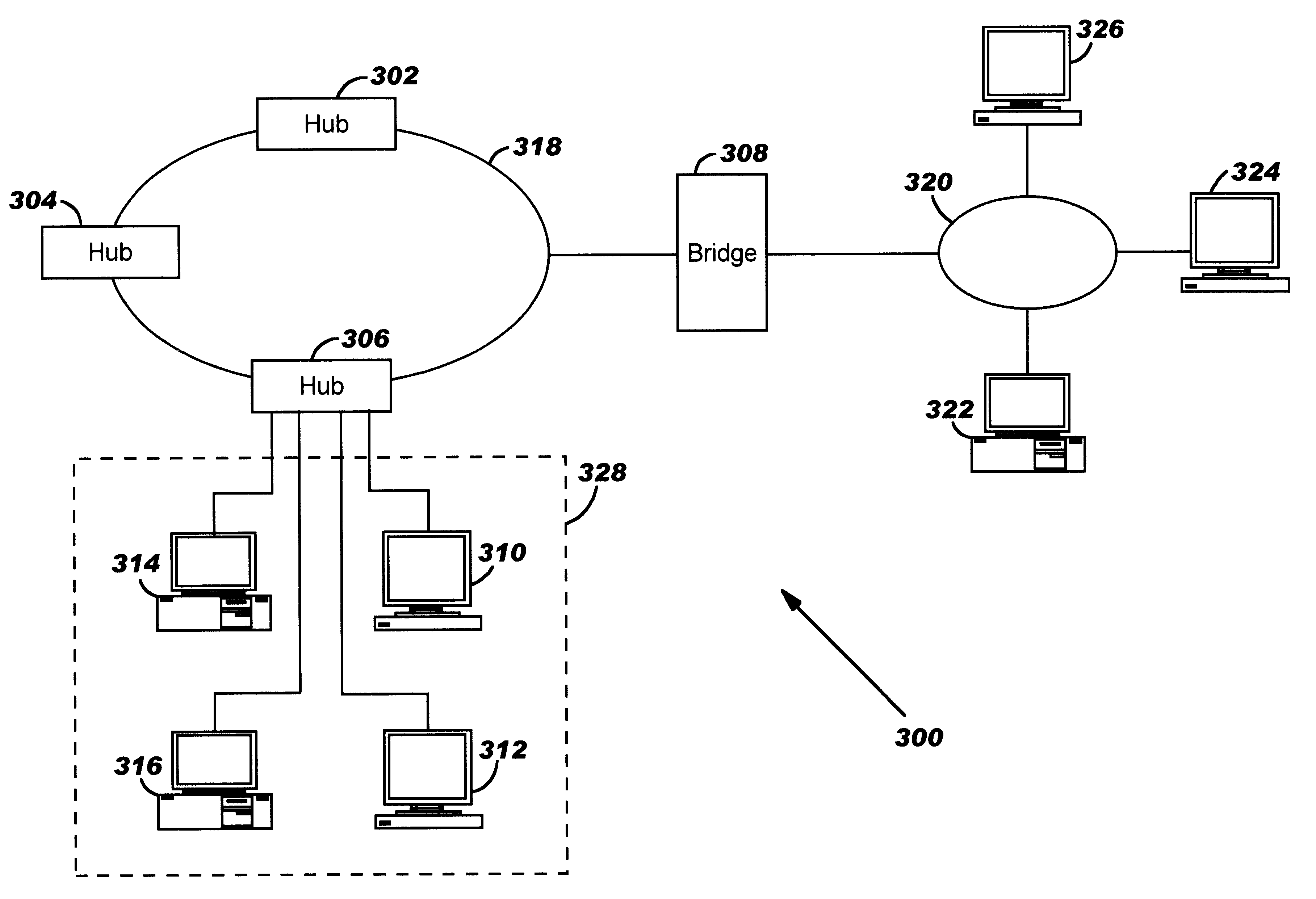

Token ring network topology discovery and display

InactiveUS6483812B1Efficient collectionReduce network trafficError preventionTransmission systemsInterconnect topologyData transmission

A method and system for determining the topology of a communications network that utilizes routing information fields contained within transmission frames for controlling routine transmissions. First, a plurality of transmission frames associated with routine data transmissions are collected. Next, a plurality of routing information fields are extracted from the plurality of transmission frames. Thereafter, the plurality of routing information frames are analyzed and parsed, thereby yielding interconnected topology data. Finally, the interconnected topology data from the plurality of routing information fields is converted and stored into programming language data objects, such that the data objects may thereafter be utilized to display the interconnected topology of the communications network.

Owner:IBM CORP

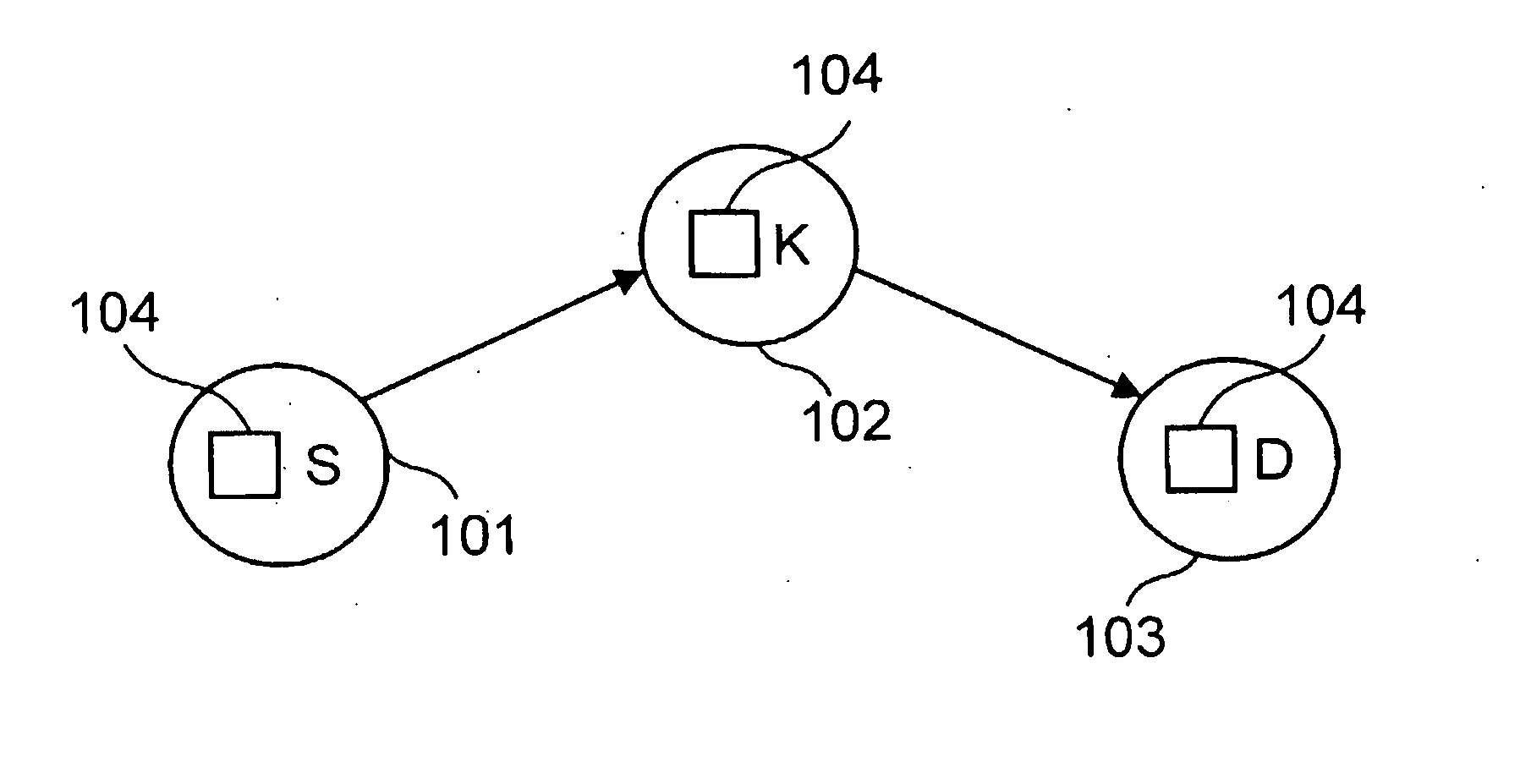

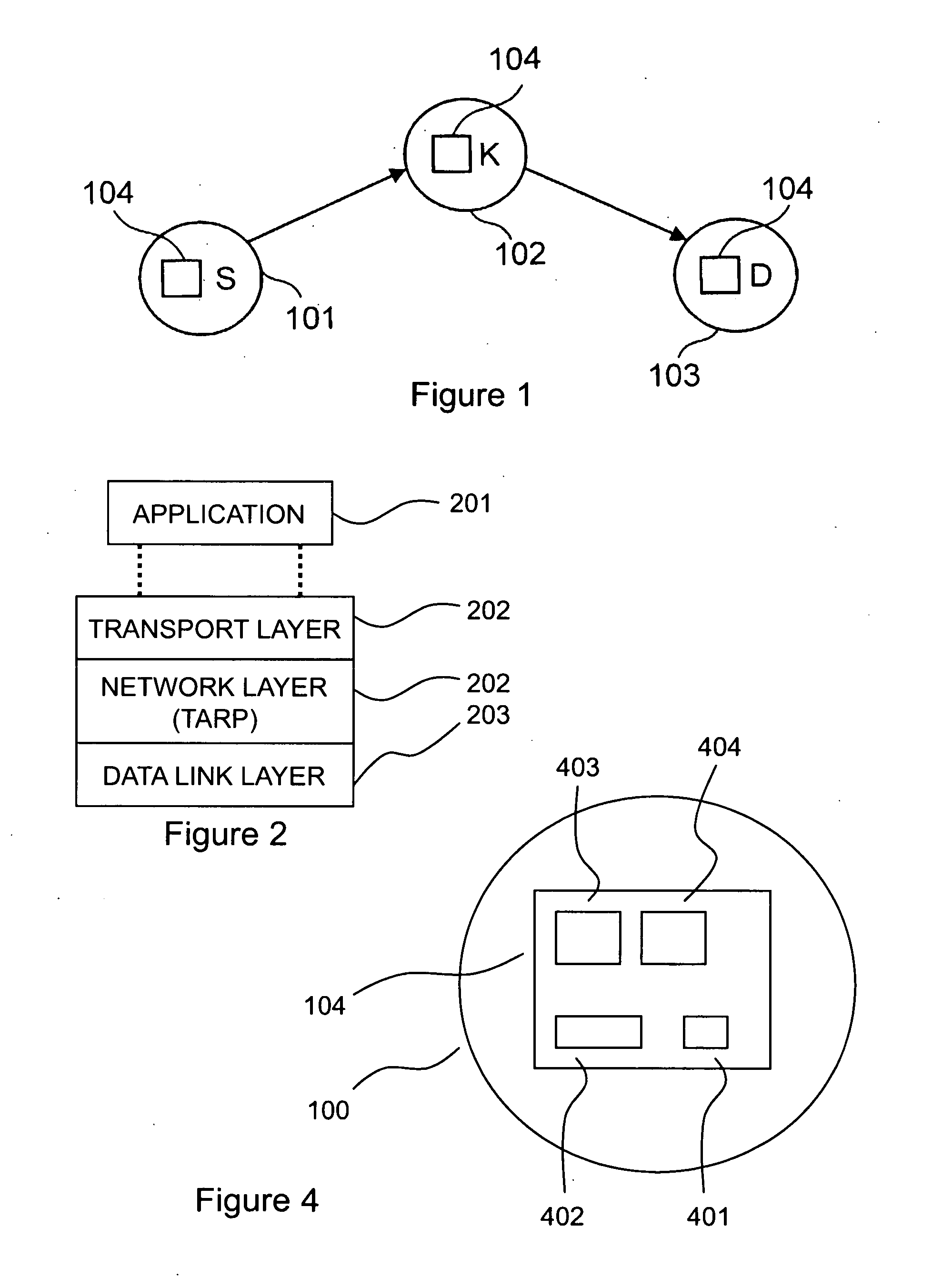

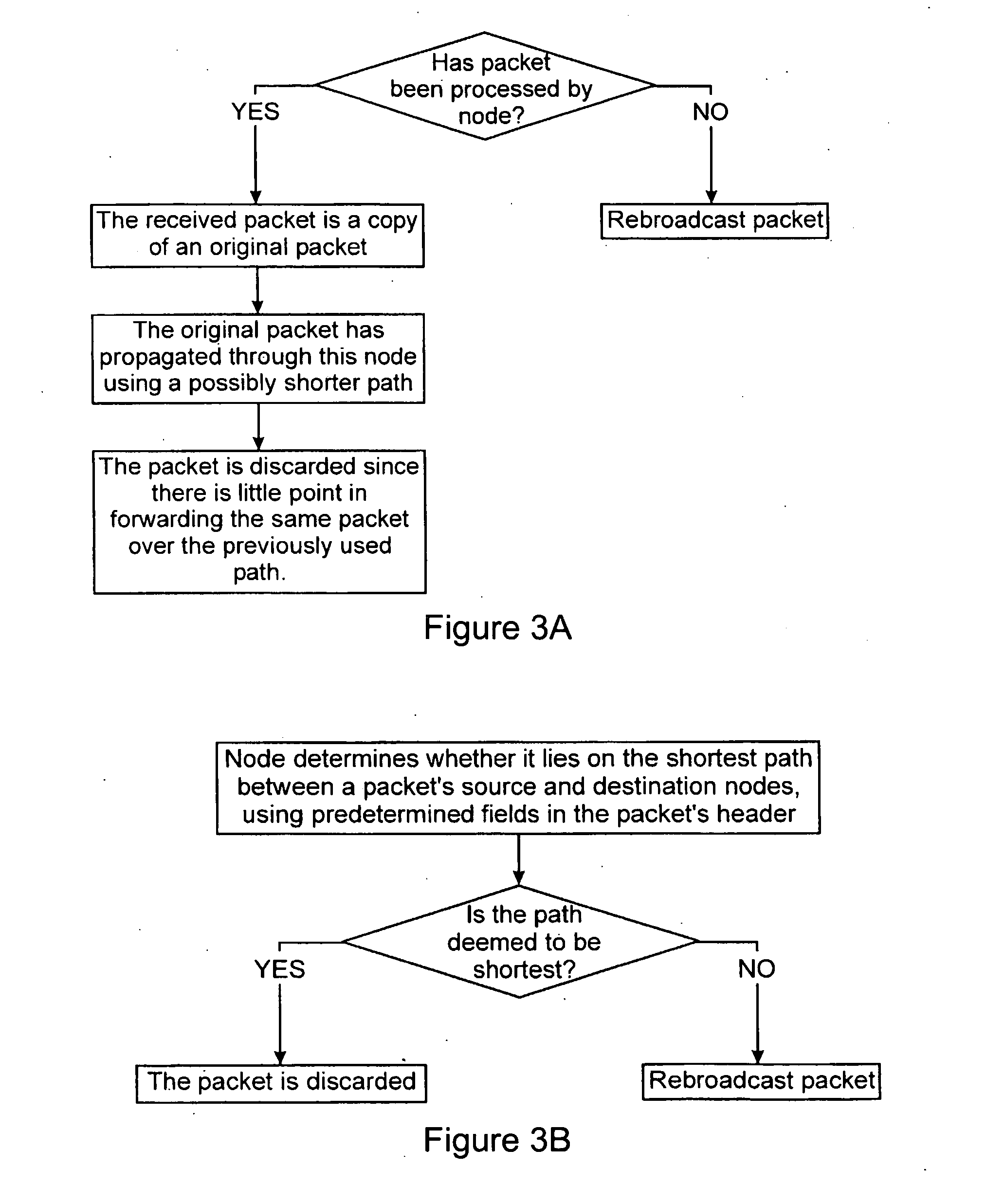

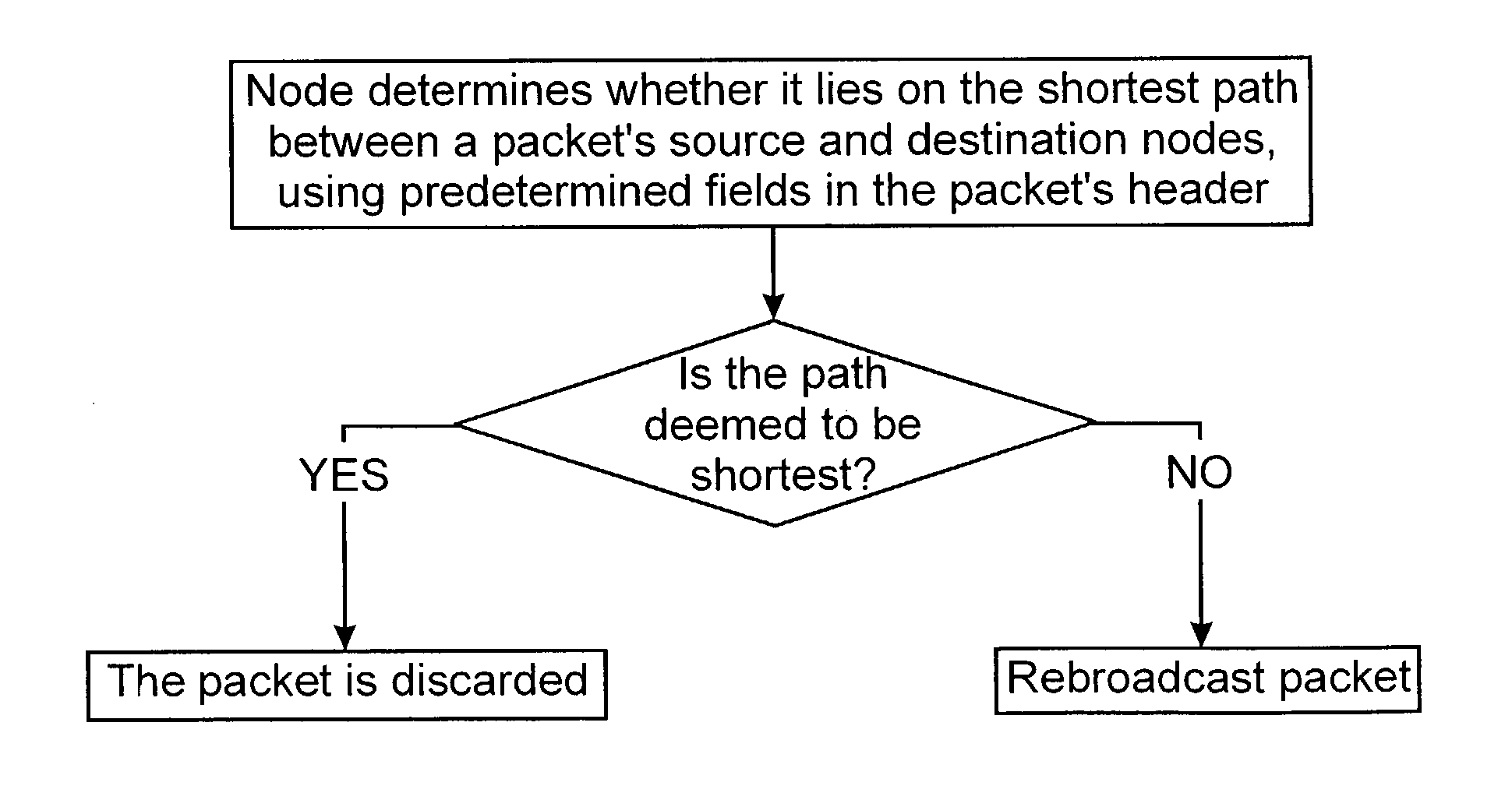

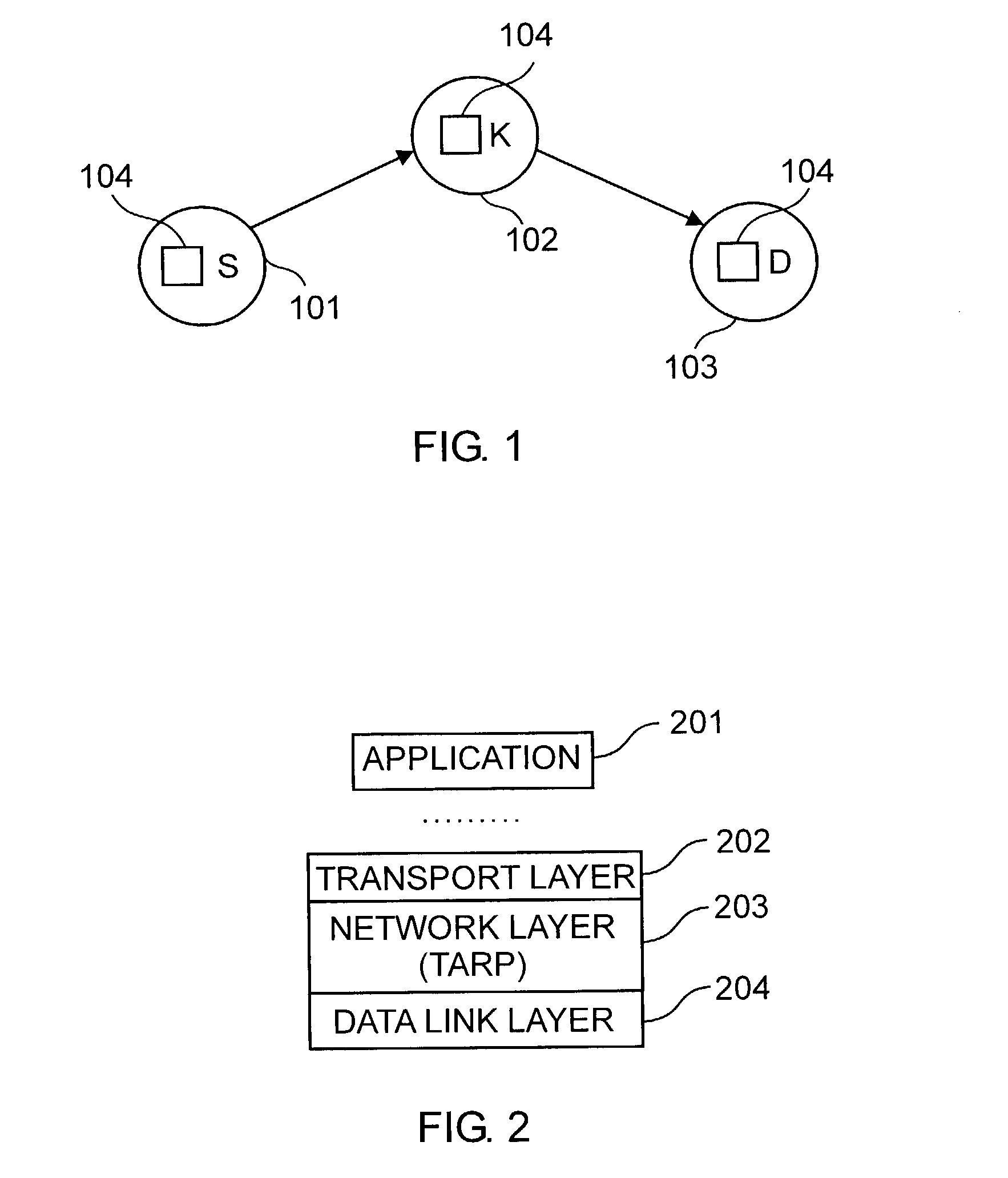

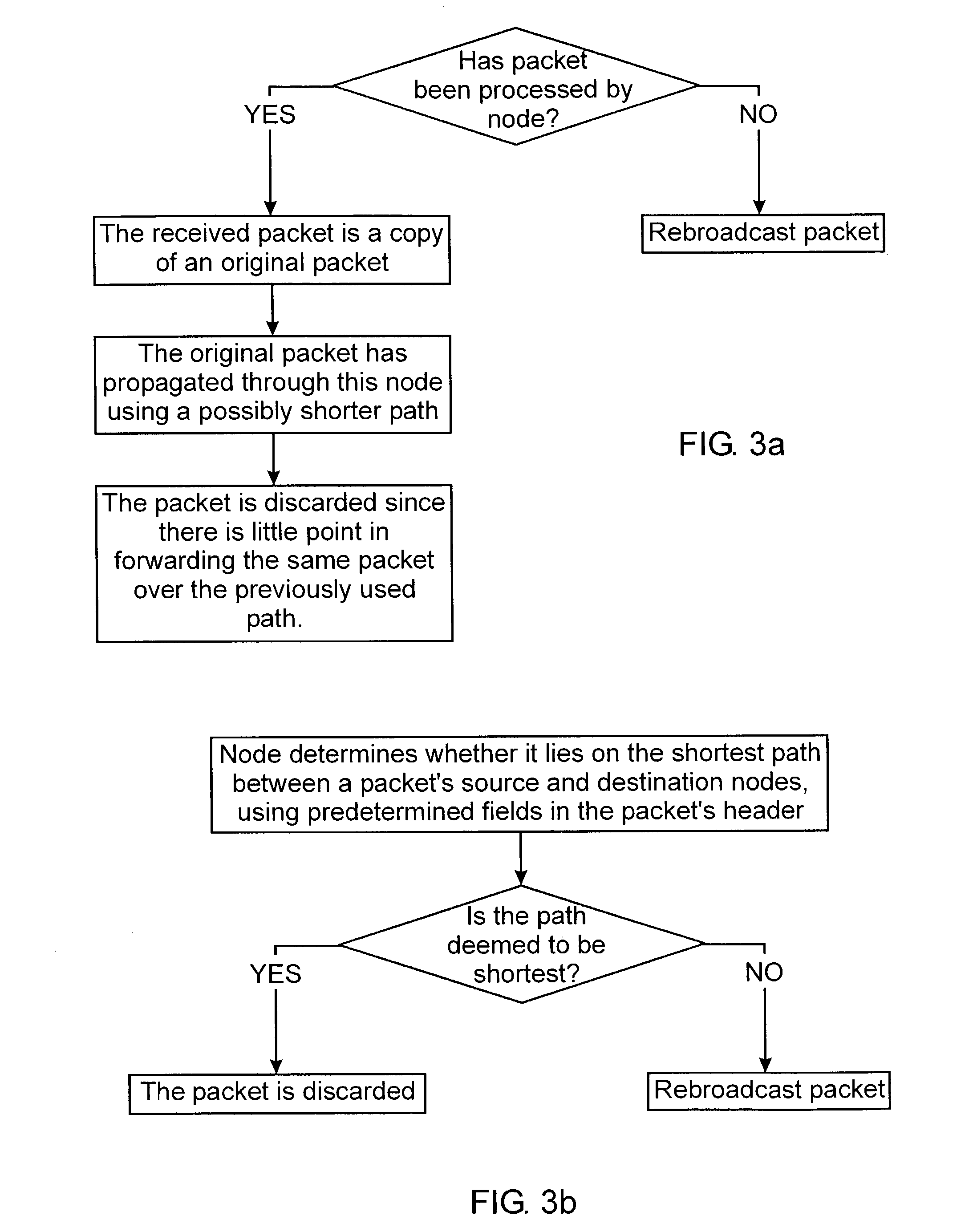

Method for Routing Ad-Hoc Signals

InactiveUS20100254316A1Error prevention/detection by using return channelNetwork topologiesInterconnect topologyBroadcast packet

Owner:INTEL CORP

Buffered memory having a control bus and dedicated data lines

InactiveUS7526597B2Memory adressing/allocation/relocationDigital storageParallel computingControl bus

A memory system architecture / interconnect topology includes a configurable width buffered module having a configurable width buffer device. The configurable width buffer device is coupled to at least one memory device on the configurable width memory module. The configurable width buffer device includes an interface and a configurable serialization circuit capable of varying a data path width or a number of contacts used at the interface of the configurable width buffer device in accessing the at least one memory device. In an alternate embodiment of the present invention, a multiplexer / demultiplexer circuit is provided. A state storage provides a data width for the configurable width buffer and a SPD provides the configurable width buffer and / or module capabilities to the memory system.

Owner:RAMBUS INC

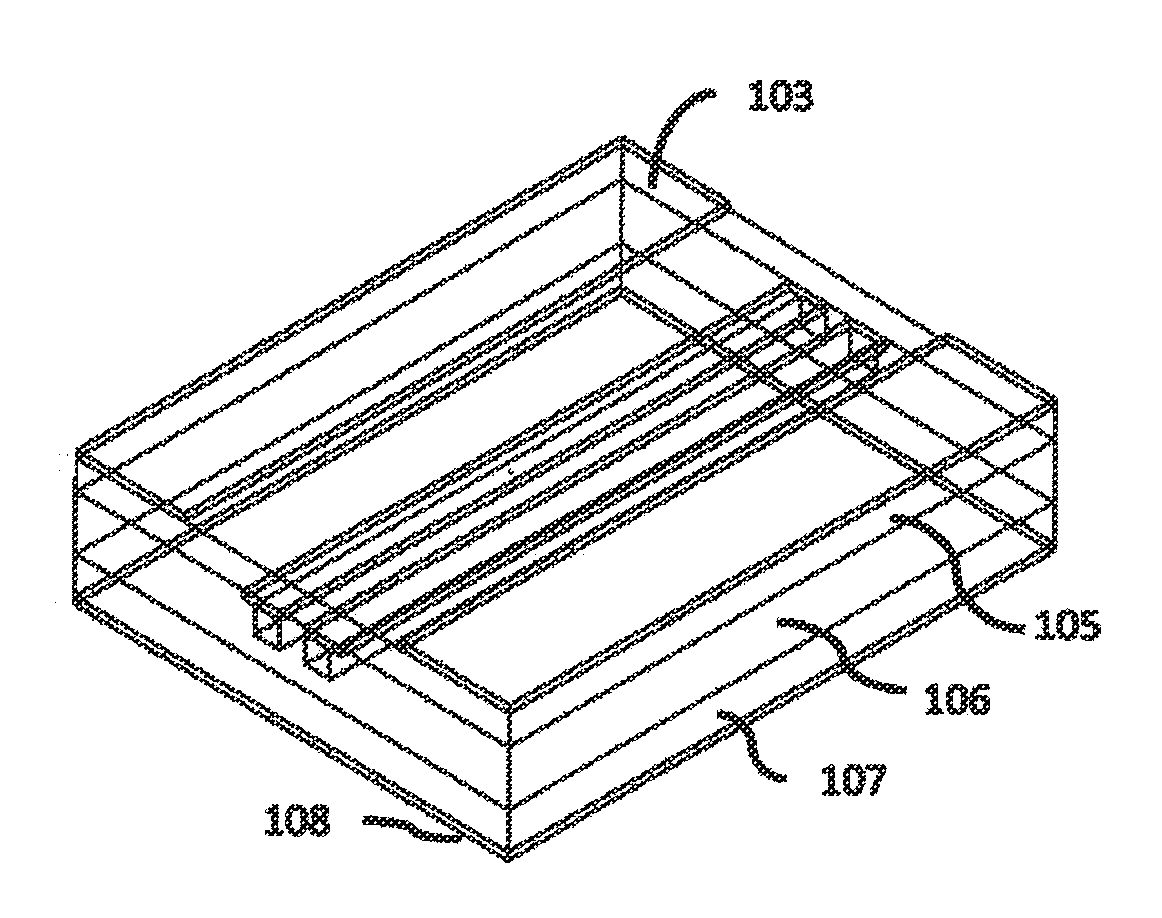

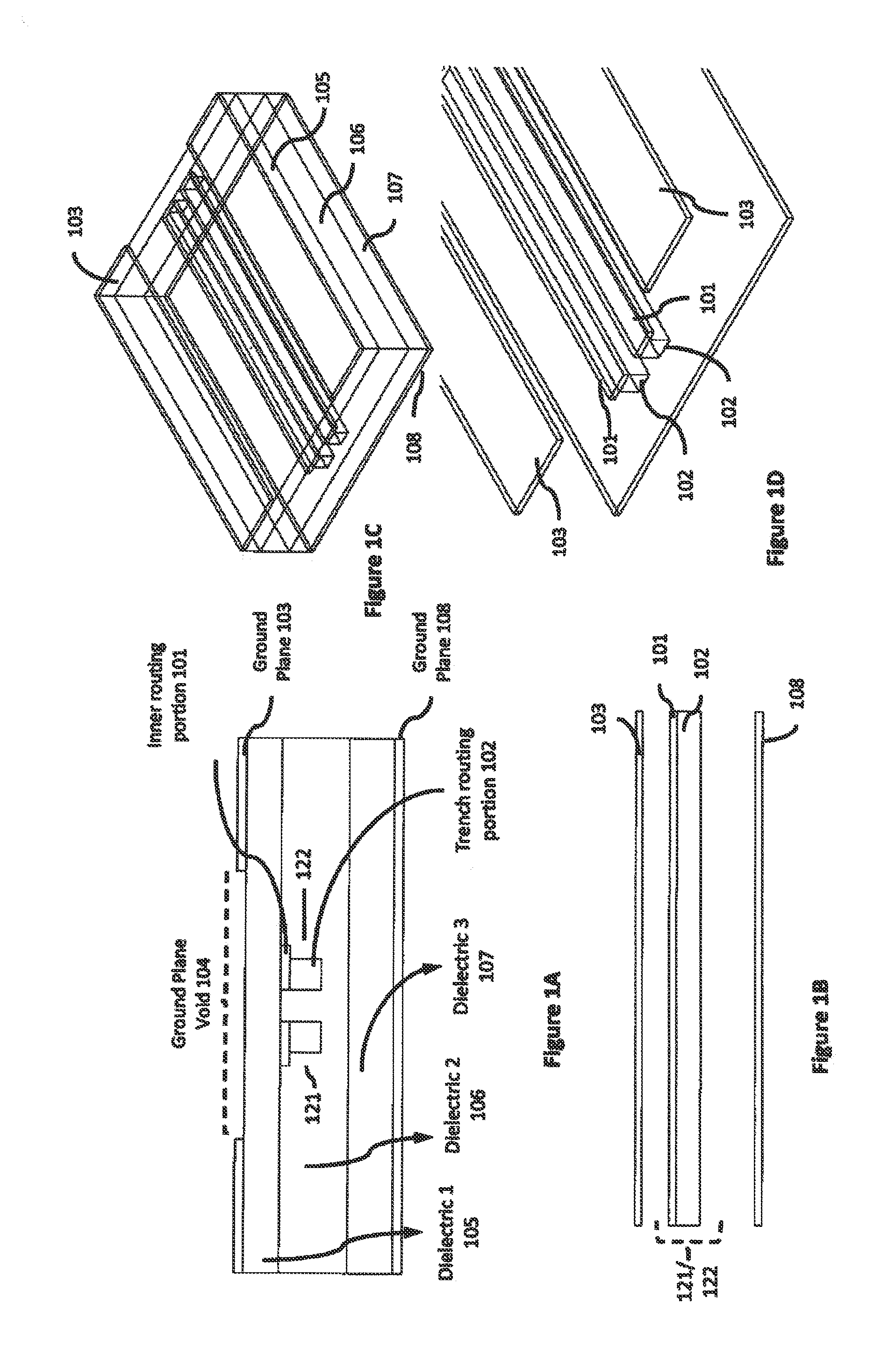

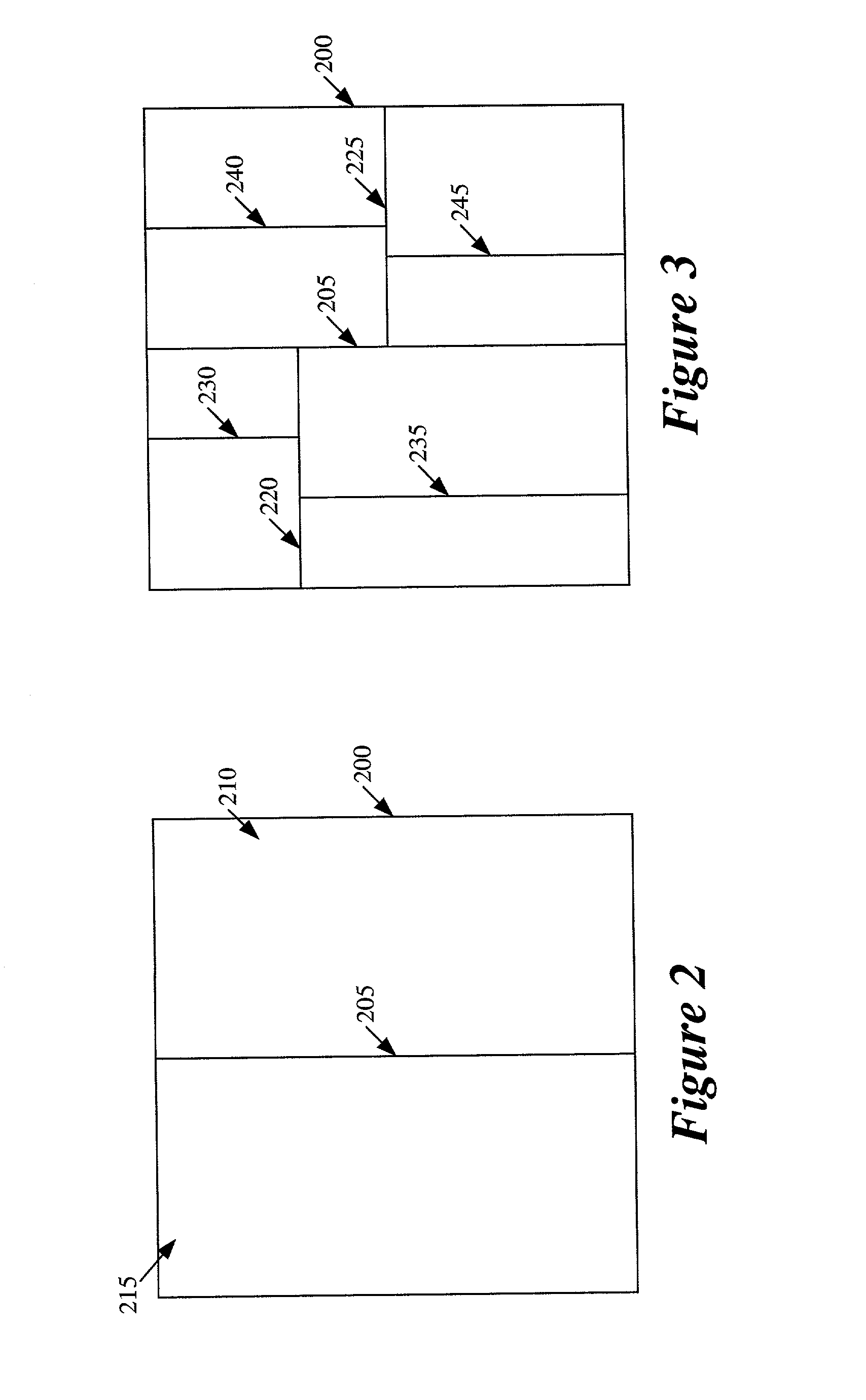

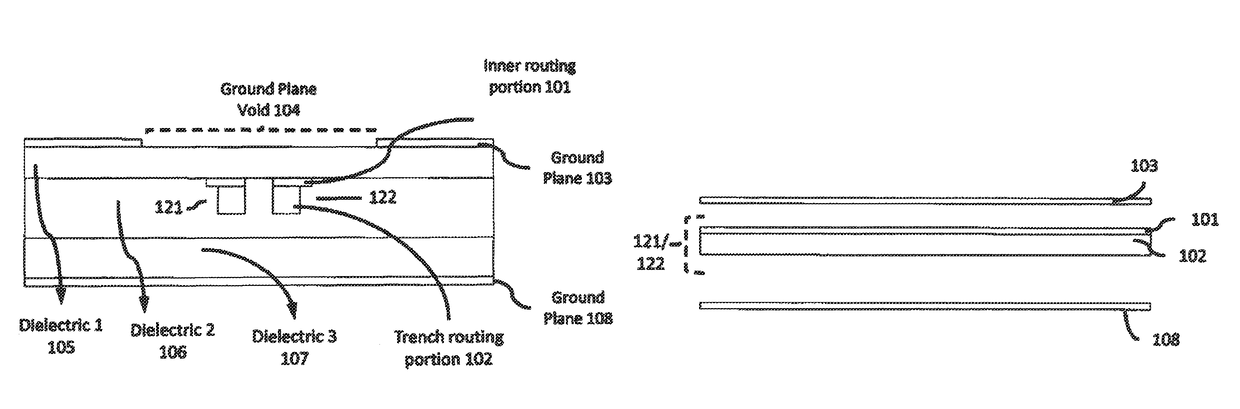

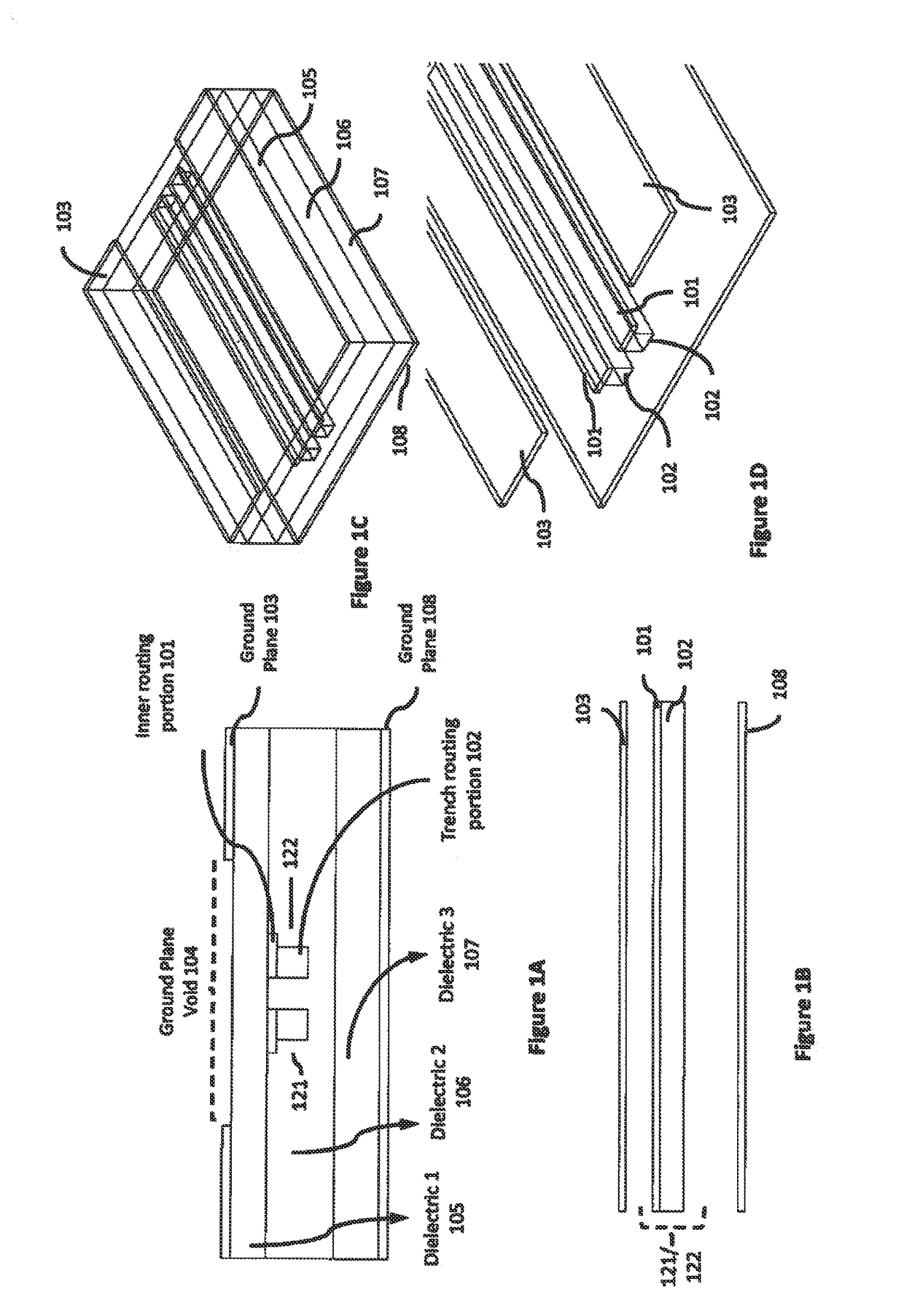

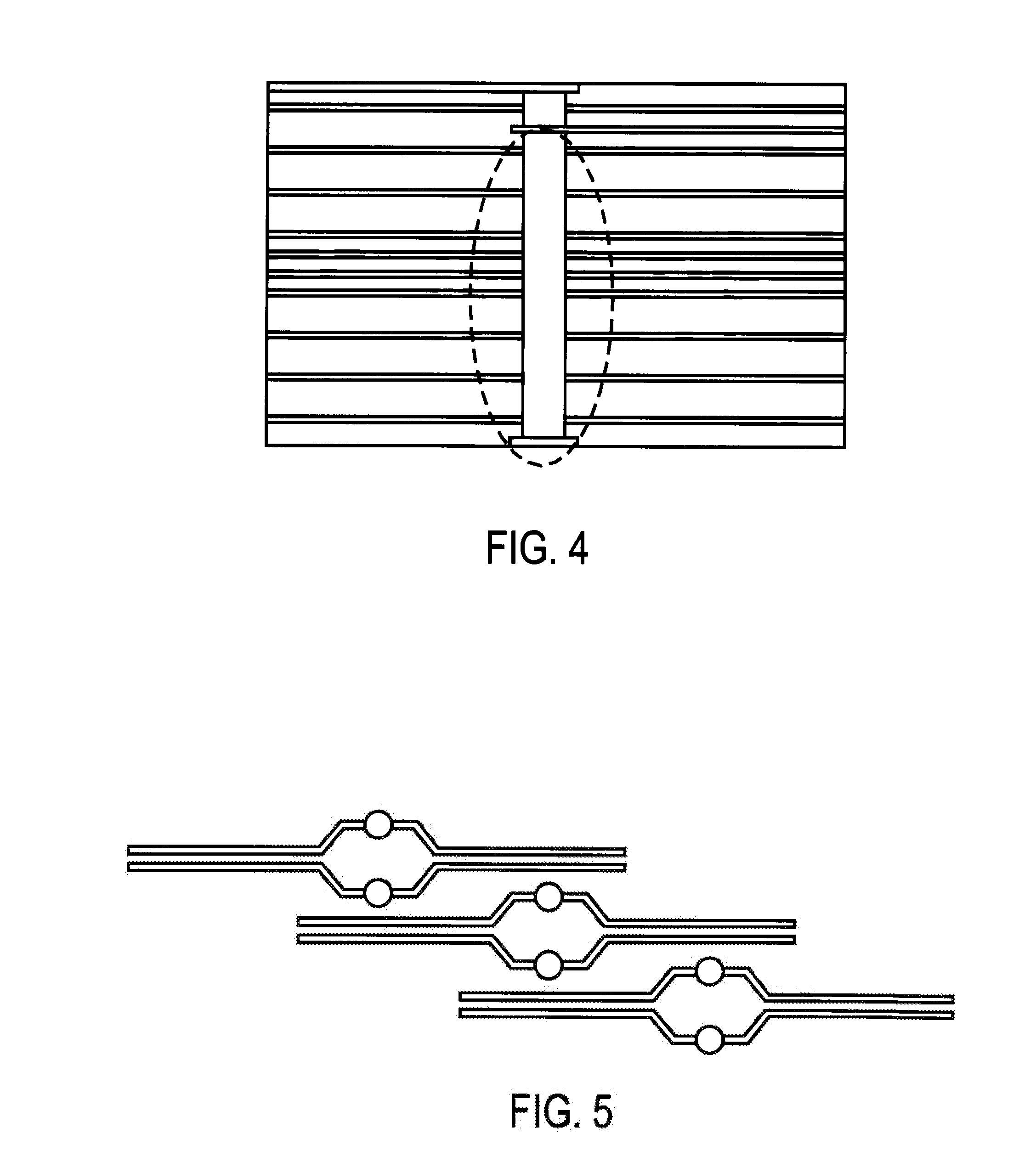

Vertical trench routing in a substrate

ActiveUS20160174374A1Semiconductor/solid-state device detailsPrinted circuit aspectsInterconnect topologyElectrical conductor

An interconnect topology that includes vertical trench routing in a substrate is disclosed. In one embodiment, the interconnect comprises a substrate having a plurality of layers including a first ground plane layer; a pair of signal conductors that form a differential signal pair, each conductor of the pair of signal conductors having a first portion and a second portion, the second portion extending from the first portion into at least one of the plurality of layers, wherein width of the second portion is less than width of the first portion; and wherein the first ground plane layer is only a first partial layer and has a first void region that is closer to the pair of signal conductors than the first partial layer.

Owner:INTEL CORP

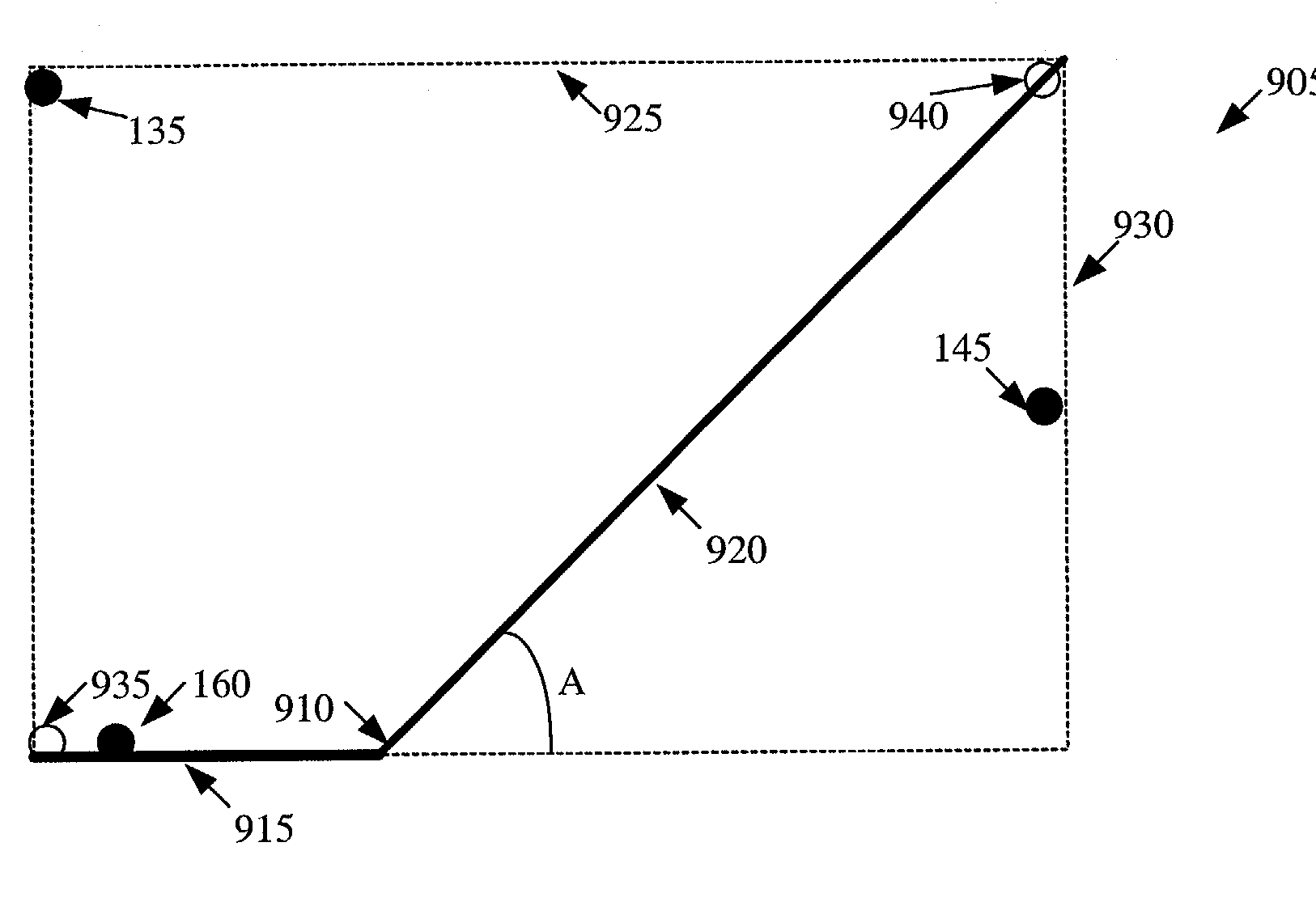

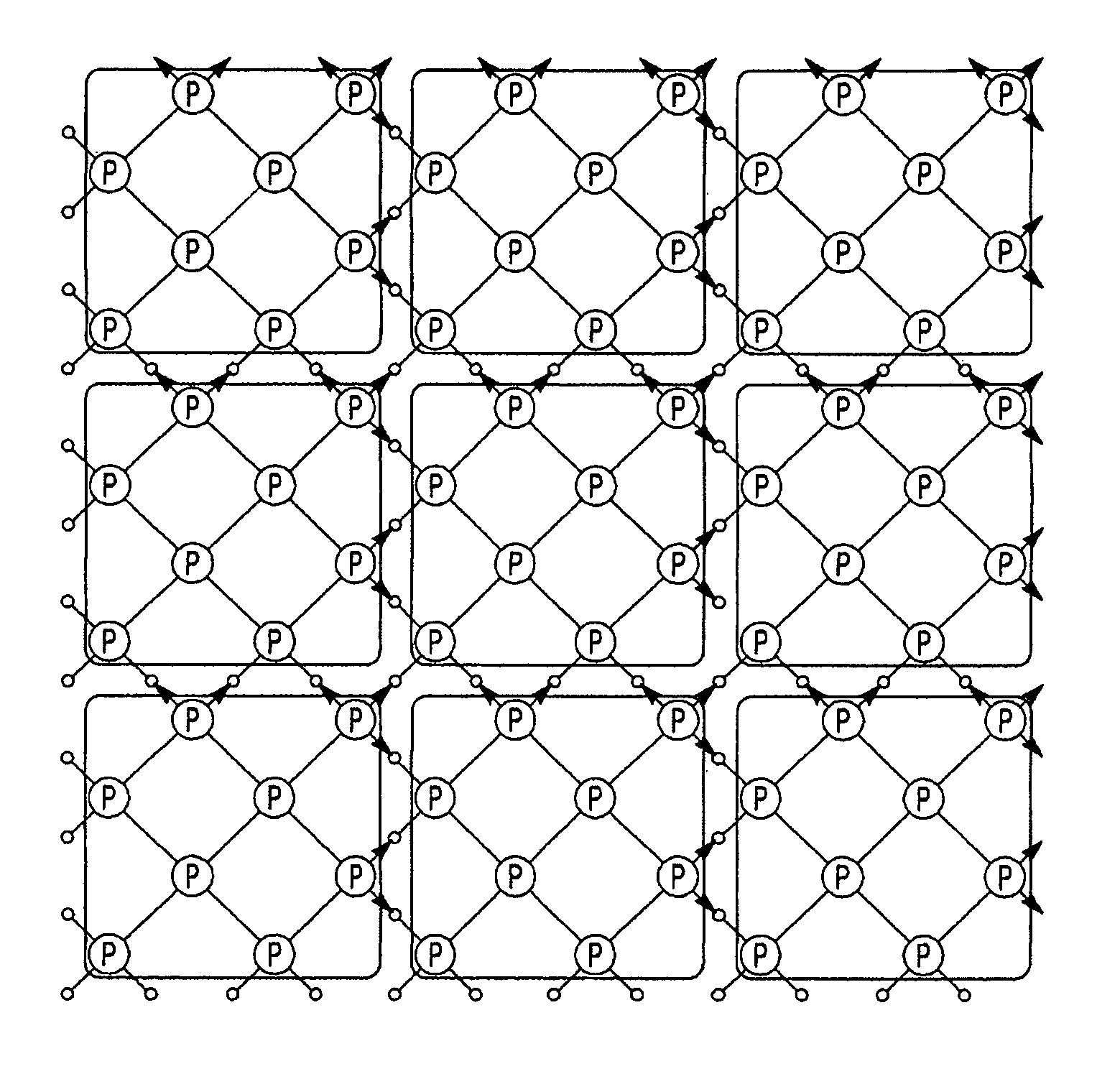

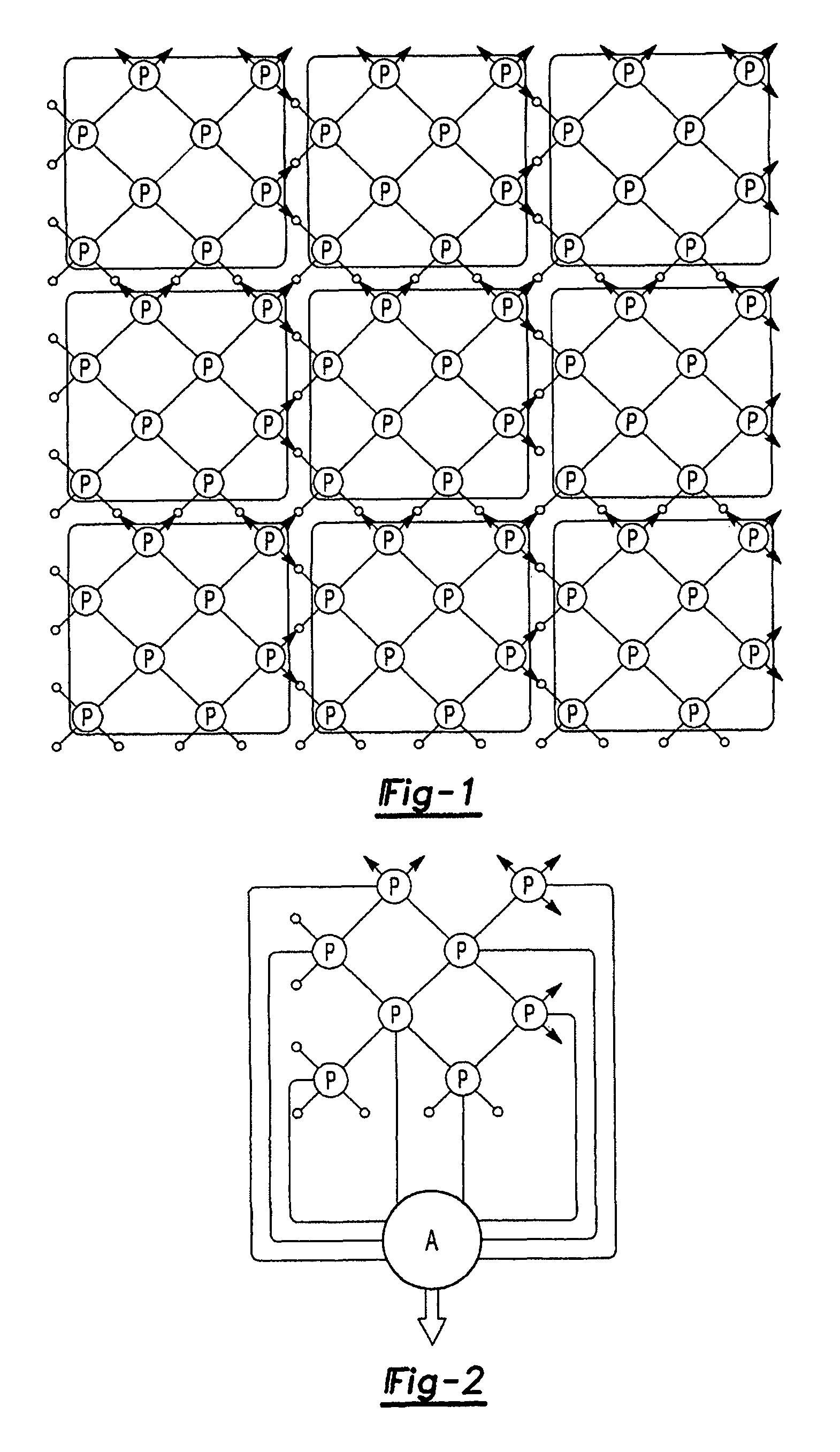

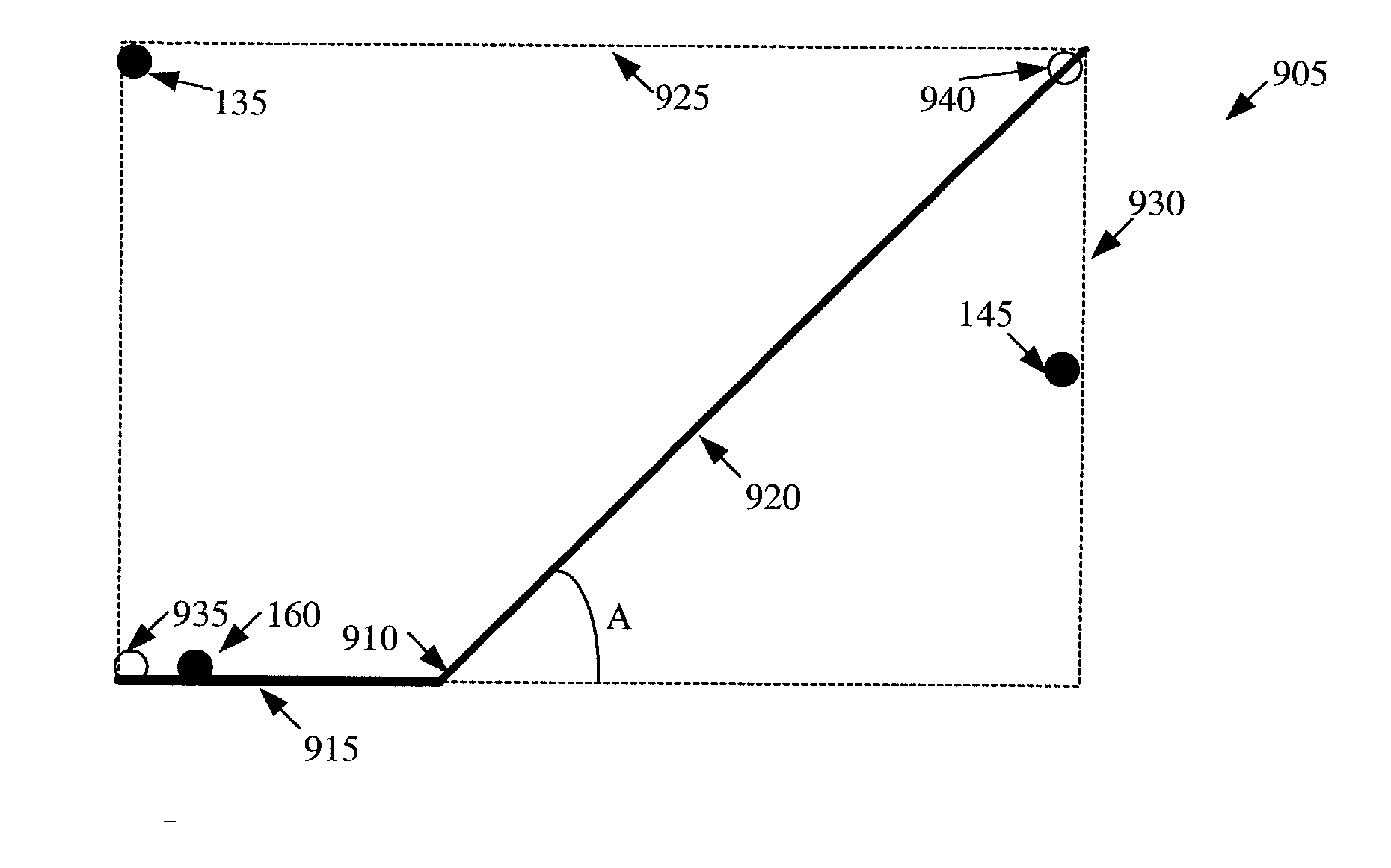

Method and apparatus for considering diagonal wiring in placement

InactiveUS7024650B2Multi-objective optimisationSoftware simulation/interpretation/emulationInterconnect topologyDiagonal

The invention is directed towards method and apparatus that consider diagonal wiring in placement. Some embodiments of the invention are placers that use diagonal lines in calculating the costs of potential placement configurations. For instance, some embodiments estimate the wirelength cost of a placement configuration by (1) identifying, for each net in a net list, a bounding box that encloses all the circuit elements of the net, (2) computing an attribute of each bounding box by using a line that can be completely or partially diagonal, and (3) computing the wirelength cost estimate based on the computed attributes. To estimate the wirelength cost of different placement configurations, other embodiments construct connection graphs that model the net interconnect topologies. These connection graphs can have edges that are completely or partially diagonal. Other embodiments use diagonal lines to measure congestion costs of potential placement configurations. For instance, some placers use diagonal lines as cut lines that divide the IC layout into regions. These placers then generate congestion-cost estimates by measuring the number of nets cut by the diagonal cut lines.

Owner:CADENCE DESIGN SYST INC

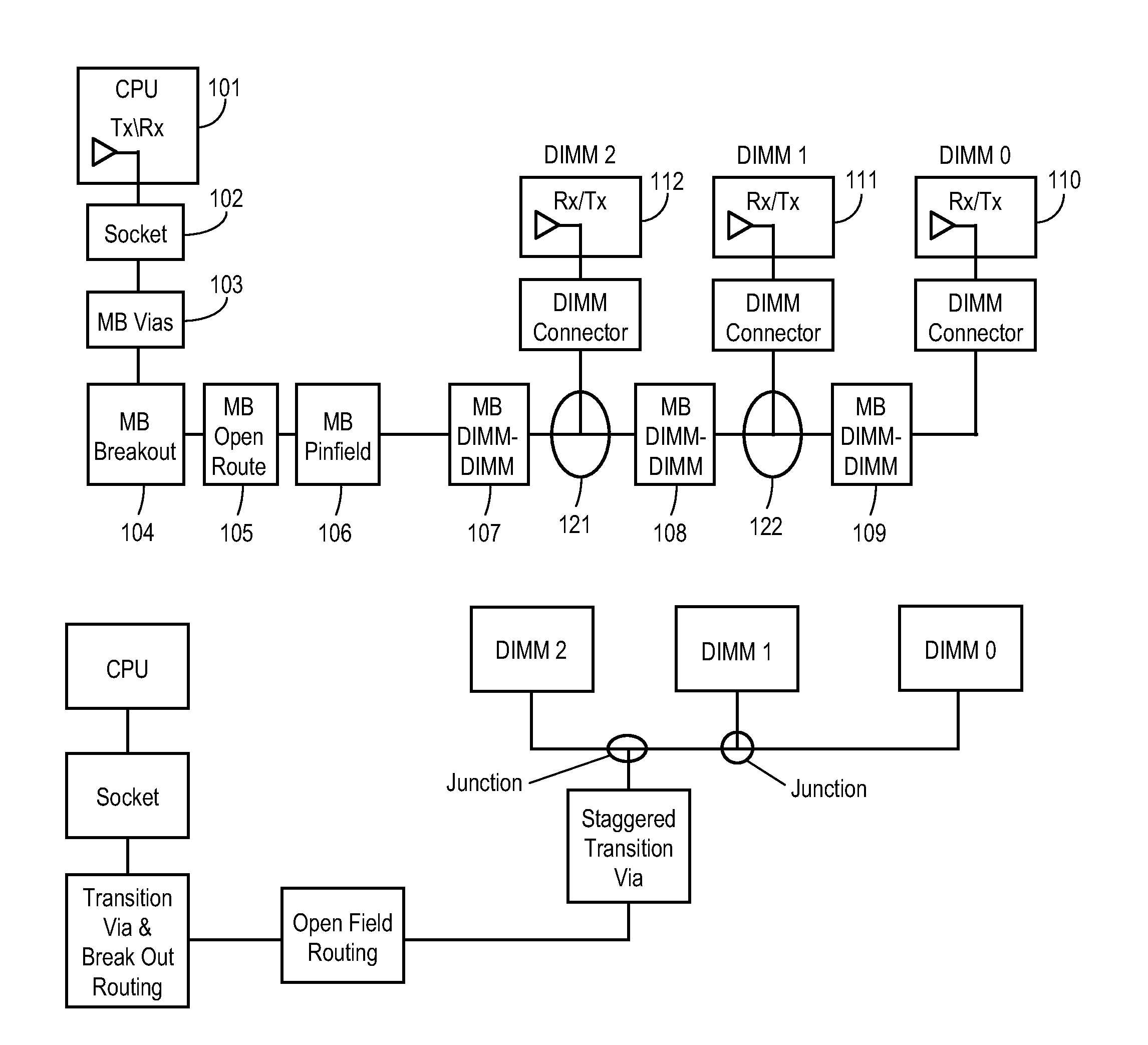

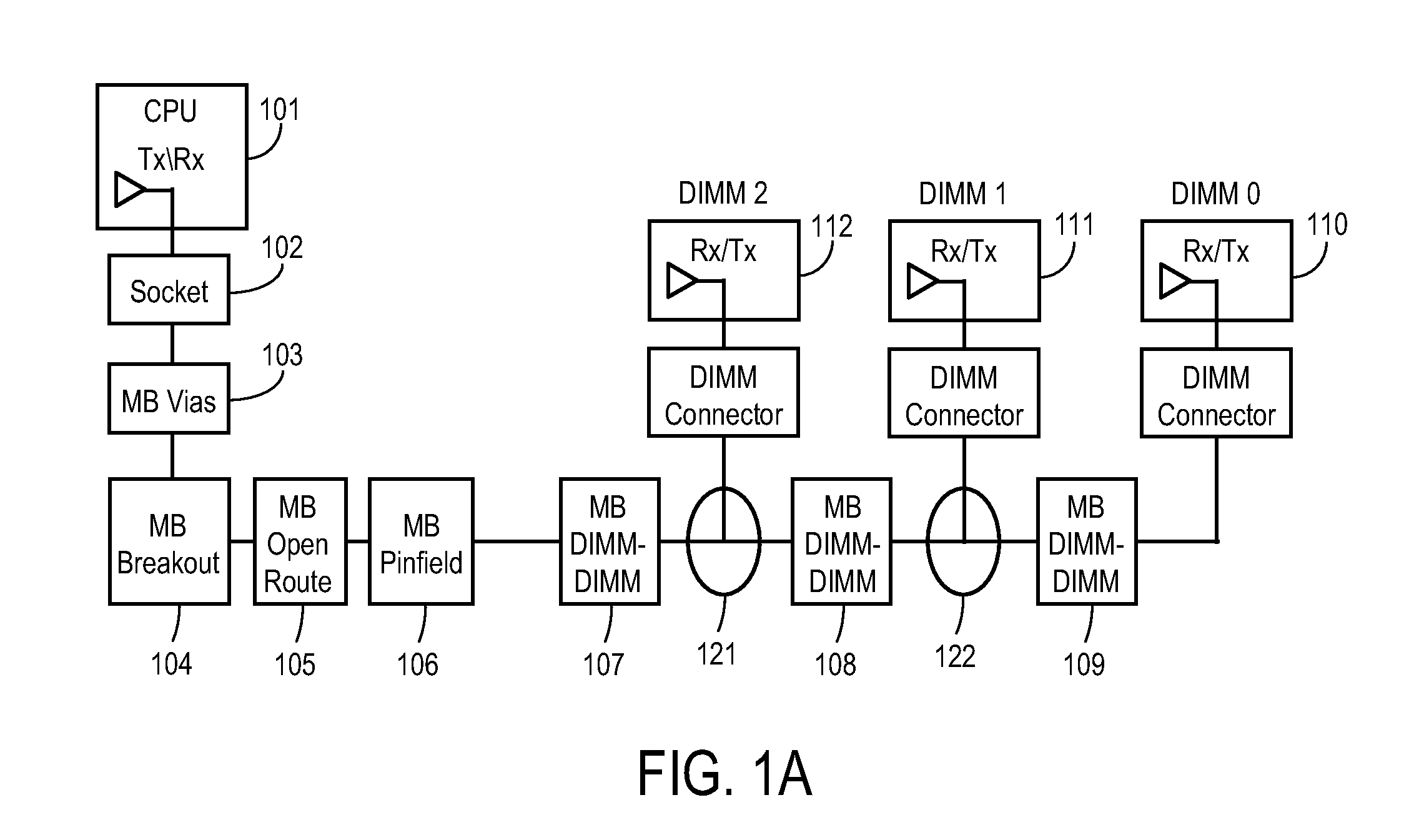

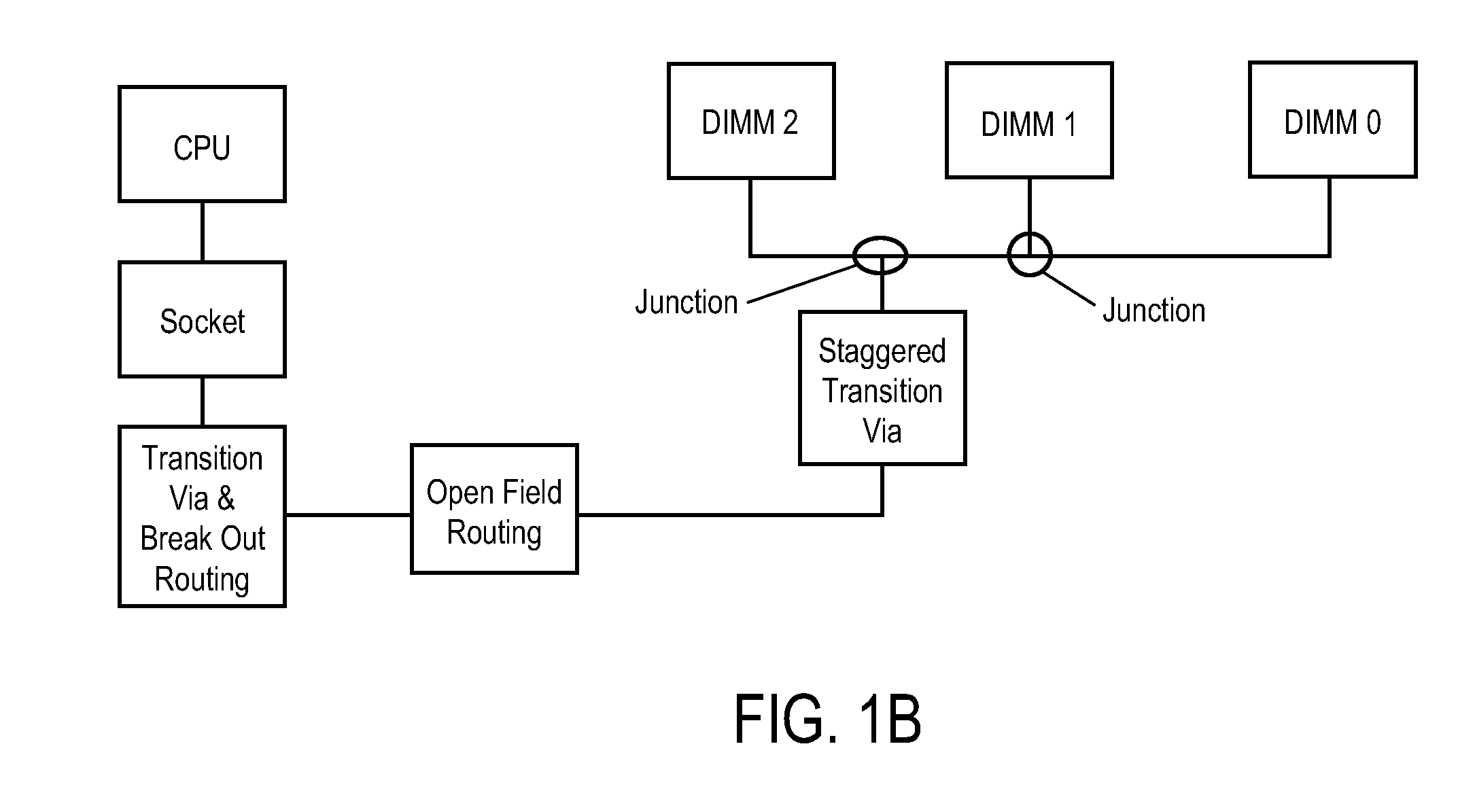

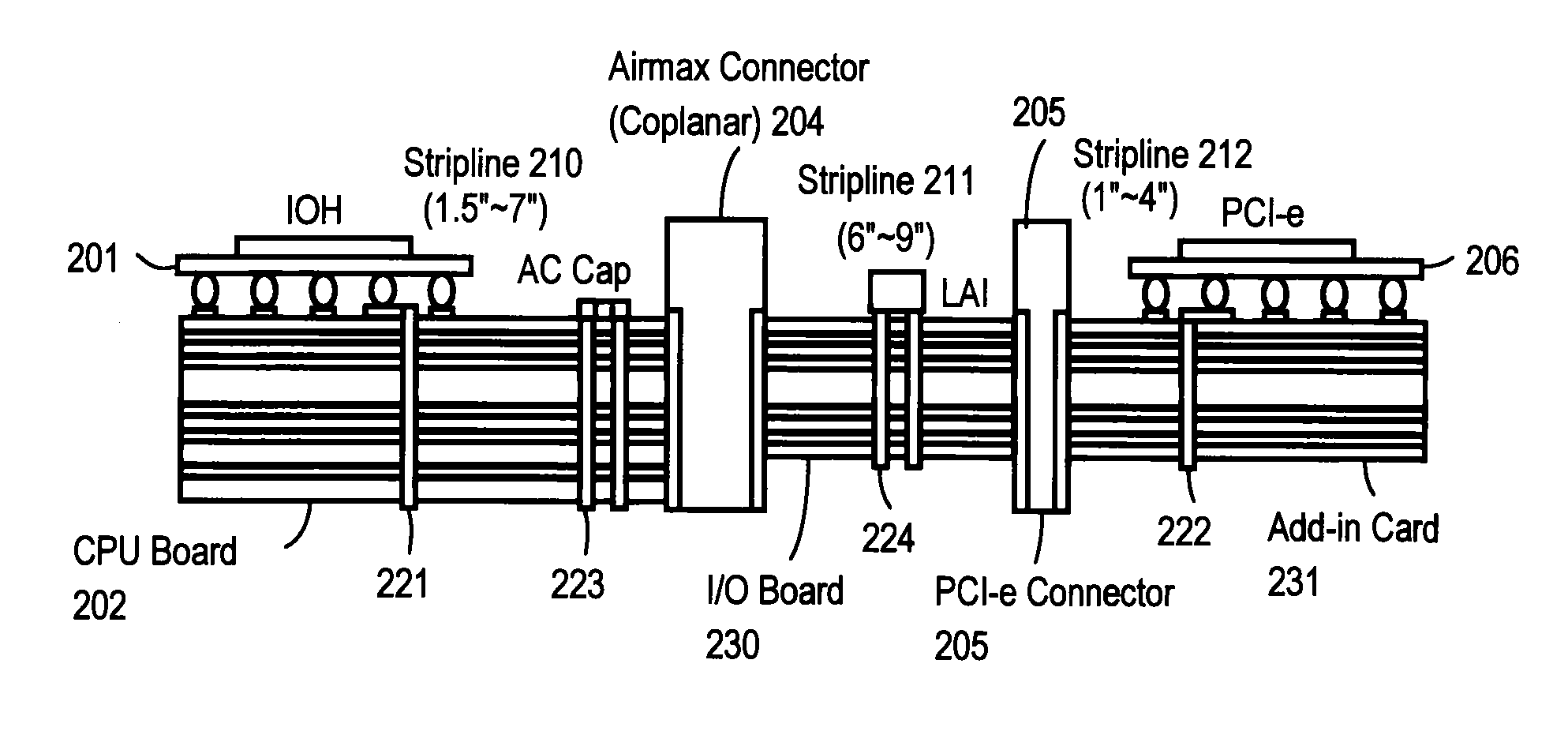

Signal integrity in mutli-junction topologies

A channel (e.g., memory channel) coupling a processor to multiple devices (e.g., DIMMs) is described. The channel has an interconnect topology with multiple interconnect portions coupled together with two or more junctions. At least one of these junctions has first and second interconnect portions that cross each other to form a plus-shaped junction. Also, the interconnect routing between the two or more junctions has an impedance matched to impedance of the two or more junctions.

Owner:INTEL CORP

Ultra-scalable supercomputer based on MPU architecture

InactiveUS8159973B2High-performance and sustained computing resourcesCostData switching by path configurationMultiple digital computer combinationsSupercomputerInterconnect topology

Owner:SHANGHAI REDNEURONS

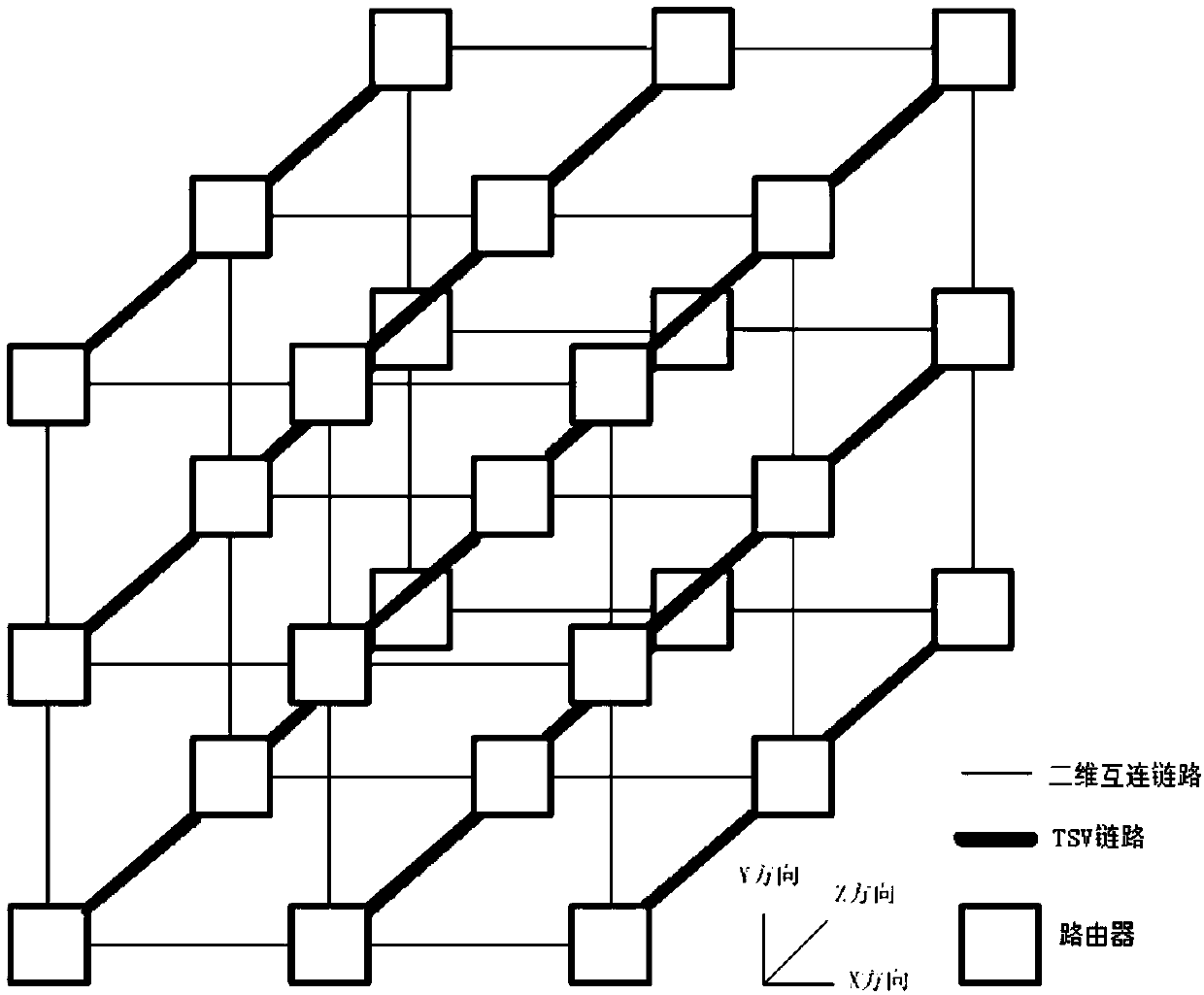

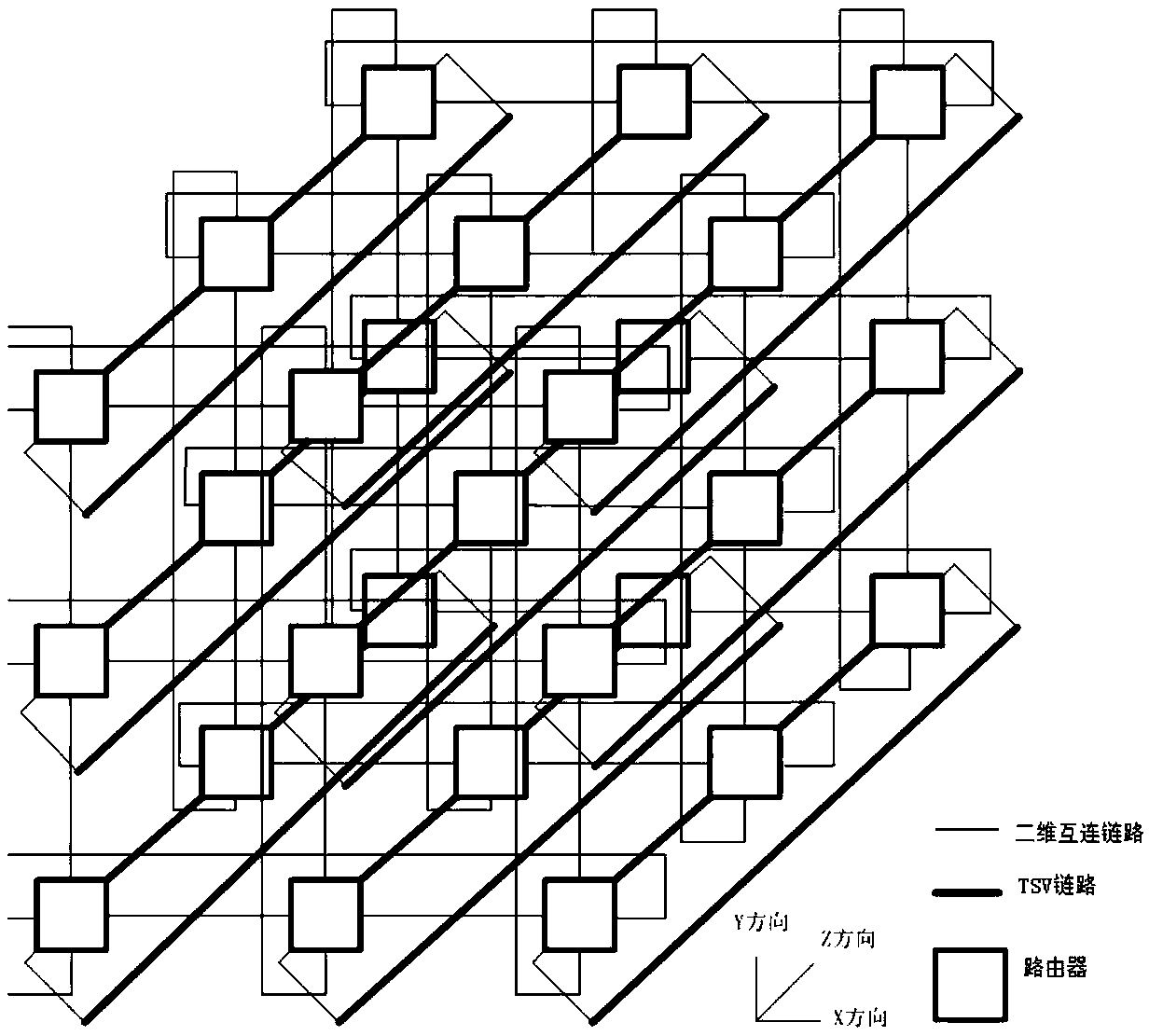

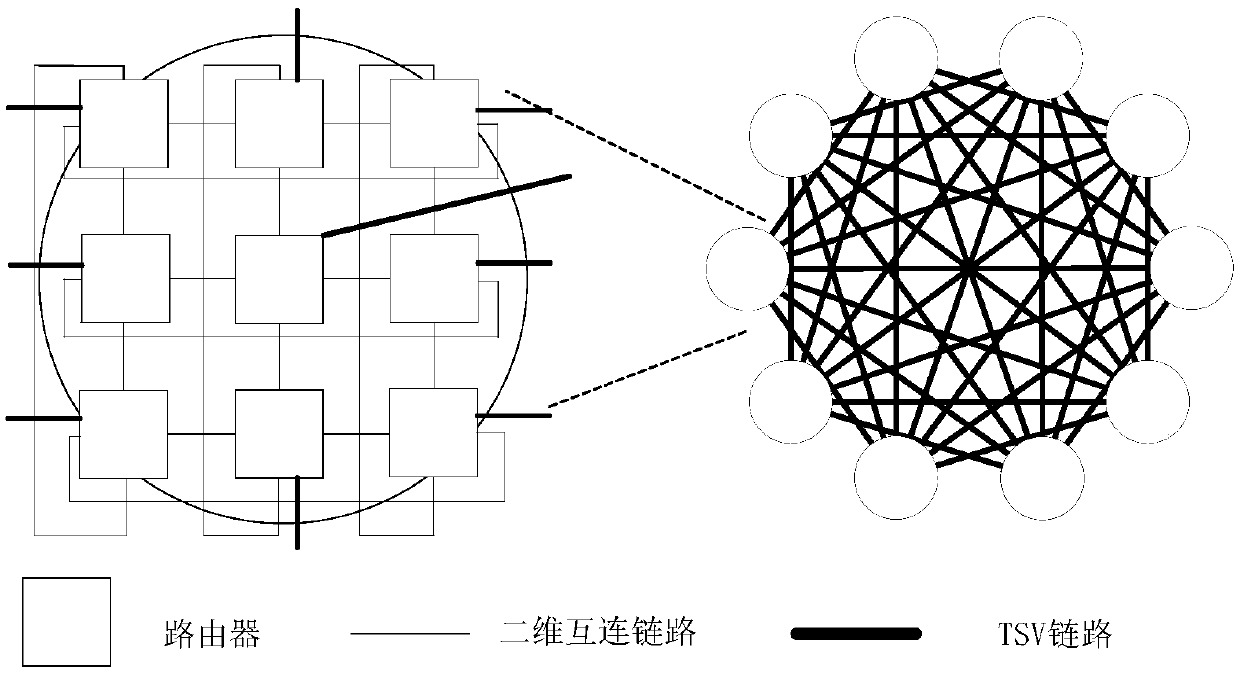

Three-dimensional network topology structure and routing algorithm thereof

ActiveCN109561034AReduce network diameterReduce communication delayData switching networksRouting algorithmThree dimensional integration

The invention discloses a three-dimensional network topology structure and a routing algorithm thereof. The three-dimensional network topology structure comprises multiple first-layer virtual subnets,wherein each first-layer virtual subnet is a Torus topology structure; the multiple first-layer virtual subnets form a full-interconnection topology structure through a TSV interconnecting link, andthe full-interconnection topology is a second-layer virtual subnet. The technical scheme of the invention constructs a hierarchical network topology structure through combining the Torus topologies and the full-interconnection topology based on a three-dimensional integration technology and a TSV technology, which at least can effectively compress the network diameter and reduce the communicationdelay.

Owner:中科曙光信息产业成都有限公司 +1

Method and Apparatus for Using Connection Graphs with Potential Diagonal Edges to Model Interconnect Topologies During Placement

The invention is directed towards method and apparatus that consider diagonal wiring in placement. Some embodiments of the invention are placers that use diagonal lines in calculating the costs of potential placement configurations. For instance, some embodiments estimate the wirelength cost of a placement configuration by (1) identifying, for each net in a net list, a bounding box that encloses all the circuit elements of the net, (2) computing an attribute of each bounding box by using a line that can be completely or partially diagonal, and (3) computing the wirelength cost estimate based on the computed attributes. To estimate the wirelength cost of different placement configurations, other embodiments construct connection graphs that model the net interconnect topologies. These connection graphs can have edges that are completely or partially diagonal. Other embodiments use diagonal lines to measure congestion costs of potential placement configurations. For instance, some placers use diagonal lines as cut lines that divide the IC layout into regions. These placers then generate congestion-cost estimates by measuring the number of nets cut by the diagonal cut lines.

Owner:CADENCE DESIGN SYST INC

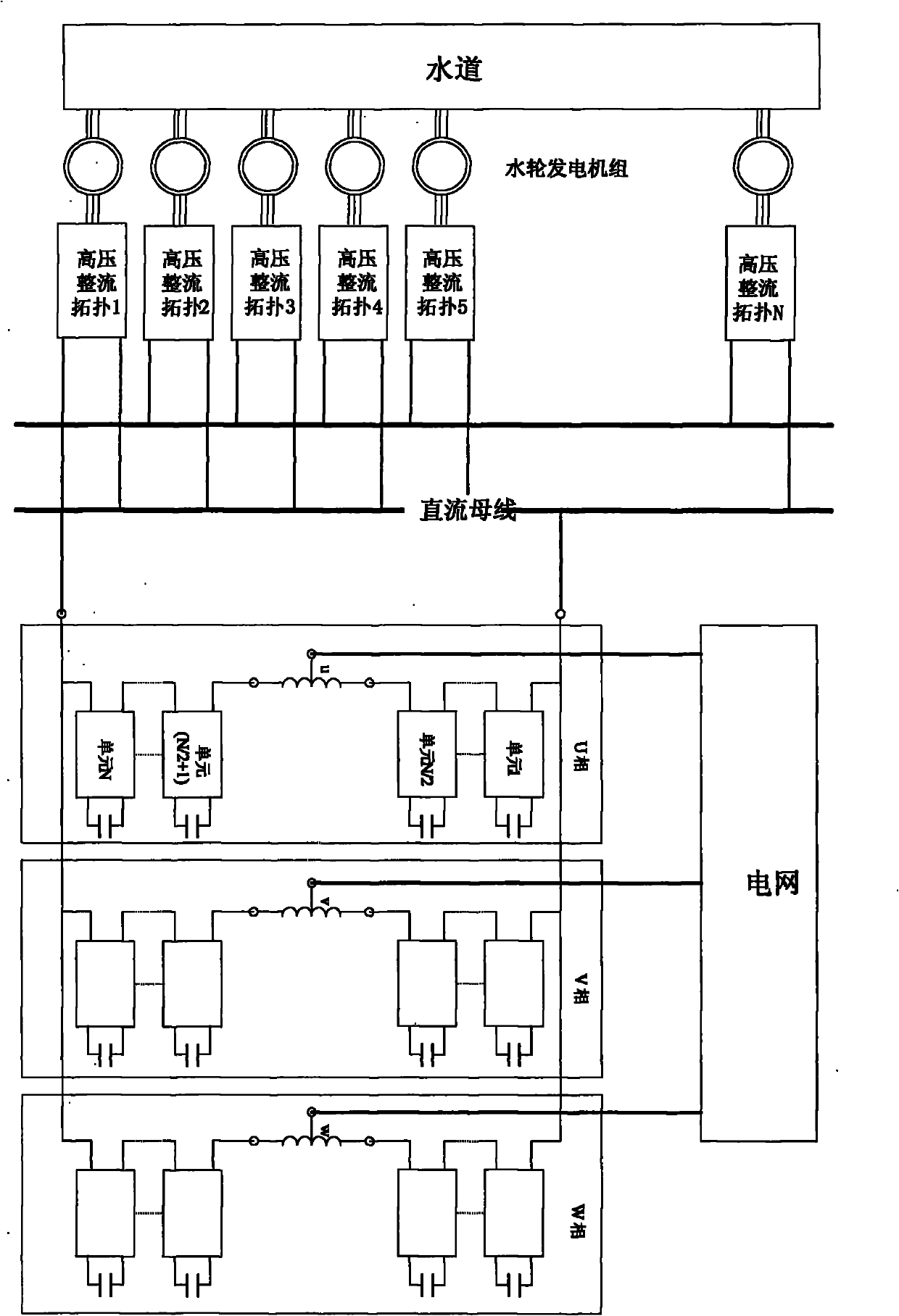

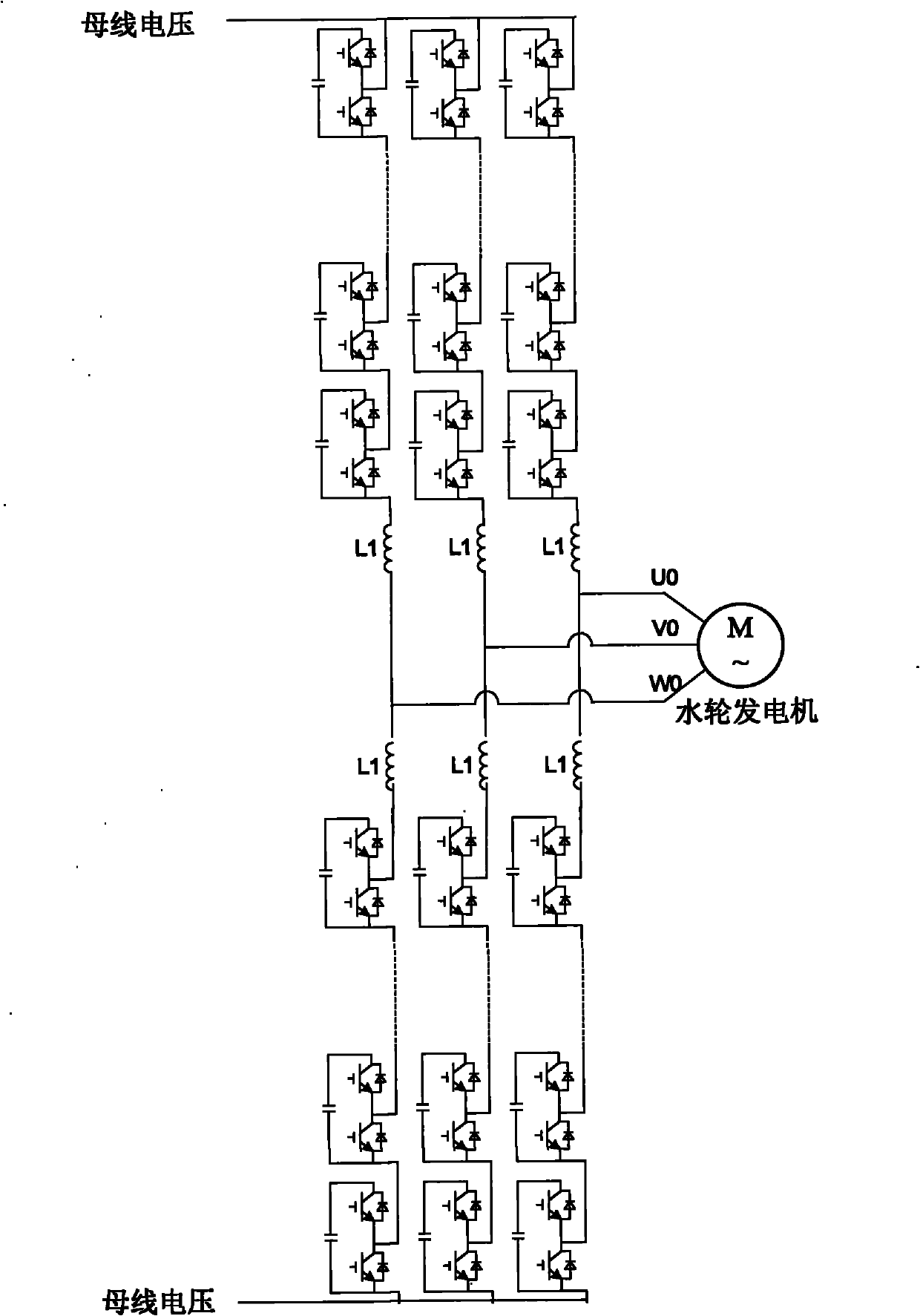

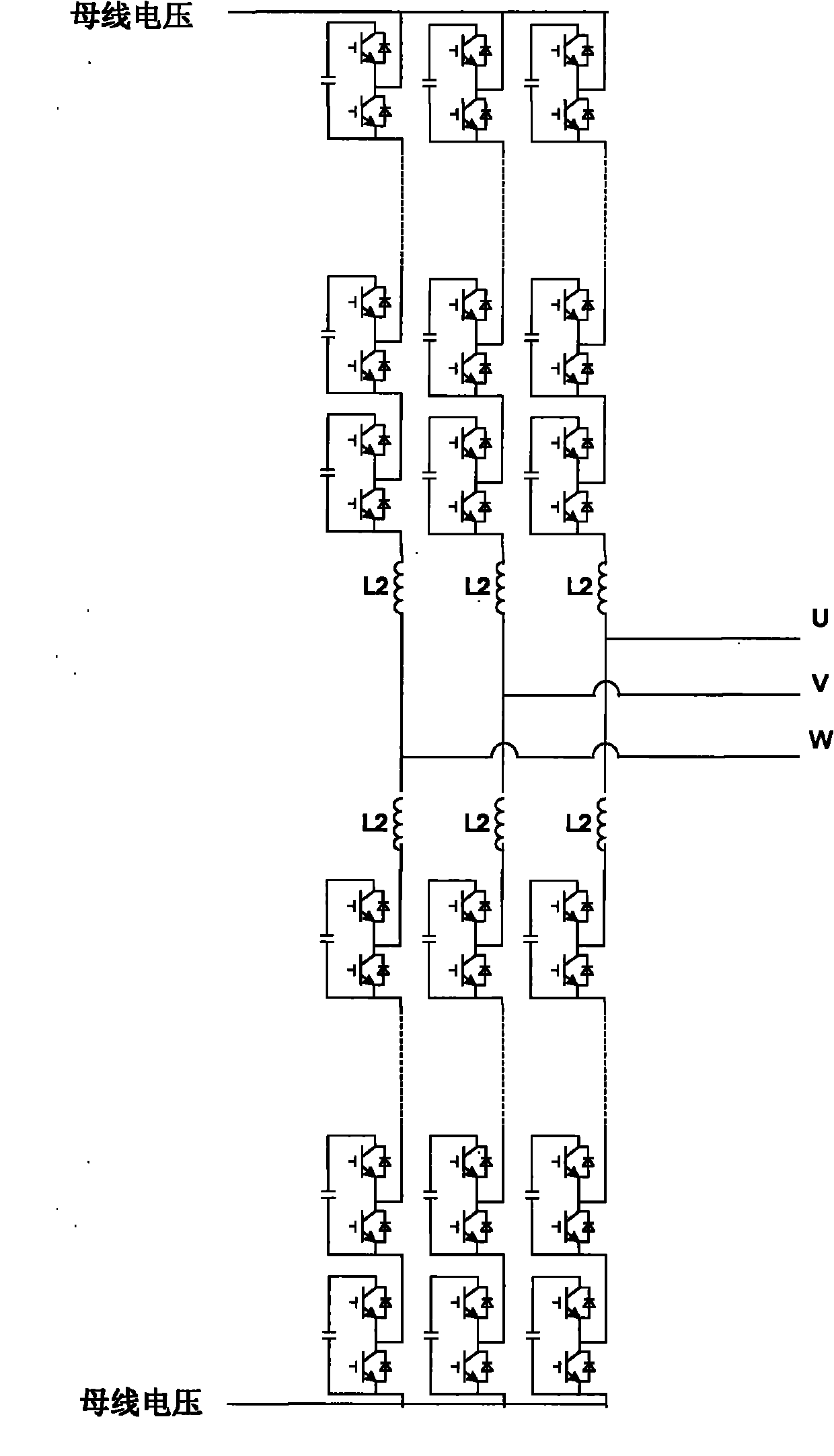

Power-generating interconnected topological structure of transformerless water-turbine generator

InactiveCN102025166AImprove efficiencyGood output voltage waveformAc-dc conversionSingle network parallel feeding arrangementsTransformerWater turbine

The invention relates to a power-generating interconnected topological structure of a transformerless water-turbine generator, which comprises a water-turbine generator set, a high-voltage rectifying topology, a direct-current bus and an inverting topology, wherein the high-voltage rectifying topology comprises a plurality of high-voltage rectifying modules, the inverting topology comprises a plurality of inverting modules, the high-voltage alternating current with any frequency generated by each water-turbine generator is rectified by the high-voltage rectifying topology to obtain a direct-current high voltage, the generated direct-current high voltages are connected together and collected onto the direct-current bus, the voltage on the direct-current bus is used as the direct-current side voltage of the inverting topology, and the direct-current side voltage is inverted into an alternating-current voltage by the inverting topology to generate a high voltage to be connected to a power grid. The invention has the advantages that: no transformer exists at an input end, thereby the equipment investment is saved, and the waterpower generation efficiency is greatly improved. The transformer does not exist at the input end, so that the volume of a waterpower-generating interconnected topology is reduced, the occupied land is reduced, the weight is lightened, and the cost is lowered; and meanwhile, the energy consumption can be lowered, so that the manufacturing process is simplified, and the production period is reduced.

Owner:RONGXIN POWER ELECTRONICS

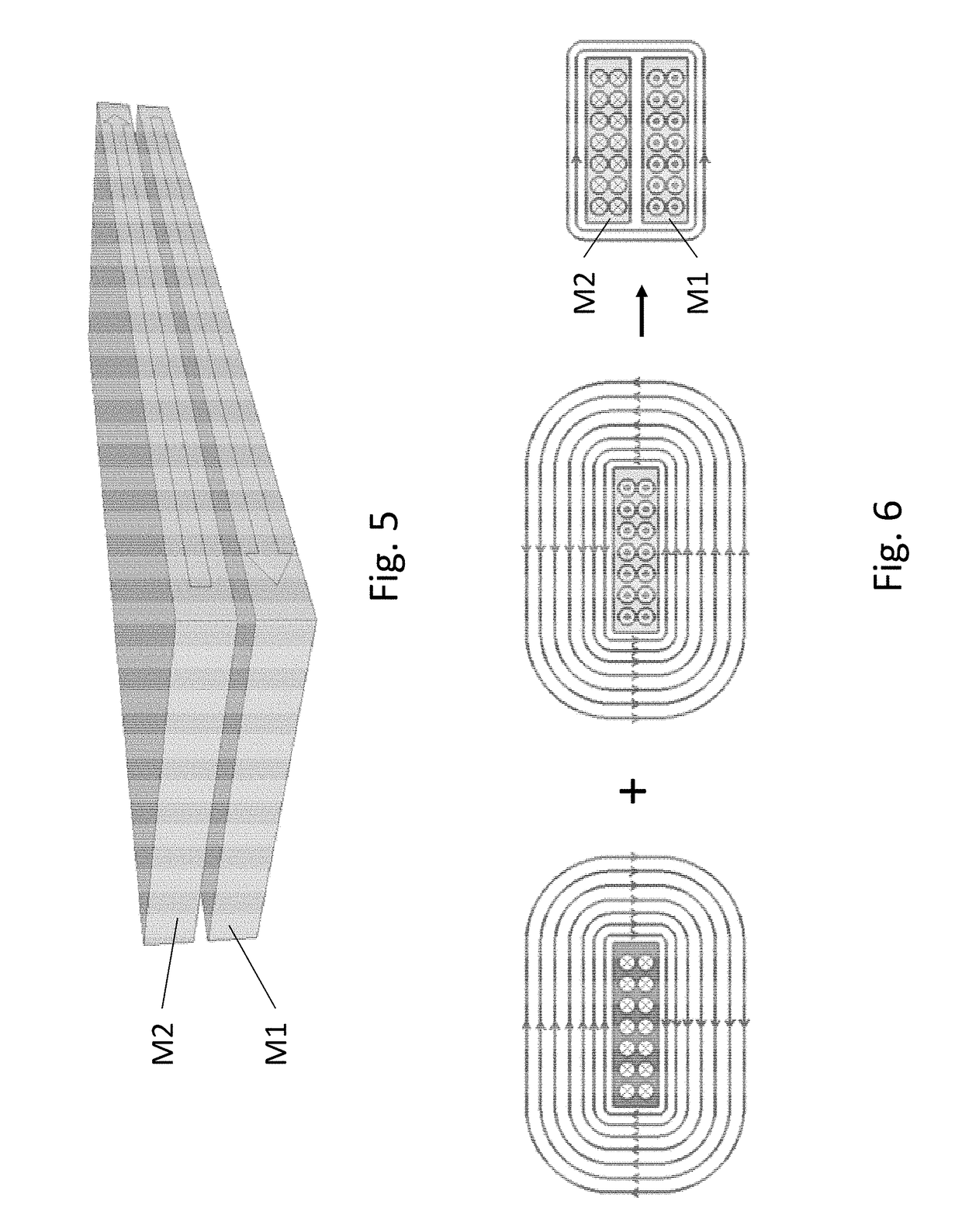

HIGH CURRENT LATERAL GaN TRANSISTORS WITH SCALABLE TOPOLOGY AND GATE DRIVE PHASE EQUALIZATION

ActiveUS20190081623A1Improve performanceIncrease the areaTransistorSemiconductor/solid-state device detailsRedistribution layerPhase difference

Owner:GAN SYST

Method for routing ad-hoc signals

InactiveUS7760645B2Error prevention/detection by using return channelTransmission systemsInterconnect topologyBroadcast packet

Owner:INTEL CORP

Configurable width buffered module having switch elements

Owner:RAMBUS INC

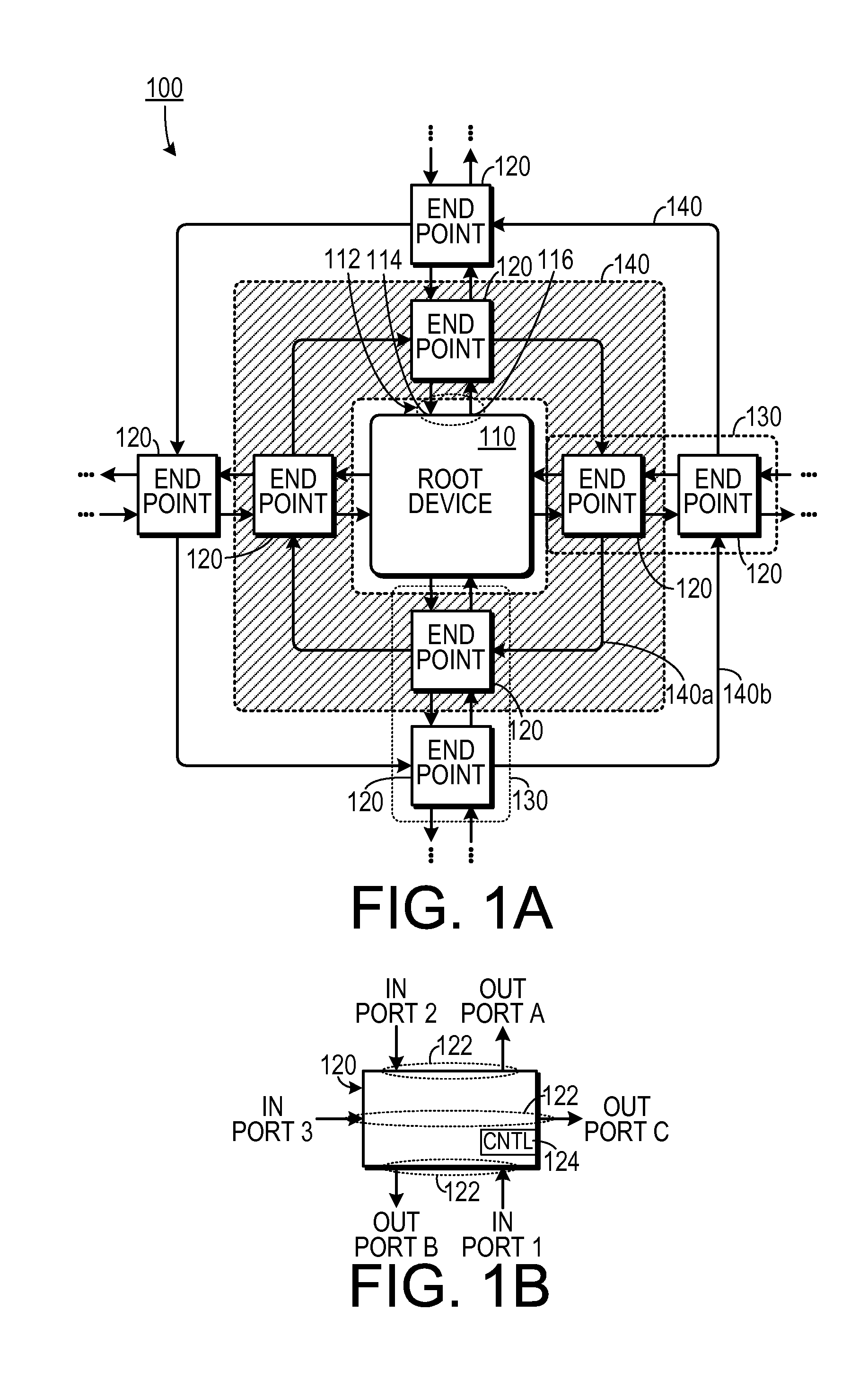

Spider Web Interconnect Topology Utilizing Multiple Port Connection

A data communications apparatus includes a central device and a plurality of communication devices. The central device includes a plurality of central port pairs, in which each central port pair includes an input port and an output port. The plurality of communication devices is arranged in a spoke and ring configuration, in which each communication device is part of a communication spoke. Each communication spoke is in communication with a different central port pair. Each communication device is also a part of a communication ring, so that each communication device in a selected communication ring belongs to a different communication spoke.

Owner:LENOVO GLOBAL TECH INT LTD

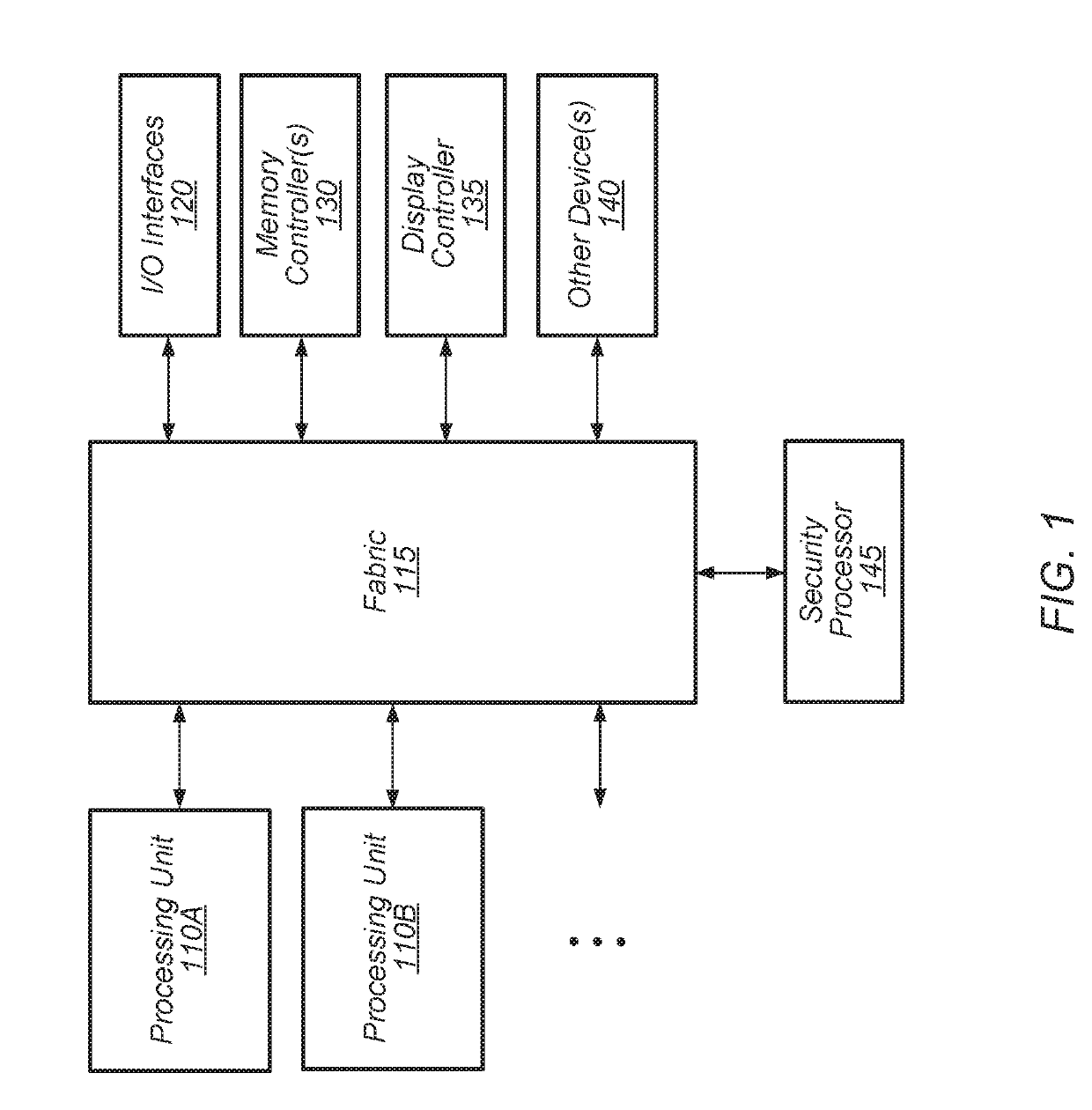

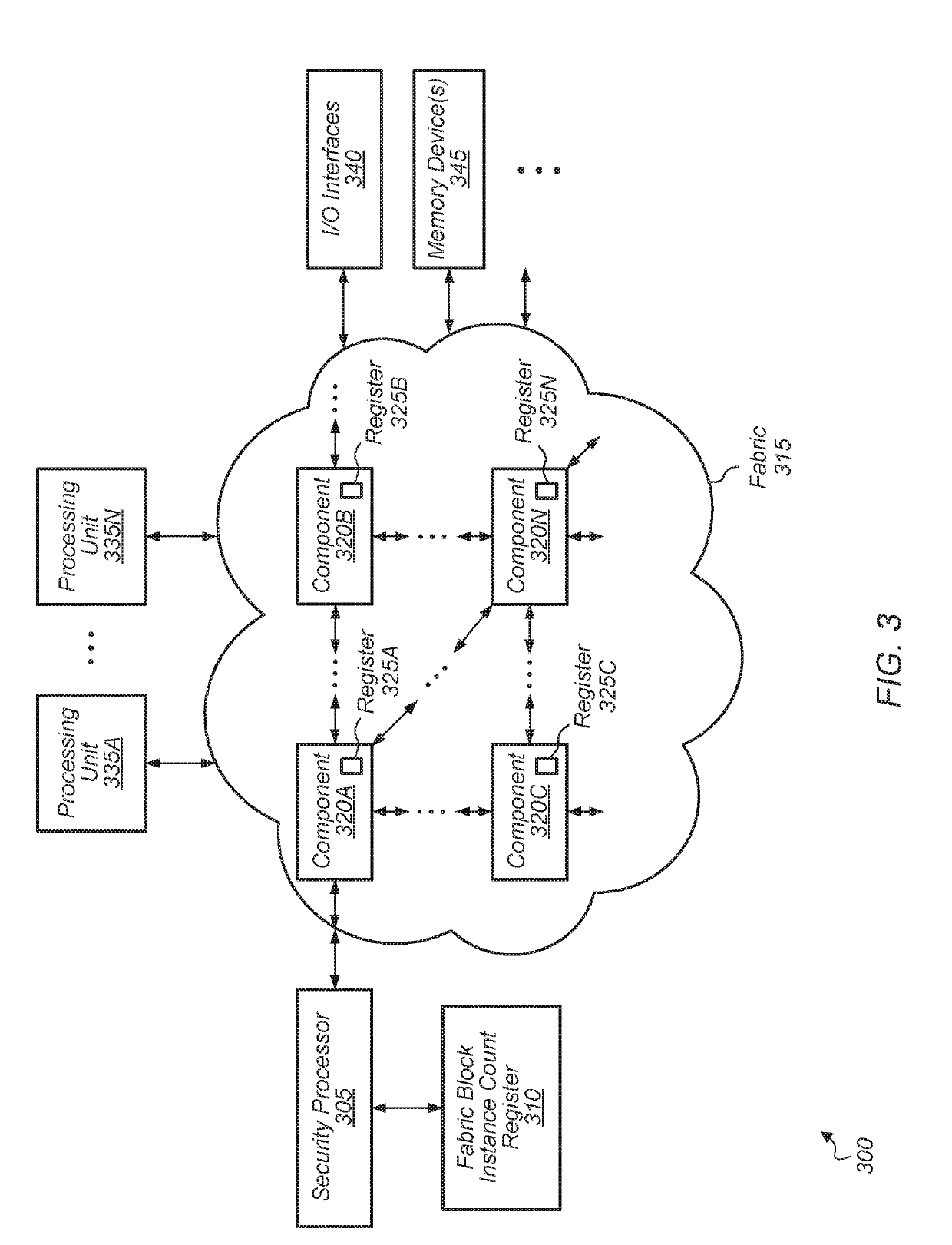

Self identifying interconnect topology

ActiveUS20190199617A1Facilitate communicationIncreased complexityComputer security arrangementsEnergy efficient computingInterconnect topologyRouting table

A system for automatically discovering fabric topology includes at least one or more processing units, one or more memory devices, a security processor, and a communication fabric with an unknown topology coupled to the processing unit(s), memory device(s), and security processor. The security processor queries each component of the fabric to retrieve various attributes associated with the component. The security processor utilizes the retrieved attributes to create a network graph of the topology of the components within the fabric. The security processor generates routing tables from the network graph and programs the routing tables into the fabric components. Then, the fabric components utilize the routing tables to determine how to route incoming packets.

Owner:ADVANCED MICRO DEVICES INC

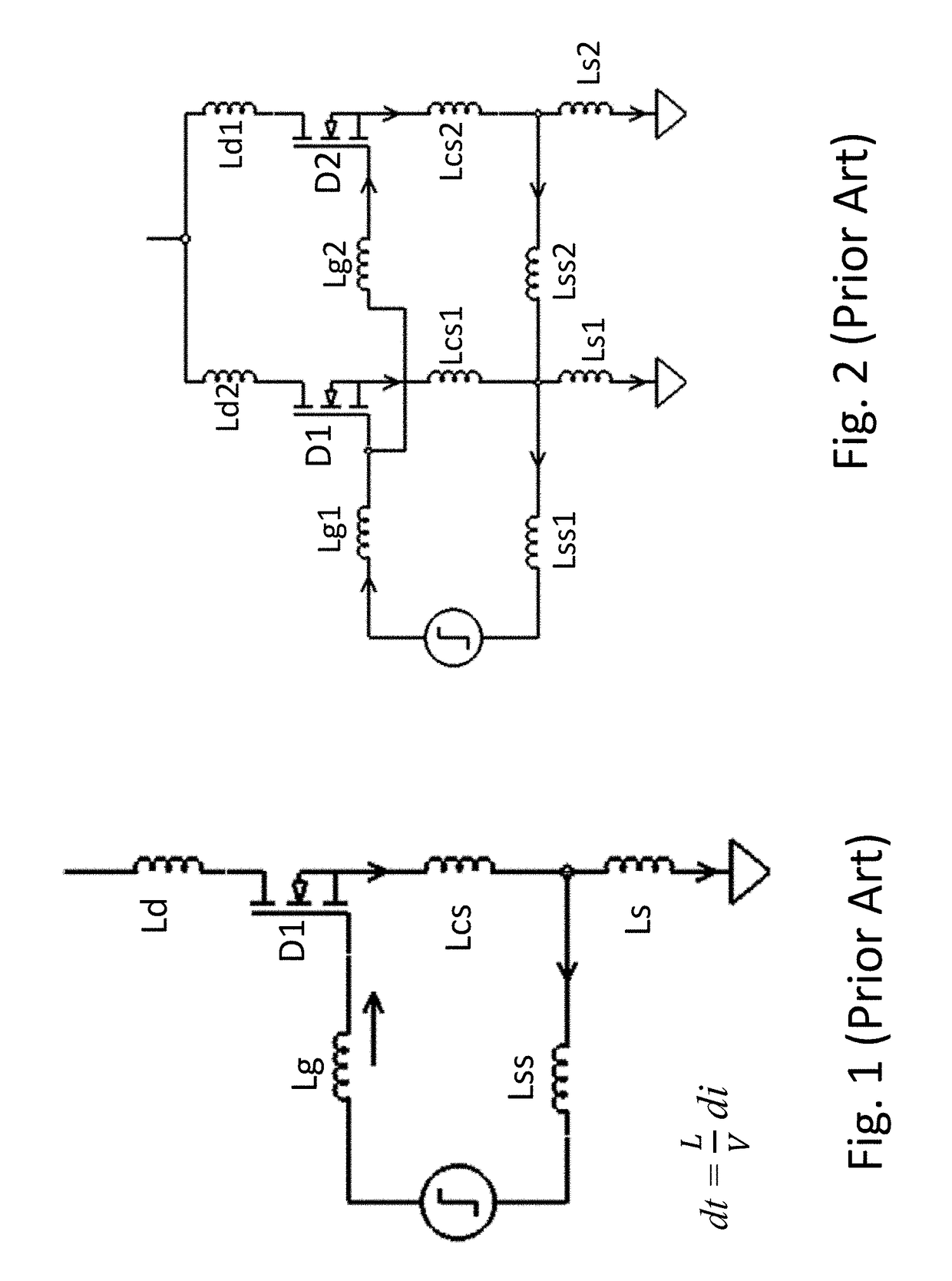

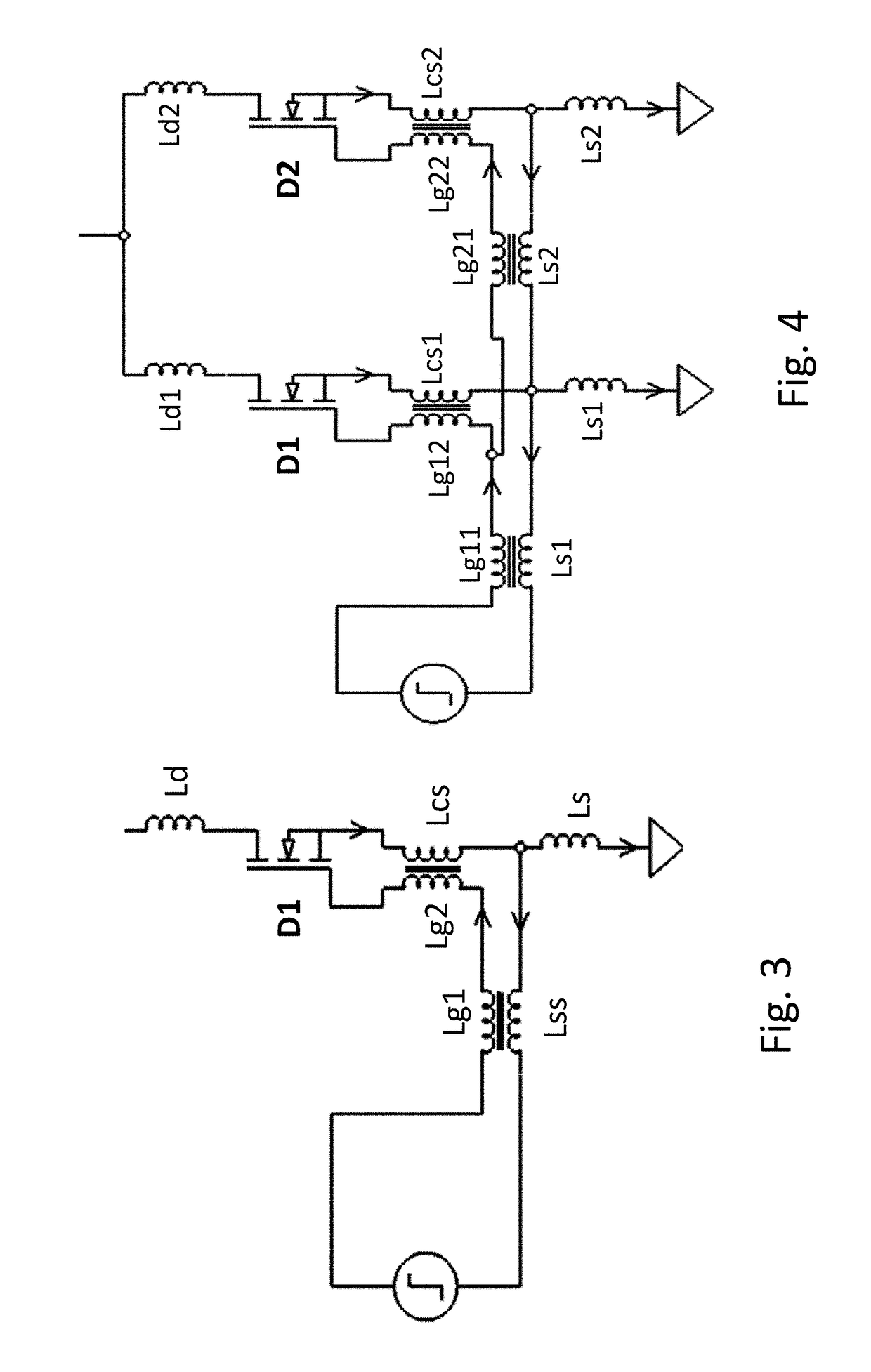

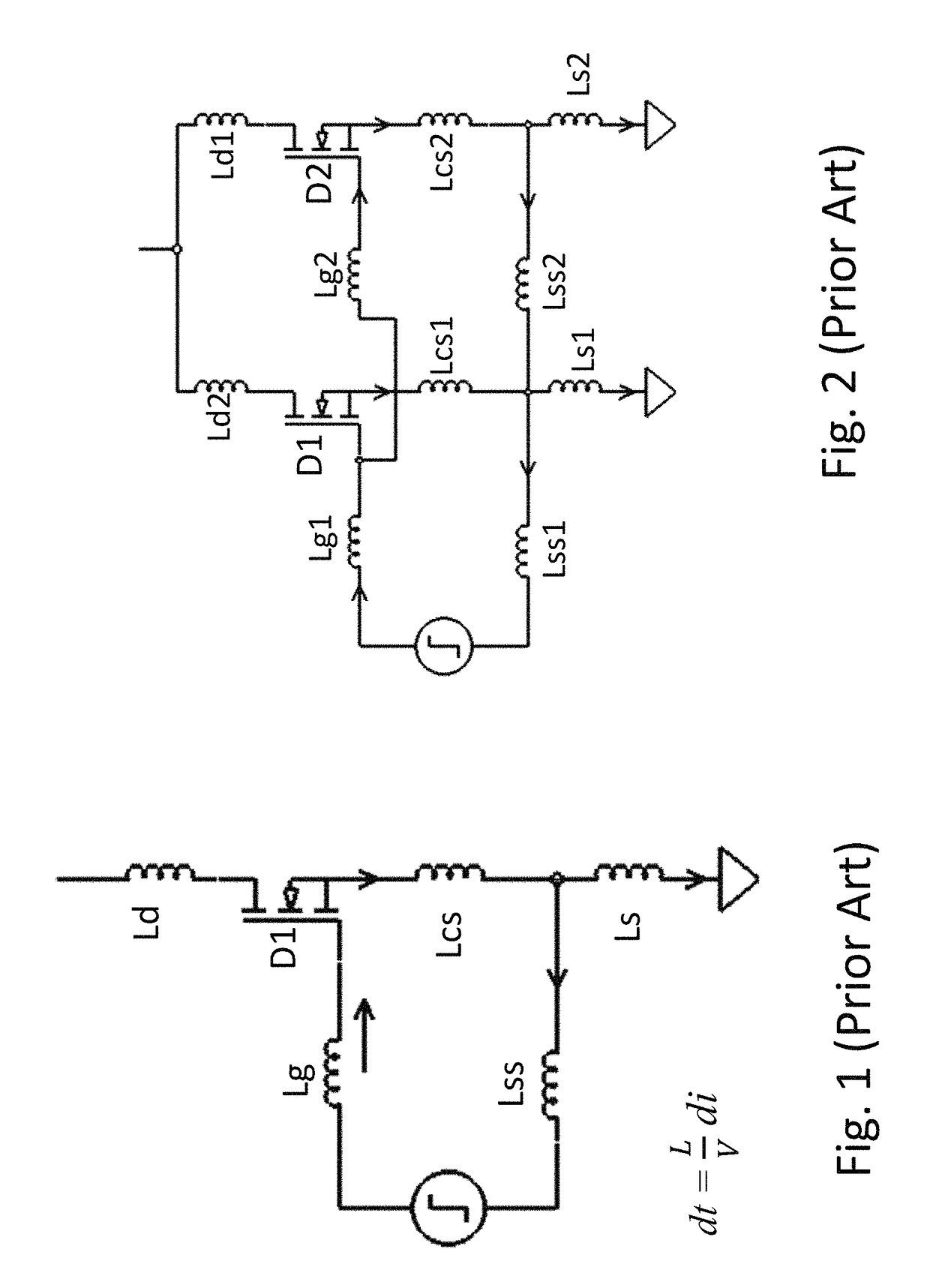

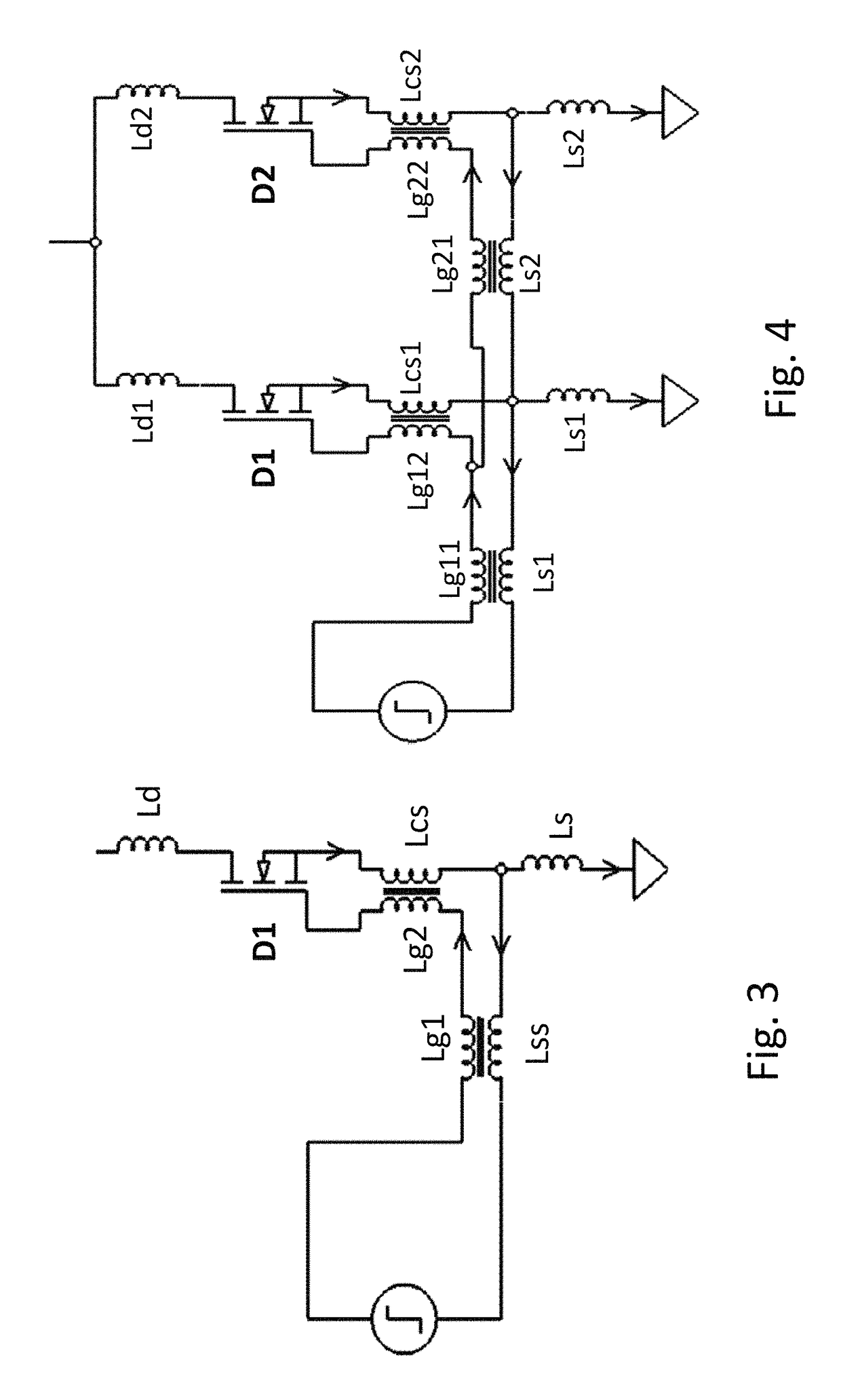

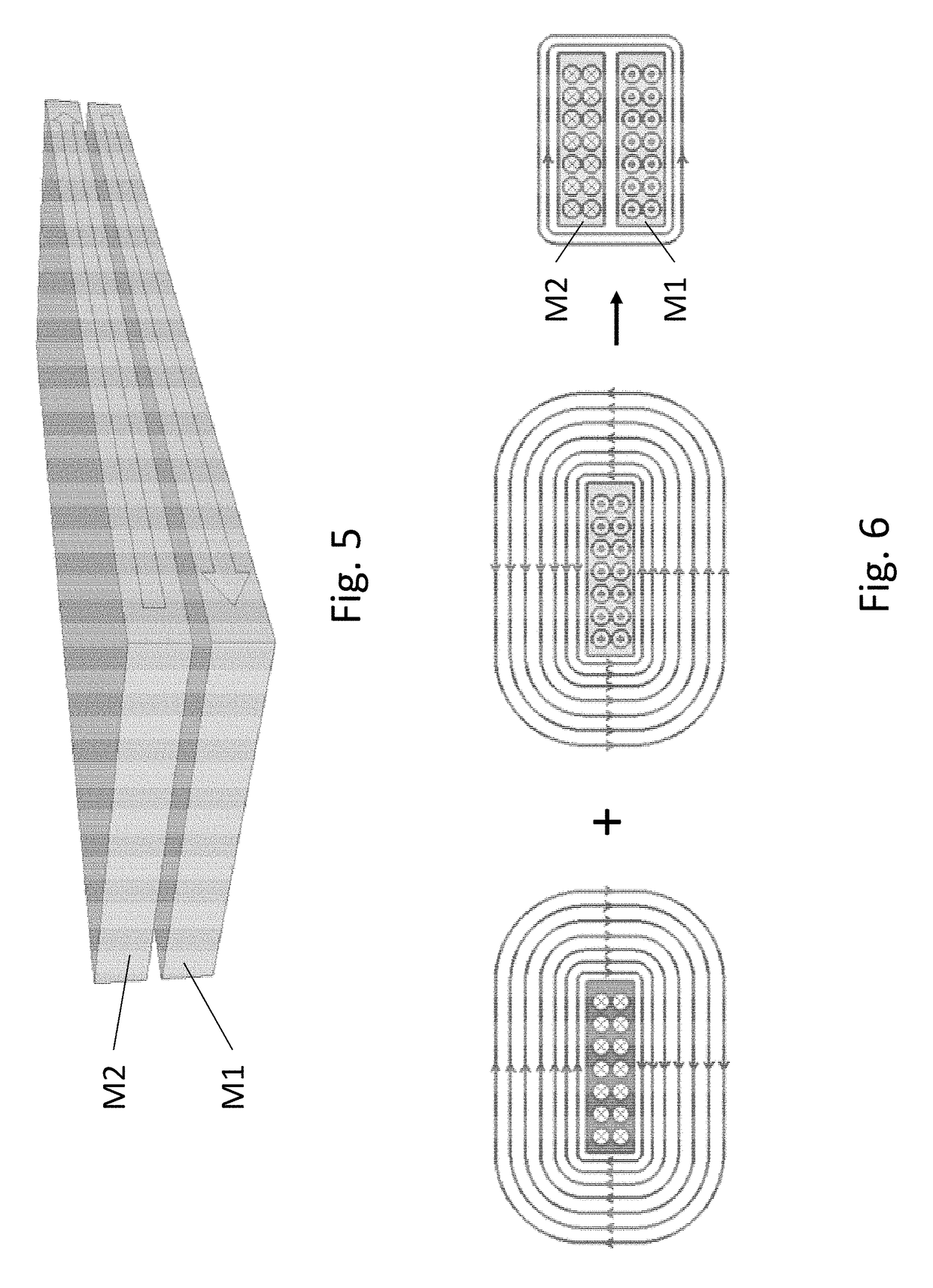

High current lateral GaN transistors with scalable topology and gate drive phase equalization

ActiveUS10218346B1Improve performanceIncrease the areaTransistorSemiconductor/solid-state device detailsRedistribution layerPhase difference

Large area, high current, lateral GaN power transistors are implemented using an on-chip interconnect topology wherein the transistor is arranged as an array of sections, each section comprising a set of transistor islands; gate and source buses that form each gate drive loop have substantially the same track widths; the source bus runs over or under the gate bus, and the tracks are inductively coupled to provide flux cancellation in the gate drive loop, thereby reducing parasitic inductances. The gate delay in each gate drive loop is reduced, minimizing the gate drive phase difference across the transistor. An overlying current redistribution layer preferably has a track width no greater than that of the underlying source and drain buses, for efficient coupling. This topology provides improved scalability, enabling fabrication of multi-section, large scale, high current lateral GaN transistors with reduced gate drive loop inductance, for improved operational stability.

Owner:GAN SYST

Vertical trench routing in a substrate

ActiveUS10079158B2Semiconductor/solid-state device detailsPrinted circuit aspectsInterconnect topologyElectrical conductor

Owner:INTEL CORP

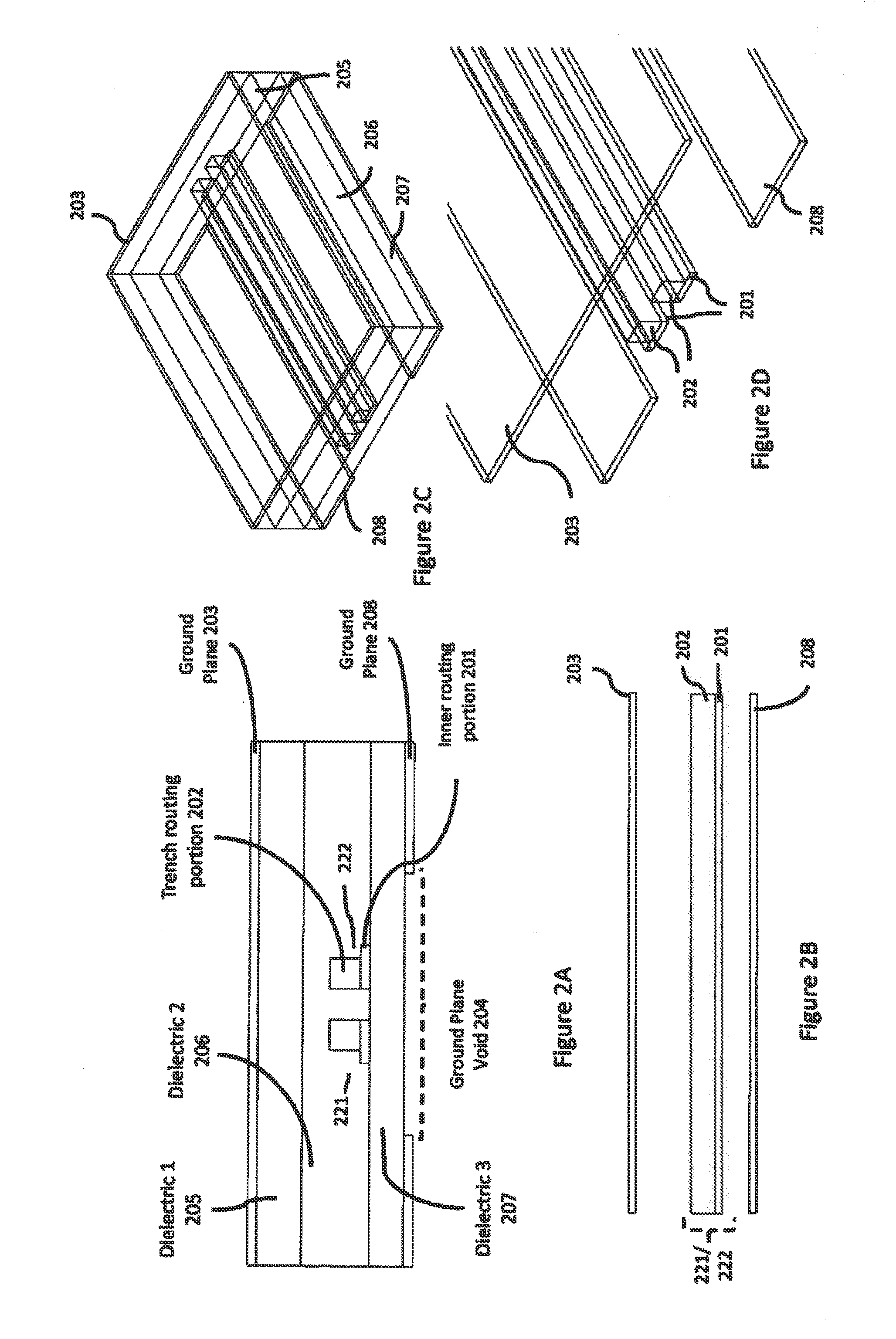

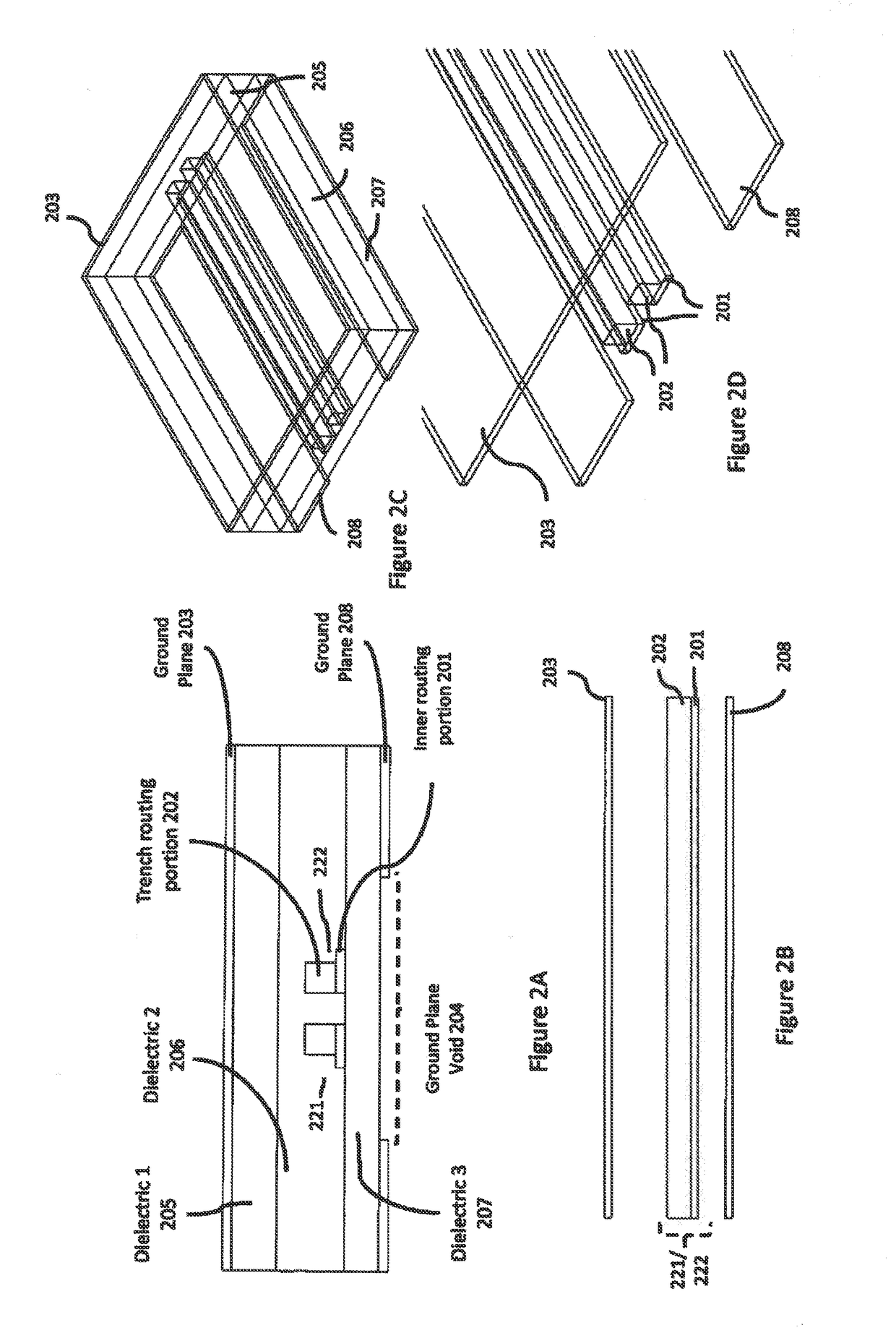

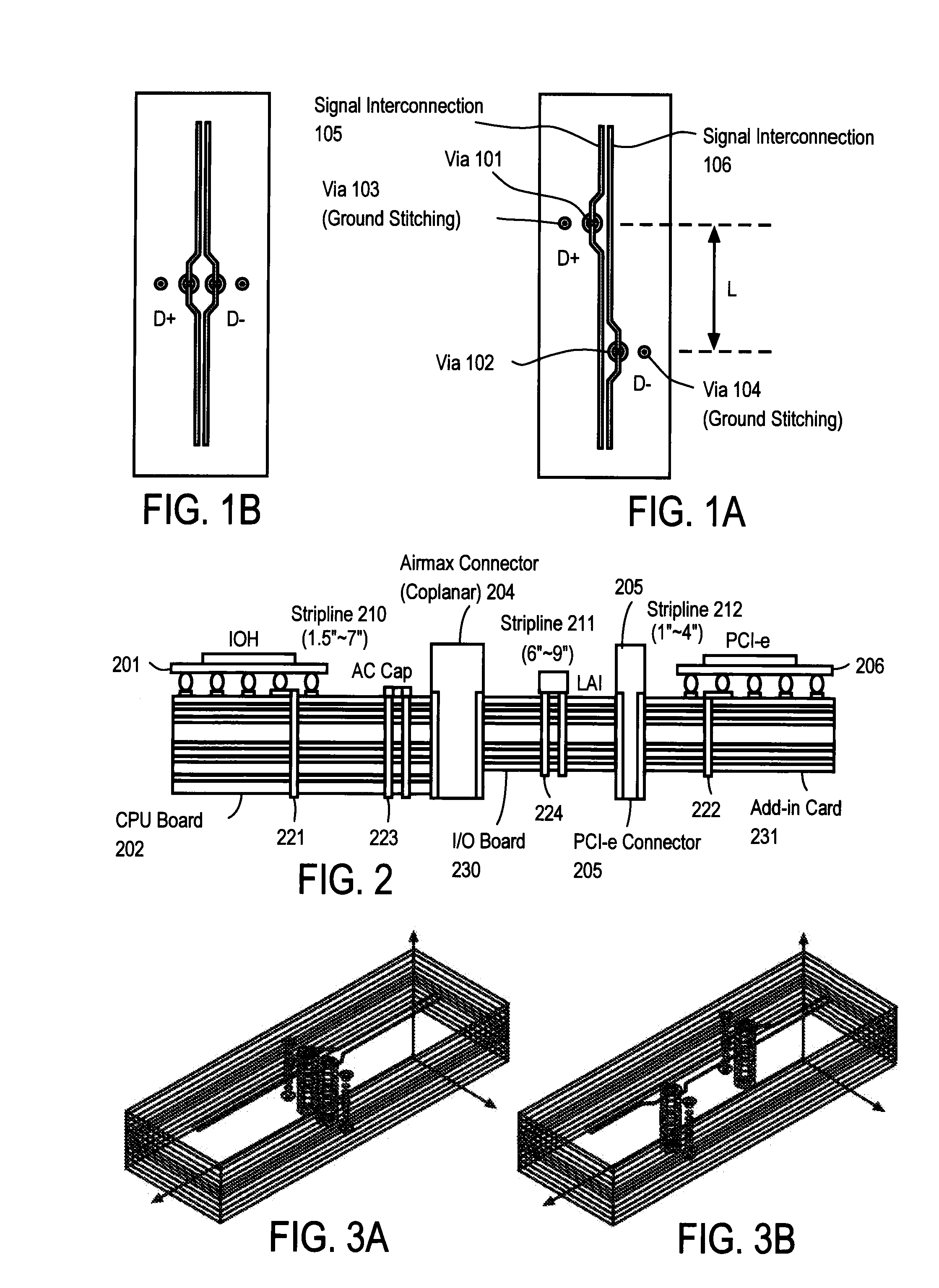

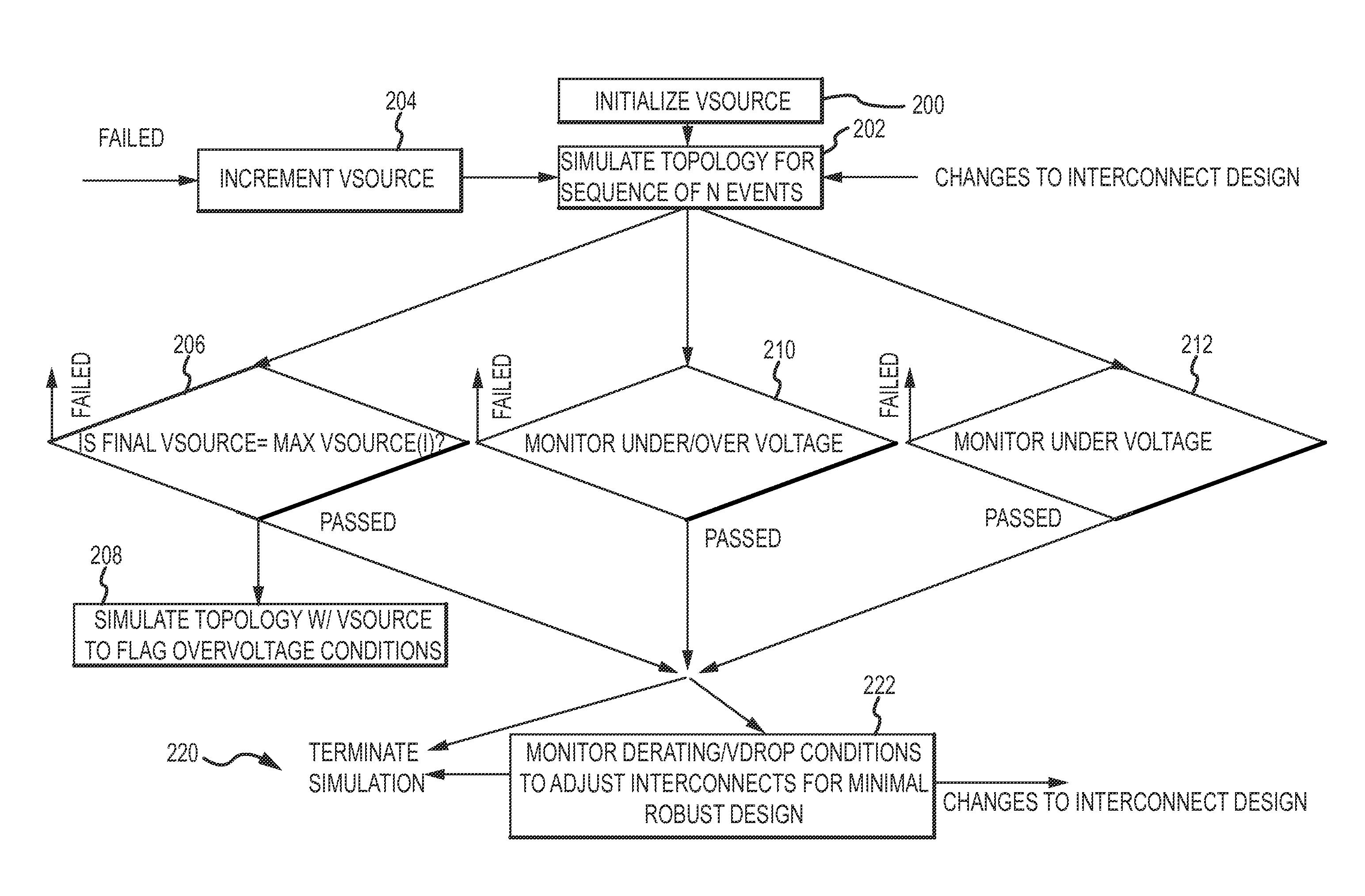

Differential interconnect topology in a substrate with staggered vias

InactiveUS20160172734A1Printed circuit aspectsHigh frequency circuit adaptationsInterconnect topologyDifferential signaling

An interconnect topology is disclosed that includes a plurality of interconnections, each of which is coupled together using a via, where at least two of the vias are staggered with respect to each other. In one embodiment, the interconnect topology comprises a substrate, multiple signal traces routed through the substrate on multiple layers, and a plurality of vias, where each via couples a pair of the signal traces to form an interconnection between different ones of the multiple layers, and where a pair of vias comprise a first via to carry a positive differential signal via and a second via to carry a negative differential signal that are coupled to signal traces to form a differential signal pair. The differential first and second vias are staggered with respect to each other.

Owner:INTEL CORP

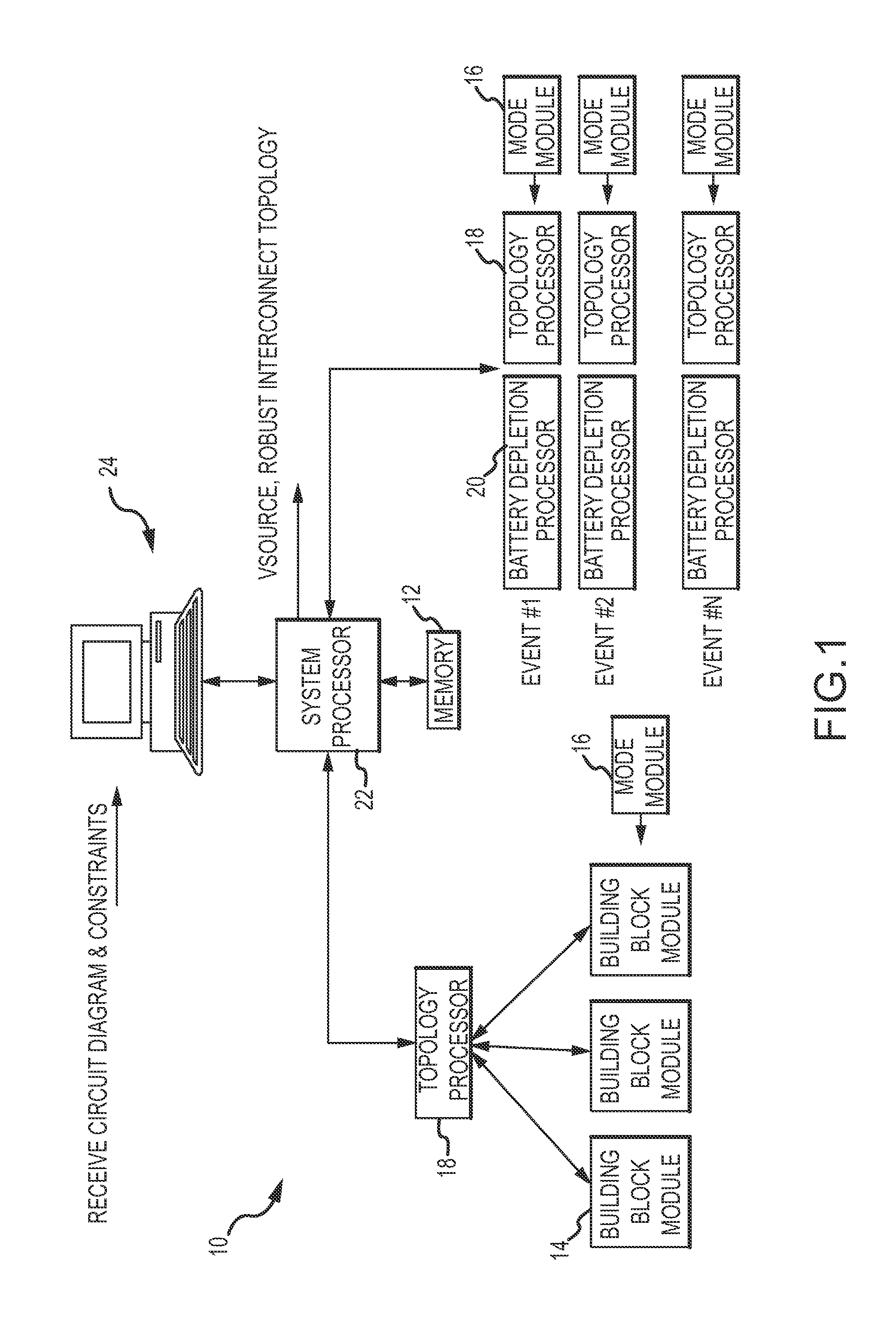

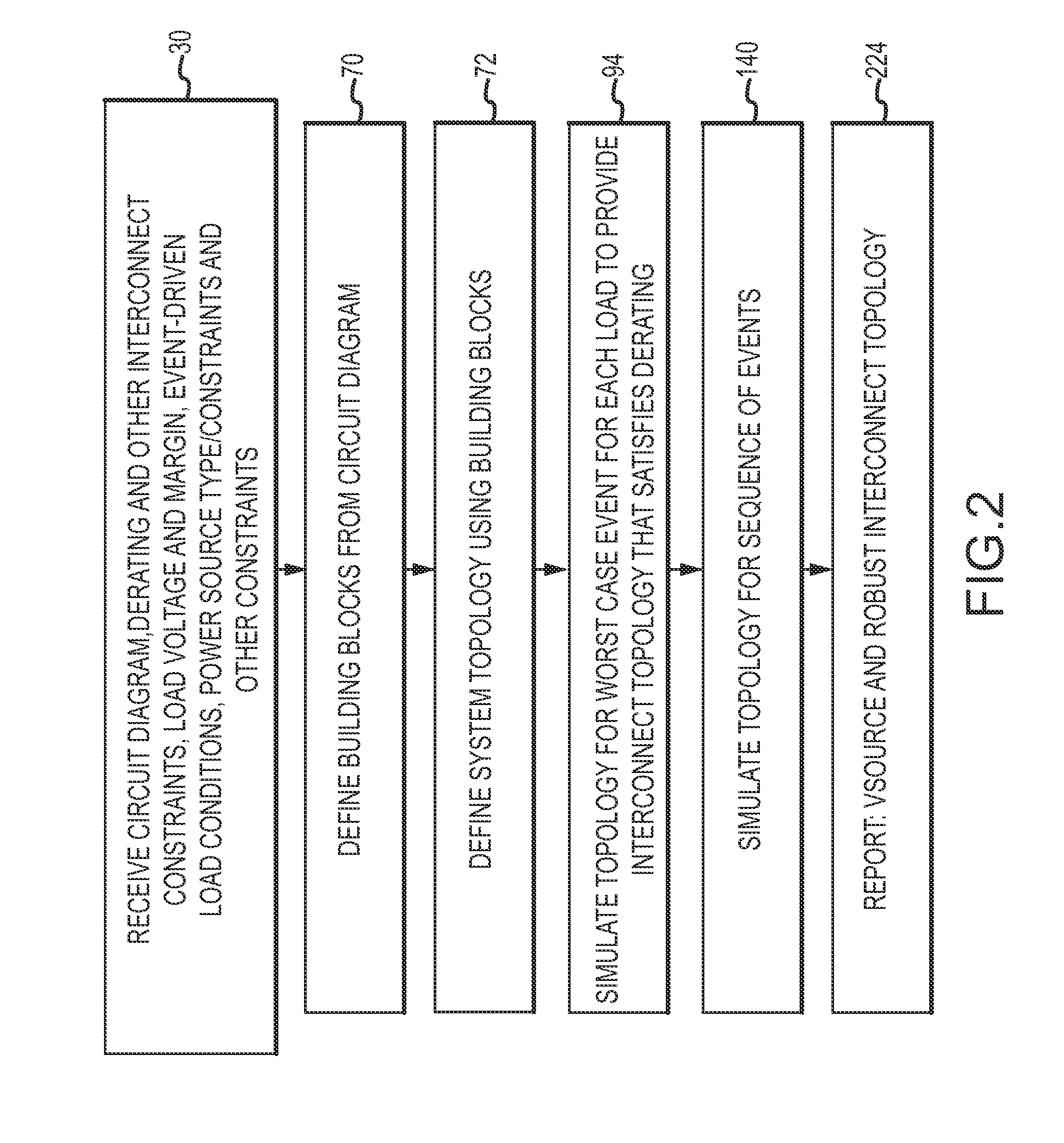

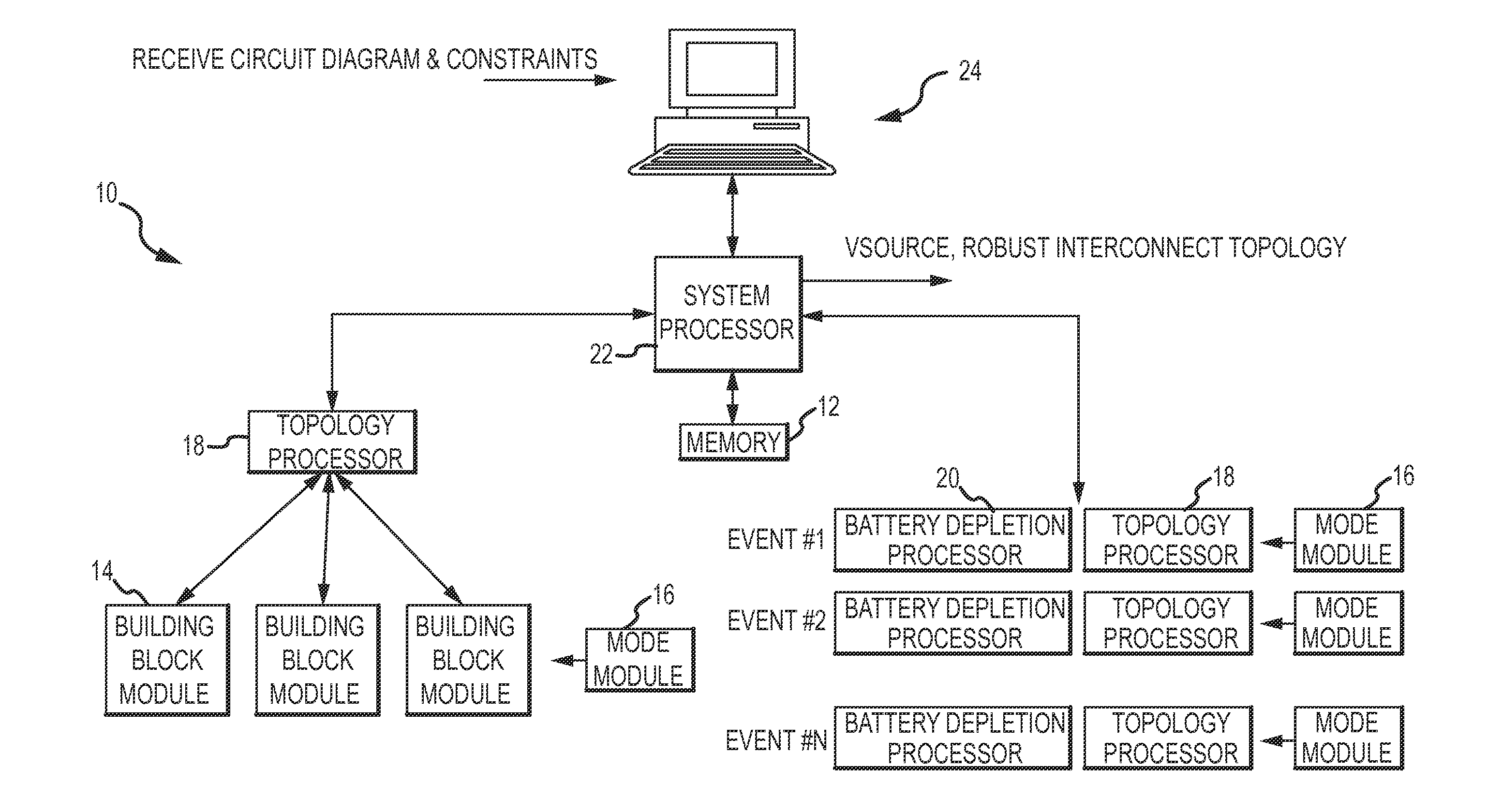

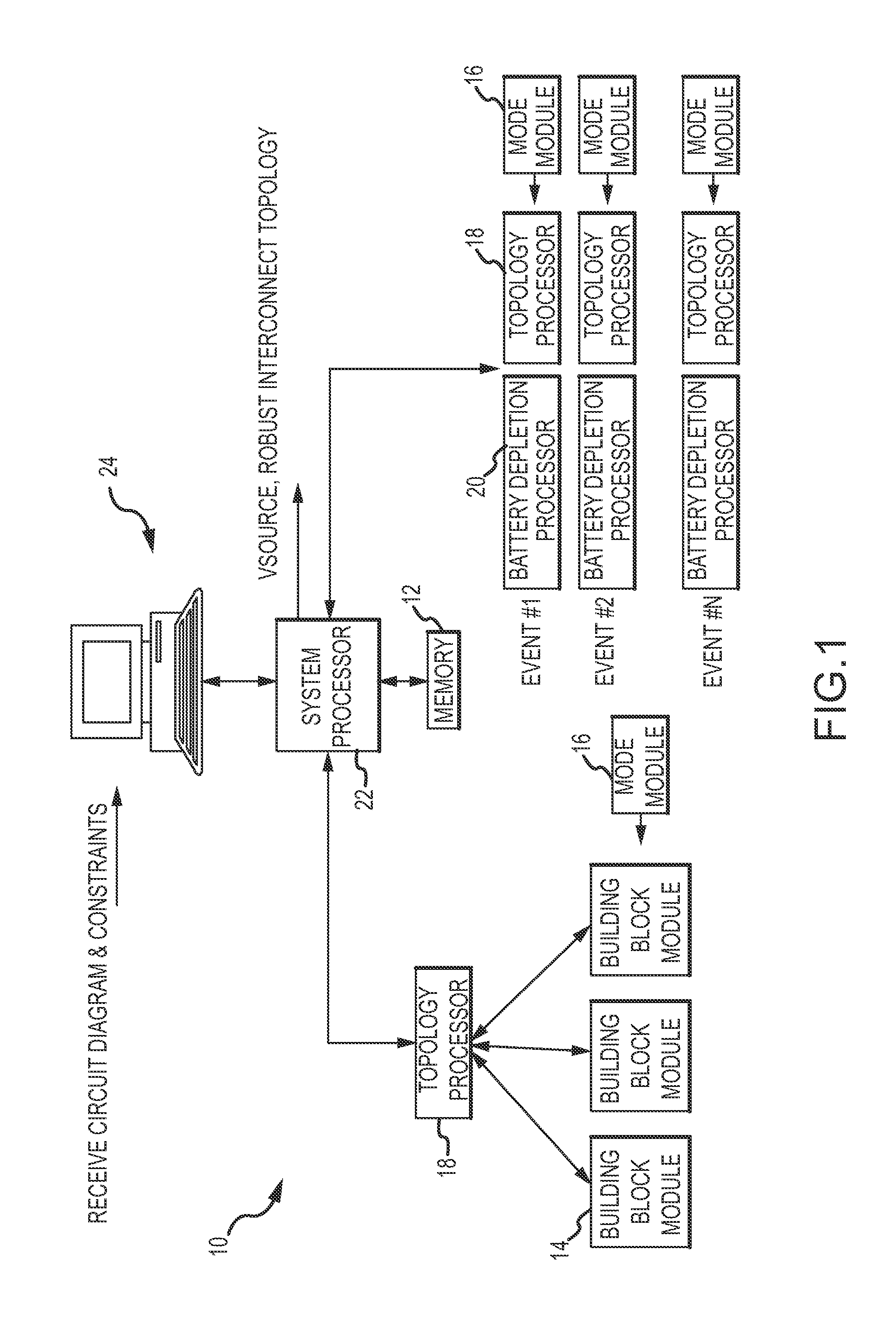

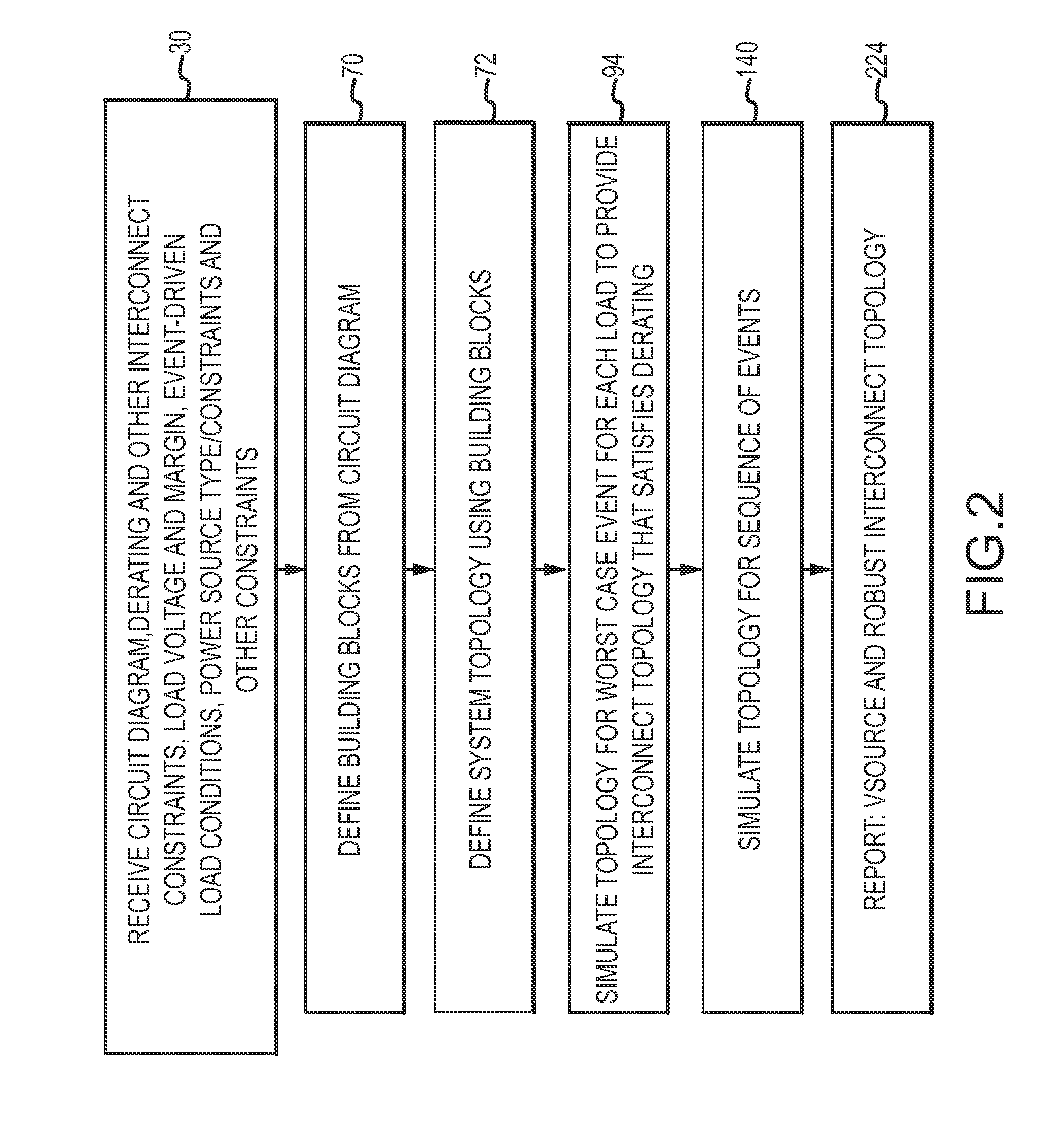

Systems power distribution tool

ActiveUS8195437B2Reduce any large voltage dropMore balancedAnalogue computers for electric apparatusAnalogue computers for nuclear physicsInterconnect topologyEngineering

A systems power distribution tool integrates the design of the power source and distribution network to provide a robust interconnect topology and power source. This is accomplished with a machine of one or more computing devices configured as a systems power distribution tool. The tool “pulls” load current from the source through interconnects to the loads. This allows the interconnects to be designed to satisfy derating conditions for worst case voltage and current conditions and the power source to be designed to source the loads under actual conditions without margin stacking.

Owner:RAYTHEON CO

Systems power distribution tool

ActiveUS20110082682A1Reduce any large voltage dropMore balancedAnalogue computers for electric apparatusAnalogue computers for control systemsInterconnect topologyEngineering

A systems power distribution tool integrates the design of the power source and distribution network to provide a robust interconnect topology and power source. This is accomplished with a machine of one or more computing devices configured as a systems power distribution tool. The tool “pulls” load current from the source through interconnects to the loads. This allows the interconnects to be designed to satisfy derating conditions for worst case voltage and current conditions and the power source to be designed to source the loads under actual conditions without margin stacking.

Owner:RAYTHEON CO