Subsystem integration method and subsystem integration system for integration design of system-on-chip

A system-on-a-chip, integration method technology, applied in computing, special data processing applications, instruments, etc., can solve the problems of low integration efficiency, low flexibility, and low subsystem integration configurability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

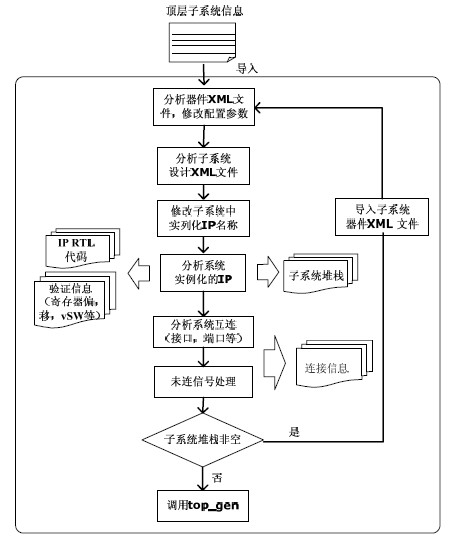

[0070] refer to Figure 1 to Figure 6 , a subsystem integration method for system chip integration design, the subsystem integration method comprises the steps of:

[0071] 1) Adopt the IP-XACT standard to package the subsystem, and the subsystem includes the XML file of the subsystem device, the XML file of the subsystem design and the subsystem generator;

[0072] 2) Write a subsystem XML file analysis tool using script language. During the instantiation process of the subsystem, analyze the instantiated devices in the subsystem, and analyze other subsystems instantiated in the subsystem iteratively at the same time, for each instantiation Create a directory for the device, and transfer the working directory to the corresponding directory, call the device generator to generate the device RTL code and test stimulus template, and use the code modification tool in step 3) to modify the module and macro name; when the iterative analysis of the subsystem is completed After that,...

example

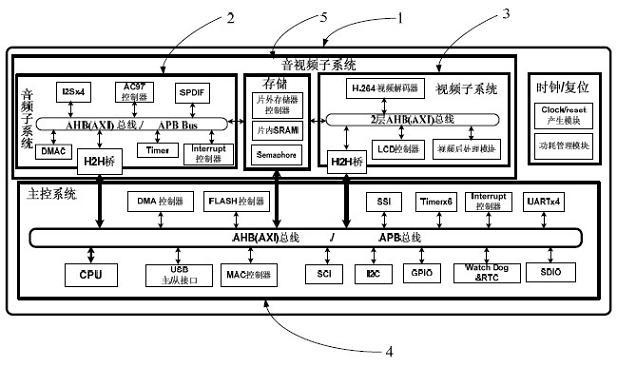

[0111] Example: The IP owned by Hangzhou Zhongtian Microsystems is packaged into a library using the IP-XACT standard. The IP of Hangzhou Zhongtian Microsystems is composed of two parts: one is the IP independently developed by the company, including CKCore embedded with independent intellectual property rights type processor, h.264 video decoder, etc.; the second is DesignWare IP based on Synoposis. Based on the SoC architecture of Hangzhou Zhongtian Microsystems, commonly used functional modules are packaged into subsystems, mainly including: video subsystem, audio subsystem, peripheral interface subsystem, etc. Put all packaged IP and subsystems into the IP library, and the IP library is named aphrodite.

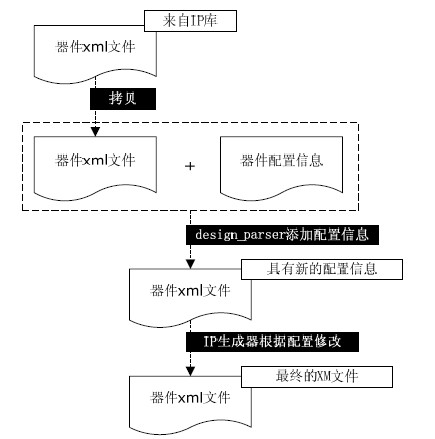

[0112] Write the subsystem design XML file analysis tool in Perl language and name it design_parser to extract relevant information from the subsystem XML file and pass it to the subsystem top-level RTL code generation tool through the internal data structure of Perl to g...

Embodiment 2

[0155] refer to Figure 1 to Figure 6 , a subsystem integration system for system chip integration design, the subsystem integration system includes: subsystem device XML file, used to describe the VLNV information of the subsystem, bus interface, physical port, configuration parameters, subsystem generation In the system chip integration process, the subsystem is integrated as a common IP and indexed from the IP library through VLNV information;

[0156] The subsystem design XML file is used to describe the instantiated IP in the subsystem and the interconnection between IPs;

[0157] The subsystem generator is used to modify the components and design XML files of the subsystem according to the configuration parameters;

[0158] The subsystem design XML file analysis tool is used to extract the information of each part step by step from the subsystem XML file and save it in the internal data structure of the script, and then call the subsystem top-level RTL code gen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More