General signal processing board card based on multi-core DSP (digital signal processor)

A digital signal processing and board card technology, applied in the fields of image processing, missile, radar, communication, digital signal processing, and remote sensing, it can solve the problem of small memory capacity, low speed, short transmission distance of upper computer control, and data throughput between processors. Small and other problems, to achieve the effect of enhancing system stability, reducing design cost and shortening design cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

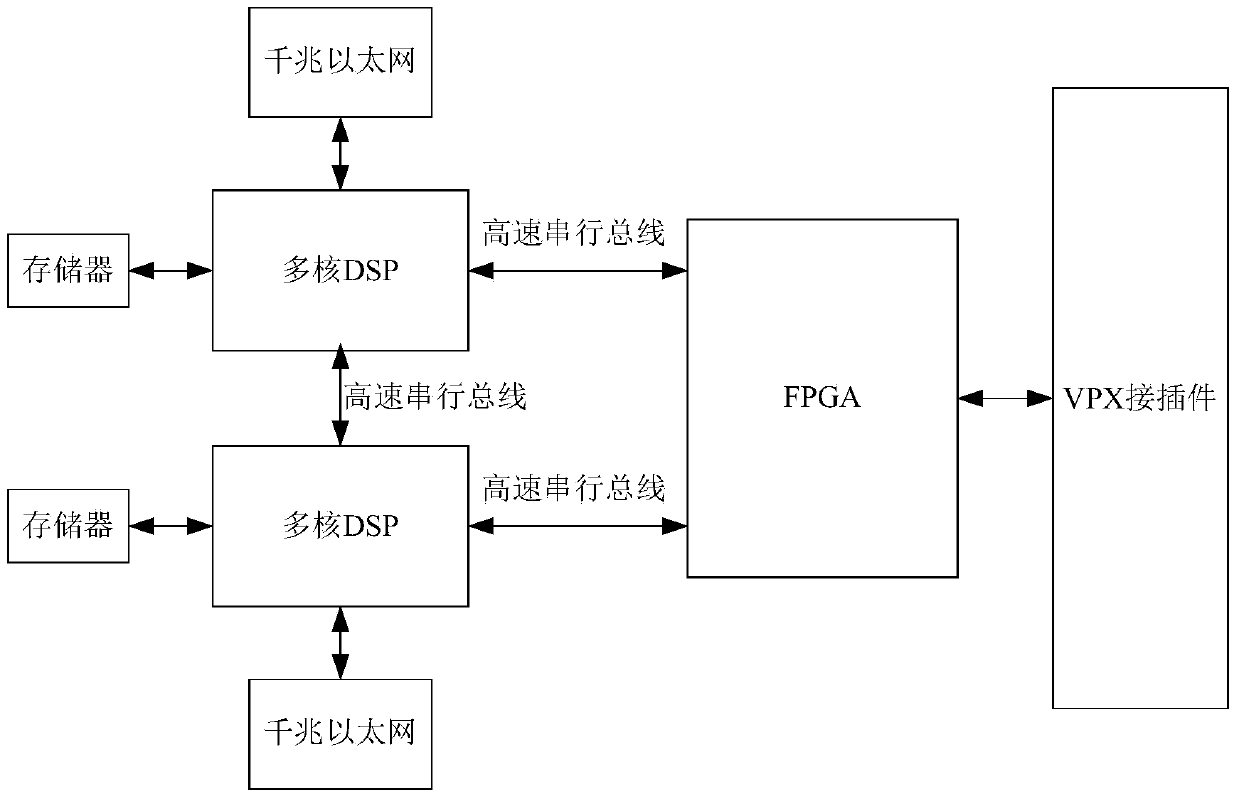

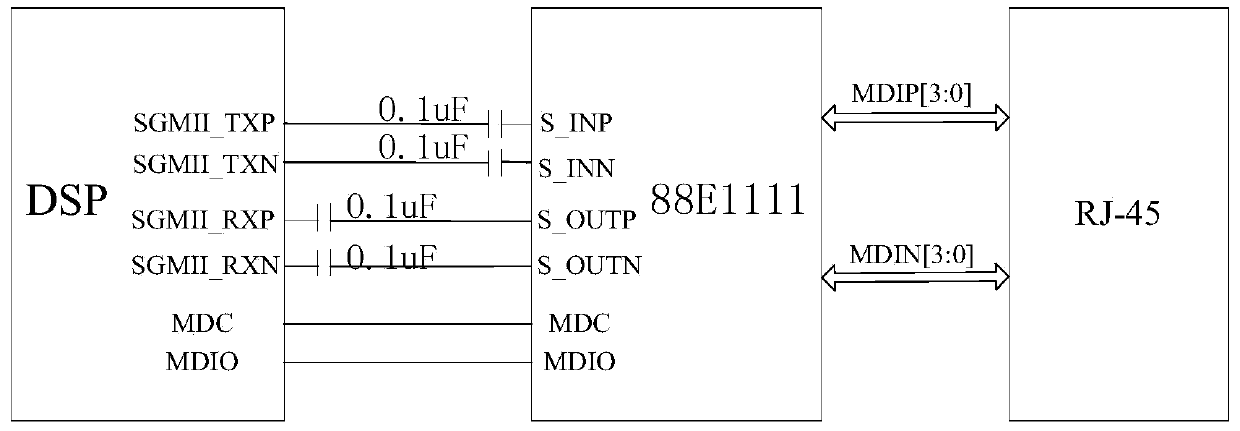

[0033] Reference attached figure 1 In this example, an FPGA chip is used as the main control core, and two multi-core DSP chips are used as the main data processing unit. The DSP chips are all interconnected by high-speed serial bus. The peripherals of the DSP chips are also extended with high-speed large-capacity memory and Gigabit Ethernet interface. The entire board uses VPX connectors to connect with the external system; this example can realize fast data transfer. Transmission, storage, processing and playback.

[0034]The FPGA in this example uses the Virtex-6 series chip XC6VLX130T-FF1156, which integrates 128,000 logic units, 1740Kb distributed RAM memory, 9504Kb block RAM memory, 480 digital signal processing logic units (DSP48E1), 600 Input and output (I / O) pins and 20 gigabit transceiver resources are mainly used for high-speed data transmission of general digital signal processing boards and processing of some simple digital signal processing algorithms, such as F...

Embodiment 2

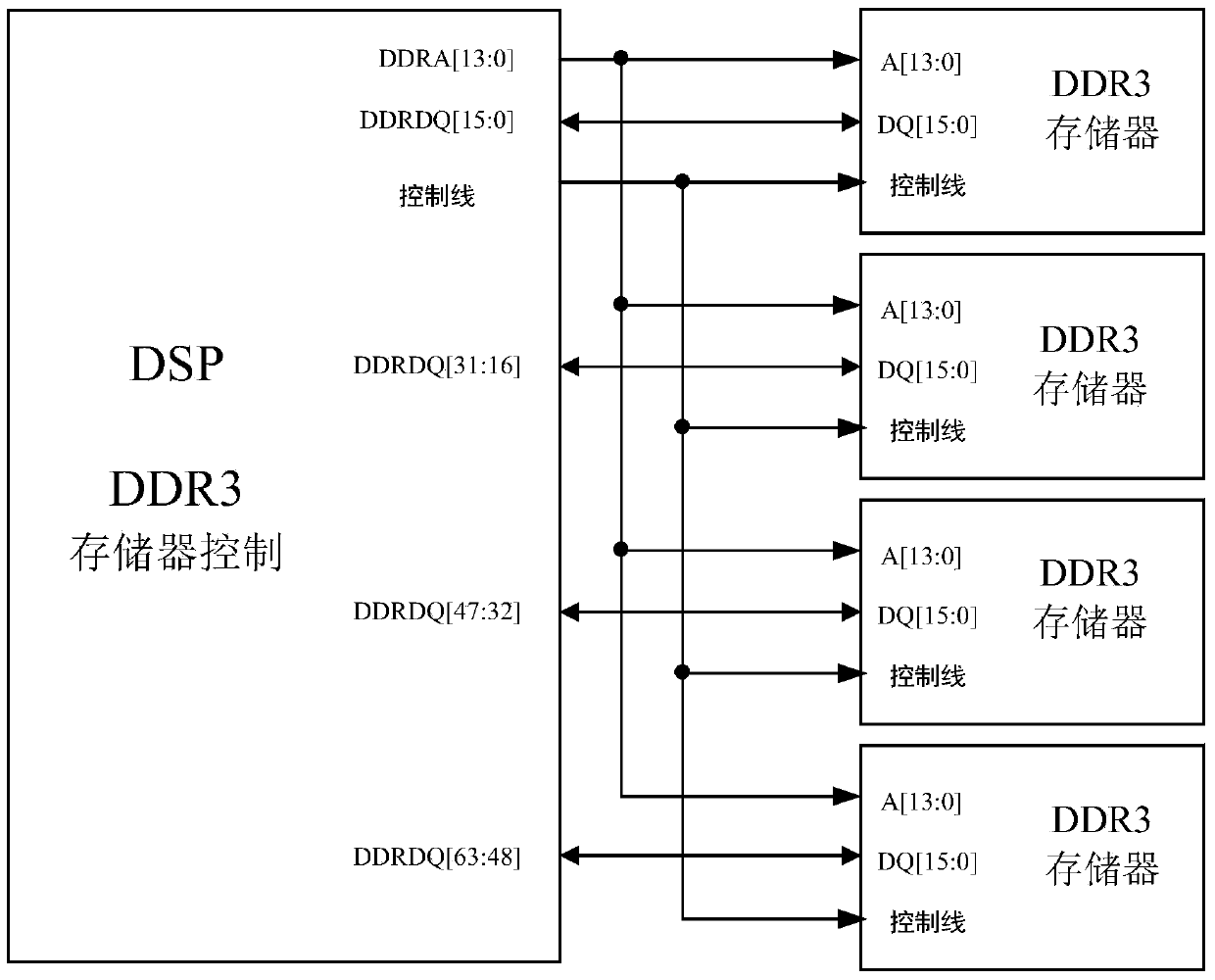

[0054] The overall composition of the general digital signal processing board based on multi-core DSP and the connection mode between the processors are the same as in Embodiment 1, wherein the FPGA chip of this example selects the Virtex-6 series chip XC6VLX240T-FF1156, which integrates 241152 logic units inside , 3650Kb distributed RAM memory, 14976Kb block RAM memory, 768 digital signal processing logic units (DSP48E1), 600 input and output (I / O) pins and 20 gigabit transceiver resources; multi-core DSP chooses TI company The quad-core chip TMS320C6674, the main frequency of each core of this chip is 1.25GHz, and the four cores provide up to 160GMAC fixed-point operation or 80GFLOP floating-point operation per second; the DDR3 chip uses Samsung's K4B2G1646E, and the highest transmission rate of DDR3 is 1600Mb / s, the total storage capacity of four chips is 1GB. This embodiment is compared with embodiment 1, and the internal resource of FPGA chip expands approximately twice ...

Embodiment 3

[0057] The overall composition of the general digital signal processing board based on multi-core DSP and the connection mode between the processors are the same as in Embodiment 1, wherein the FPGA chip of this example selects the Virtex-6 series chip XC6VLX315T-FF1156, which integrates 314880 logic units , 5090Kb distributed RAM memory, 25344Kb block RAM memory, 1344 digital signal processing logic units (DSP48E1), 600 input and output (I / O) pins and 20 gigabit transceiver resources; multi-core DSP chooses TI company The octa-core chip TMS320C6678, the main frequency of each core of this chip is 1.25GHz, and the eight cores provide up to 320GMAC fixed-point operation or 160GFLOP floating-point operation per second; the DDR3 chip uses Samsung's K4B4G1646B, and the highest transmission rate of DDR3 is 1600Mb / s, the total storage capacity of the four chips is 2GB; other aspects of this embodiment, including the overall architecture and interconnection between processors, are th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More