Patents

Literature

85results about How to "Reduce interconnection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

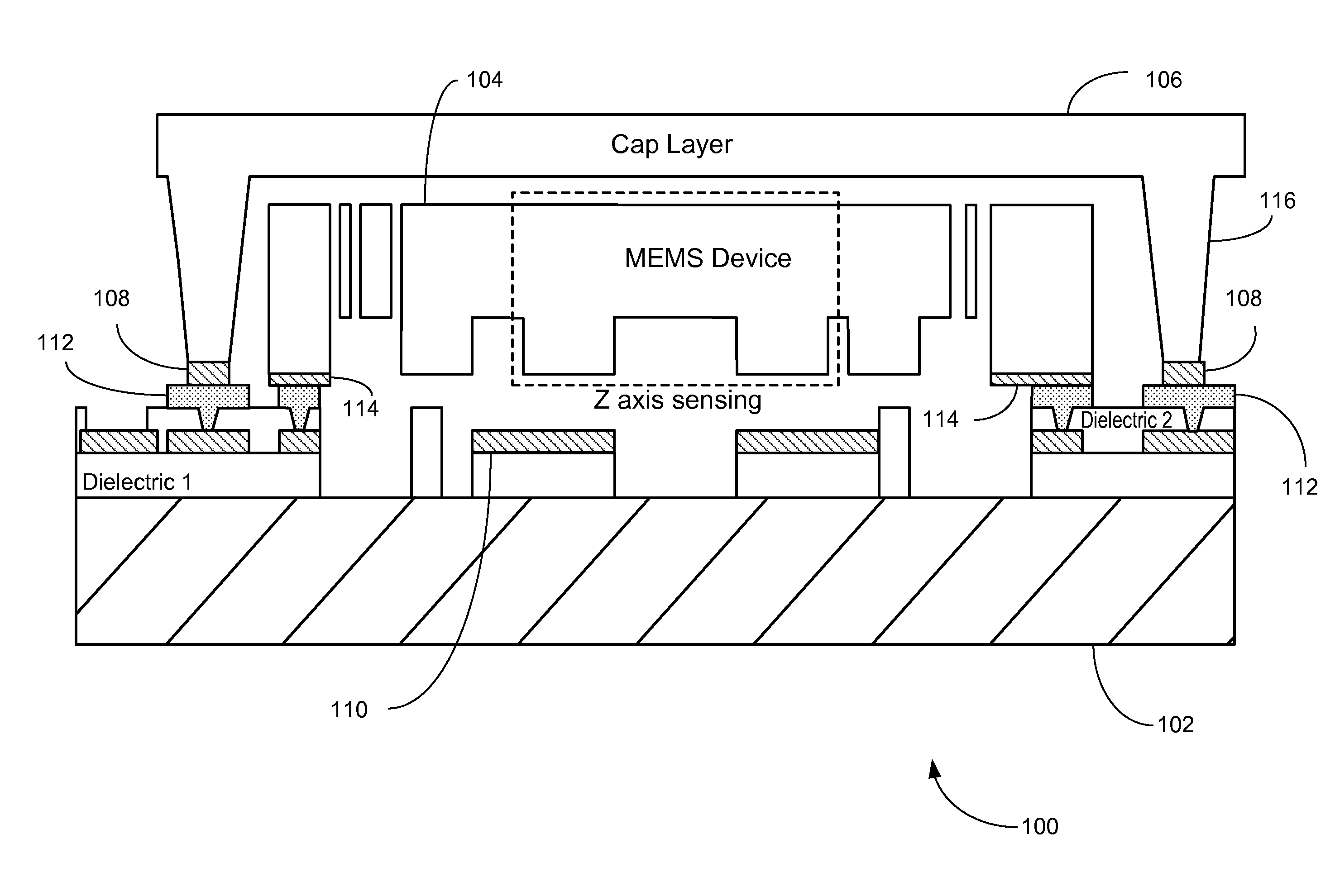

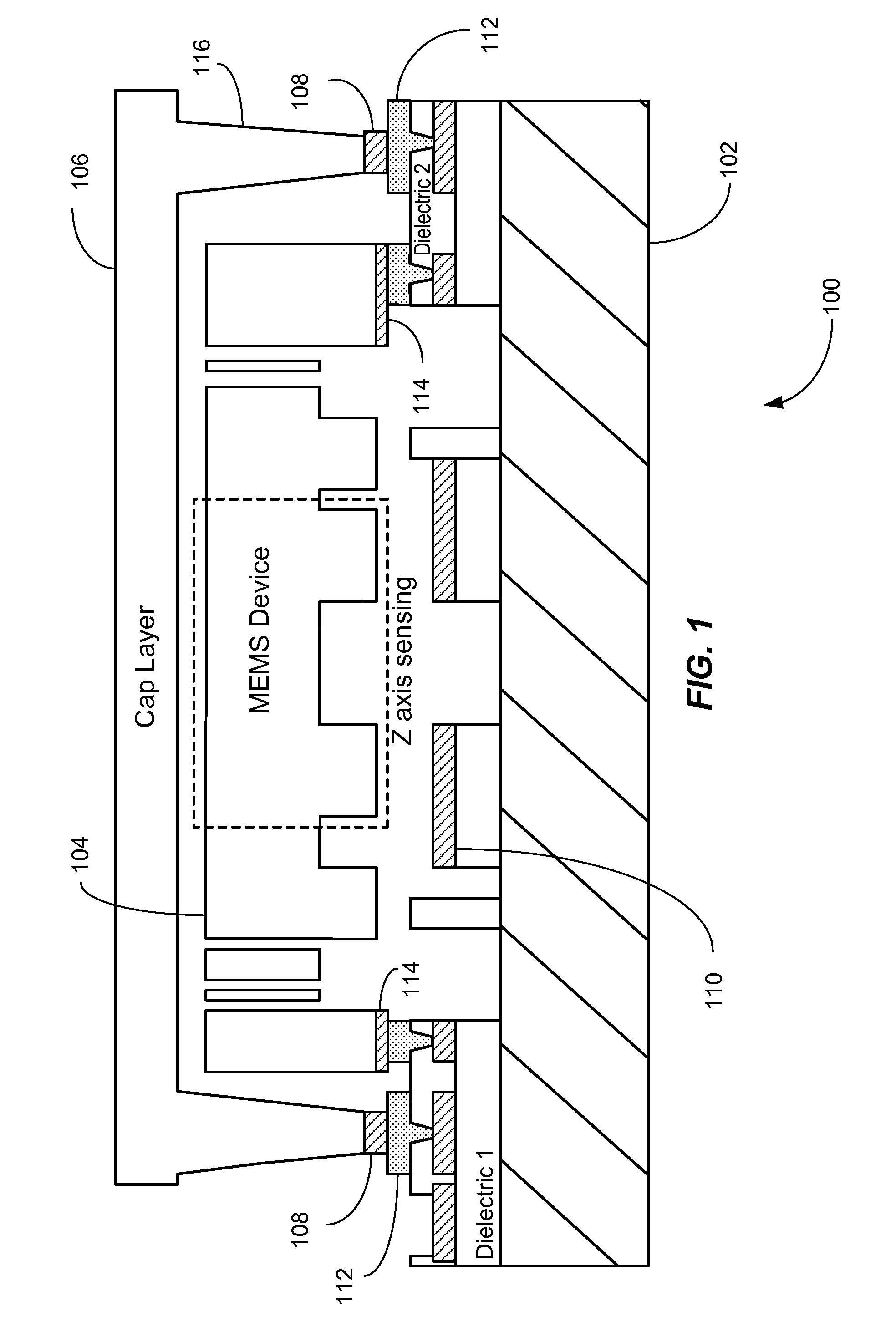

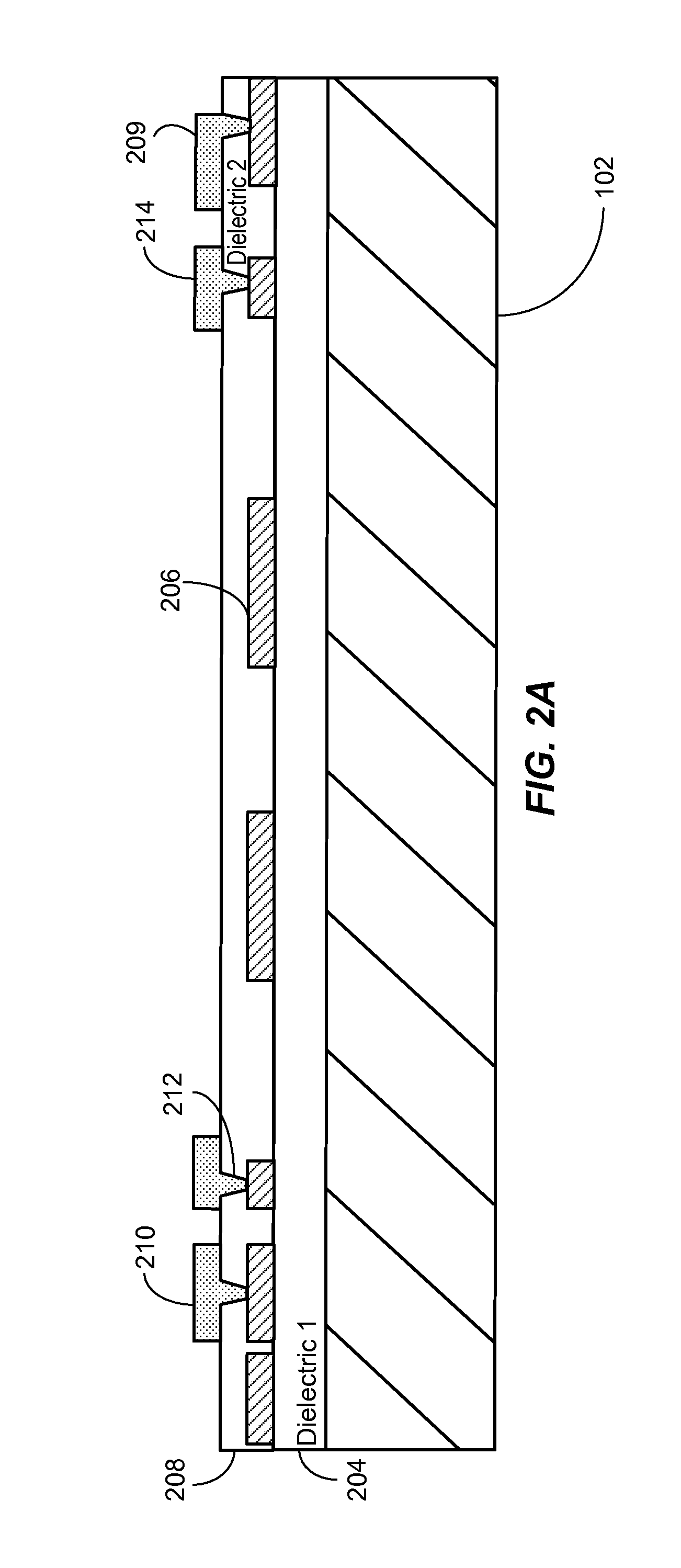

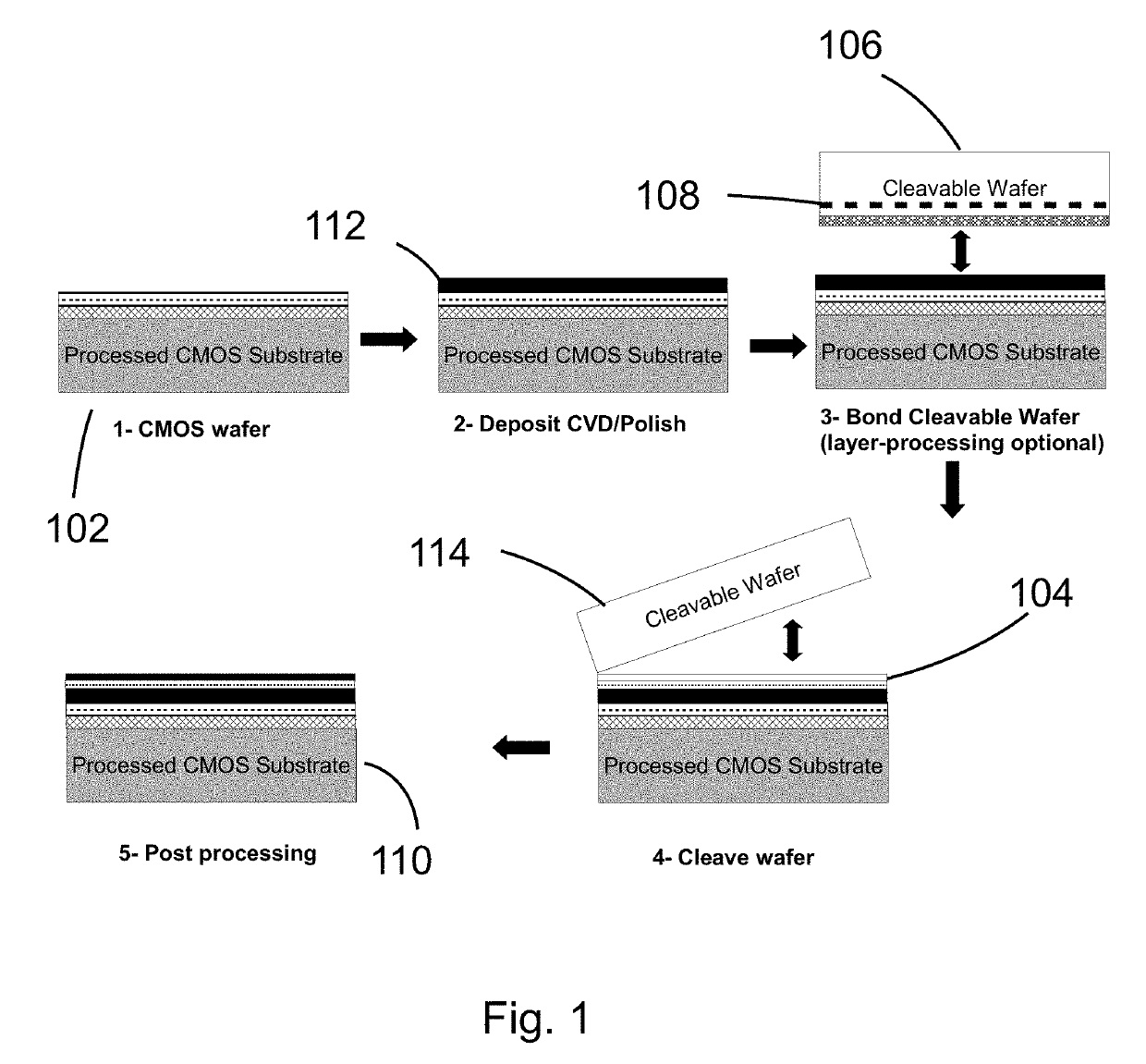

Method and system for MEMS devices

InactiveUS20110049652A1Accurately depositAccurately definedAcceleration measurement using interia forcesSemiconductor/solid-state device manufacturingEngineeringElectrical and Electronics engineering

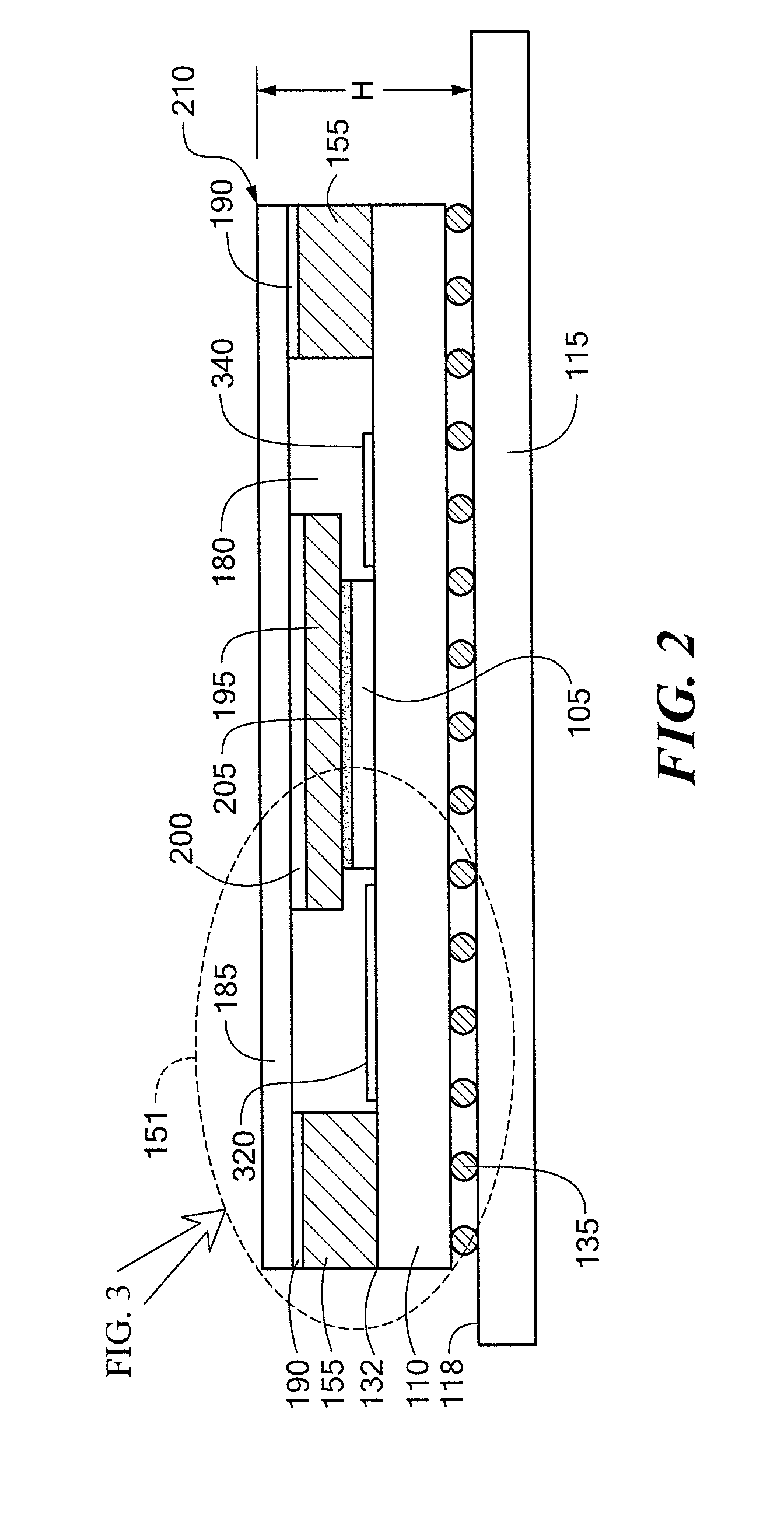

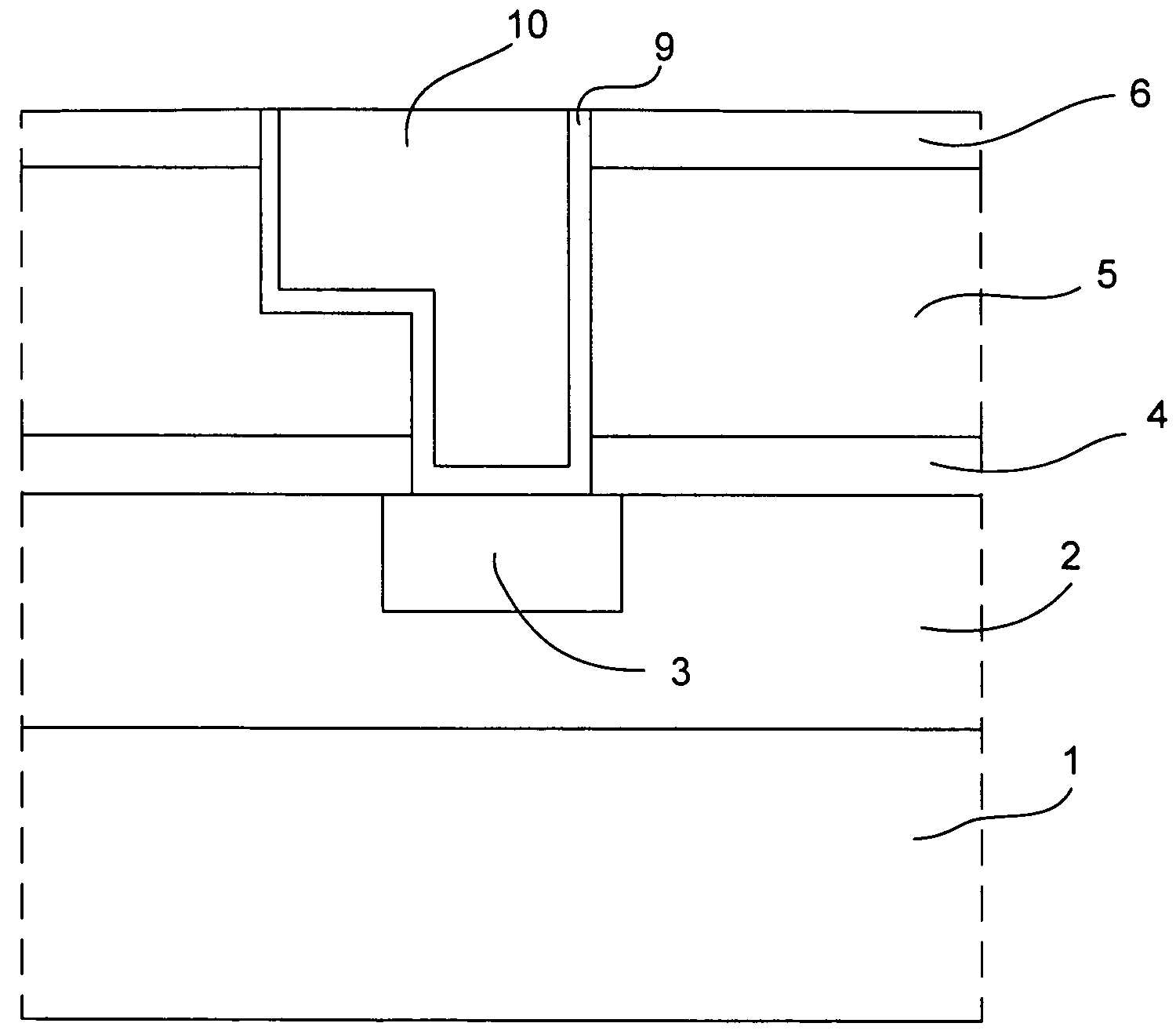

A micro electro-mechanical (MEMS) device assembly is provided. The MEMS device assembly includes a first substrate that has a plurality of electronic devices, a plurality of first bonding regions, and a plurality of second bonding regions. The MEMS device assembly also includes a second substrate that is bonded to the first substrate at the plurality of first bonding regions. A third substrate having a recessed region and a plurality of standoff structures is disposed over the second substrate and bonded to the first substrate at the plurality of second bonding regions. The plurality of first bonding regions provide a conductive path between the first substrate and the second substrate and the plurality of the second bonding regions provide a conductive path between the first substrate and the third substrate.

Owner:MIRADIA INC

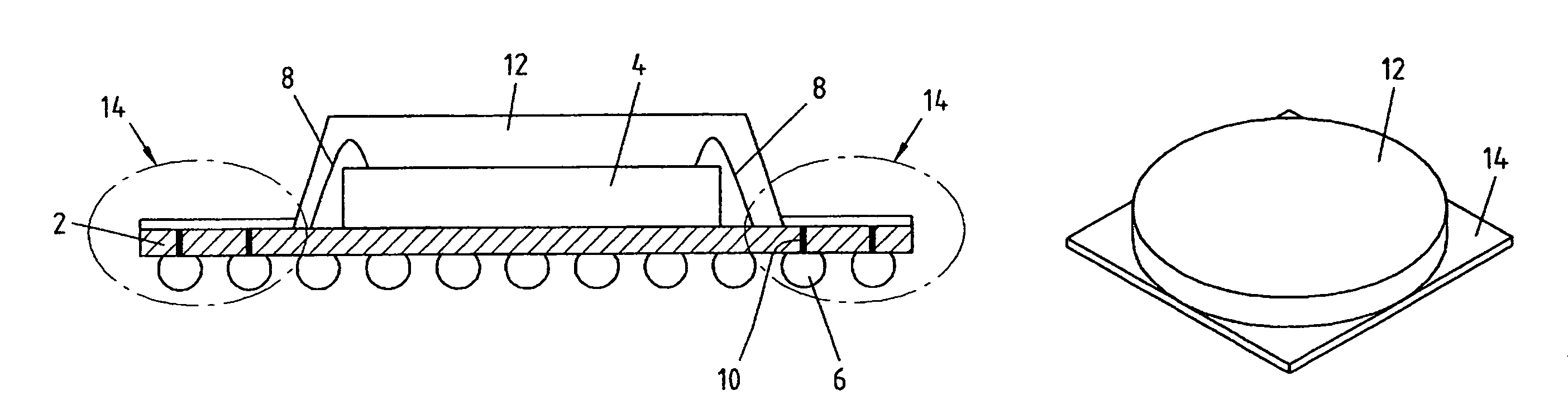

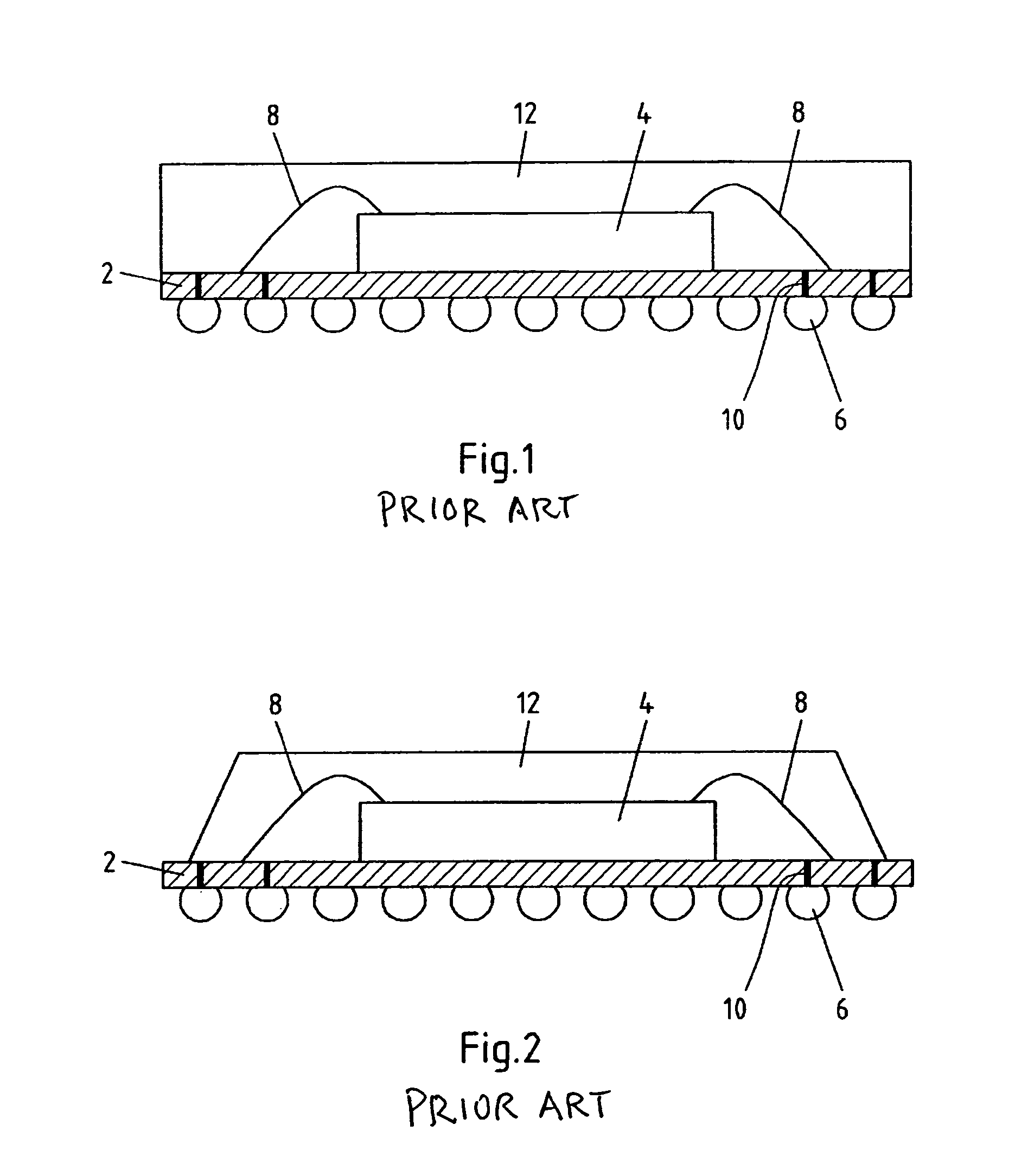

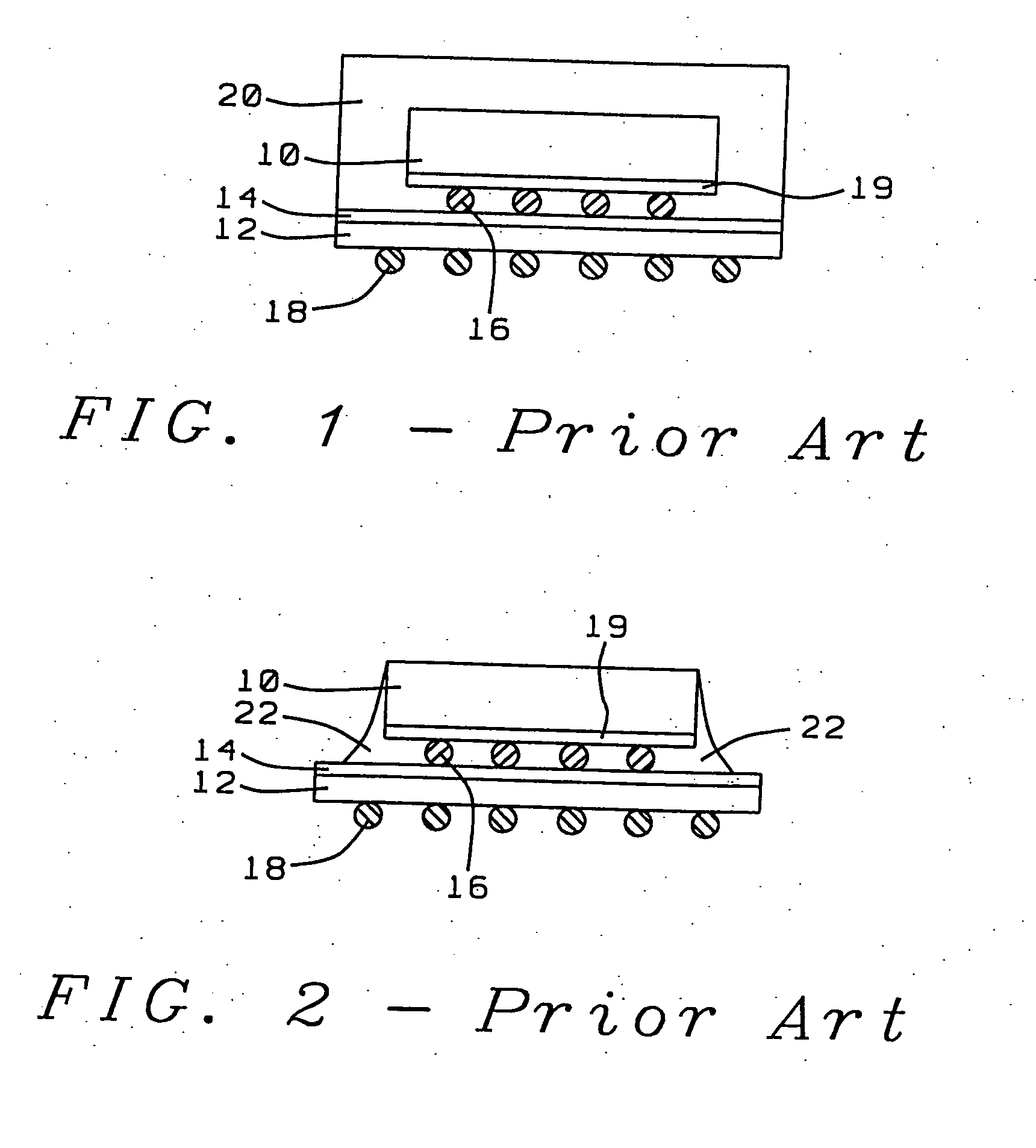

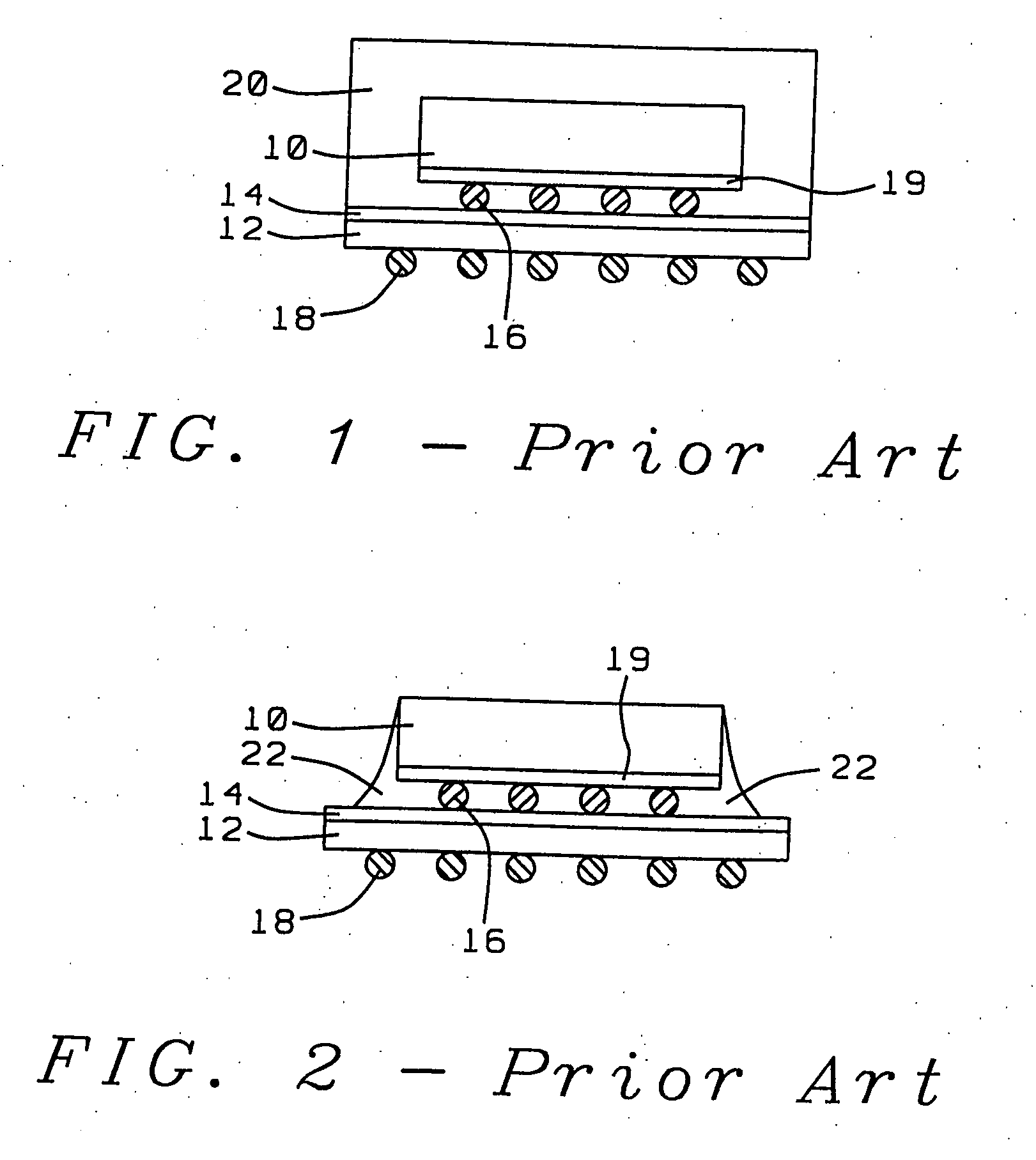

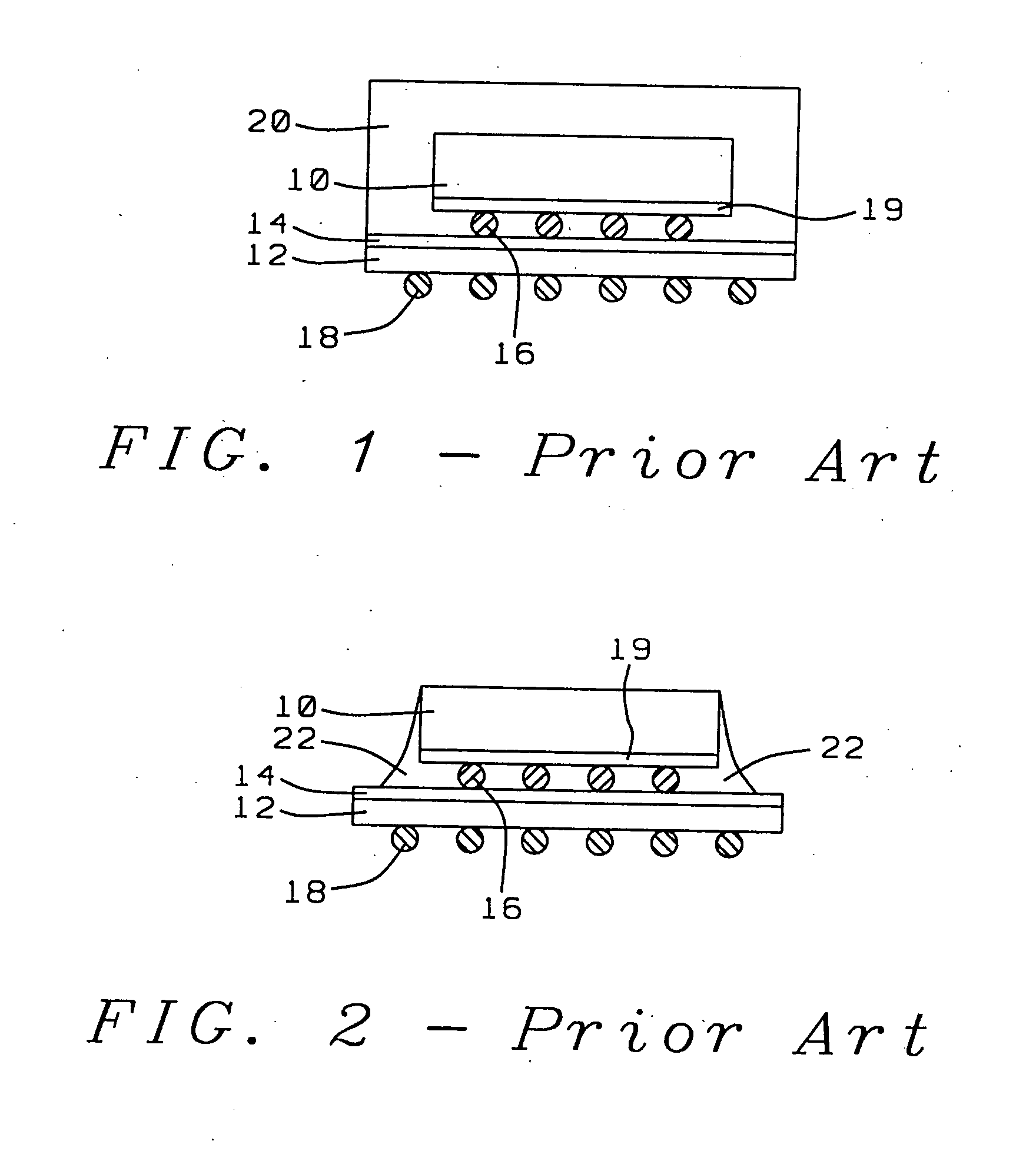

Integrated circuit package with optimized mold shape

InactiveUS7233057B2Reduce stiffnessIncrease flexibilitySemiconductor/solid-state device detailsSolid-state devicesChip sizeInterconnection

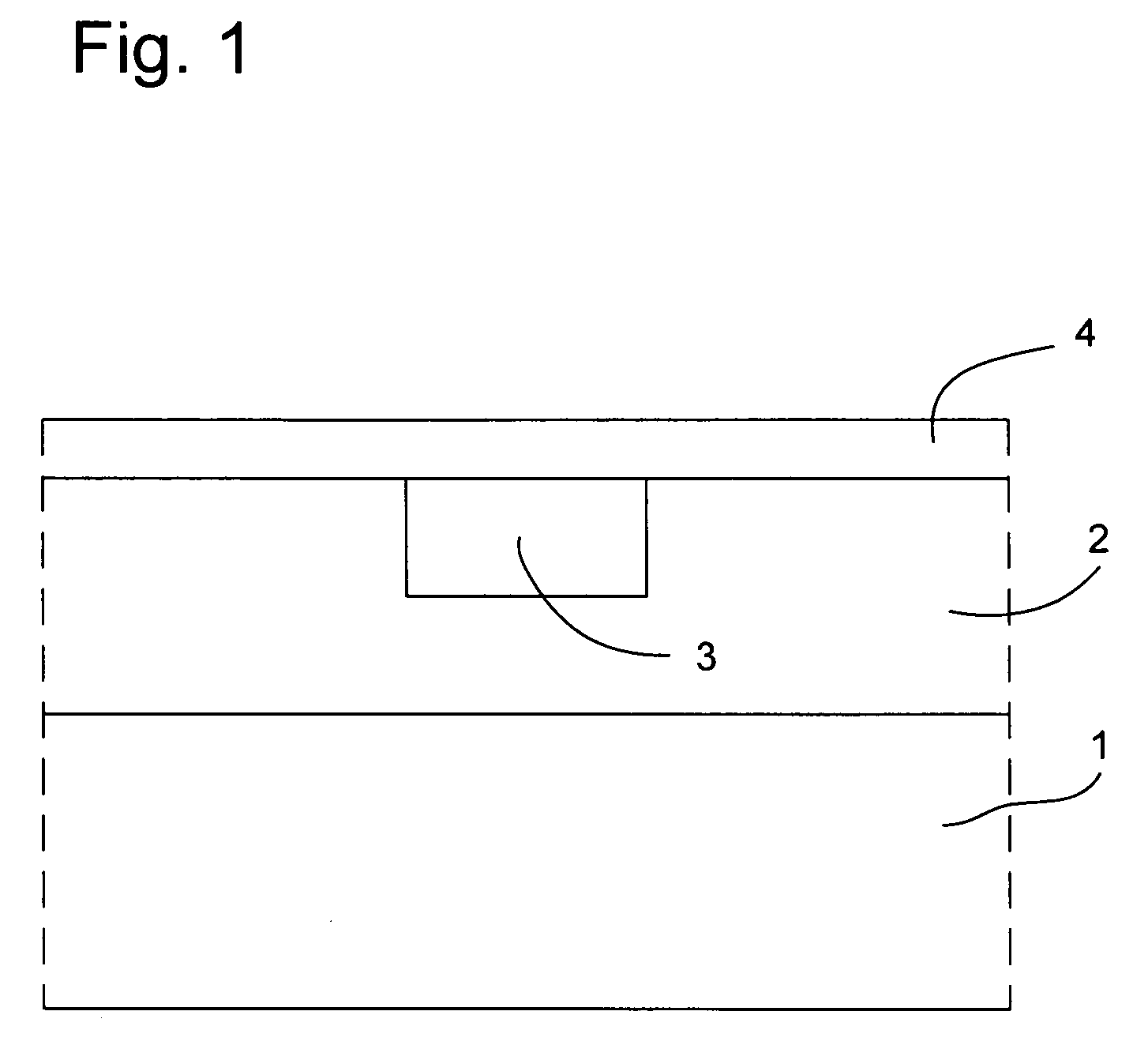

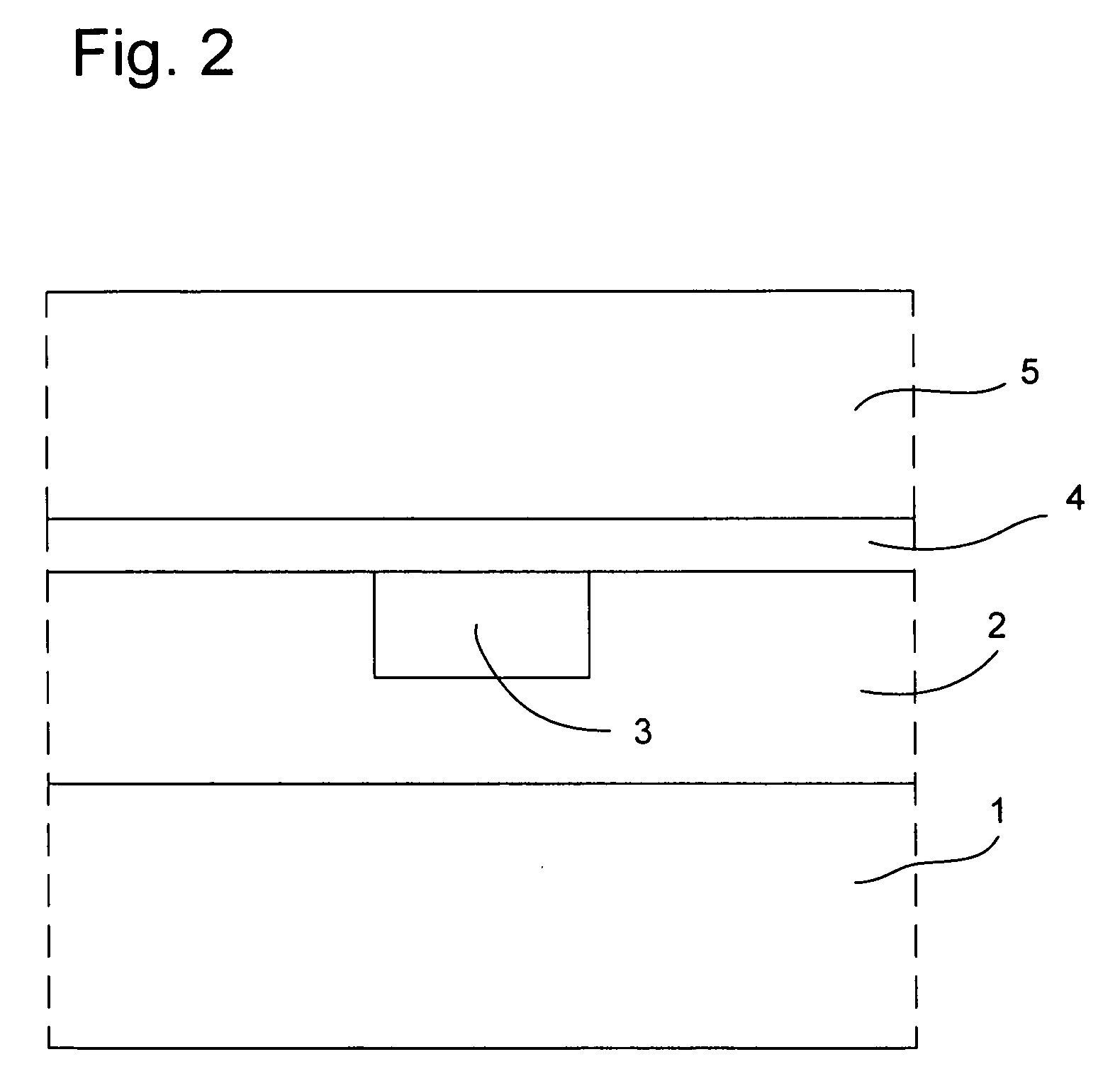

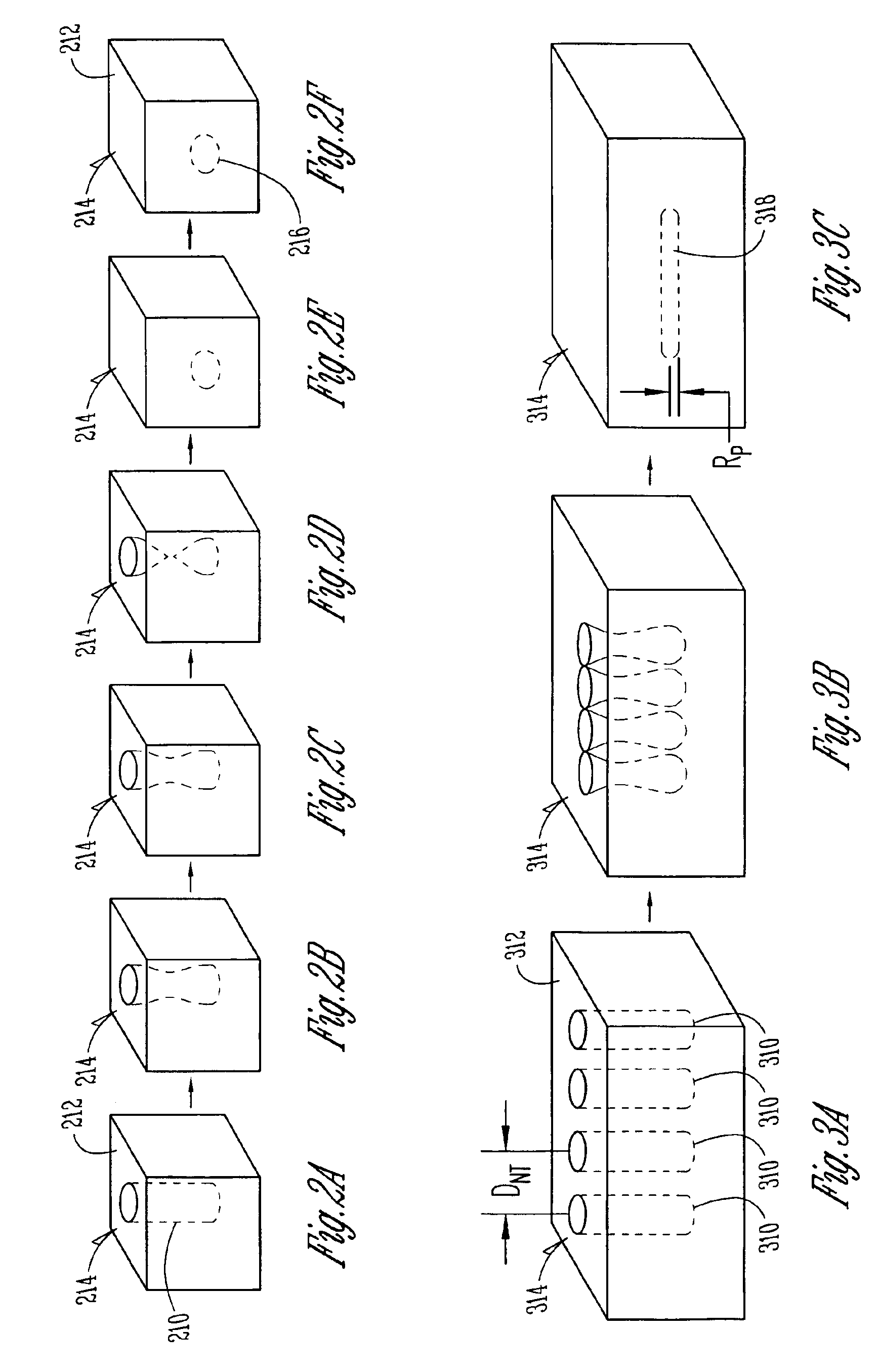

The invention relates to an integrated circuit package, in particular an integrated chip size package or an integrated chip scale package, comprising a substrate carrying a die, and connection elements, interconnection elements, connecting pins of said die with said connection elements, and a mold encapsulating said die on said substrate. To increase reliability and to reduce failure due to deformation stress, the invention provides said mold with reduced stiffness at areas located substantially at one of said interconnection elements providing increased flexibility of said package at said areas compared to other areas of said package.

Owner:NOKIA CORP

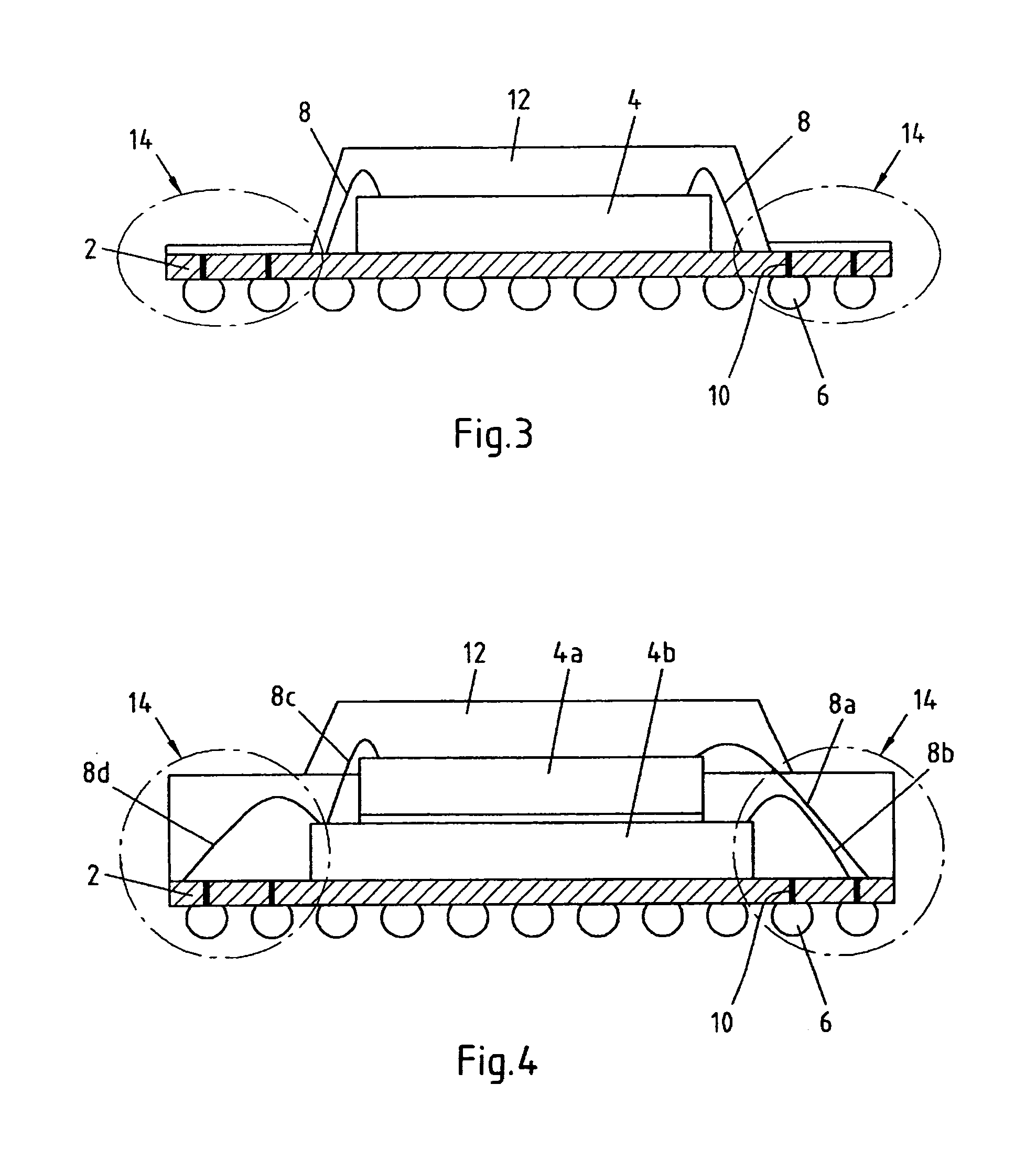

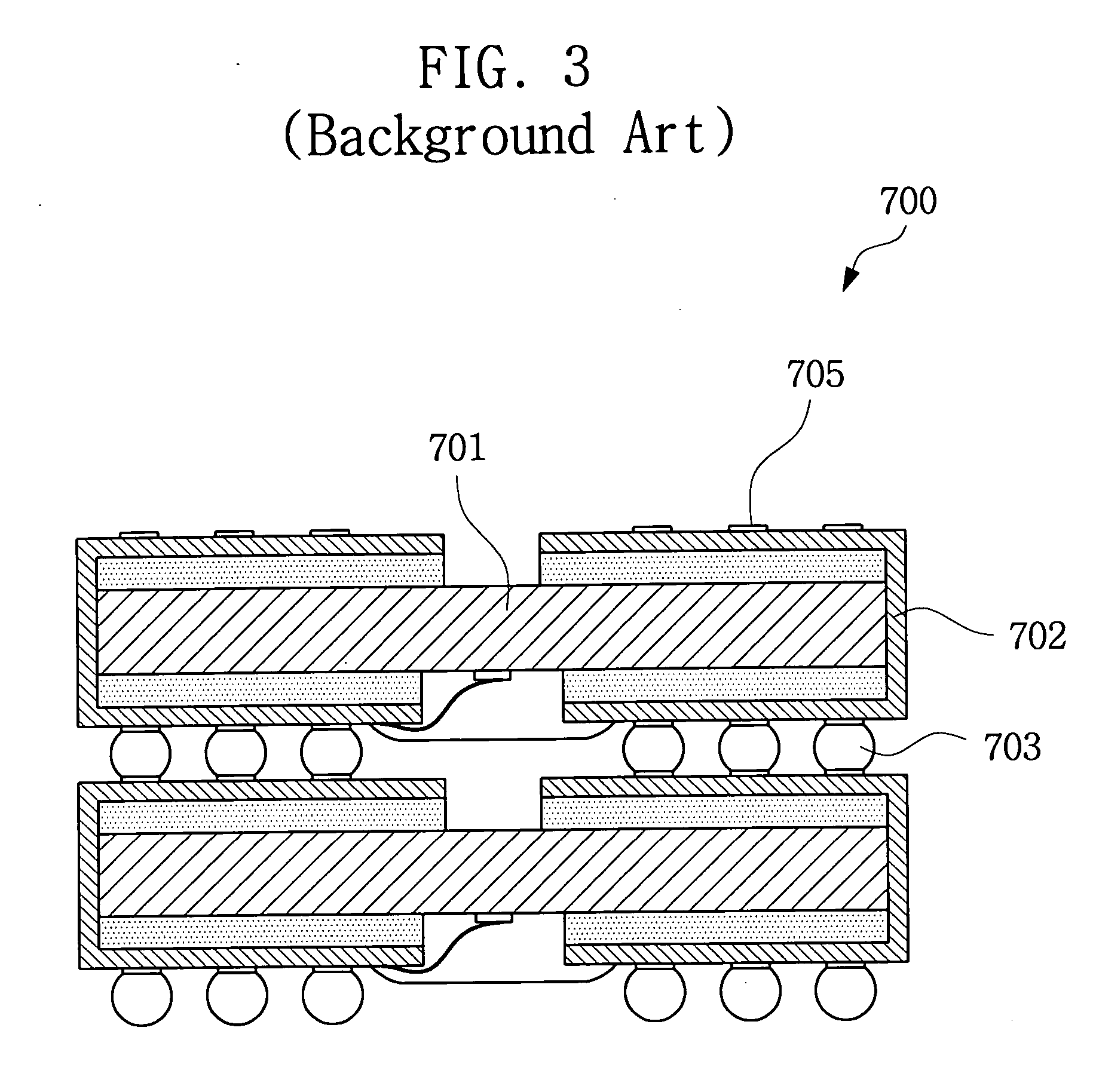

Area array type package stack and manufacturing method thereof

InactiveUS20050040508A1Reduce package heightReduce the overall heightSemiconductor/solid-state device detailsSolid-state devicesEngineeringFlexible cable

A package stack has at least two packages of area array types (AAT), each having connecting pads. A flexible cable having conductive patterns is provided between the AAT packages and electrically connected to the connecting pads of the packages.

Owner:SAMSUNG ELECTRONICS CO LTD

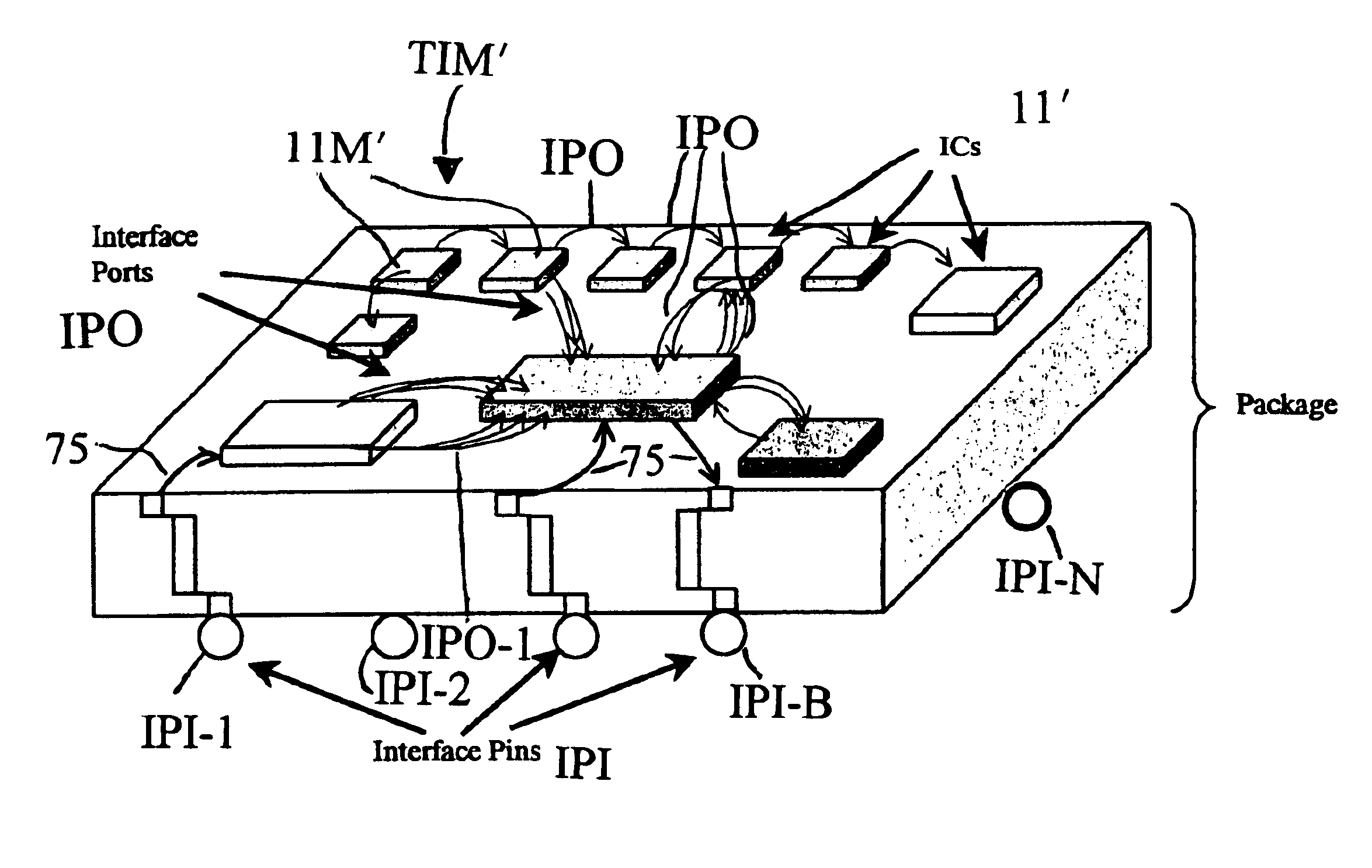

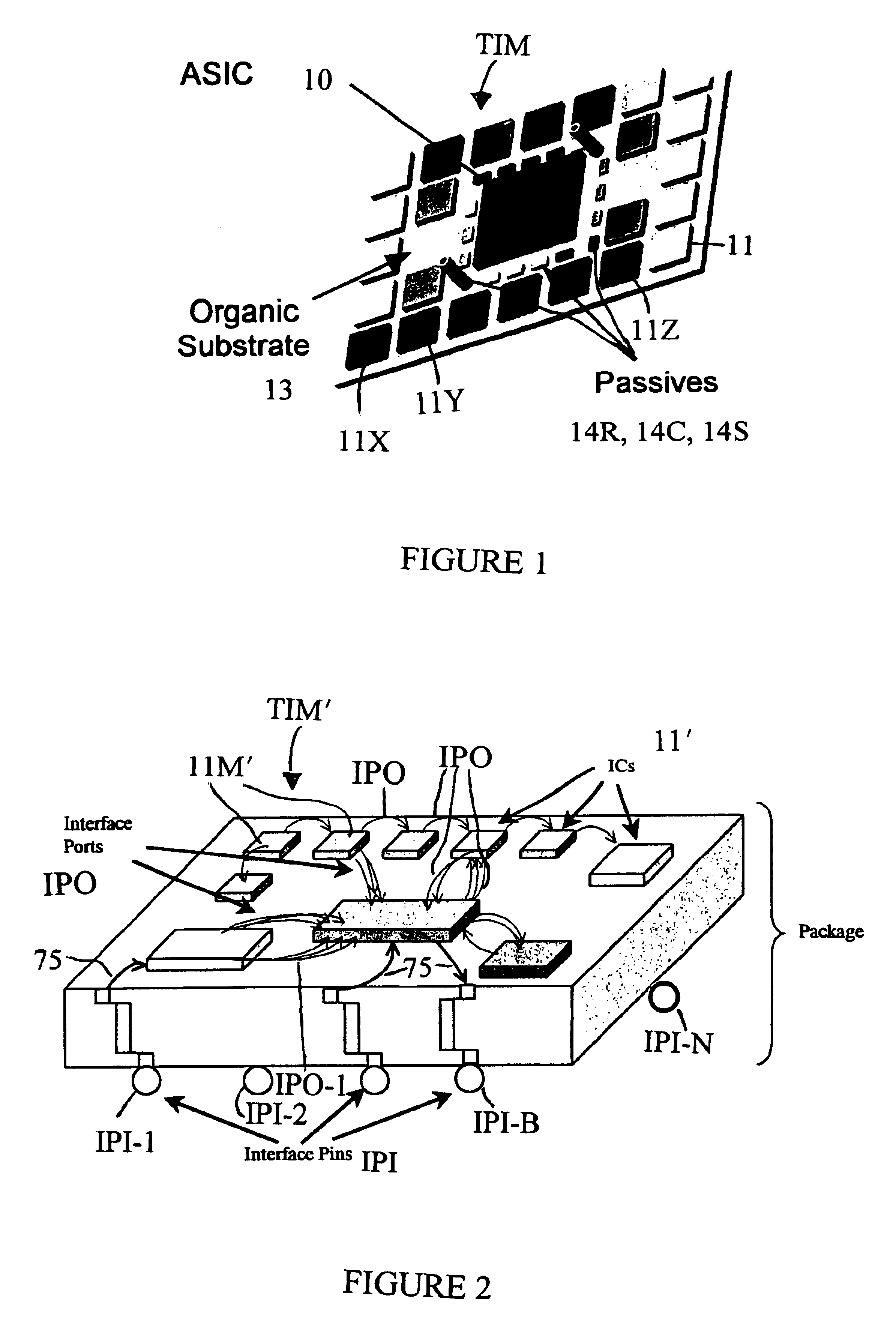

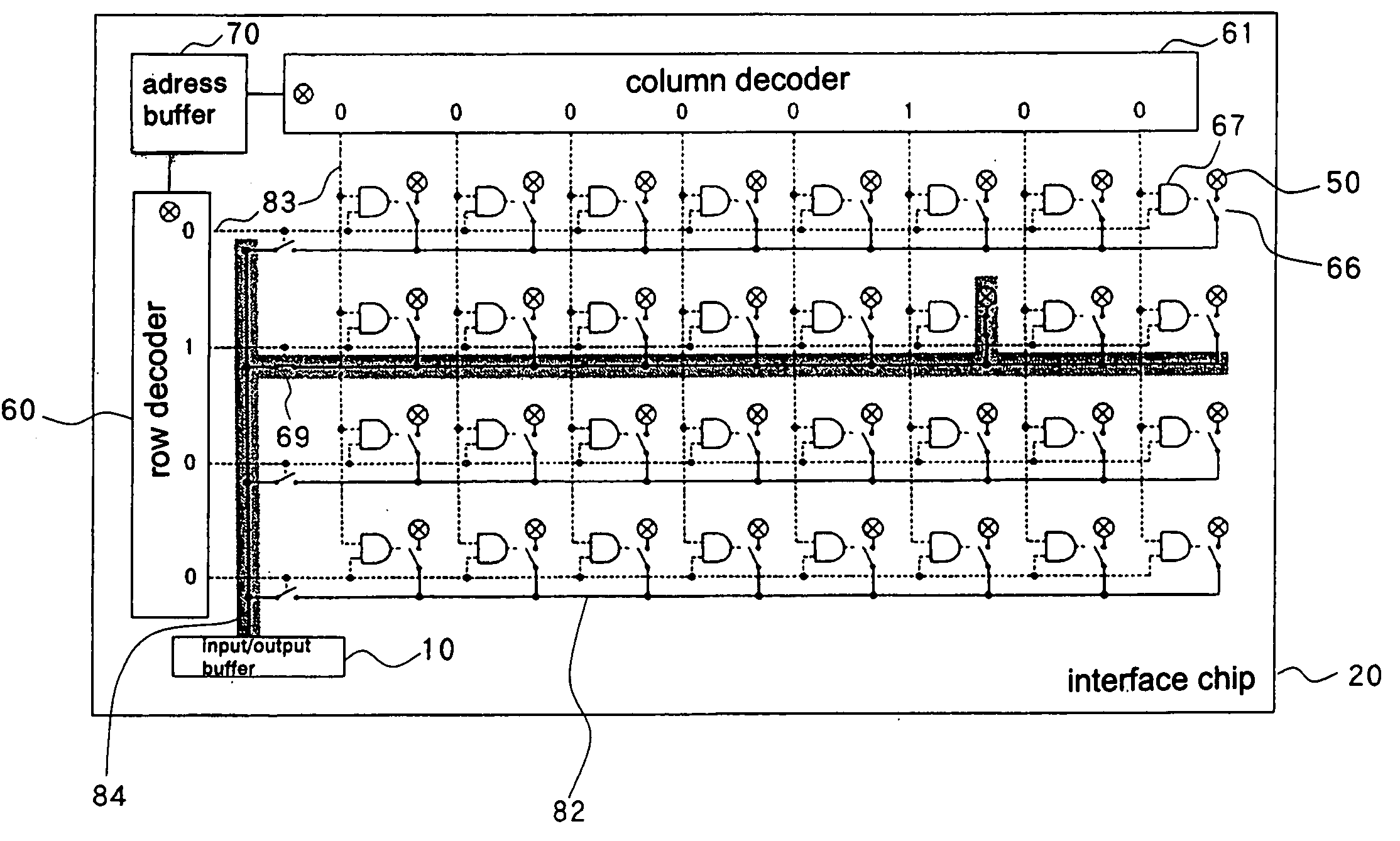

Tailored interconnect module

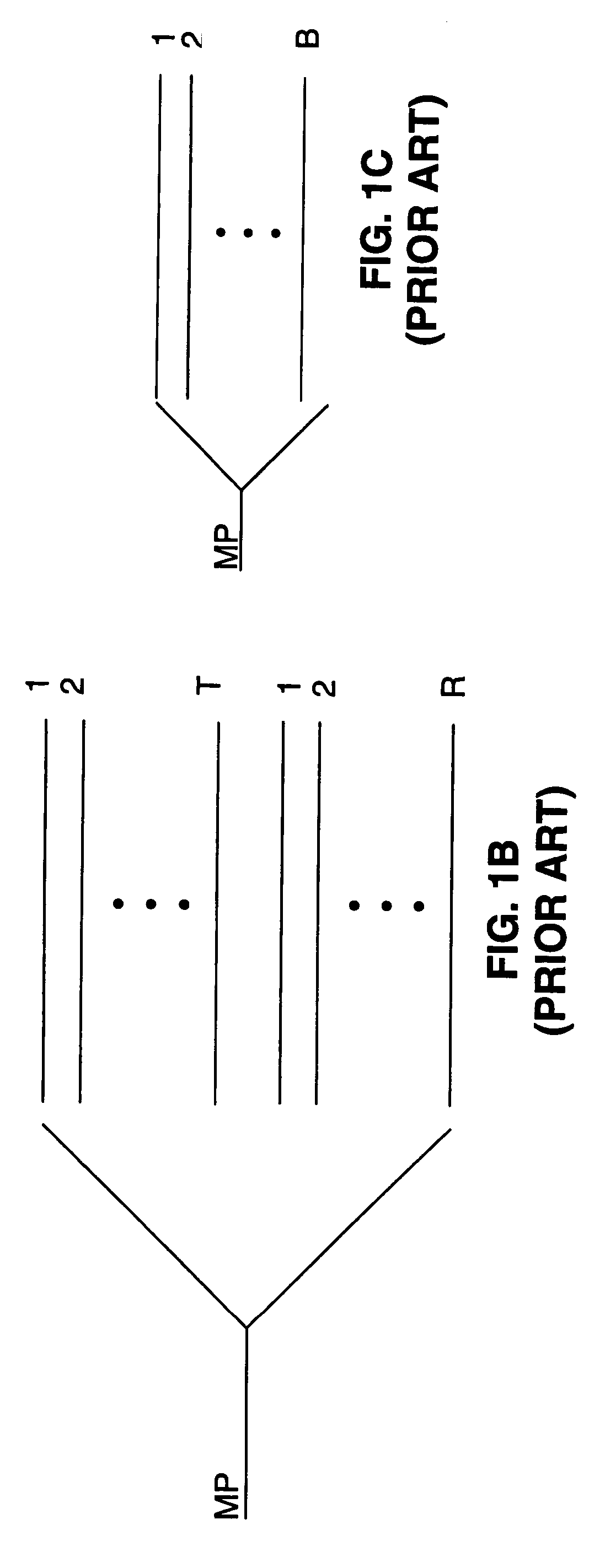

InactiveUS6908314B2Improve scalabilityMinimize the numberSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit interconnectComputer module

An integrated circuit interconnect module for reducing interconnections between integrated circuit chips MOUNTED ON a support substrate. At least one primary integrated circuit (IC) device chip and a plurality of interacting peripheral integrated chip devices. The interconnect module including a plurality of interface pins, each integrated circuit device having a plurality of interface ports. At least one interface port of which is connected to another one of said plurality of integrated circuit devices, at least one of said integrated circuit devices having an interface port connected to an interface pin whereby the majority of nodes on the interacting peripheral devices are adapted to interface with nodes of the primary IC devices in such a way as to condense the number of nets so that the total number of nodes connected to external pins is minimized.

Owner:ALCATEL LUCENT SAS

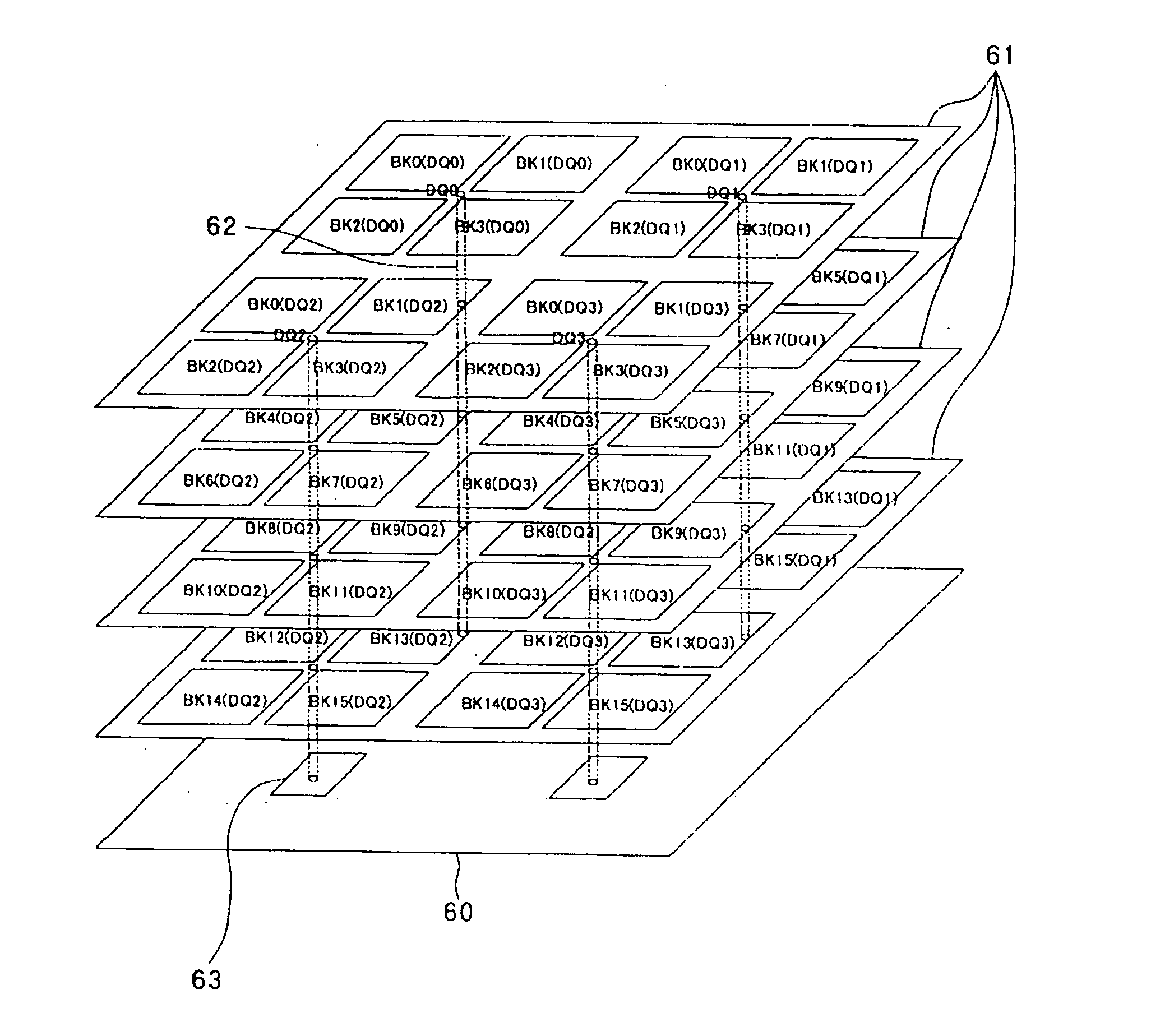

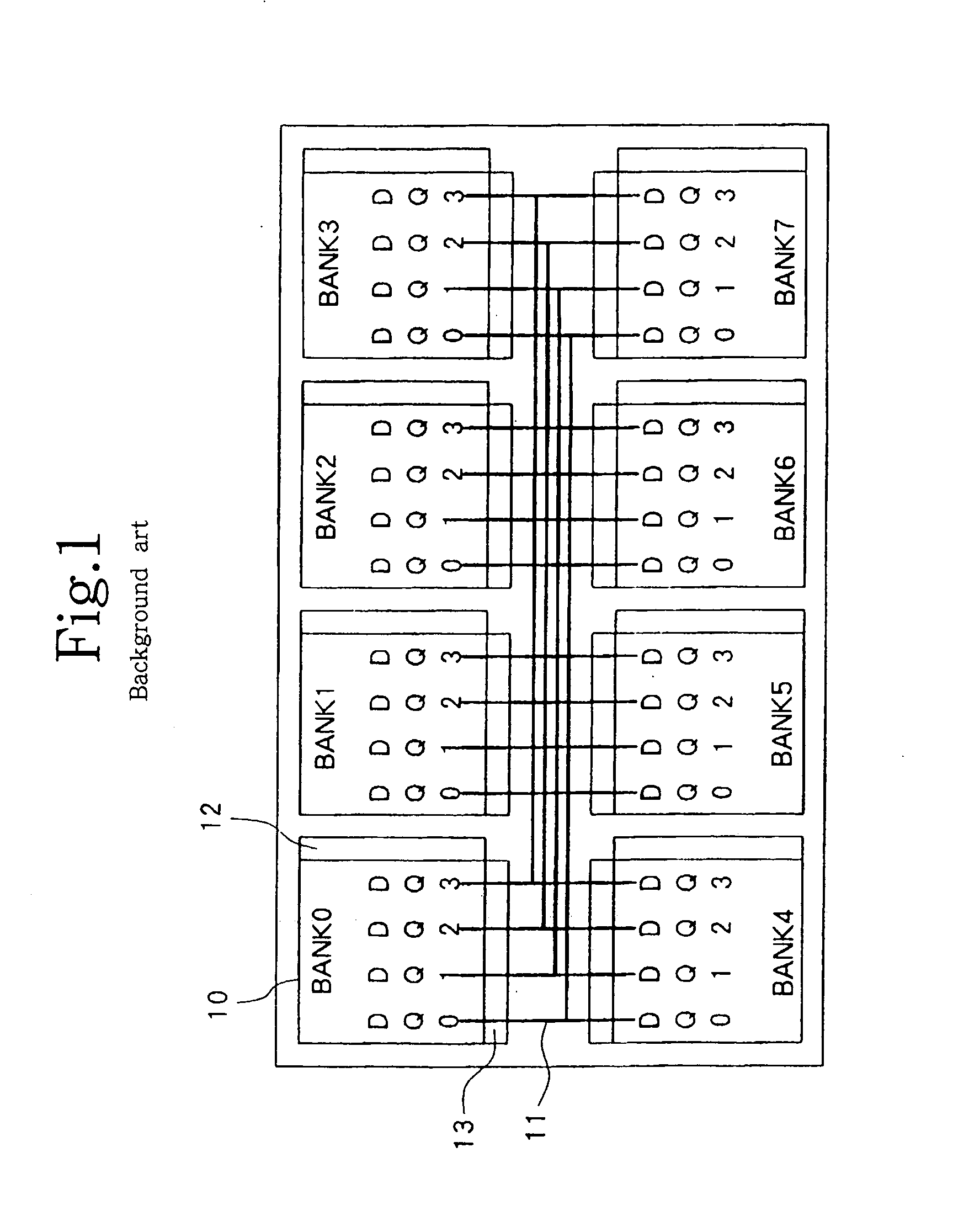

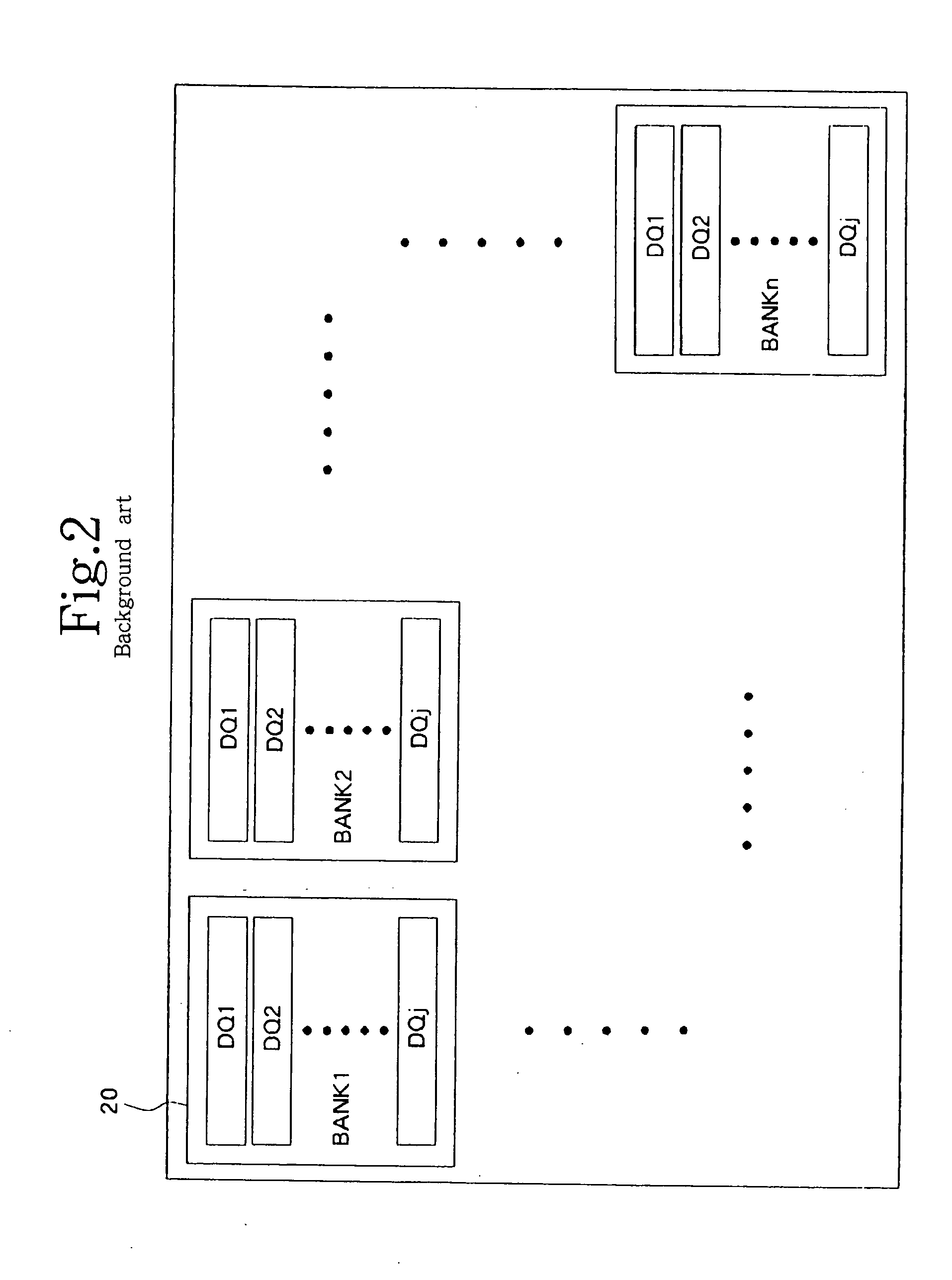

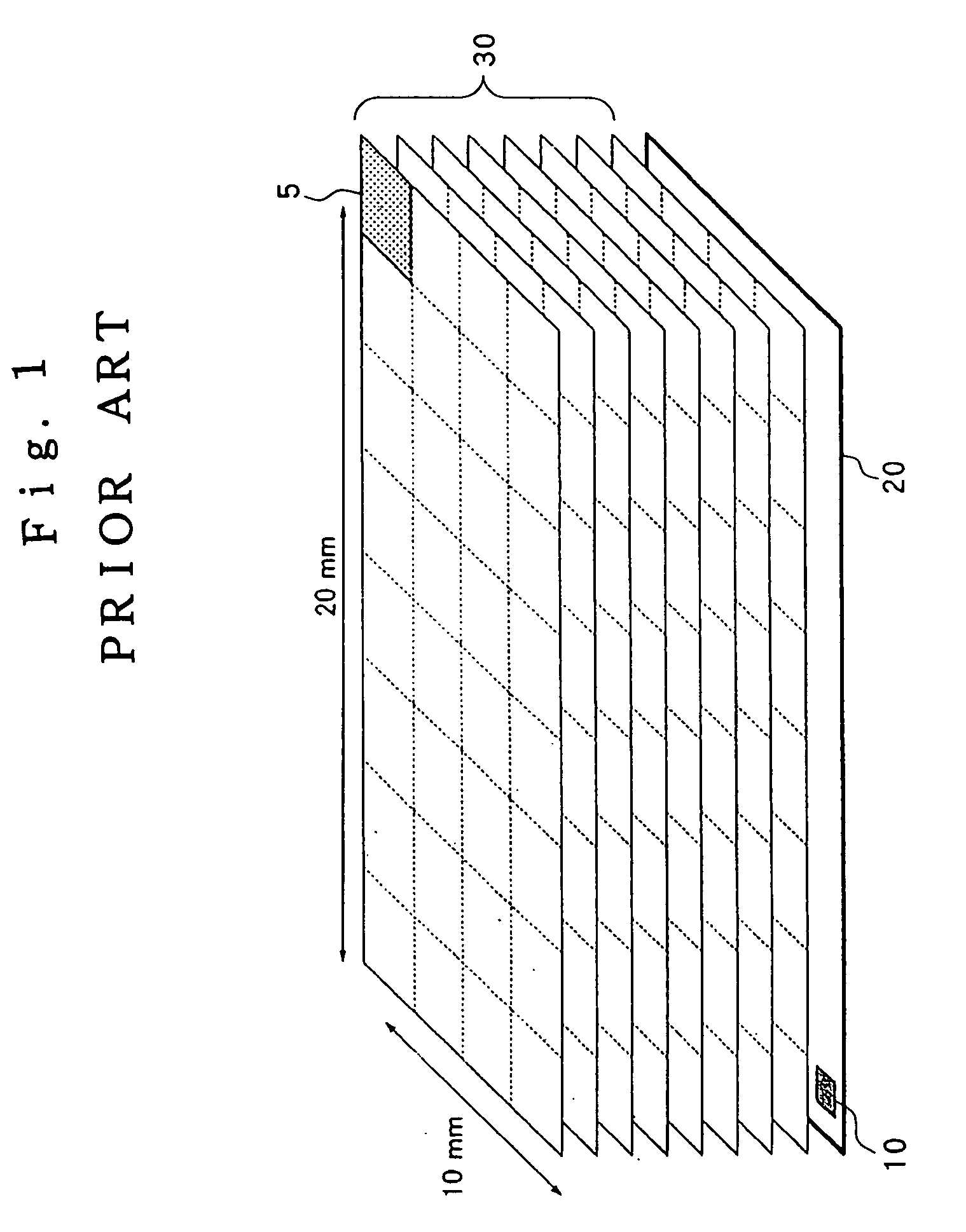

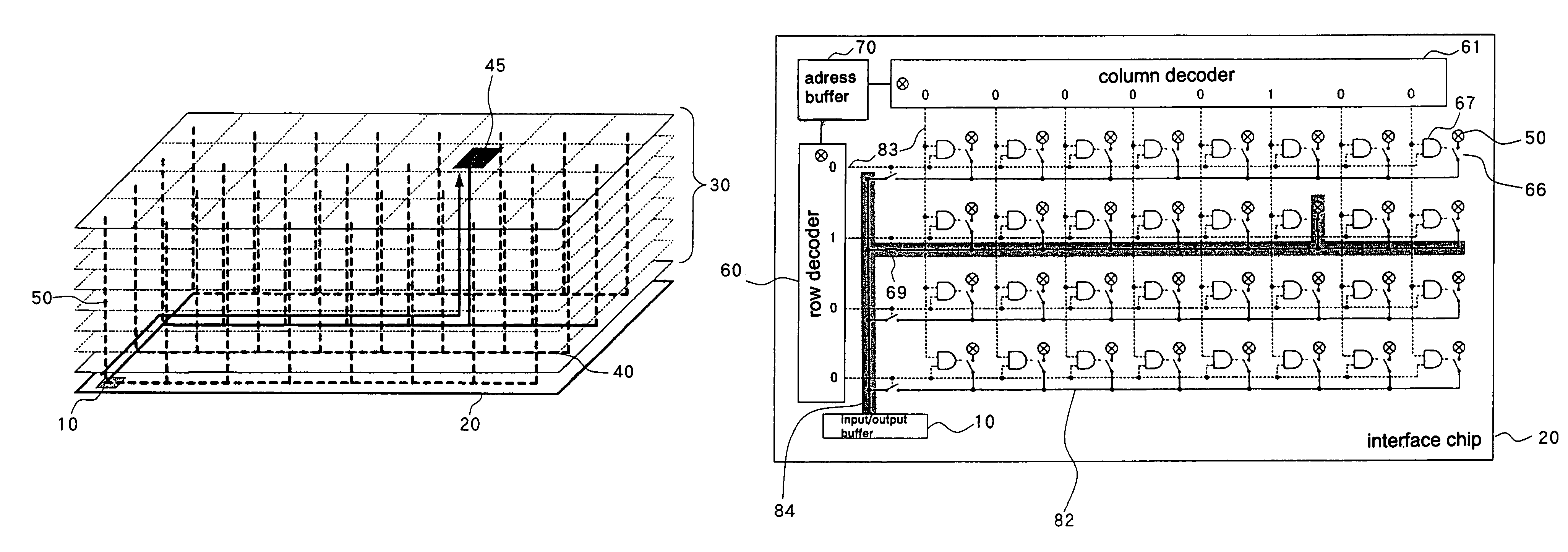

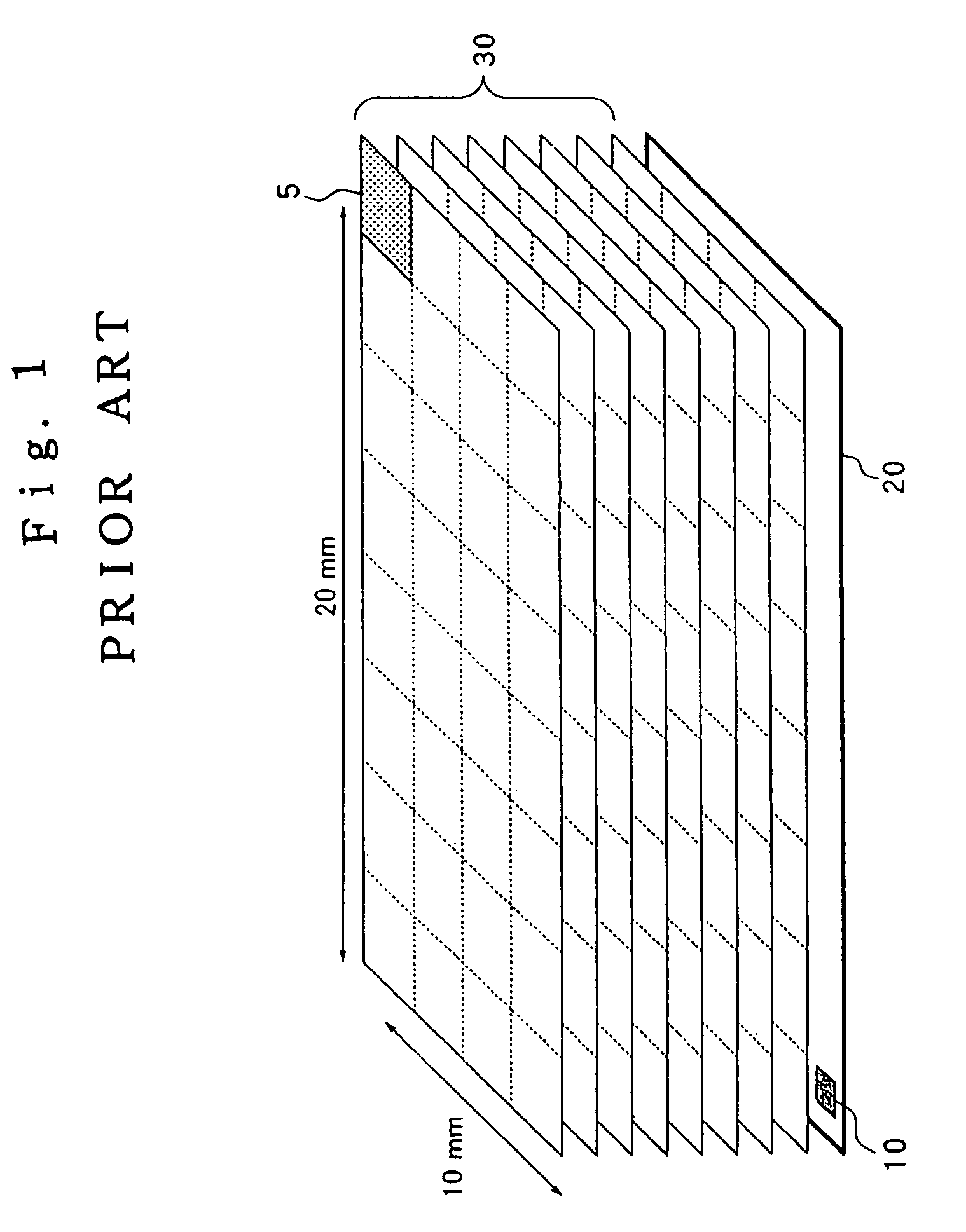

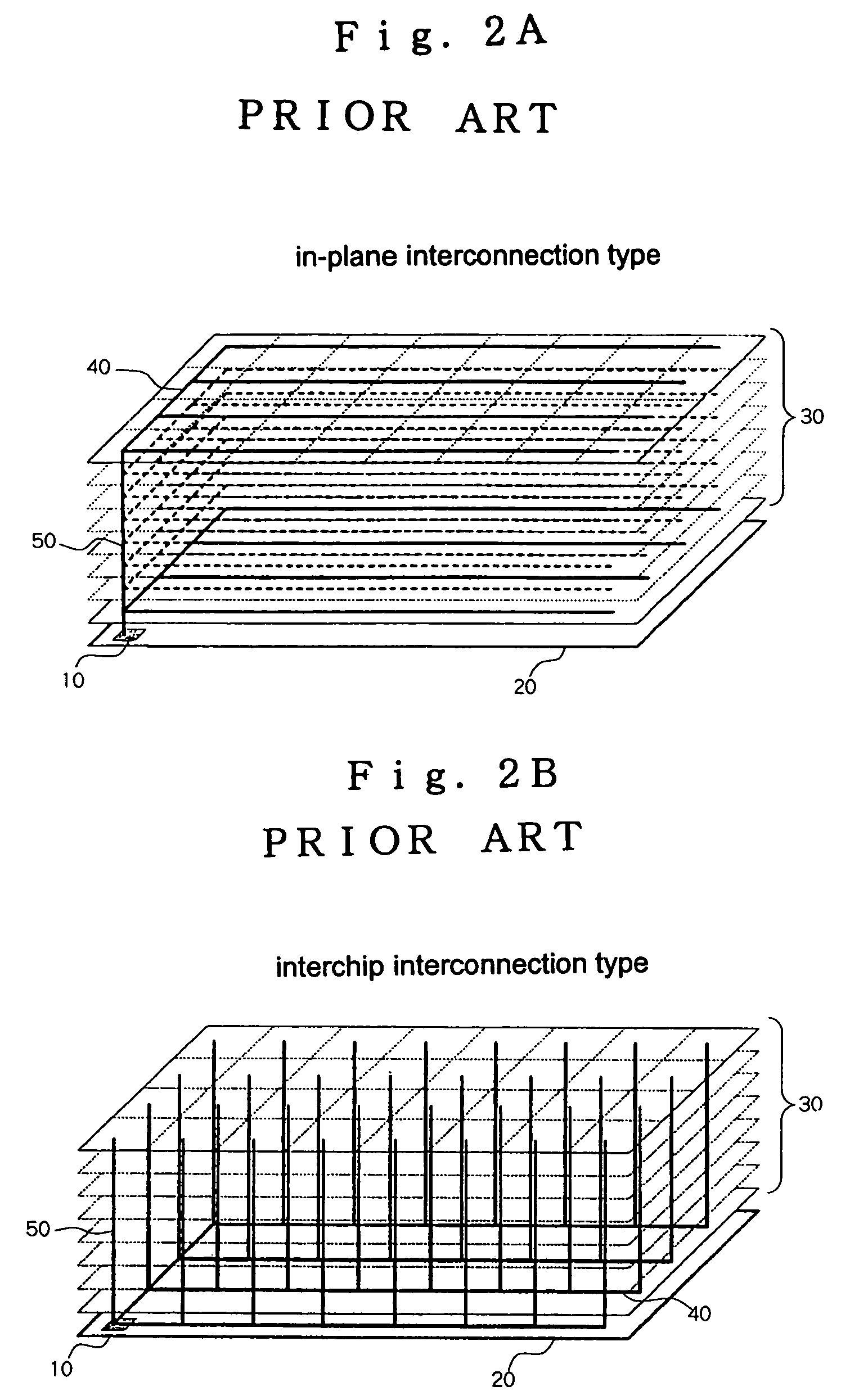

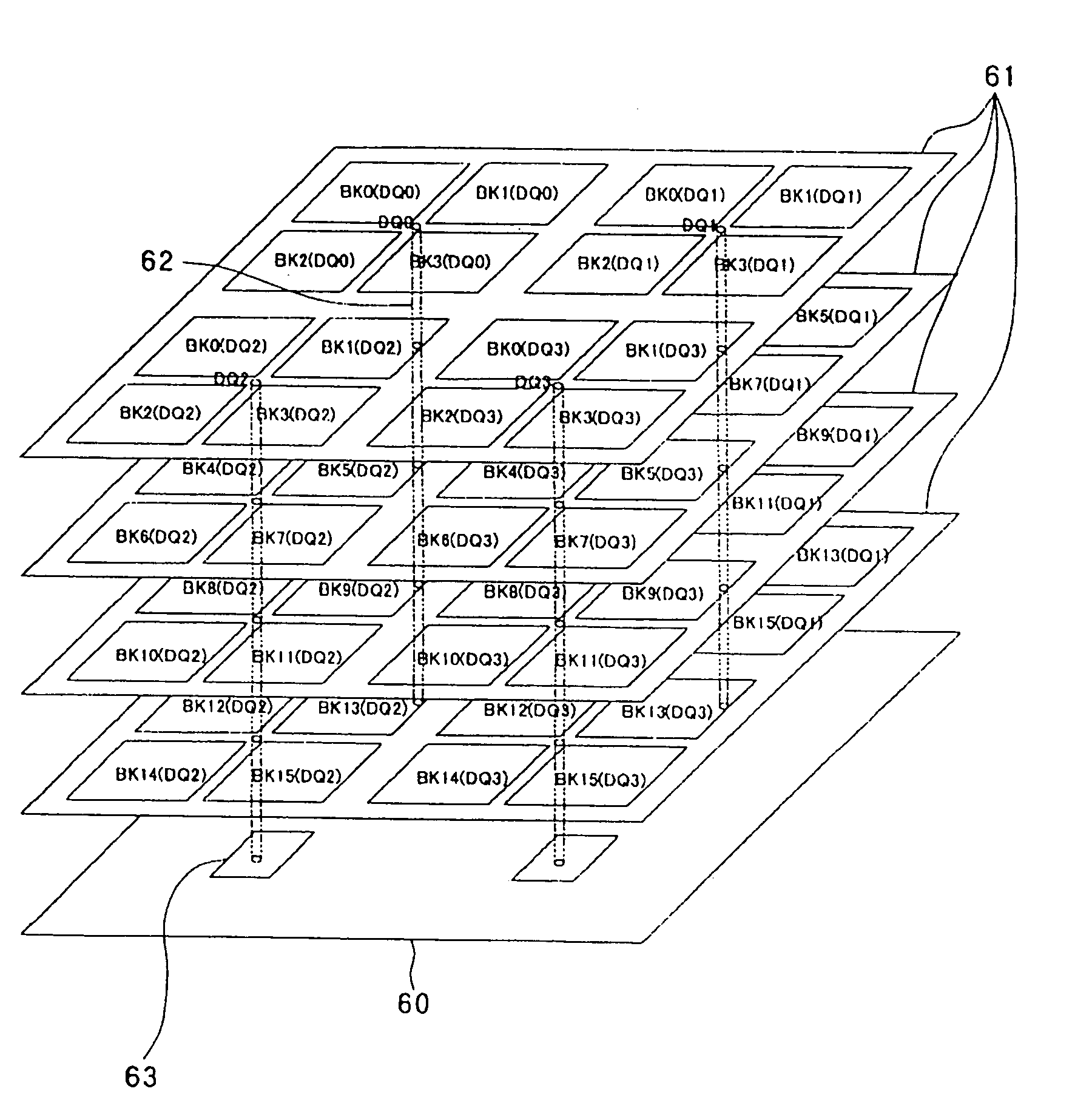

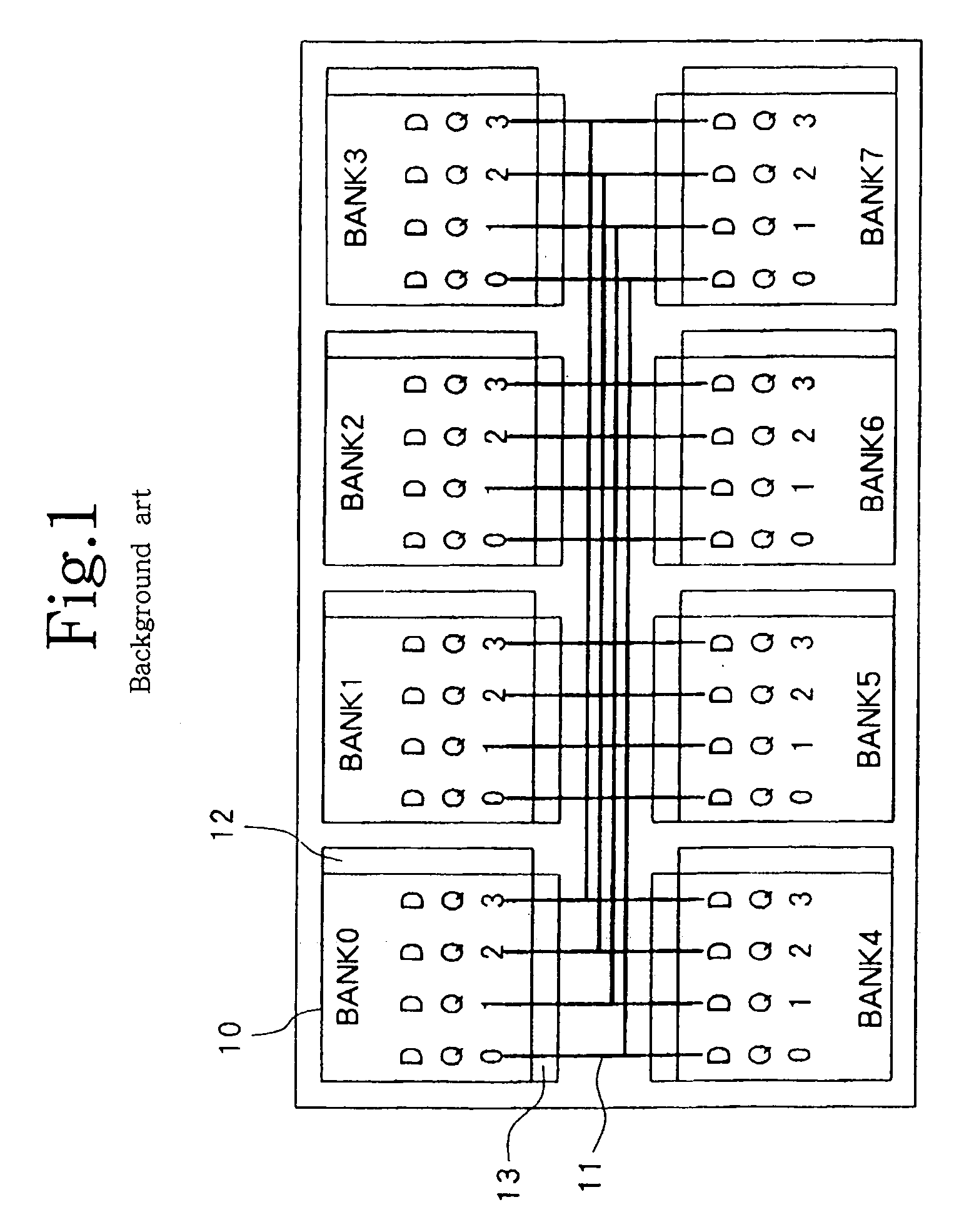

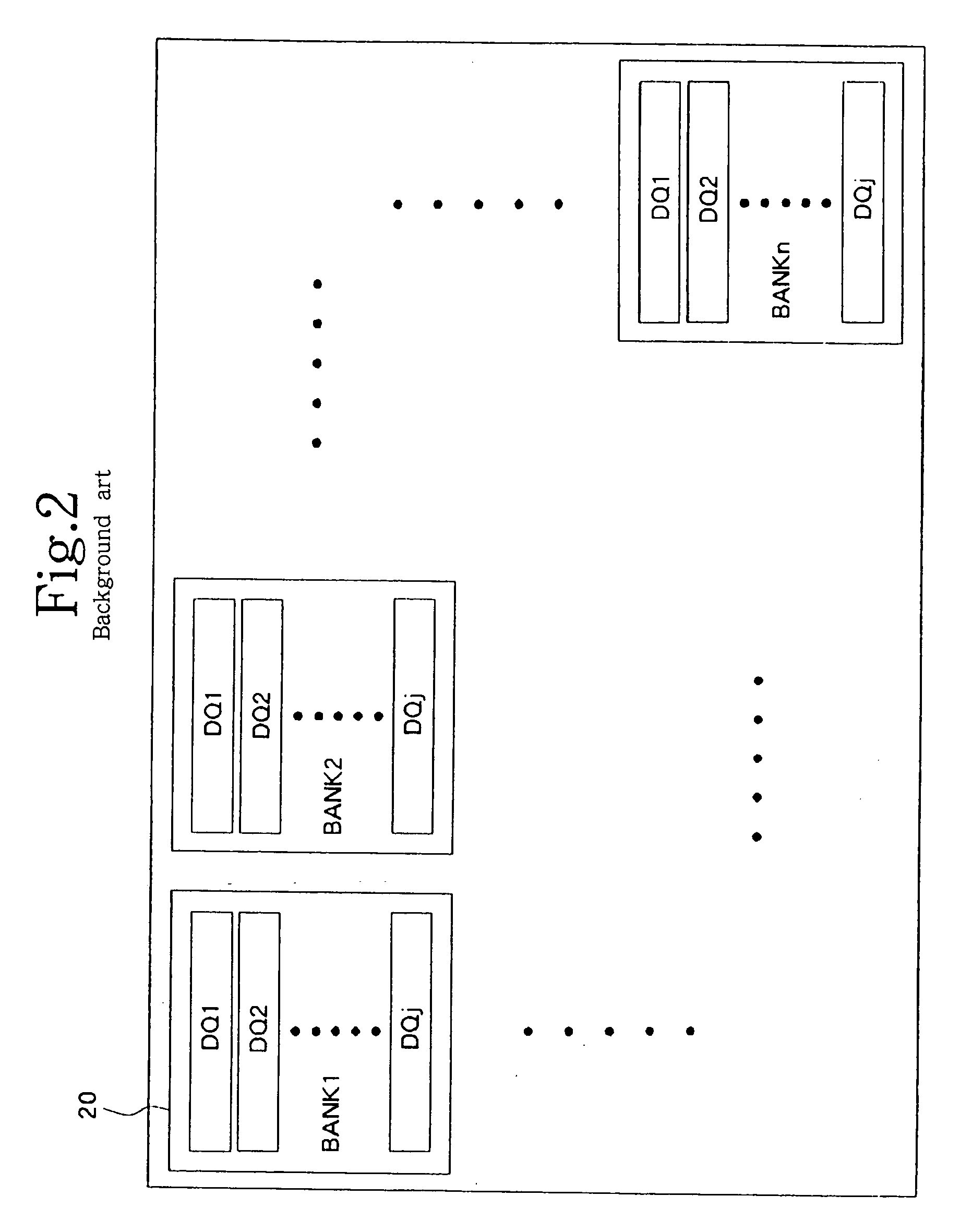

Stacked semiconductor memory device

ActiveUS20050286334A1Reducing interconnect capacitanceReduce power consumptionSemiconductor/solid-state device detailsSolid-state devicesCapacitanceSemiconductor chip

A three-dimensional semiconductor memory device having the object of decreasing the interconnection capacitance that necessitates electrical charge and discharge during data transfer and thus decreasing power consumption is provided with: a plurality of memory cell array chips, in which sub-banks that are the divisions of bank memory are organized and arranged to correspond to input / output bits, are stacked on a first semiconductor chip; and interchip interconnections for connecting the memory cell arrays such that corresponding input / output bits of the sub-banks are the same, these interchip interconnections being provided in a number corresponding to the number of input / output bits and passing through the memory cell array chips in the direction of stacking.

Owner:LONGITUDE LICENSING LTD

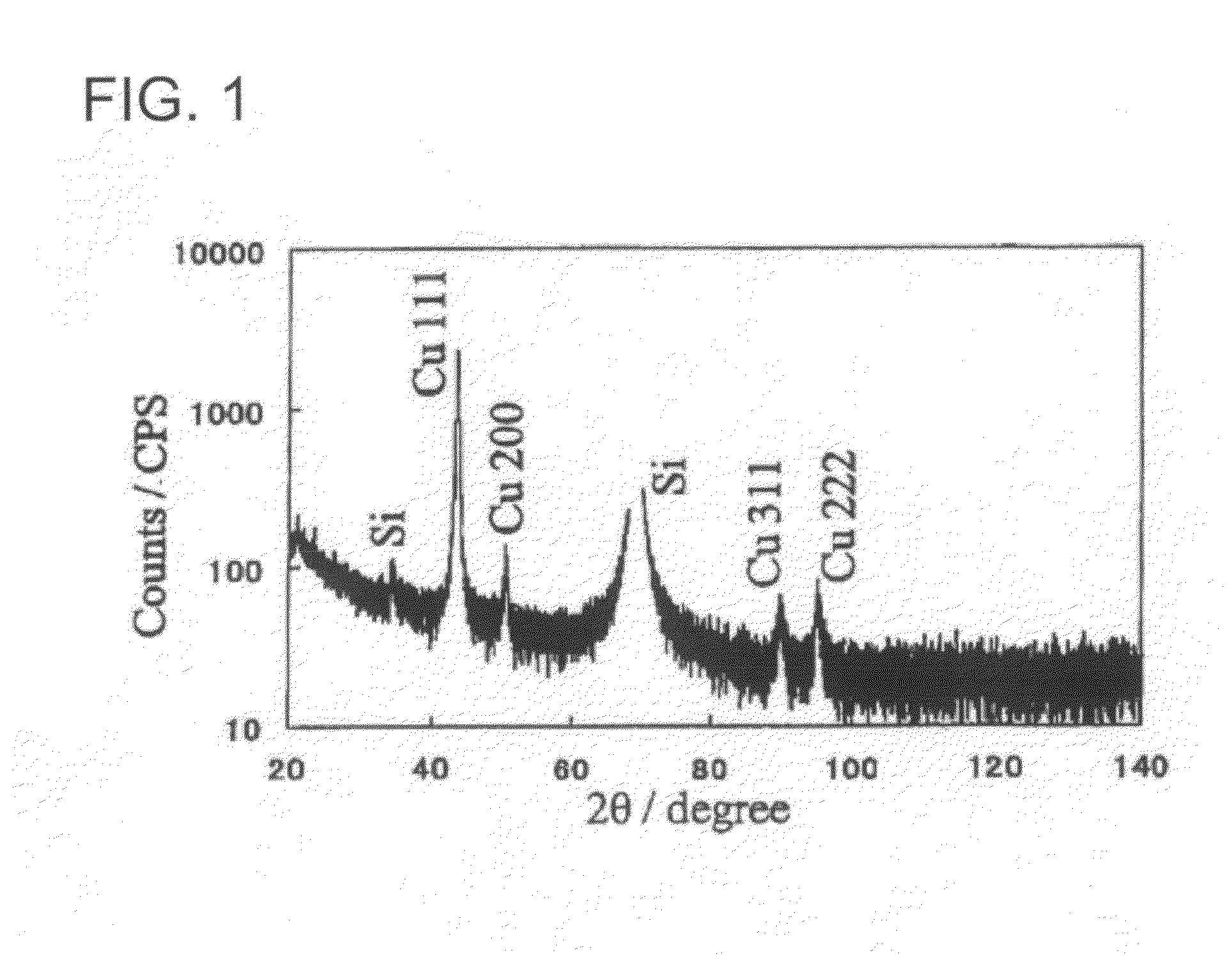

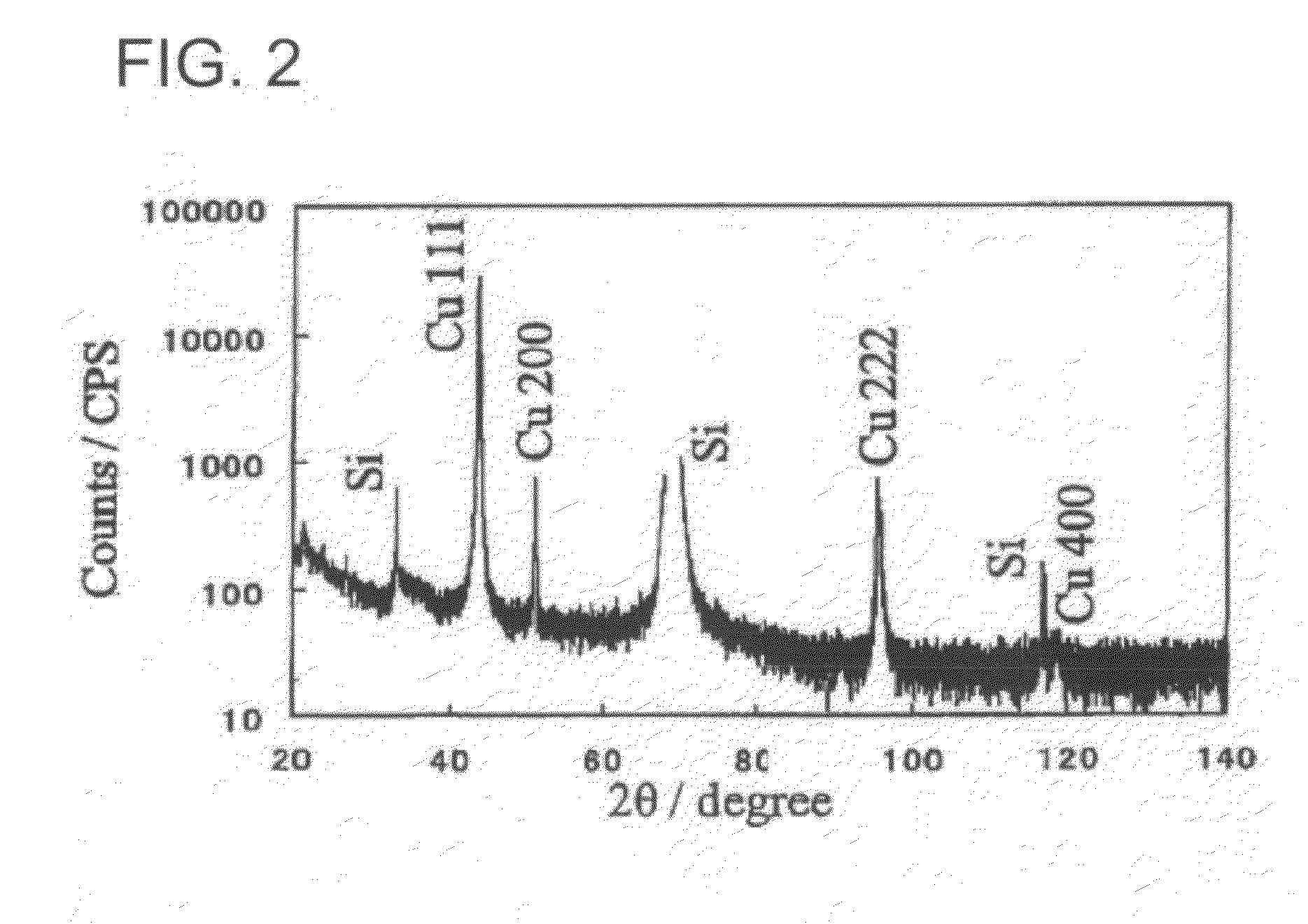

Method for forming copper interconnection structures

InactiveUS20100154213A1Reduce in quantityLower resistanceContact member manufacturingSemiconductor/solid-state device detailsOxideMetal

A method for forming a copper interconnection structure includes the steps of forming an opening in an insulating layer, forming a copper alloy layer including a metal element on an inner surface of the opening, and conducting a heat treatment on the copper alloy layer so as to form a barrier layer. An enthalpy of oxide formation for the metal element is lower than the enthalpy of oxide formation for copper. The heat treatment is conducted at temperatures ranging from 327° C. to 427° C. and for a time period ranging from 1 minute to 80 minutes.

Owner:ADVANCED INTERCONNECT MATERIAL

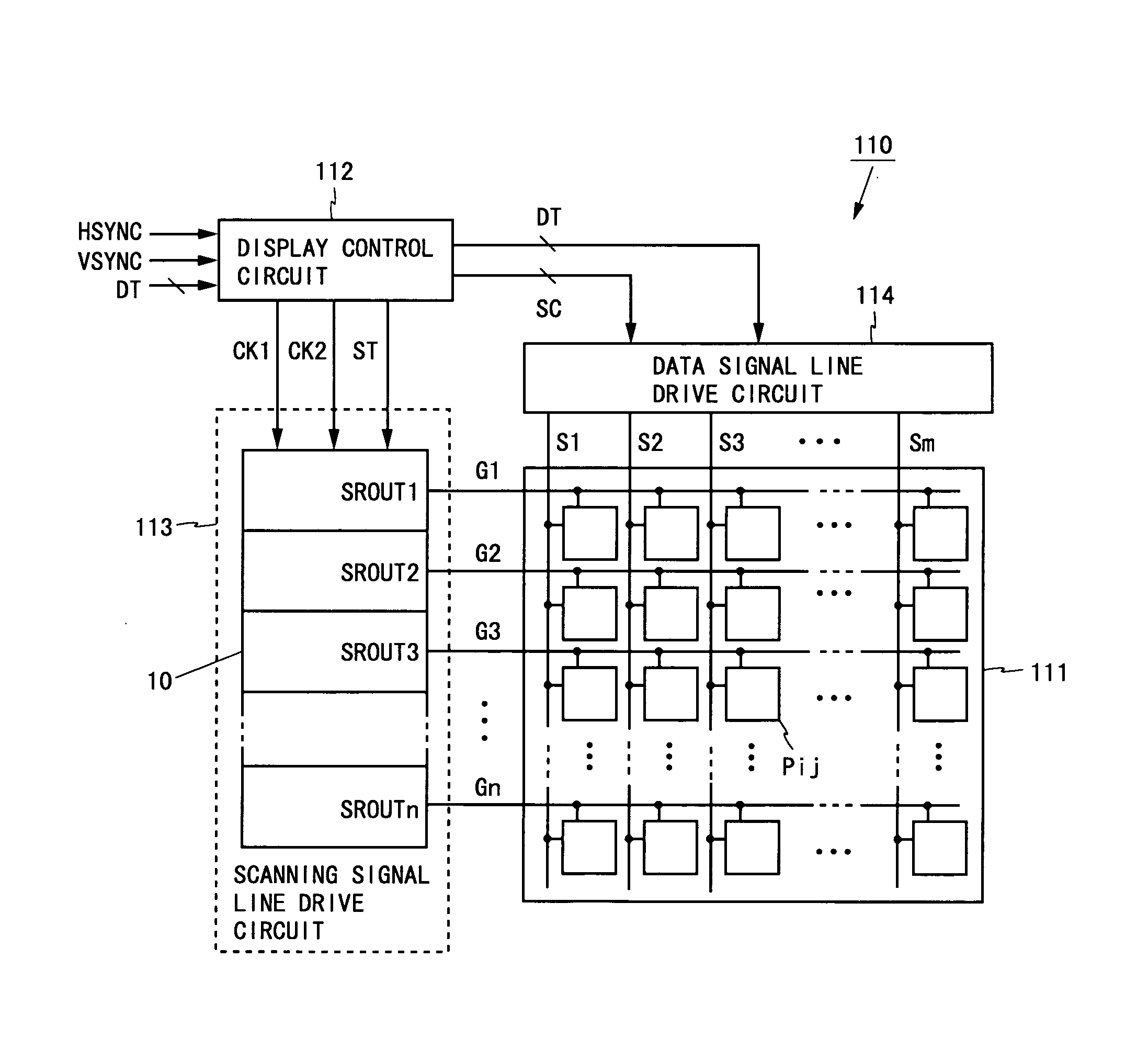

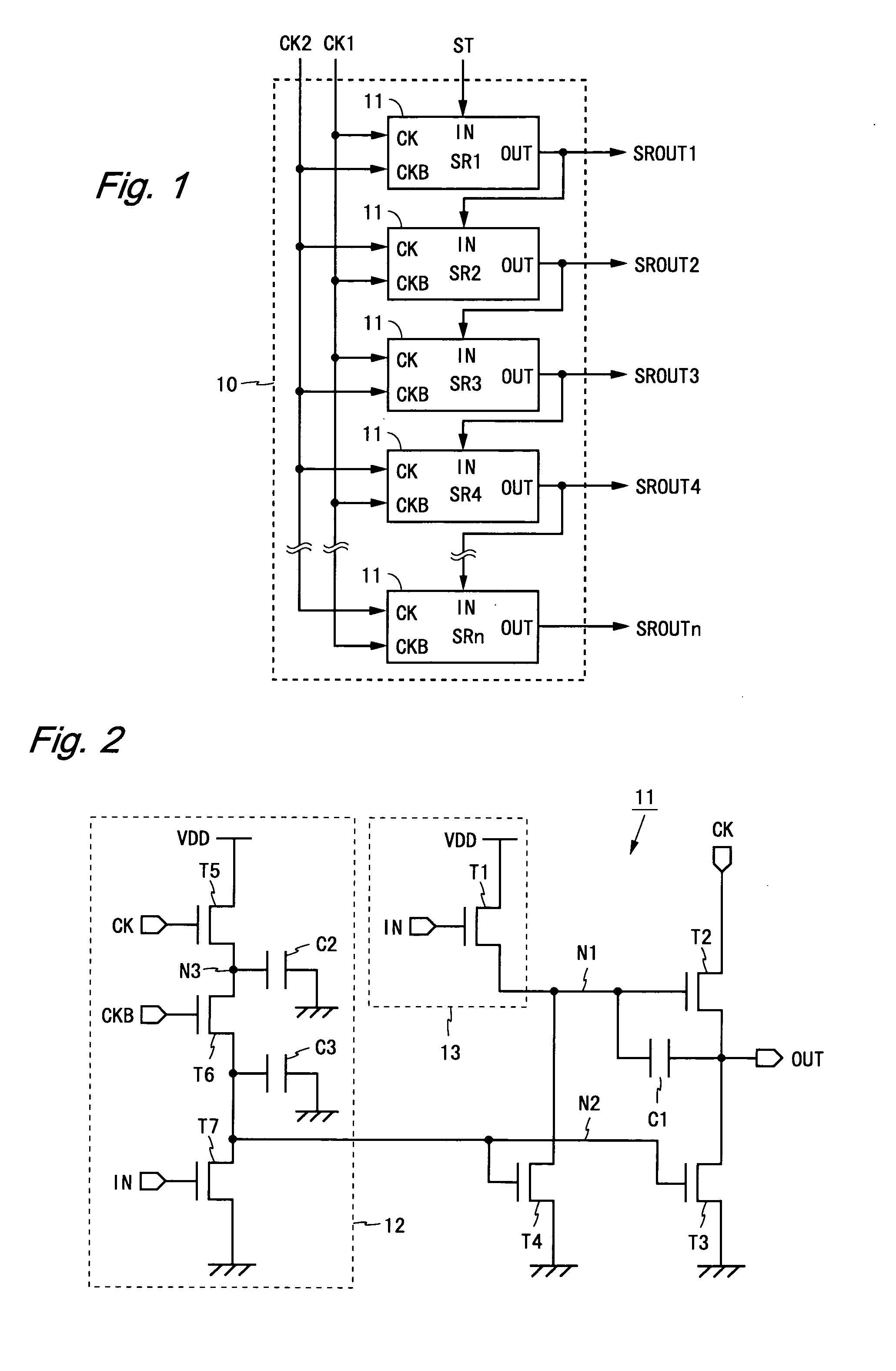

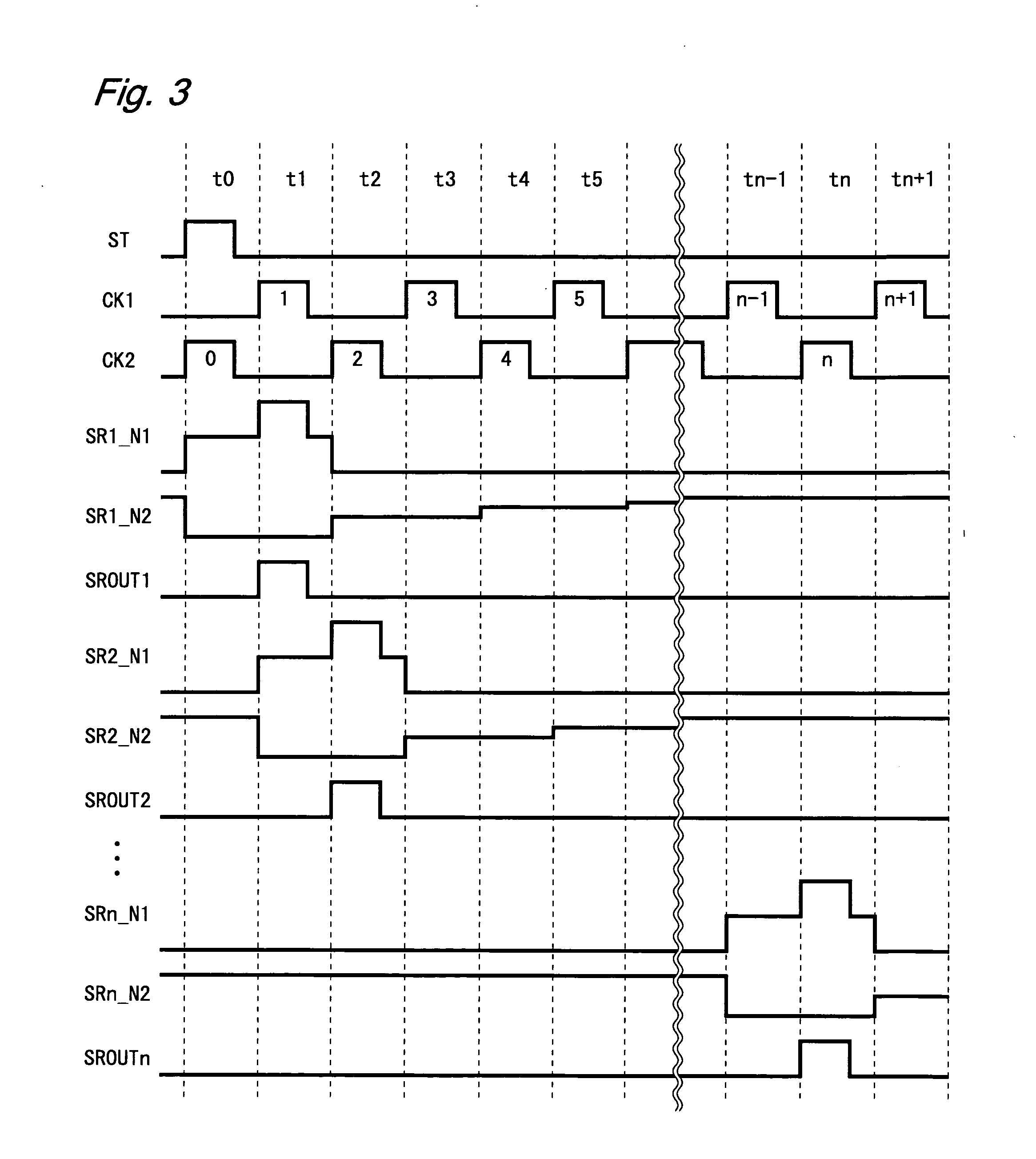

Shift register

ActiveUS20100141642A1Reduce interconnectionReduce layout areaCathode-ray tube indicatorsDigital storageShift registerElectricity

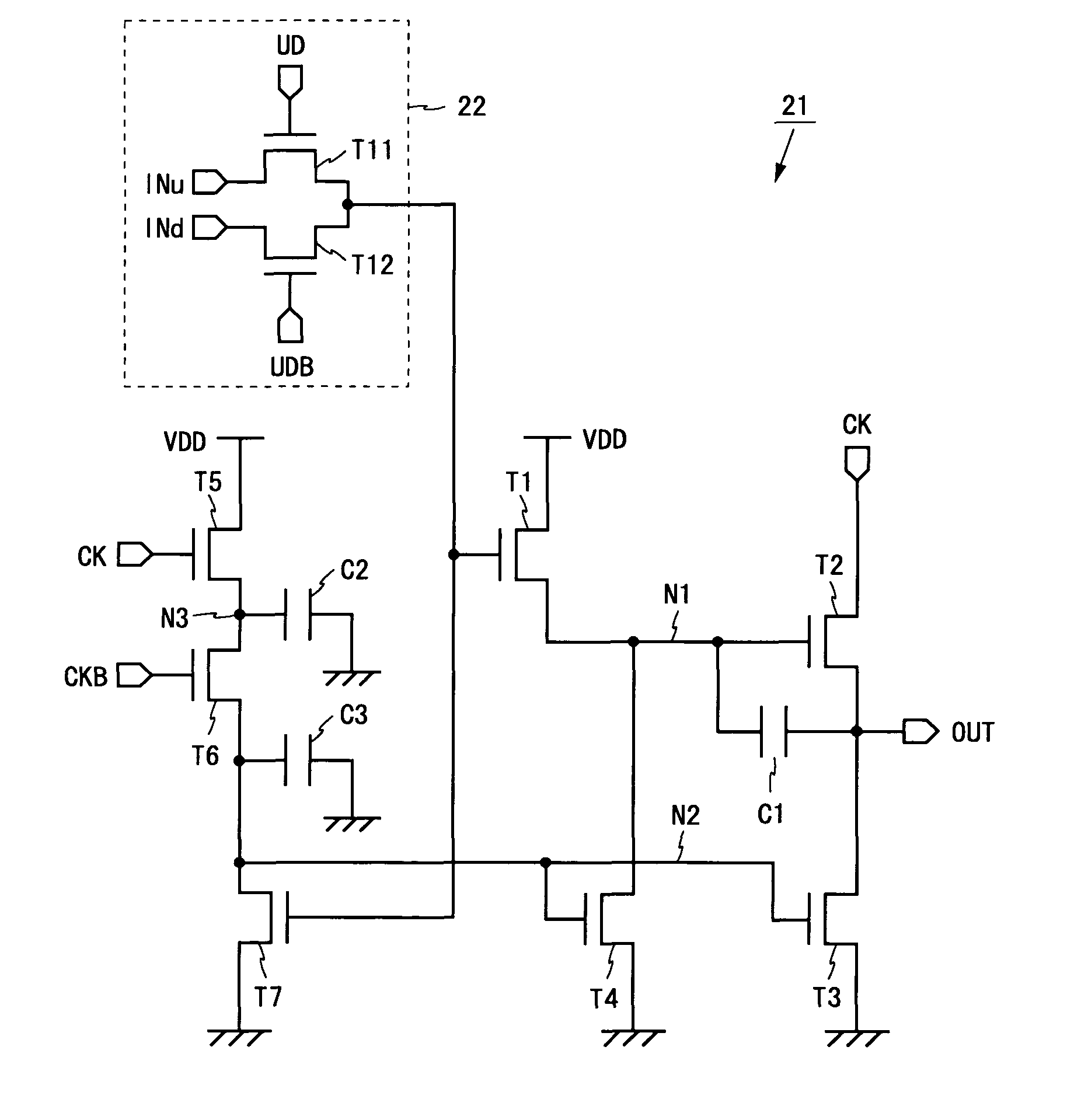

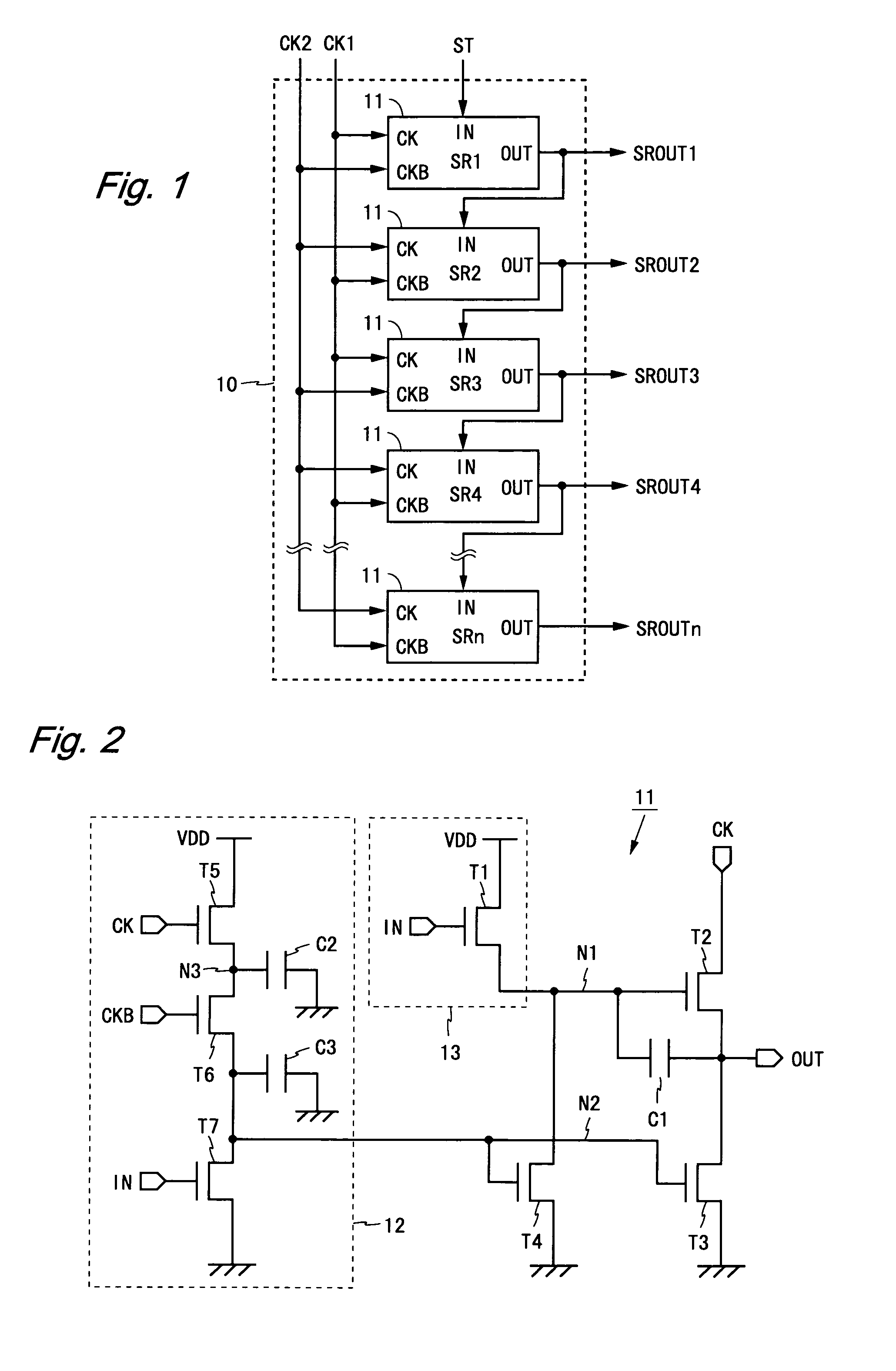

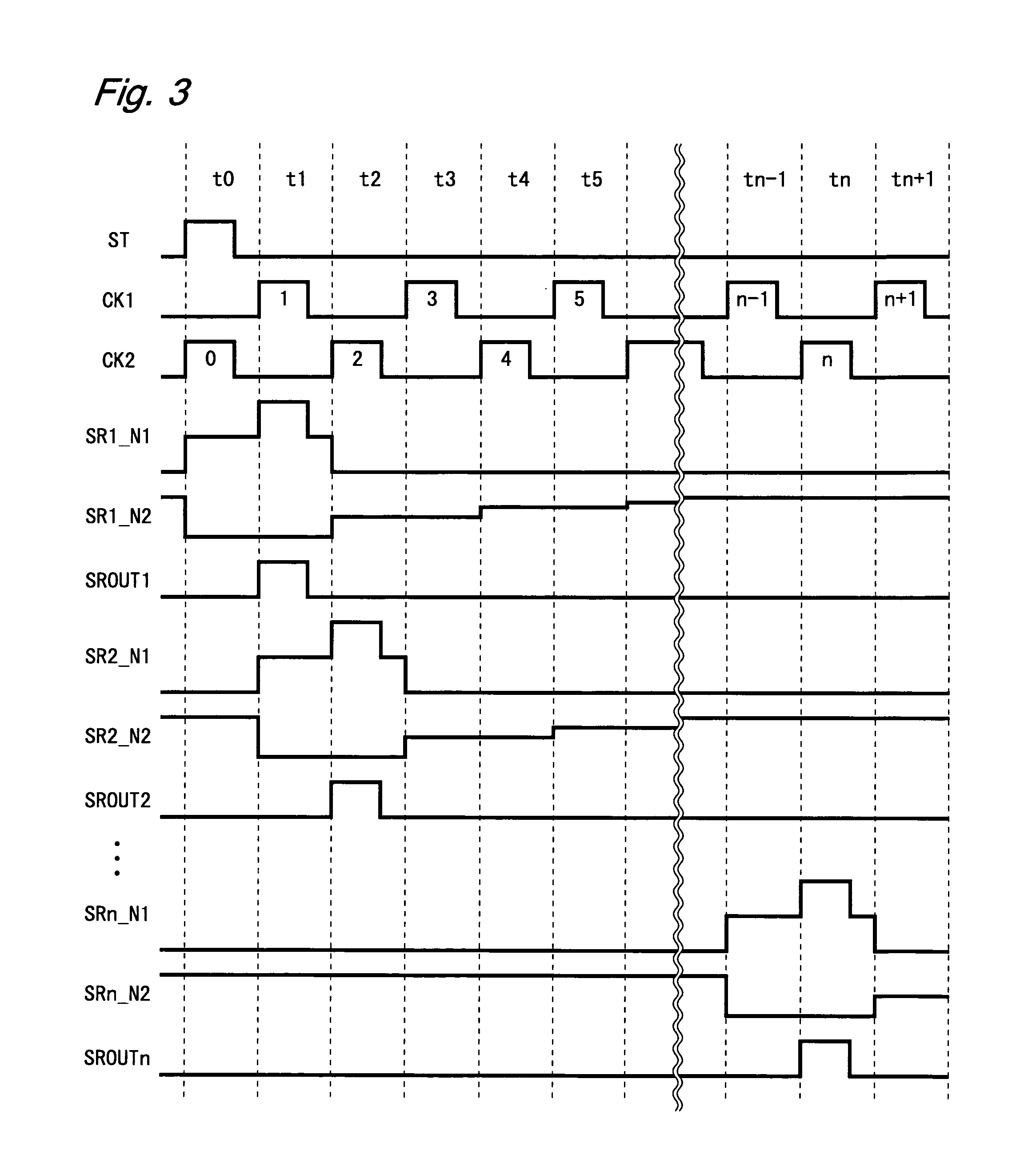

In one embodiment of the present invention, a unit circuit of a shift register includes a bootstrap circuit configured with a transistor T1, a transistor T2 and a capacitor, a transistor T3, a transistor T4, and a reset signal generation circuit. By use of two-phase clock signals whose high level periods do not overlap with each other, the reset signal generation circuit generates a reset signal which is at a high level in a normal state and changes to a low level when an input signal turns into the high level. During a period that the reset signal is at the high level, transistors perform discharge of a node and pull-down of an output signal. Thus, it is possible to obtain a shift register which performs discharge of a node and pull-down of an output signal and achieves a small area and low power consumption without using an output signal from a subsequent circuit.

Owner:SHARP KK

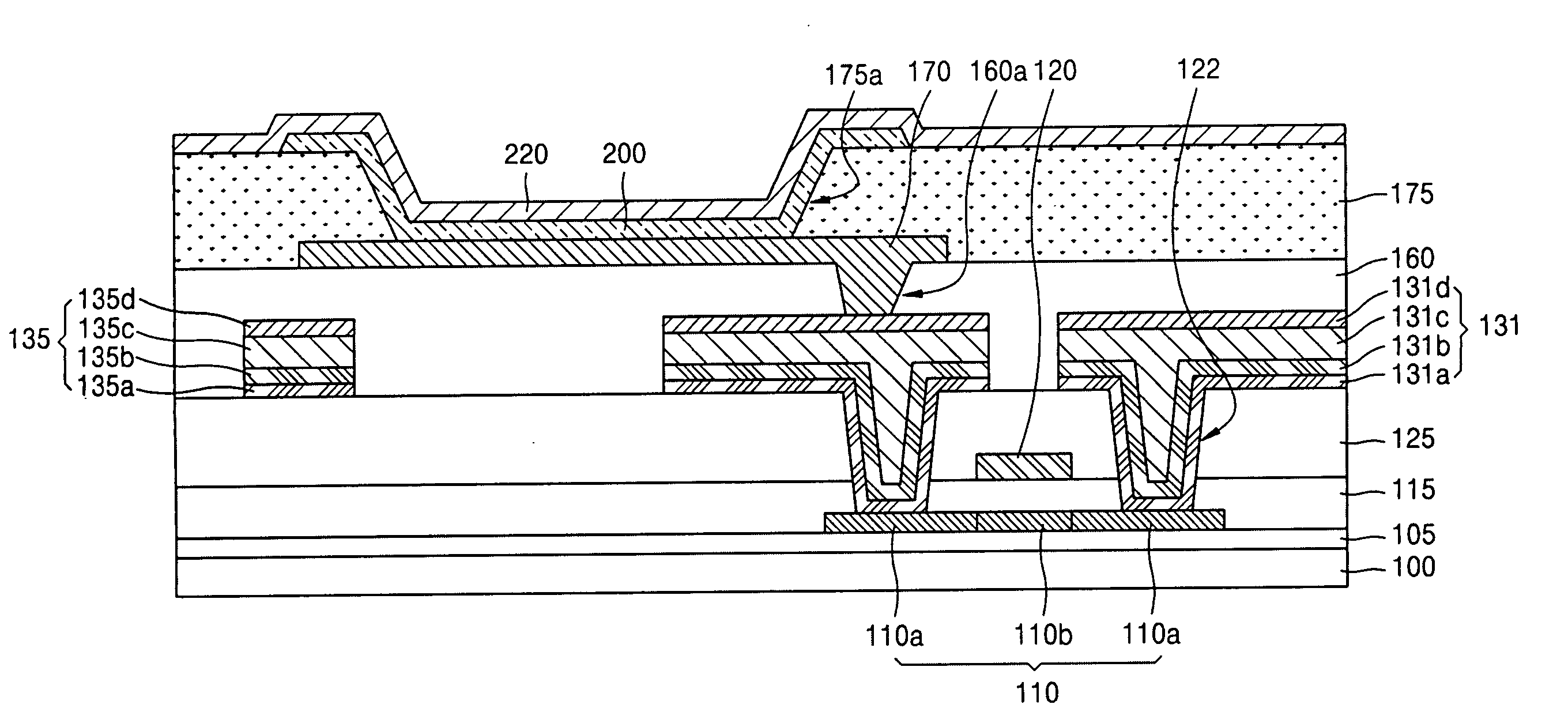

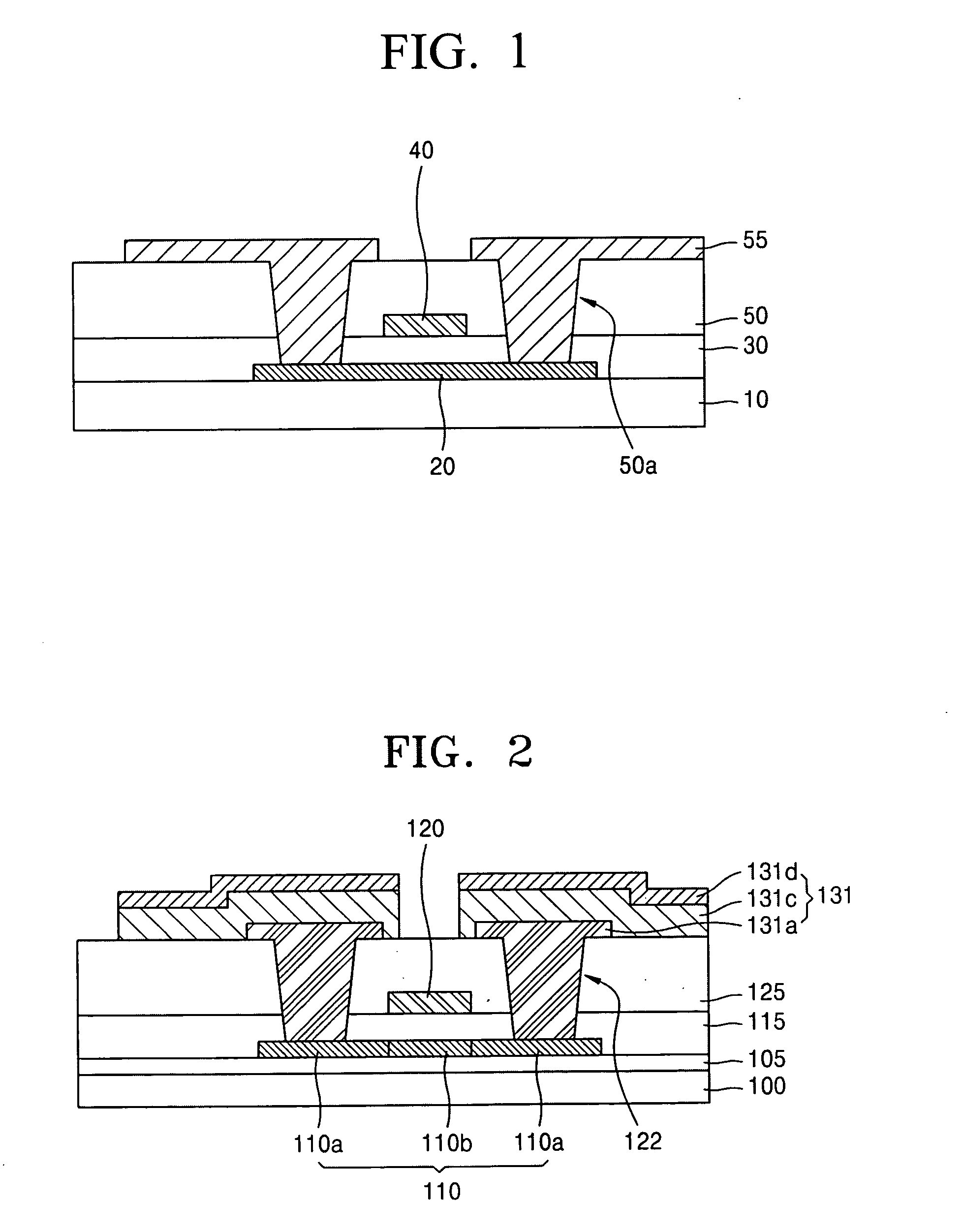

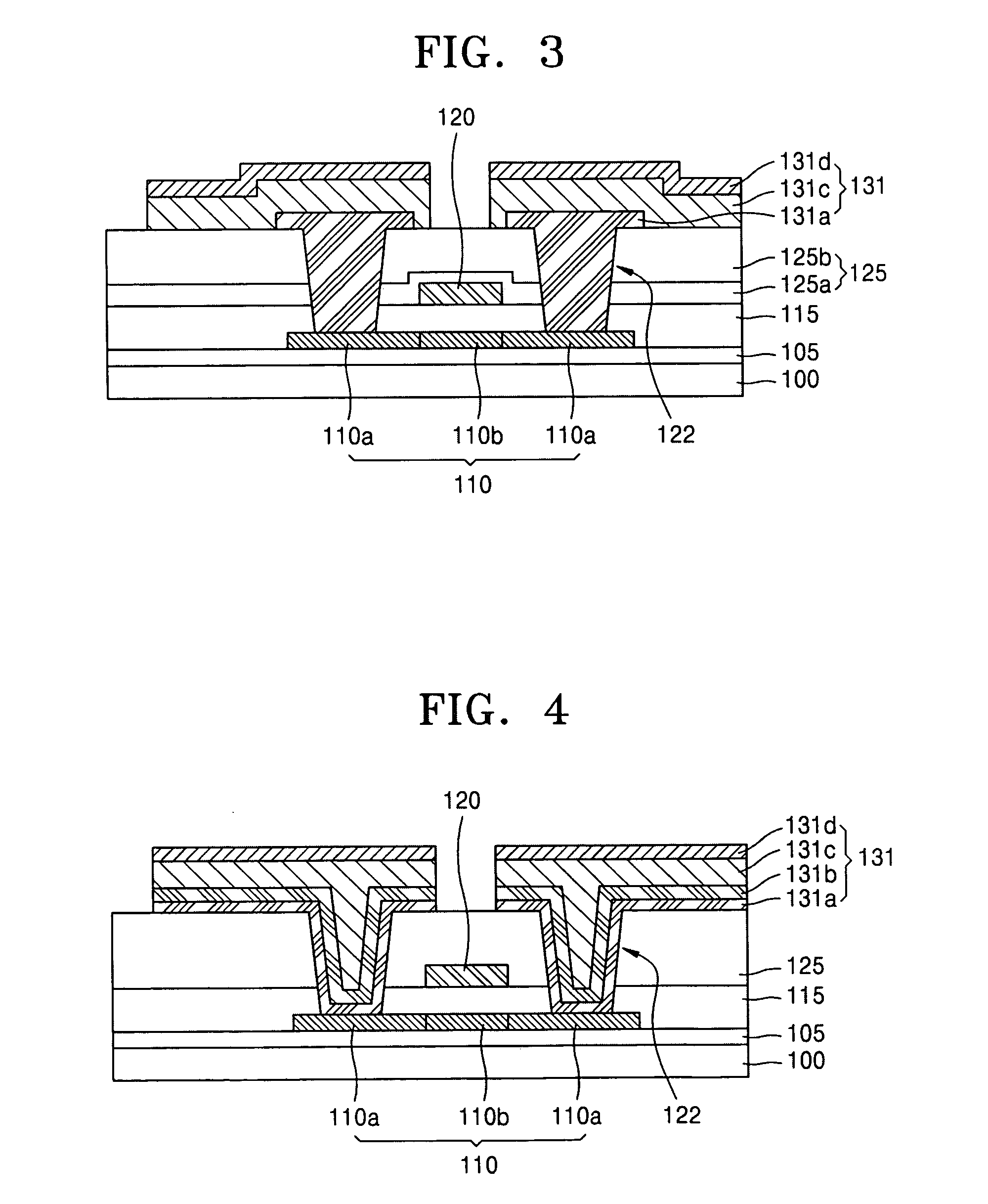

Thin film transistor (TFT) and flat panel display including the TFT and their methods of manufacture

InactiveUS20060001091A1Reduce resistanceSmooth supplySolid-state devicesSemiconductor/solid-state device manufacturingHydrogenDisplay device

A Thin Film Transistor (TFT) reduces interconnection resistance of source / drain electrodes, prevents contamination from an active layer, reduces contact resistance between a pixel electrode and the source / drain electrodes, smoothly supplies hydrogen to the active layer and has high mobility, on-current characteristics, and threshold voltage characteristics The TFT includes an active layer having a channel region and source / drain regions, a gate electrode supplying a signal to the channel region, source / drain electrodes respectively connected to the source / drain regions and including at least one of Ti, a Ti alloy, Ta, and a Ta alloy; and an insulating layer interposed between the source / drain electrodes and the active layer and including silicon nitride.

Owner:SAMSUNG SDI CO LTD

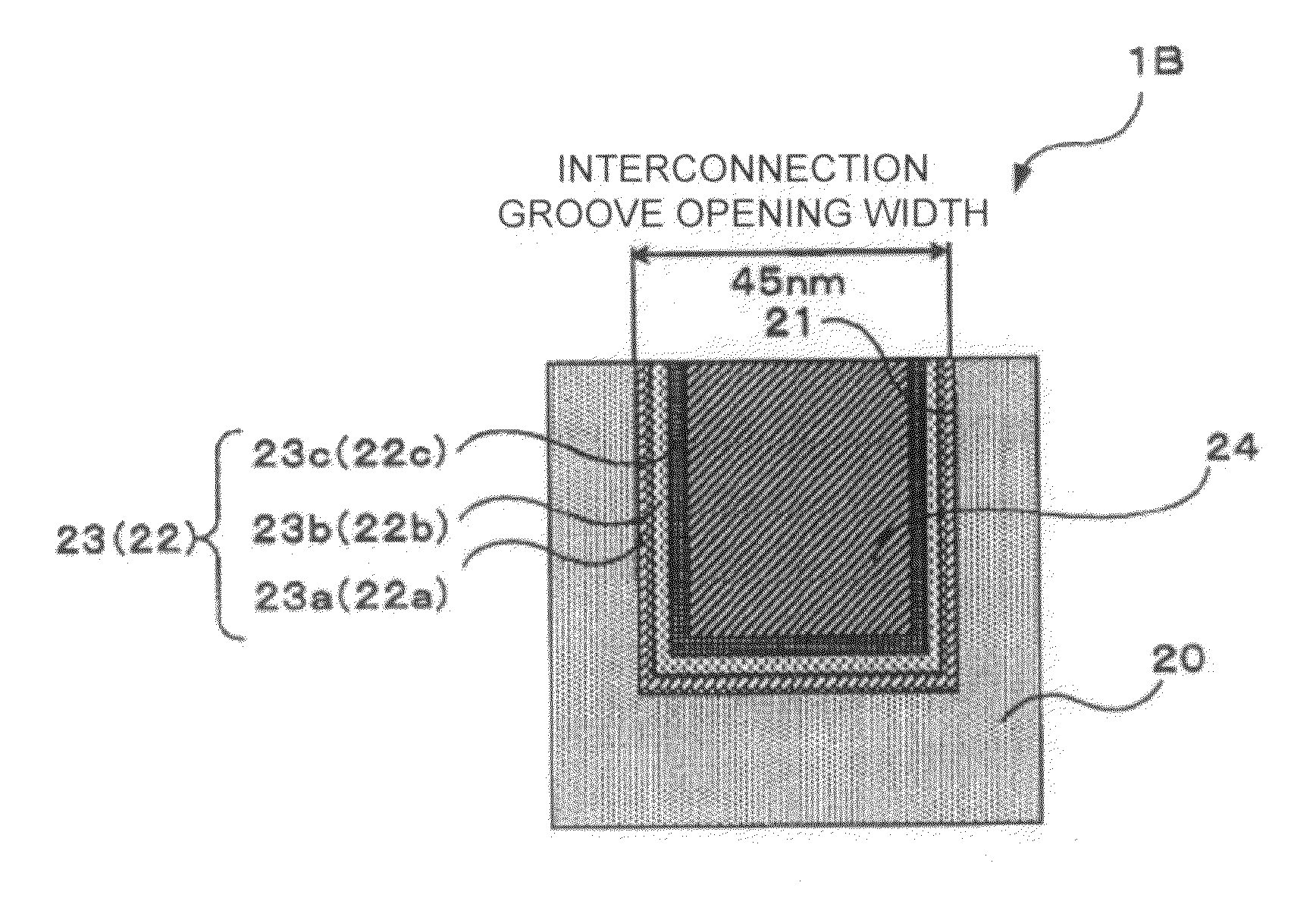

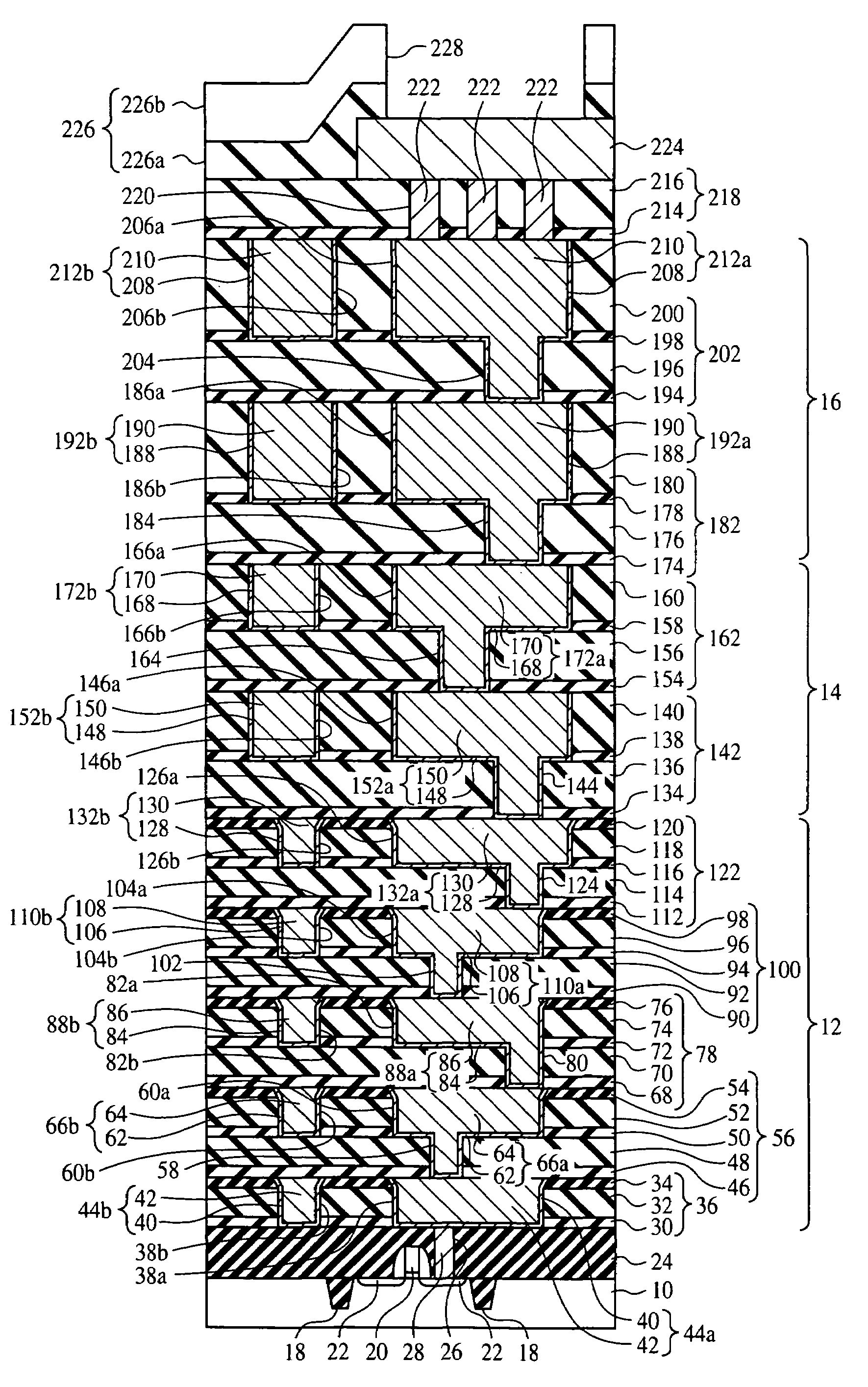

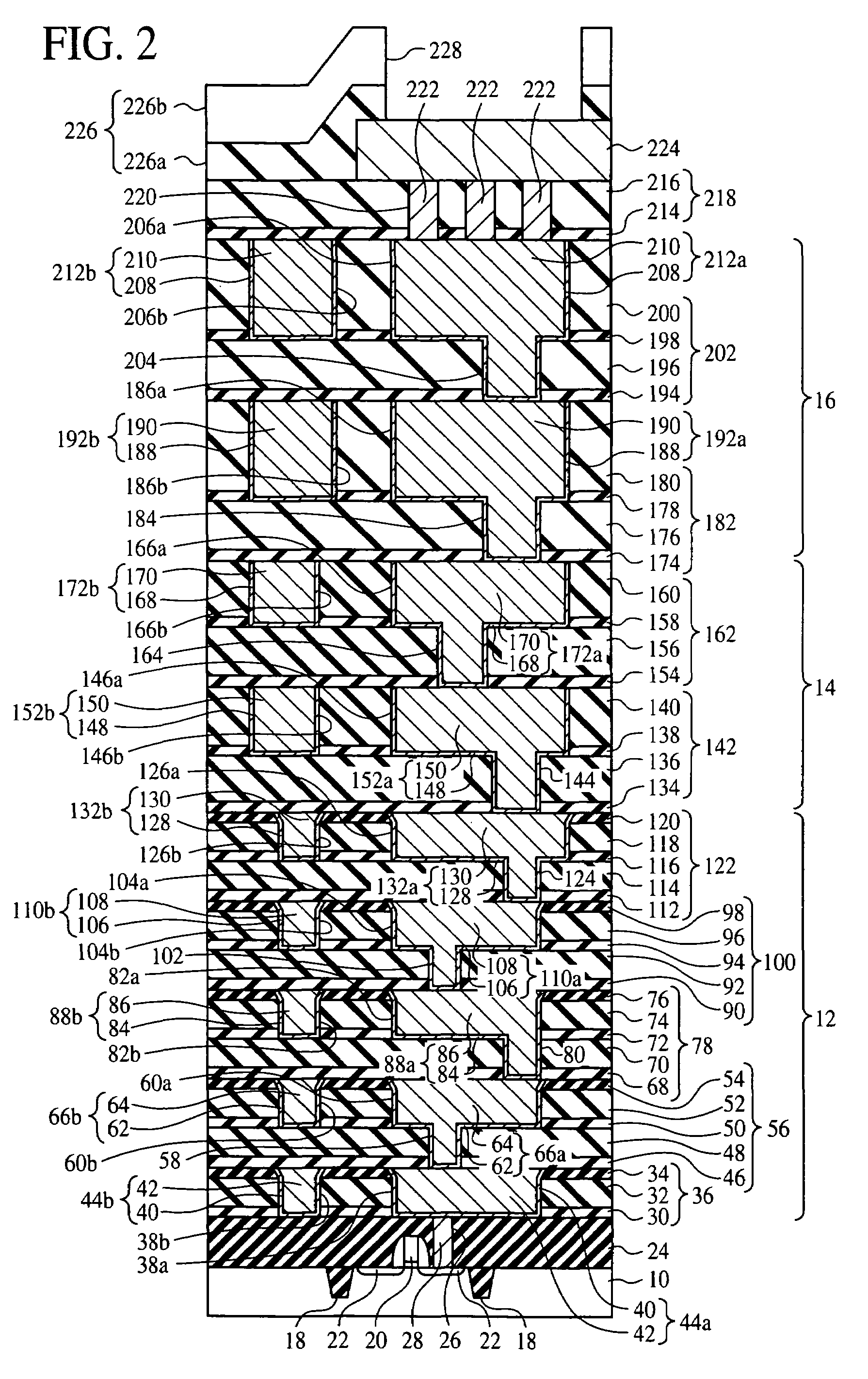

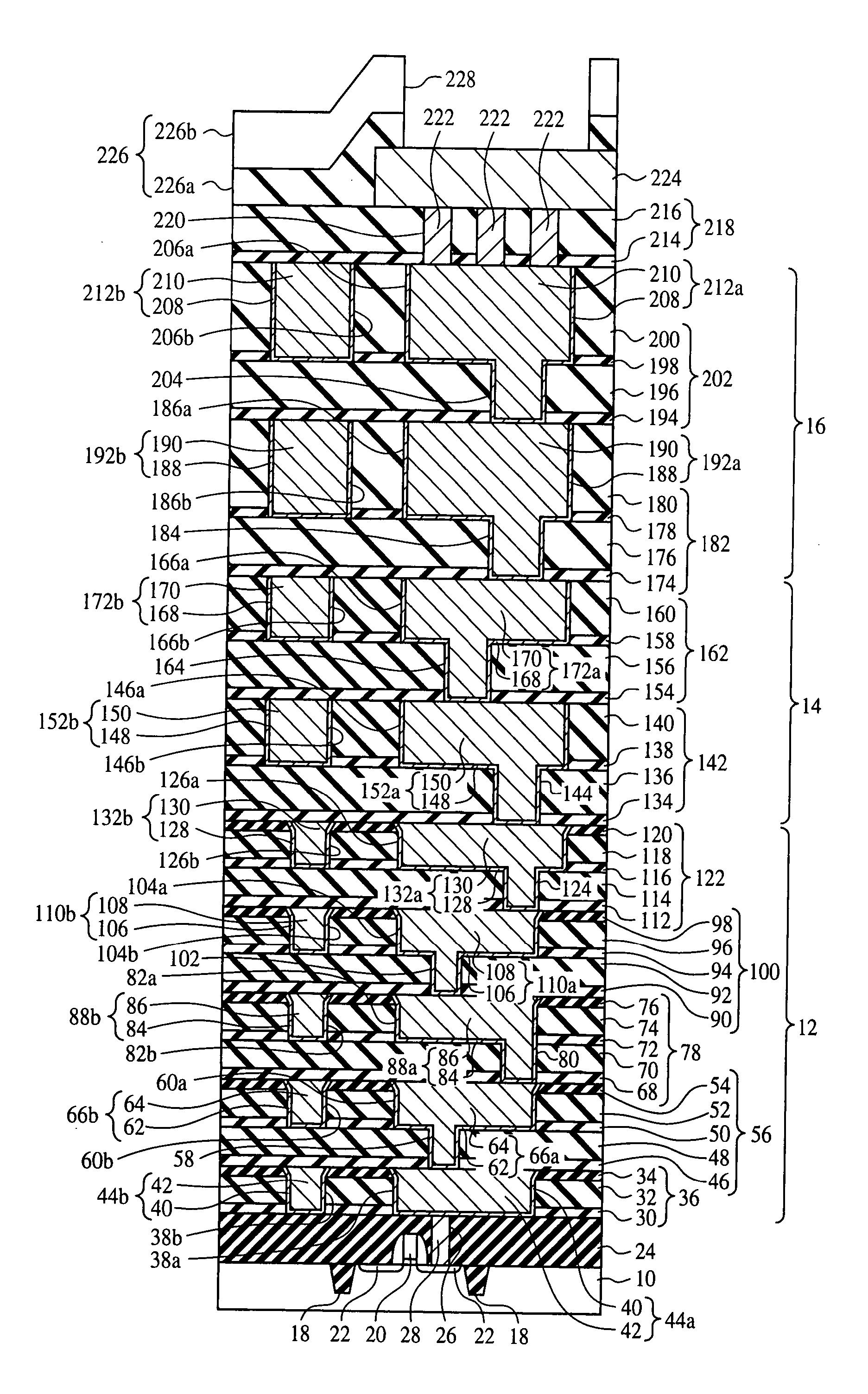

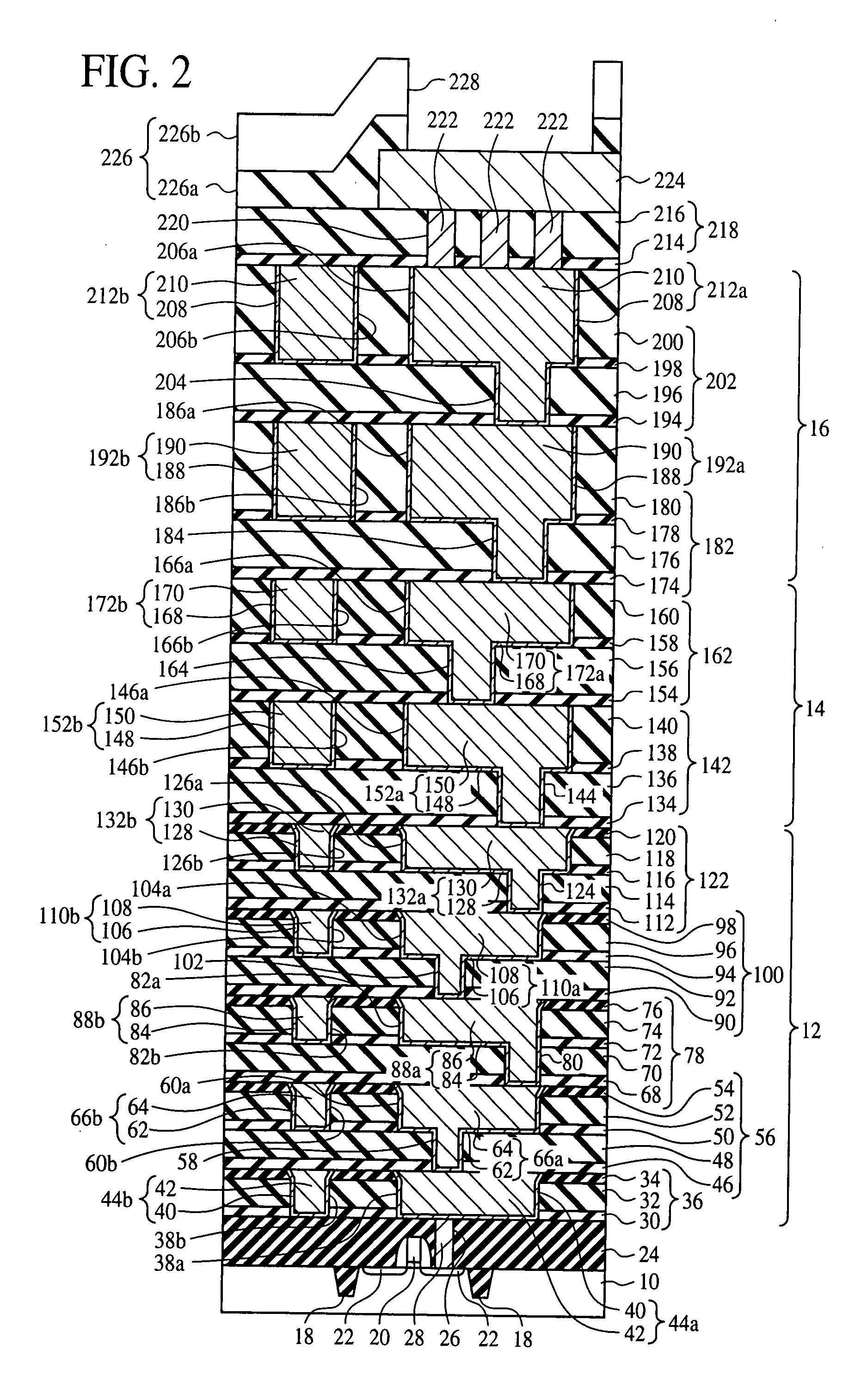

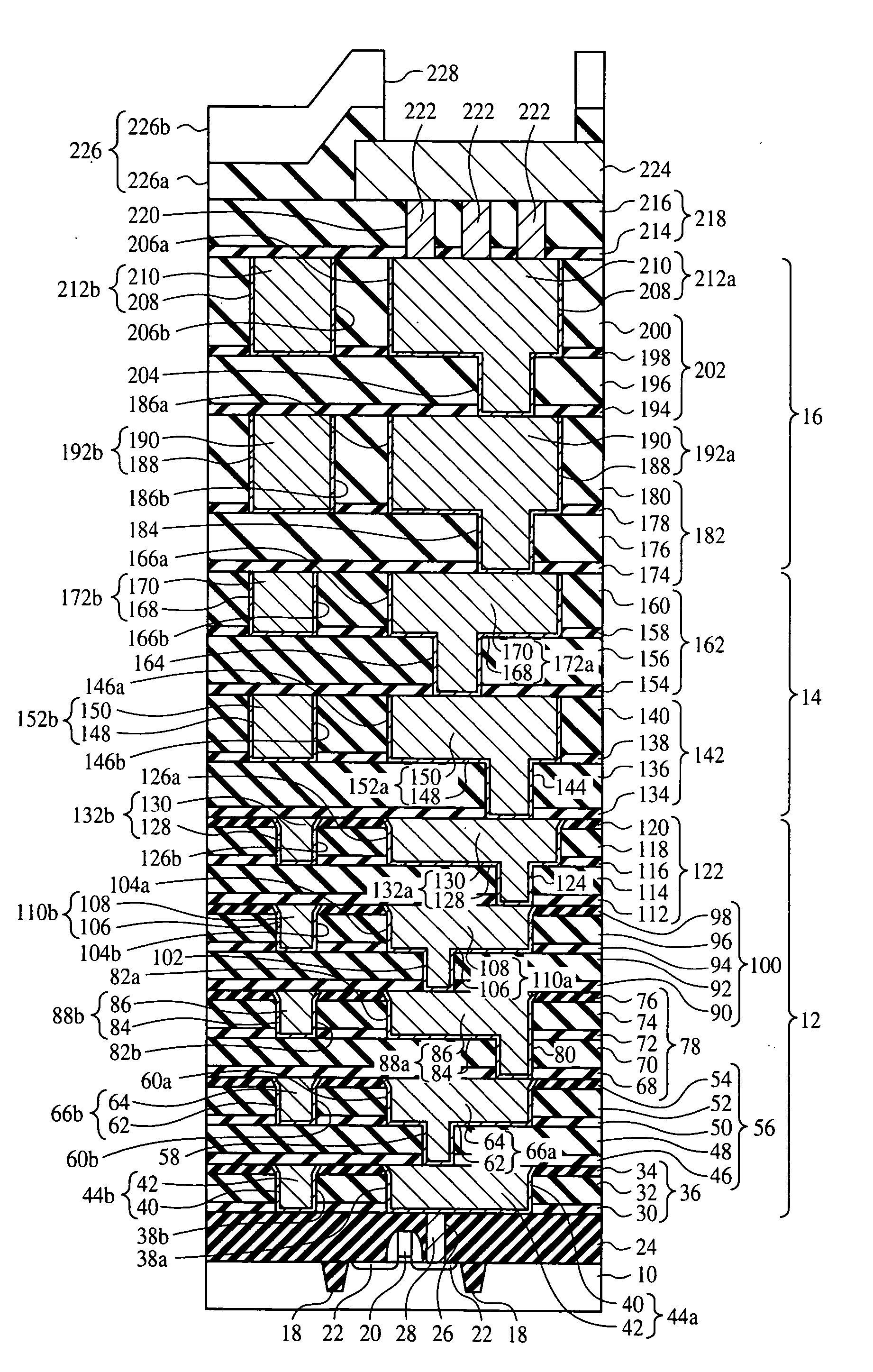

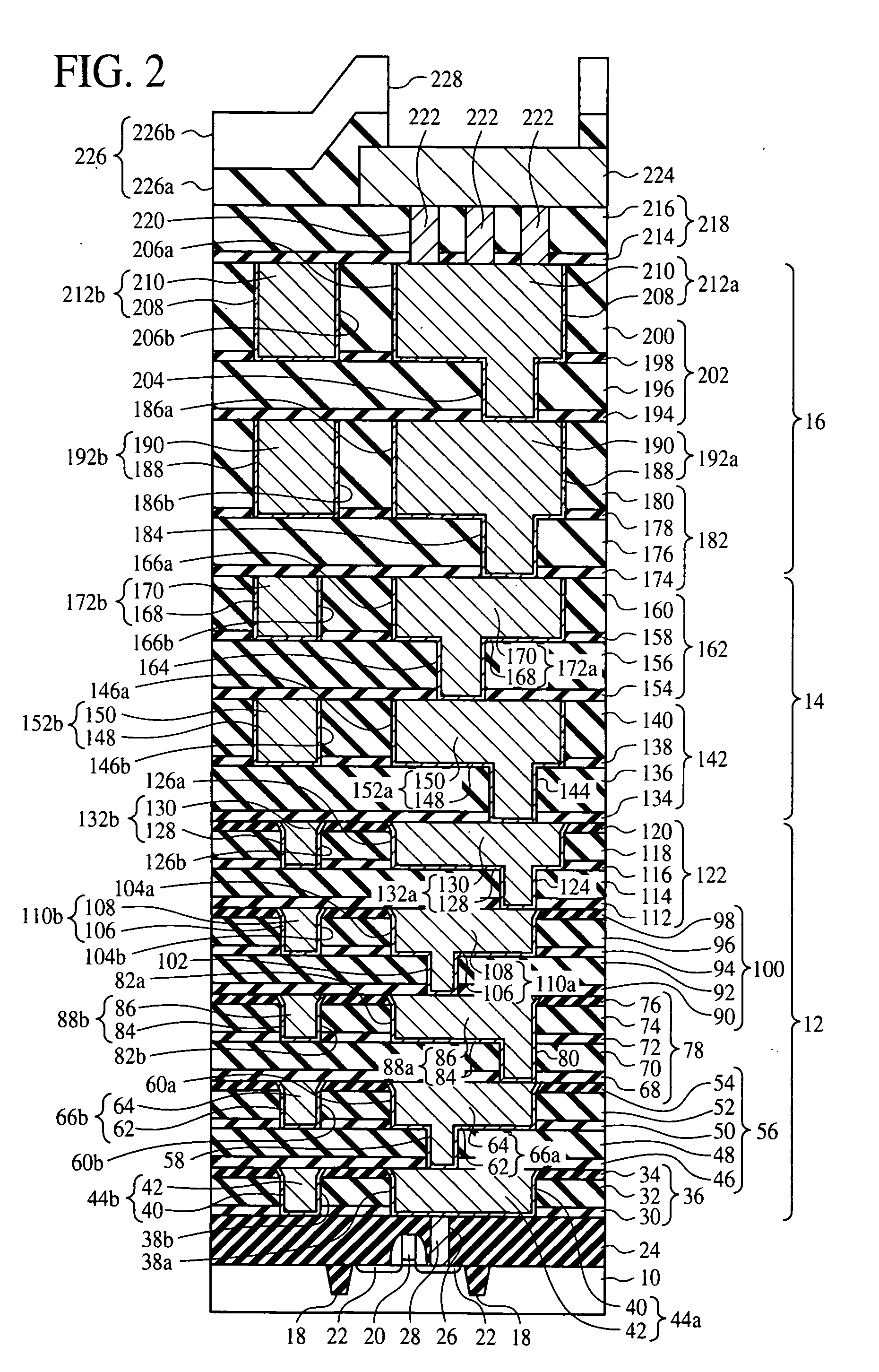

Semiconductor device and method for fabricating the same

InactiveUS7250679B2Inhibition of defect generationReduce interconnectionSemiconductor/solid-state device detailsSolid-state devicesInter layerEngineering

The semiconductor device comprises a lower interconnection part 12 which is formed on a silicon substrate 10 and includes an inter-layer insulation film 36 formed of a low-k film 32 and a hydrophilic insulation film 34 formed on the low-k film 32, and an interconnection layer 44a, 44b buried in interconnection trenches 38a, 38b formed in the inter-layer insulation film 36 and having an interconnection pitch which is a first pitch; and an intermediate interconnection part 14 which is formed on the lower interconnection part 12 and includes an inter-layer insulation film 142 formed of low-k films 136, 140, an interconnection layer 152a, 152b buried in interconnection trenches 146a, 146b formed in the inter-layer insulation film 142 and having an interconnection pitch which is a second pitch larger than the first pitch, and an SiC film 154 formed directly on the low-k film 140 and the interconnection layer 152a, 152b.

Owner:FUJITSU SEMICON LTD

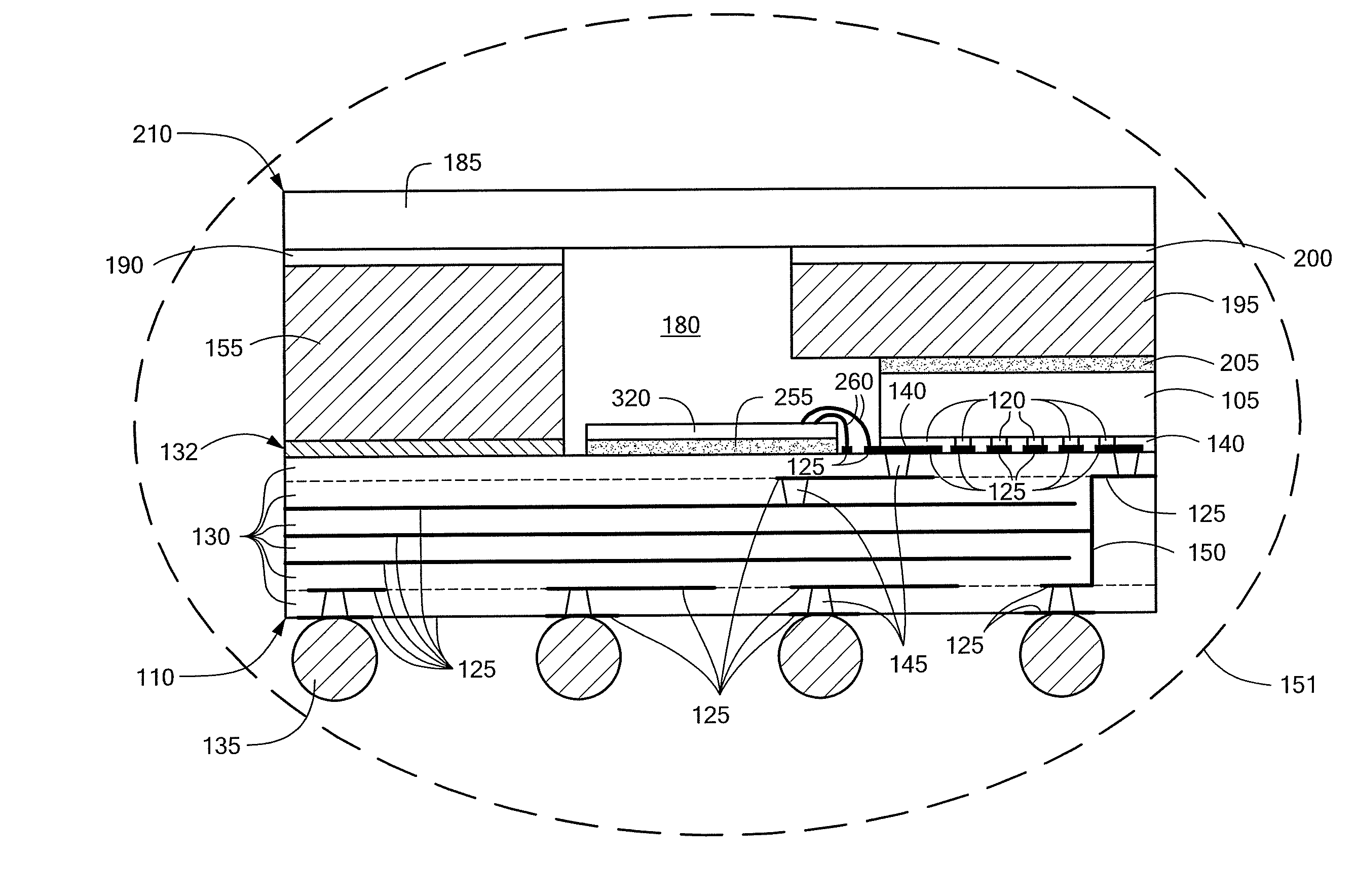

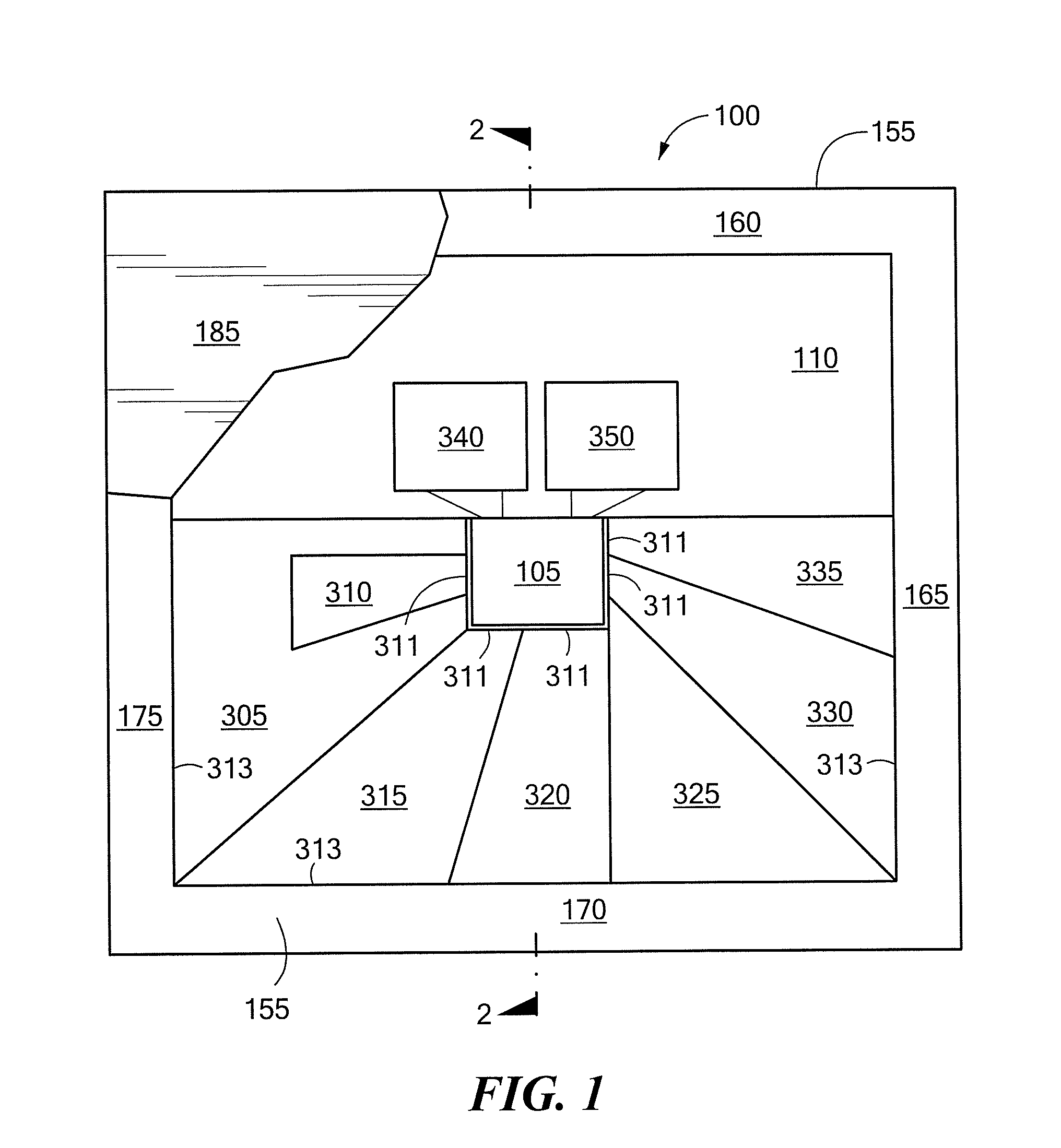

Low noise high thermal conductivity mixed signal package

ActiveUS20110018126A1Efficient thermal managementHigh thermal conductivity materialSemiconductor/solid-state device detailsSolid-state devicesLow noiseEngineering

An improved microelectronic assembly (100) and packaging method includes a device package for housing a semiconductor die or chip, (105), an array of passive electronic components (305-355) operating in cooperation with the flip chip semiconductor die (105) and housed inside the device package to decouple noise from input signals, and a heat spreader (195) disposed between a top surface of the semiconductor die (105) and a package cover (185). The semiconductor die (105) is configured as a flip chip die and the device package includes a package substrate (110) configured as a ball grid array. The improved microelectronic device (100) reduces parasitic inductance in electrical interconnections between the semiconductor die and an electrical system substrate (115) and reduces signal noise in mixed signal high frequency analog to digital converters operating at clock rates above 1 GHz.

Owner:RAYTHEON CO

Shift register

ActiveUS8269714B2Reduce interconnectionReduce areaCathode-ray tube indicatorsDigital storageShift registerElectricity

Owner:SHARP KK

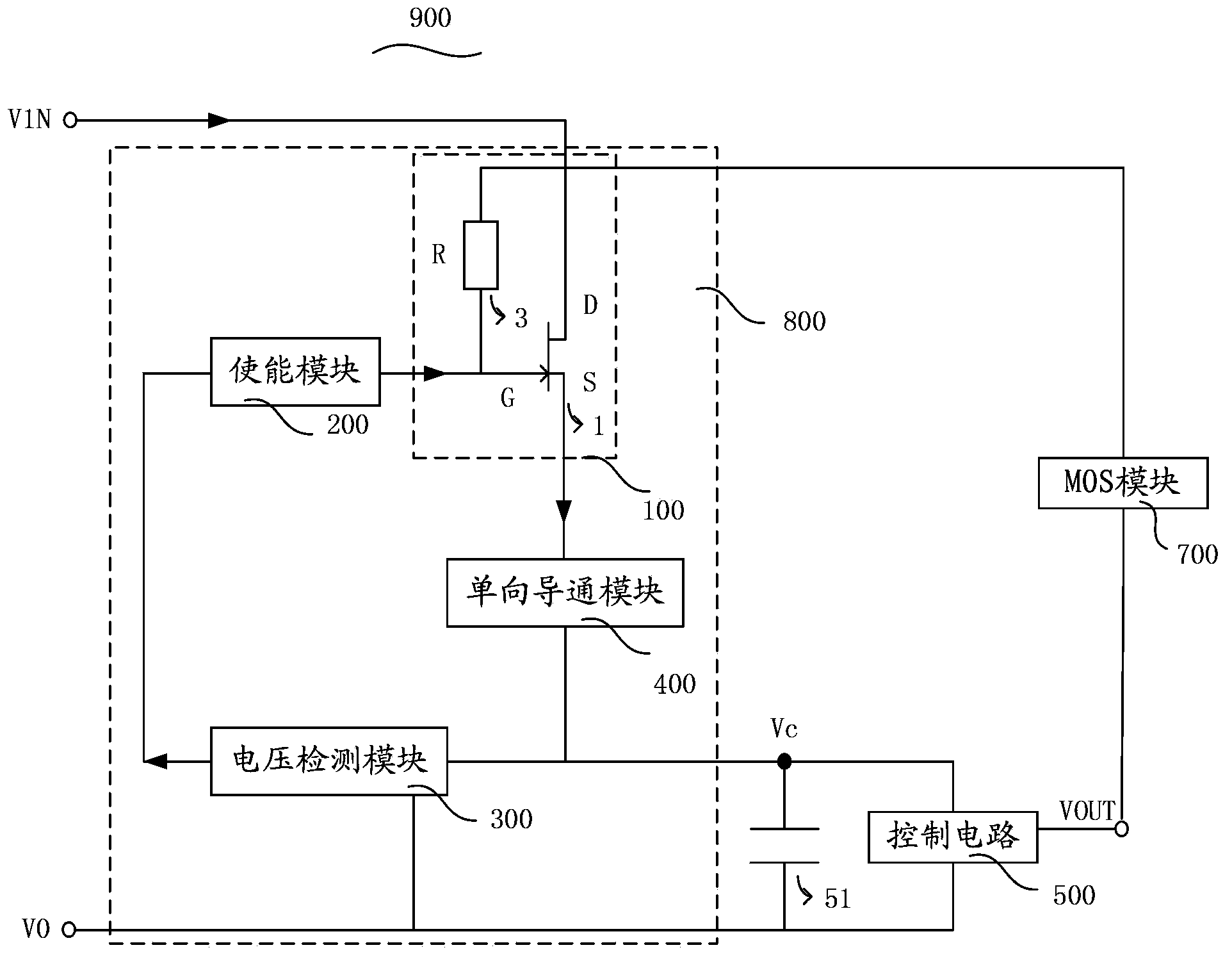

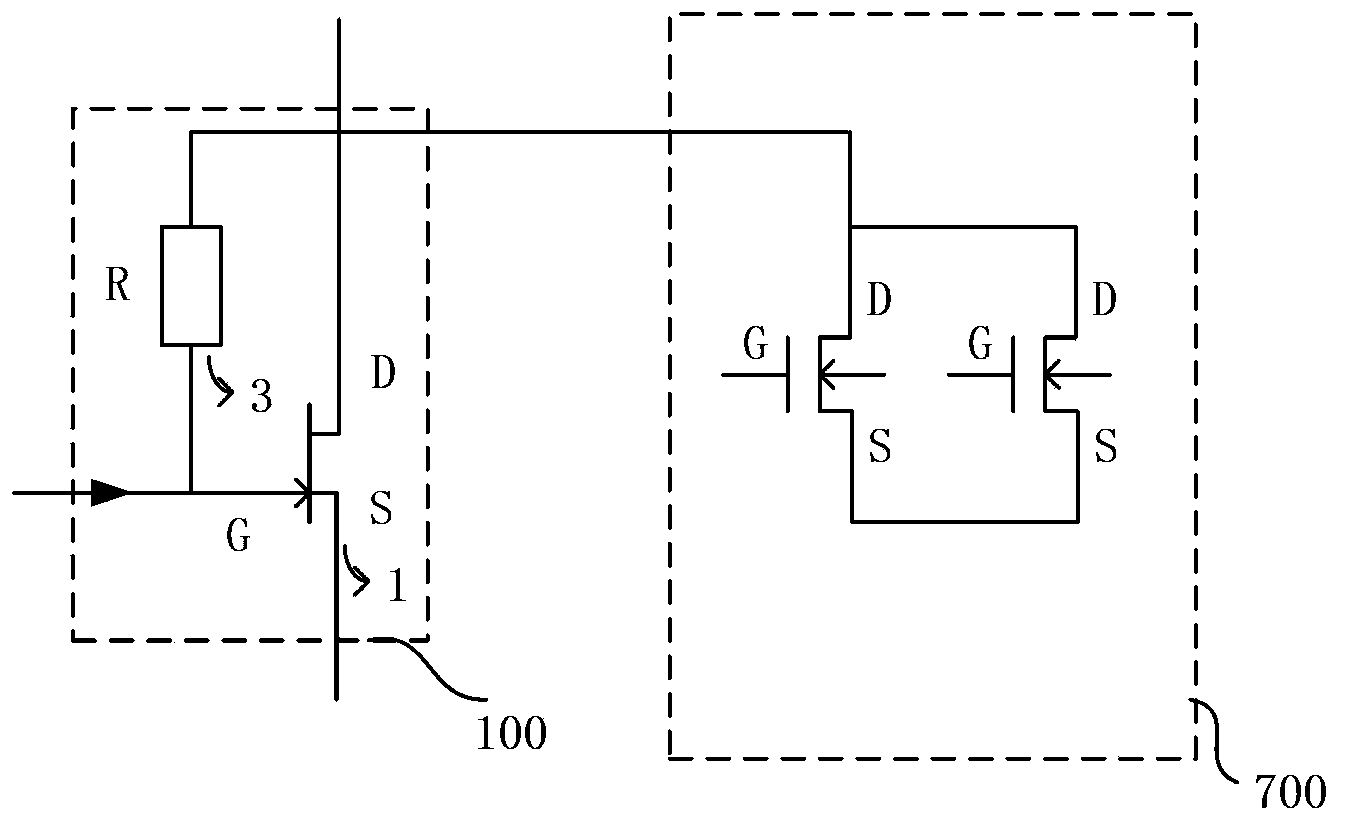

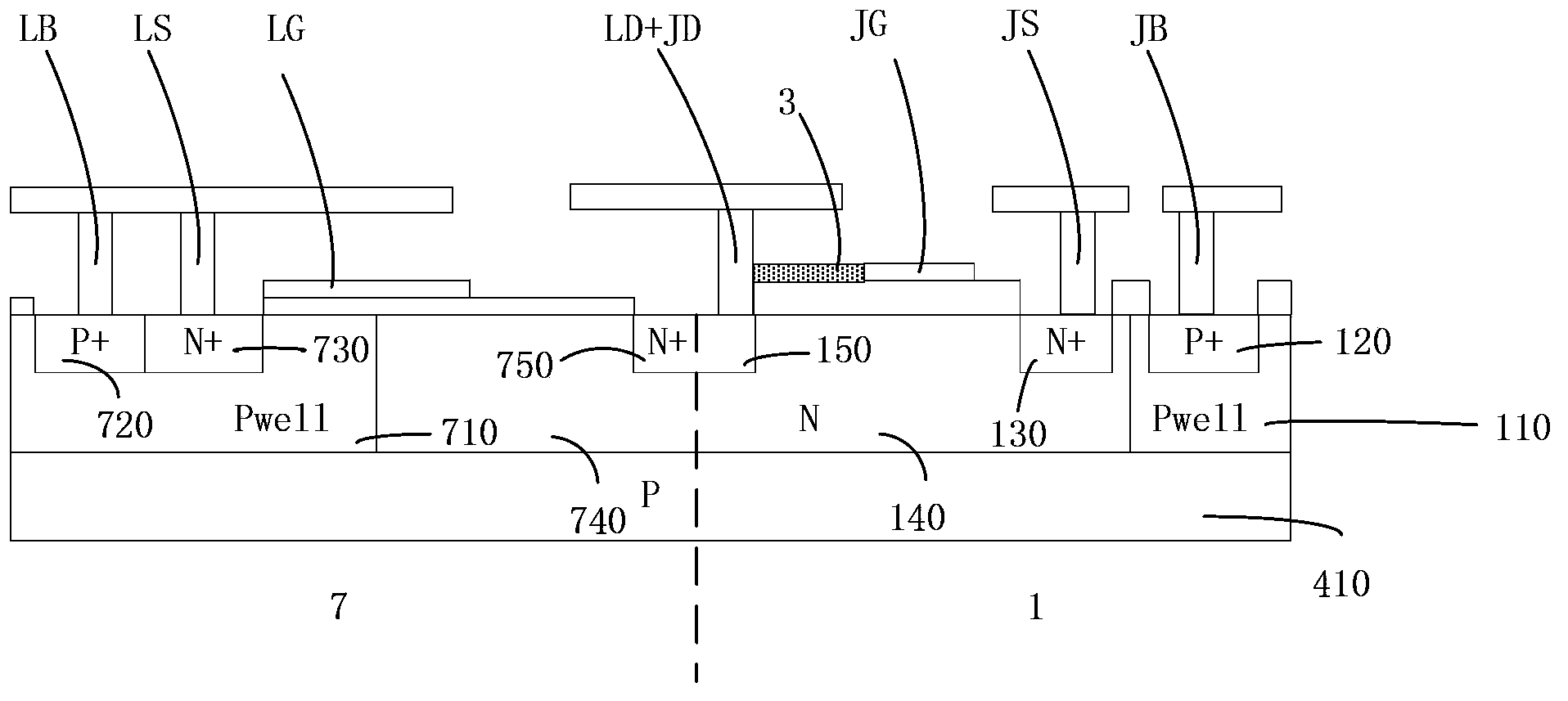

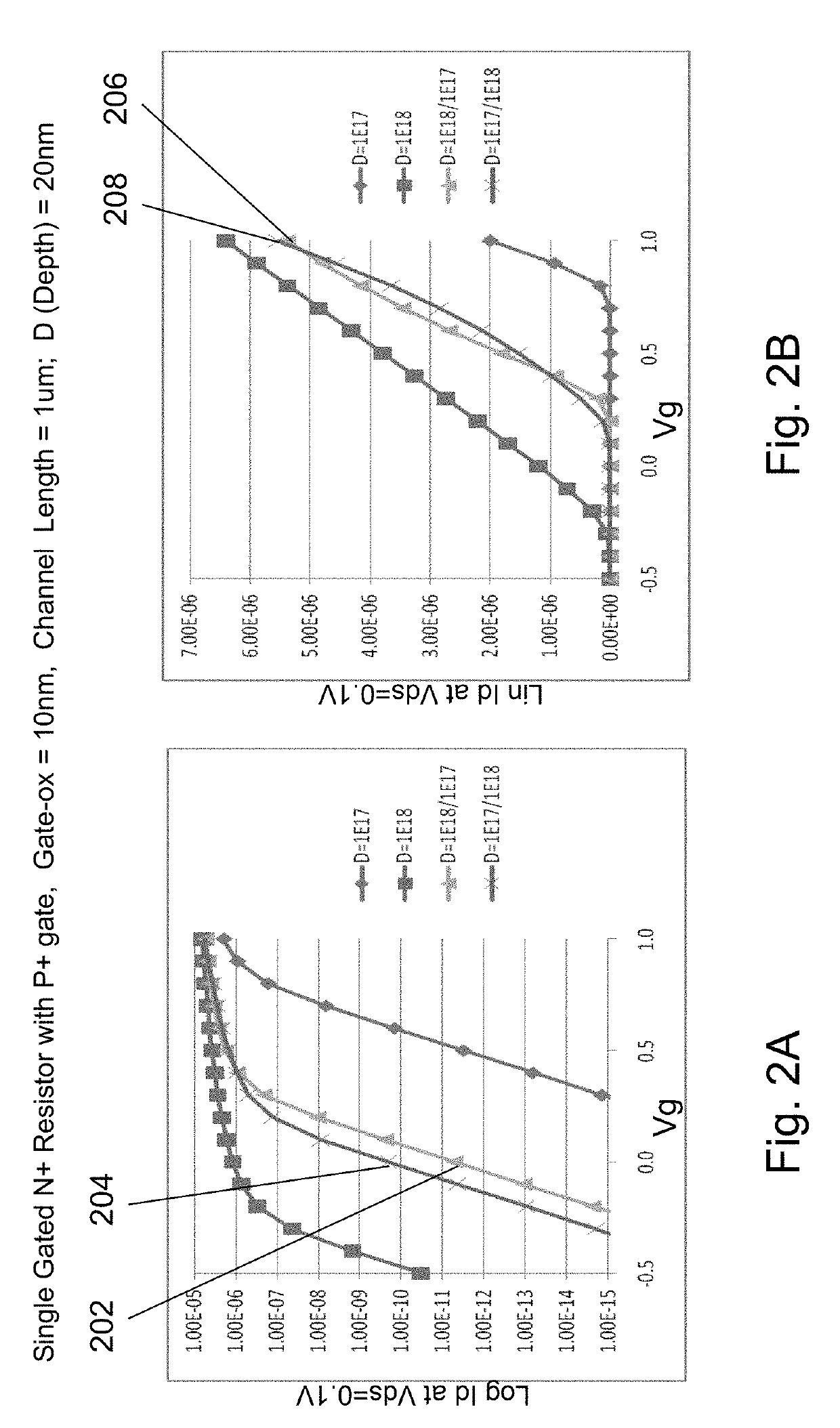

Semiconductor device and forming method, starting circuit and switching power source of semiconductor device

ActiveCN103441145AImprove reliabilityReduce areaSemiconductor/solid-state device manufacturingElectric variable regulationElectrical resistance and conductanceIntrinsics

The invention provides a semiconductor device and a forming method, a starting circuit and a switching power source of the semiconductor device. The switching power source comprises the starting circuit. The semiconductor device comprises a P-type semiconductor substrate, an N-type drift region, an oxide layer, an intrinsic polycrystalline silicon layer, a doping polycrystalline silicon layer and a metal plug, wherein a source electrode and a drain electrode of a negative threshold field-effect tube are arranged at the two ends of the N-type drift region, the source electrode and the drain electrode are exposed out of the oxide layer, the intrinsic polycrystalline silicon layer is arranged at one end, close to the source electrode, of the oxide layer, and the doping polycrystalline silicon layer is arranged at one end, close to the drain electrode, of the oxide layer. The intrinsic polycrystalline silicon layer and the oxide layer form a grid electrode of the negative threshold field-effect tube, the doping polycrystalline silicon layer forms a resistor connected with the grid electrode, and the metal plug is connected with the drain electrode of the negative threshold field-effect tube and is adjacent to the doping polycrystalline silicon layer. In the semiconductor device, the resistor connected with the drain electrode and the grid electrode of the negative threshold field-effect tube is formed at the position, arranged between the drain electrode and the grid electrode, of the semiconductor substrate and shares the metal plug with the drain electrode, the area of a chip is saved, metal interconnection is reduced through port sharing, and the reliability of the semiconductor device is improved.

Owner:CSMC TECH FAB2 CO LTD

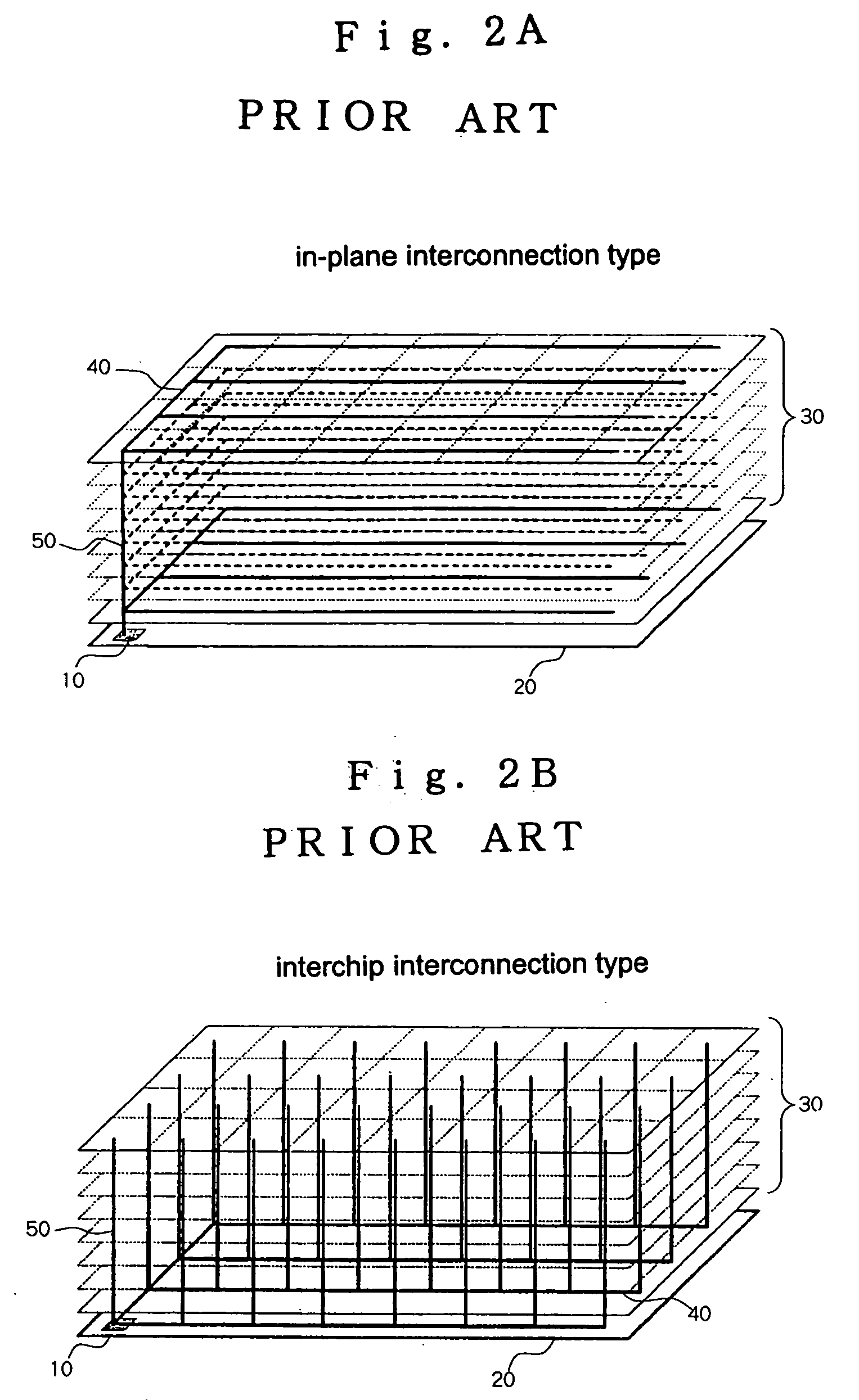

Three-dimensional semiconductor device provided with interchip interconnection selection means for electrically isolating interconnections other than selected interchip interconnections

ActiveUS20050286286A1Run at high speedReduce power consumptionTransistorSolid-state devicesCapacitanceDevice material

In a three-dimensional semiconductor device in which a plurality of semiconductor circuit chips are stacked and that is provided with a plurality of interchip interconnections for signal transmission between these semiconductor circuit chips, when transmitting signals, only one interchip interconnection that serves for signal transmission is selected and other interchip interconnections are electrically isolated by means of switches that are provided between the interchip interconnections and signal lines. Interchip interconnection capacitance relating to the charge and discharge of interconnections is thus minimized.

Owner:NEC CORP +1

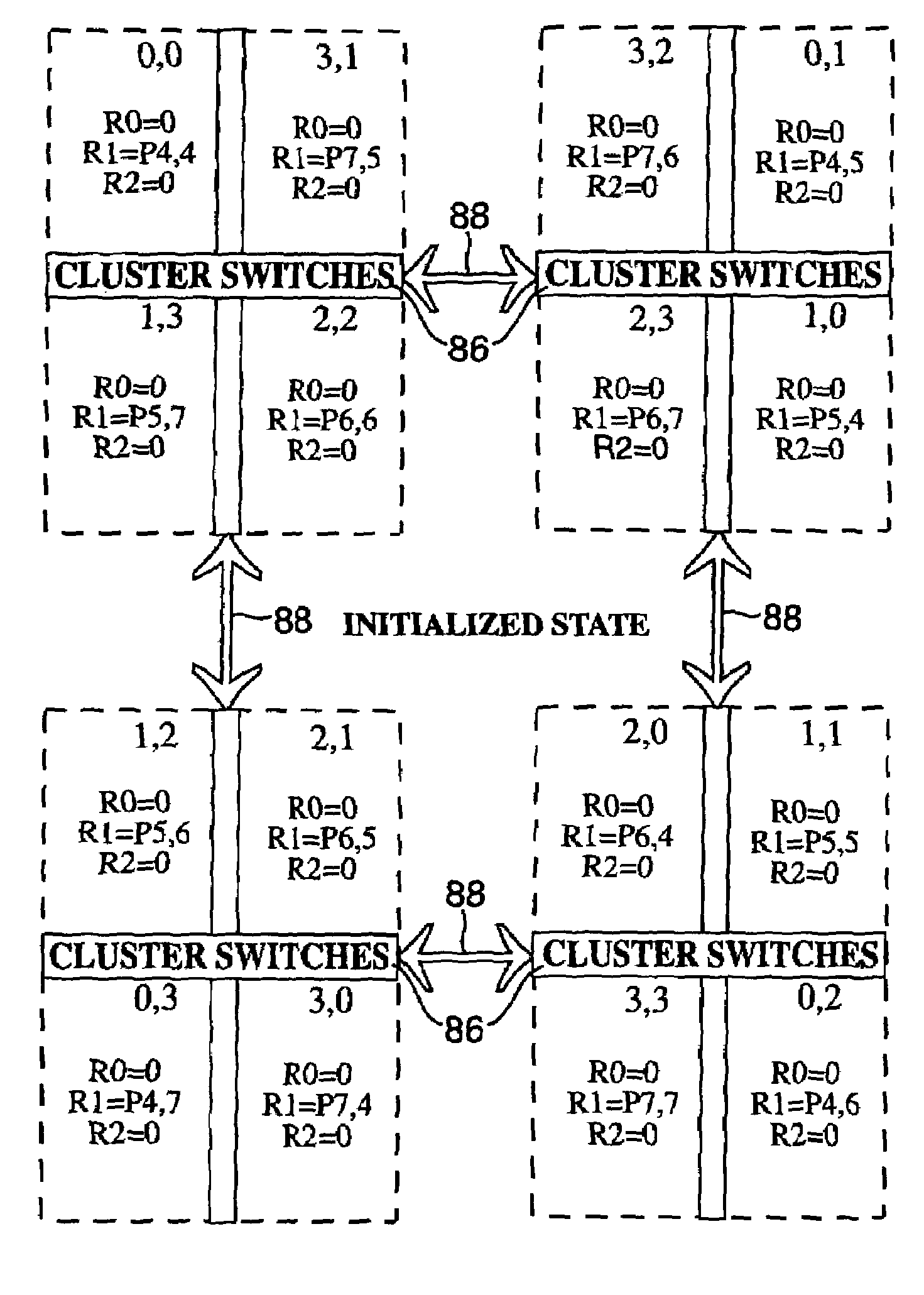

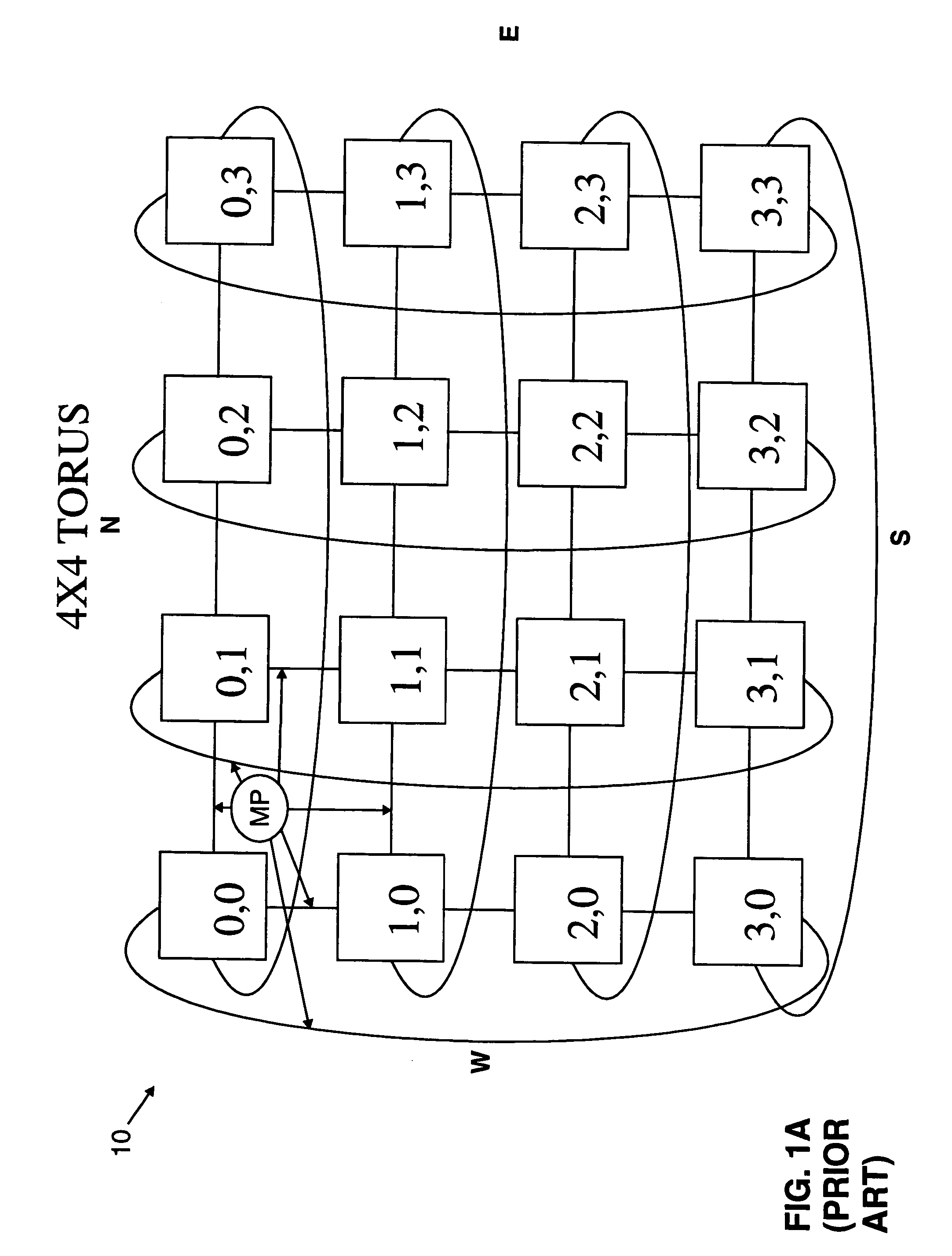

Manifold array processor

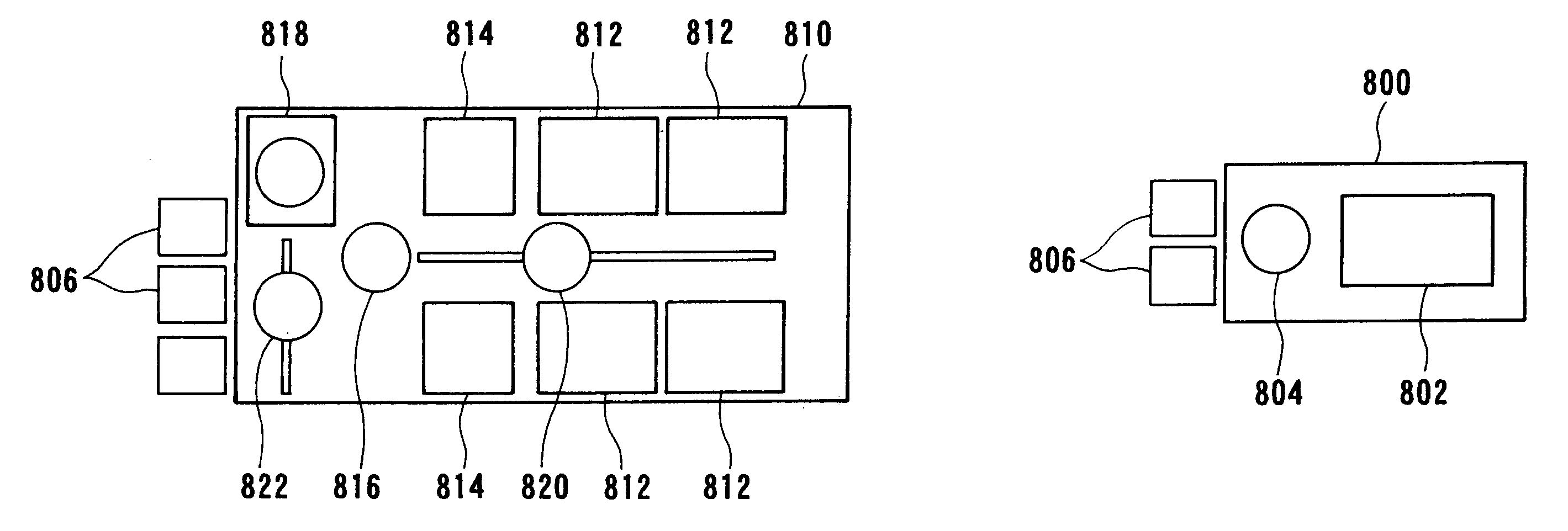

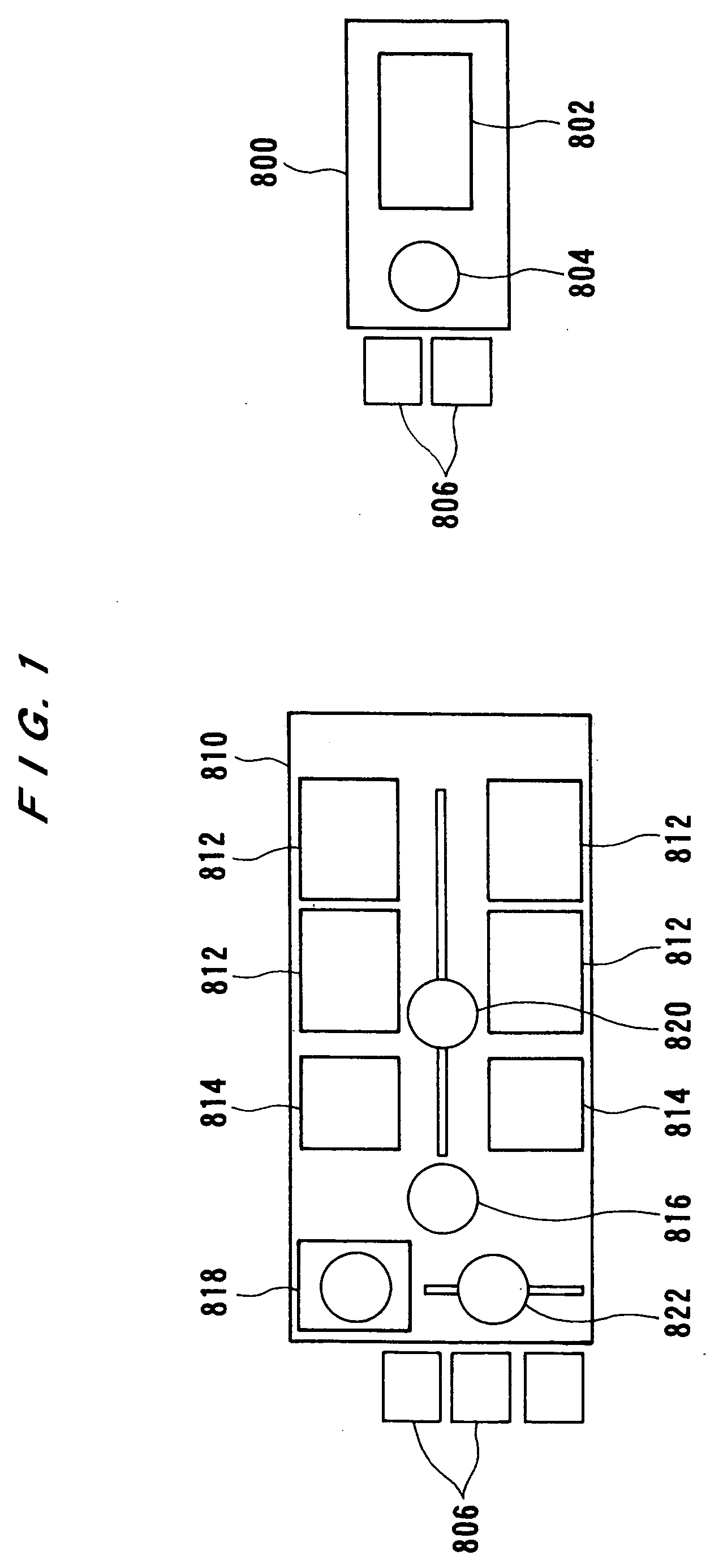

InactiveUS7197624B2Lower latencyShorten the lengthSingle instruction multiple data multiprocessorsMultiple digital computer combinationsProcessing elementDatapath

An array processor includes processing elements (00, 01, 02, 03, 10, 11, 12, 13, 20, 21, 22, 23, 30, 31, 32, 33) arranged in clusters (e.g., 44, 46, 48, 50) to form a rectangular array (40). Inter-cluster communication paths (88) are mutually exclusive. Due to the mutual exclusivity of the data paths, communications between the processing elements of each cluster may be combined in a single inter-cluster path, thus eliminating half the wiring required for the path. The length of the longest communication path is not directly determined by the overall dimension of the array, as in conventional torus arrays. Rather, the longest communications path is limited by the inter-cluster spacing. Transpose elements of an N×N torus may be combined in clusters and communicate with one another through intra-cluster communications paths. Transpose operation latency is eliminated in this approach. Each PE may have a single transmit port (35) and a single receive port (37). Thus, the individual PEs are decoupled from the array topology.

Owner:ALTERA CORP

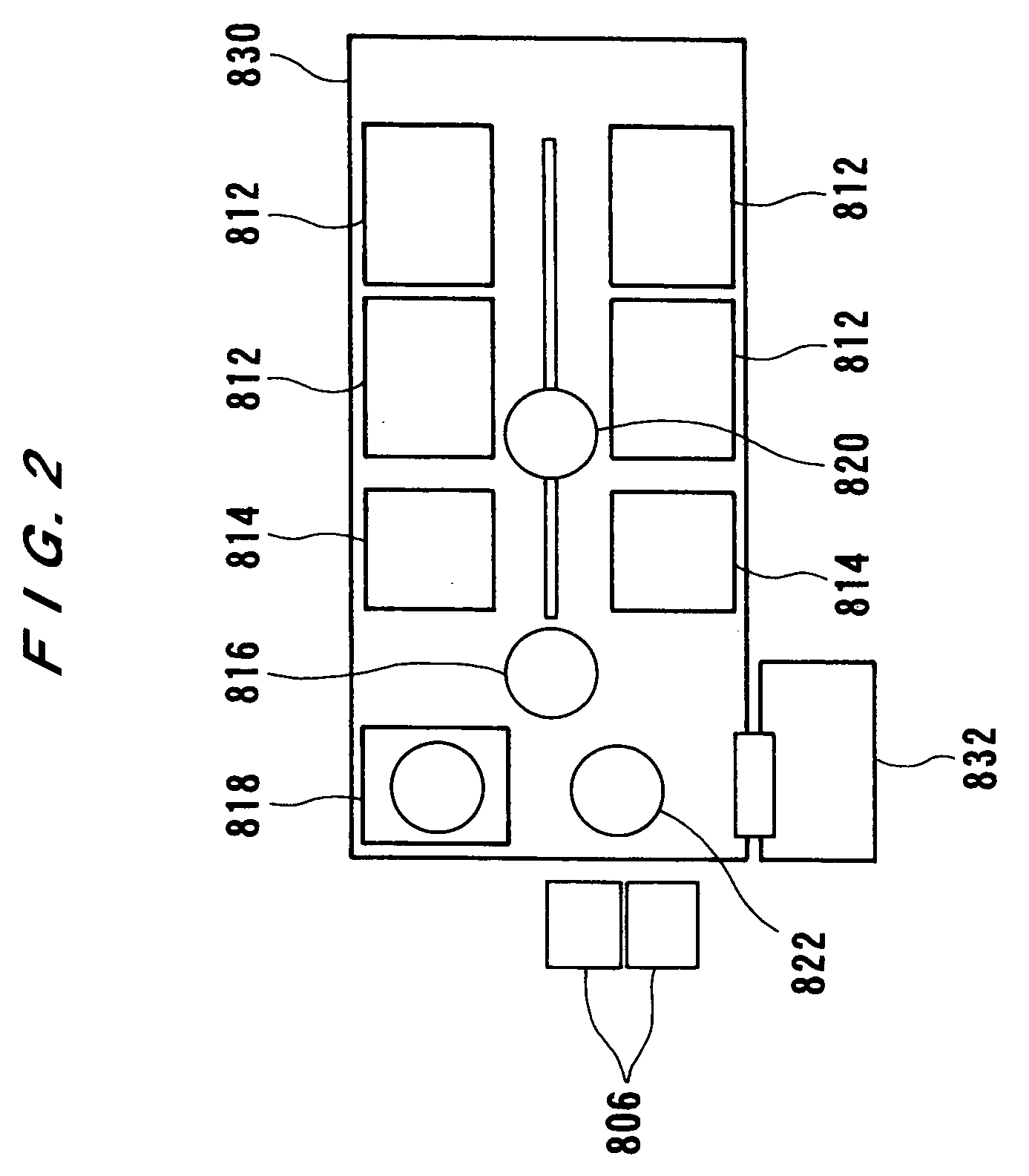

Substrate processing apparatus

InactiveUS20050236268A1Reduce throughputLow costCellsMachining electric circuitsEngineeringMechanical engineering

A substrate processing apparatus has a plating apparatus configured to plate a substrate to deposit a metal on a surface of the substrate and an additional process apparatus configured to perform an additional process on the substrate. The plating apparatus has a substrate placement stage on which the substrate to be transferred to the additional process apparatus is placed. The additional process apparatus has an additional process unit configured to perform the additional process on the substrate and a substrate transfer device operable to transfer the substrate between the substrate placement stage of the plating apparatus and the additional process unit. The substrate processing apparatus can perform an additional process in addition to a plating process without lowering a throughput of the apparatus and can upgrade the additional process at a low cost.

Owner:EBARA CORP

Three-dimensional semiconductor device provided with interchip interconnection selection means for electrically isolating interconnections other than selected interchip interconnections

ActiveUS7330368B2Run at high speedReduce power consumptionTransistorSolid-state devicesCapacitanceInterconnection

Owner:NEC CORP +1

Stacked semiconductor memory device

ActiveUS7209376B2Reduce power consumptionReduce interconnectionSemiconductor/solid-state device detailsSolid-state devicesCapacitanceSemiconductor chip

Owner:LONGITUDE LICENSING LTD

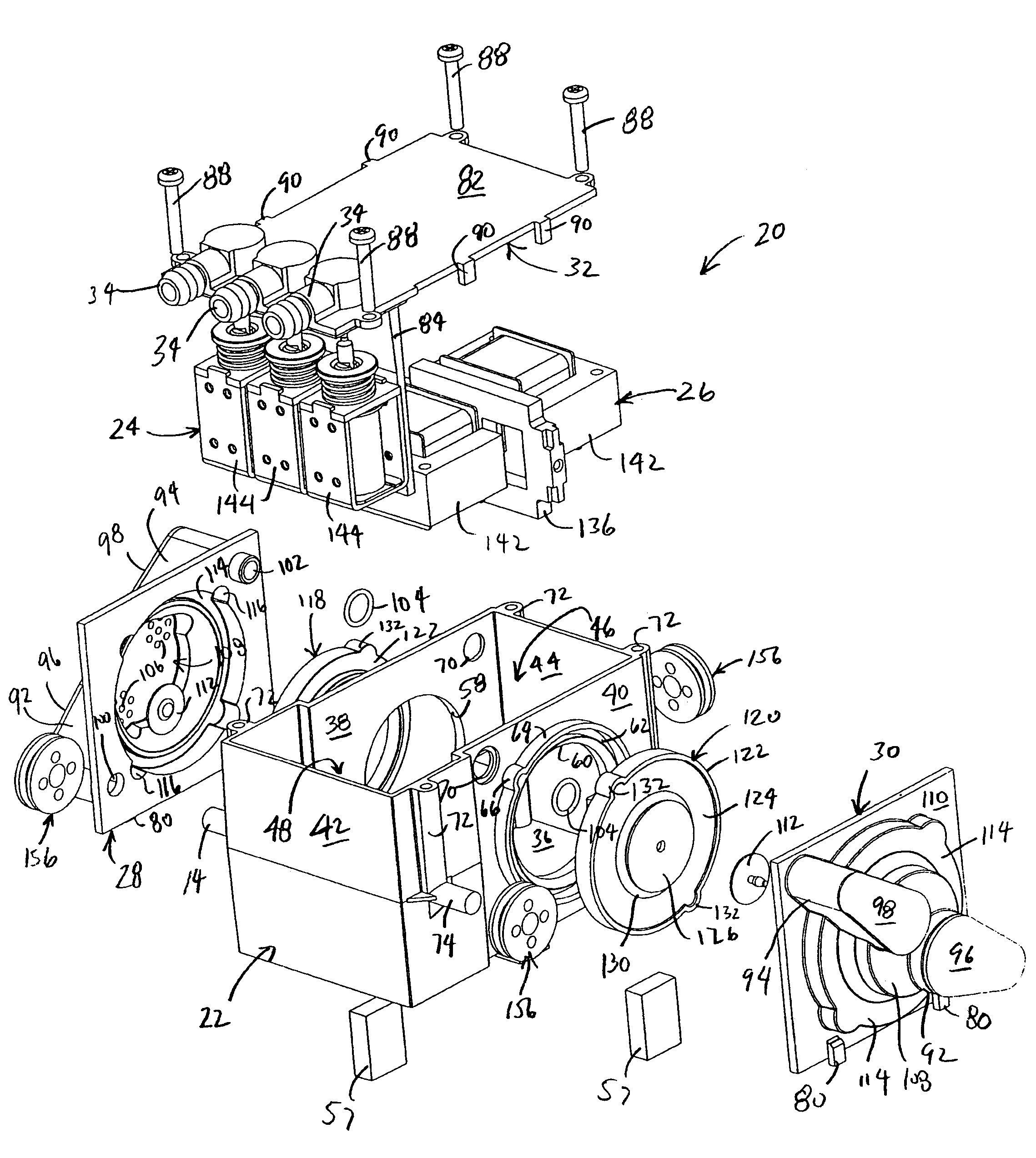

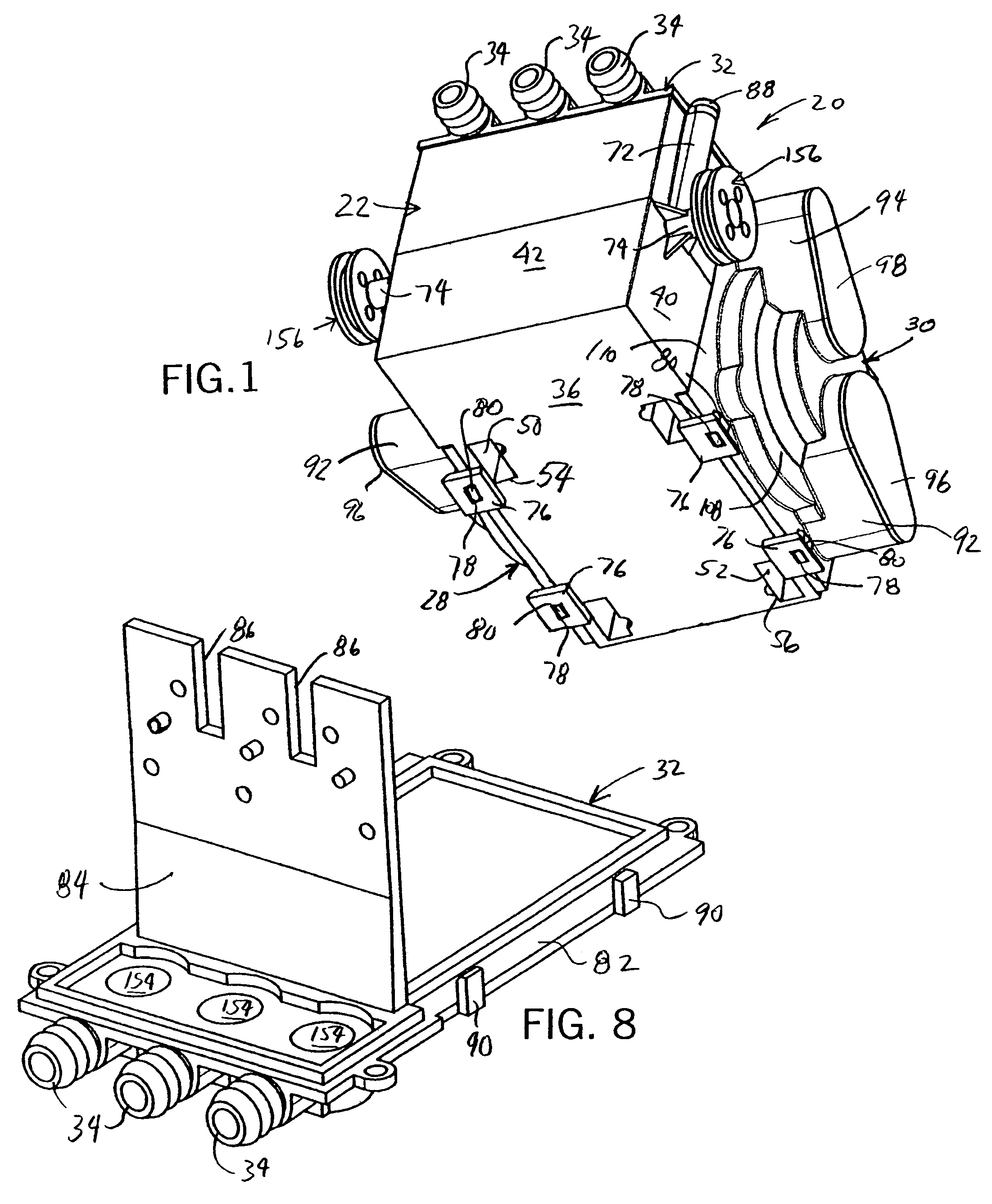

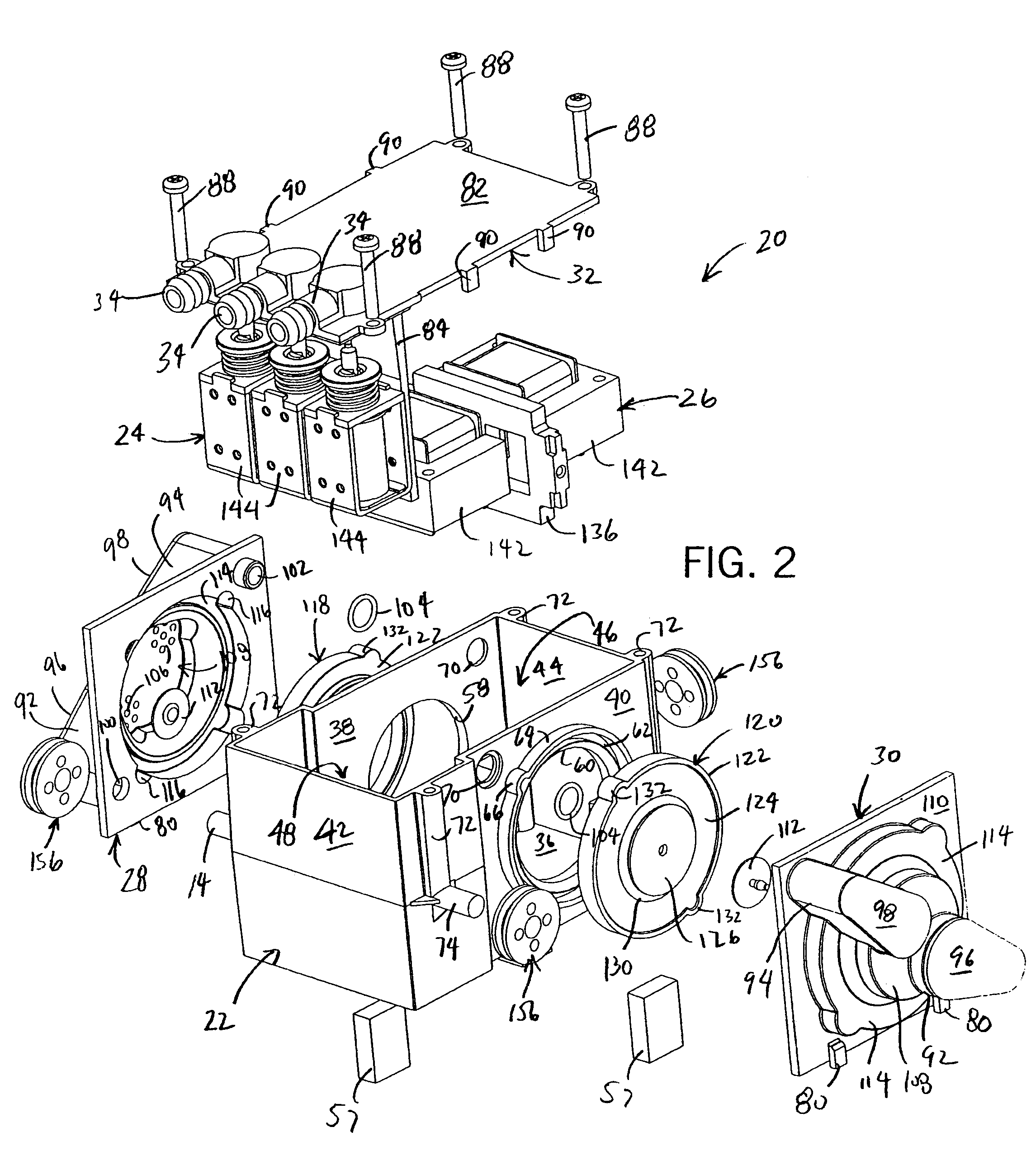

Compact linear air pump and valve package

InactiveUS7322801B2Reduce vibrationImprove vibrationPositive displacement pump componentsFlexible member pumpsDiaphragm pumpSolenoid valve

A compact air pump and valve package includes pump and valve assemblies integral with a pressure housing defining inlet ports and a plurality of fittings for connecting air lines to an interior of the pressure housing. The linear diaphragm pump assembly has a permanent magnetic shuttle mounting two diaphragms reciprocated by an electromagnet. The valve assembly has a plurality of solenoid valves disposed within the pressure housing, each solenoid valve being operable to control flow into or out of the pressure housing through an associated one of the plurality of fittings. Thus, no tubes or hoses are required to transfer air from the pump assembly to the valves. The housing has special mounts to isolate vibration arising from movement of the shuttle.

Owner:THOMAS IND INC

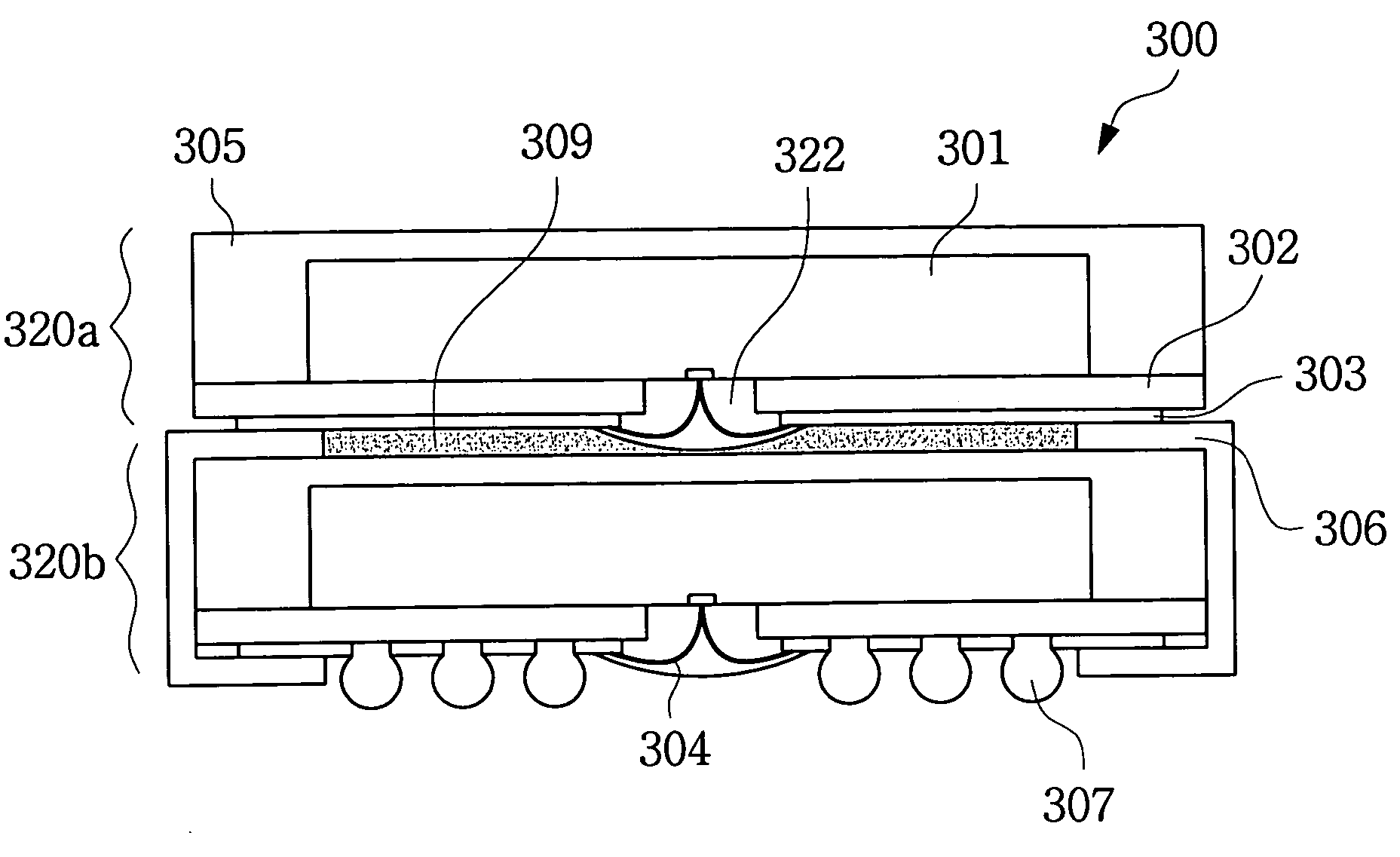

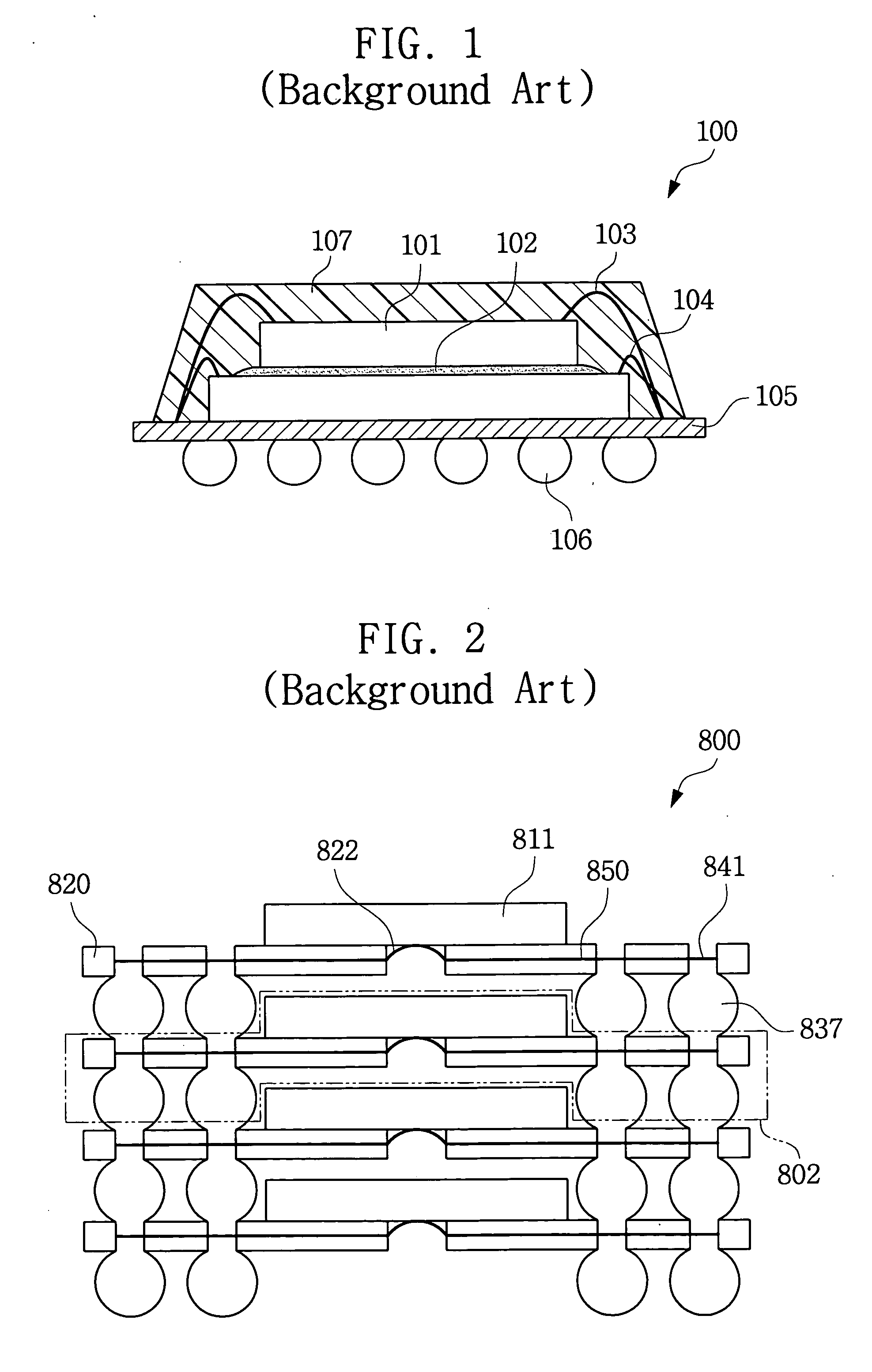

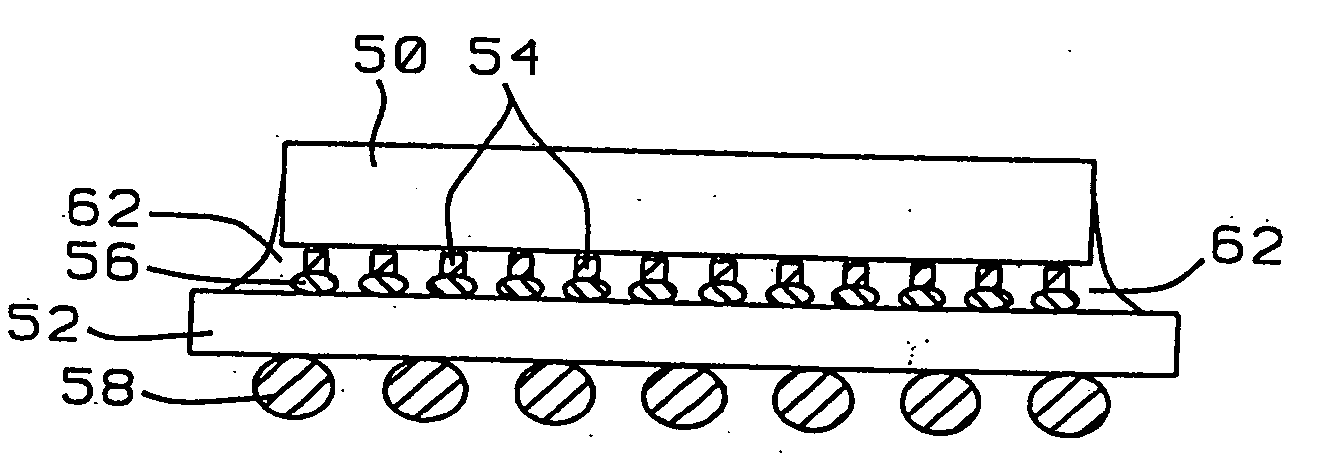

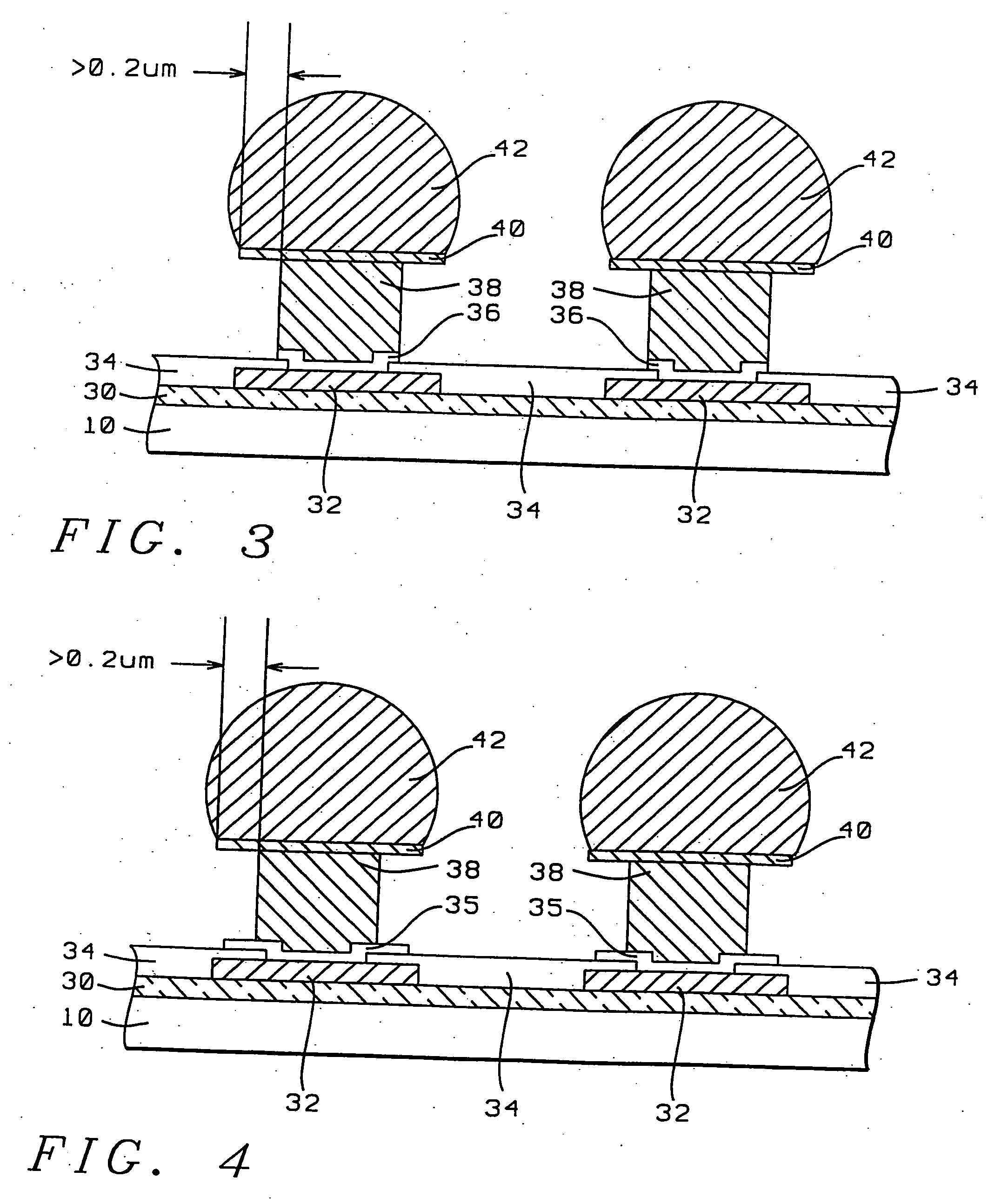

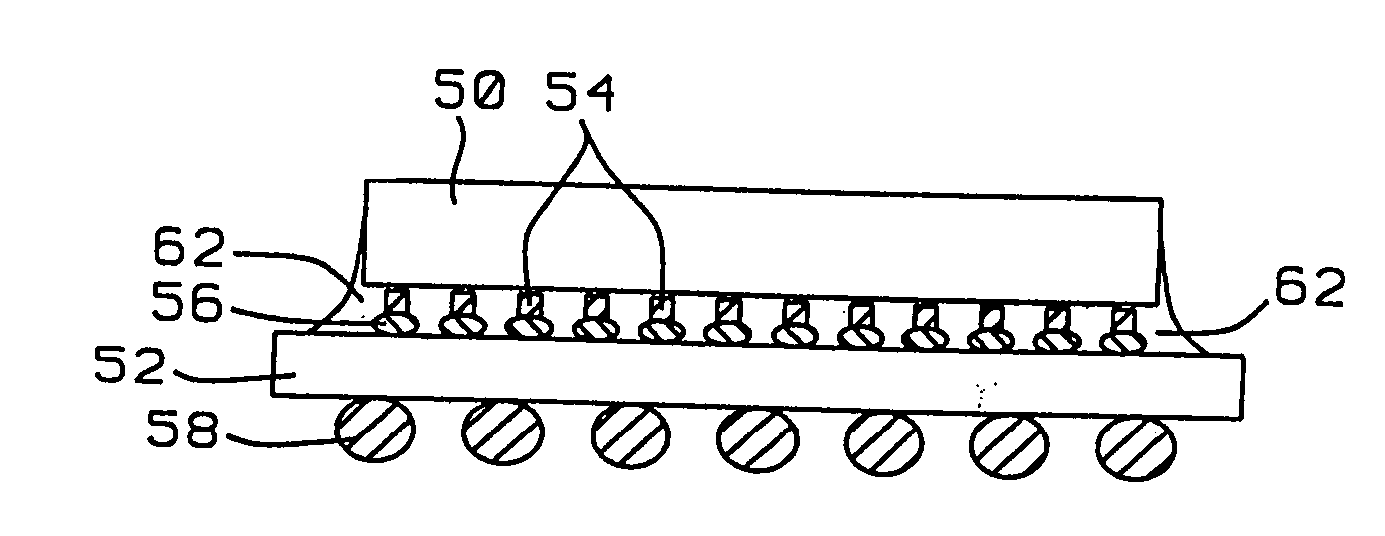

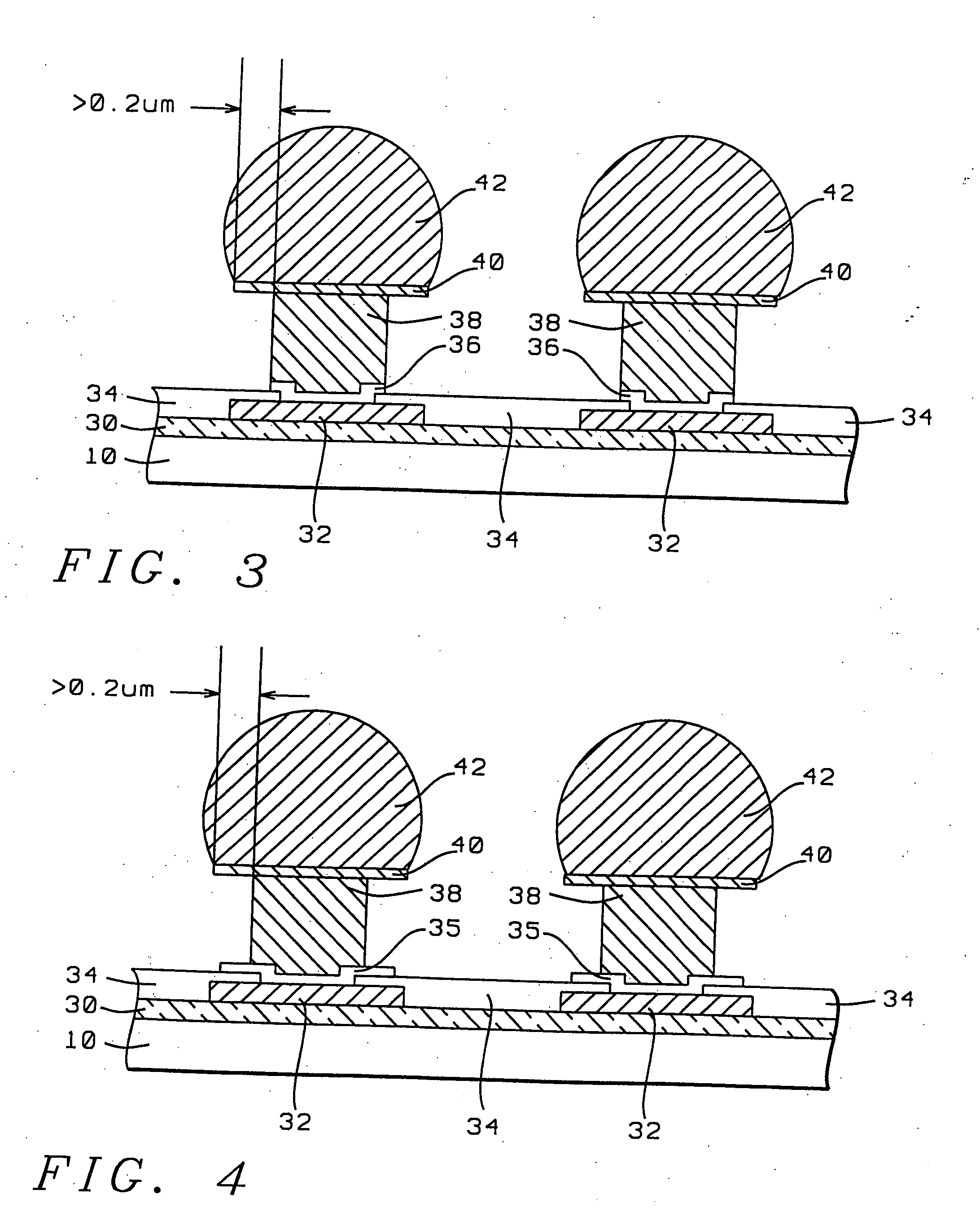

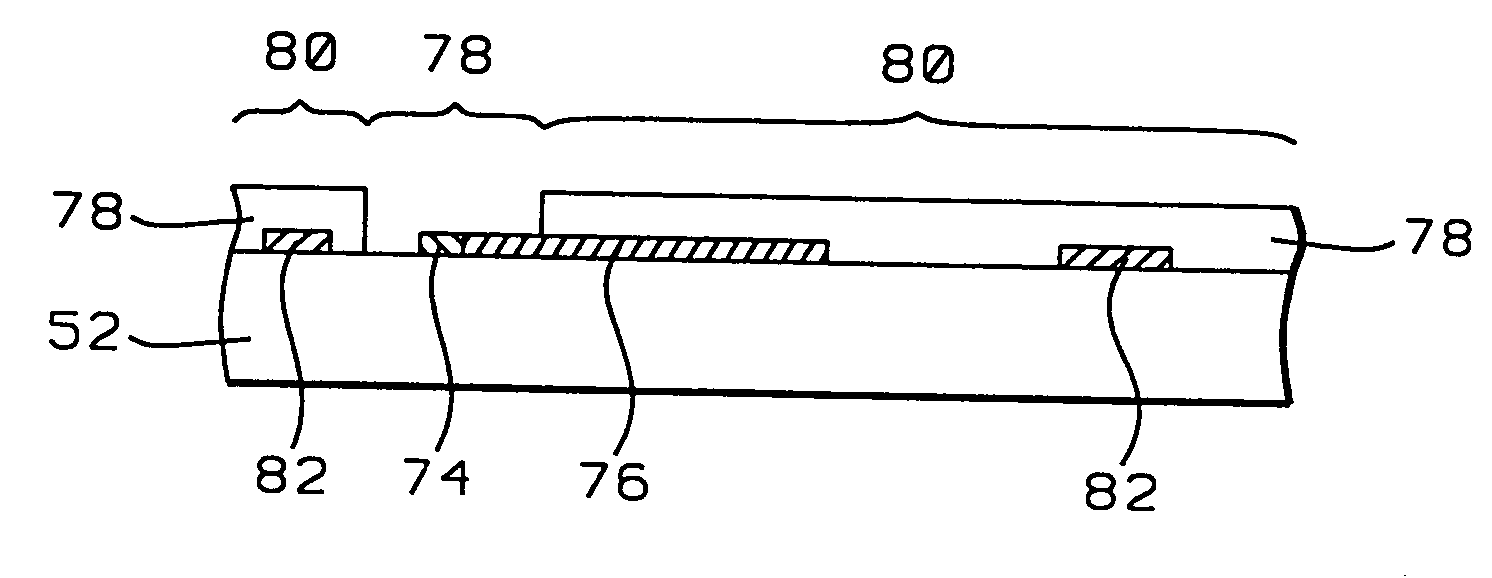

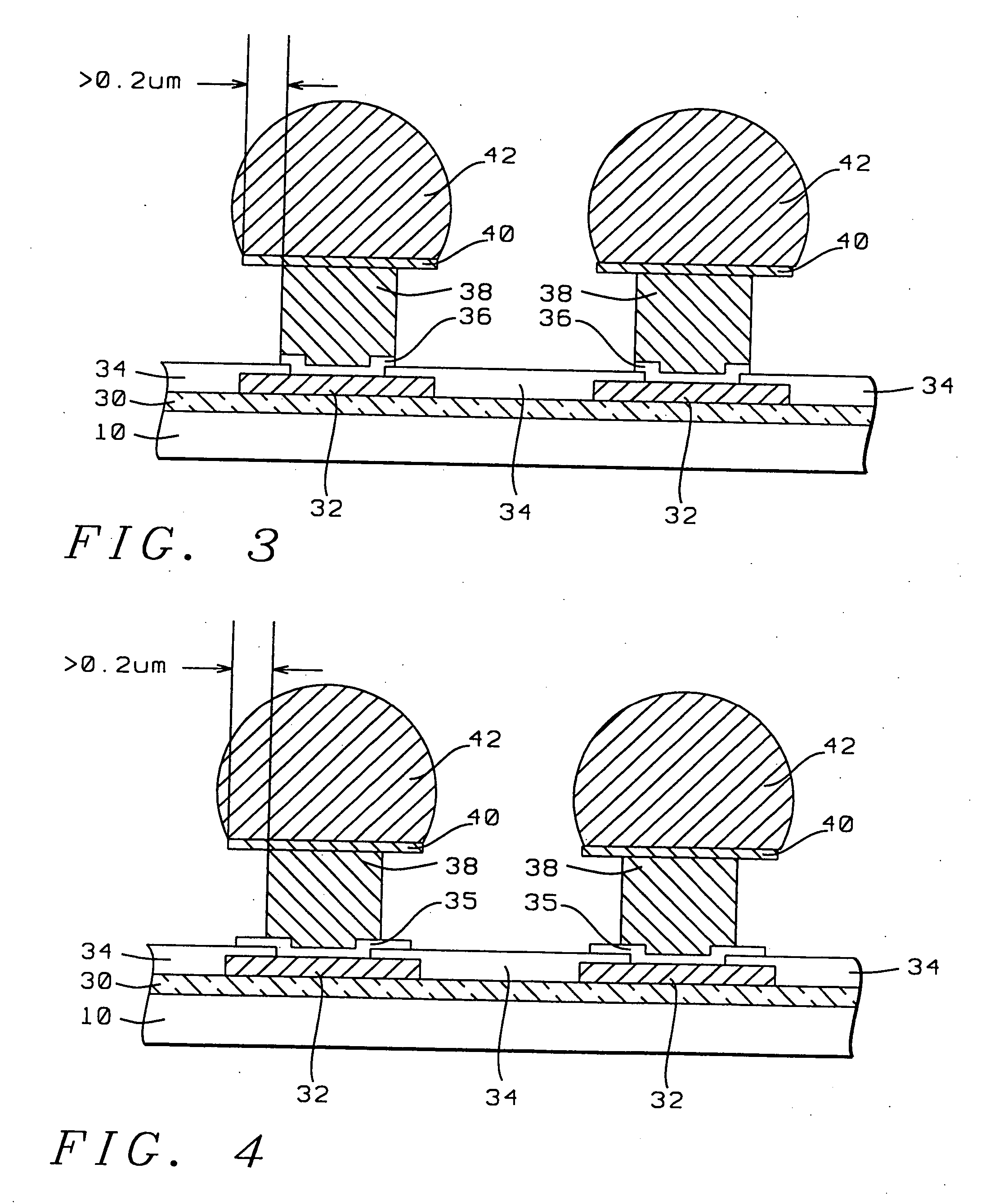

Structure and manufacturing method of a chip scale package

InactiveUS20080088019A1Reduce interconnectionImprove electrical performanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor

A new method and package is provided for the mounting of semiconductor devices that have been provided with small-pitch Input / Output interconnect bumps. Fine pitch solder bumps, consisting of pillar metal and a solder bump, are applied directly to the I / O pads of the semiconductor device, the device is then flip-chip bonded to a substrate. Dummy bumps may be provided for cases where the I / O pads of the device are arranged such that additional mechanical support for the device is required.

Owner:QUALCOMM INC

Semiconductor device and method for manufacturing the same

InactiveUS20090230558A1Reduce partMinimizing damageSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor

The present invention is a method for manufacturing a semiconductor device having a conductor and an insulating film on a substrate, the method including the steps of forming the conductor on the substrate, forming the insulating film on the conductor, removing the insulating film on the conductor, and blowing an organosilane gas and a hydrogen gas to reduce an oxidized region on the conductor, wherein the oxidized region on the conductor is formed when the insulating film is removed.

Owner:TOKYO ELECTRON LTD

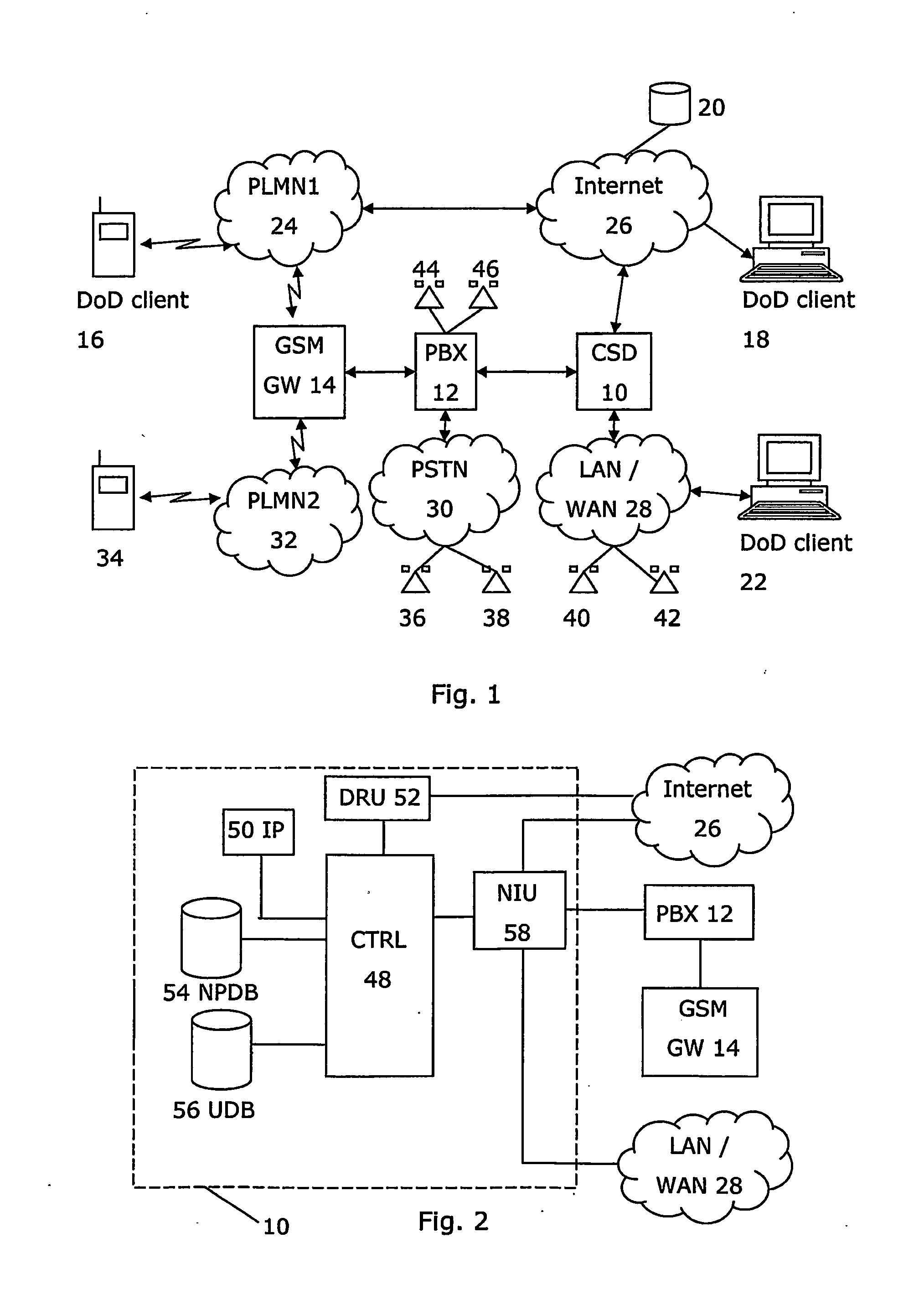

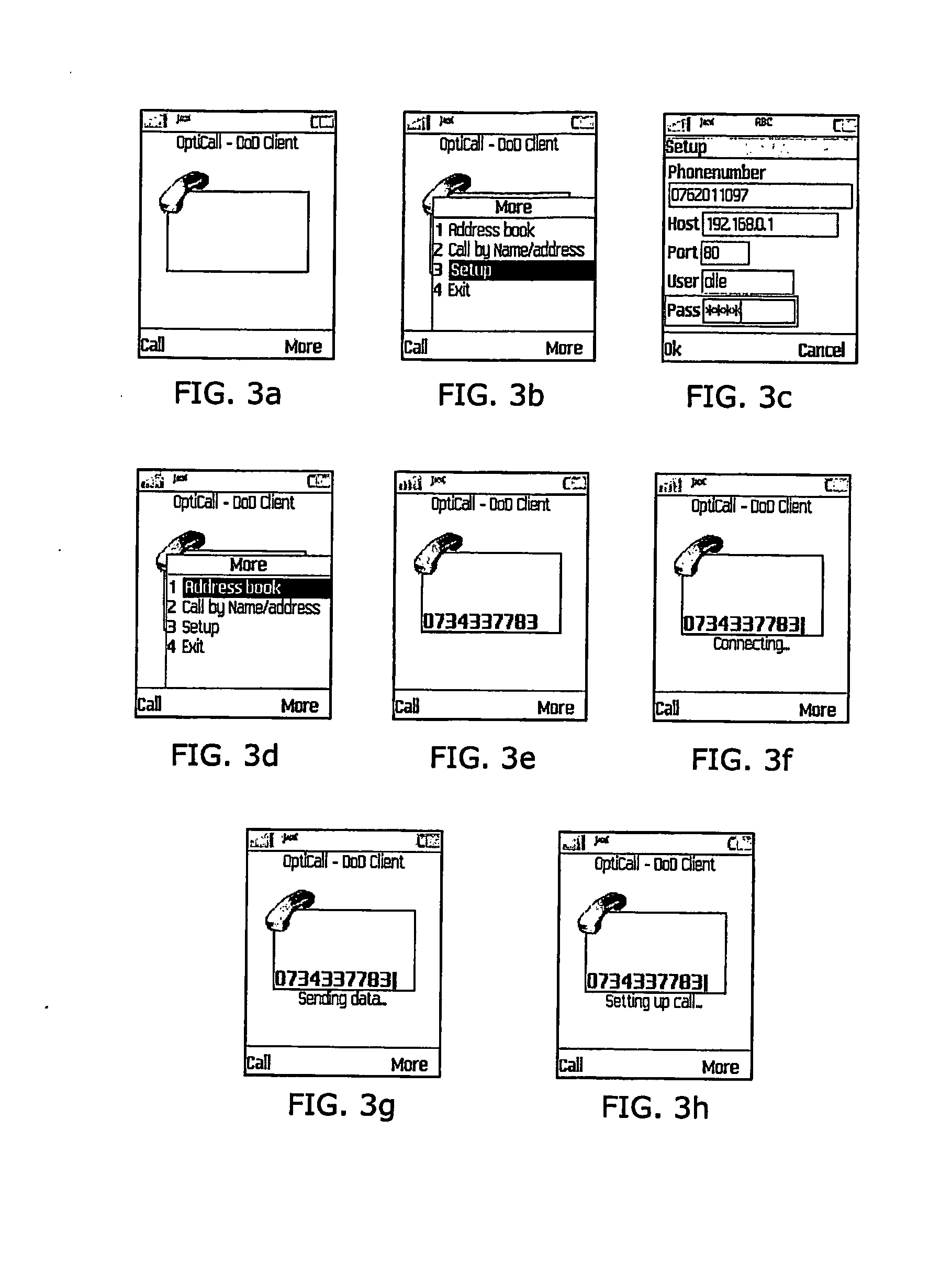

Method, Call Setup Device and Computer Product for Controlling and Setting Up Calls with Reduced Costs

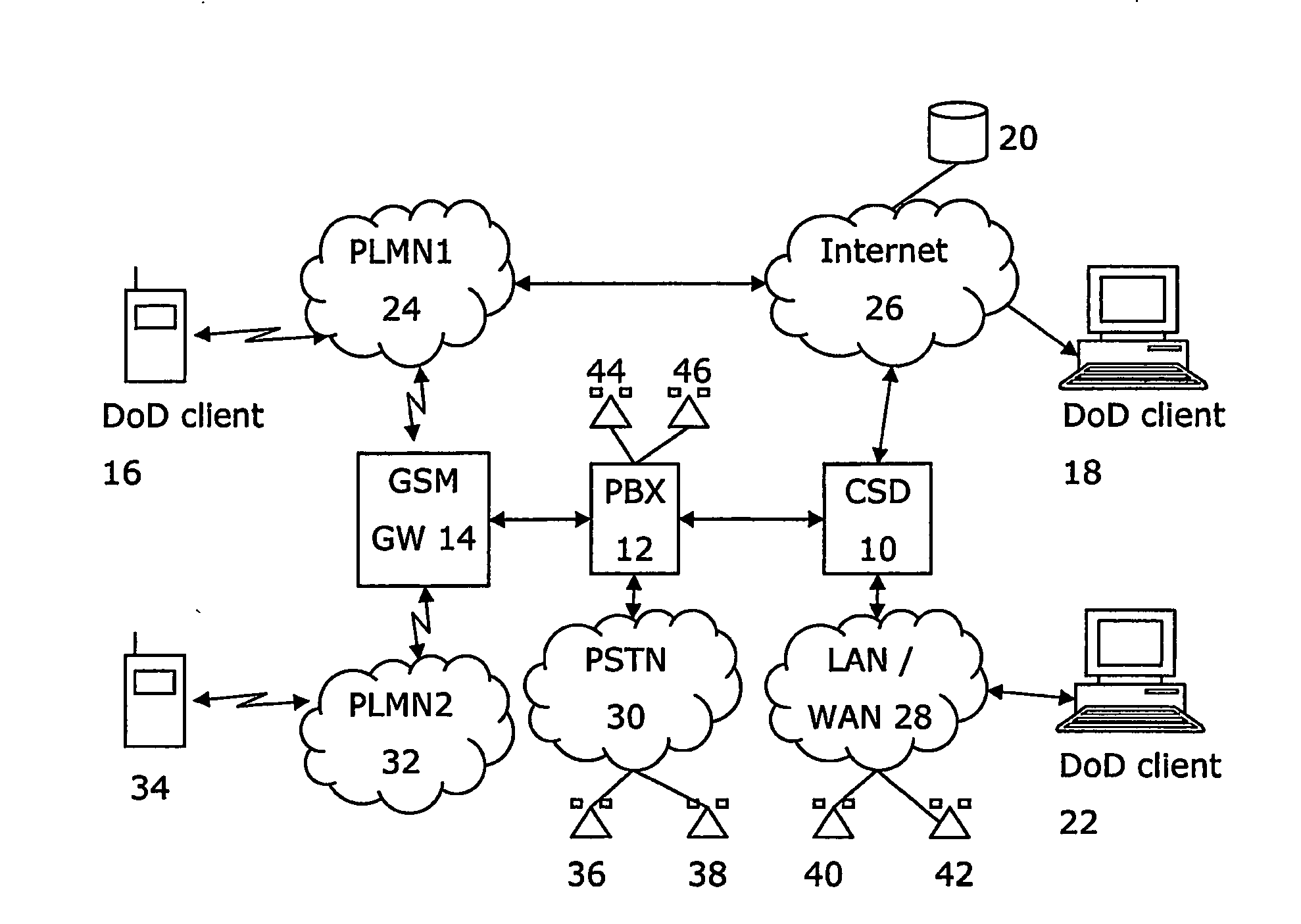

InactiveUS20080119195A1Reduce call costsCost efficientNetwork topologiesManual exchangesInterconnectionCall setup

The invention relates to a method, call setup device (10) and computer program product for controlling telephone call setup for an associated user and having access to different communication networks. The call setup device (10) comprises a data receiving unit (52) receiving a first data message (DM1) from the user comprising callee identifying information and user identifying information, and a control unit (48) having access to call placing units (12, 14, 58), each connected to corresponding networks (24 / 32) and providing telephone call setup via these networks. The control unit analyses the callee and user identifying information, determines a preferred call setup scheme based on said analysis, orders a call placing unit to set up a first telephone call to a user terminal, orders a call placing unit to set up a second telephone call to a callee terminal, and orders an interconnection of the first and the second call.

Owner:OPTICALLER SOFTWARE

Structure and manufacturing method of a chip scale package

InactiveUS20080067677A1Reduce interconnectionImprove electrical performanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor

A new method and package is provided for the mounting of semiconductor devices that have been provided with small-pitch Input / Output interconnect bumps. Fine pitch solder bumps, consisting of pillar metal and a solder bump, are applied directly to the I / O pads of the semiconductor device, the device is then flip-chip bonded to a substrate. Dummy bumps may be provided for cases where the I / O pads of the device are arranged such that additional mechanical support for the device is required.

Owner:QUALCOMM INC

Structure and manufacturing method of a chip scale package

InactiveUS20060163729A1Electrical performance be improveShorten interconnectionSemiconductor/solid-state device detailsSolid-state devicesEngineeringInput/output

A new method and package is provided for the mounting of semiconductor devices that have been provided with small-pitch Input / Output interconnect bumps. Fine pitch solder bumps, consisting of pillar metal and a solder bump, are applied directly to the I / O pads of the semiconductor device, the device is then flip-chip bonded to a substrate. Dummy bumps may be provided for cases where the I / O pads of the device are arranged such that additional mechanical support for the device is required.

Owner:QUALCOMM INC

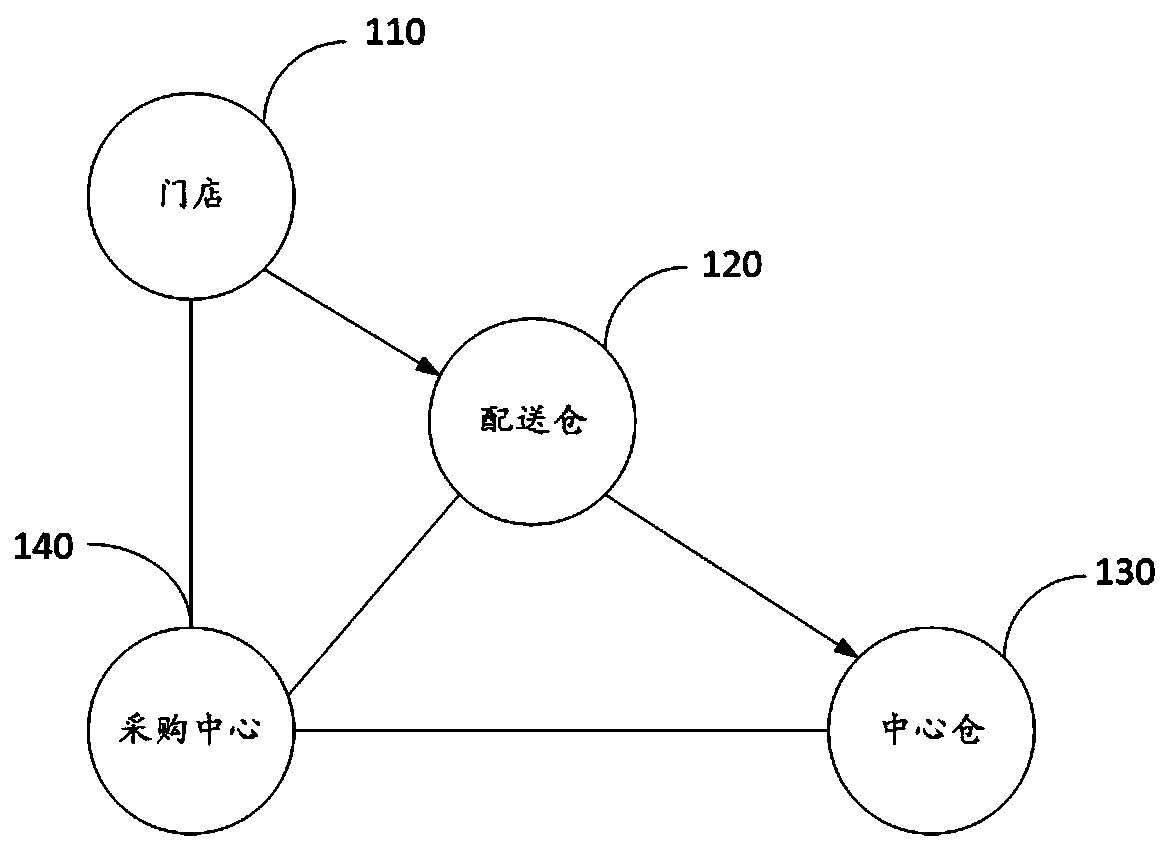

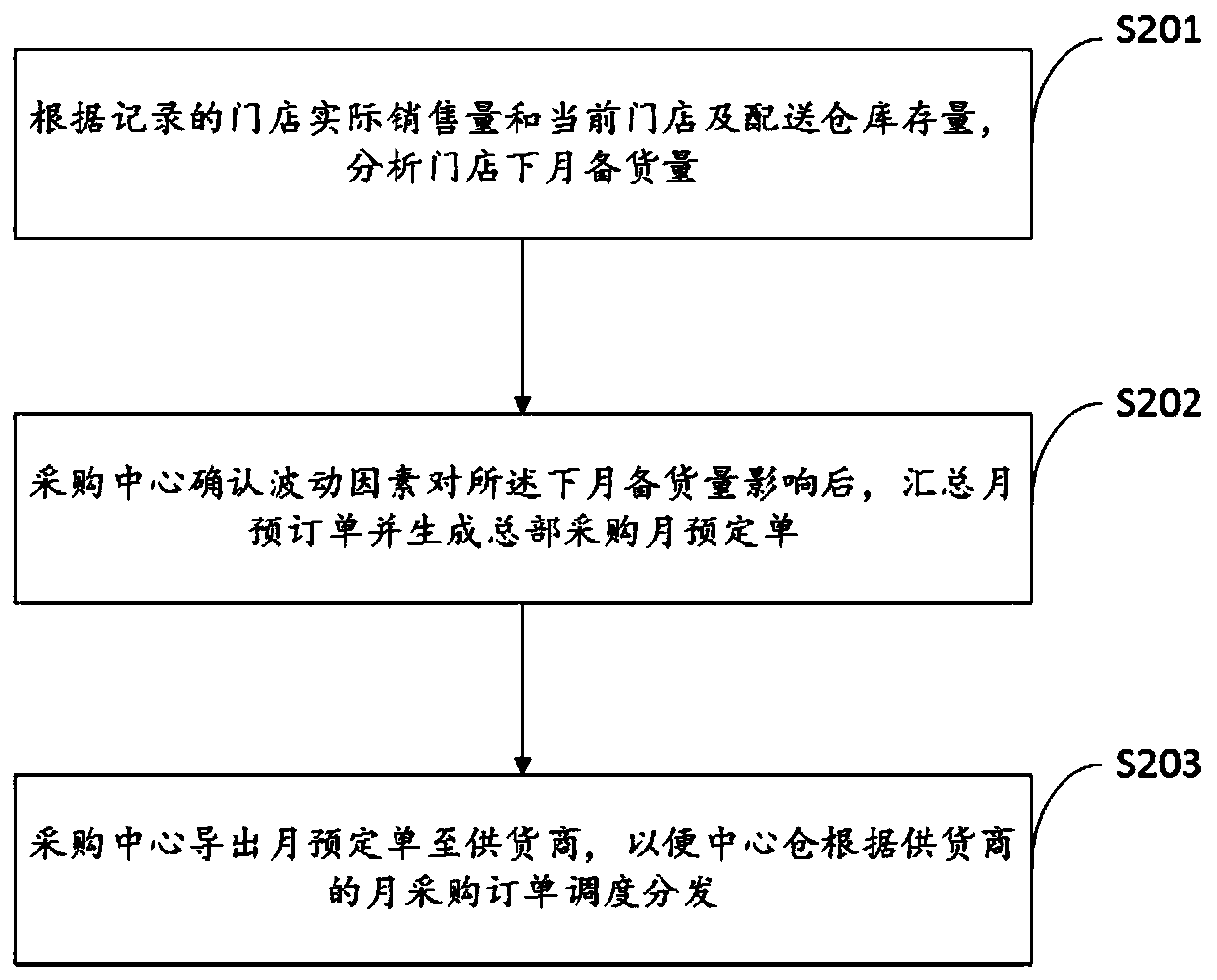

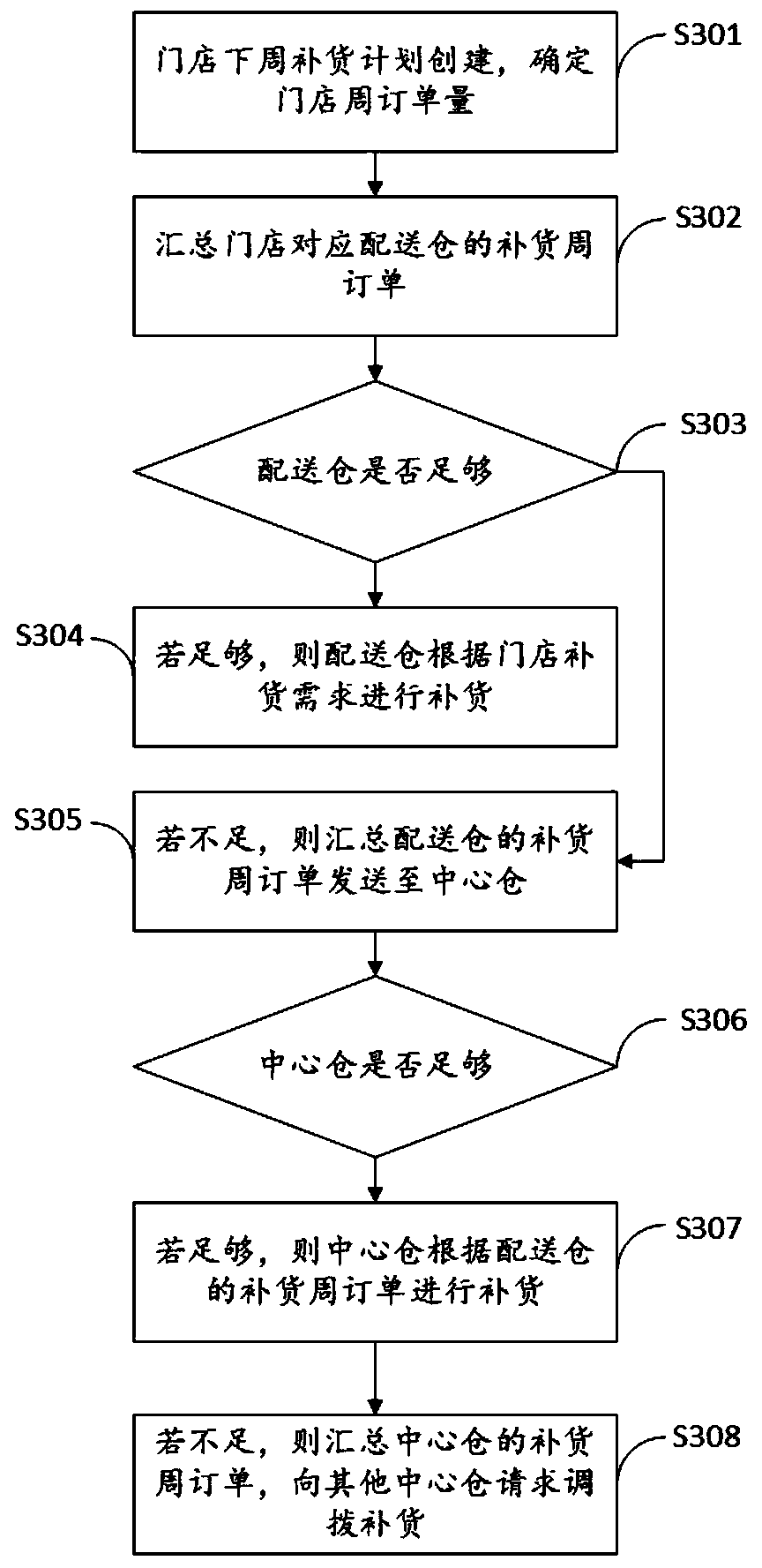

Inventory replenishment scheduling method and system

PendingCN111178797AReduce Replenishment Scheduling ManagementConvenient replenishment scheduling managementLogisticsOperations researchIndustrial engineering

The invention provides an inventory replenishment scheduling method and system, and the method comprises the steps: analyzing the stock amount of a store in the next month according to the recorded actual sales volume of the store and the current stock of the store and a distribution warehouse; after a purchasing center confirms the influence of a fluctuation factor on the next month stock amount,summarizing a month reservation order and generating a headquarters purchasing month reservation order; and enabling the purchasing center to export the month reservation order to a supplier, so thata central warehouse dispatches and distributes the month reservation order according to the month purchasing order of the supplier. By means of the scheme, the problem that deviation is likely to exist in manual intervention in the existing replenishment scheduling process is solved, manual intervention can be reduced, and it is guaranteed that the replenishment scheduling process is reasonable,efficient and accurate.

Owner:武汉微批科技有限公司

Semiconductor device and method for fabricating the same

InactiveUS20070281465A1Inhibition of defect generationReduce interconnectionSemiconductor/solid-state device detailsSolid-state devicesInter layerEngineering

The semiconductor device comprises a lower interconnection part 12 which is formed on a silicon substrate 10 and includes an inter-layer insulation film 36 formed of a low-k film 32 and a hydrophilic insulation film 34 formed on the low-k film 32, and an interconnection layer 44a, 44b buried in interconnection trenches 38a, 38b formed in the inter-layer insulation film 36 and having an interconnection pitch which is a first pitch; and an intermediate interconnection part 14 which is formed on the lower interconnection part 12 and includes an inter-layer insulation film 142 formed of low-k films 136, 140, an interconnection layer 152a, 152b buried in interconnection trenches 146a, 146b formed in the inter-layer insulation film 142 and having an interconnection pitch which is a second pitch larger than the first pitch, and an SiC film 154 formed directly on the low-k film 140 and the interconnection layer 152a, 152b.

Owner:FUJITSU MICROELECTRONICS LTD

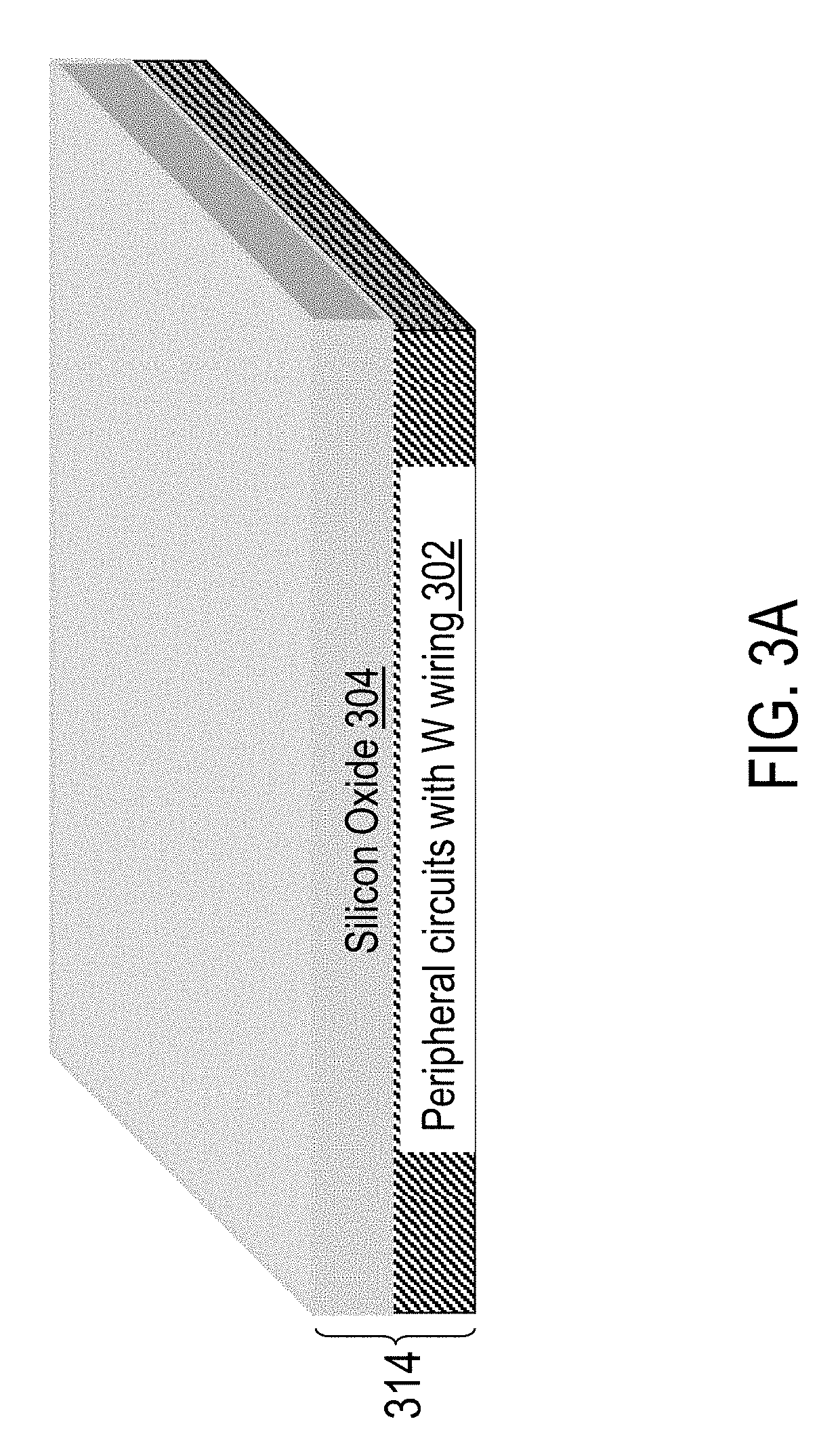

3D semiconductor device

ActiveUS20190237461A1Reduce the impactReduce in quantityTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

A 3D semiconductor device including: a first die, comprising a first die area and a plurality of first die top contacts; a second die, comprising a second die area and a plurality of first bottom contacts; and a third die, comprising a third die area and a plurality of second bottom contacts, wherein said first die area is greater than the sum of said second die area and said third die area, wherein said second die and said third die are both placed on top of said first die laterally with respect to each other, wherein said plurality of first bottom contacts are connected to said first die top contacts, and wherein said plurality of second bottom contacts are connected to said first die top contacts.

Owner:MONOLITHIC 3D

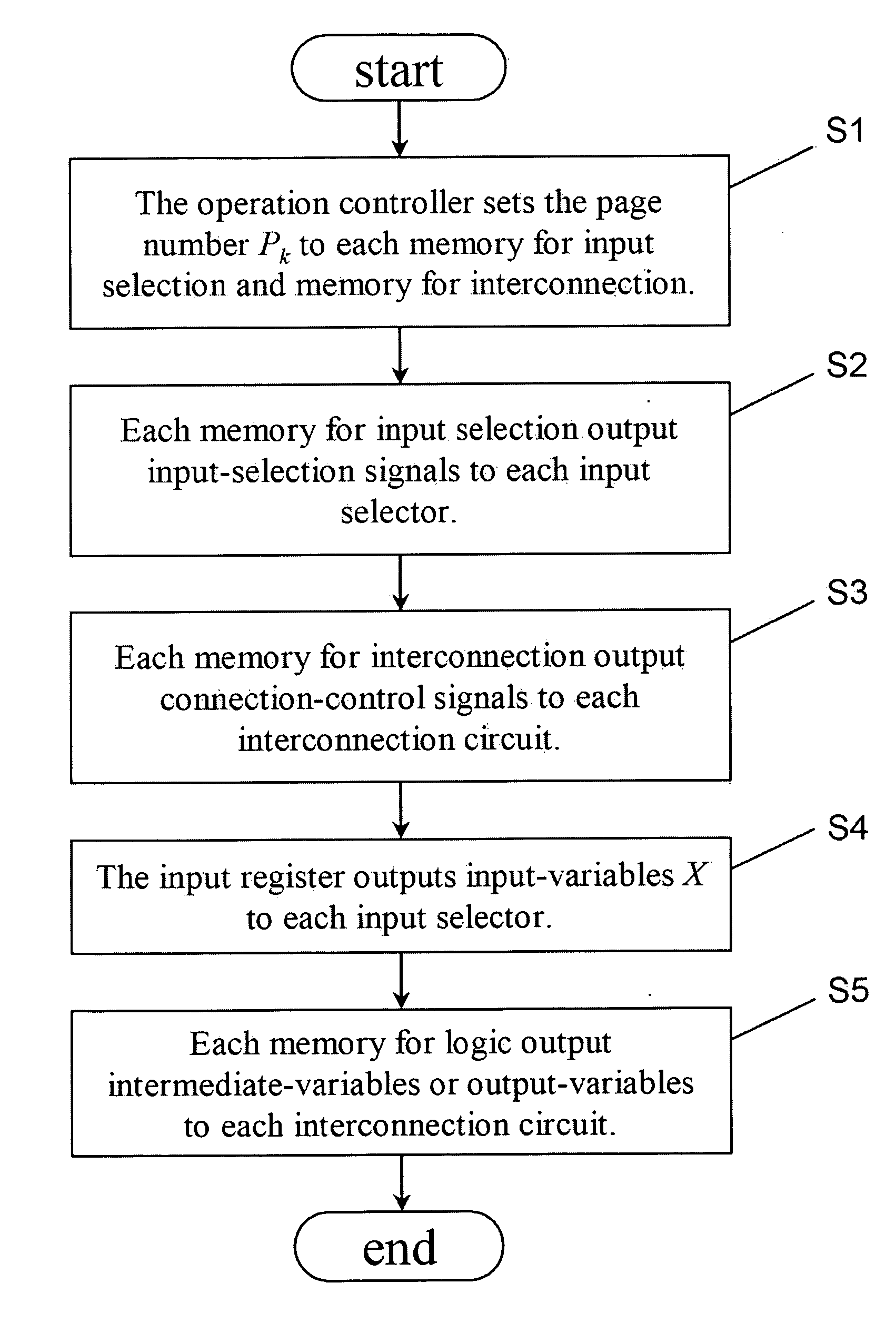

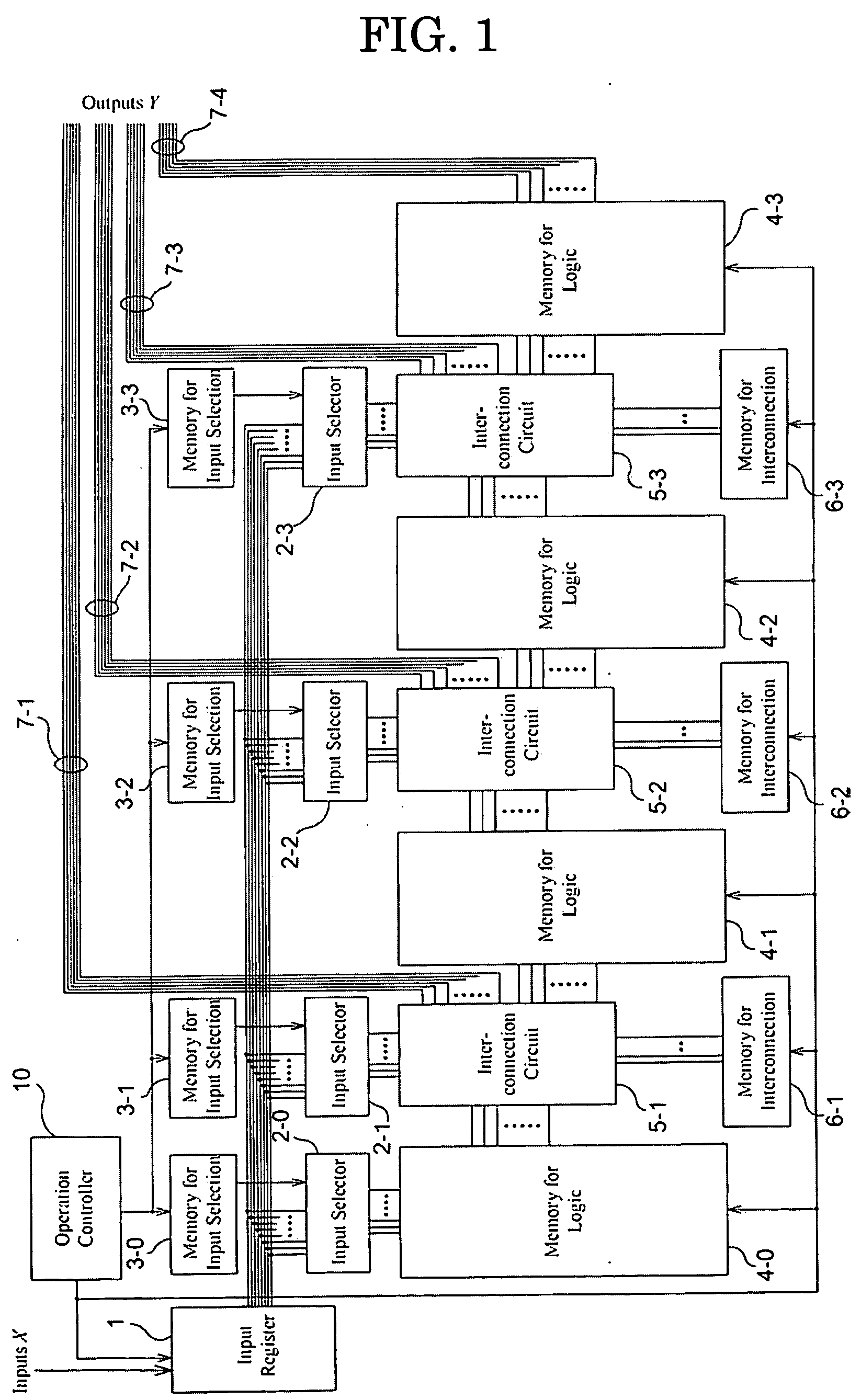

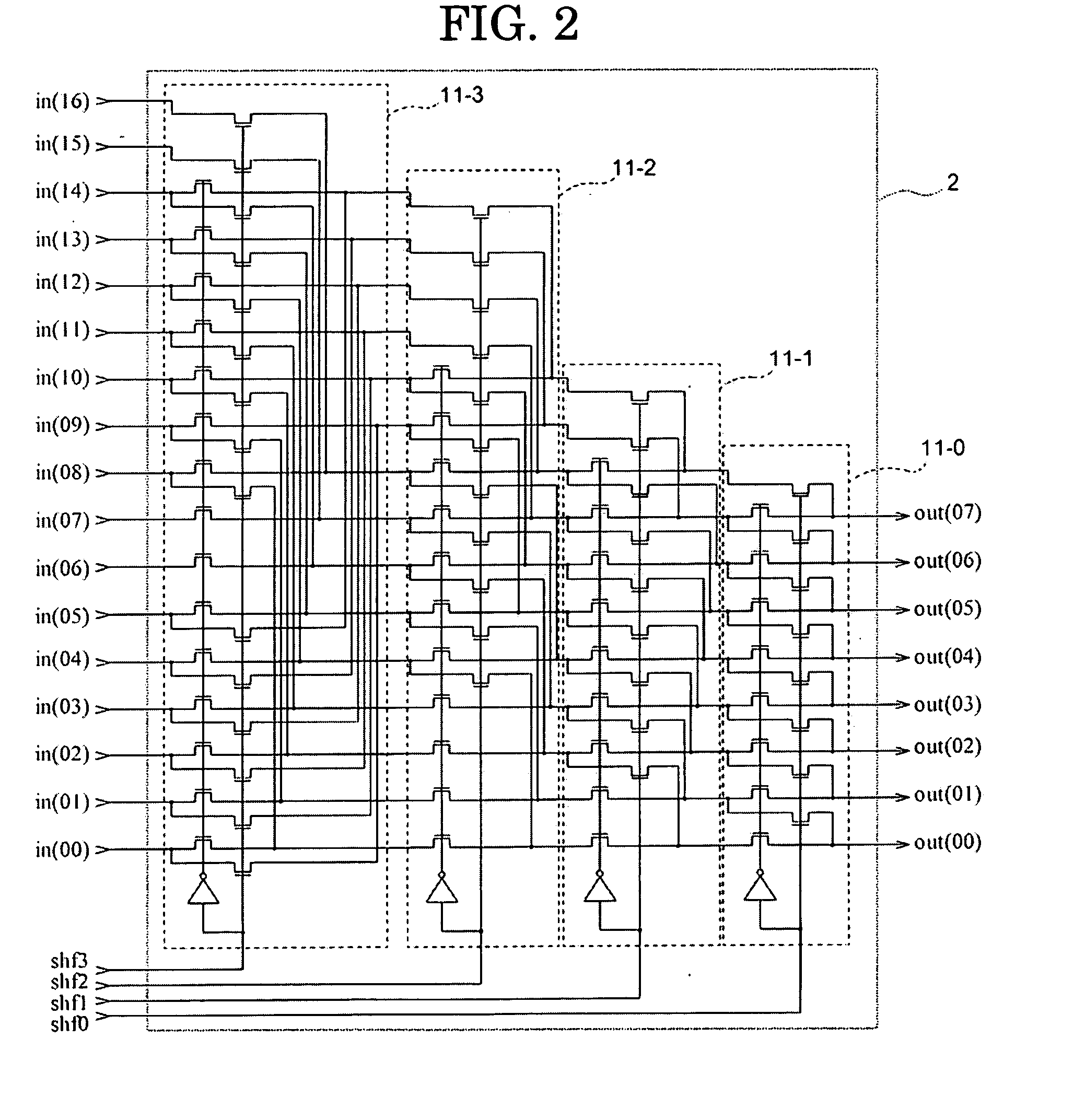

Programmable Logic Device

InactiveUS20080204072A1Reduce number of input lineSmall sizeProgramme controlSolid-state devicesProgrammable logic deviceEngineering

The invention relates to a connector (10) for connecting welding torch where the connector comprises a connector body (12) made of electrically insulating material, a cylindrical current transferring body (30) fitted on the cylindrical front part (13) of the connector body (12), made of electrically conductive material, where the current transferring body (30) has a threaded surface (32) and a side contact surface (35) besides the threaded surface (32) on its side surface, a threaded bore (37) on the side contact surface (35) for fixing current cable with screwed joint and a frontal contact surface (33), further an attachment bracket (60), made of electrically insulating plastic, the attachment bracket (60) has a sleeve part (62), which encircles space apart the threaded surface (32) and the sleeve part (62) has a flange (64) protruding from its front part for fixing, the flange (64) is provided with one or more holes (65) in it. The connector body (12) has a rear limiting surface (18) out of which a stem (75) projects, the stem (75) has a bore hole (77) in its centre line into which a liner (54) for wire guide is fixed, which liner leads in a nest (21) for fitting wire guide conduit end formed on the front surface (15) of the connector body (12), the current transferring body (30) has a pot-shape, having a bottom (39) in which there are openings (41, 42, 43) opening onto the nests (21, 23) formed on the front surface (15), further there is a positioning hole (27) in the side of the connector body (12) in the extension of the threaded bore (37) and the attachment bracket (60) has a conically narrowed part (68) projecting rearwards from the sleeve part (62), and on the inner surface near the end of the narrowed part (68) there is at least one screw thread (72) which The invention relates to a connector (10) for connecting welding torch where the connector comprises a connector body (12) made of electrically insulating material, a cylindrical current transferring body (30) fitted on the cylindrical front part (13) of the connector body (12), made of electrically conductive material, where the current transferring body (30) has a threaded surface (32) and a side contact surface (35) besides the threaded surface (32) on its side surface, a threaded bore (37) on the side contact surface (35) for fixing current cable with screwed joint and a frontal contact surface (33), further an attachment bracket (60), made of electrically insulating plastic, the attachment bracket (60) has a sleeve part (62), which encircled space apart the threaded surface (32) and the sleeve part (62) has a flange (64) protruding from its front part for fixing,—the flange (64) is provided with one or more holes (65) in it. The connector body (12) has a rear limiting surface (18) out of which a stem (75) projects, the stem (75) has a bore hole (77) in its centre line into which a liner (54) for wire guide is fixed, which liner leads in a nest (21) for fitting wire guide conduit end formed on the front surface (15) of the connector body (12), the current transferring body (30) has a pot-shape, having a bottom (39) in which there are openings (41, 42, 43) opening onto the nests (21, 23) formed on the front surface (15), fu

Owner:KITAKYUSHU FOUND FOR THE ADVANCEMENT OF IND

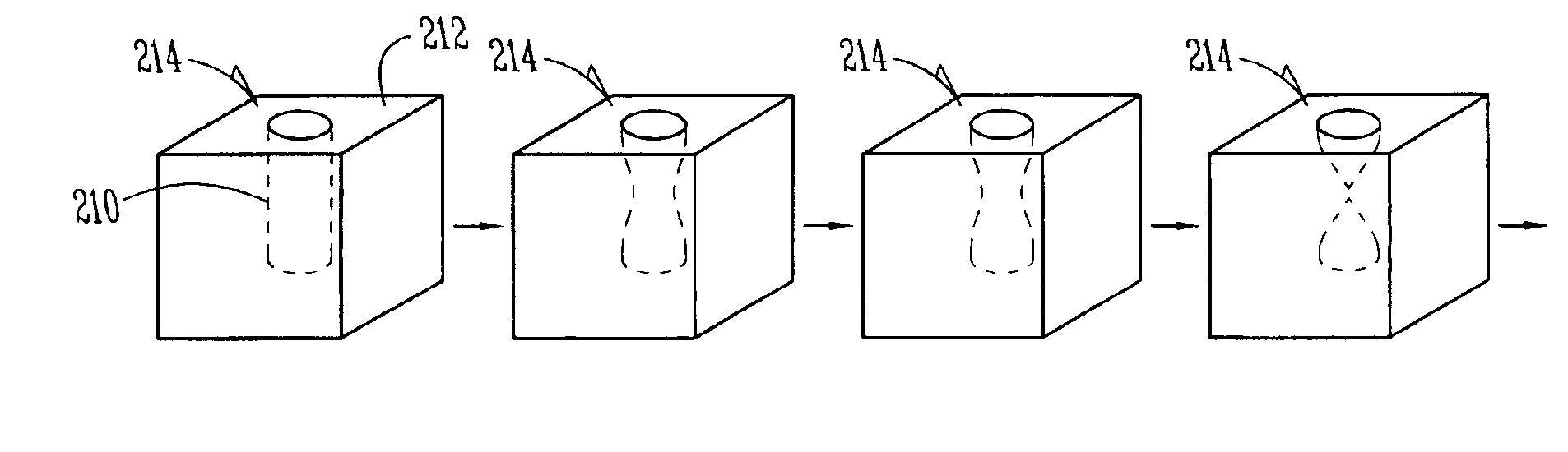

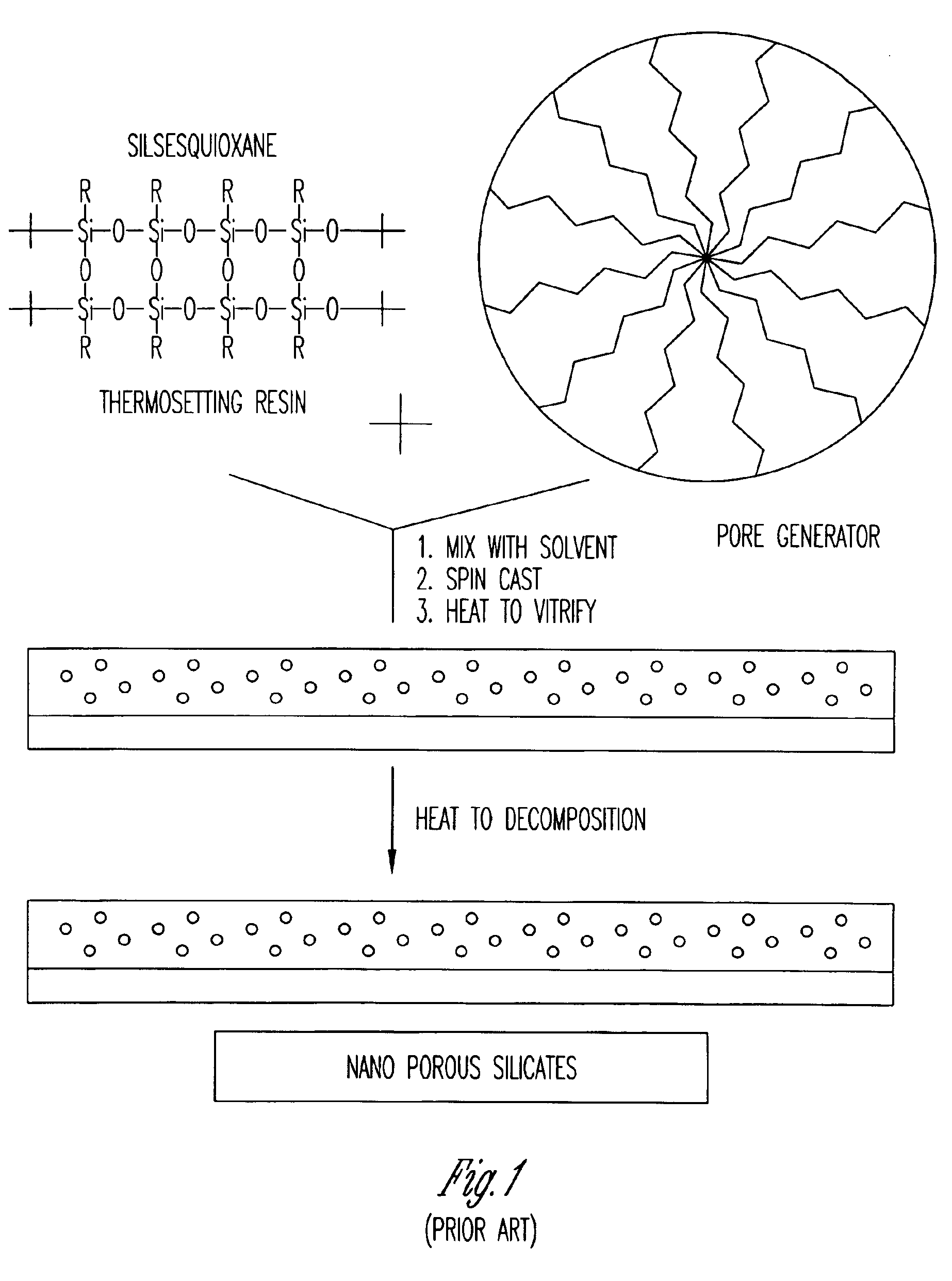

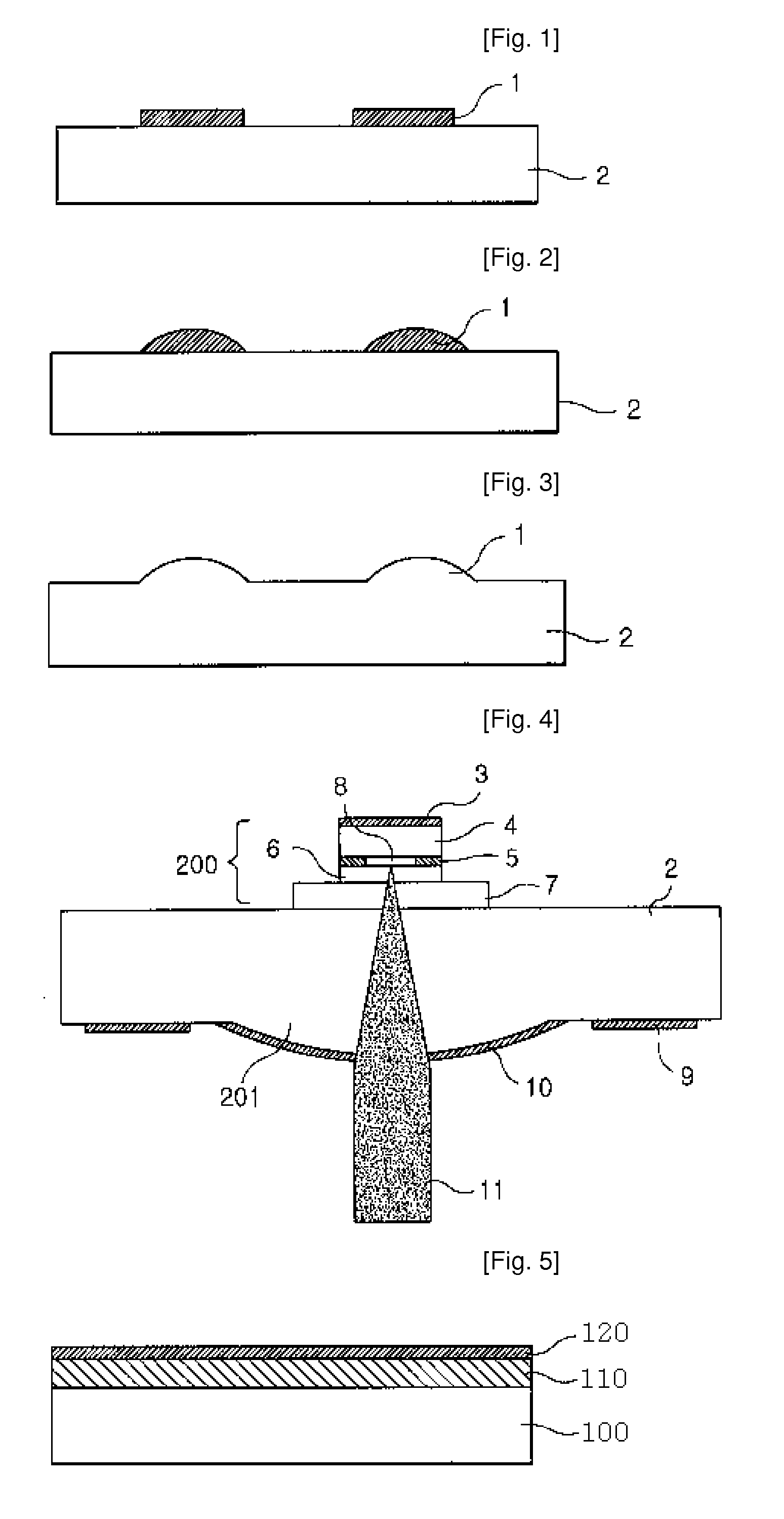

Low k interconnect dielectric using surface transformation

InactiveUS7132348B2Relieve stressEasy to prepareSemiconductor/solid-state device detailsSolid-state devicesSolid structureEngineering

Systems, devices and methods are provided to improve performance of integrated circuits by providing a low-k insulator. One aspect is an integrated circuit insulator structure. One embodiment includes a solid structure of an insulator material, and a precisely determined arrangement of at least one void formed within the solid structure which lowers an effective dielectric constant of the insulator structure. One aspect is a method of forming a low-k insulator structure. In one embodiment, an insulator material is deposited, and a predetermined arrangement of at least one hole is formed in a surface of the insulator material. The insulator material is annealed such that the low-k dielectric material undergoes a surface transformation to transform the arrangement of at least one hole into predetermined arrangement of at least one empty space below the surface of the insulator material. Other aspects are provided herein.

Owner:MICRON TECH INC

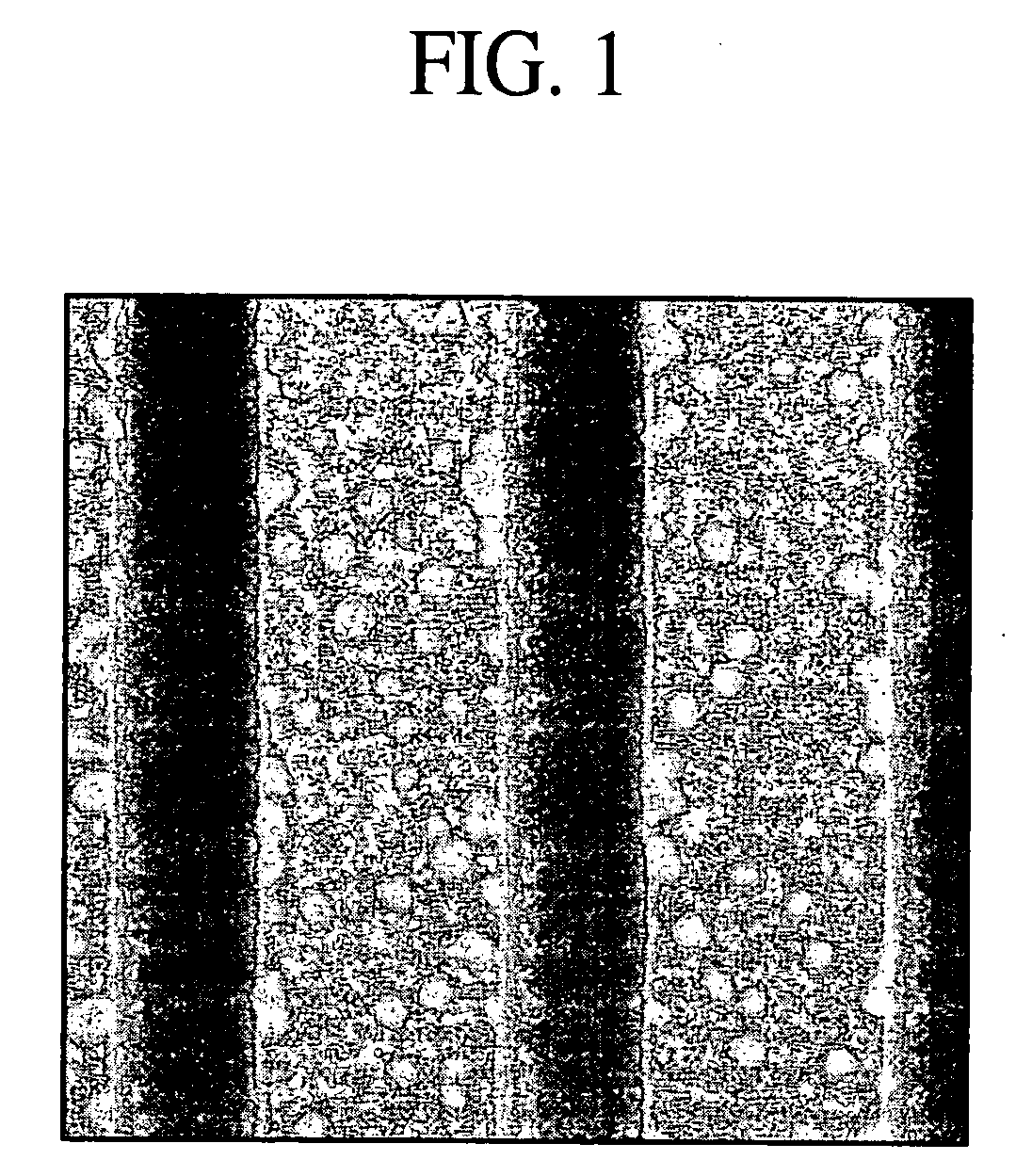

Method for Fabricating Micro-Lens and Micro-Lens Integrated Optoelectronic Devices Using Selective Etch of Compound Semiconductor

InactiveUS20090068775A1Improve characteristicSimplify fabrication processSemiconductor/solid-state device manufacturingLensMicrolensOpto electronic

Provided are a method of fabricating a microlens using selective etching of a compound semi-conductor and a method of fabricating a photoelectric device having the microlens. The formation of the microlens includes patterning a compound semiconductor layer and removing a lateral surface of the compound semiconductor layer to form a roughly hemispheric lens. The lateral surface of the compound semiconductor layer is removed by a digital alloy method. In particular, the lateral surface of the compound semiconductor layer is removed by a wet etching process.

Owner:GWANGJU INST OF SCI & TECH +1

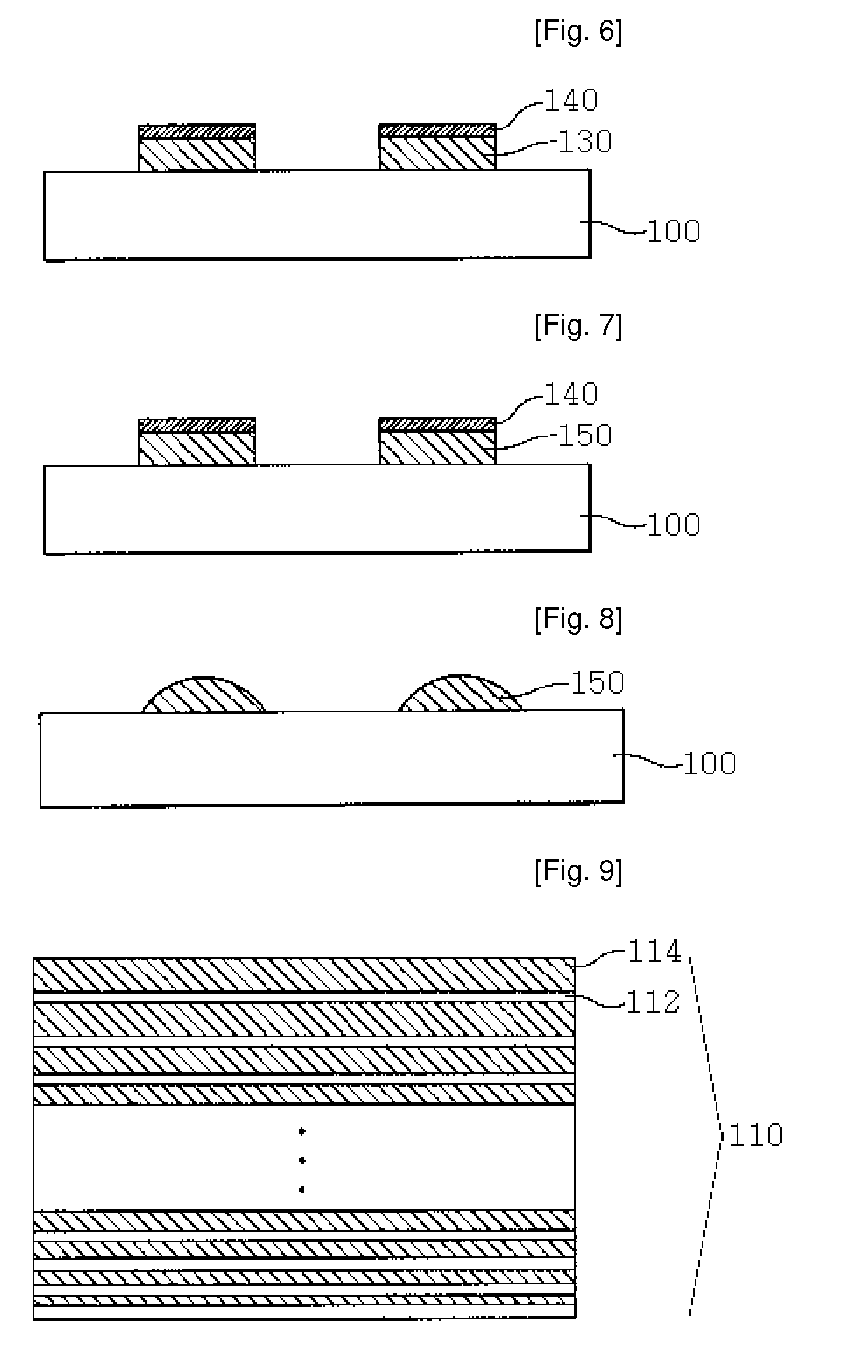

Semiconductor device and method for fabricating the same

InactiveUS20050093160A1Inhibition of defect generationReduce interconnectionSemiconductor/solid-state device detailsSolid-state devicesInter layerInterconnection

The semiconductor device comprises a lower interconnection part 12 which is formed on a silicon substrate 10 and includes an inter-layer insulation film 36 formed of a low-k film 32and a hydrophilic insulation film 34 formed on the low-k film 32, and an interconnection layer 44a, 44b buried in interconnection trenches 38a, 38b formed in the inter-layer insulation film 36 and having an interconnection pitch which is a first pitch; and an intermediate interconnection part 14 which is formed on the lower interconnection part 12 and includes an inter-layer insulation film 142 formed of low-k films 136, 140, an interconnection layer 152a, 152b buried in interconnection trenches 146a, 146b formed in the inter-layer insulation film 142 and having an interconnection pitch which is a second pitch larger than the first pitch, and an SiC film 154 formed directly on the low-k film 140 and the interconnection layer 152a, 152b.

Owner:FUJITSU SEMICON LTD