Patents

Literature

116 results about "Integrated circuit interconnect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

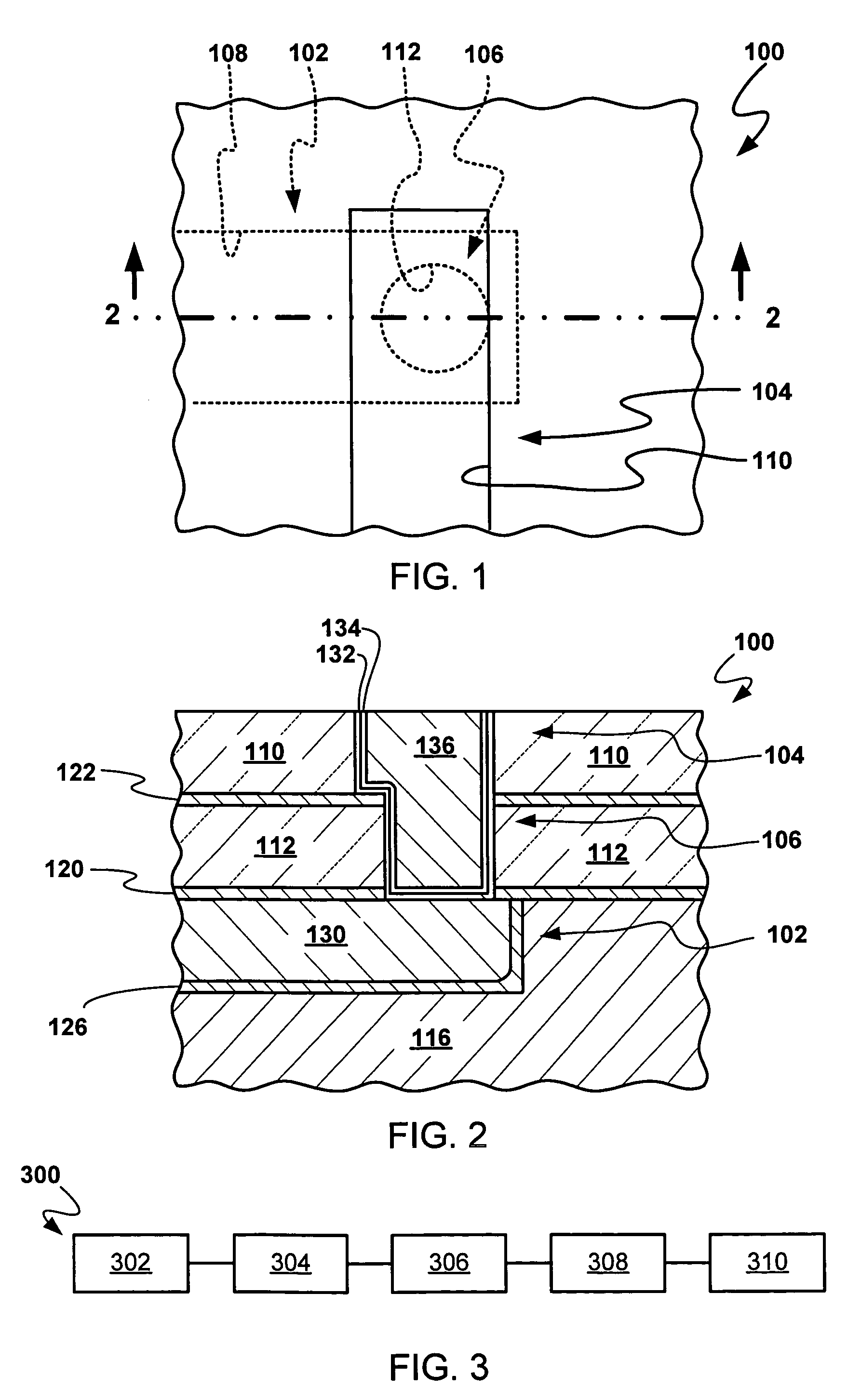

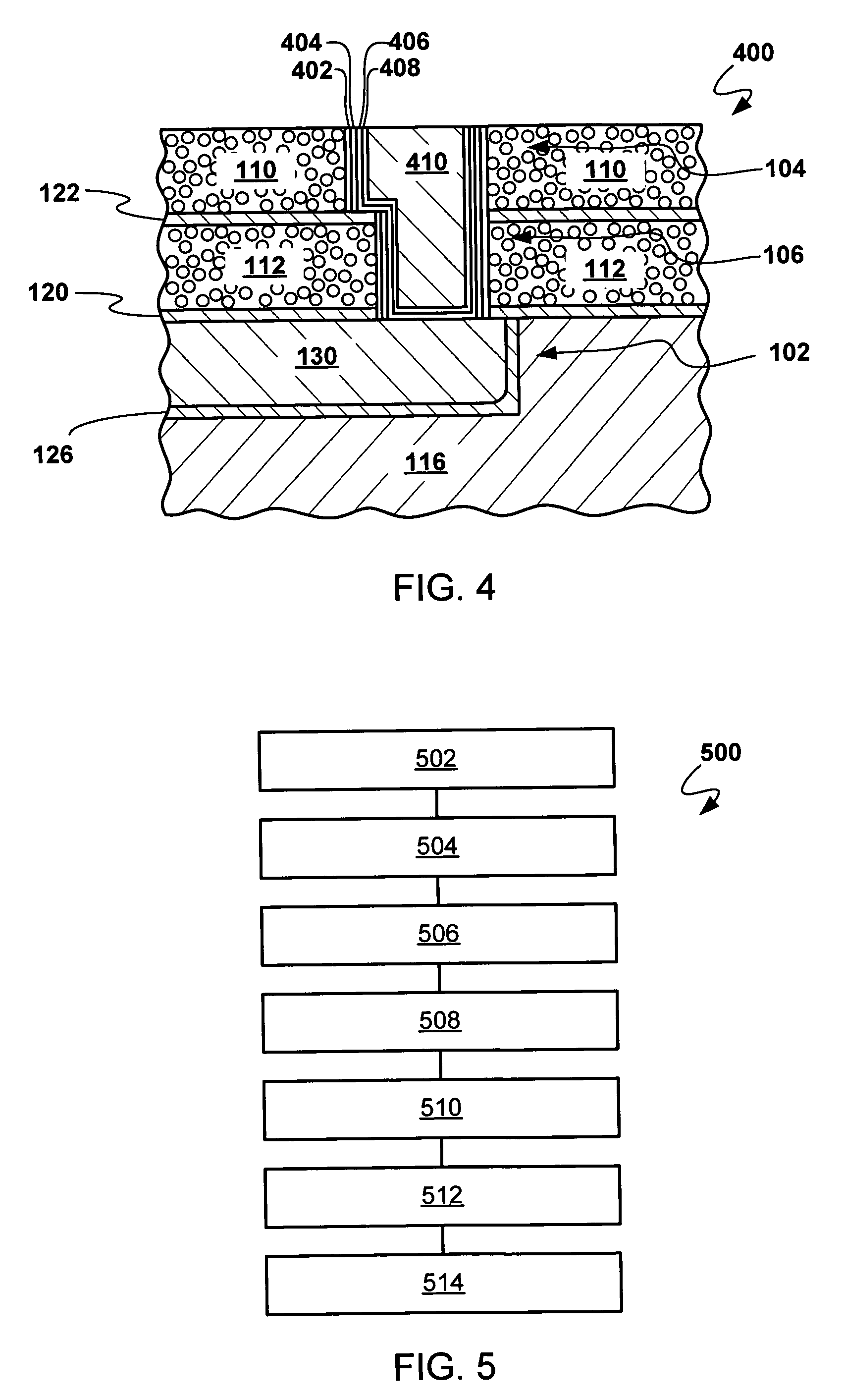

Cleaning processes in the formation of integrated circuit interconnect structures

InactiveUS20080124919A1Small shiftDecreased trench enlargementSemiconductor/solid-state device manufacturingRemote plasmaIntegrated circuit interconnect

A method for fabricating an integrated circuit includes providing a substrate, forming a low-k dielectric layer over the substrate, etching the low-k dielectric layer to form an opening in the low-k dielectric layer wherein an underlying metal is exposed through the opening, performing a remote plasma treatment to the substrate wherein a plasma used for the remote plasma treatment is generated from a plasma generator separated from a chamber in which the substrate is located, forming a diffusion barrier layer in the opening, and filling the opening with a conductive material. The method preferably includes an in-situ plasma treatment in a same chamber as the step of etching the low-k dielectric layer.

Owner:TAIWAN SEMICON MFG CO LTD

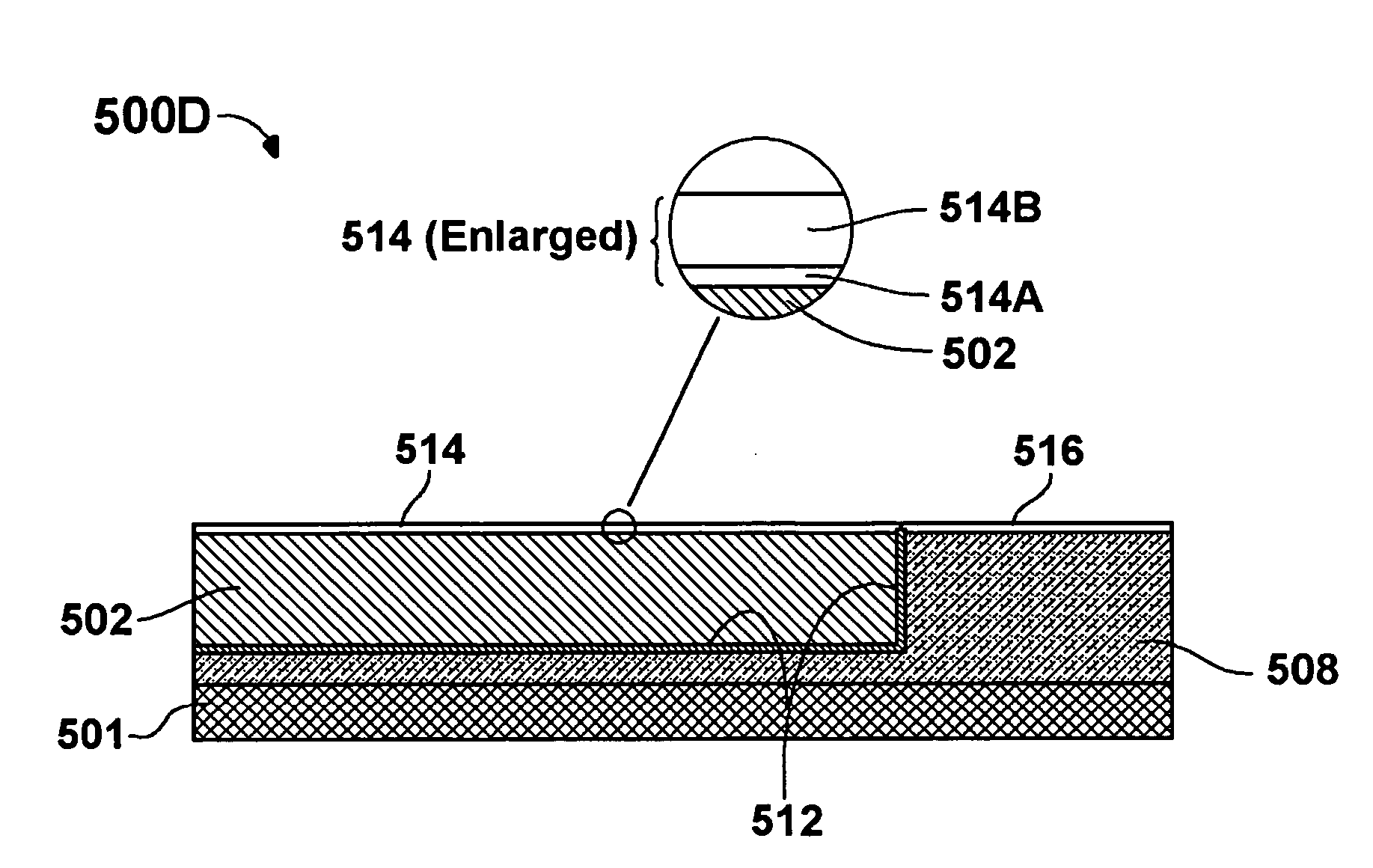

Copper interconnect wiring and method of forming thereof

ActiveUS20060105570A1Electric discharge tubesSemiconductor/solid-state device detailsCopper interconnectIntegrated circuit interconnect

Capping layer or layers on a surface of a copper interconnect wiring layer for use in interconnect structures for integrated circuits and methods of forming improved integration interconnection structures for integrated circuits by the application of gas-cluster ion-beam processing. Reduced copper diffusion and improved electromigration lifetime result and the use of selective metal capping techniques and their attendant yield problems are avoided.

Owner:TEL EPION

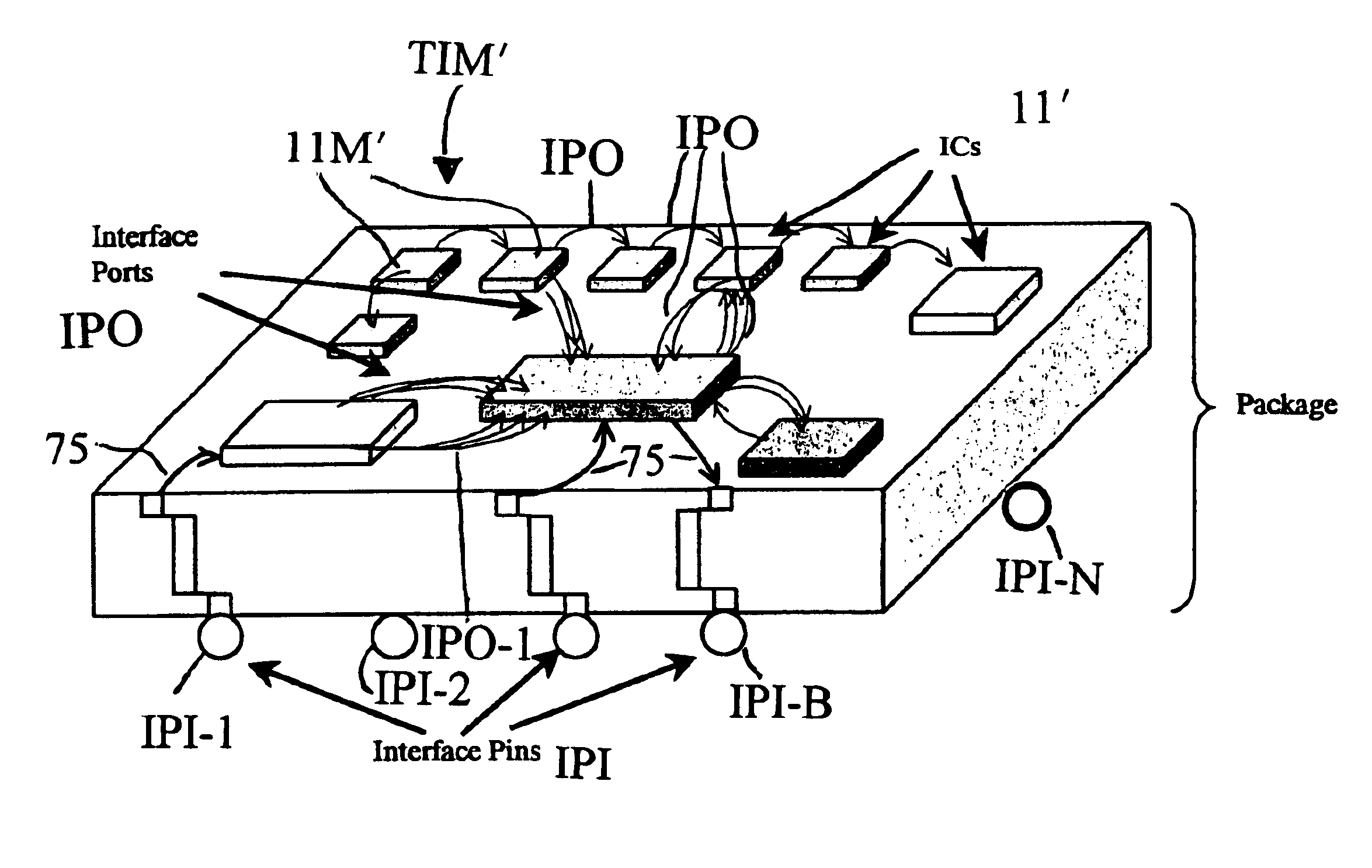

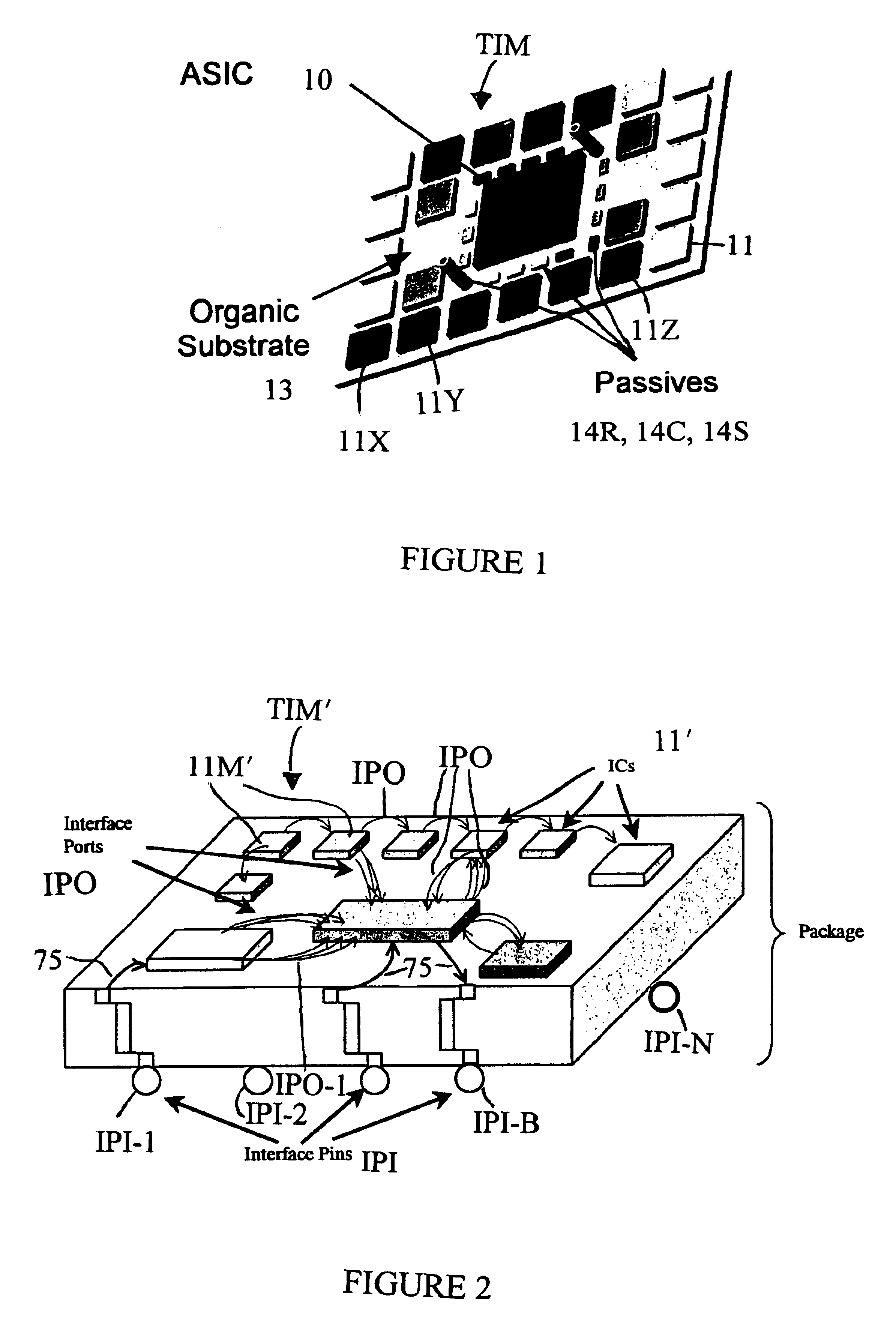

Tailored interconnect module

InactiveUS6908314B2Improve scalabilityMinimize the numberSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit interconnectComputer module

An integrated circuit interconnect module for reducing interconnections between integrated circuit chips MOUNTED ON a support substrate. At least one primary integrated circuit (IC) device chip and a plurality of interacting peripheral integrated chip devices. The interconnect module including a plurality of interface pins, each integrated circuit device having a plurality of interface ports. At least one interface port of which is connected to another one of said plurality of integrated circuit devices, at least one of said integrated circuit devices having an interface port connected to an interface pin whereby the majority of nodes on the interacting peripheral devices are adapted to interface with nodes of the primary IC devices in such a way as to condense the number of nets so that the total number of nodes connected to external pins is minimized.

Owner:ALCATEL LUCENT SAS

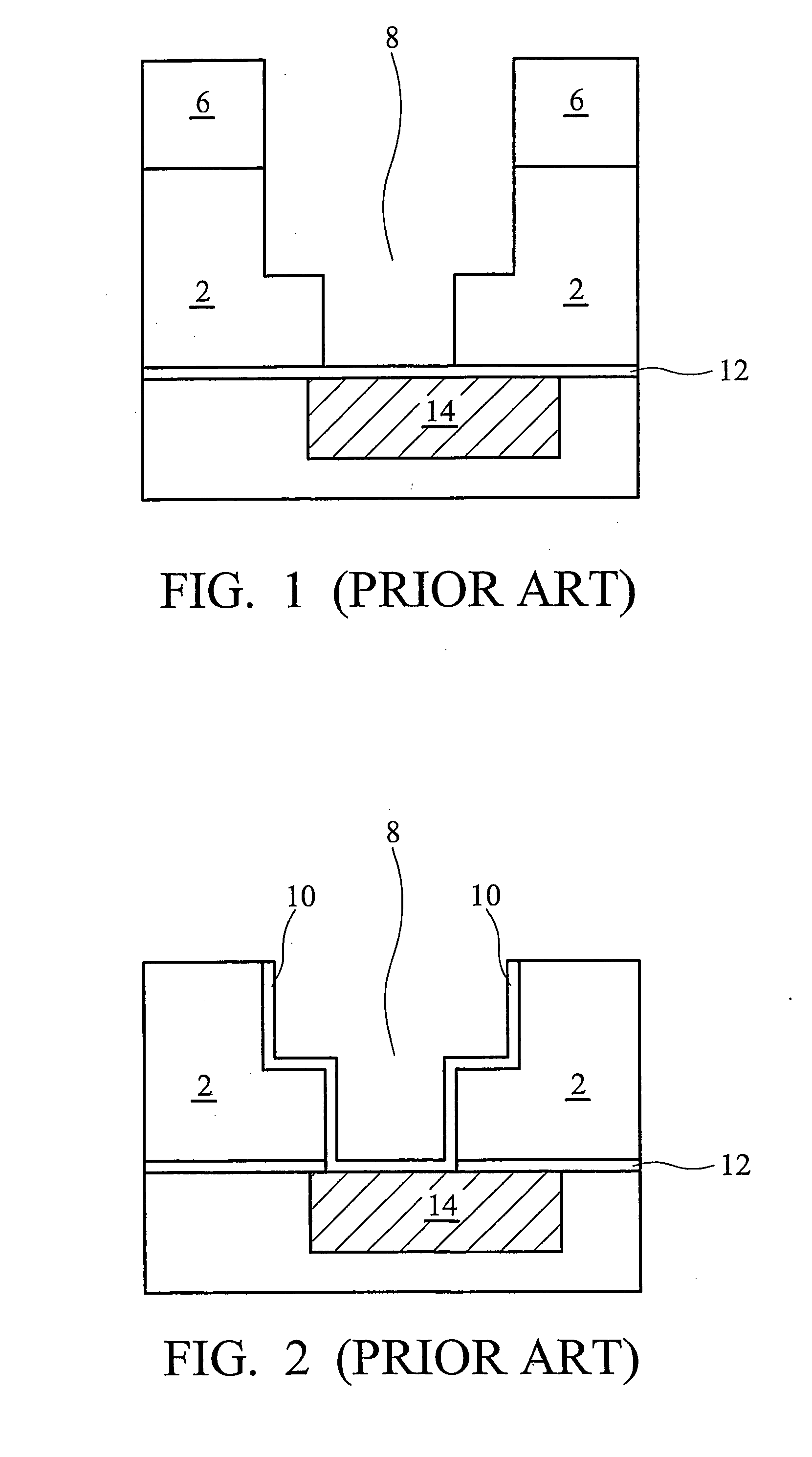

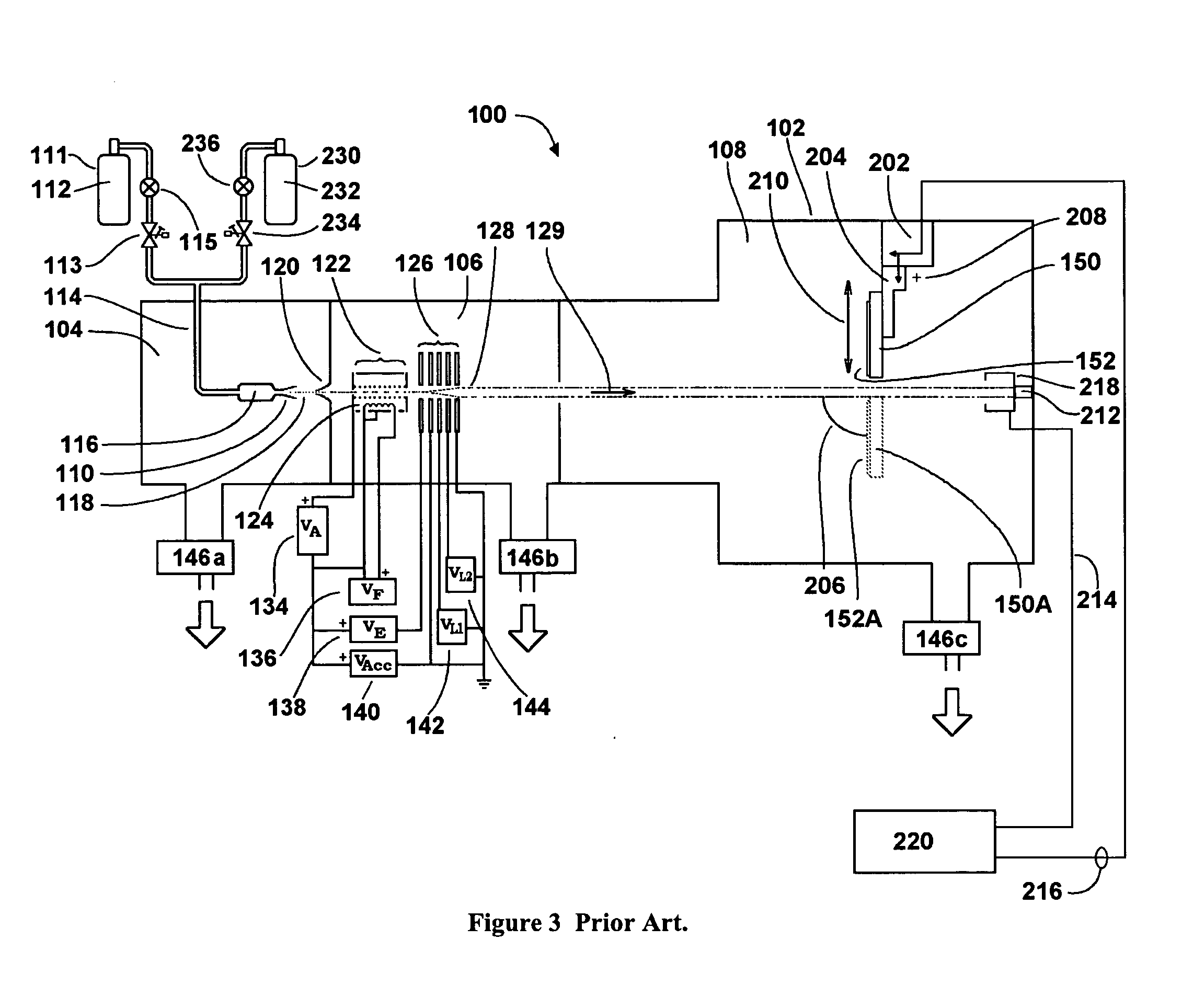

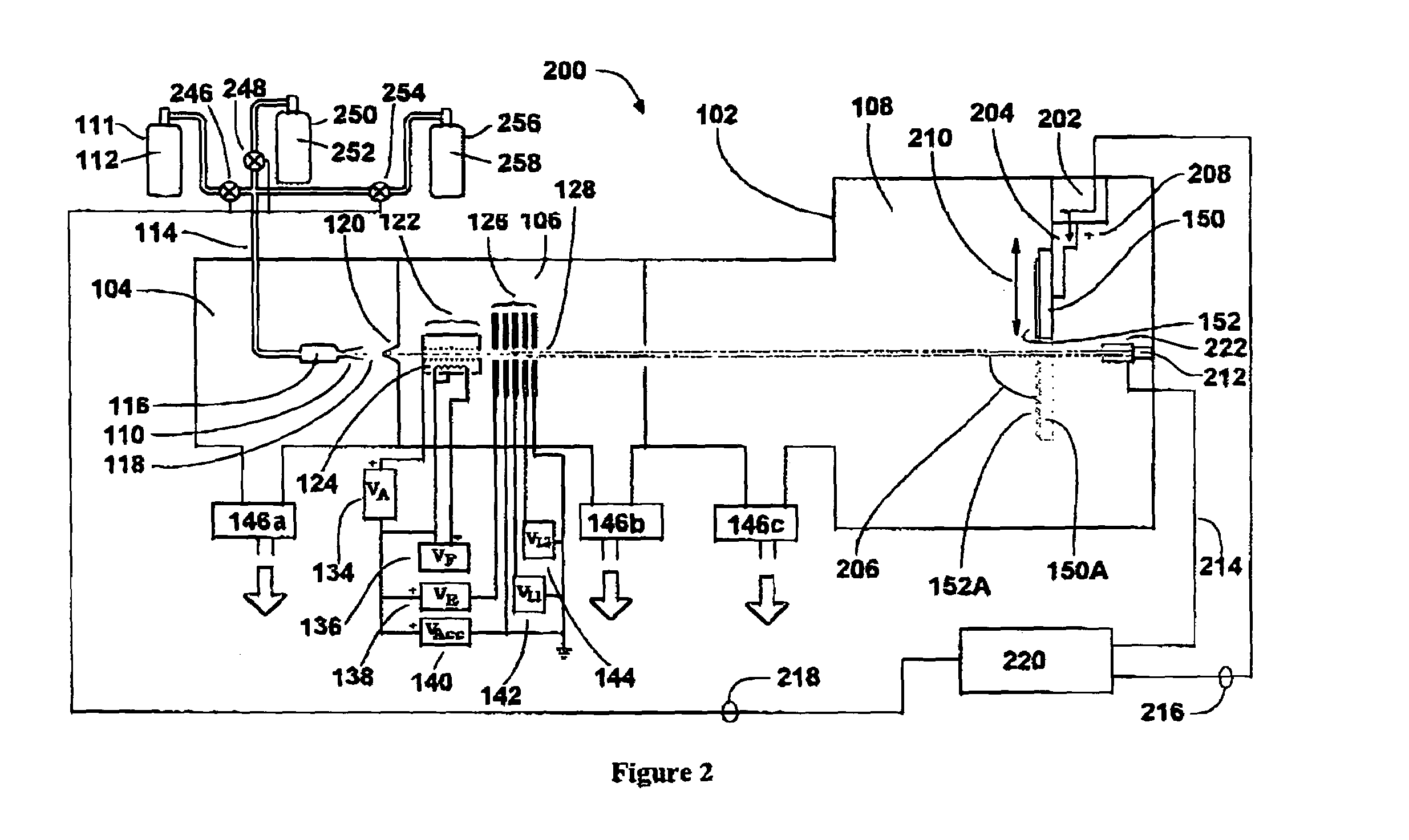

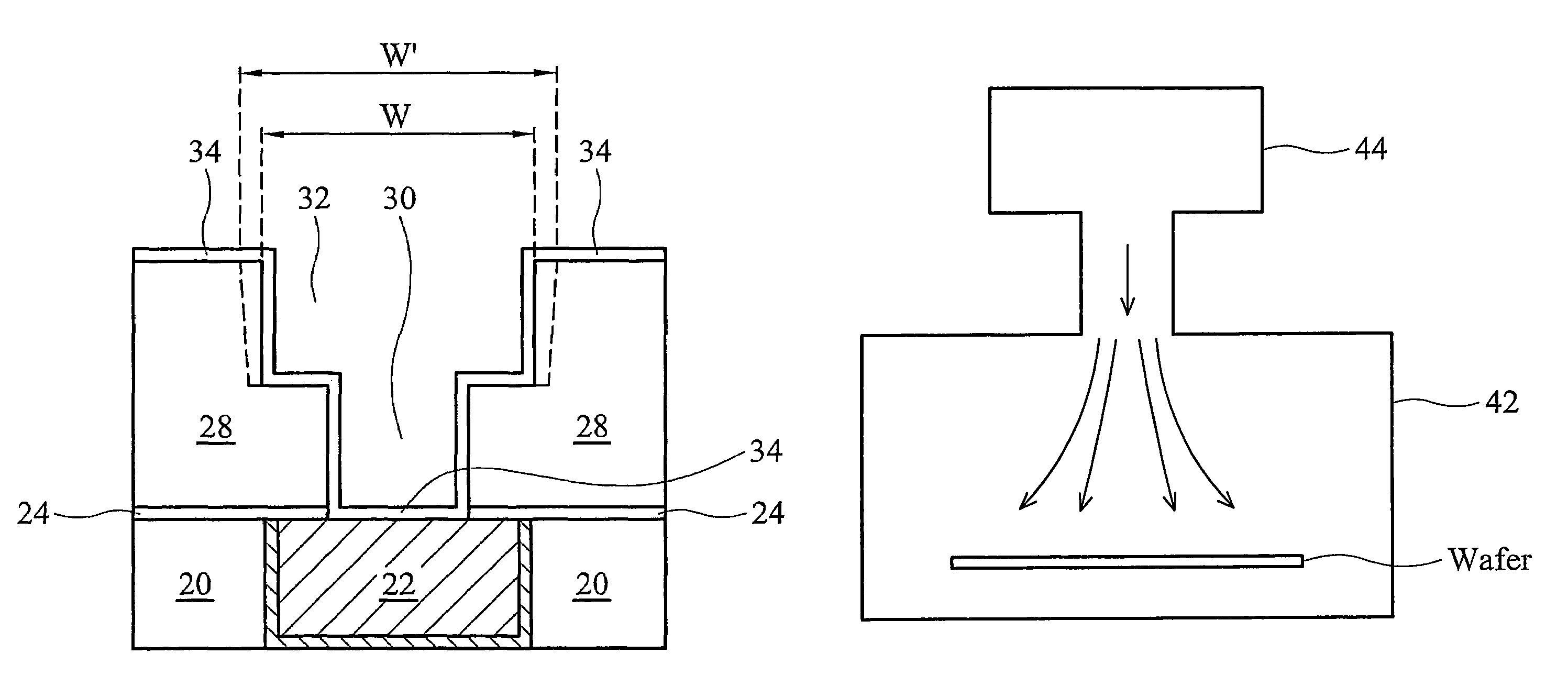

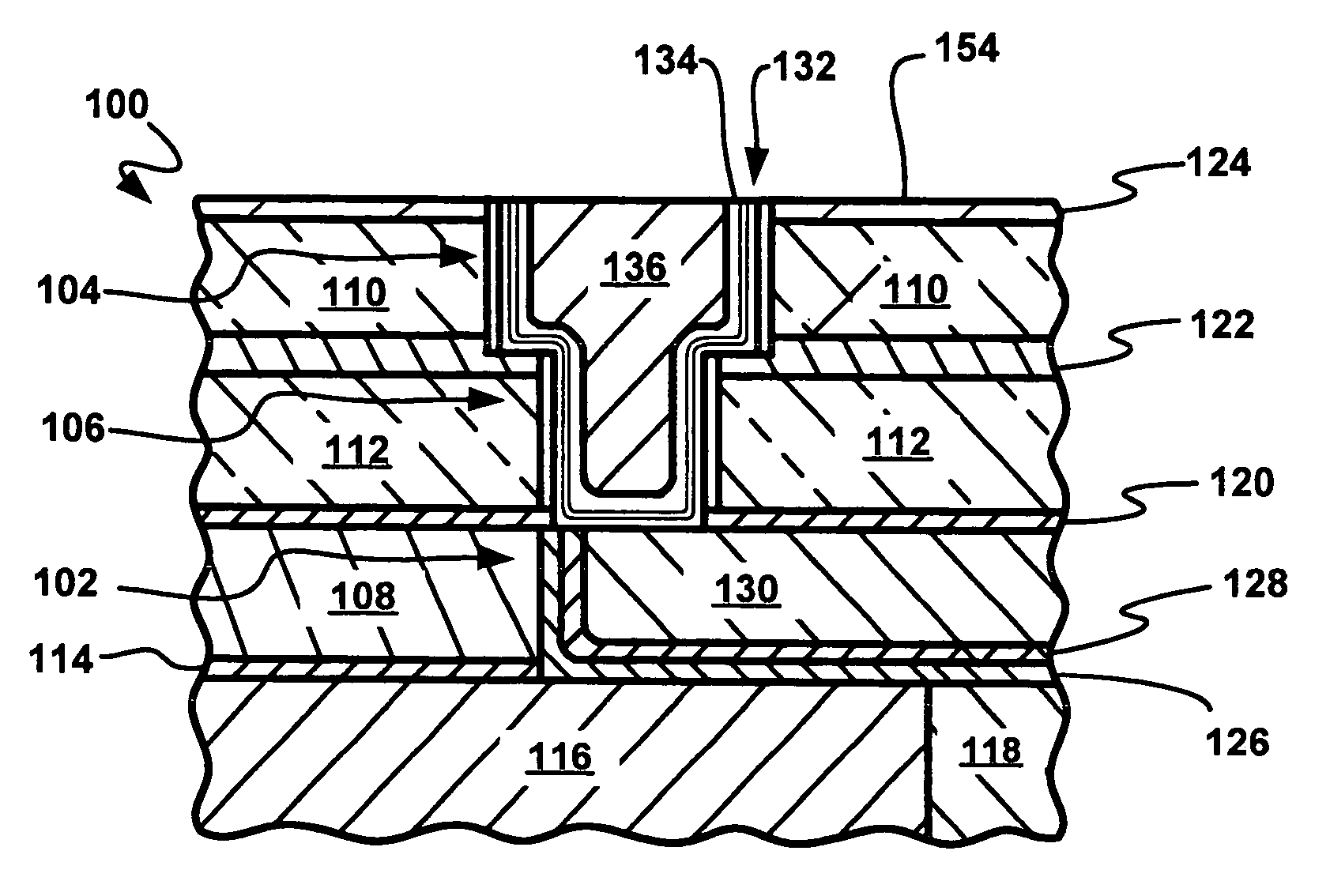

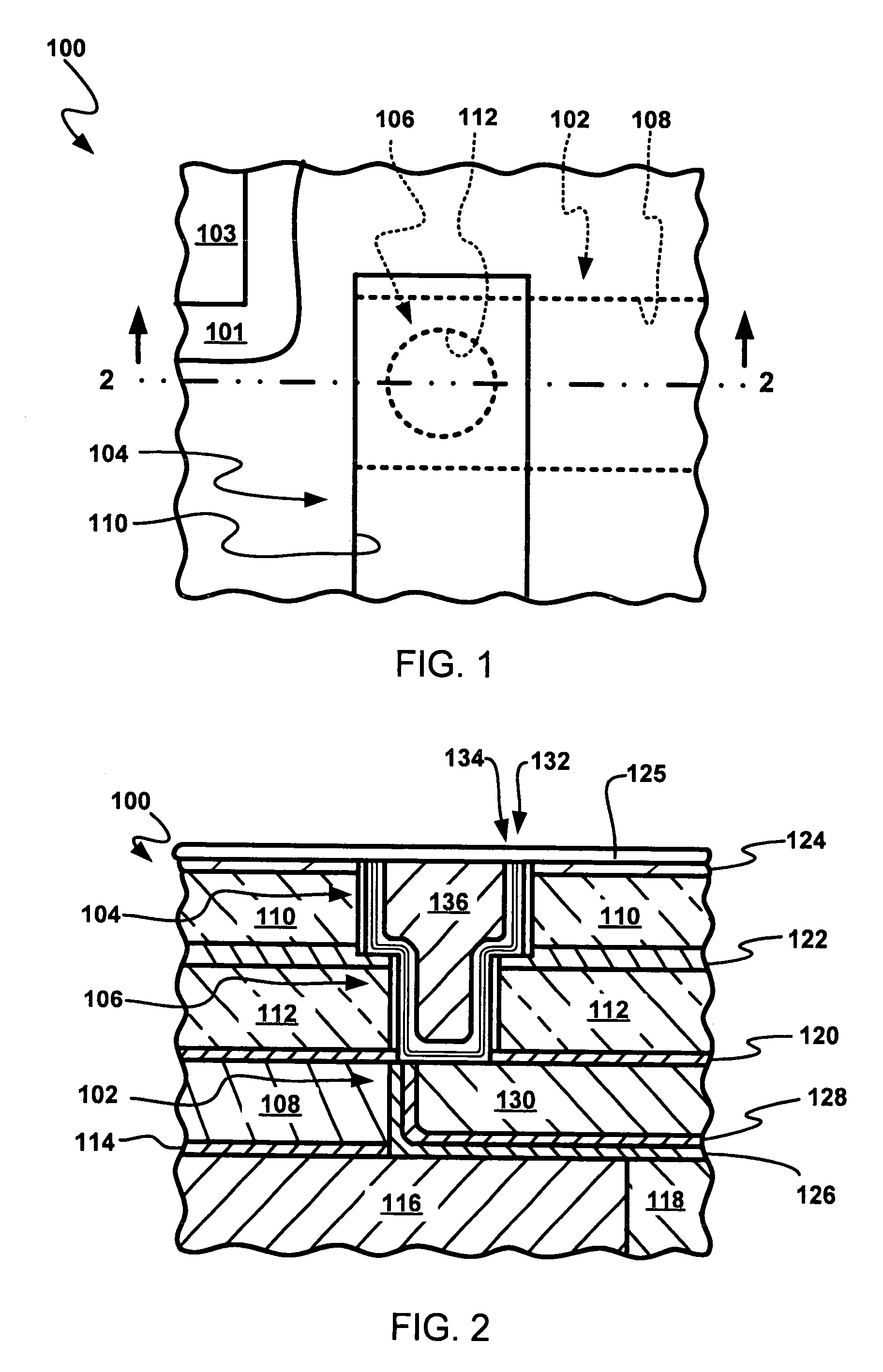

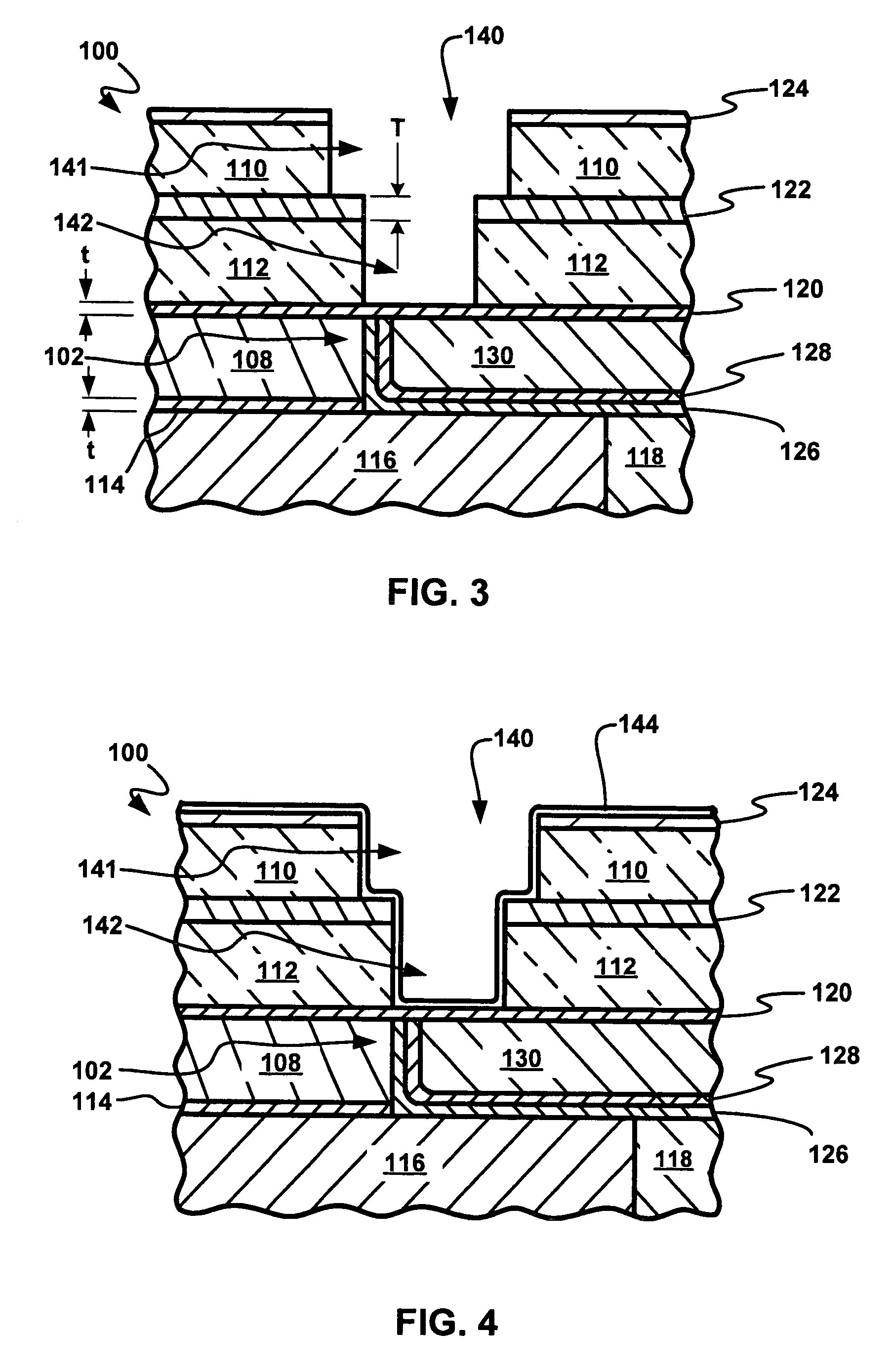

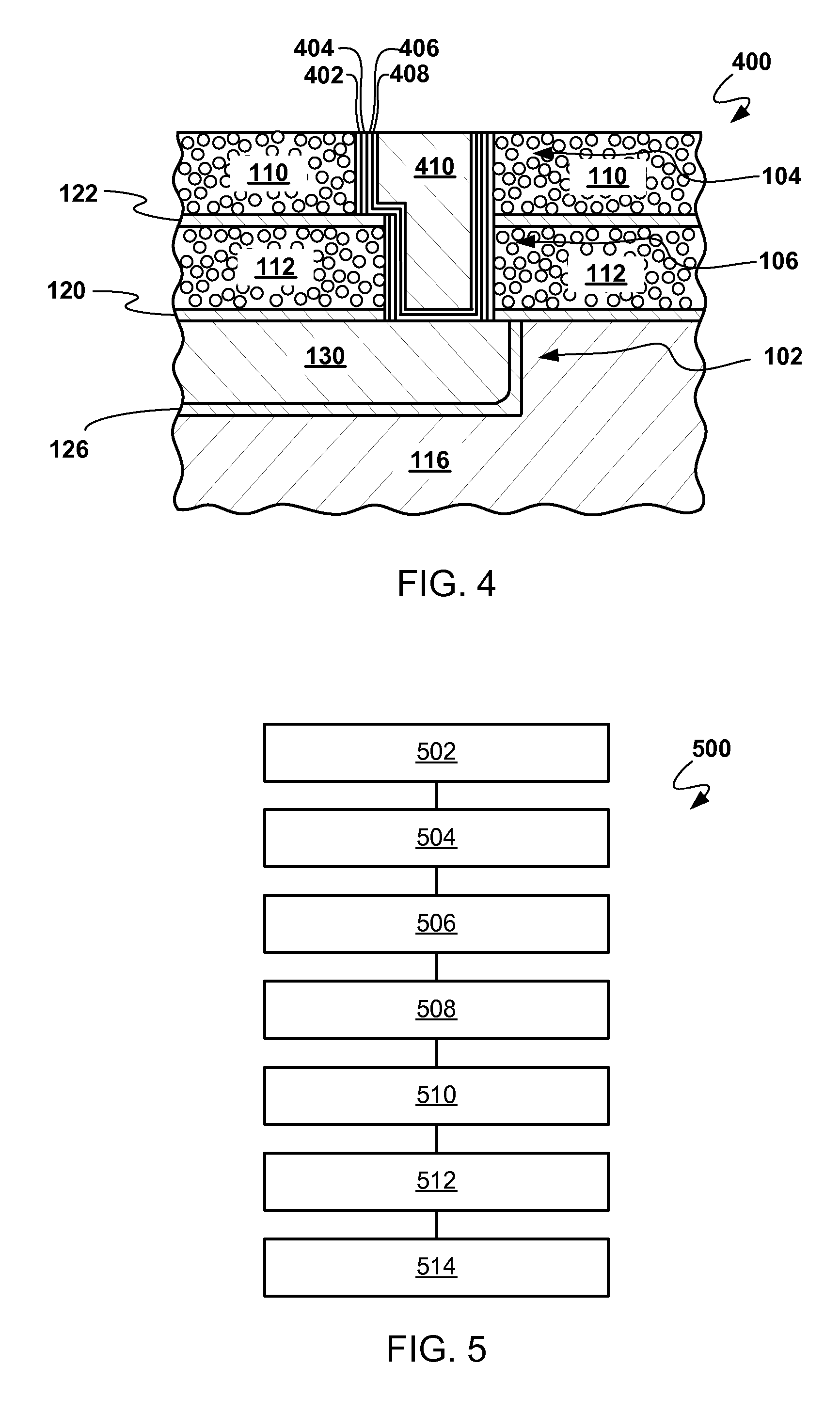

GCIB processing of integrated circuit interconnect structures

InactiveUS7115511B2Improving fabrication process and qualityImprove usabilityElectric discharge tubesSemiconductor/solid-state device manufacturingMetal interconnectIntegrated circuit interconnect

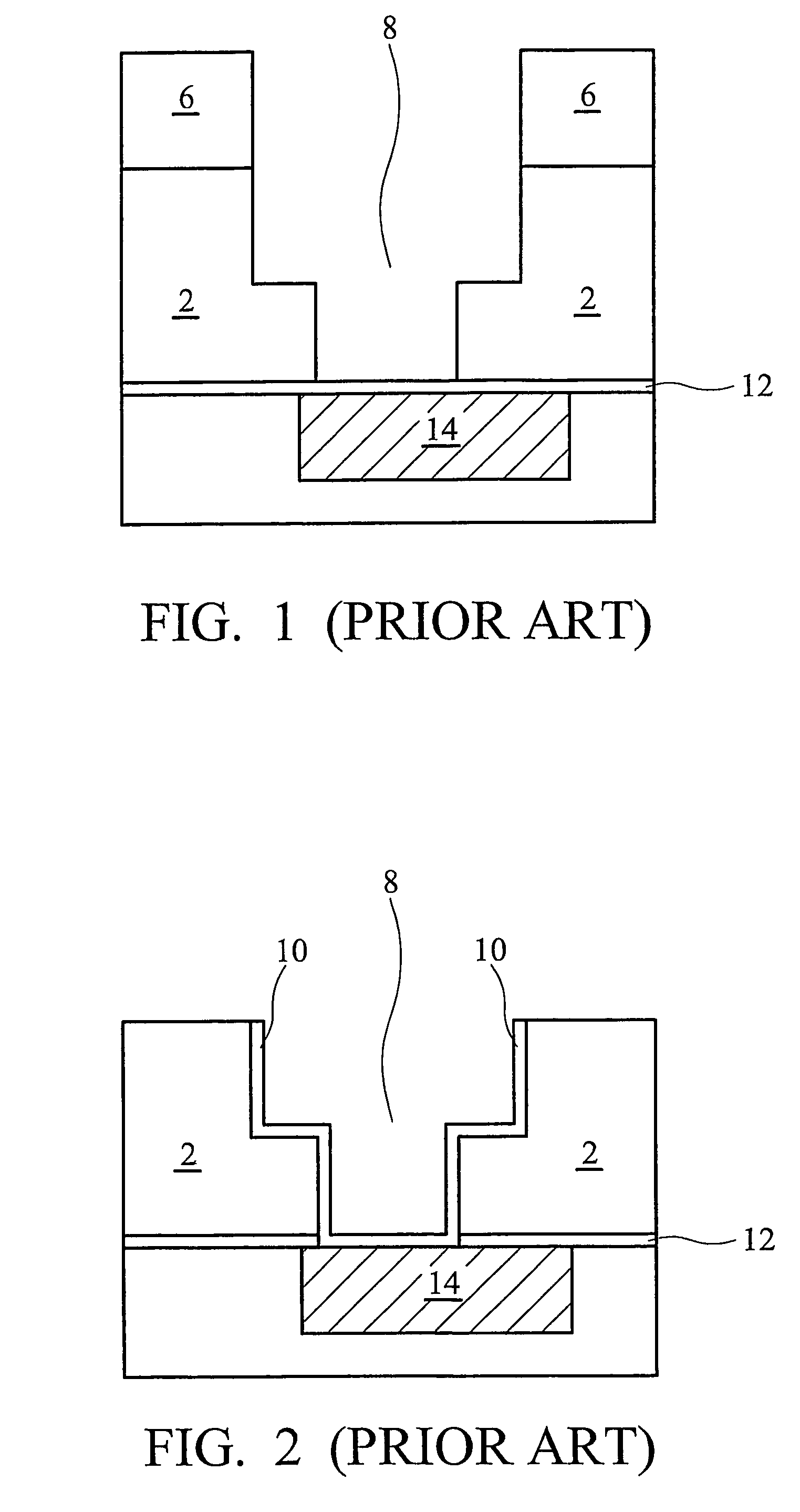

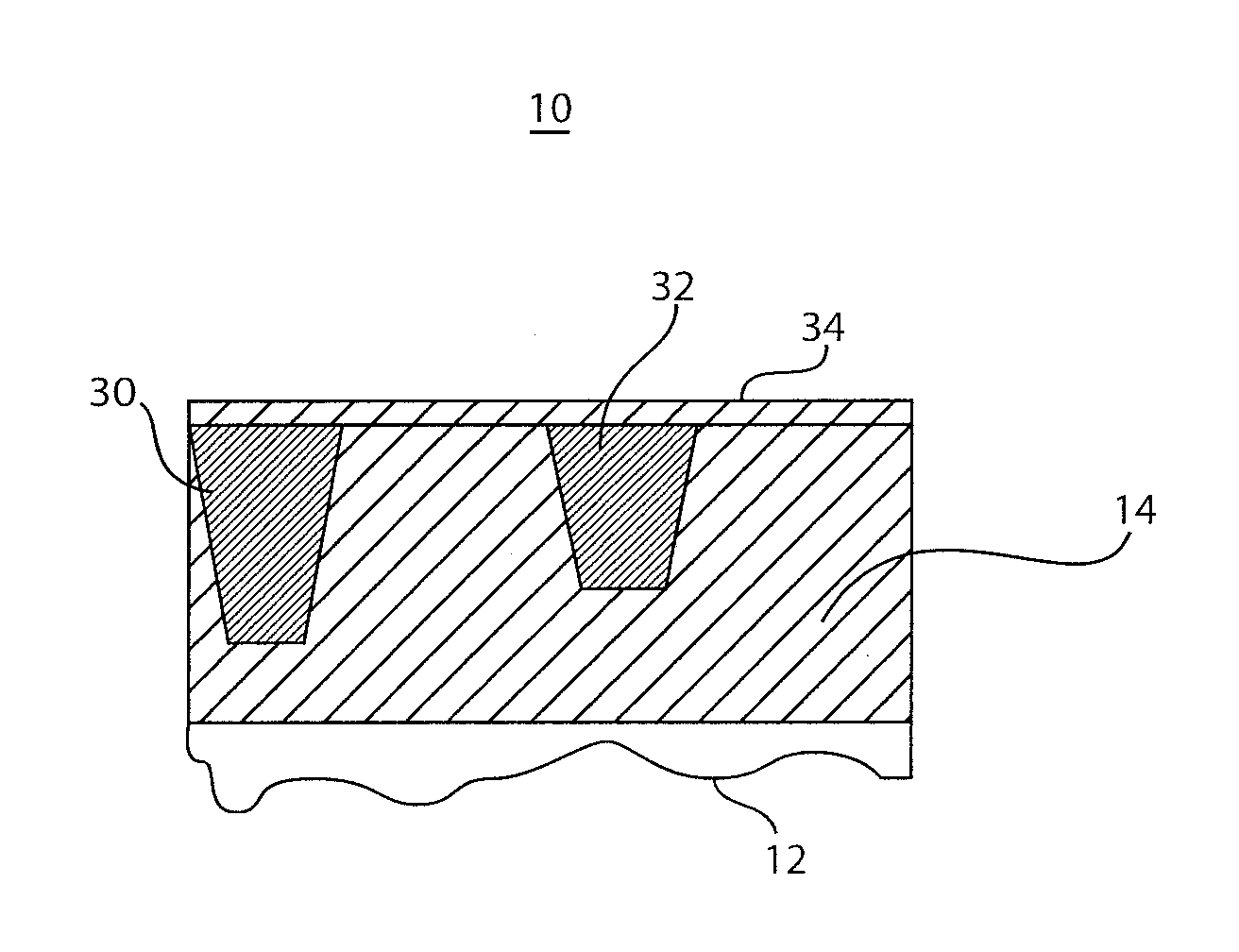

Method for removing and / or redistributing material in the trenches and / or vias of integrated circuit interconnect structures by a gas cluster ion beam (GCIB) is described to improve the fabrication process and quality of metal interconnects in an integrated circuit. The process entails opening up an undesired ‘necked in’ region at the entrance to the structure, re-depositing the barrier metal from thicker areas such as the neck or bottom of the structure to the side walls and / or removing some of the excess and undesired material on the bottom of the structure by sputtering. The GCIB process may be applied after the barrier metal deposition and before the copper seed layer / copper electroplating or the process may be applied after the formation of the copper seed layer and before electroplating. The method may extend the usability of the known interconnect deposition technologies to next generation integrated circuits and beyond.

Owner:TEL EPION

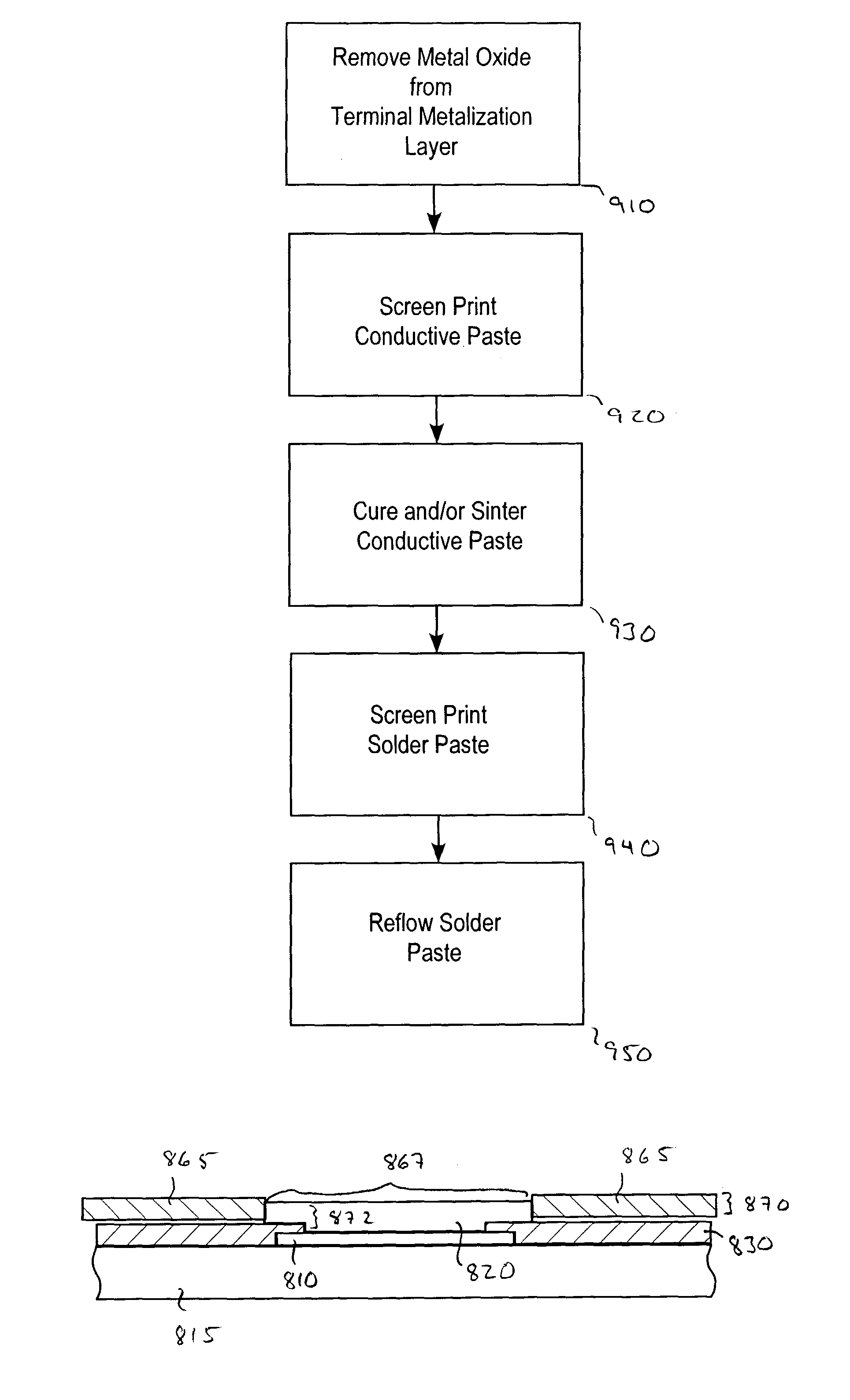

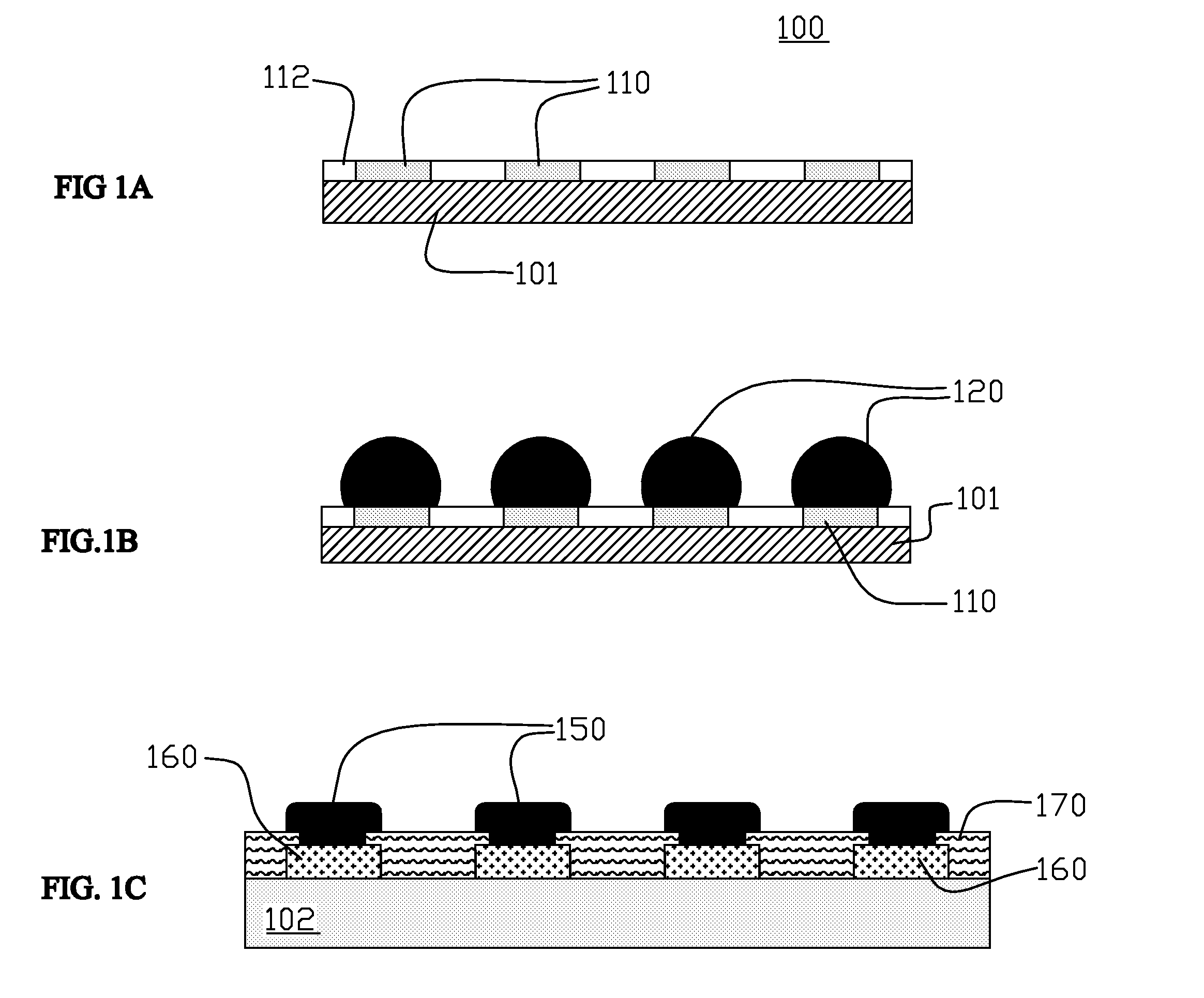

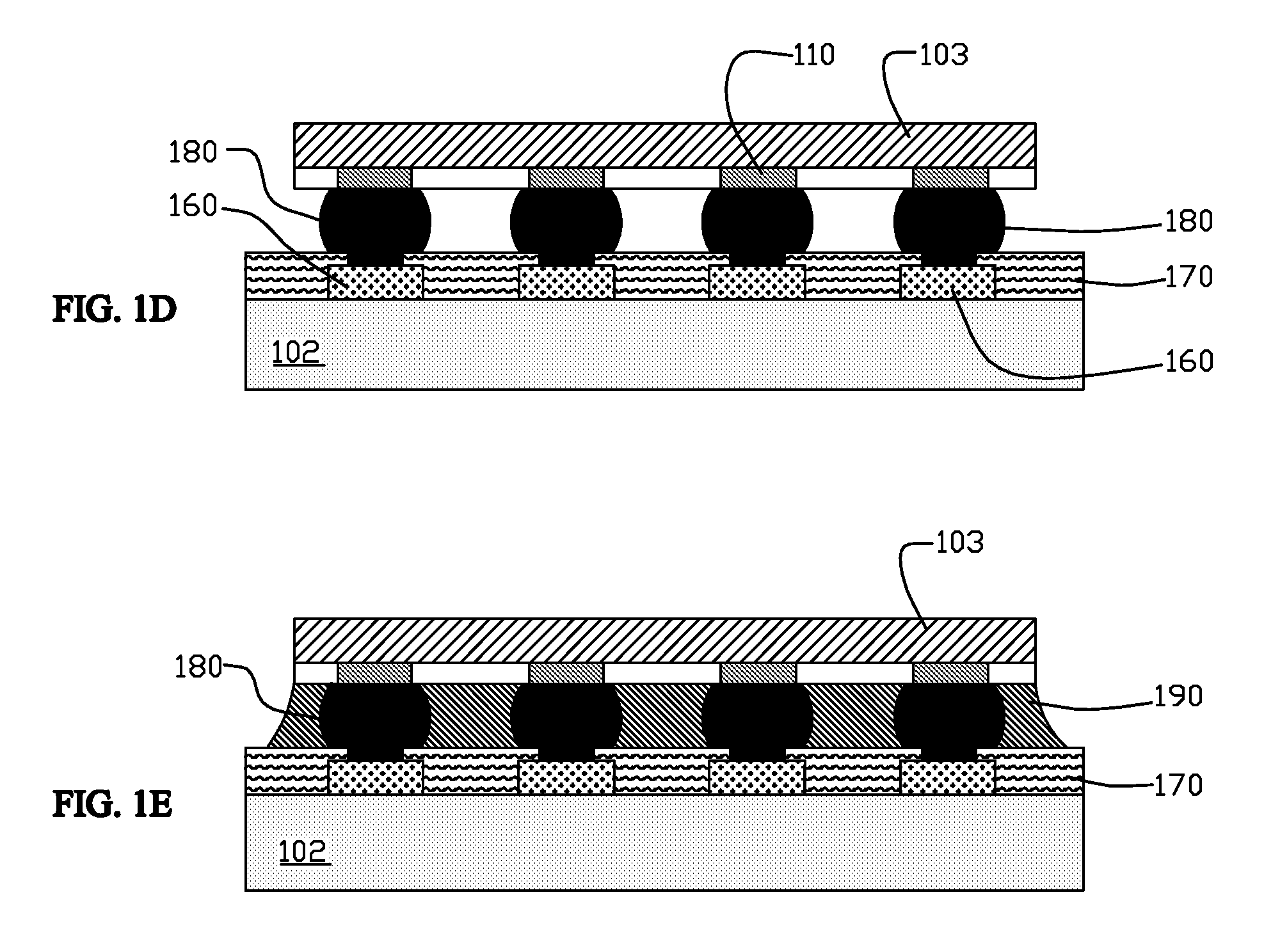

Screen print under-bump metalization (UBM) to produce low cost flip chip substrate

InactiveUS6992001B1Few process stepsShorten production timeSemiconductor/solid-state device detailsSolid-state devicesConductive pasteScreen printing

A method for forming an integrated circuit interconnect pad is described. In one embodiment a method of forming an integrated circuit comprises screen printing a conductive paste onto a terminal metalization pad and curing the conductive paste in an inert or reducing atmosphere at an elevated temperature to form an under-bump metalization layer of an interconnect pad. The elevated temperature is below a melting temperature of the terminal metalization pad.

Owner:KULICKE & SOFFA IND INC

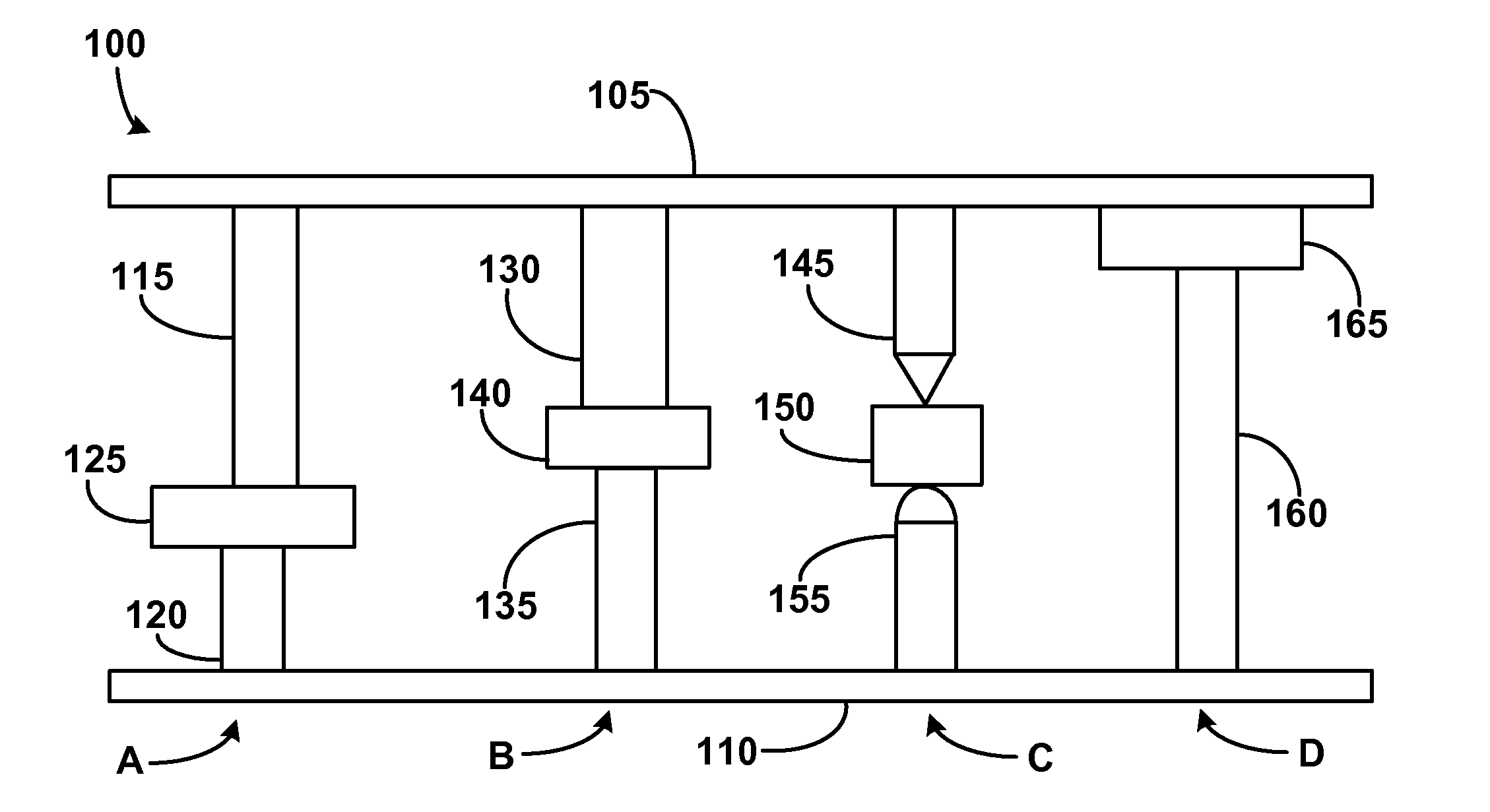

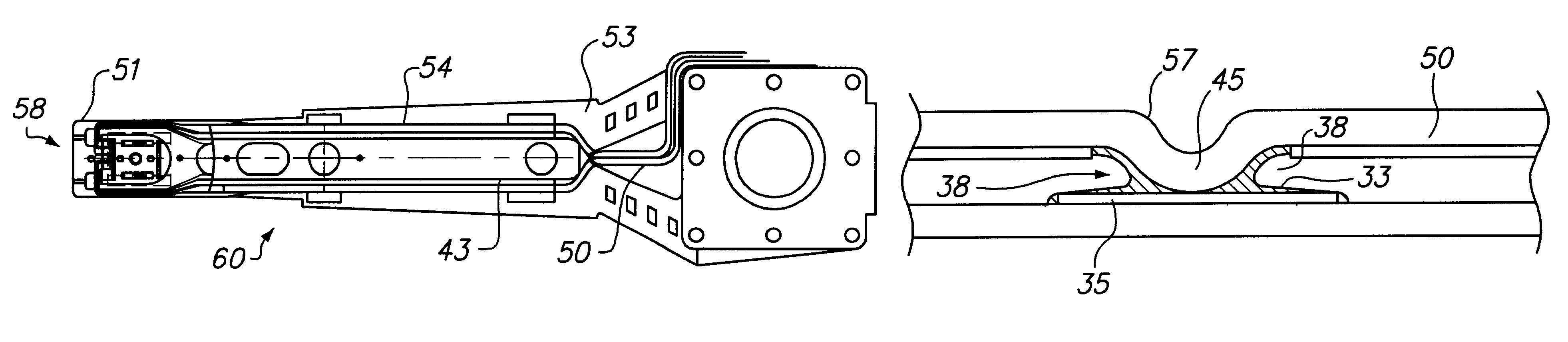

Integrated circuit interconnection devices and methods

InactiveUS20080073795A1High aspect ratioHigh profile featureSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit interconnectElectrical conductor

Integrated circuit interconnection devices and methods are provided. An interconnection to connect components can comprise a first portion, a second portion, and a joining portion. The first portion can extend from a first component, and the first portion can be made with a single conductor. The second portion can extend from a second component, and the second portion can be made with the single conductor. The joining section can be disposed between the first portion and the second portion so that the first component and second component are interconnected to each other to form an interconnect. The joining section can be made of the single conductor so that the interconnect structure consists only of the single conductor. An interconnect can also be formed with two portions, and be formed to have a high-aspect ratio. Other embodiments are also claimed and described.

Owner:GEORGIA TECH RES CORP

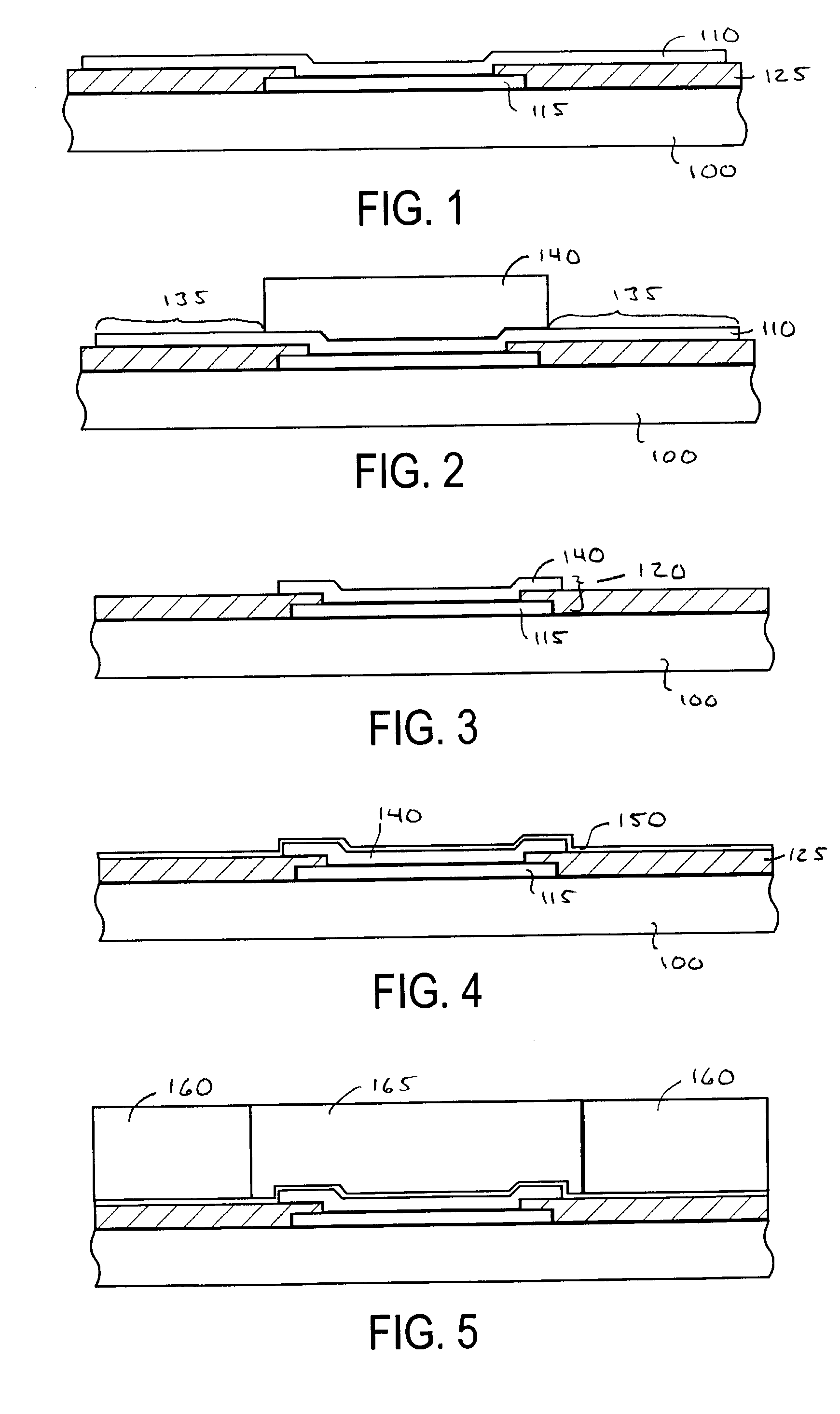

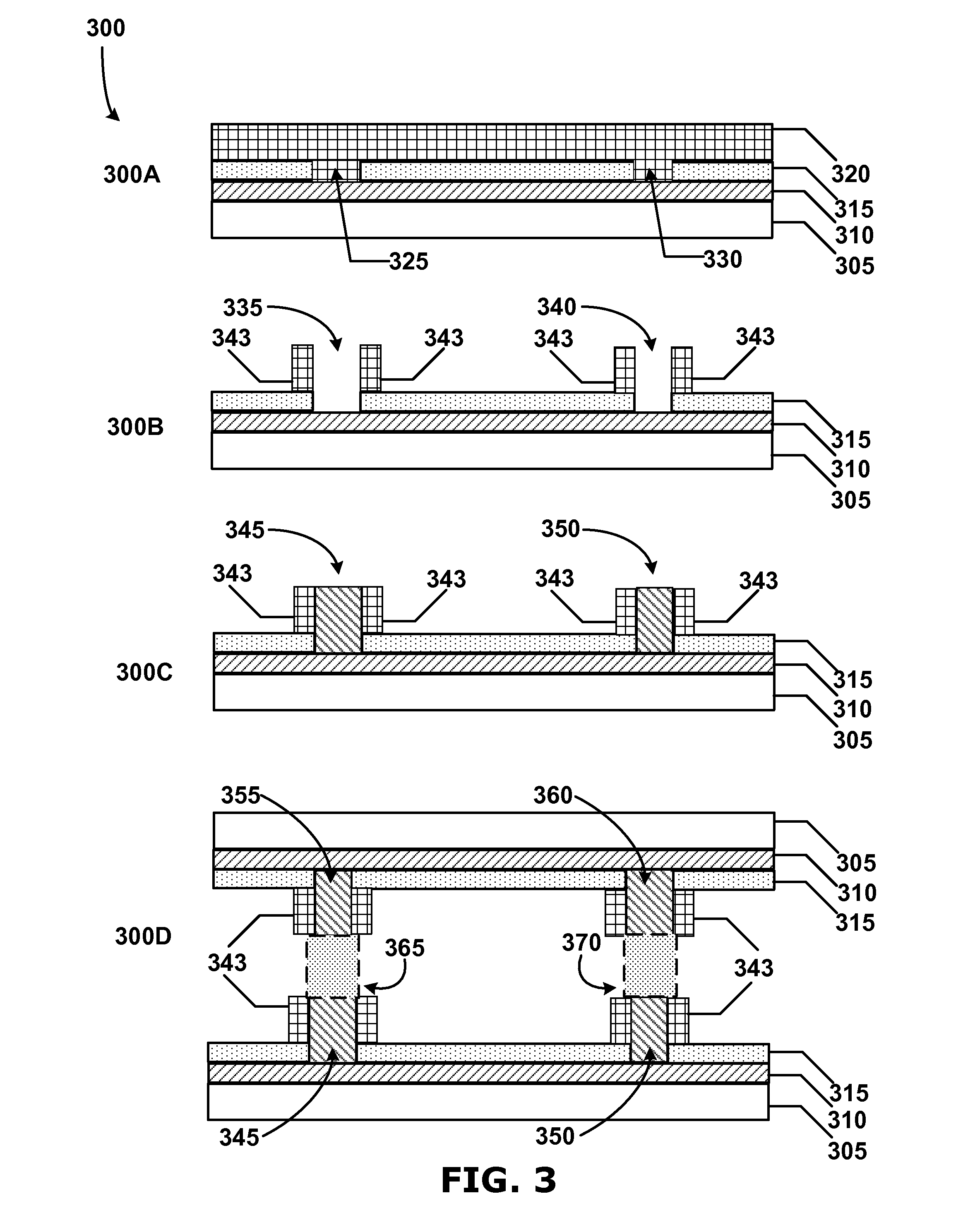

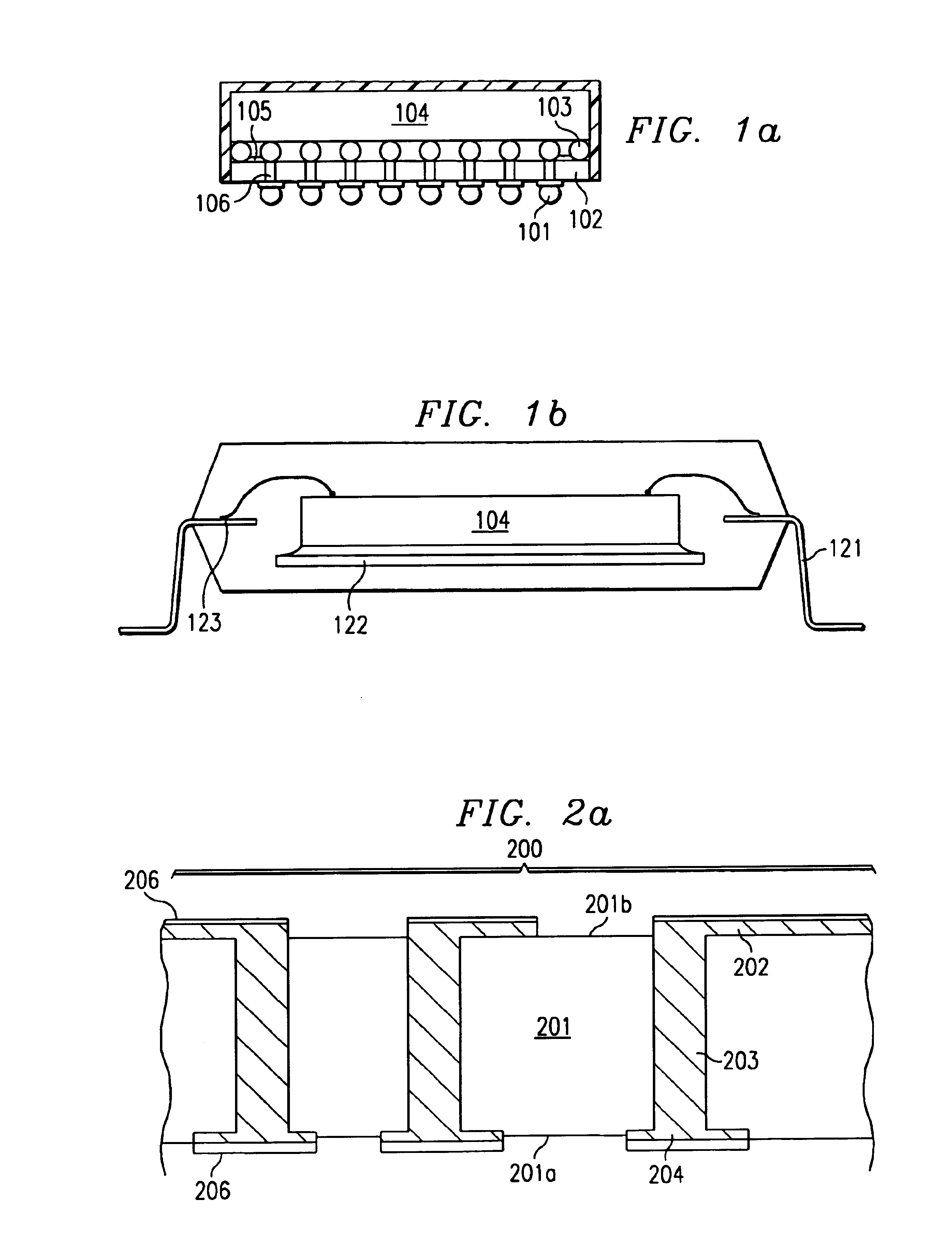

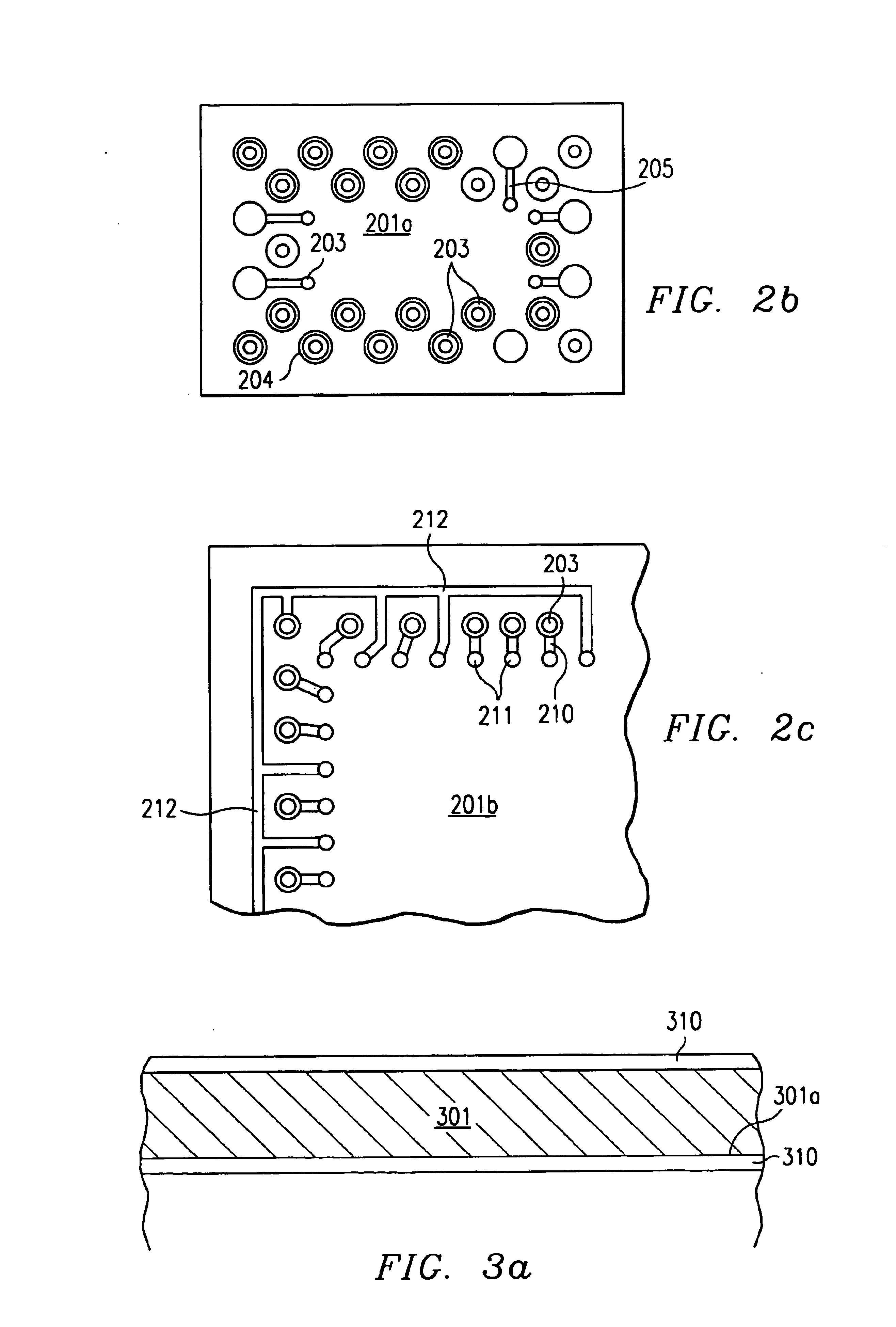

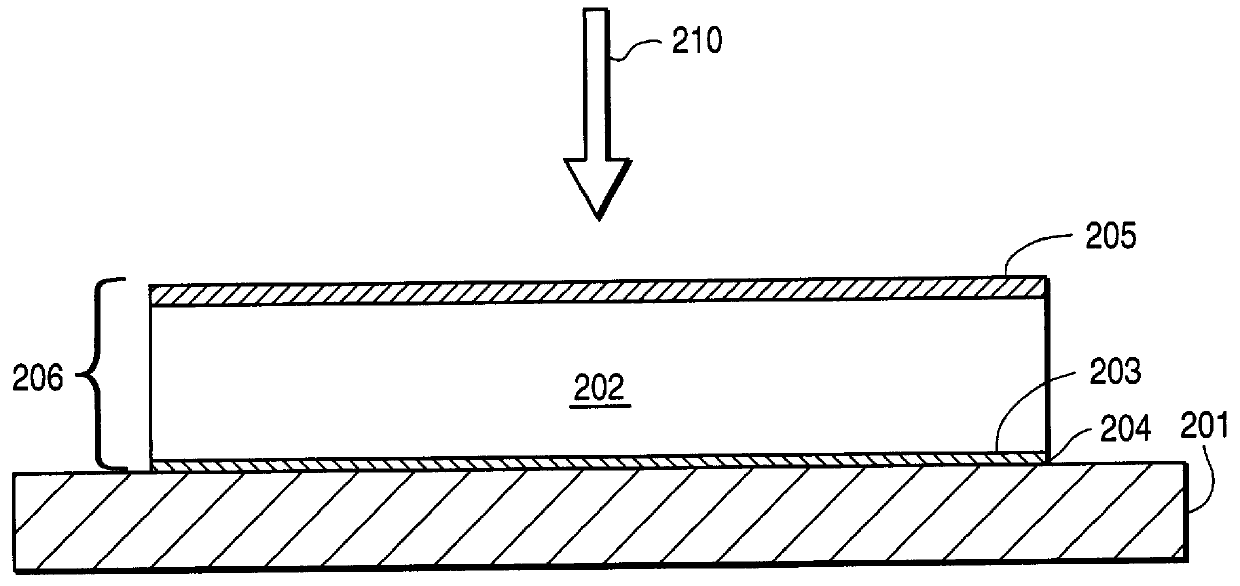

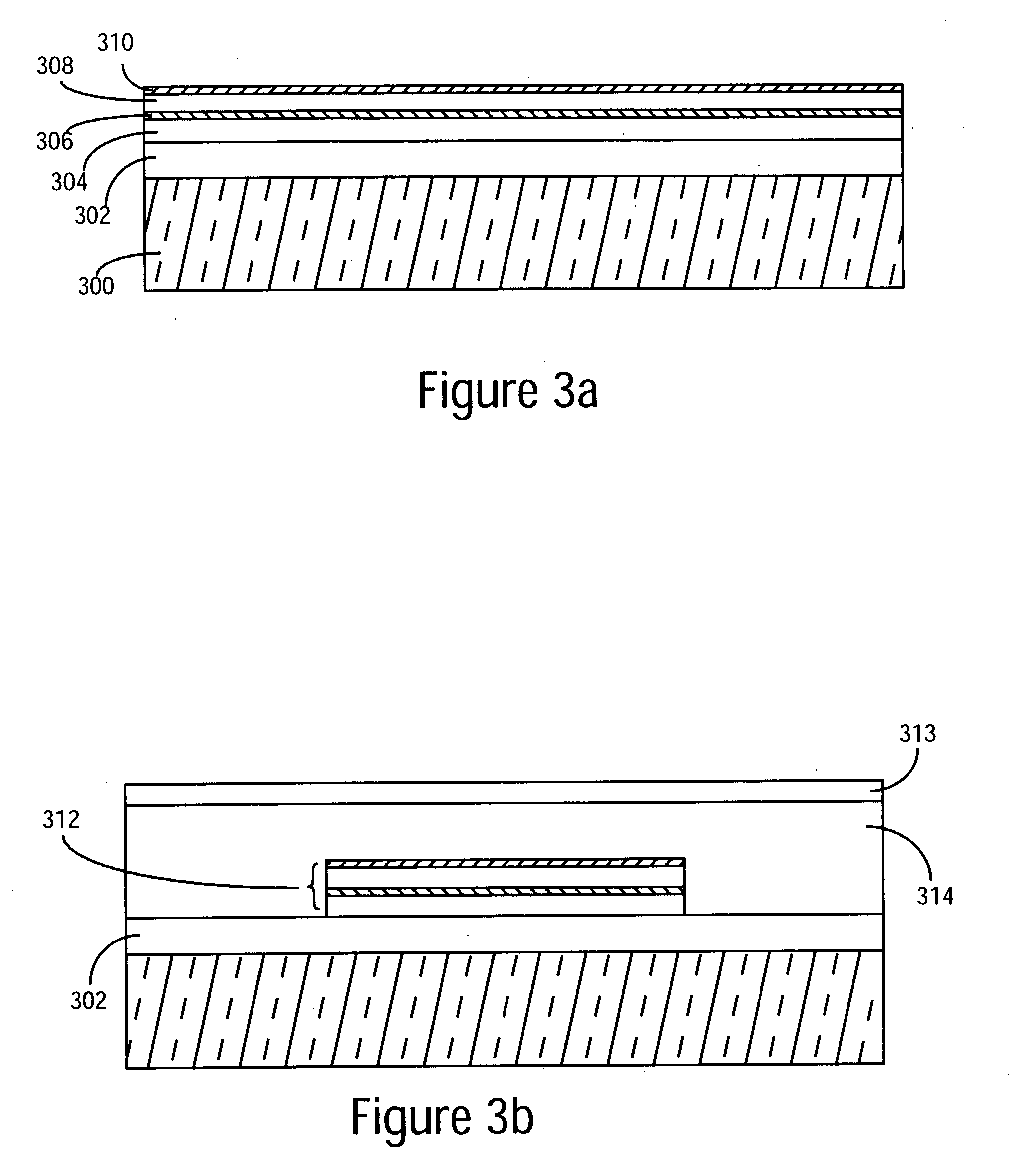

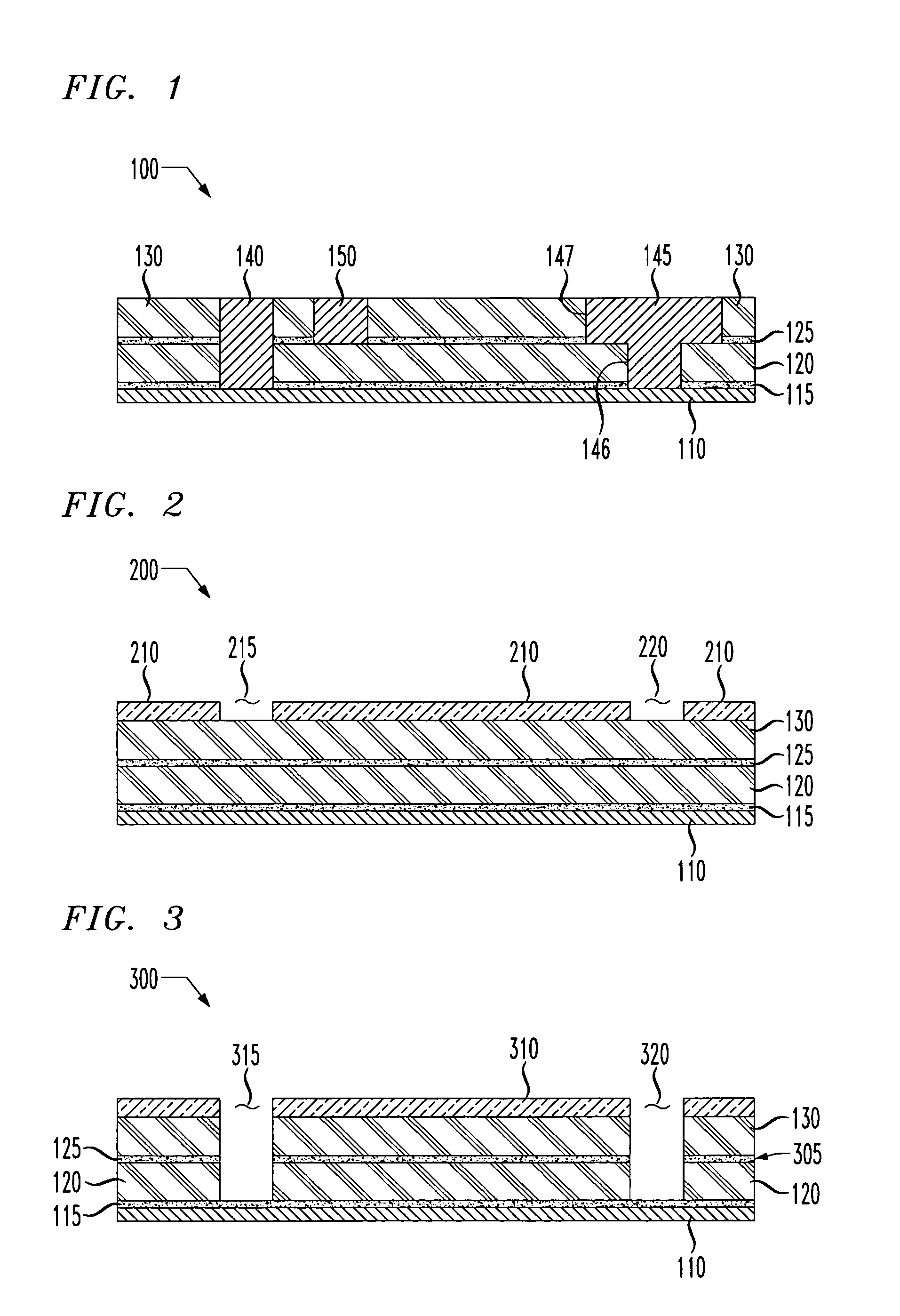

Method of fabricating flexible circuits for integrated circuit interconnections

InactiveUS6915566B2Increases conductor thicknessConnection sealPrinted circuit assemblingLine/current collector detailsIntegrated circuit interconnectFlexible circuits

A method for the fabrication of a double-sided electrical interconnection flexible circuit (200) particularly useful as a substrate for an area array integrated circuit package. A copper matrix with studs (203) is pressed through a dielectric film (201) having a copper layer on the opposite surface, thereby forming an intermediate structure for a flex circuit with self-aligned solid copper vias in a one step process. The contacts are reinforced by plating both surfaces with a layer of copper, and conventional processes are used to complete the circuit patterning.

Owner:TEXAS INSTR INC

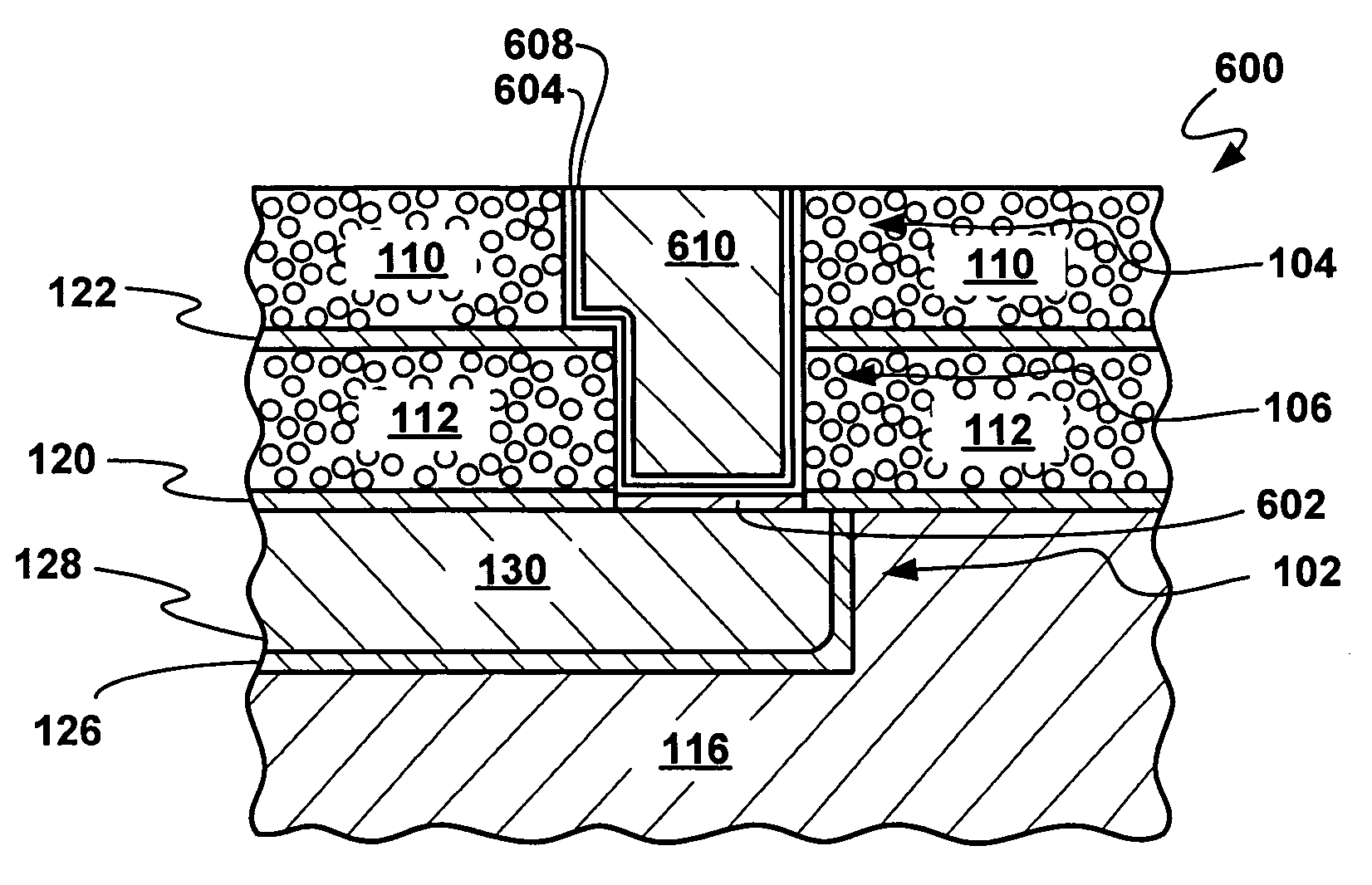

Cleaning processes in the formation of integrated circuit interconnect structures

InactiveUS7700479B2Small shifts in the low-k dielectric propertiesDecreased trench enlargementSemiconductor/solid-state device manufacturingRemote plasmaIntegrated circuit interconnect

A method for fabricating an integrated circuit includes providing a substrate, forming a low-k dielectric layer over the substrate, etching the low-k dielectric layer to form an opening in the low-k dielectric layer wherein an underlying metal is exposed through the opening, performing a remote plasma treatment to the substrate wherein a plasma used for the remote plasma treatment is generated from a plasma generator separated from a chamber in which the substrate is located, forming a diffusion barrier layer in the opening, and filling the opening with a conductive material. The method preferably includes an in-situ plasma treatment in a same chamber as the step of etching the low-k dielectric layer.

Owner:TAIWAN SEMICON MFG CO LTD

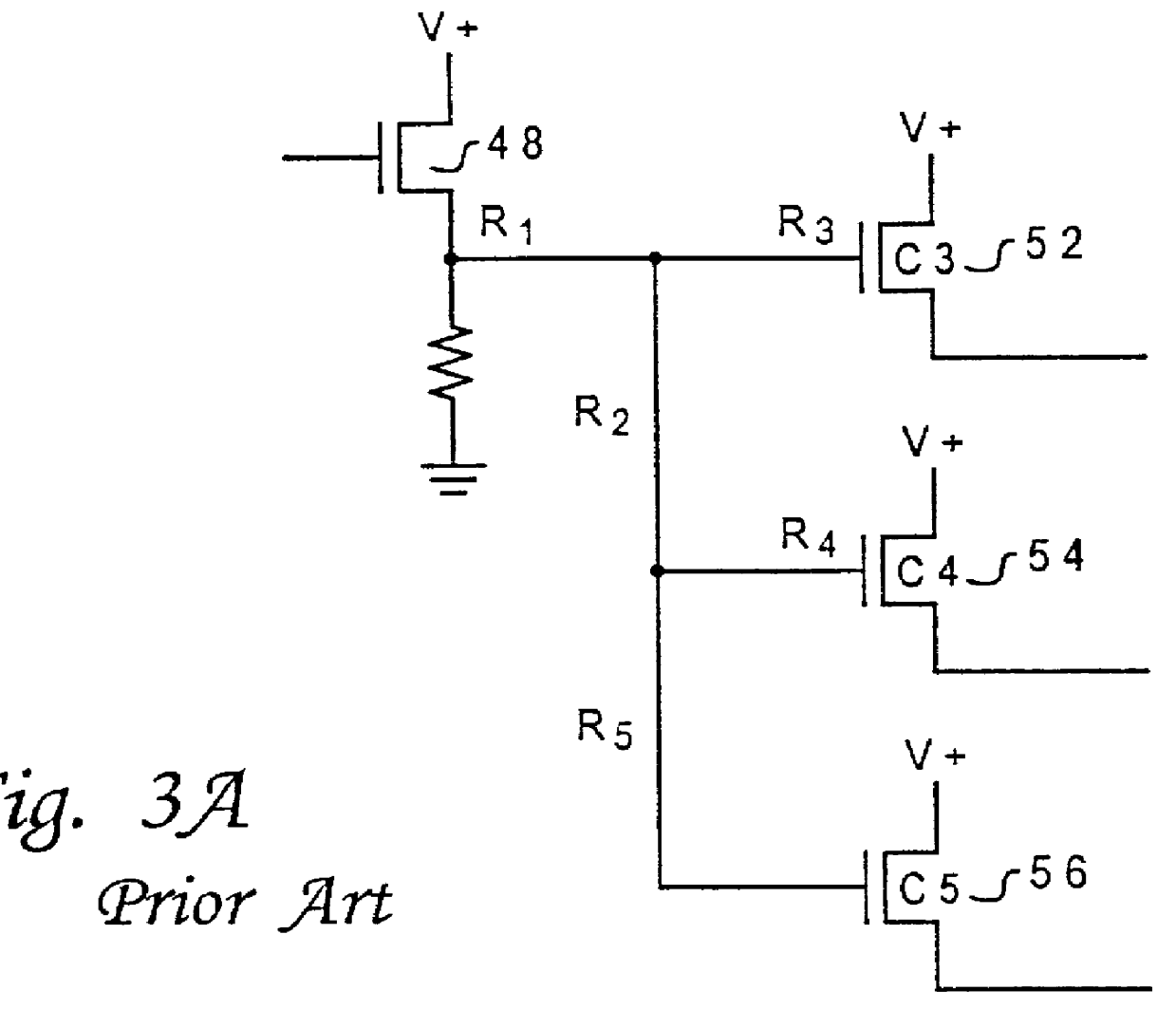

Method and system for segmenting wires prior to buffer insertion

InactiveUS6044209AEffectively and efficiently evaluateEfficient insertionComputer aided designSoftware simulation/interpretation/emulationIntegrated circuit interconnectCapacitance

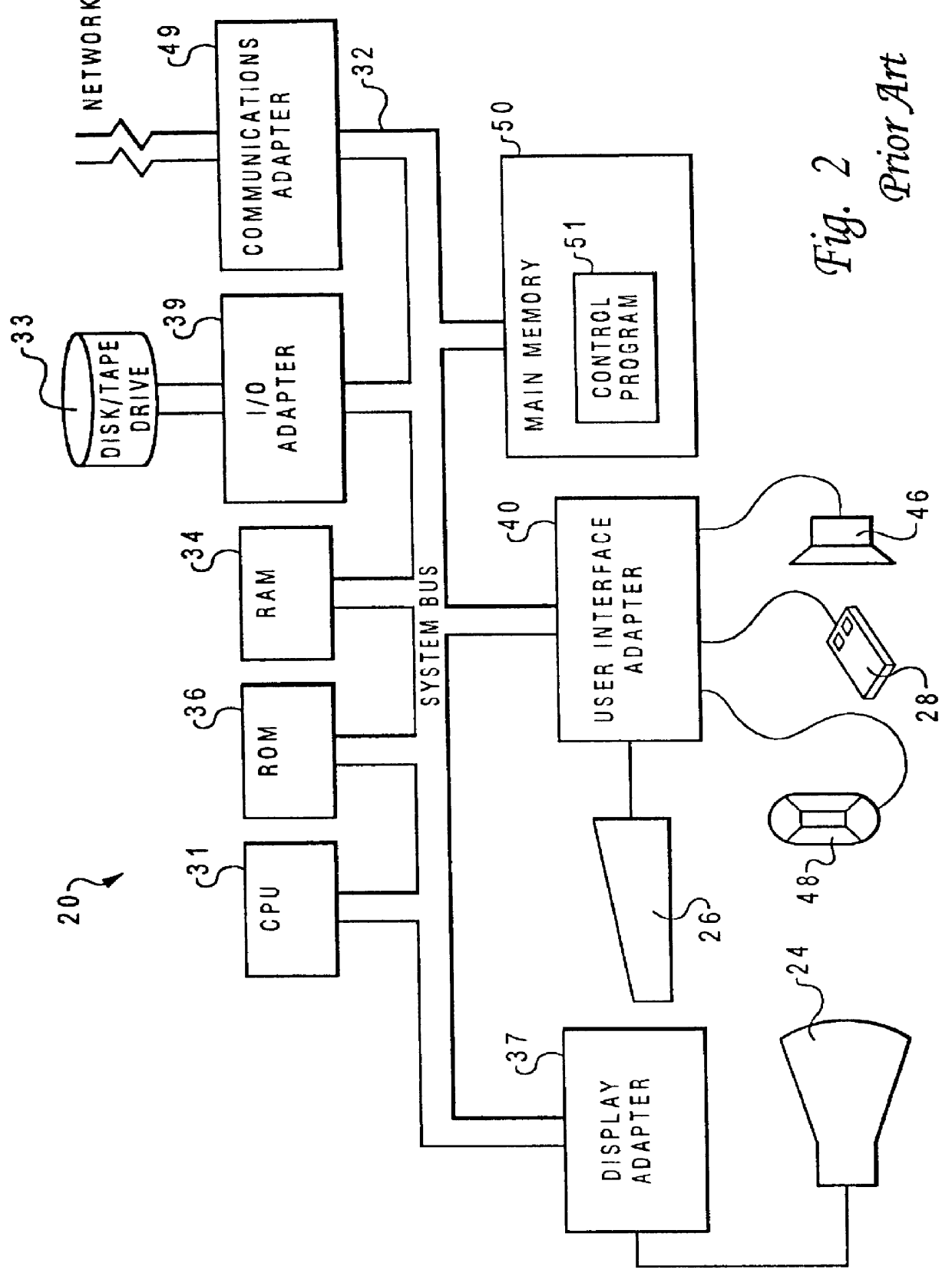

A method and system for segmenting wires in the design stage of a integrated circuit to allow for the efficient insertion of an optimum quantity of buffers. The method begins by locating wires in the integrated circuit which interconnect transistors and then determining the characteristics of the transistor and the characteristics of the interconnecting wires. Next, the method computes a first upper limit for an optimum quantity of buffers utilizing total capacitive load wire and transistor characteristics, then the method computes a second upper limit for an optimum quantity of buffers assuming buffer insertion has decoupled the capacitive load. Finally, the method segments the wires by inserting nodes utilizing the greater of the first computation or the second computation. A determined upper limit on buffer quantity allows wires to be segmented such that the number of candidate buffer insertion topologies is manageable. Therefore, an optimum number of buffers can be efficiently inserted by buffer insertion method which utilize the segmented wires.

Owner:GOOGLE LLC

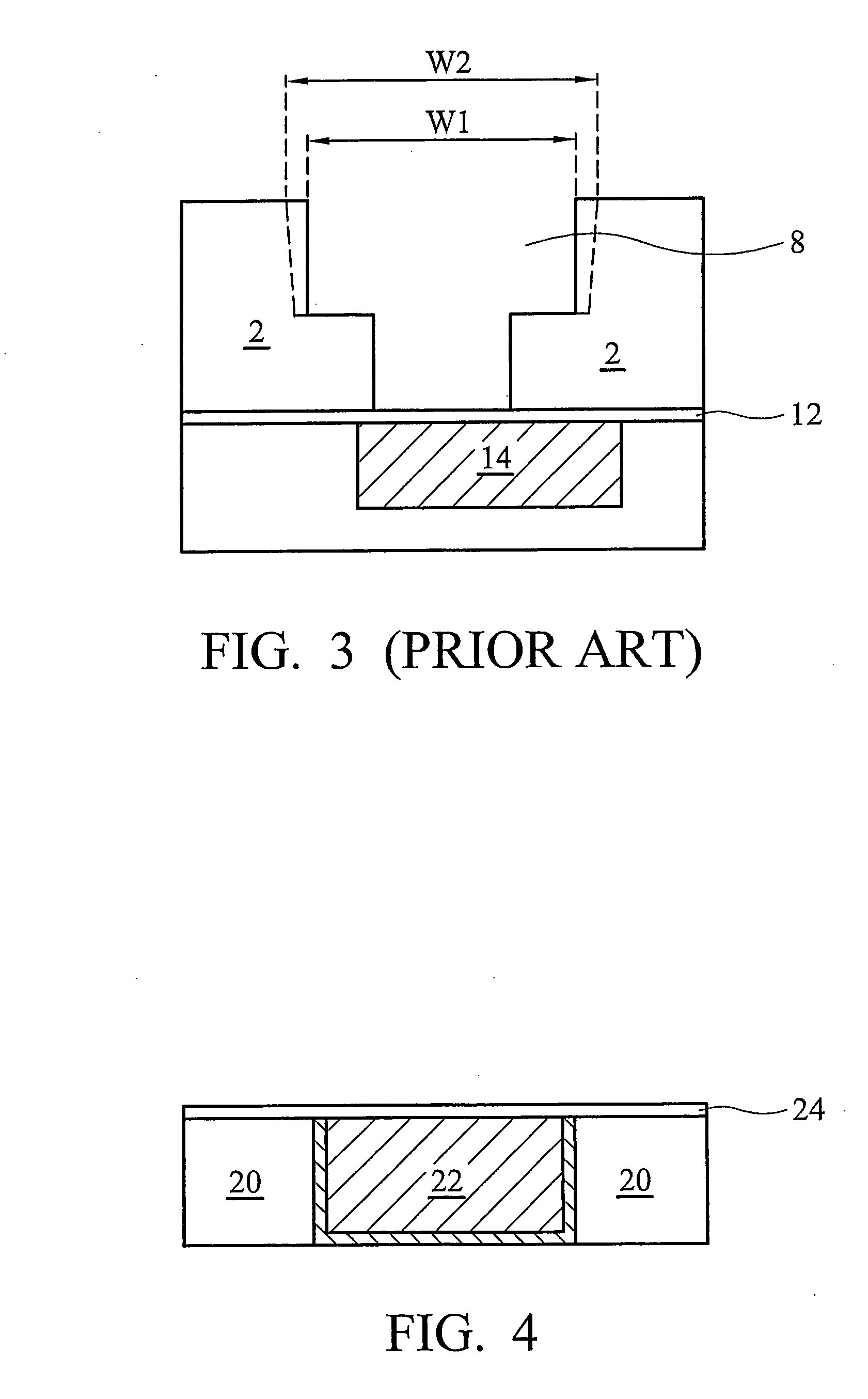

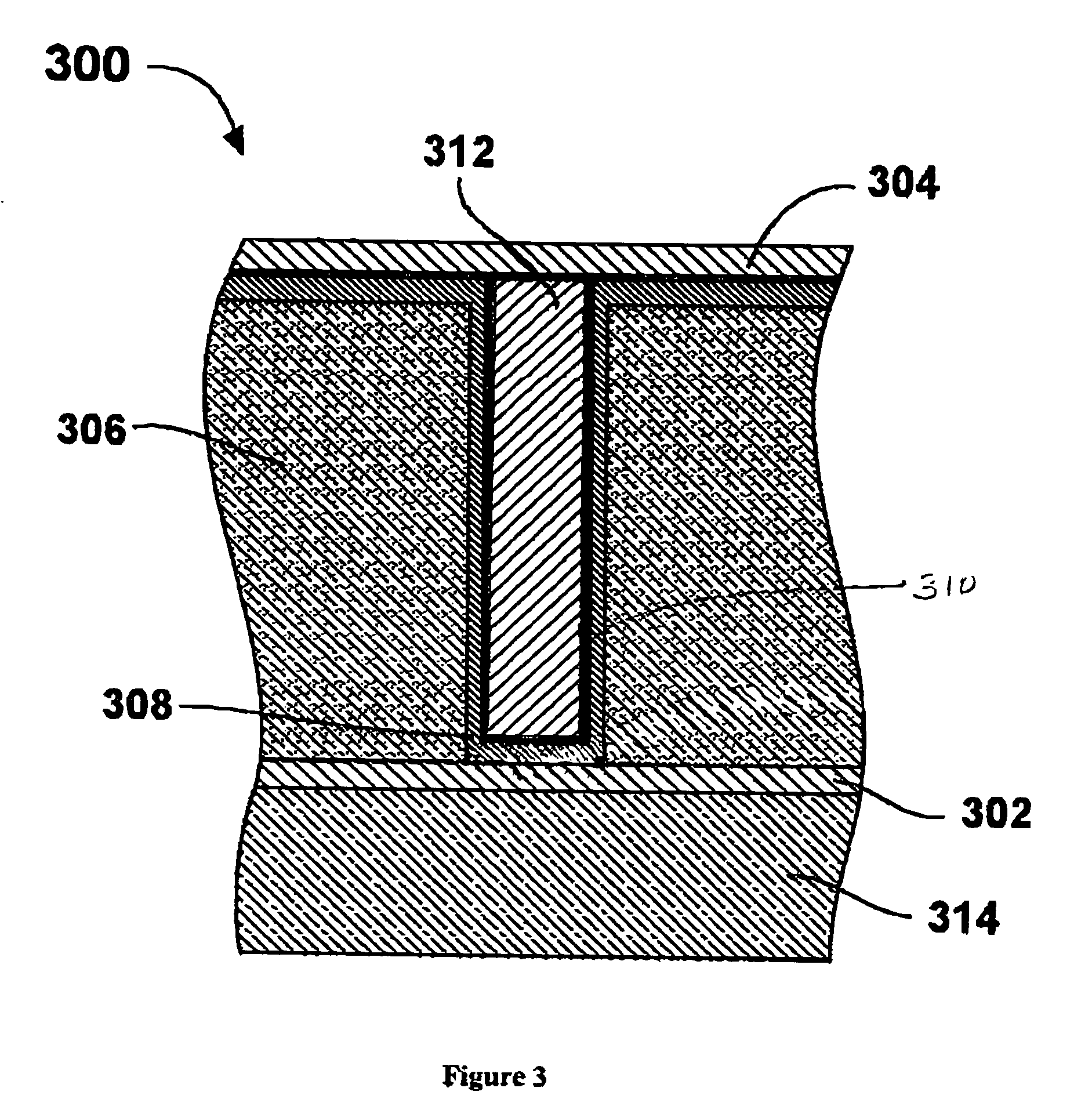

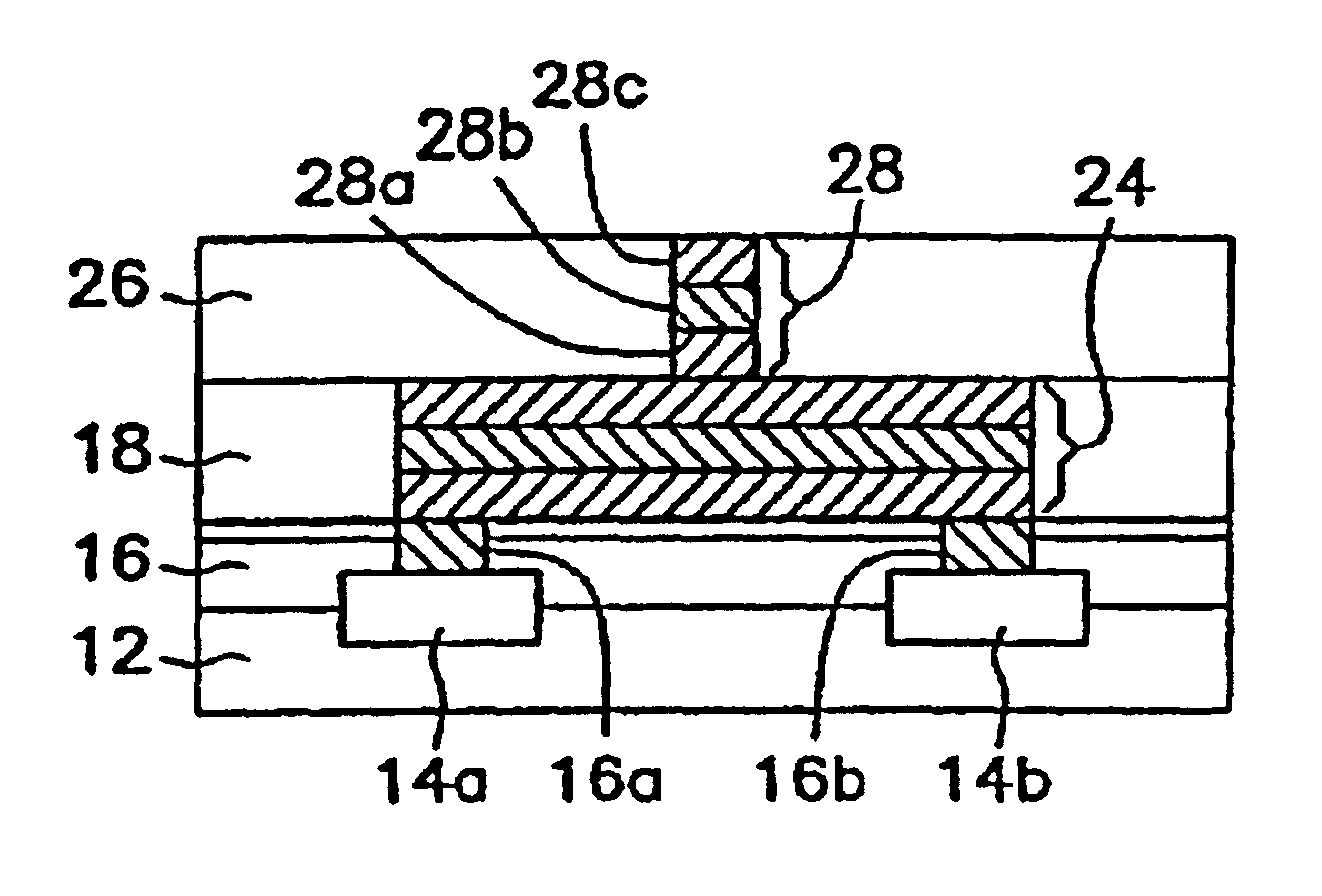

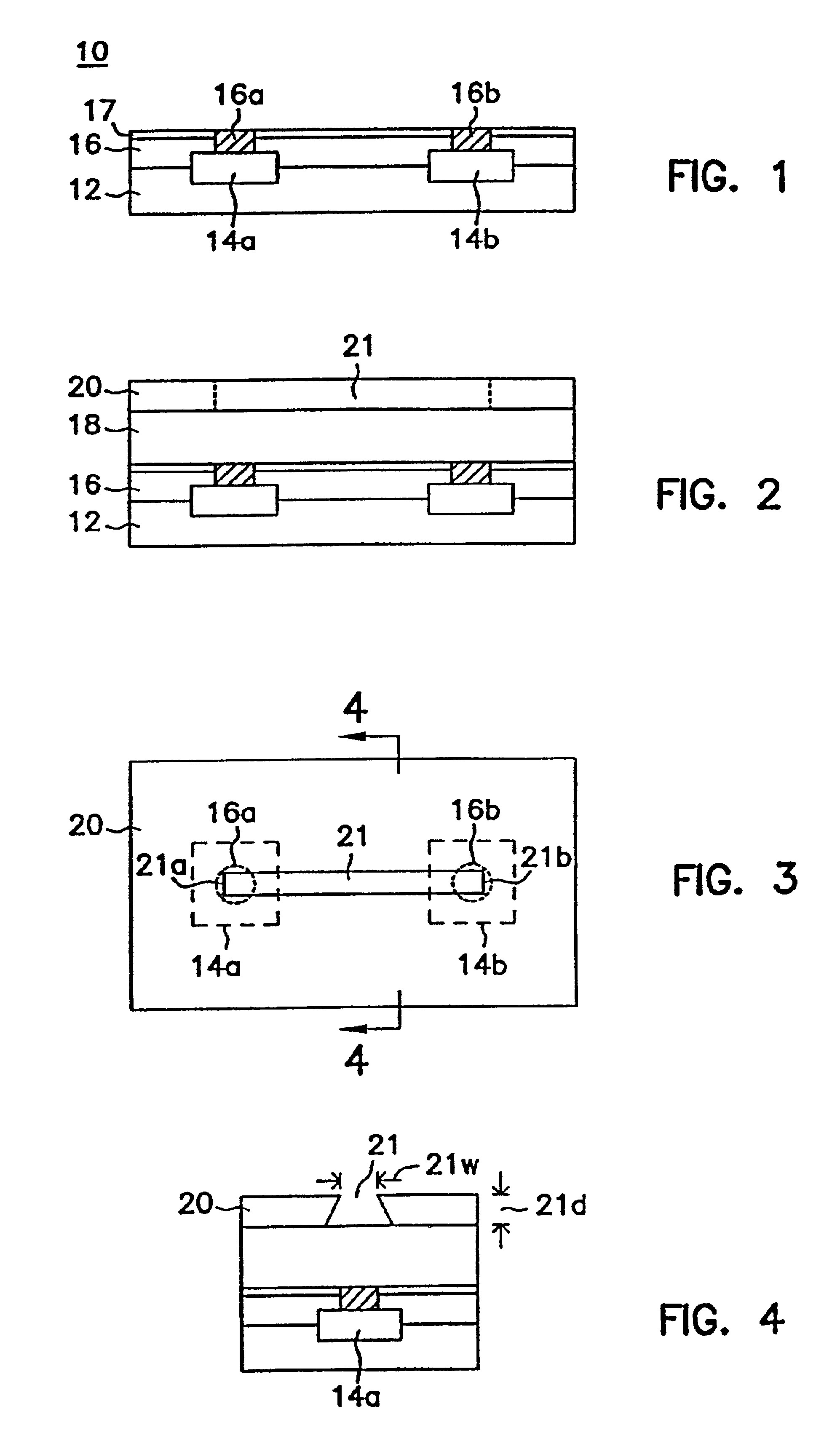

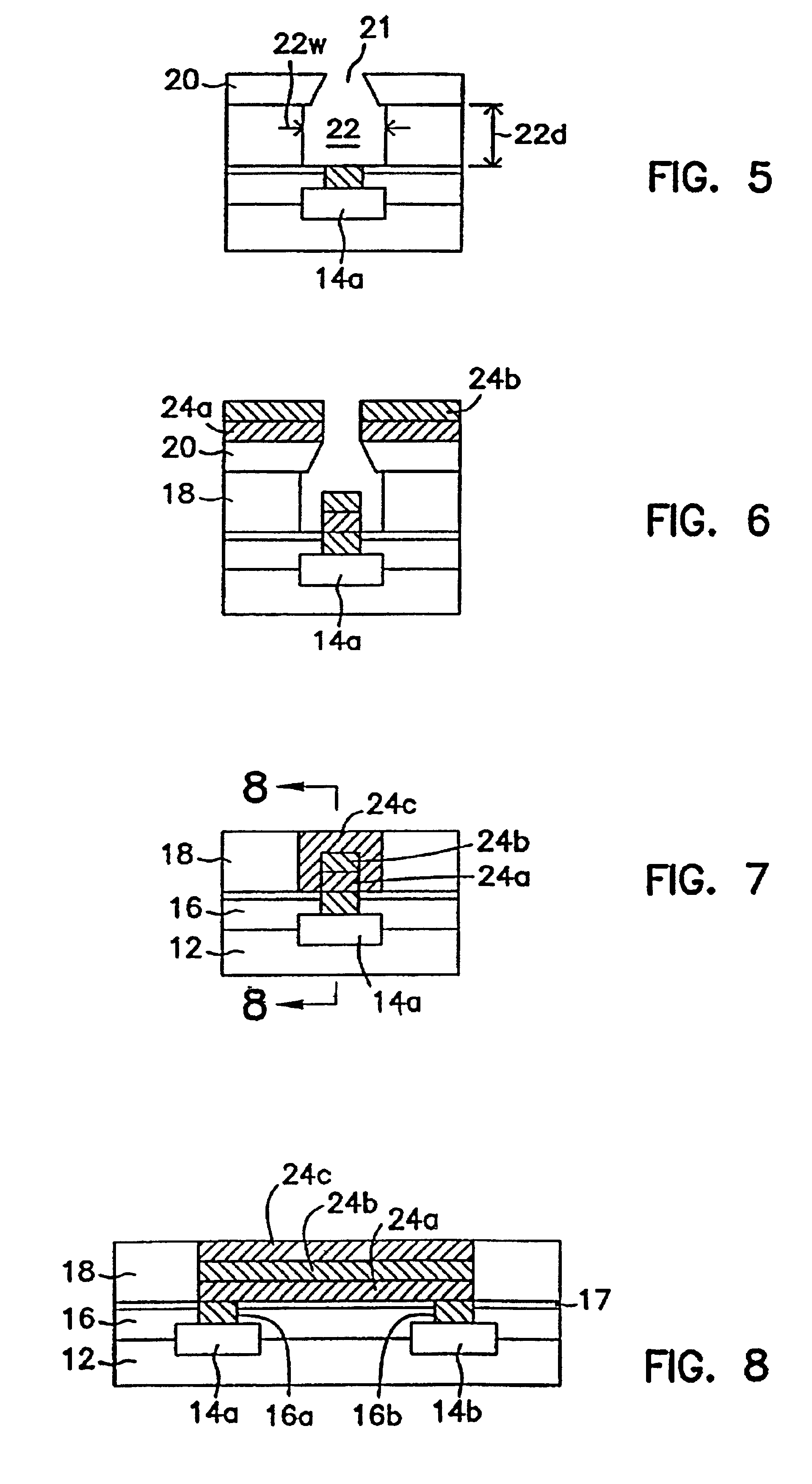

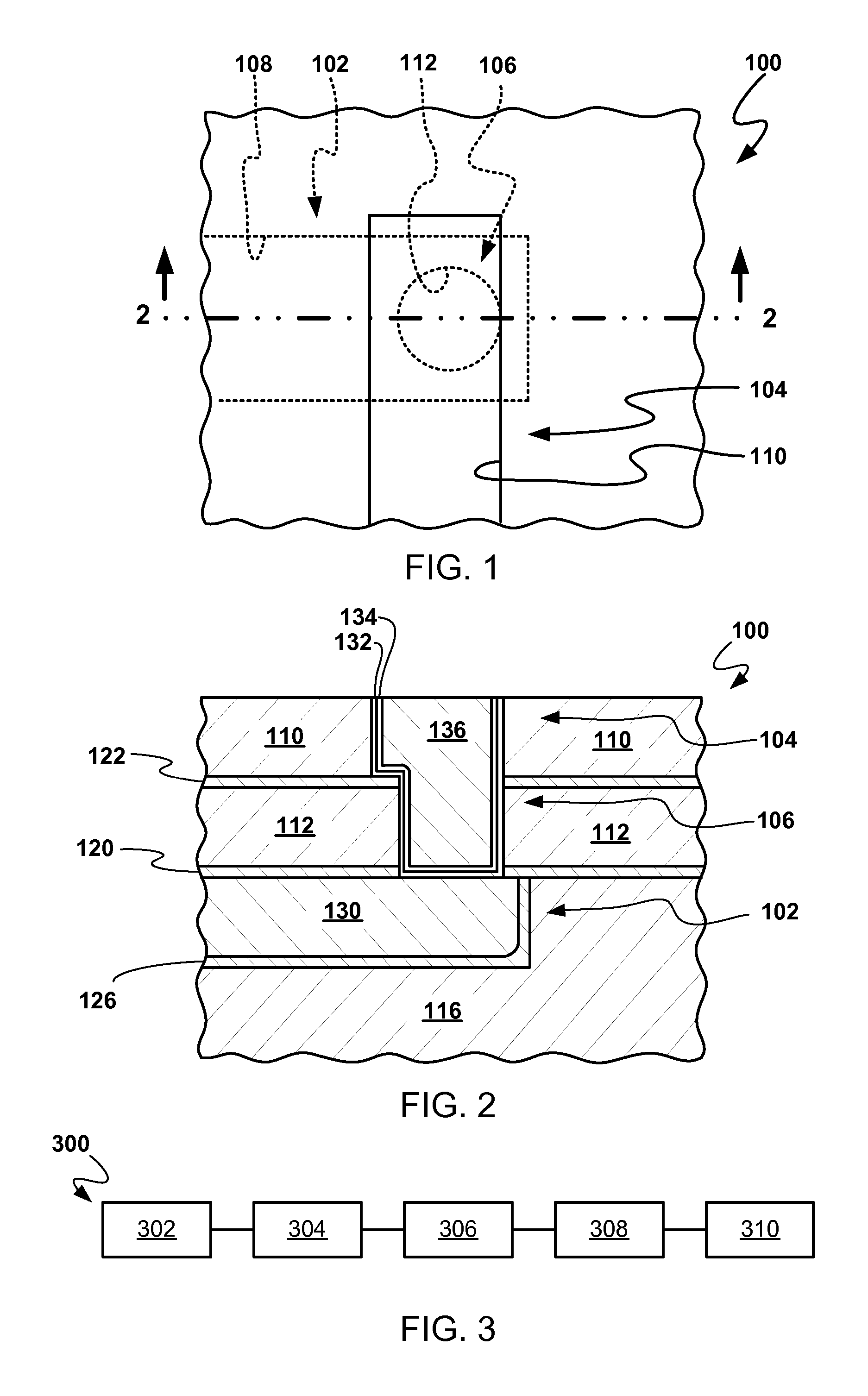

Conformal barrier liner in an integrated circuit interconnect

InactiveUS6989604B1Improve adhesionSmall sizeSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorIntegrated circuit interconnect

An integrated circuit having a substrate and a semiconductor device thereon. A stop layer over the substrate has a first dielectric layer formed thereon having an opening into which a first conformal barrier is formed. A first conformal barrier liner is formed in the opening, processed, and treated to improve adhesion. Portions of the first conformal barrier liner on the sidewalls act as a barrier to diffusion of conductor core material to the first dielectric layer. A conductor material is formed in the opening over the vertical portions of the first conformal barrier liner and the first stop layer.

Owner:INNOVATIVE FOUNDRY TECH LLC

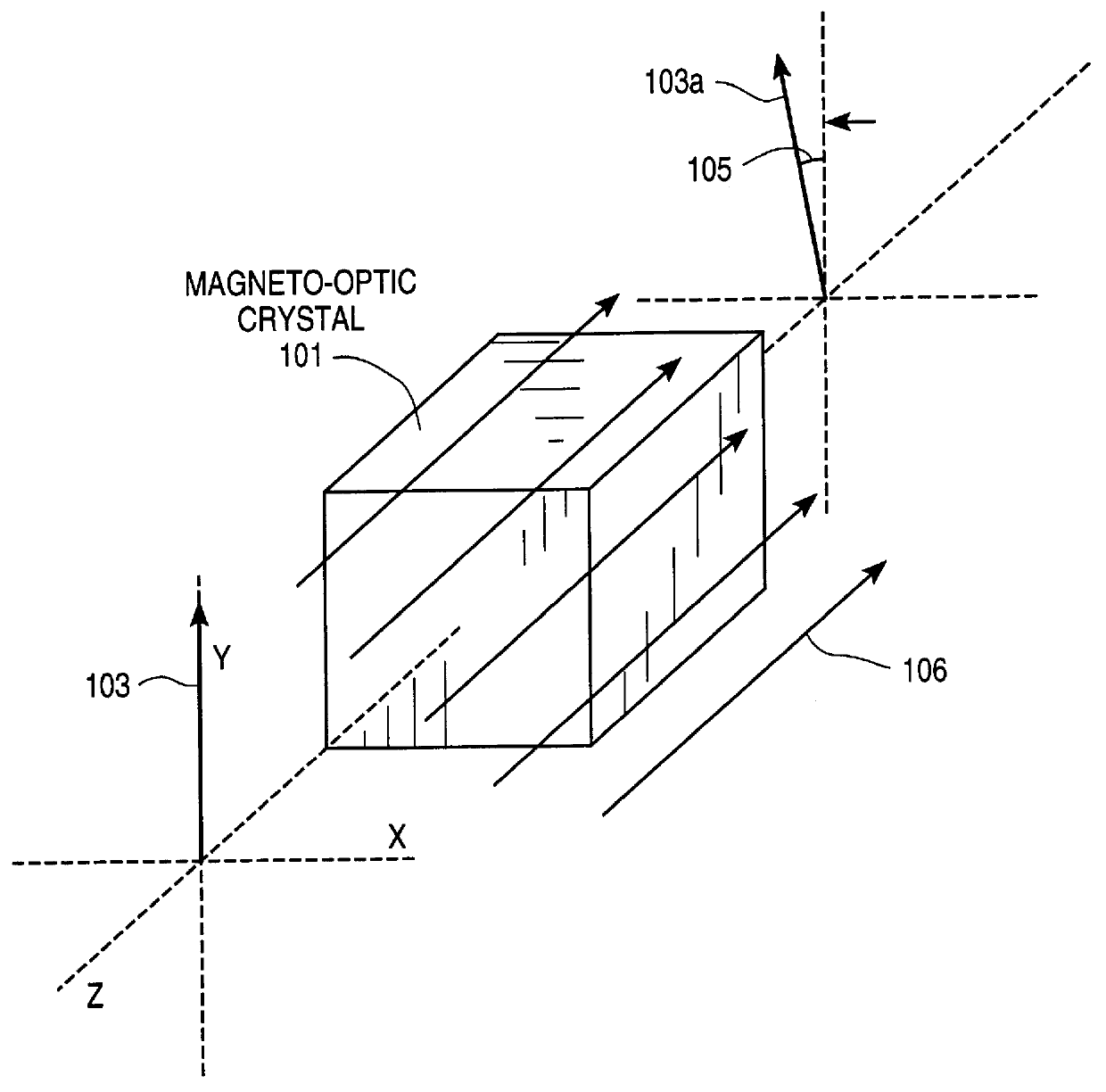

Method for performing quantitative measurement of DC and AC current flow in integrated circuit interconnects by the measurement of magnetic fields with a magneto optic laser probe

InactiveUS6084396AVoltage/current isolationMagnitude/direction of magnetic fieldsElectrical conductorIntegrated circuit interconnect

A laser probe for measuring a magnetic field is disclosed. A polarized laser beam is passed through a magneto-optic crystal in the presence of an unknown magnetic field. The rotation of the polarization which occurs through the magneto-optic crystal is measured in order to determine the magnitude of the magnetic field. The measured magnetic field is used to determine, for example, the current through a conductor such as an interconnect line on a semiconductor chip. A method of calibrating the magnetic field using a known magnetic from a solenoid is also disclosed. Further disclosed is a method of providing a zero-reference current by momentarily stopping the chip clock.

Owner:INTEL CORP

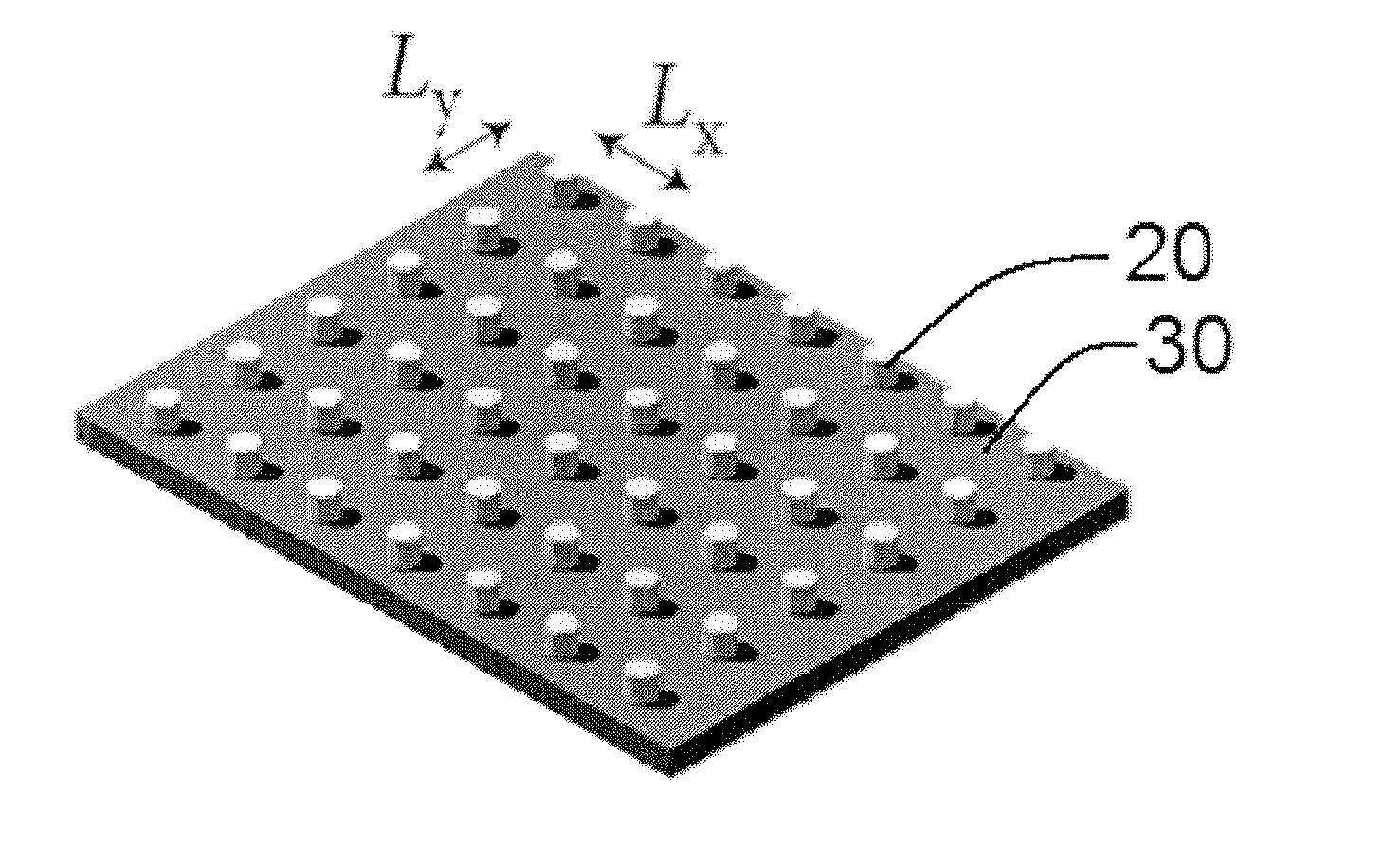

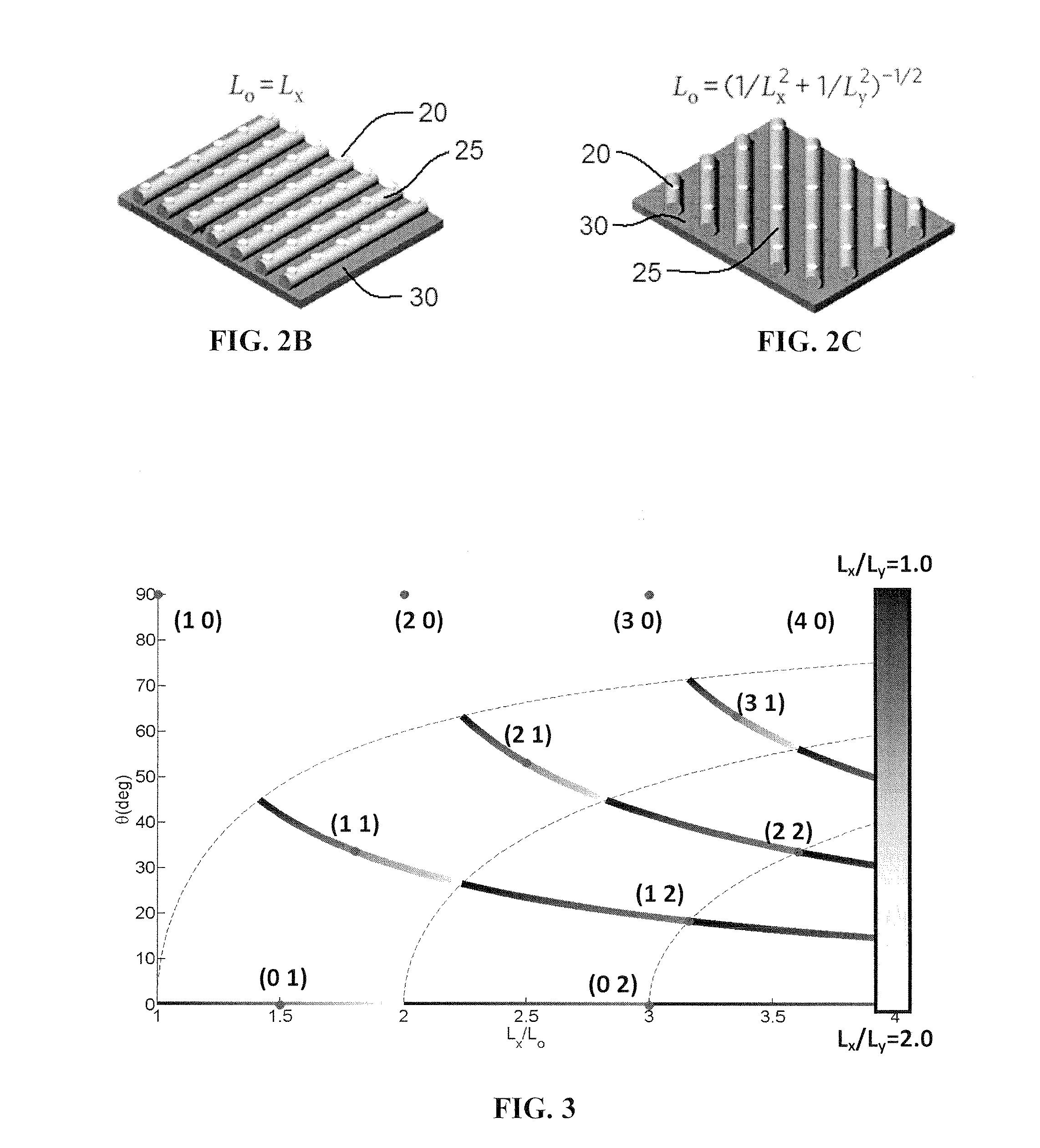

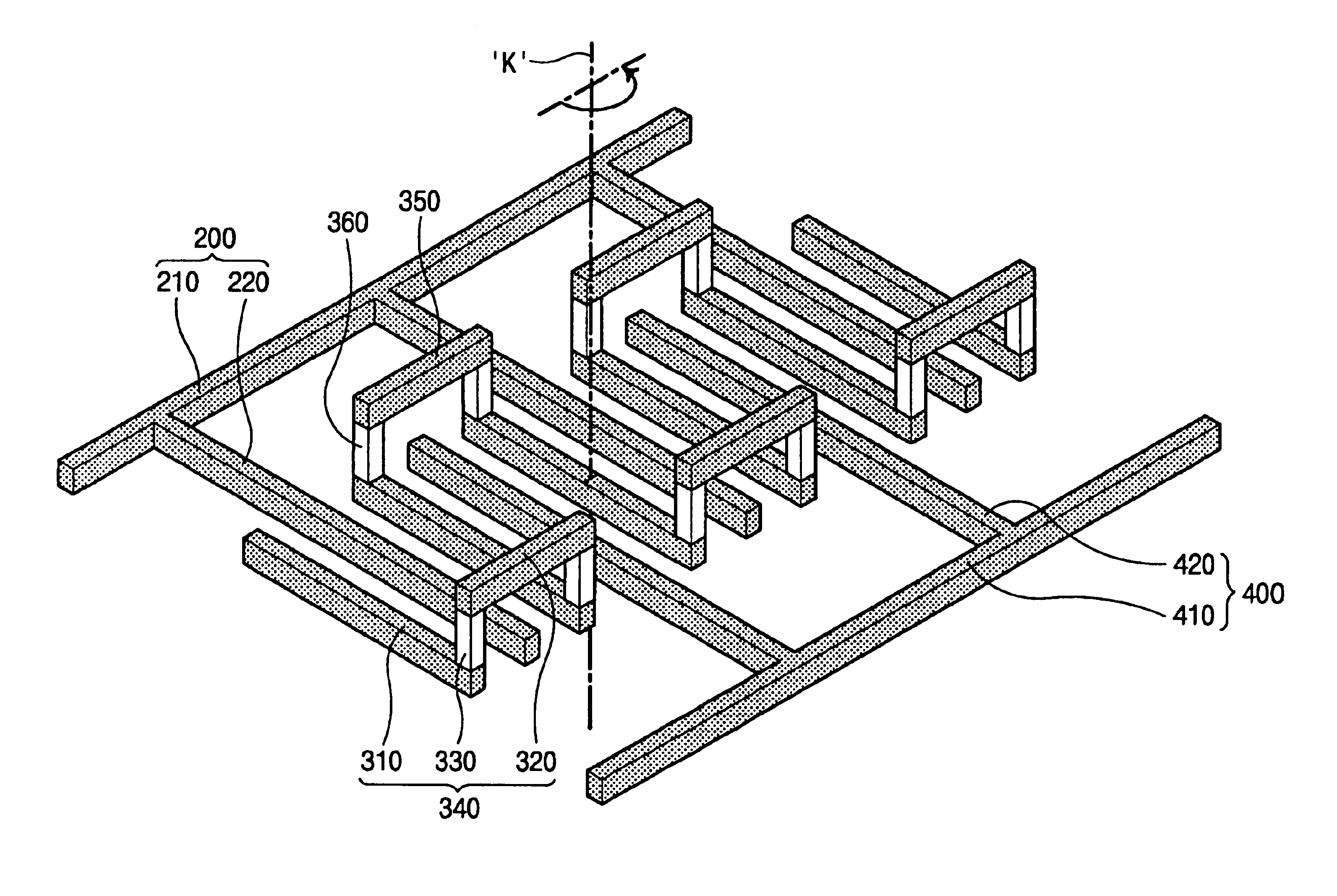

Guided self-assembly of block copolymer line structures for integrated circuit interconnects

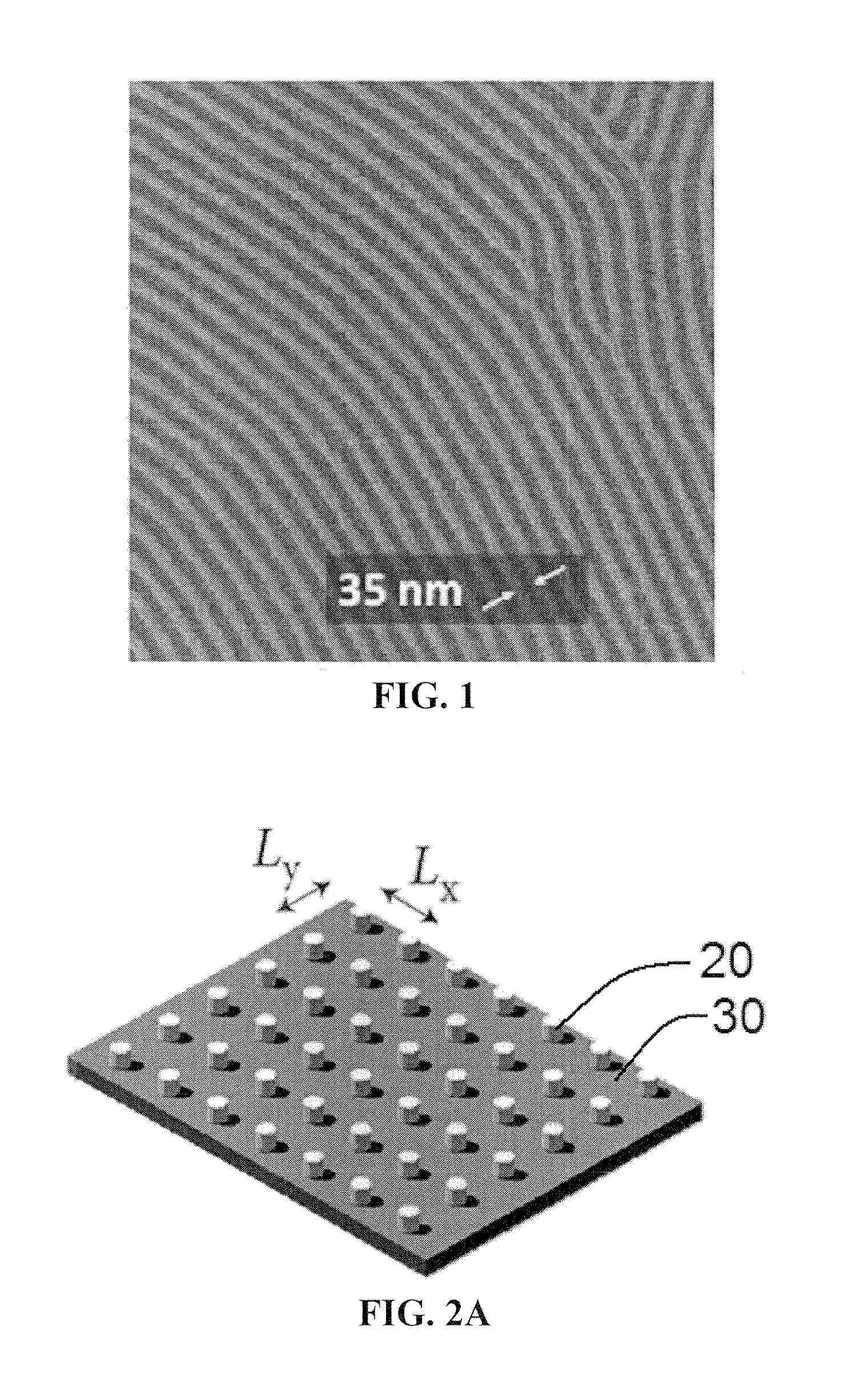

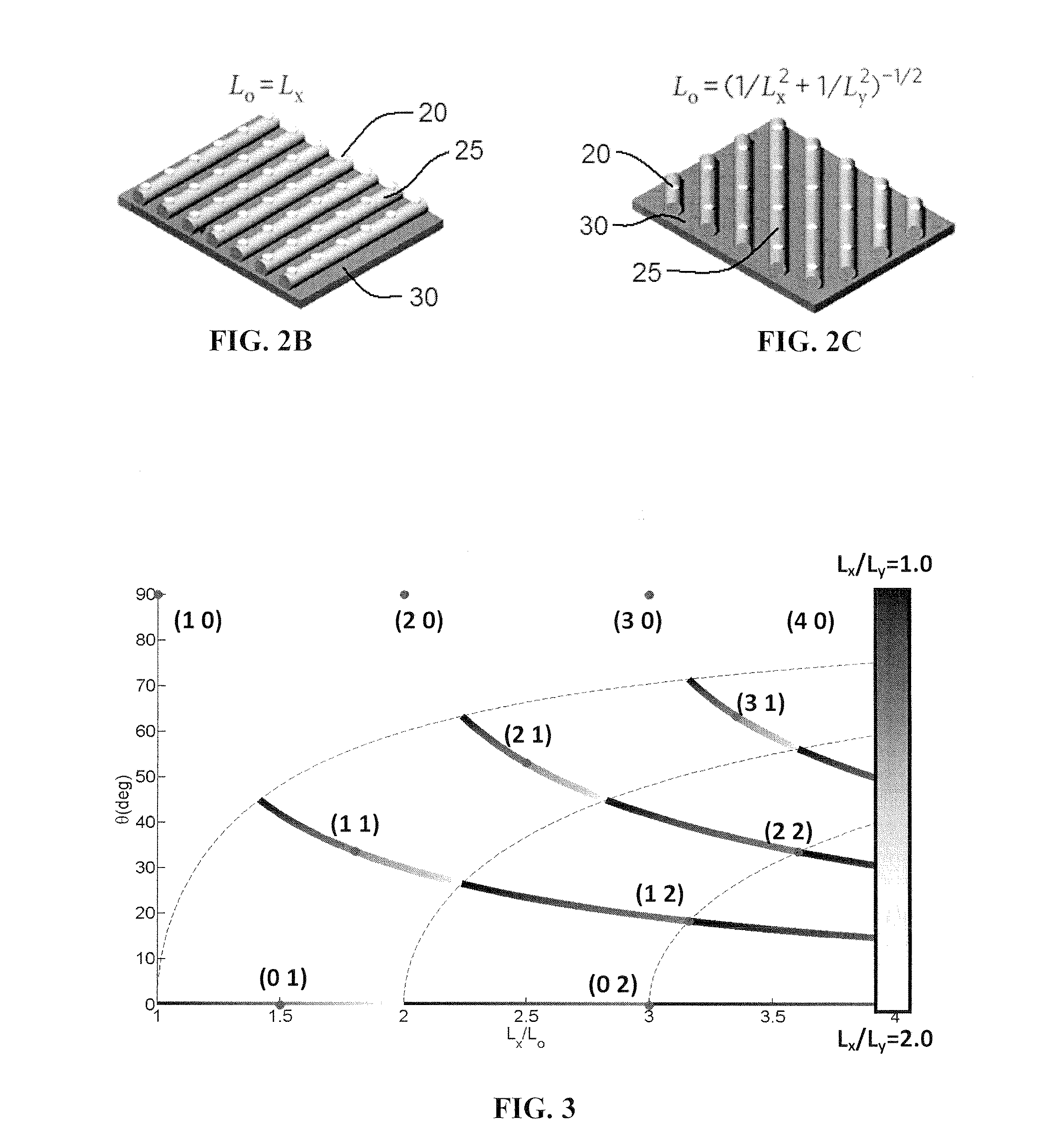

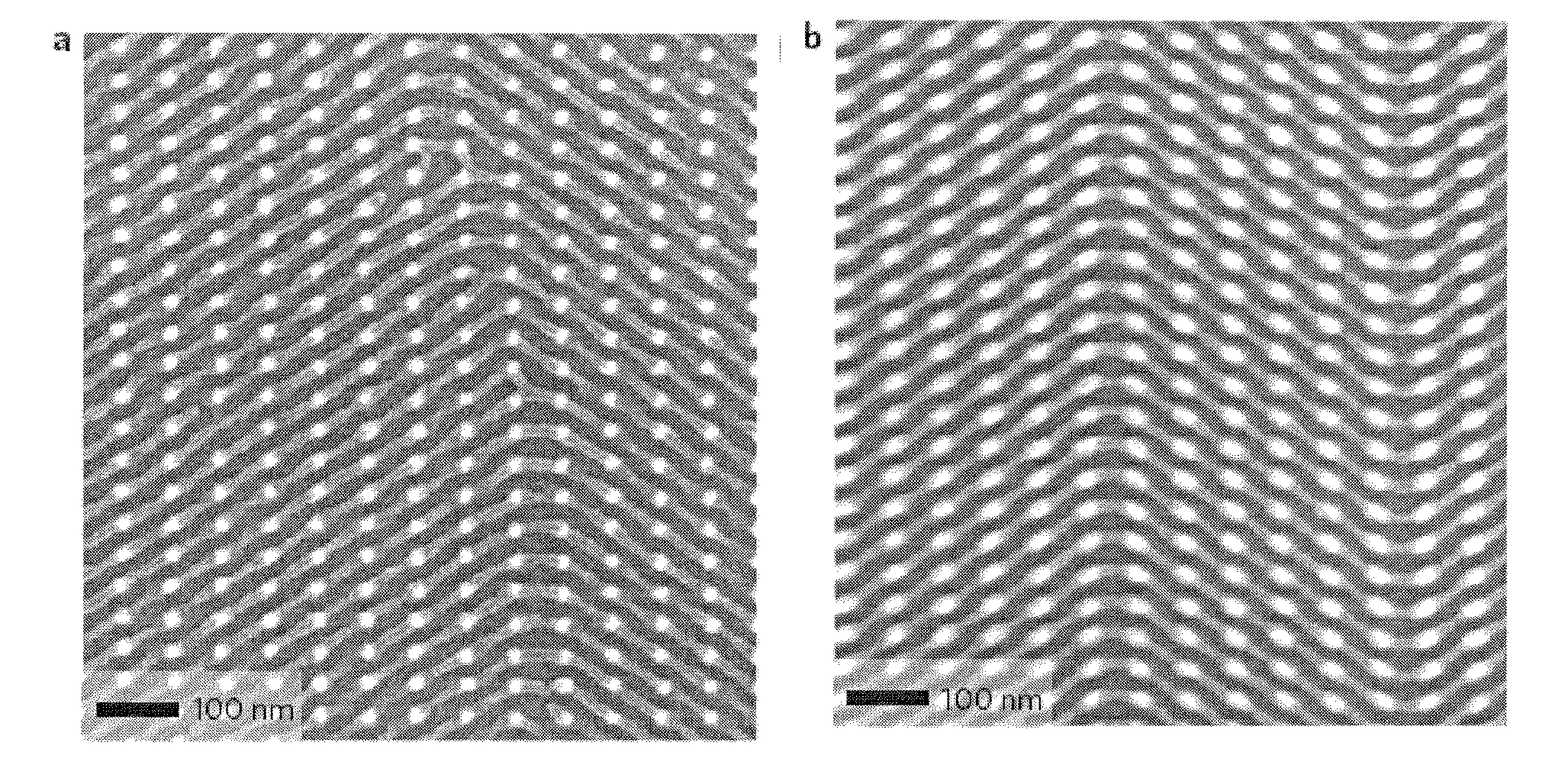

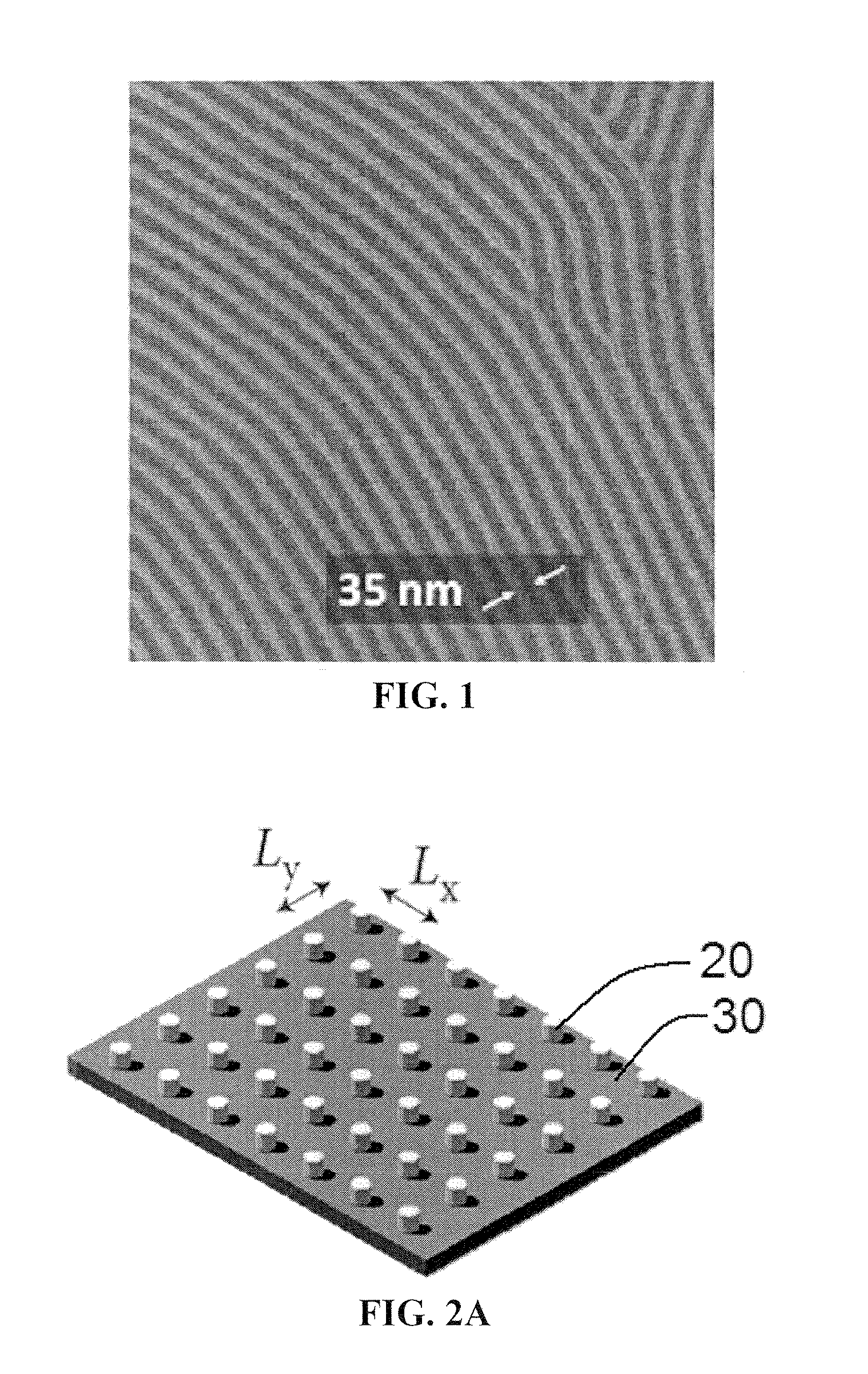

InactiveUS20120009390A1Minimizing densityLow costElectric discharge tubesDecorative surface effectsResistManufacturing technology

Complex self-assembled patterns can be created using a sparse template and local changes to the shape or distribution of the posts of the template to direct pattern generation of block copolymer. The post spacing in the template is formed commensurate with the equilibrium periodicity of the block copolymer, which controls the orientation of the linear features. Further, the posts can be arranged such that the template occupies only a few percent of the area of the final self-assembled patterns. Local aperiodic features can be introduced by changing the period or motif of the lattice or by adding guiding posts. According to one embodiment, an array of carefully spaced and shaped posts, prepared by electron-beam patterning of an inorganic resist, can be used to template complex patterns in a cylindrical-morphology block copolymer. These complex self-assembled patterns can form a mask used in fabrication processes of arbitrary structures such as interconnect layouts.

Owner:MASSACHUSETTS INST OF TECH

Guided self-assembly of block copolymer line structures for integrated circuit interconnects

InactiveUS8309278B2Minimizing densityArrangement is complexElectric discharge tubesDecorative surface effectsResistIntegrated circuit interconnect

Complex self-assembled patterns can be created using a sparse template and local changes to the shape or distribution of the posts of the template to direct pattern generation of block copolymer. The post spacing in the template is formed commensurate with the equilibrium periodicity of the block copolymer, which controls the orientation of the linear features. Further, the posts can be arranged such that the template occupies only a few percent of the area of the final self-assembled patterns. Local aperiodic features can be introduced by changing the period or motif of the lattice or by adding guiding posts. According to one embodiment, an array of carefully spaced and shaped posts, prepared by electron-beam patterning of an inorganic resist, can be used to template complex patterns in a cylindrical-morphology block copolymer. These complex self-assembled patterns can form a mask used in fabrication processes of arbitrary structures such as interconnect layouts.

Owner:MASSACHUSETTS INST OF TECH

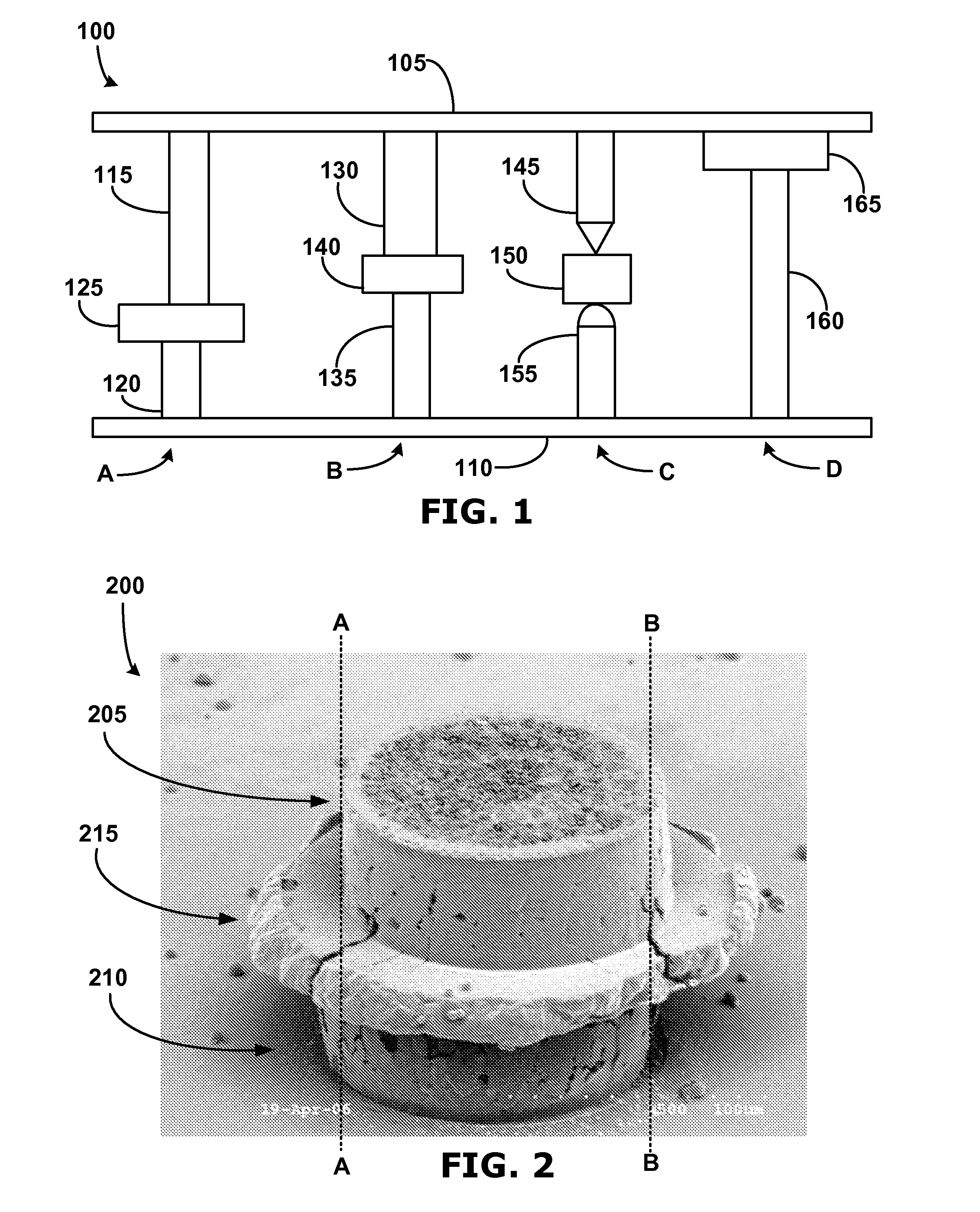

Nano-electrode-array for integrated circuit interconnects

ActiveUS7226856B1NanotechSemiconductor/solid-state device manufacturingNanoelectrode arrayIntegrated circuit interconnect

An integrated circuit and a method of manufacturing an integrated circuit is provided including providing an integrated circuit having a trench and via provided in a dielectric layer. A nano-electrode-array is formed over the dielectric layer in the trench and via, and a conductor is deposited over the nano-electrode-array. The conductor and the nano-electrode-array are coplanar with a surface of the dielectric layer.

Owner:KLA TENCOR CORP

Forming submicron integrated-circuit wiring from gold, silver, copper, and other metals

InactiveUS6849927B2Reduced responsePreserves insulativeSemiconductor/solid-state device detailsSolid-state devicesCapacitanceElectrical resistance and conductance

A typical integrated circuit interconnects millions of microscopic transistors and resistors with aluminum wires buried in silicon-dioxide insulation. Yet, aluminum wires and silicon-dioxide insulation are a less attractive combination than gold, silver, or copper wires combined with polymer-based insulation, which promise both lower electrical resistance and capacitance and thus faster, more efficient circuits. Unfortunately, conventional etch-based techniques are ineffective with gold, silver, or copper, and conventional polymer formation promote reactions with metals that undermine the insulative properties of polymer-based insulations. Accordingly, the inventor devised methods which use a liftoff procedure to avoid etching problems and a non-acid-polymeric precursor and non-oxidizing cure procedure to preserve the insulative properties of the polymeric insulator. The resulting interconnective structures facilitate integrated circuits with better speed and efficiency.

Owner:ROUND ROCK RES LLC

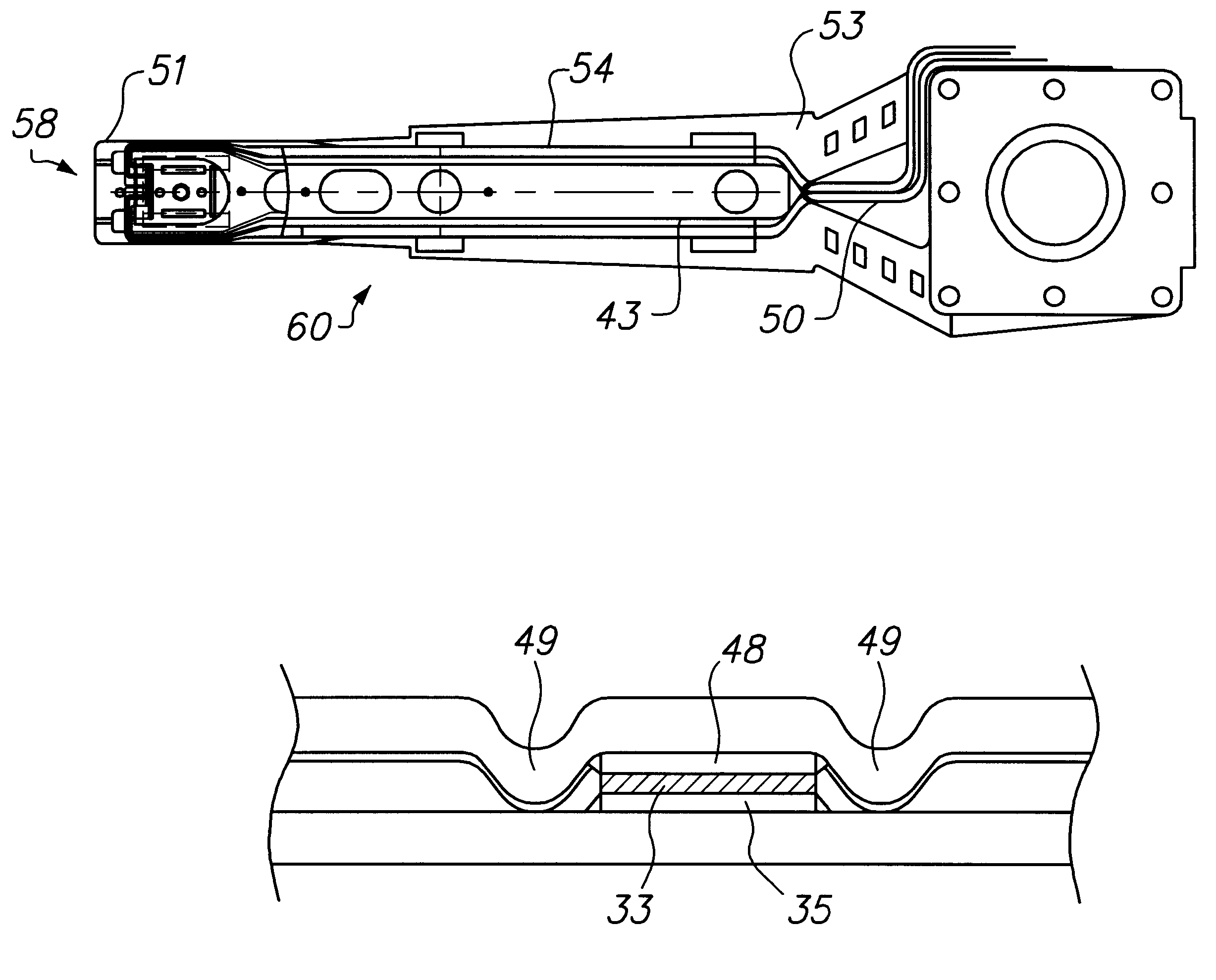

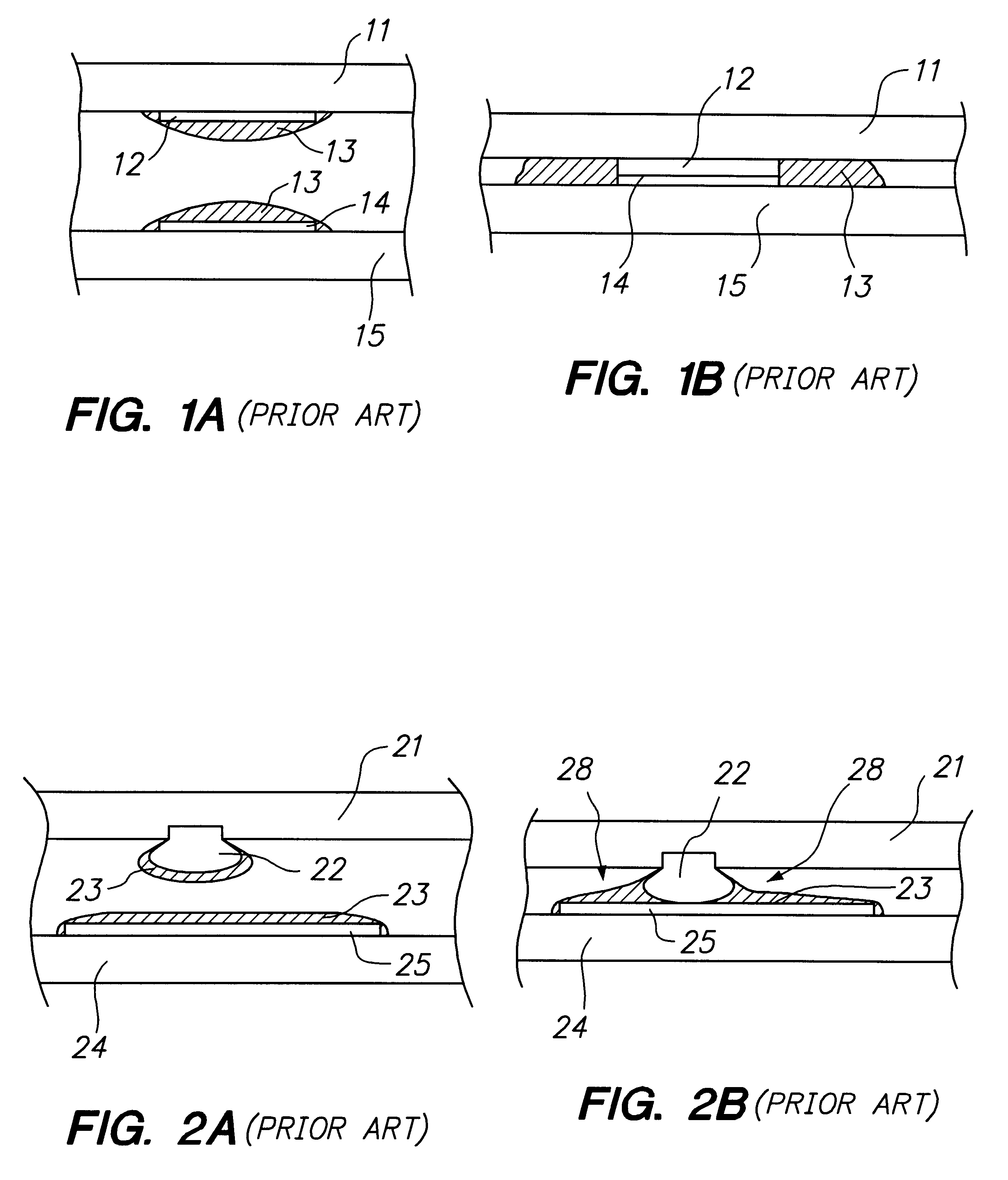

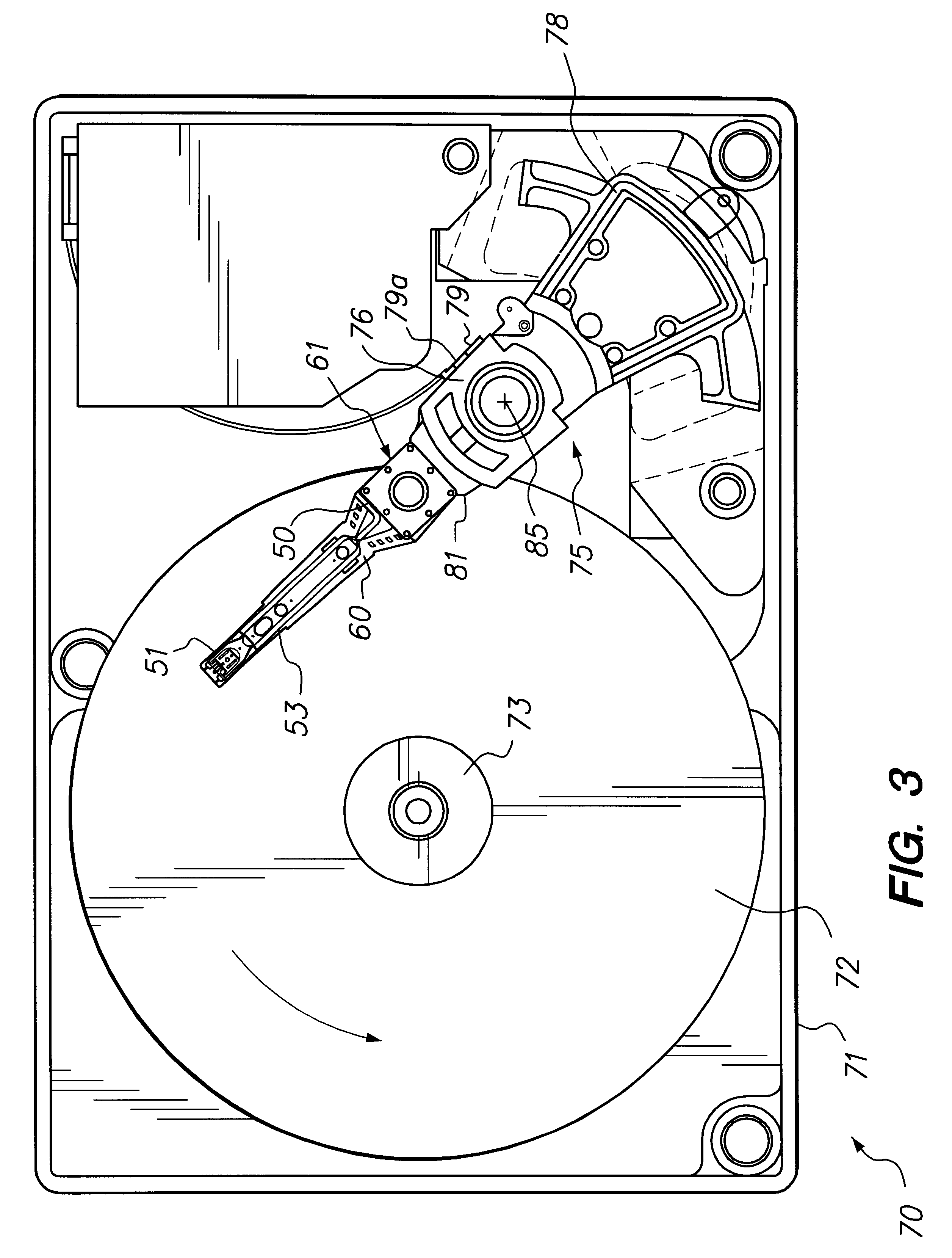

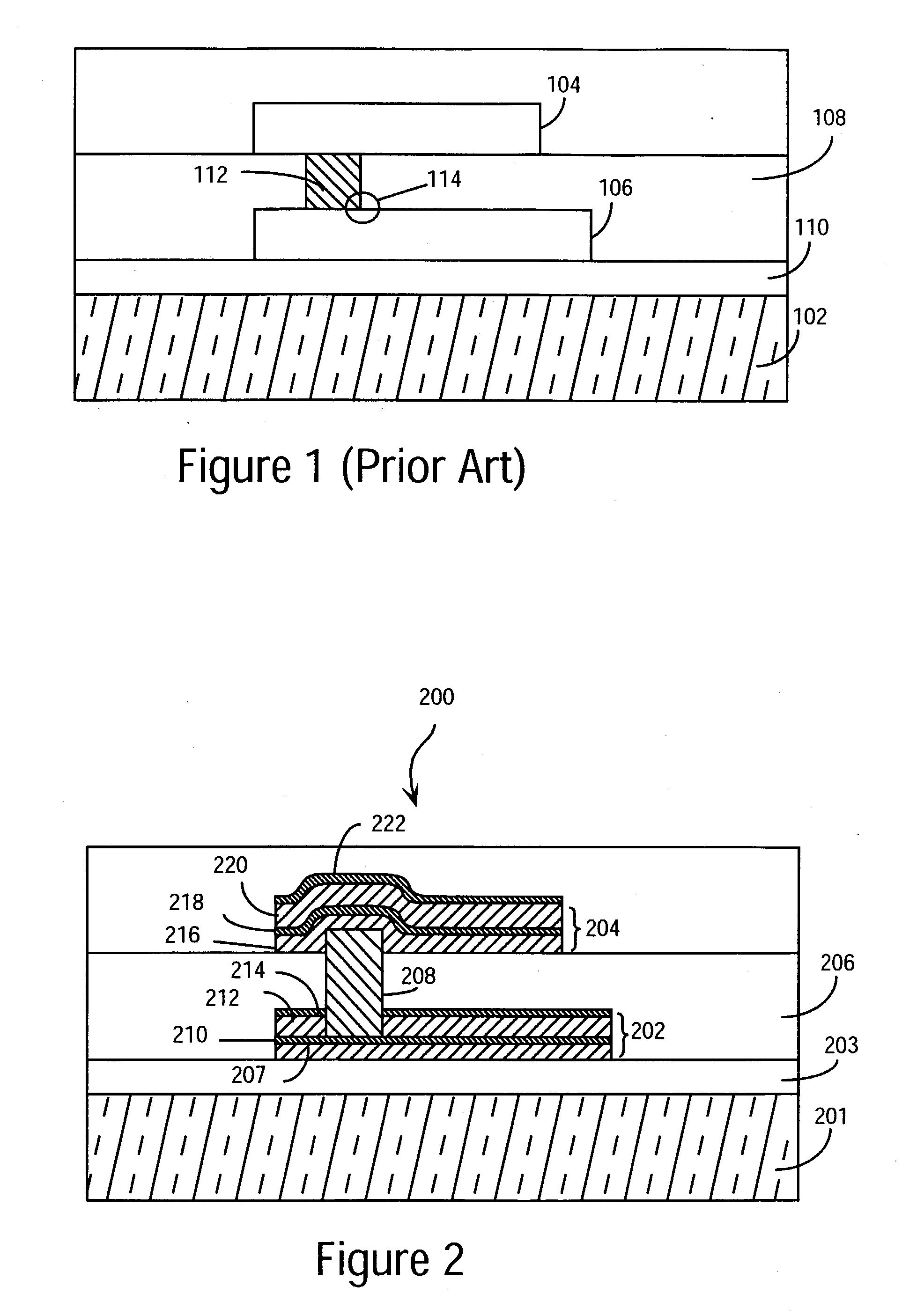

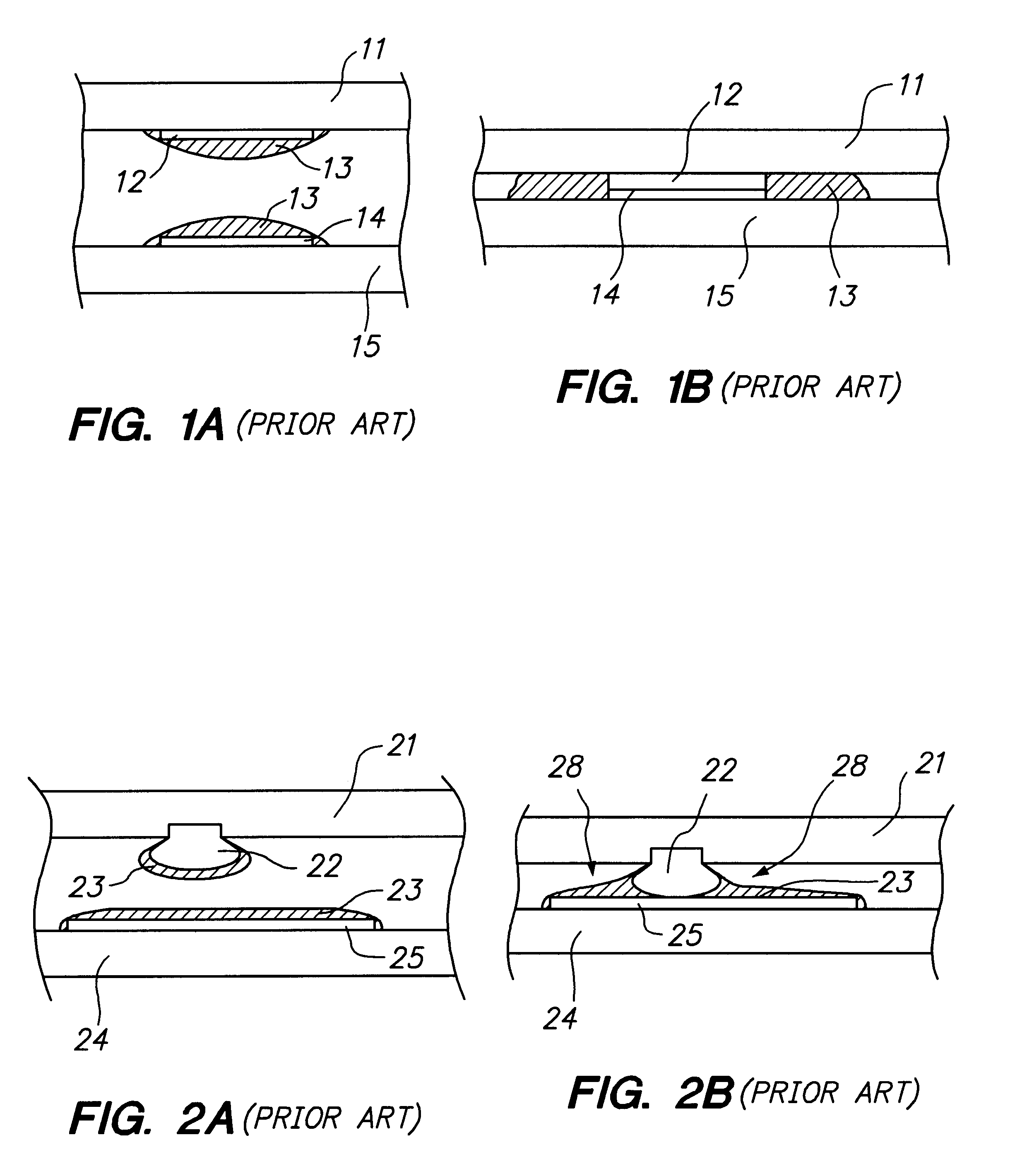

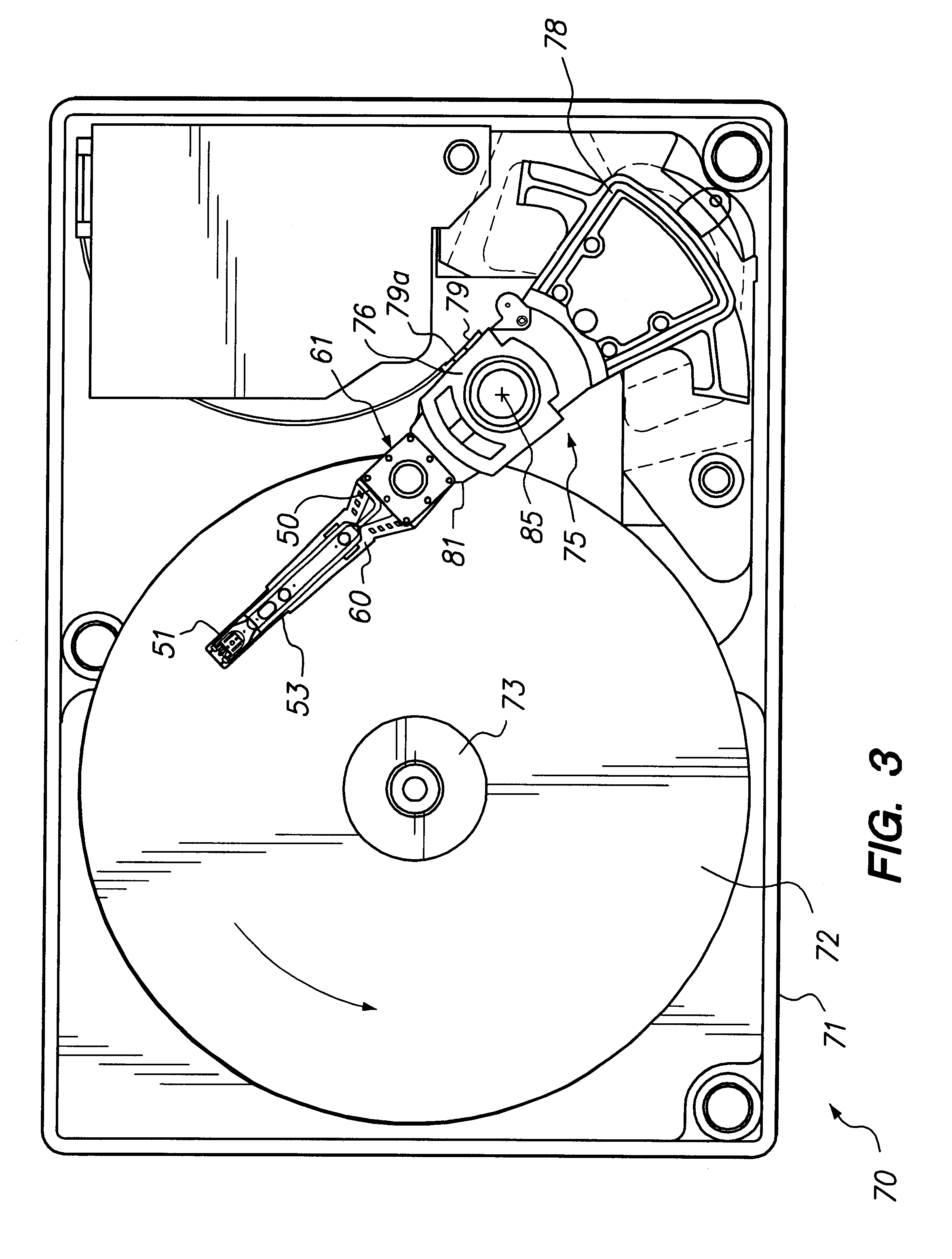

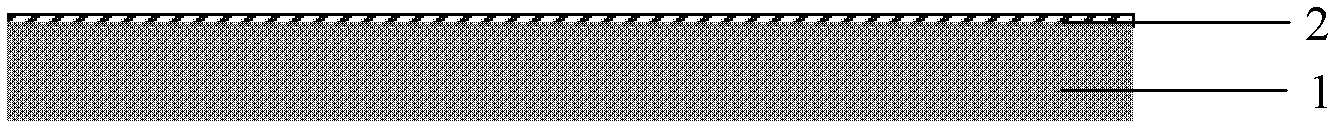

Mechanically formed standoffs in a circuit interconnect

InactiveUS6246548B1Low costReliable connectorPrinted circuit assemblingElectrical connection between head and armIntegrated circuit interconnectBonding process

Mechanically formed standoffs in a disk drive integrated circuit interconnect reduces the cost of manufacturing and improves the reliability of the electrical interconnections thereof. Connection pads defined along the interconnect are bonded with bonding pads of a signal producing source and a signal processing source. The standoffs provide mechanical stops during the bonding process, enabling sufficient bonding material to form between bonding areas. The standoffs are mechanically formed with a punch and die assembly either directly through a bonding pad predefined along traces on the interconnect or adjacent the bonding pad. The standoffs formed through the bonding pads are covered with solder or other electrically conductive bonding material.

Owner:MAXTOR

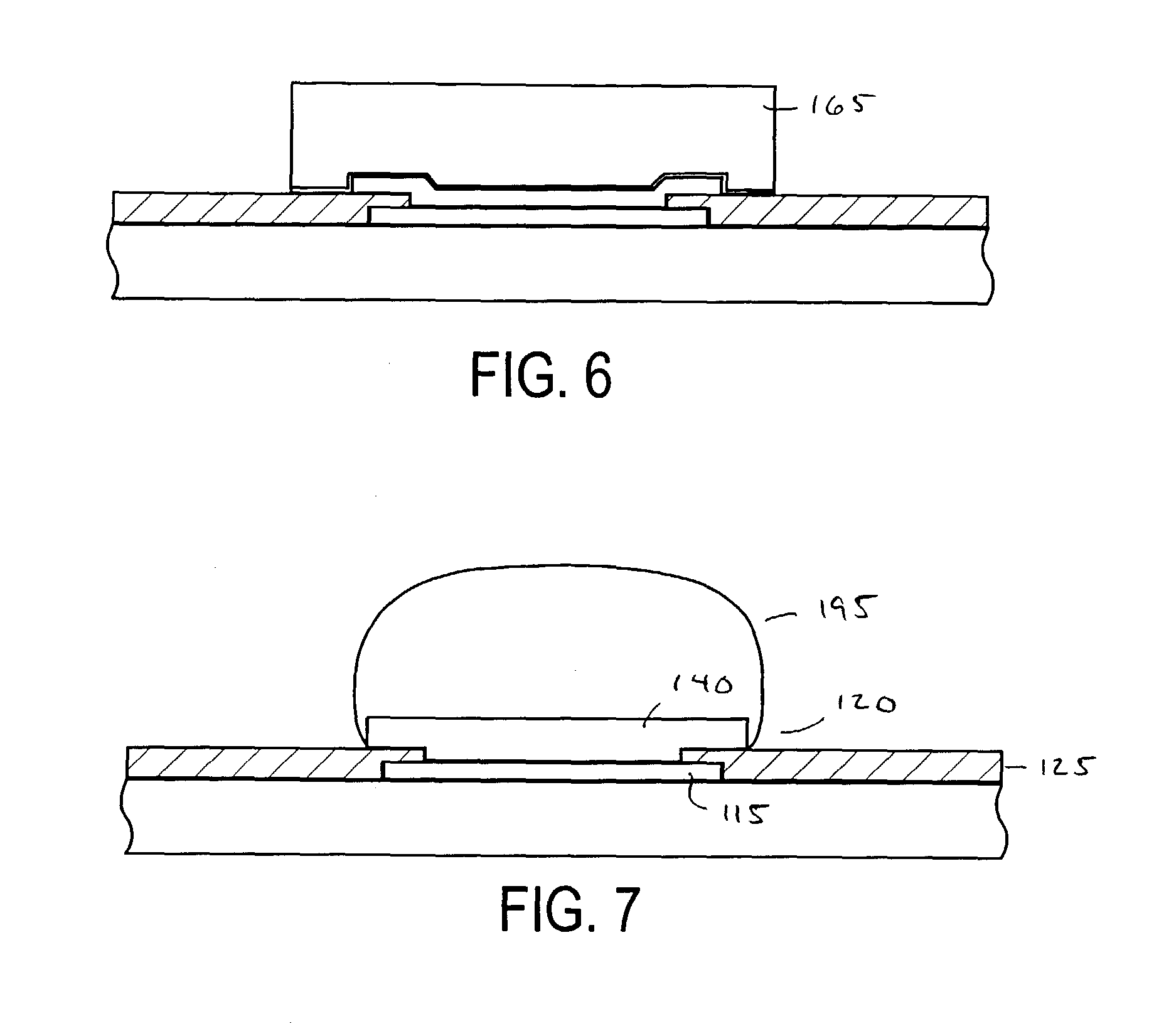

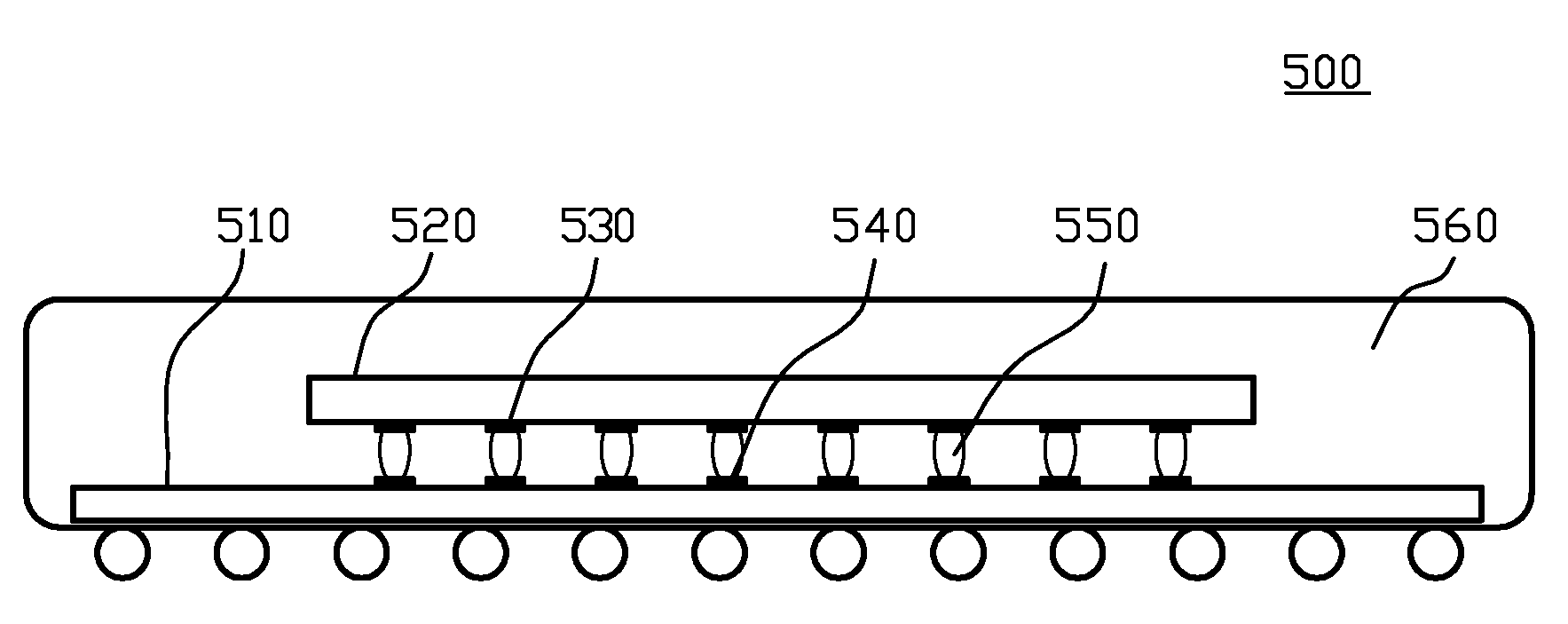

Integrated Circuit Interconnect Method and Apparatus

InactiveUS20100025863A1Low costImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit interconnectElectrical connection

Techniques for interconnecting an IC chip and a receiving substrate are provided. A method includes the steps of: providing the IC chip, the IC chip including at least a first connection site formed thereon; providing the receiving substrate, the receiving substrate including at least a second connection site formed thereon; forming an alloy structure on at least a portion of an upper surface of the second connection site; orienting the IC chip relative to the receiving substrate so that the at least first connection site is aligned with the alloy deposit formed on the at least second connection site; and forming an electrical connection between the first and second connection sites, the electrical connection comprising a volume of electrically conductive fusible material, wherein a majority of the volume of electrically conductive fusible material is supplied from the alloy structure.

Owner:IBM CORP

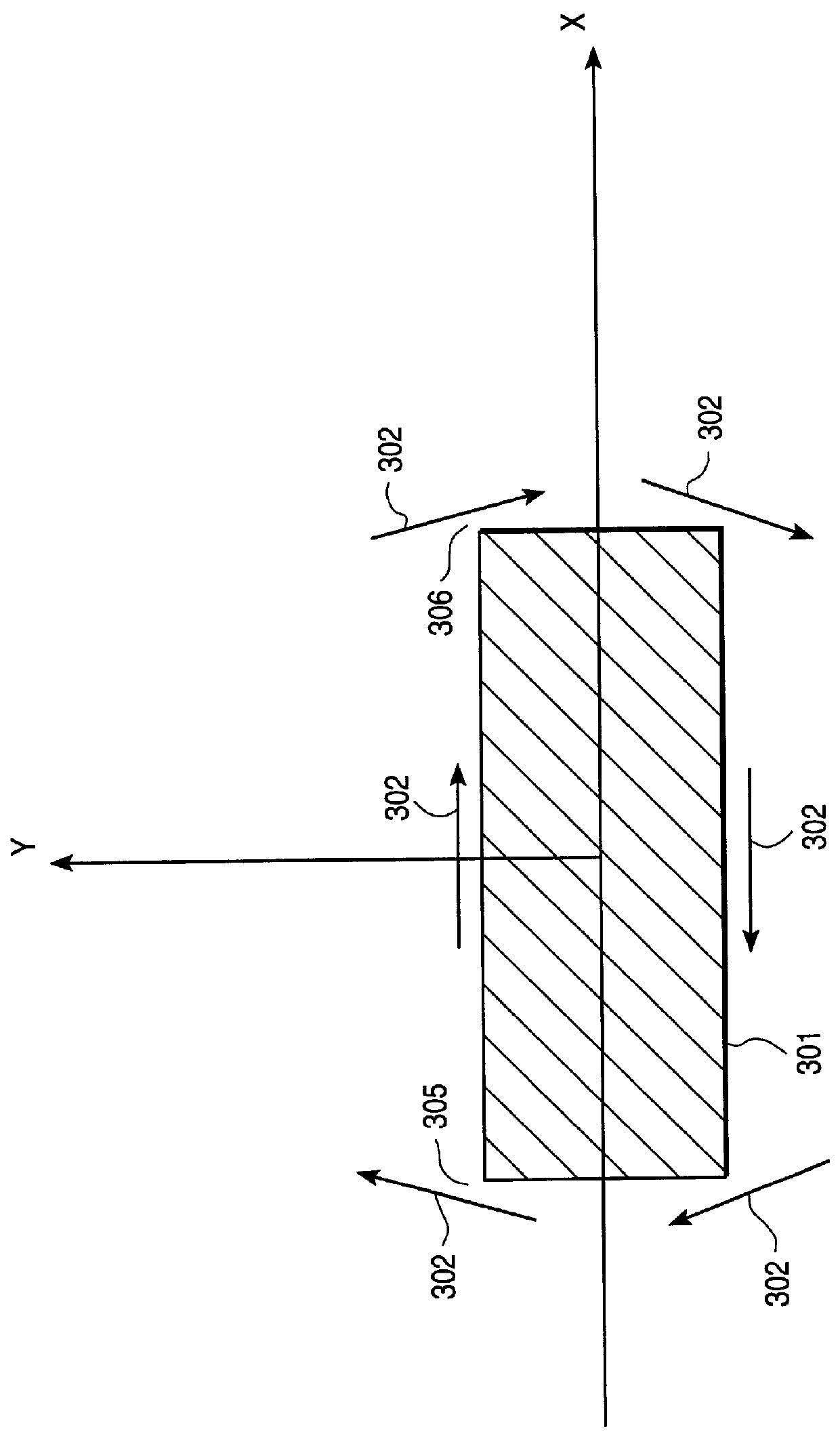

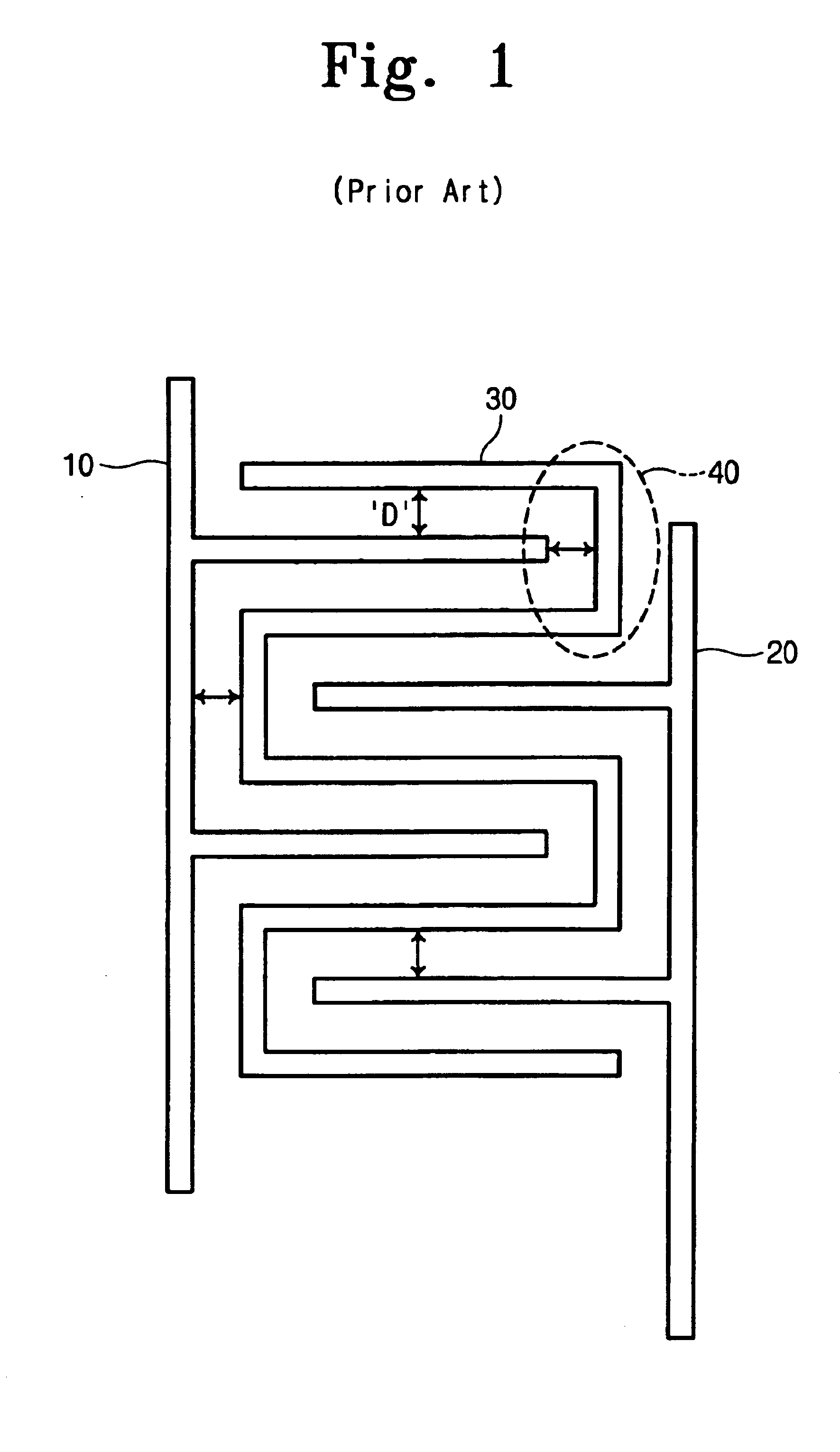

Apparatus for testing reliability of interconnection in integrated circuit

InactiveUS6842028B2Detected particularly easily and effectivelyElectronic circuit testingIndividual semiconductor device testingElectricityIntegrated circuit interconnect

In the present invention, an apparatus of testing a leakage protection reliability of an integrated circuit interconnection. The apparatus has at least one comb-like pattern, a serpentine-like pattern and means of applying a bias to the patterns and forms a maximum field region at an interconnection formed around a via, i.e., at the end of a tooth portion composing the comb-like pattern. In one structure of the present invention, the comb-like pattern is formed at one level, and the serpentine-like pattern has a plurality of unit parts corresponding to the tooth portions, respectively, and connection parts connecting the neighboring two unit parts. Each of the unit parts is formed at the same level with the comb-like pattern and spaced apart from the tooth portion by a minimum design length according to a design rule. The unit part has vias formed through an interlayer dielectric layer at the both ends of a tooth parallel part, two tooth parallel parts connected with the vias, respectively, and a length parallel part electrically connecting two tooth parallel parts.

Owner:SAMSUNG ELECTRONICS CO LTD

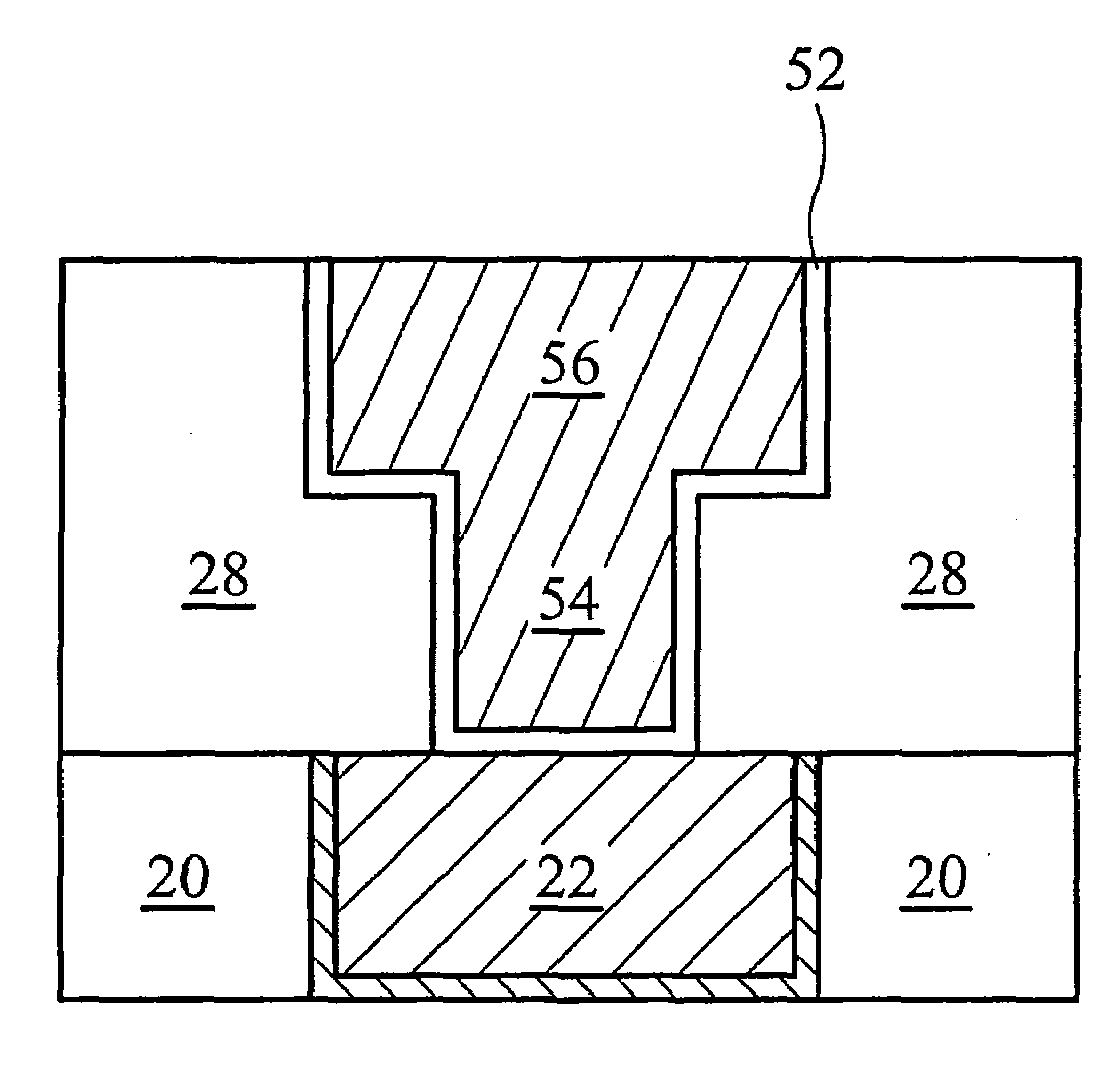

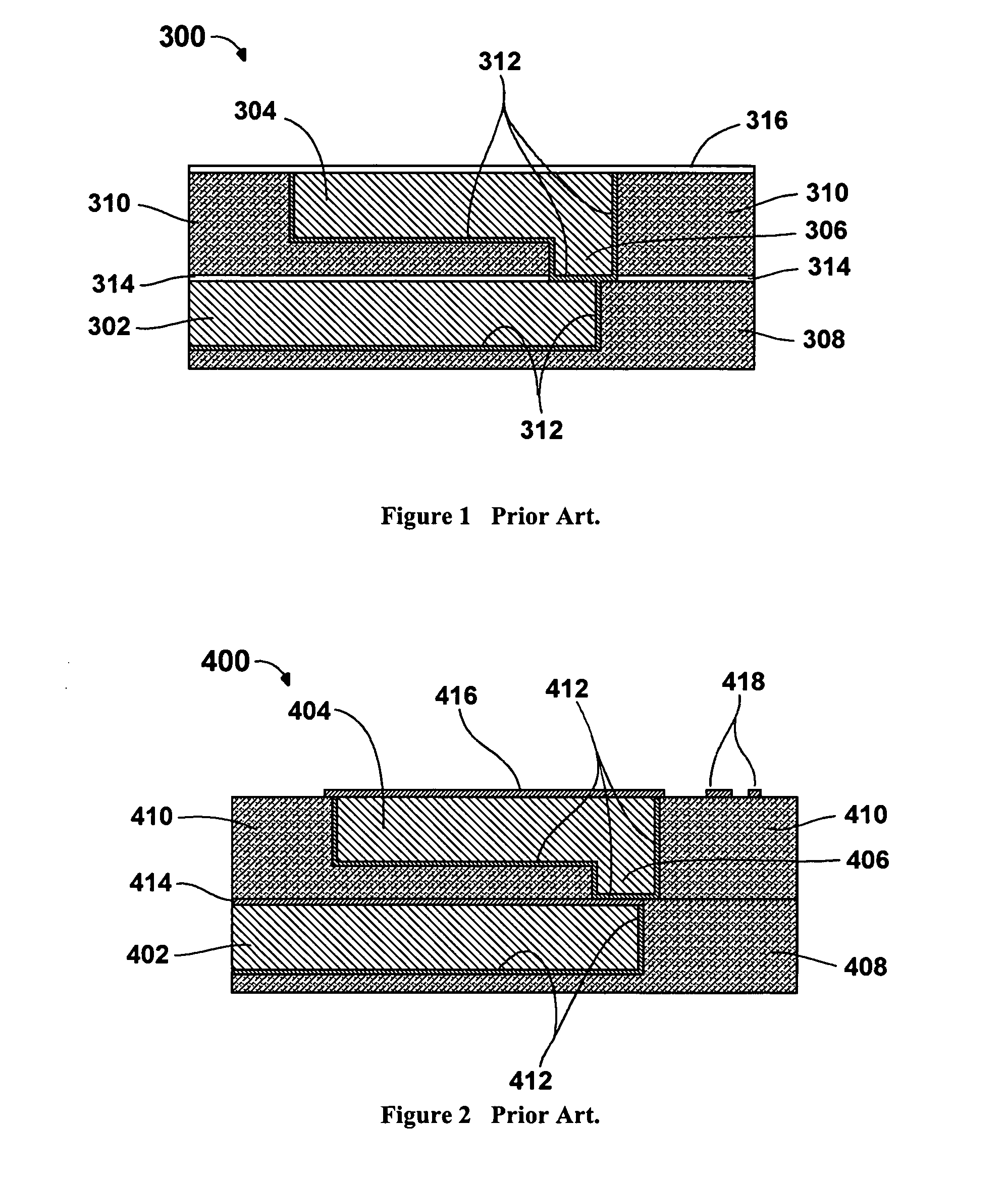

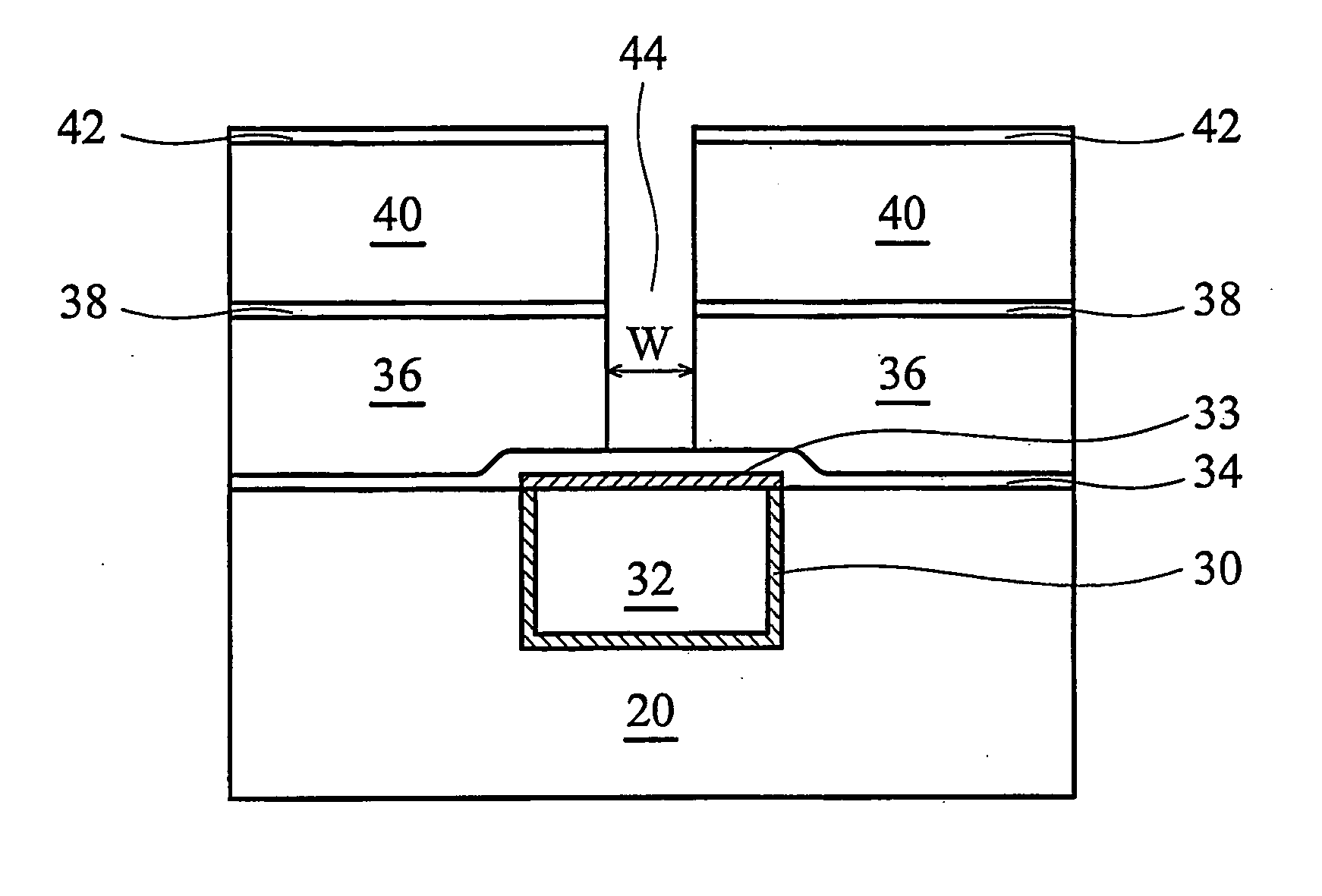

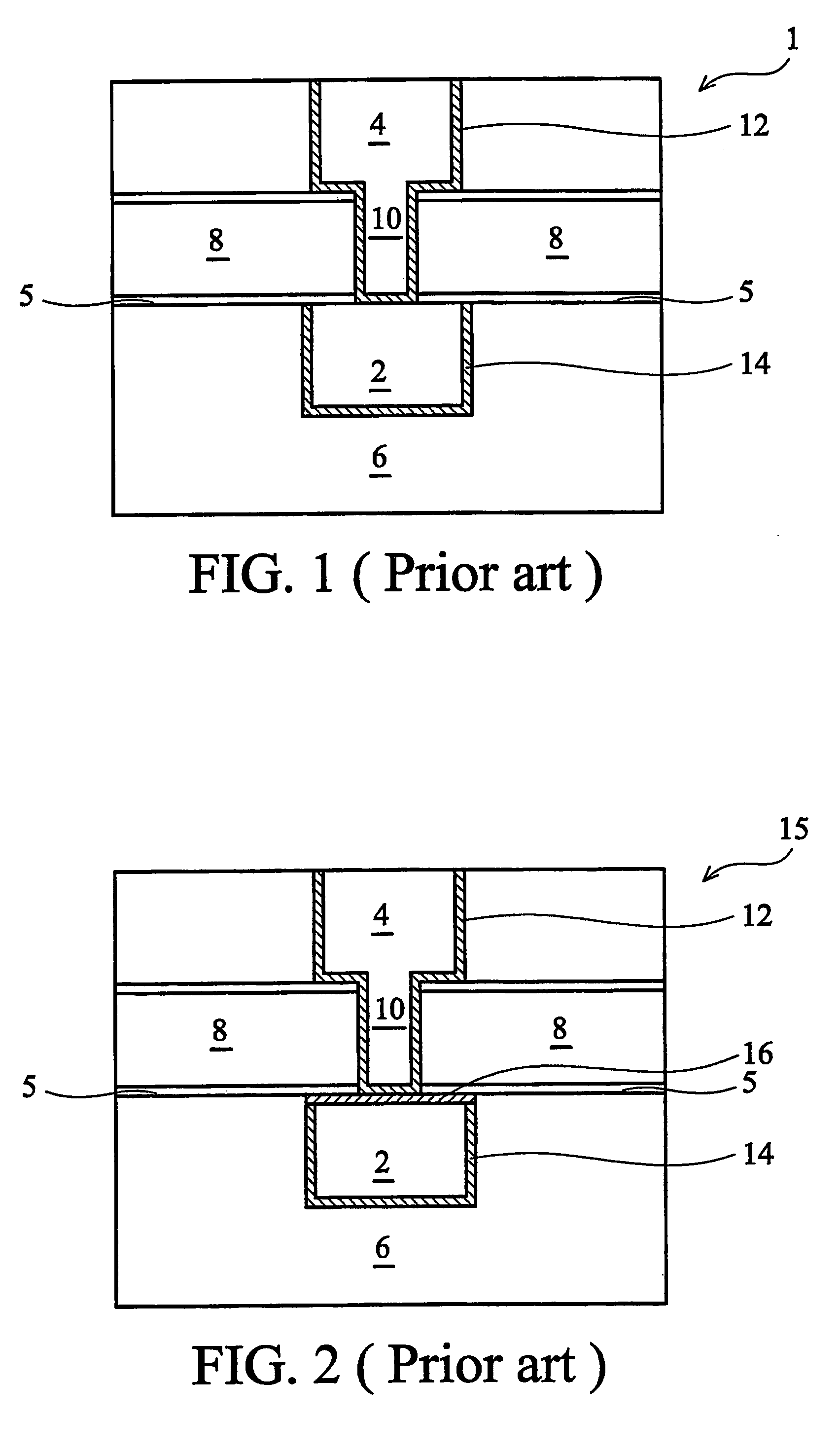

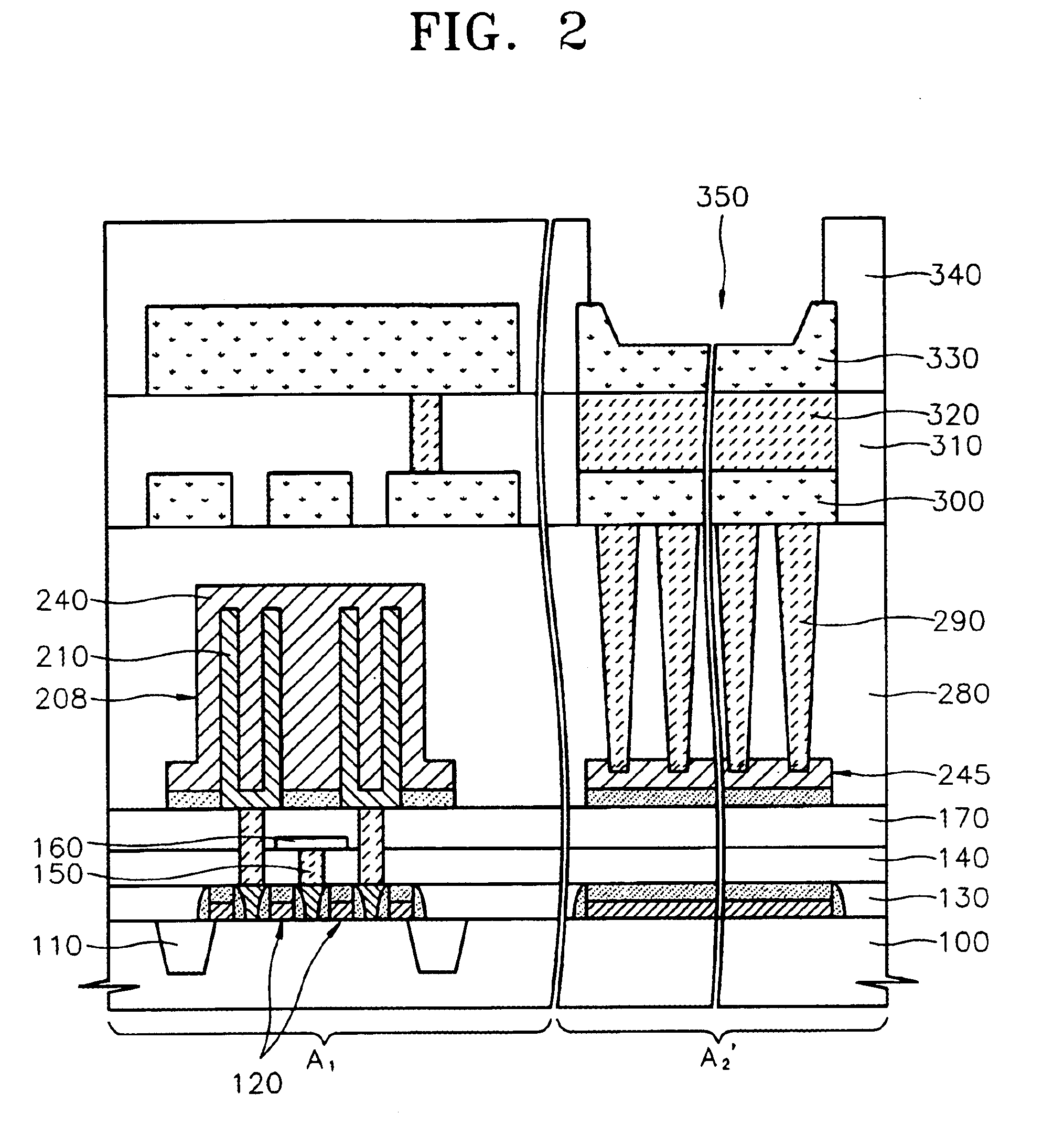

Damascene interconnect structure with cap layer

ActiveUS7259463B2Improve performanceImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesDielectricIntegrated circuit interconnect

A method of forming an integrated circuit interconnect structure is presented. A first conductive line is formed over a semiconductor substrate. A conductive cap layer is formed on the first conductive line to improve device reliability. An etch stop layer (ESL) is formed on the conductive cap layer. An inter-level dielectric (IMD) is formed on the ESL. A via opening and a trench are formed in the ESL, IMD, and conductive cap layer. A recess is formed in the first conductive line. The recess can be formed by over etching when the first dielectric is etched, or by a separate process such as argon sputtering. A second conductive line is formed filling the trench, opening and recess.

Owner:TAIWAN SEMICON MFG CO LTD

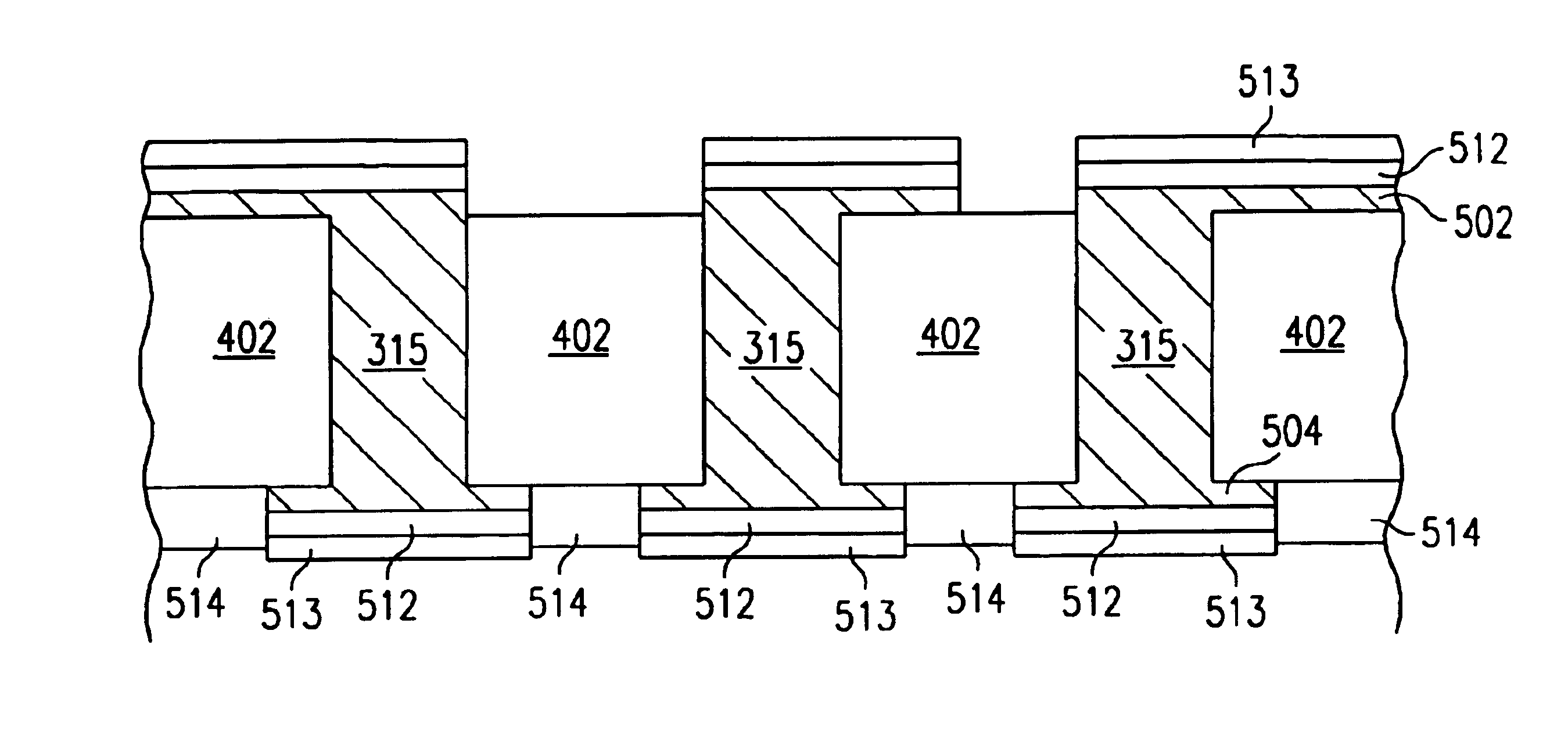

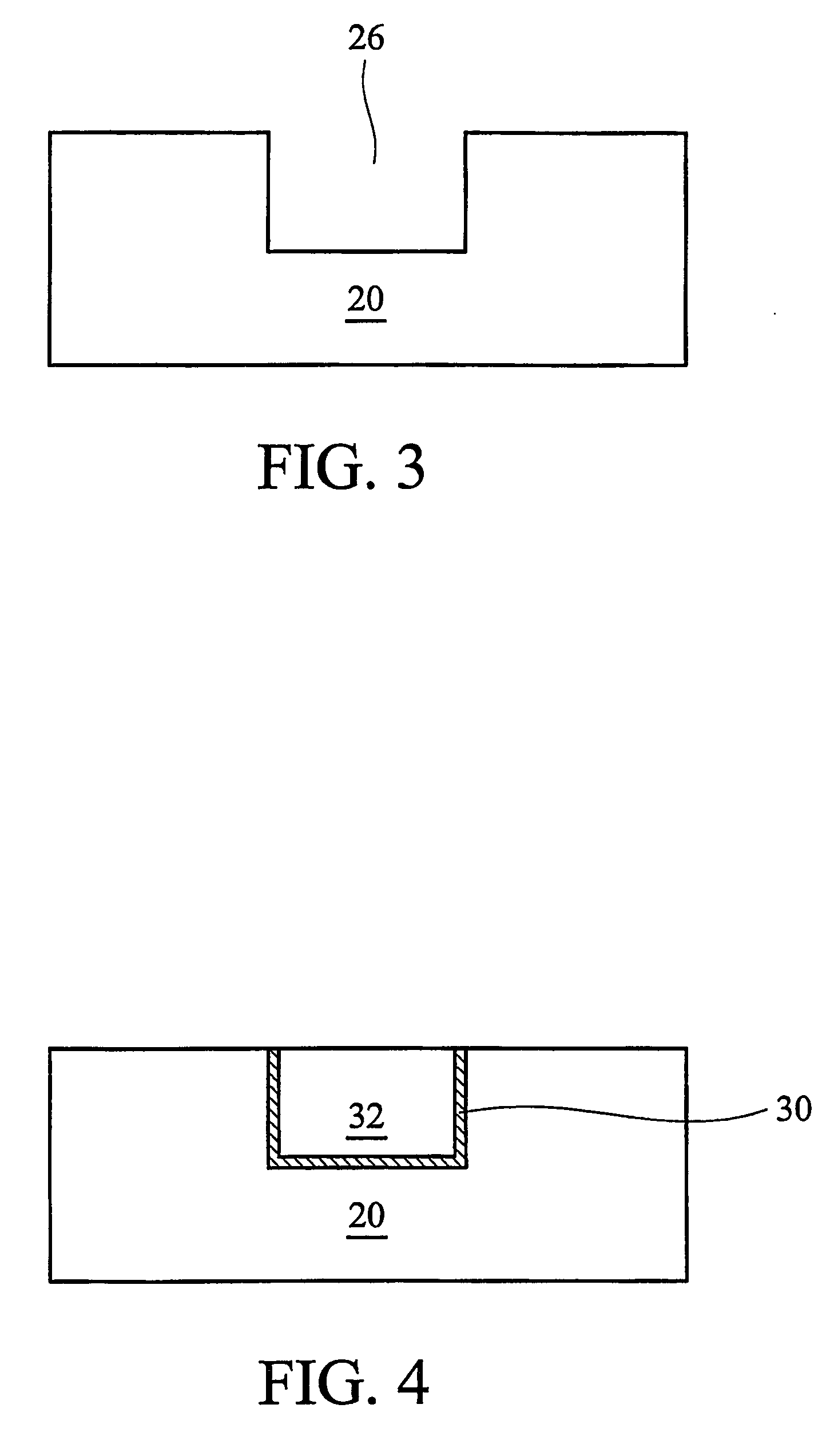

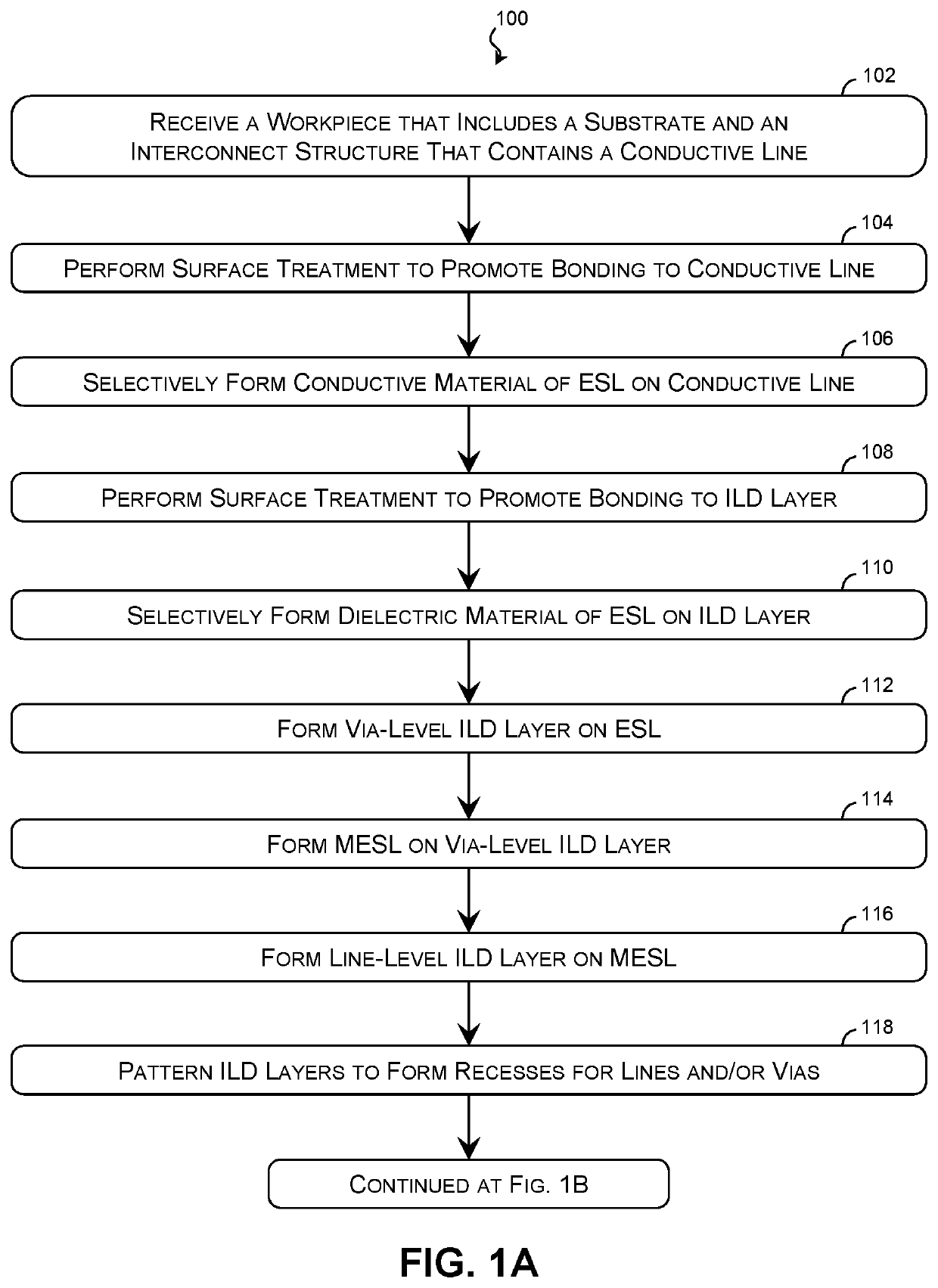

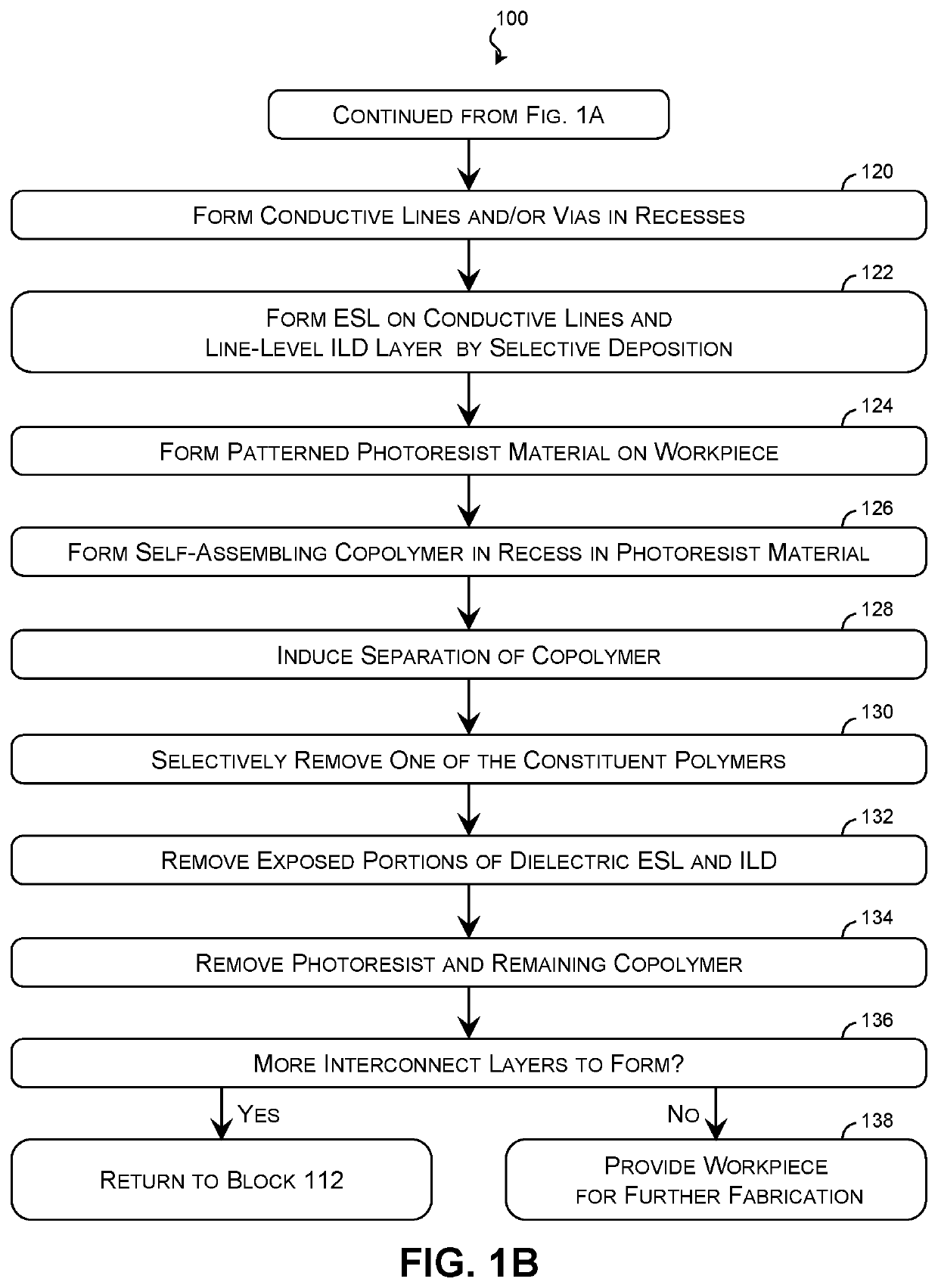

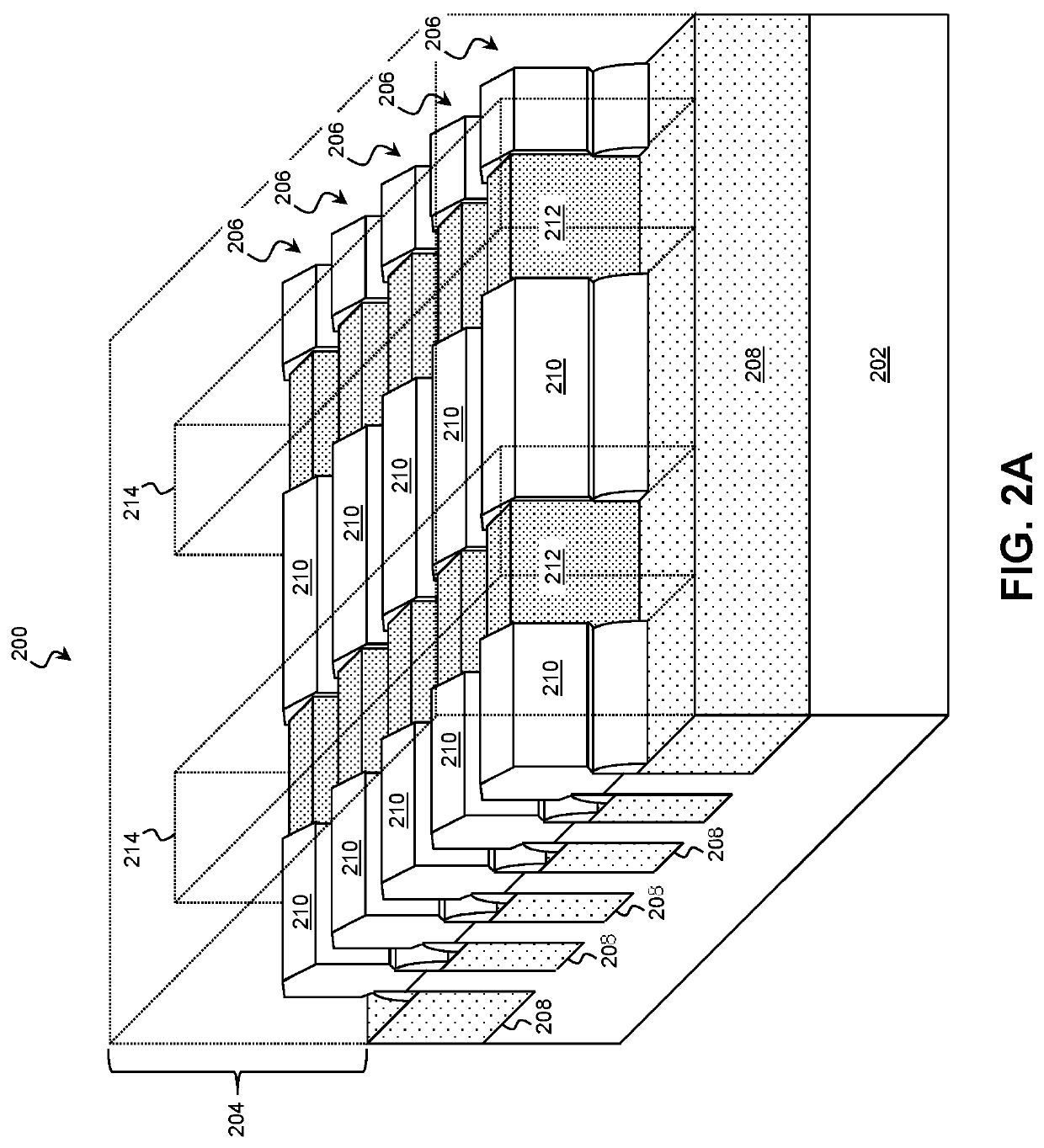

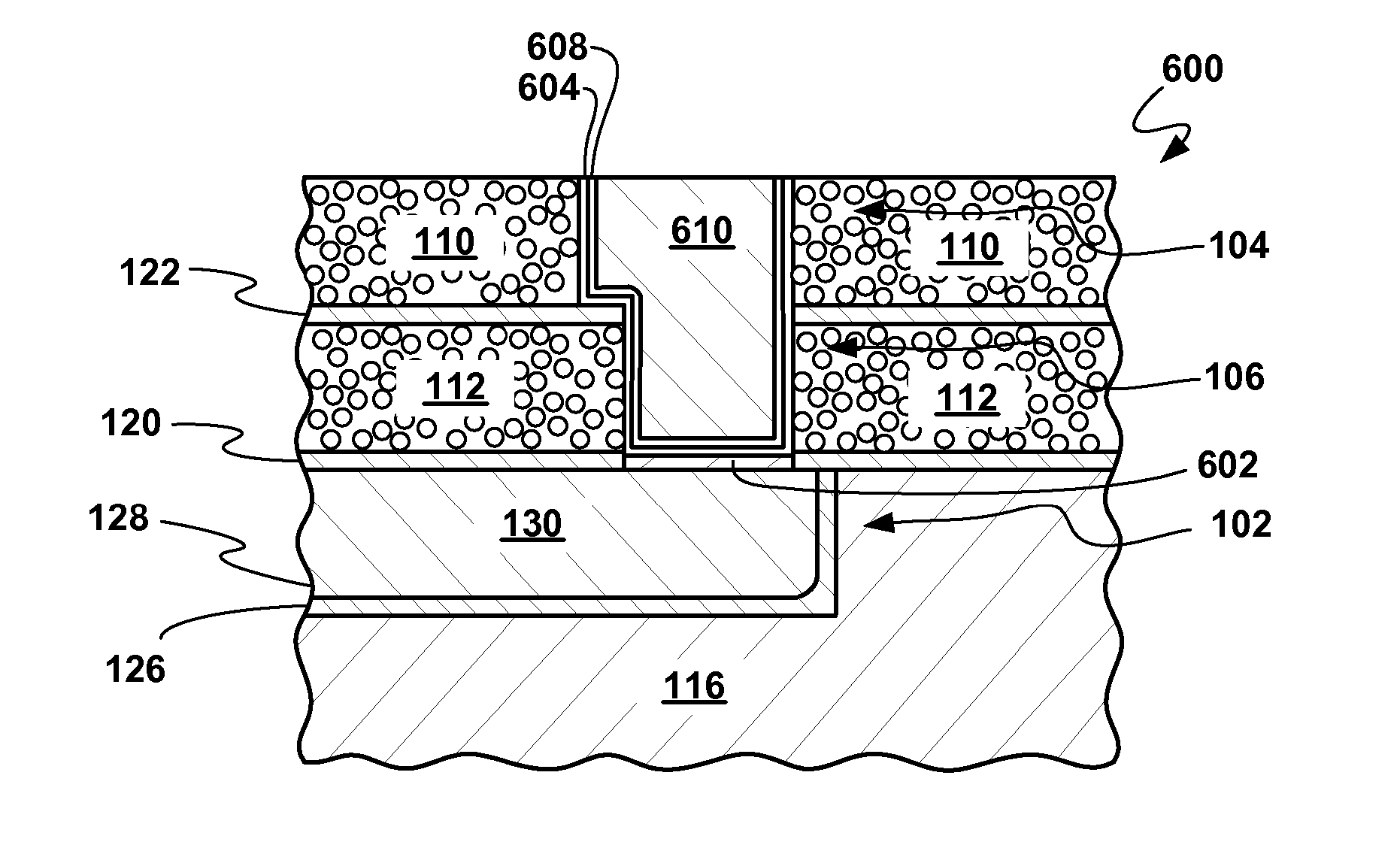

Integrated Circuit Interconnect Structures with Air Gaps

ActiveUS20200006228A1Semiconductor/solid-state device detailsSolid-state devicesDielectricIntegrated circuit interconnect

Examples of an integrated circuit with an interconnect structure and a method for forming the integrated circuit are provided herein. In some examples, the method includes receiving a workpiece having an interconnect structure that includes a first conductive feature, a second conductive feature disposed beside the first conductive feature, and an inter-level dielectric disposed between the first conductive feature and the second conductive feature. A conductive material of an etch stop layer is selectively deposited on the first conductive feature and on the second conductive feature without depositing the conductive material on the inter-level dielectric, and the inter-level dielectric is removed to form a gap between the first conductive feature and the second conductive feature.

Owner:TAIWAN SEMICON MFG CO LTD

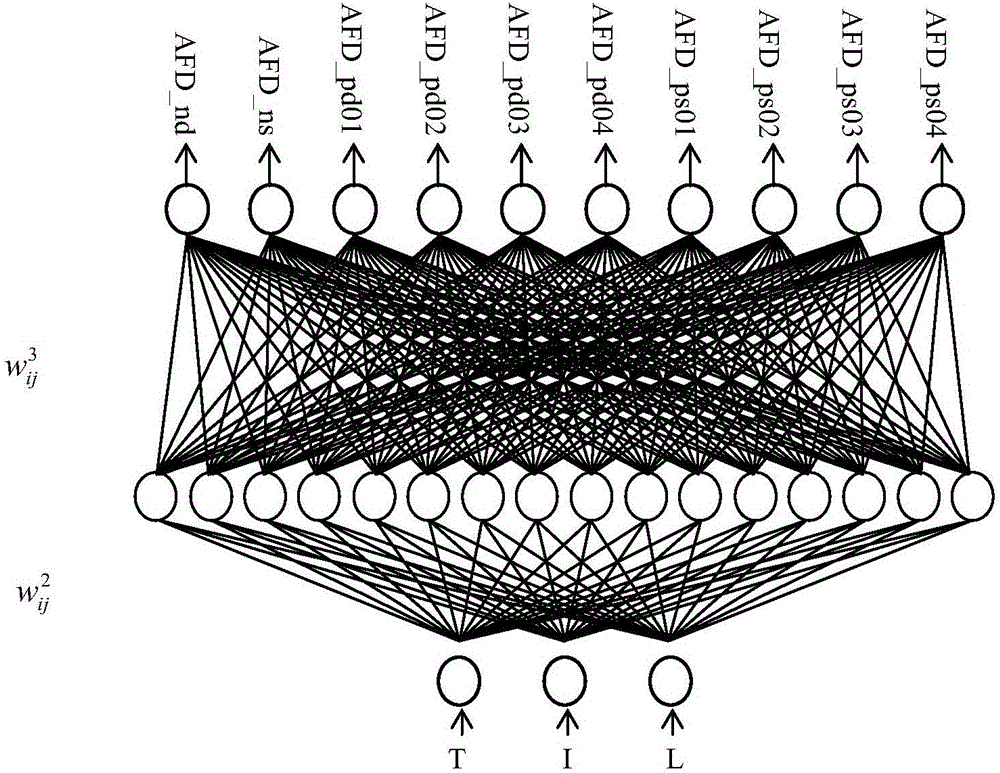

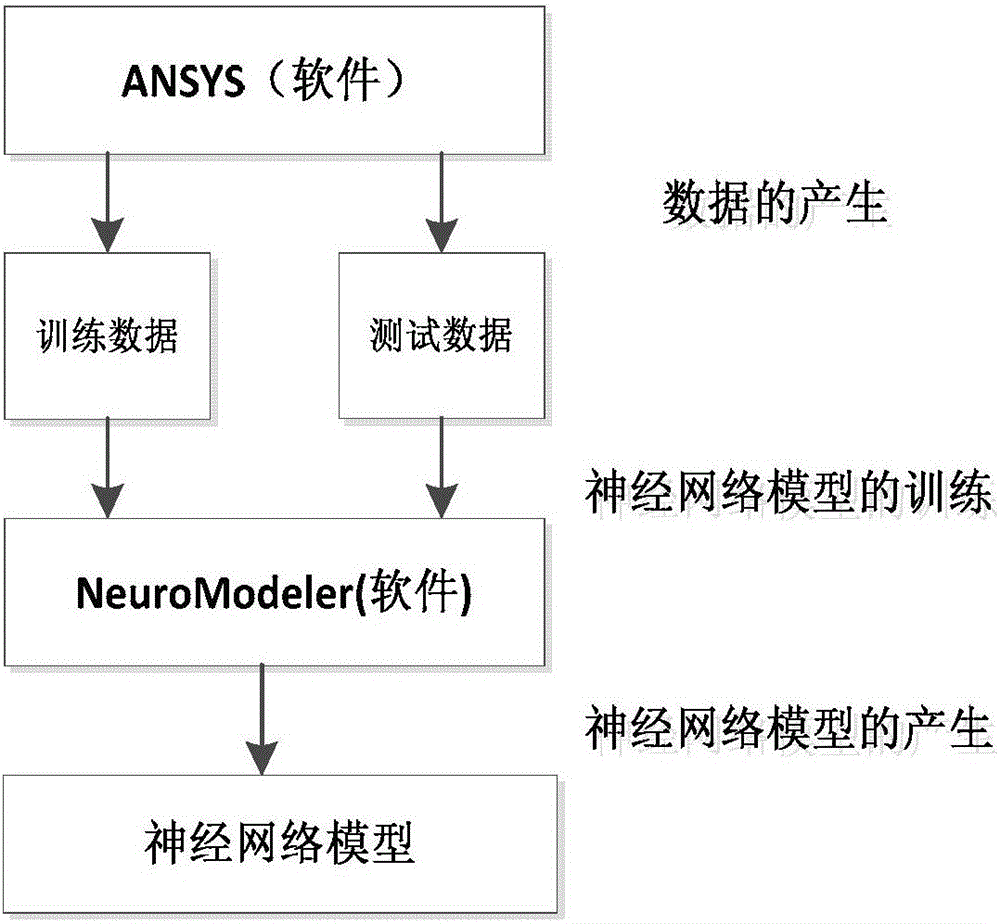

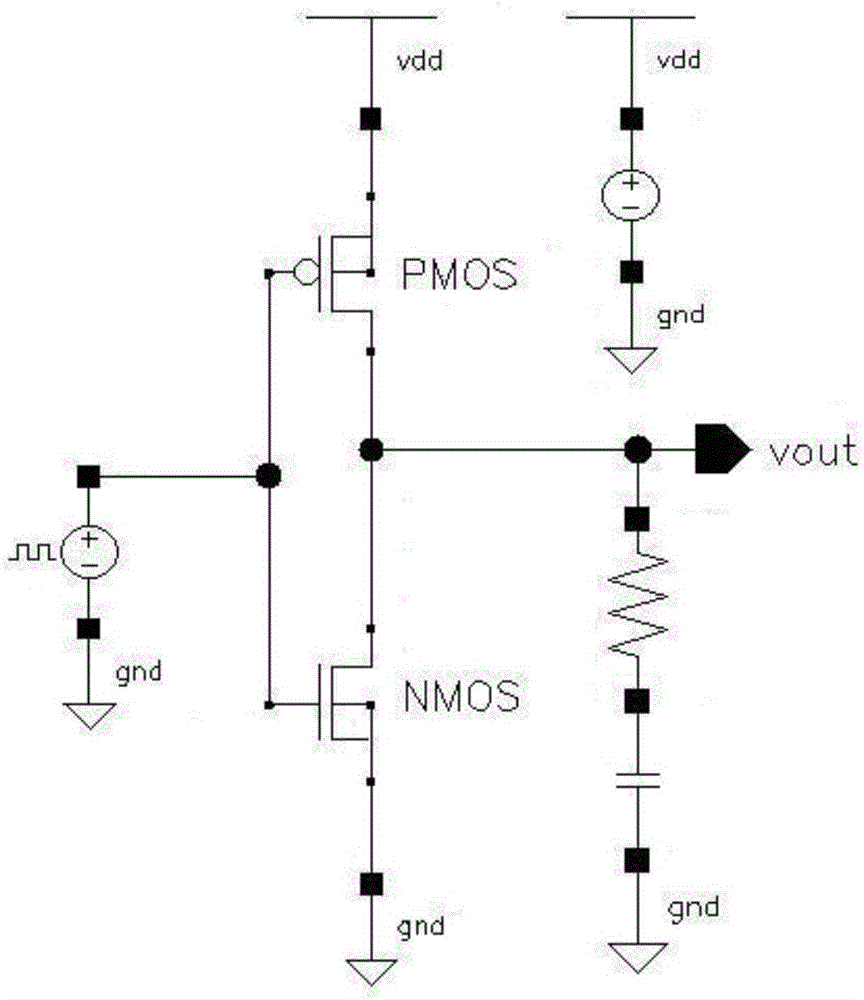

Integrated circuit interconnection reliability analysis method for modeling based on neural network parameters

InactiveCN106547962AOvercome the disadvantage of long simulation timeImproving the Efficiency of Interconnect Reliability SimulationDesign optimisation/simulationSpecial data processing applicationsCircuit reliabilityIntegrated circuit interconnect

The invention discloses an integrated circuit interconnection reliability analysis method for modeling based on neural network parameters. The method comprises the steps of acquiring training data by ANSYS simulation; building a neural network model structure based on EM reliability; and training a reliability neural network model and acquiring a model result. The advantages that the neural network has a strong non-linear mapping function and a rapid learning ability are utilized to model an EM reliability input and output relation via the neural network and train the model, results with respect to reliability under various work conditions are acquired after the model is built, reliability data under different conditions can be predicted in very short time, the defect that simulation time is long due to the fact that the reliability results under all input conditions need to be simulated when traditional ANSYS finite element software analyzes circuit reliability in different conditions, and the method provided by the invention is significant in research on interconnection reliability of the integrated circuit.

Owner:TIANJIN UNIV

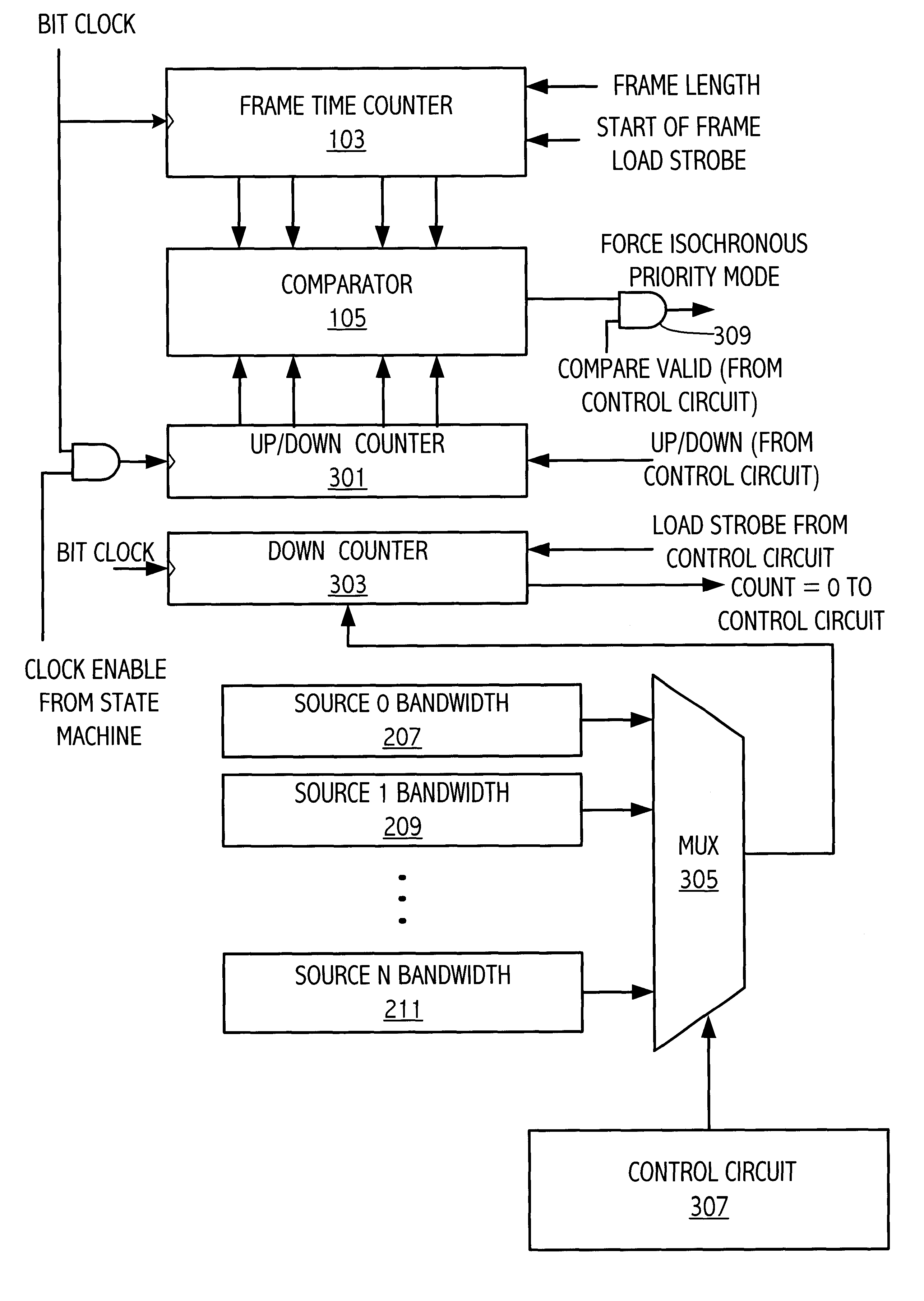

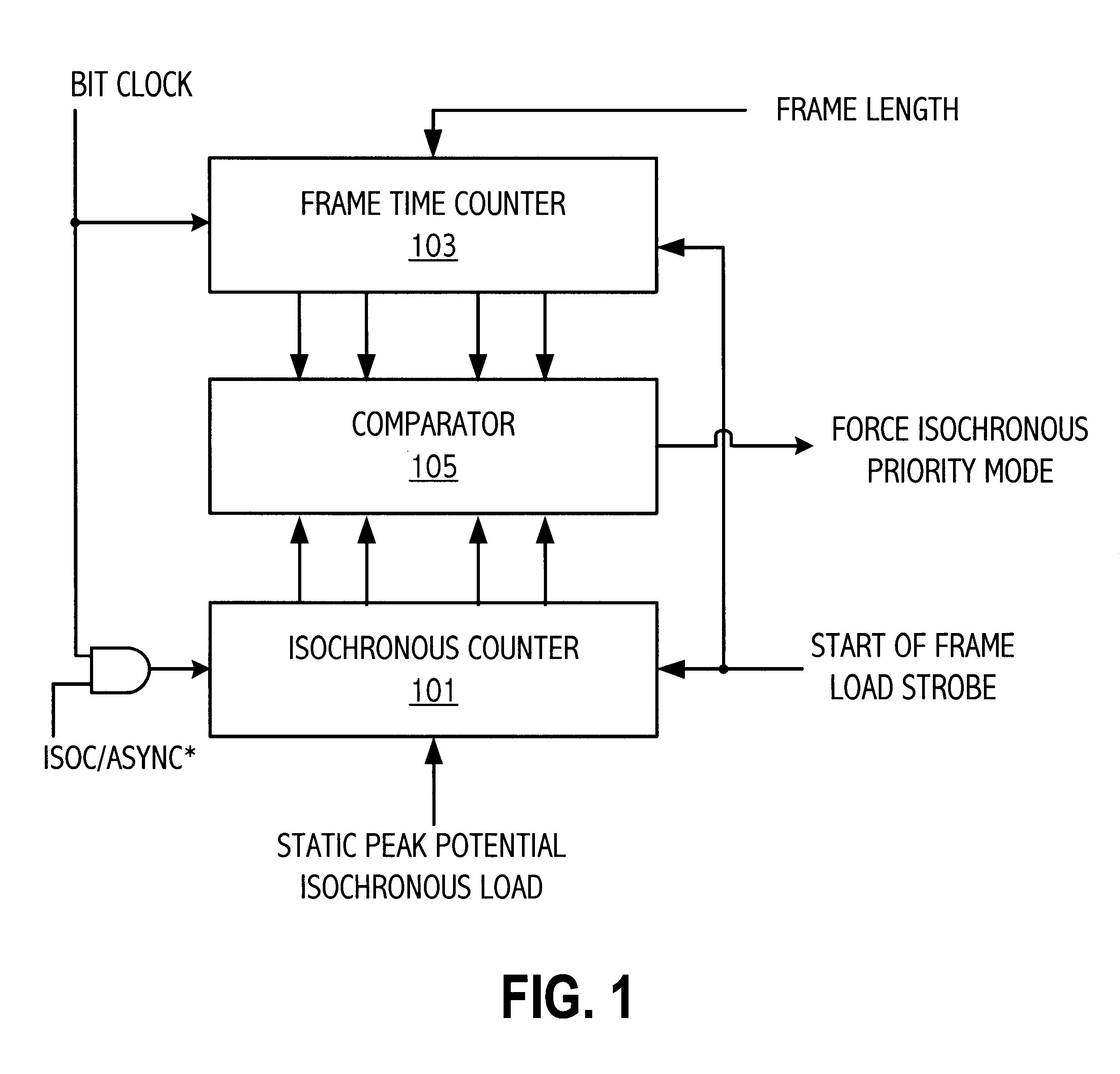

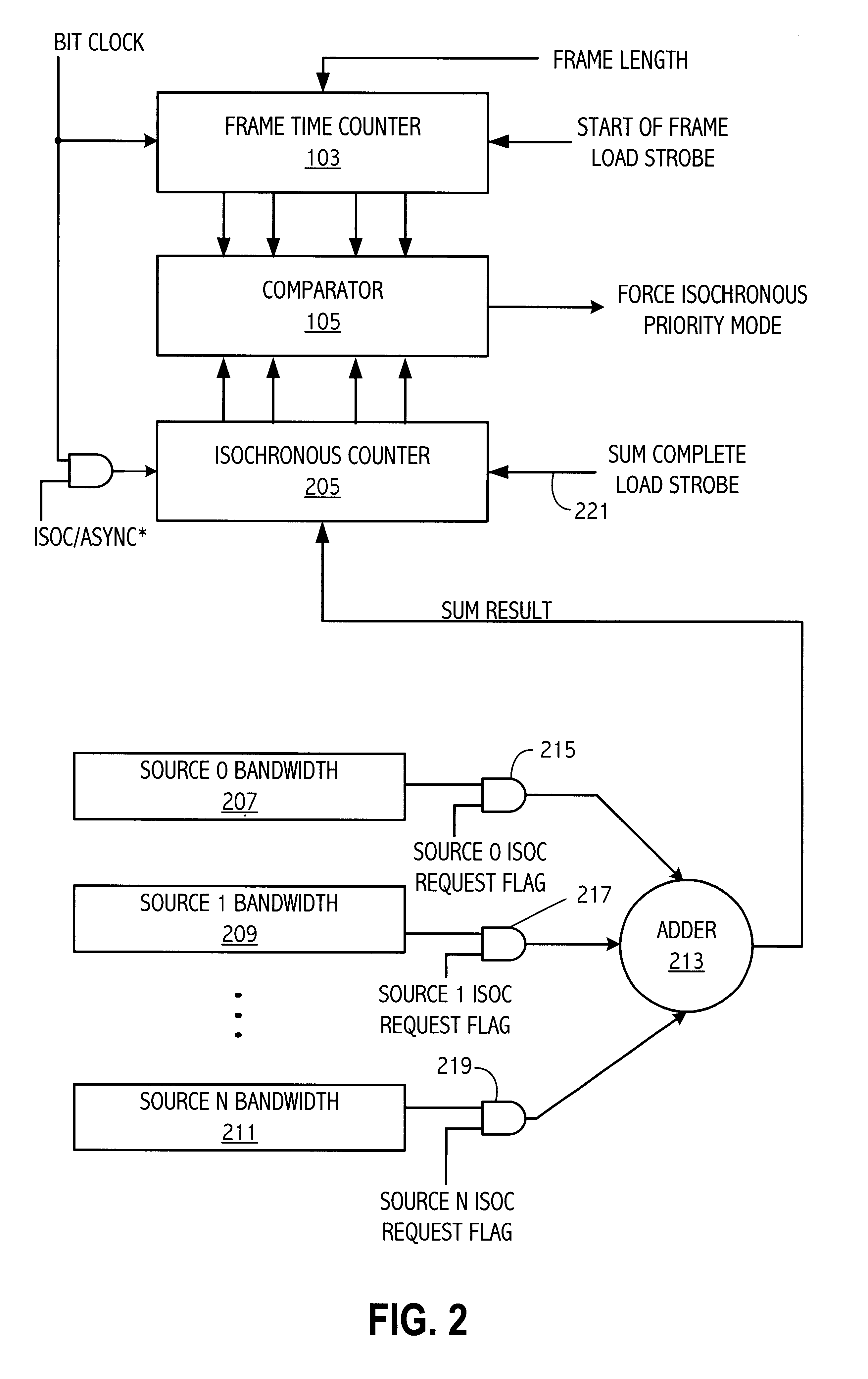

Dynamic scheduling mechanism for an asynchronous/isochronous integrated circuit interconnect bus

InactiveUS6336179B1General purpose stored program computerMultiple digital computer combinationsIntegrated circuit interconnectReal-time computing

A first counter sequentially counts a plurality of numbers from respective sources requesting transfer of data. Each of the numbers represents an amount of isochronous data to transfer over the bus from the respective ones of the sources during a frame on a bus. A count value in a second counter is selectably incremented when the first counter is counting, to provide a remaining count value indicative a remaining amount of data to transfer during the frame. The remaining count value in the second counter is decremented for each isochronous transfer on the bus after the remaining amount of data to transfer has been determined from all sources requesting transfer of isochronous data during the frame. A third counter tracks the time remaining in the frame and compares the remaining count value to the time remaining in the frame to determine a priority mode on the bus. The bus switches to isochronous priority mode on the bus according to a comparison of the remaining count value and the time remaining in the time period.

Owner:ADVANCED MICRO DEVICES INC

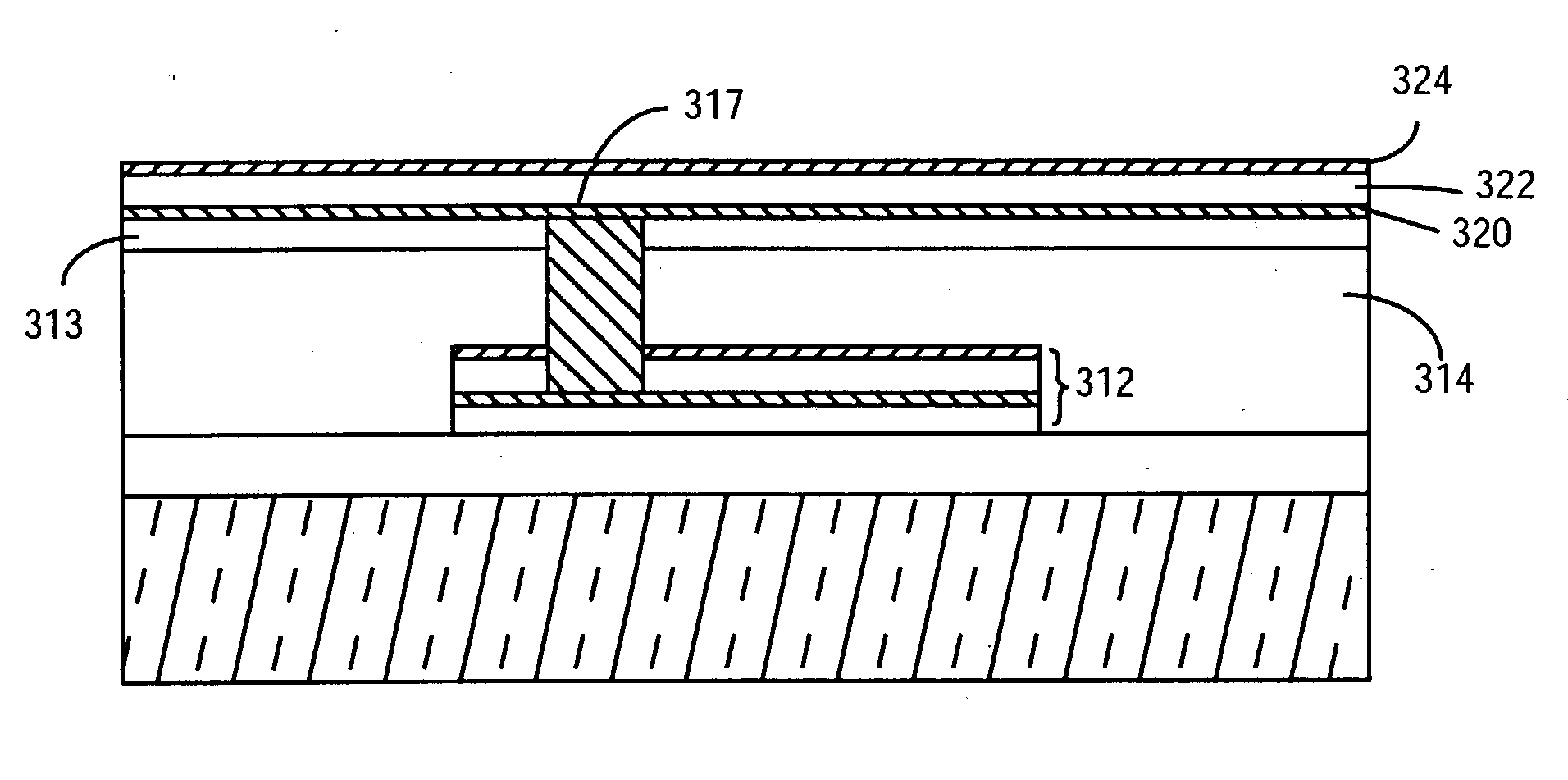

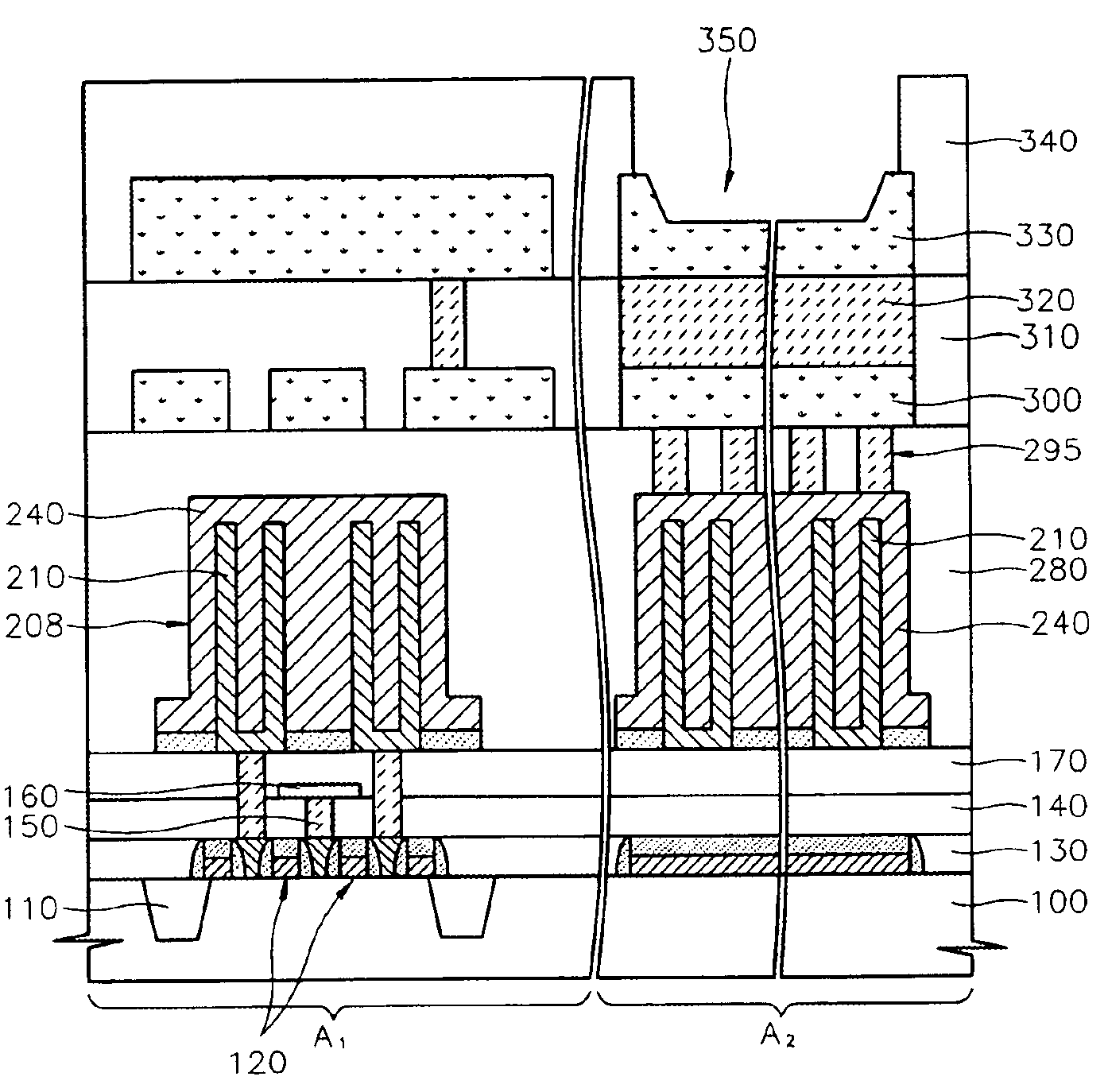

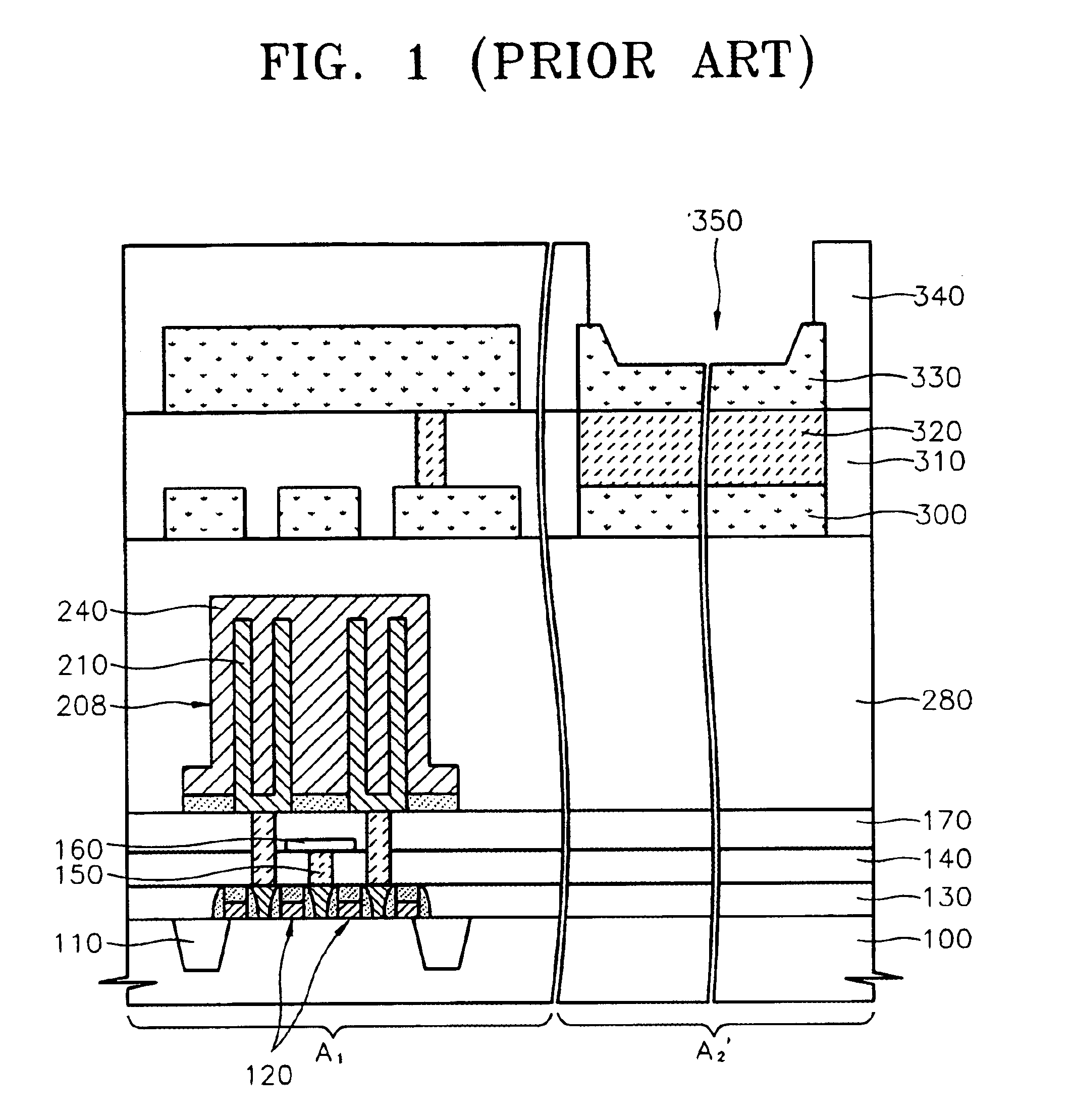

Novel interconnection structures and methods of fabrication

InactiveUS20030148603A1Semiconductor/solid-state device detailsSolid-state devicesInterconnectionSilicon

A novel, high performance, high reliability interconnection structure for an integrated circuit. The interconnection structure of the present invention is formed on a first insulating layer which in turn is formed on a silicon substrate or well. A first multilayer interconnection comprising a first aluminum layer, a first refractory metal layer, and a second aluminum layer is formed on the first insulating layer. A second insulating layer is formed over the first multilayer interconnection. A conductive via is formed through the second insulating layer and recessed into the first multilayer interconnection wherein a portion of the via extends above the second insulating layer. A second interconnection is formed on the second insulating layer and on and around the portion of the via extending above the second insulating layer.

Owner:INTEL CORP

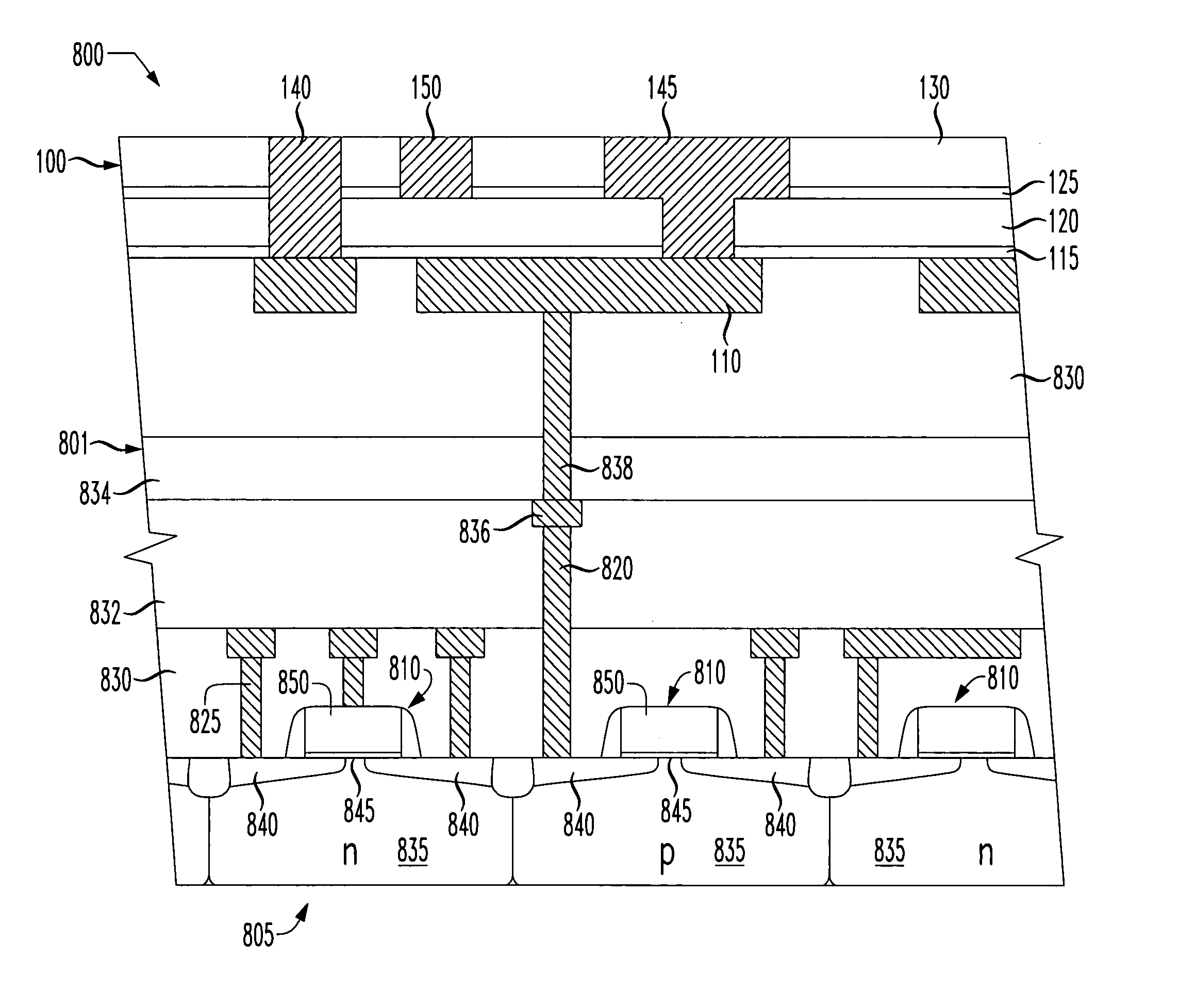

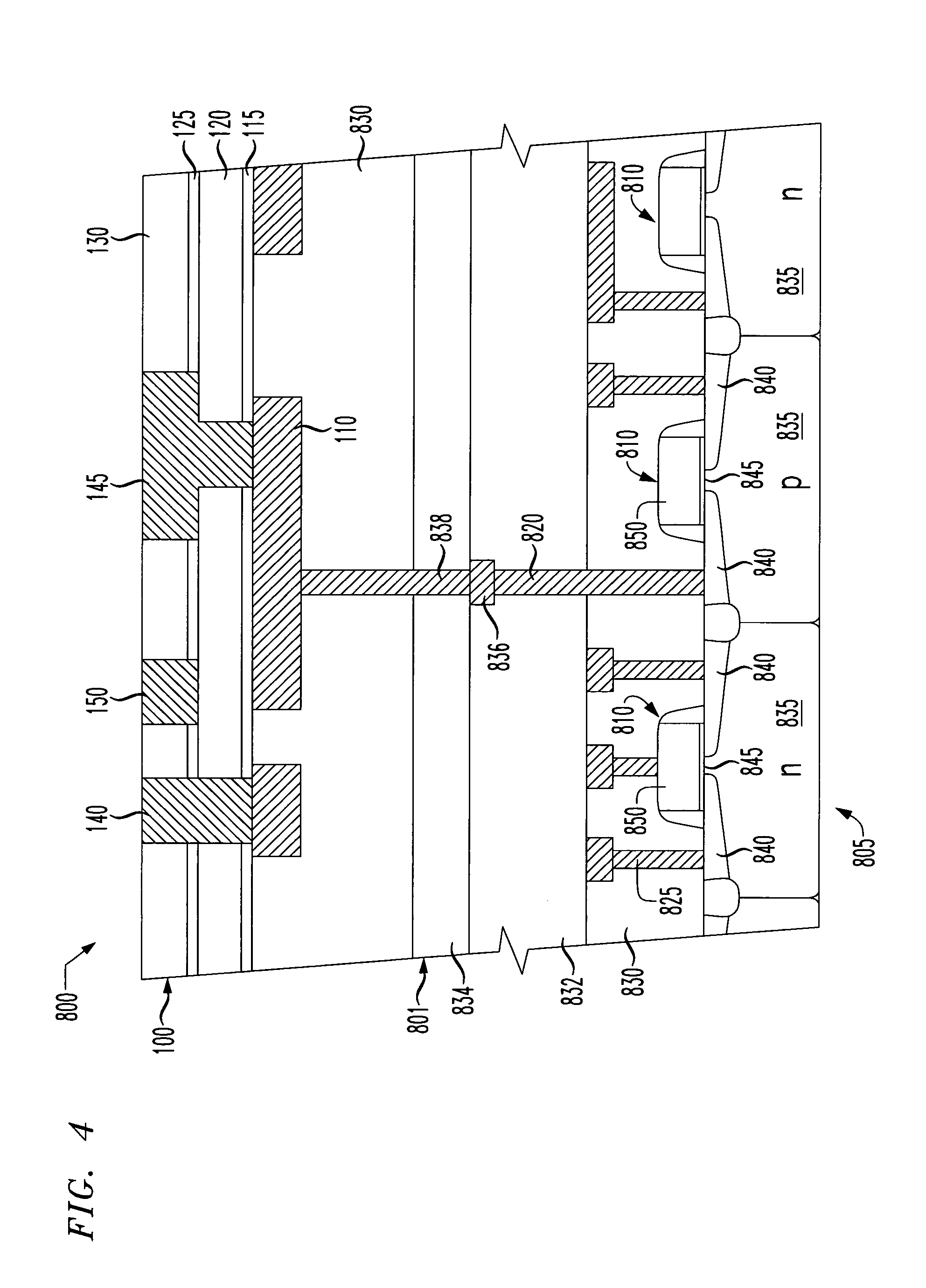

Bonding pad structure of a semiconductor device

InactiveUS6984895B2Improve the immunityMinimizing or eliminating additional or special process stepsTransistorSemiconductor/solid-state device detailsIntegrated circuit interconnectTension stress

A bonding pad structure in an integrated circuit (IC) and a method for manufacturing thereof comprises a plurality of dummy patterns deposited in sub-layers of the IC, each dummy pattern being connected via a metal link to a plurality of complementary top surface bonding pads, wherein the dummy patterns and the metal link are constructed during the same process steps used to construct the circuit elements included in the IC, without additional or special process steps. Such an imbedded and anchored bonding pad provides contact reliability for both conductive and non-conductive pads used for the interconnection of integrated circuits in a manner that resists layer separation or de-lamination under pulling stresses that are present on the bonding pads.

Owner:SAMSUNG ELECTRONICS CO LTD

Dual damascene process with no passing metal features

InactiveUS6989602B1Avoid problemsReduction in design ruleSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit interconnectCopper

The present invention provides a method of forming integrated circuit interconnect structures wherein a passing metal feature does not include a landing pad. In an exemplary embodiment, the method includes forming a via opening through first and second dielectric layers, such as silicon dioxide layer, located over a conductive layer, such as copper, and to a first etch stop layer, such as silicon nitride, located over the conductive layer. A trench opening is then formed through the second dielectric layer and to a second etch stop layer. Once the via and trench openings are formed, an etch is conducted that etches through the first etch stop layer such that the opening contacts the underlying conductive layer.

Owner:BELL SEMICON LLC +1

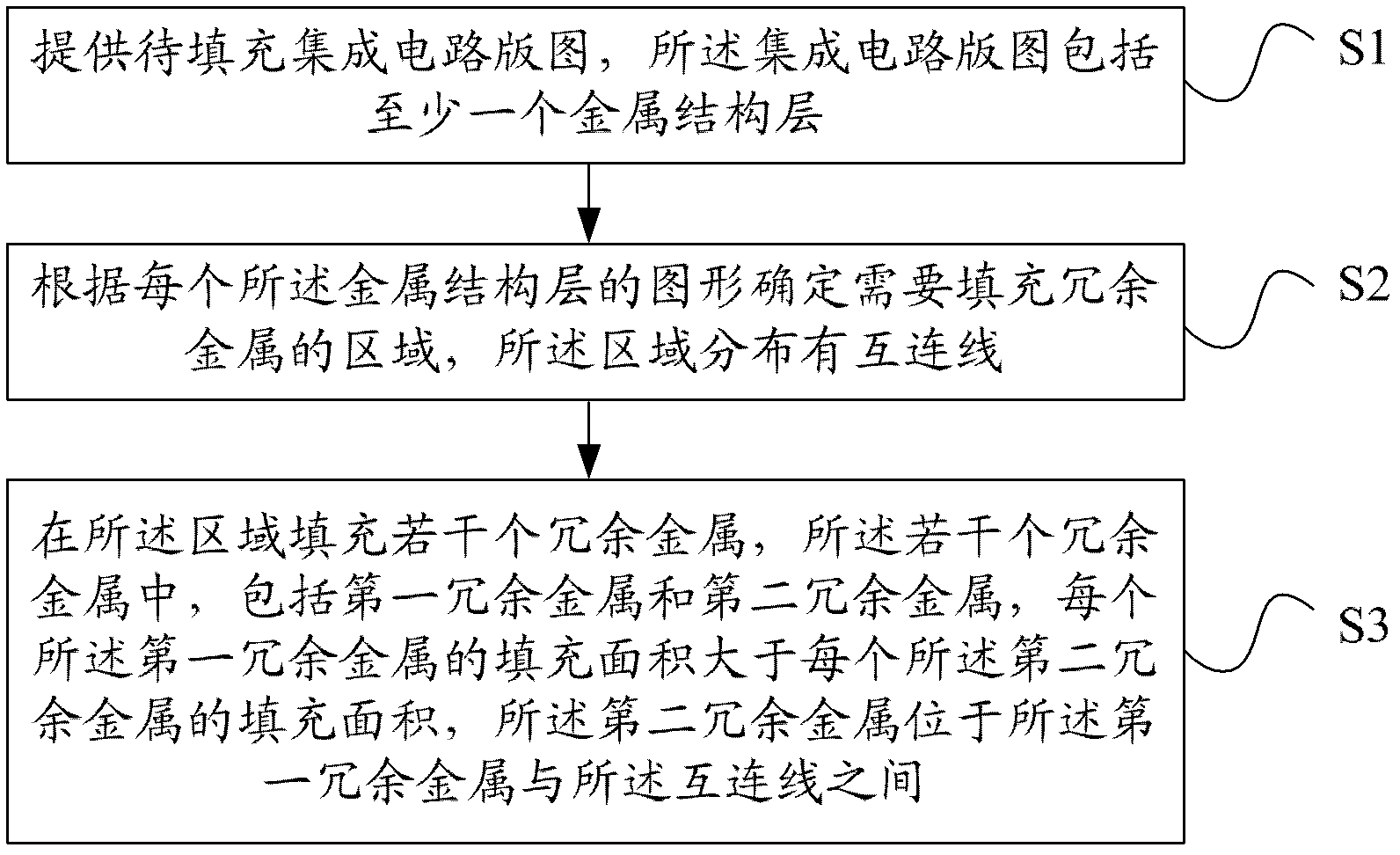

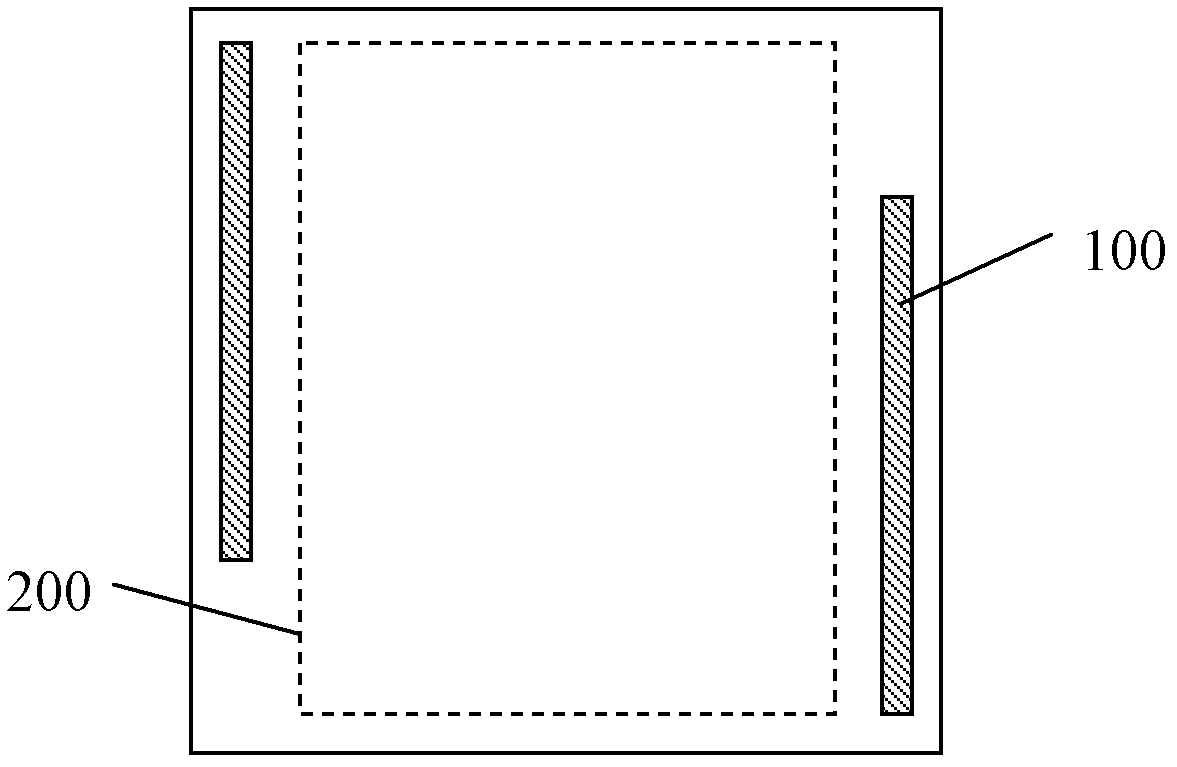

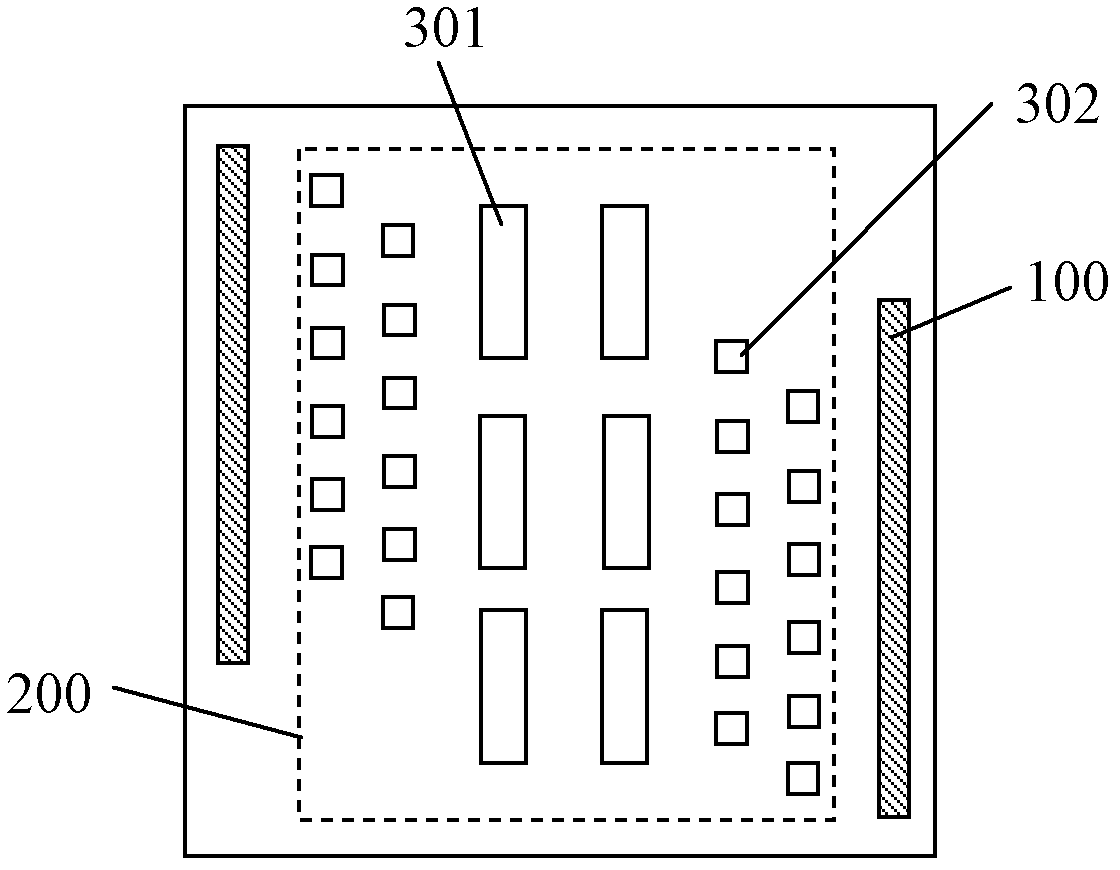

Dummy metal filling method and integrated circuit layout structure

ActiveCN102543853AAchieve Thickness ConsistencyIncrease capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceIntegrated circuit interconnect

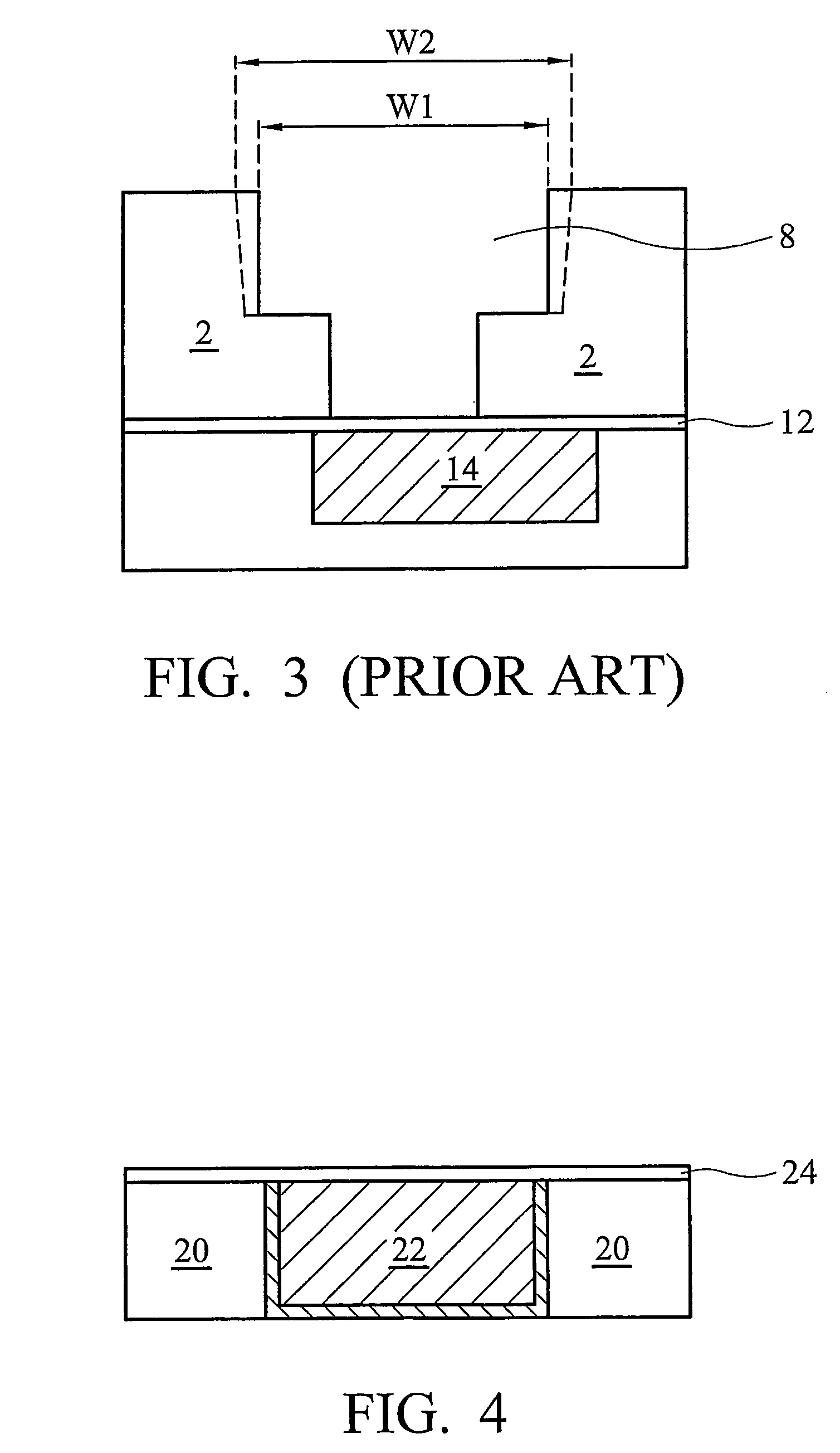

The invention provides a dummy metal filling method. According to the invention, a plurality of dummy metals are filled in an area required to be filled by the dummy metals including first dummy metals and second dummy metals; the filling area of each first dummy metal is larger than that of each second dummy metal; and the second dummy metals are positioned between interconnection lines of the first dummy metals and the area where the dummy metals are positioned. Accordingly, the invention further provides an integrated circuit layout structure. Through the dummy metal filling method provided by the invention, the thickness consistency of an integrated circuit layout is realized, and the capacitance increment between the interconnection lines of an integrated circuit is reduced at the same time, the function of the chip is prevented from being damaged due to the introduction of the dummy metals, the dummy metals in different areas can be filled in the area required to be filled by the dummy metals, the filling number of the dummy metals is reduced, and other calculation data quality is reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Mechanically formed standoffs in a circuit interconnect

InactiveUS6417997B1Low costReliable connectorPrinted circuit assemblingElectrical connection between head and armIntegrated circuit interconnectBonding process

Mechanically formed standoffs in a disk drive integrated circuit interconnect reduces the cost of manufacturing and improves the reliability of the electrical interconnections thereof. Connection pads defined along the interconnect are bonded with bonding pads of a signal producing source and a signal processing source. The standoffs provide mechanical stops during the bonding process, enabling sufficient bonding material to form between bonding areas. The standoffs are mechanically formed with a punch and die assembly either directly through a bonding pad predefined along traces on the interconnect or adjacent the bonding pad. The standoffs formed through the bonding pads are covered with solder or other electrically conductive bonding material.

Owner:WILLIAMS STEPHEN P

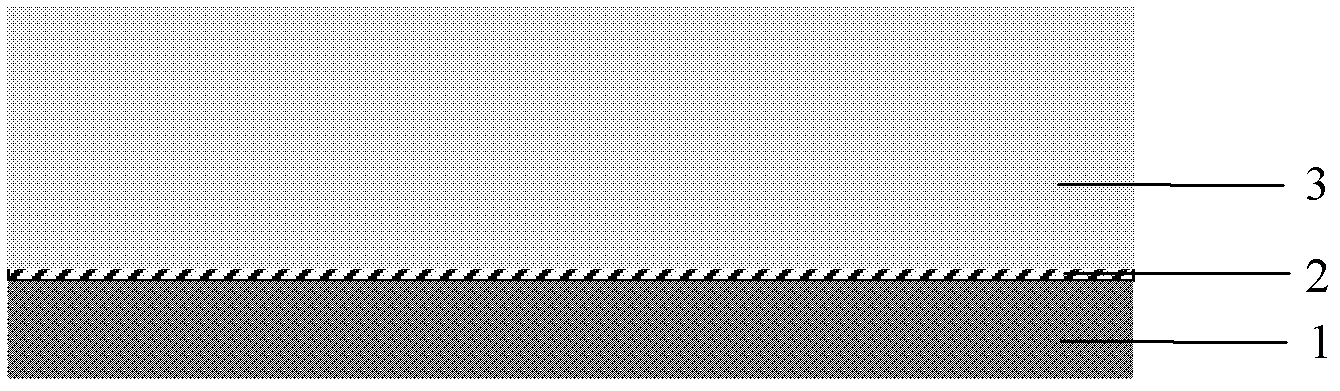

Metal interconnection structure of integrated circuit and preparation method for metal interconnection structure

InactiveCN102593098AImprove conductivityImprove thermal stabilitySemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit interconnectPower flow

The invention discloses a metal interconnection structure of an integrated circuit and a preparation method for the metal interconnection structure. A graphene covering layer is coated on the upper surfaces of upper layer metal interconnection lines of the metal interconnection structure of the integrated circuit by utilizing the proper unique molecular structure and the electrology characteristic of graphene. As the electromigration-resistance current density of the graphene can reach 109A / cm<2>, once when small cavities appear in metal conductors due to electromigration, current can be possibly conducted through the graphene coated on the surfaces of the metal conductors, and thereby, the growth rate of the cavities in the metal interconnection lines is effectively lowered, the electromigration resistance of the metal interconnection lines is increased, and the service lives of the metal interconnection lines are prolonged. Meanwhile, the graphene coated on the surfaces of the metal interconnection lines is also capable of effectively stopping the growth of crystal whiskers, and thereby, the short circuit risk caused by the growth of the crystal whiskers is lowered. Moreover, the graphene covering layer is capable of effectively isolating the metal conductors from contacting with the air so as to retard or eliminate the oxidation of the surfaces of the metal interconnection lines, and thereby, the reliability of the interconnection lines of the integrated circuit is improved.

Owner:PEKING UNIV

Crenulated wiring structure and method for integrated circuit interconnects

InactiveUS20110227232A1Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorIntegrated circuit interconnect

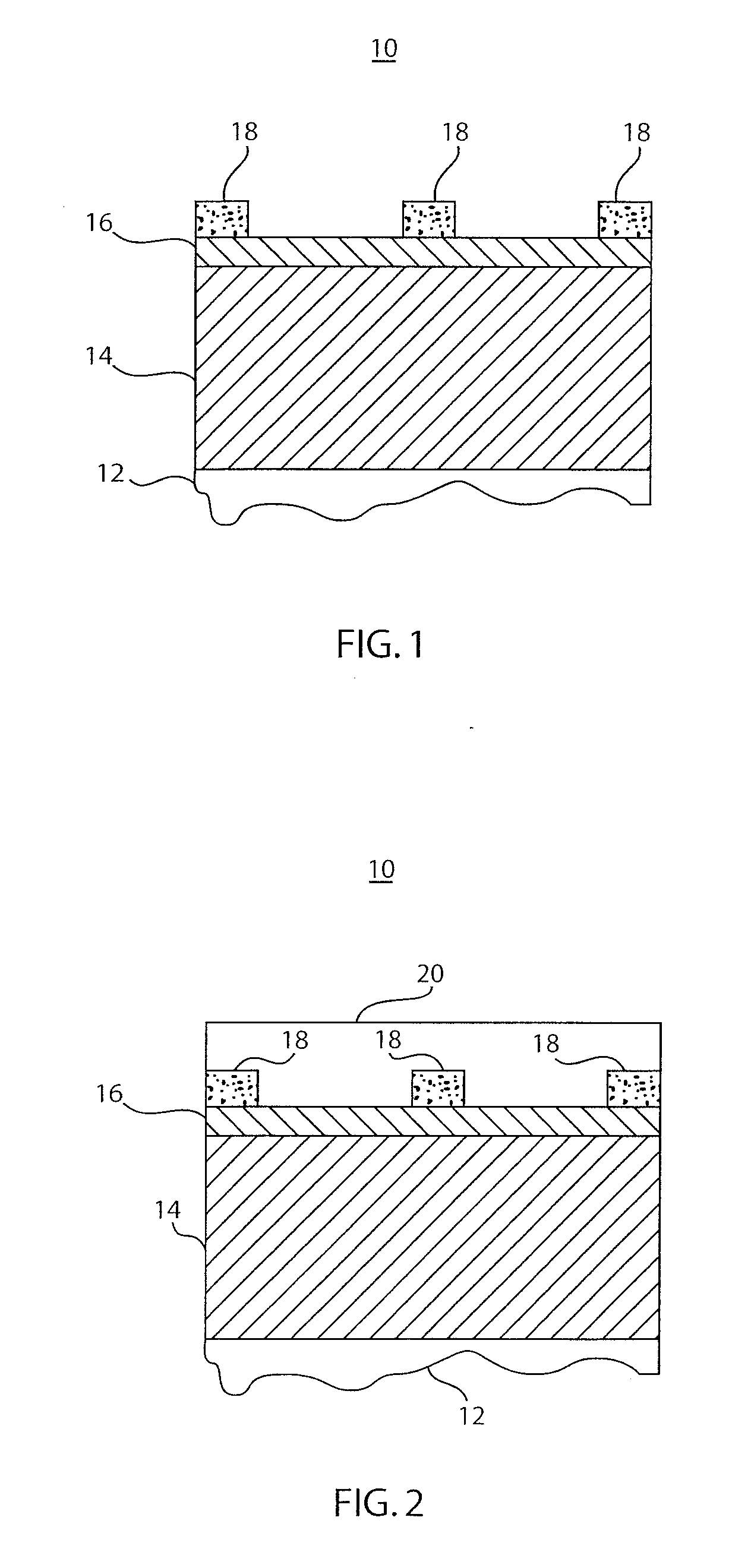

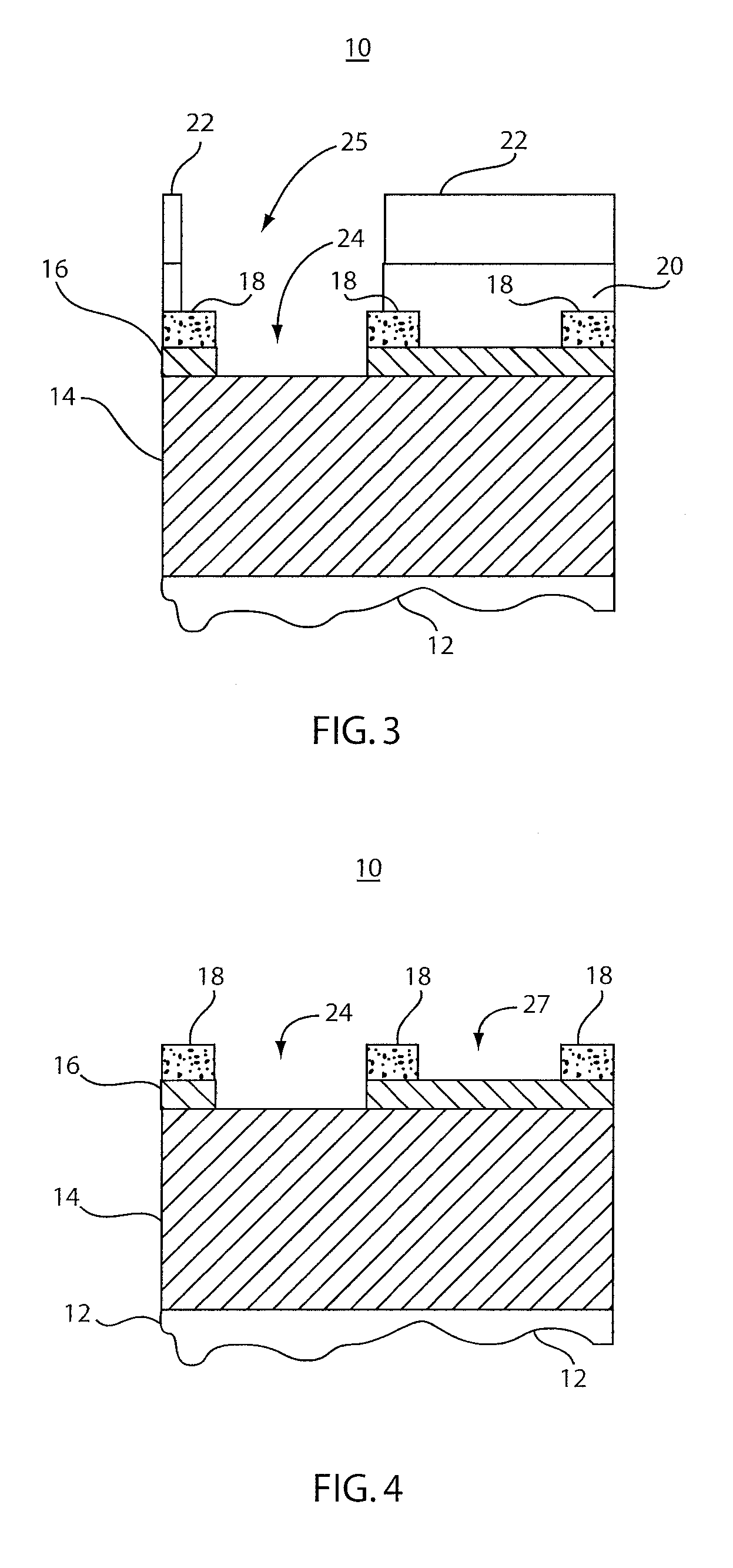

A method for forming crenulated conductors and a device having crenulated conductors includes forming a hardmask layer on a dielectric layer, and patterning the hardmask layer. Trenches are etched in the dielectric layer using the hardmask layer such that the trenches have shallower portions and deeper portions alternating along a length of the trench. A conductor is deposited in the trenches such that crenulated conductive lines are formed having different depths periodically disposed along the length of the conductive line.

Owner:IBM CORP

Nano-electrode-array for integrated circuit interconnects

InactiveUS20070284746A1NanotechSemiconductor/solid-state device detailsElectrical conductorIntegrated circuit interconnect

Owner:KLA TENCOR TECH CORP