Metal interconnection structure of integrated circuit and preparation method for metal interconnection structure

A metal interconnection structure, integrated circuit technology, applied in the direction of circuits, electrical components, electrical solid devices, etc., can solve the problems of reducing the growth rate of holes, increasing the resistance of interconnection lines, and increasing the resistivity, so as to achieve strong anti-electricity Effect of migration ability, low sheet resistance, thermal stability and chemical stability improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

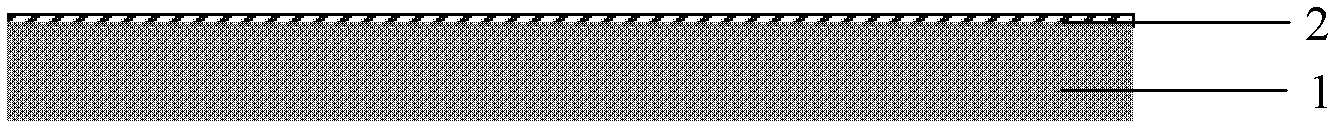

[0020] (1) Preparation of the lower layer copper interconnection 1: the lower layer copper interconnection 1 is prepared by a damascene process, and its surface is chemically mechanically polished and covered with a NiWP layer, such as figure 1 shown.

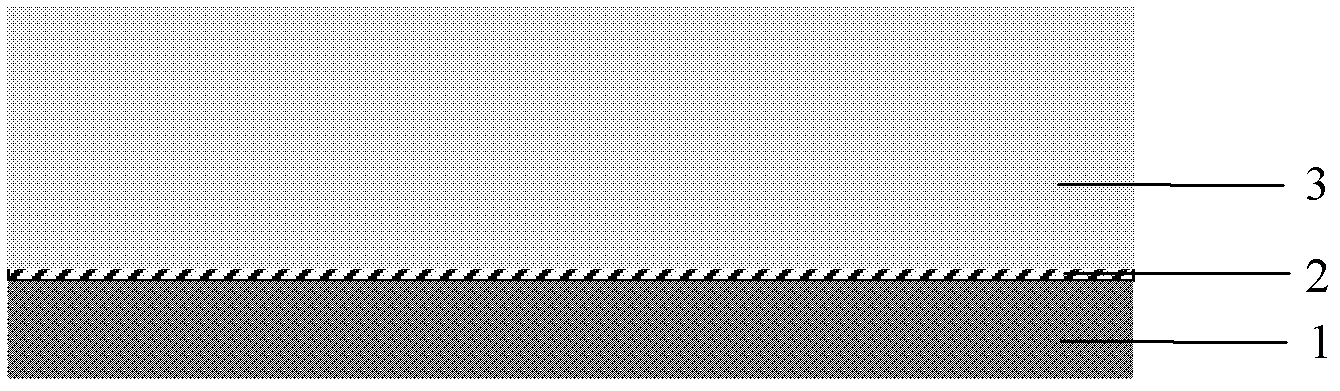

[0021] (2) Depositing a silicon dioxide dielectric layer 3 with a thickness of 1 μm on the lower copper interconnection structure by PECVD, such as figure 2 shown.

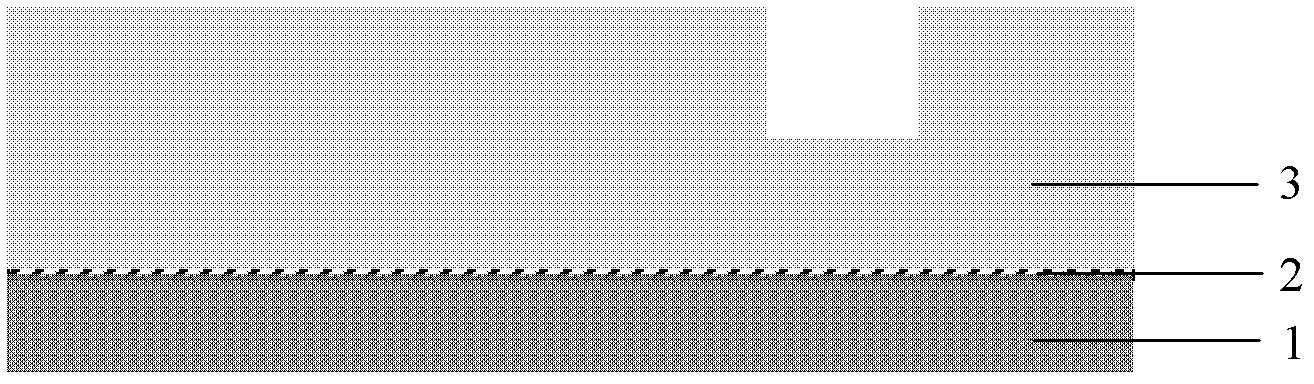

[0022] (3) Reactive ion etching (RIE) is used to etch the through hole connecting the lower copper interconnection 1 and the groove of the upper copper interconnection 5 in the silicon dioxide dielectric layer 3 (dual damascene process), Such as image 3 , 4 shown.

[0023] (4) Deposit a layer of 5nm thick TaN as a diffusion barrier layer 4 on the bottom and sidewalls of the vias and trenches by atomic layer deposition, and then use CuCl on it 2 as a reactant, H 2 A 5nm thick copper seed crystal layer was deposited by atomic layer deposition as a reducing a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More