Patents

Literature

189results about How to "Reduce parasitic parameters" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

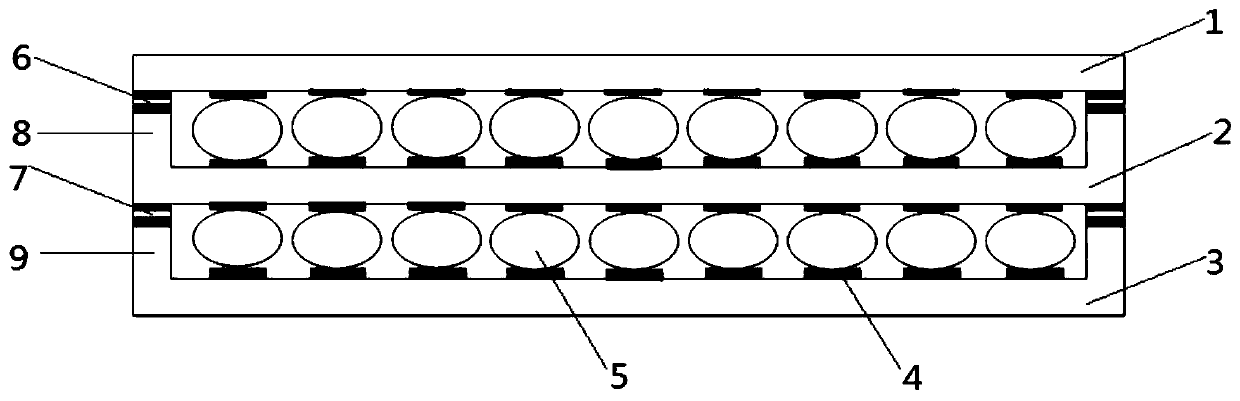

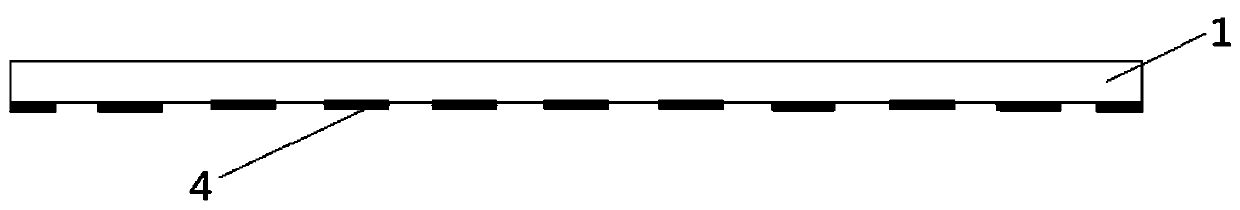

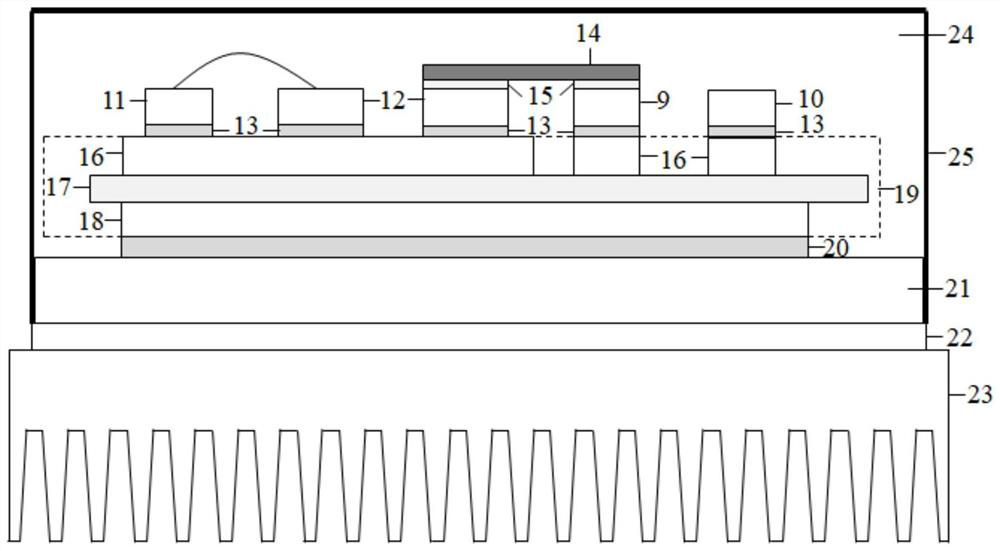

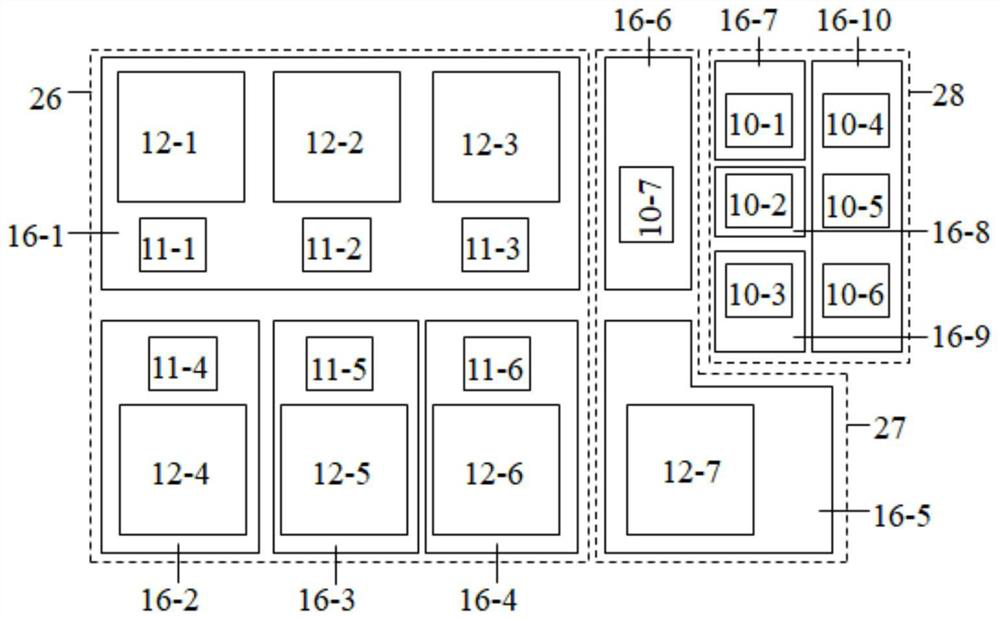

Patch antenna unit and antenna

ActiveCN105552550AIncrease the effective areaHigh bandwidthRadiating elements structural formsIndividually energised antenna arraysHigh bandwidthIntegrated circuit

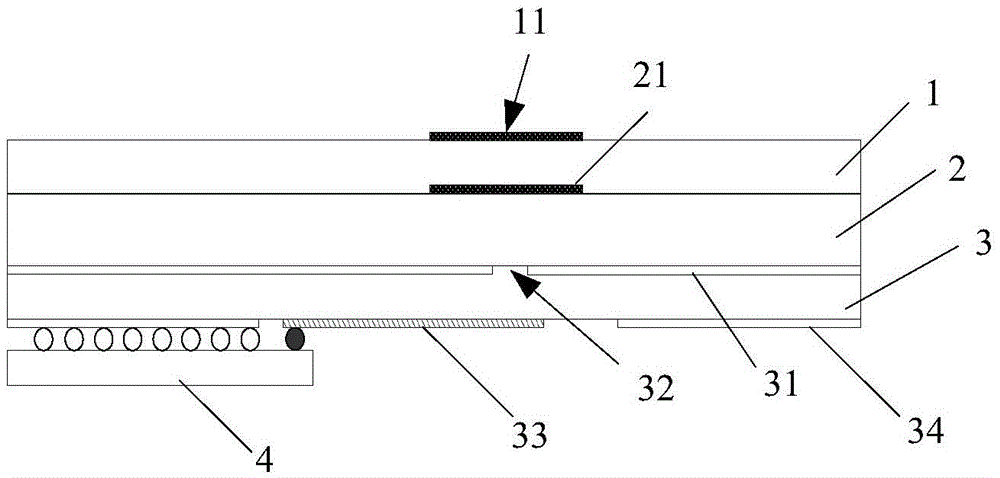

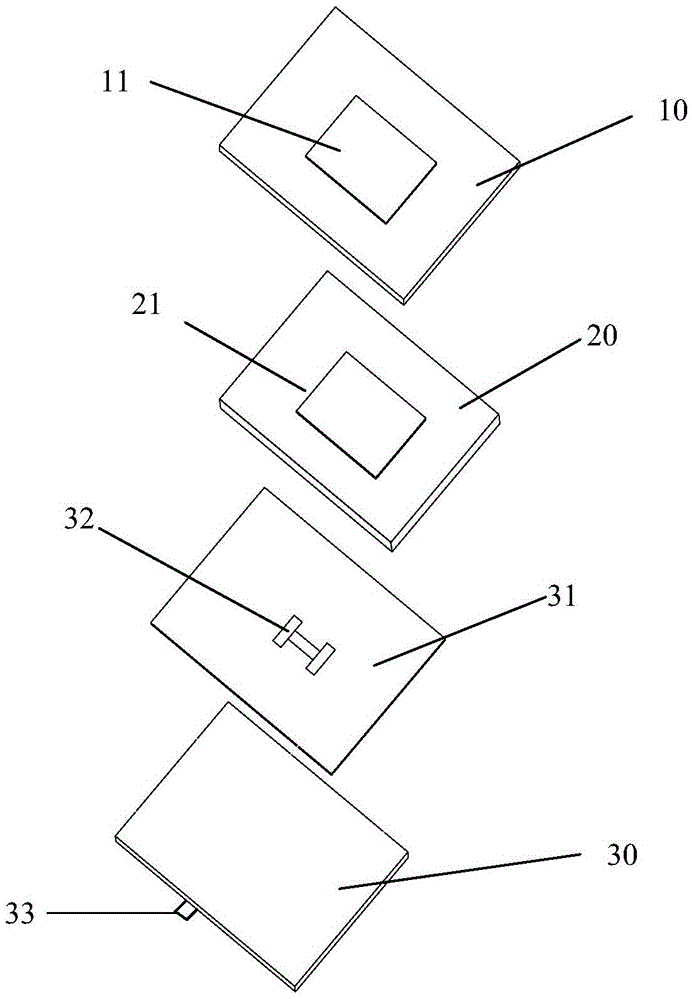

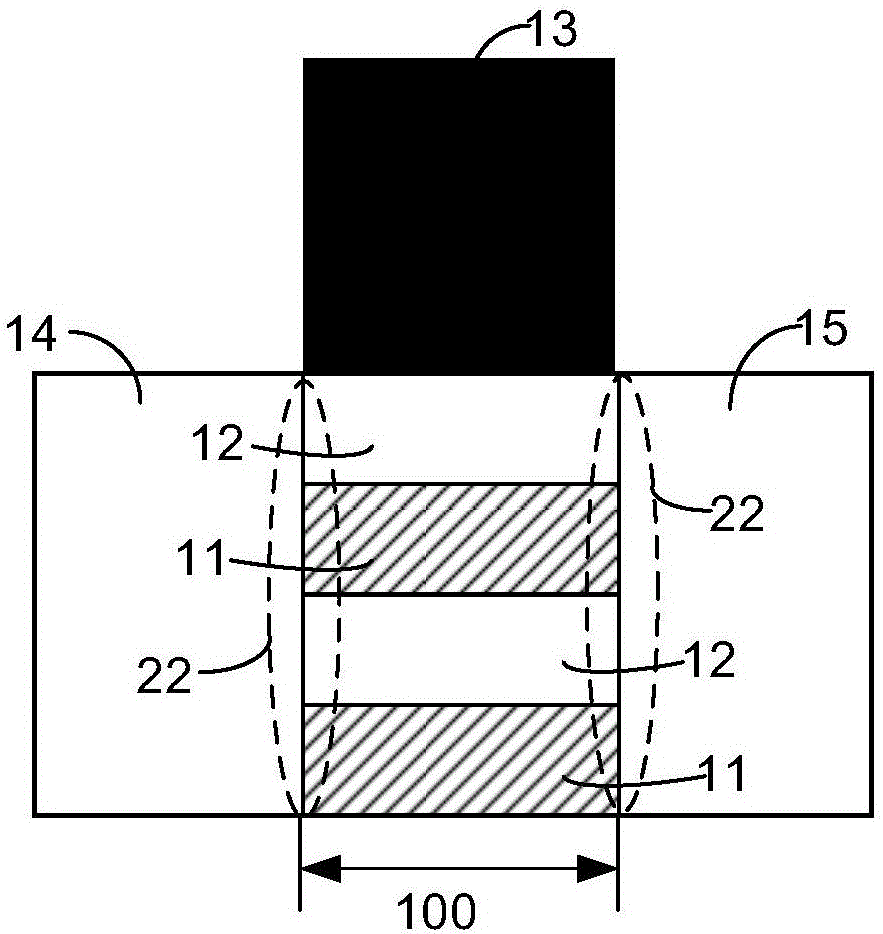

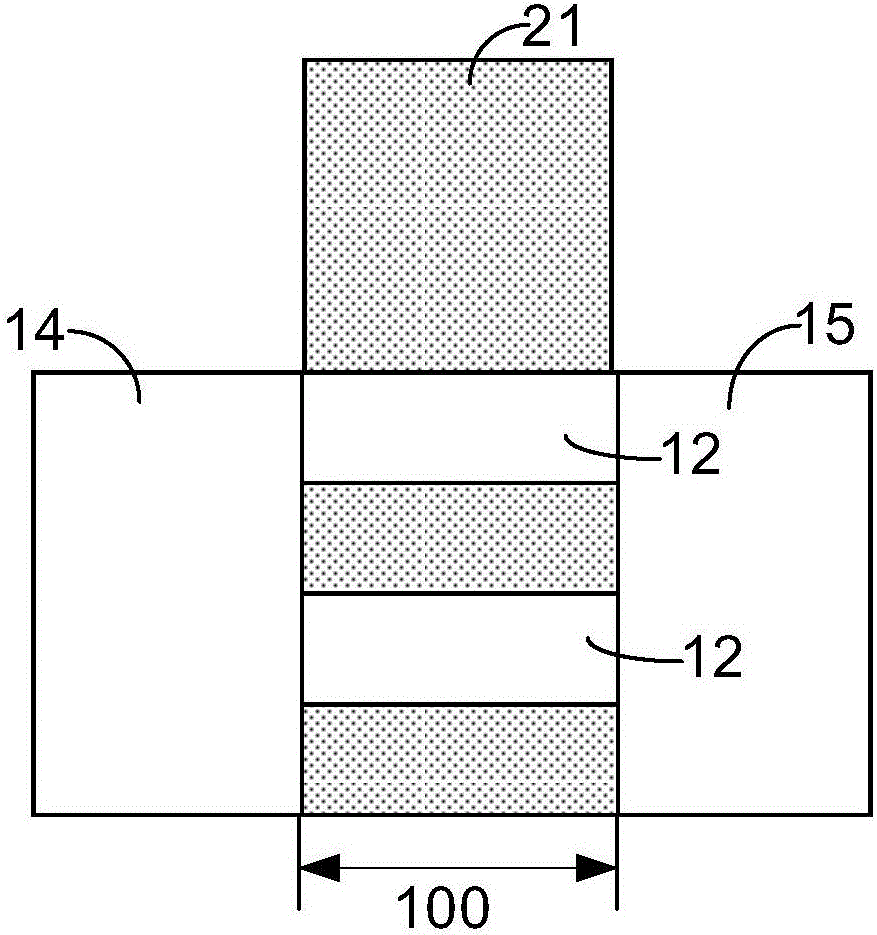

The invention relates to the technical field of communication, and discloses a patch antenna unit, an antenna and communication equipment. The patch antenna unit comprises stacked first support layer, substrate, second support layer and integrated circuit, wherein radiation patches are attached to the first support layer and the second support layer respectively; ground layers are arranged on the second support layer and are provided with coupling gaps; a feeder line corresponding to the coupling gaps is arranged on the second support layer; and the integrated circuit is connected with the first ground layers and the feeder line respectively. In a specific technical scheme, fabrication is carried out by the four layer-substrate, so that a 57-66GHz full-band high-frequency signal can be effectively fed into upper two layers of antennas for radiation by the coupling gaps in the third layer; the parasitic effect is reduced; meanwhile, the effective area of the antenna is increased by the stacked structure; and the performance effects of a high bandwidth and a high gain are brought for the antenna by achieved low parasitic parameters and high effective area.

Owner:HUAWEI TECH CO LTD

3D (three-dimensional) NAND memory and manufacturing method thereof

ActiveCN103680611AImprove controlReduce parasitic parametersSolid-state devicesRead-only memoriesInput controlComputer science

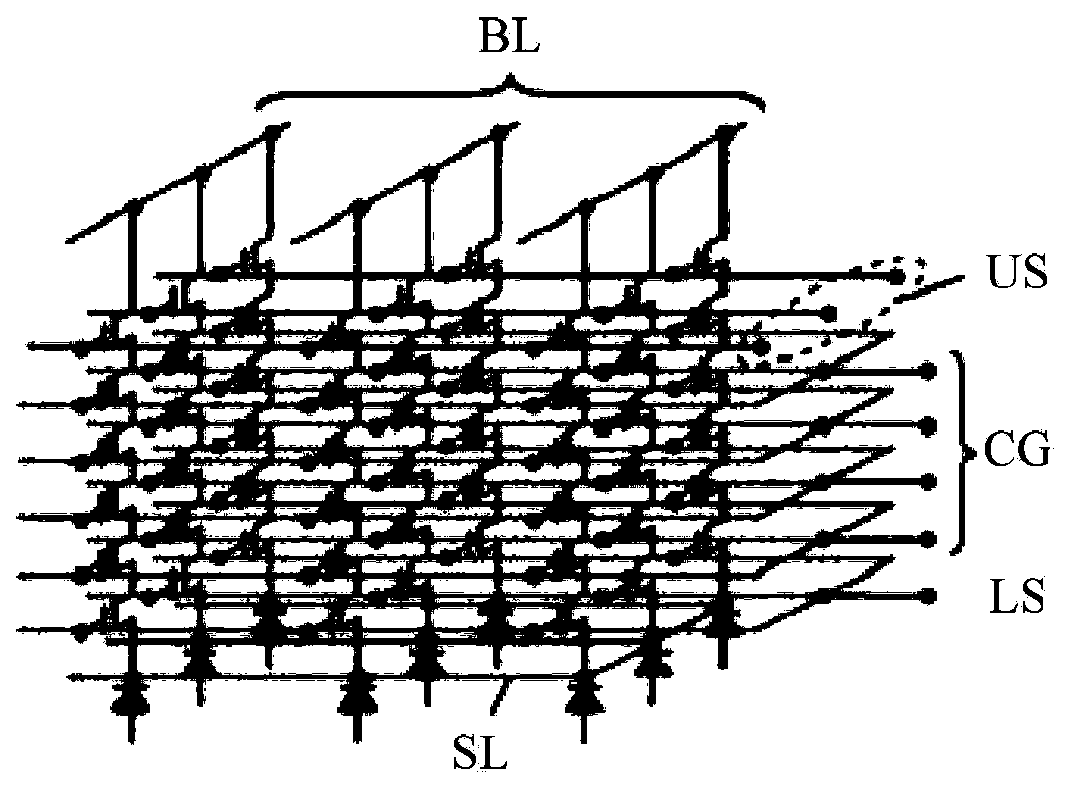

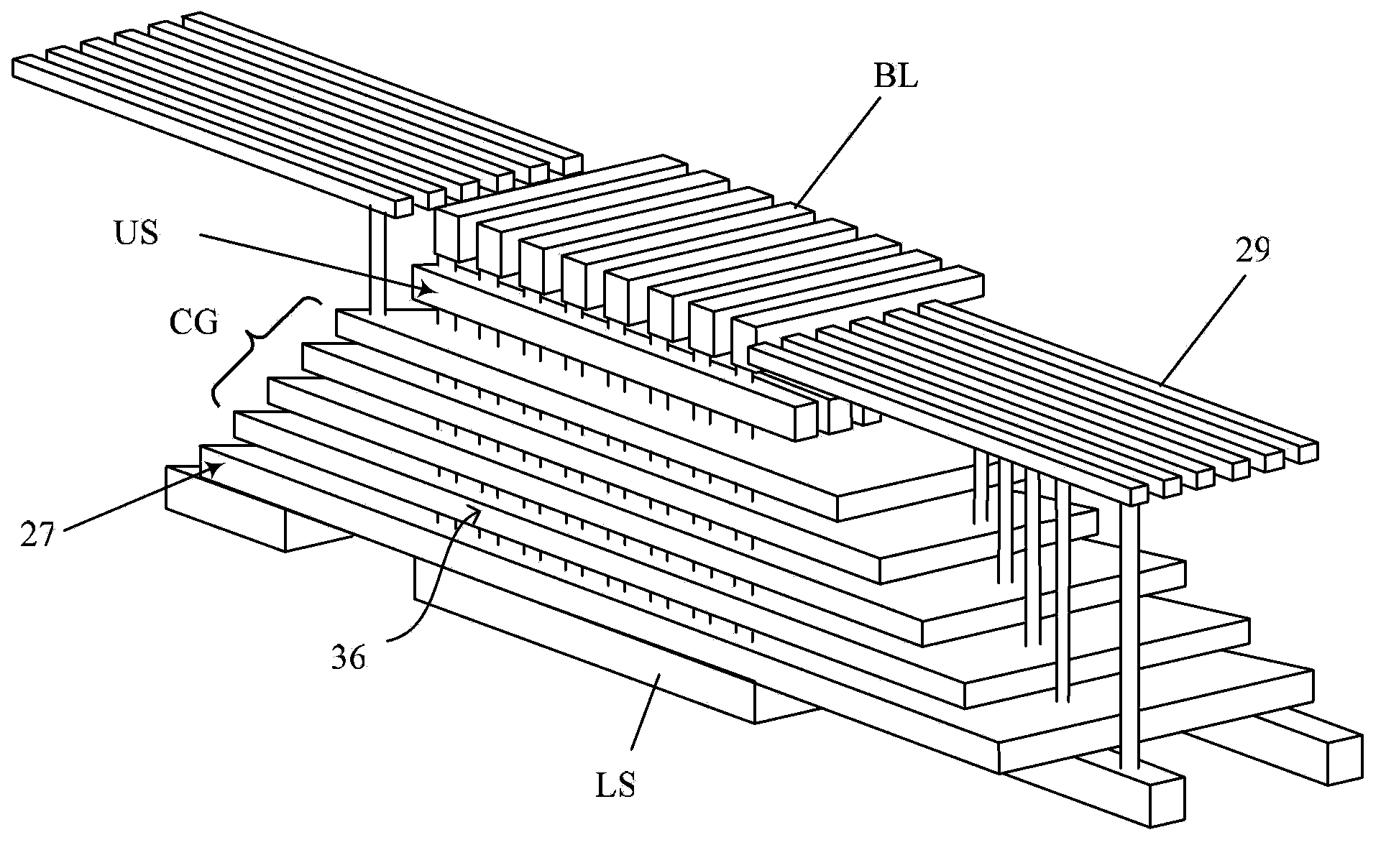

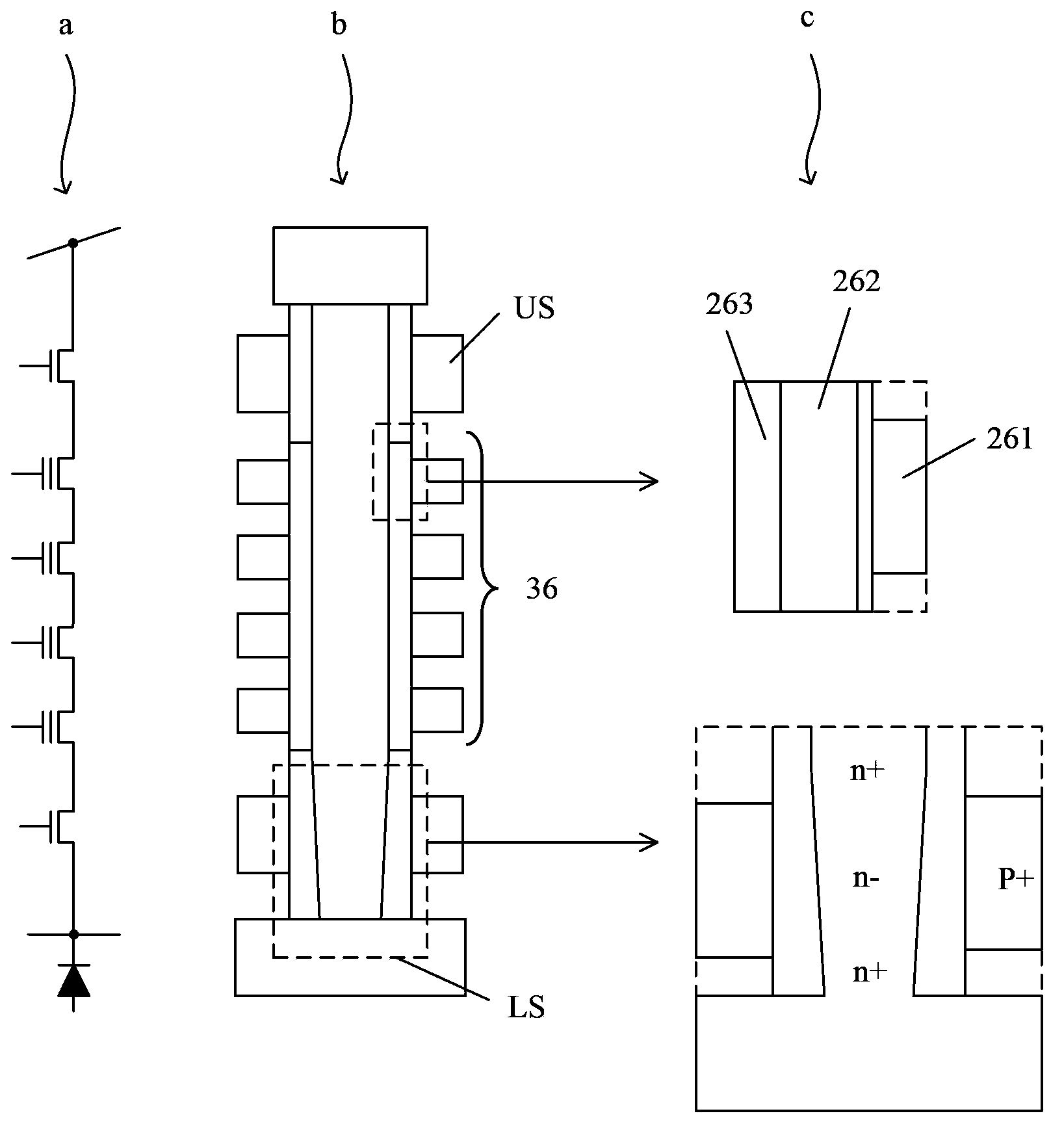

The invention discloses a 3D (three-dimensional) NAND memory and a manufacturing method of the 3D NAND memory. The 3D NAND memory comprises multiple layers of storage arrays and multiple layers of control grid circuits, wherein each layer of the control grid circuit is electrically connected to the same layer of the storage array, so that selection of each layer of the storage array is realized; each layer of the control grid circuit is obtained by cascading a same number of transistors; grids of all the transistors of the control grid circuits are electrically connected to control wires; the number of the control wires is as the same as that of the transistors comprised in each layer of the control grid circuit; the grids of different transistors positioned on the same layer of the control grid circuit are electrically connected to different control wires. According to the 3D NAND memory, a small number of input control wires SSL select a large number of control grid layers through the control grid circuits, so that the area and the volume of the whole memory cannot be enlarged due to the increase of the number of the required layers of control grids when the storage capacity of the memory is improved due to the increase of the number of storage unit layers.

Owner:SEMICON MFG INT (SHANGHAI) CORP

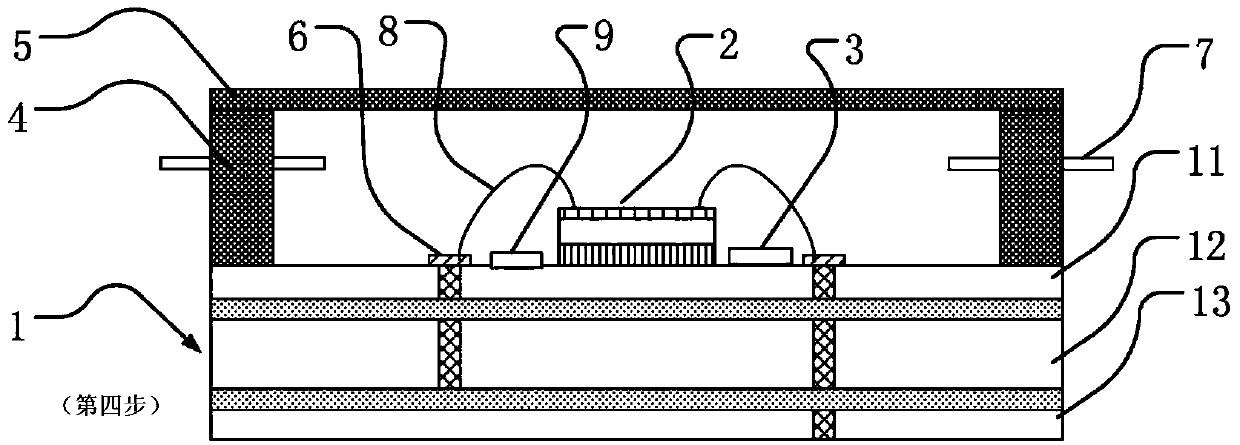

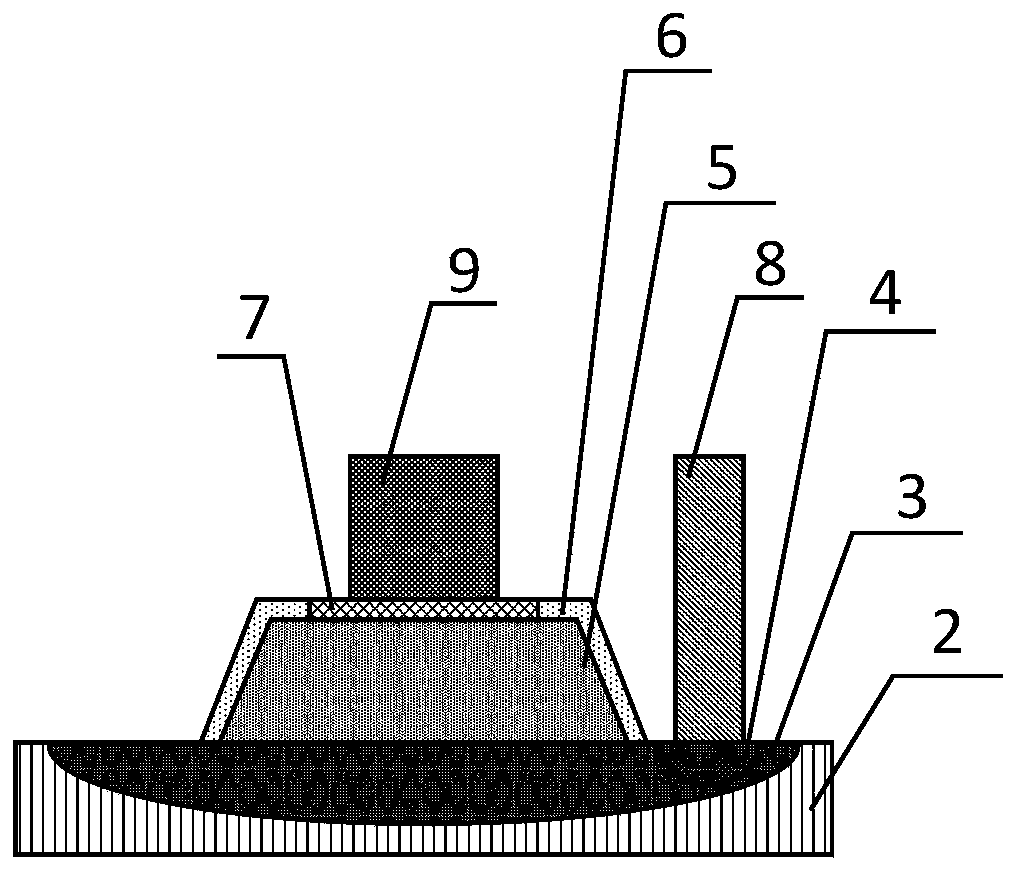

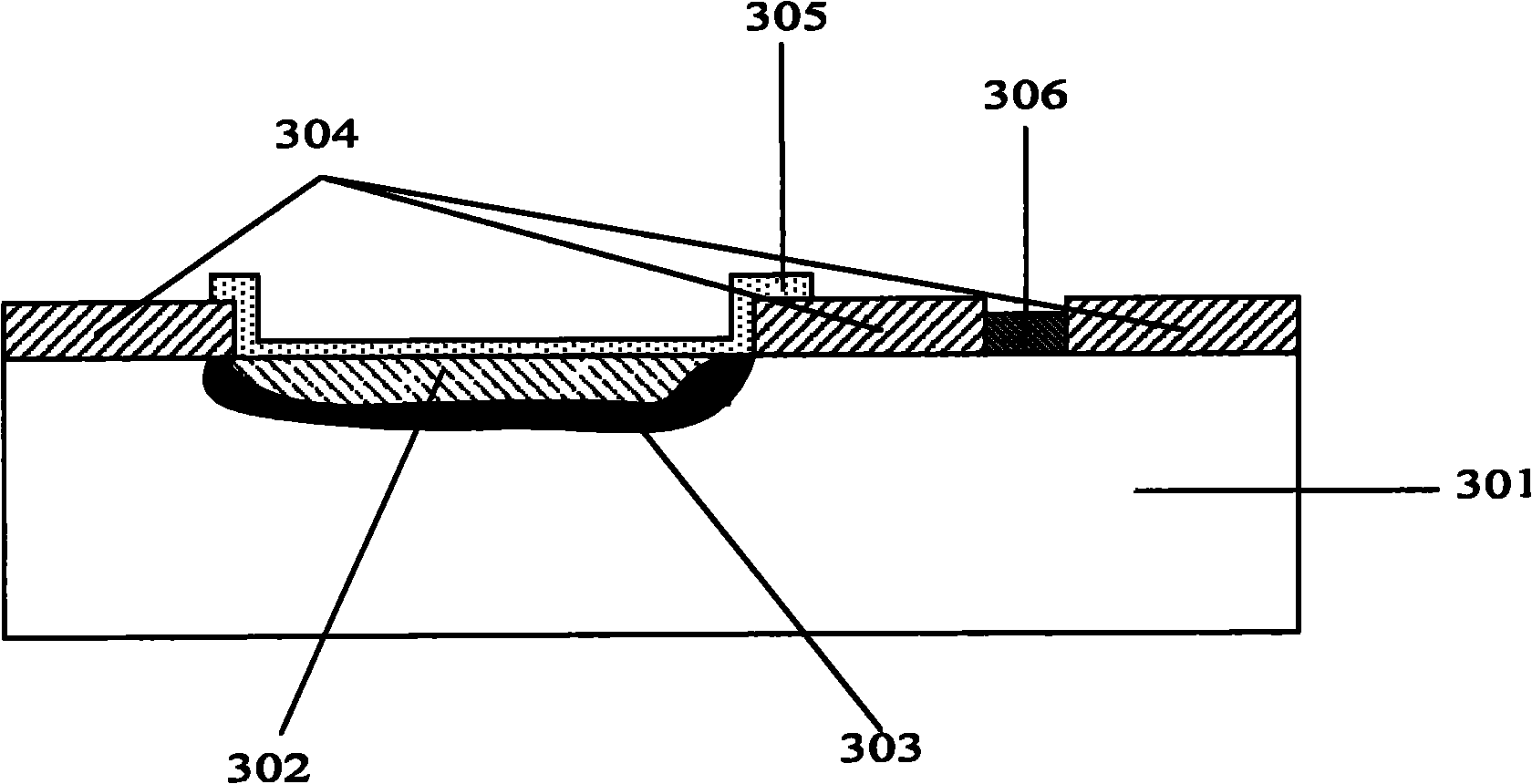

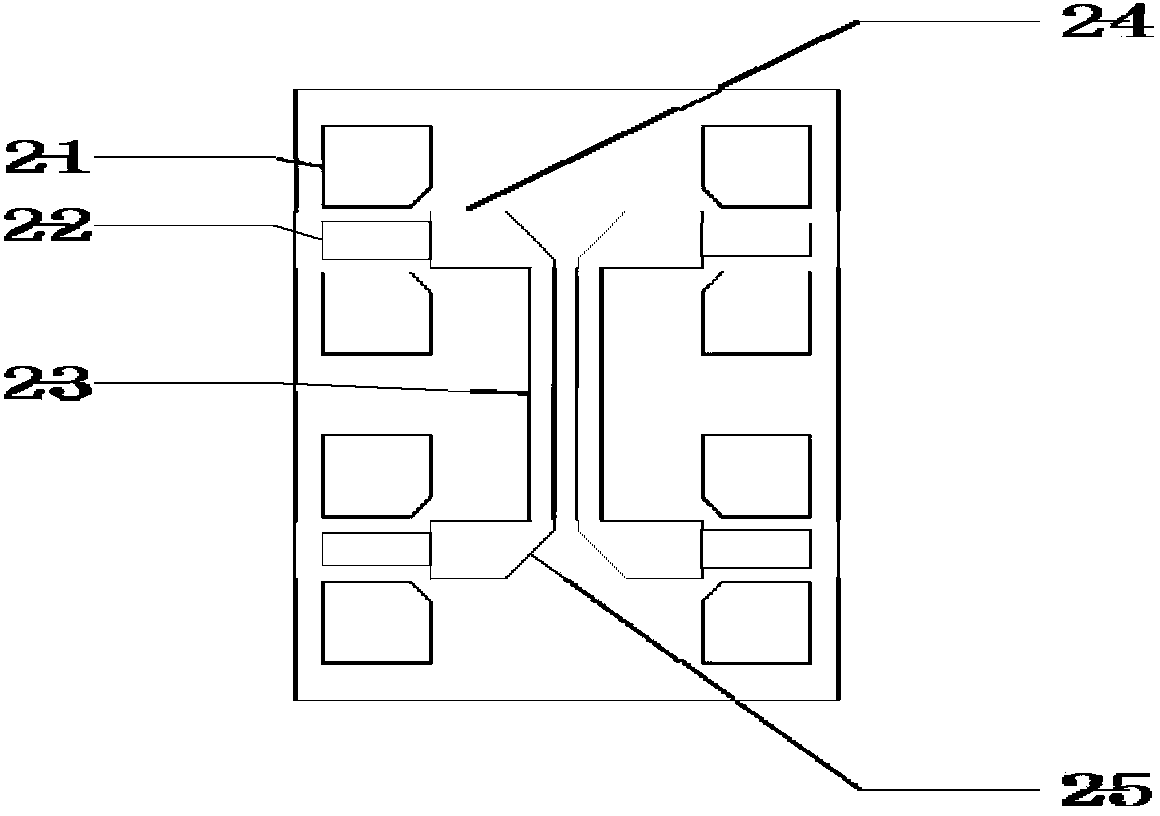

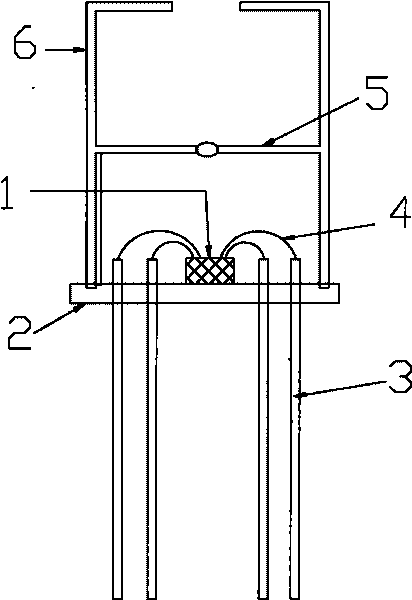

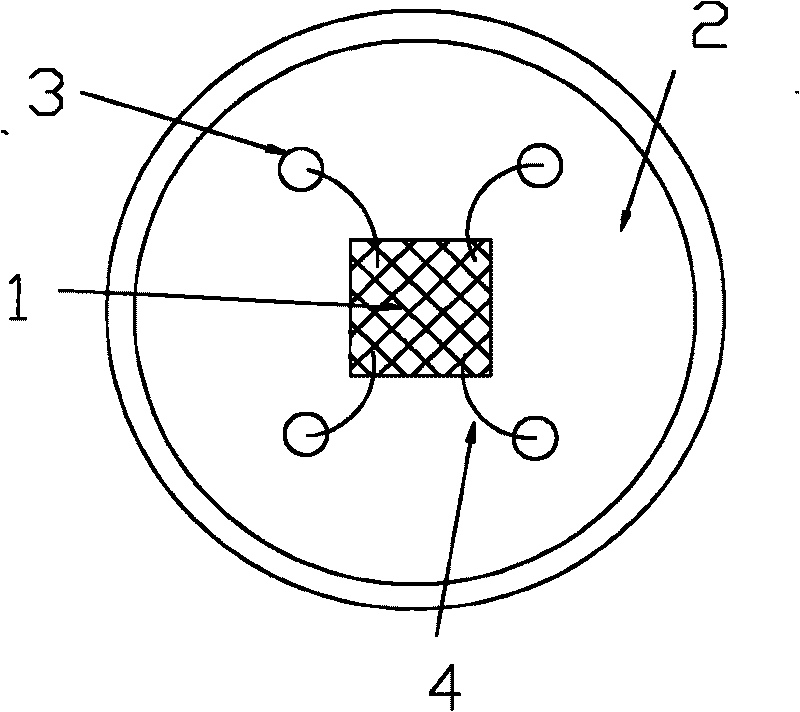

MEMS (Micro-Electromechanical System) sensor encapsulation structure and encapsulation method thereof

ActiveCN103950886ACompact structureReduce electrical connectionsDecorative surface effectsSolid-state devicesHigh densityThermal expansion

The invention relates to an MEMS sensor encapsulation structure and an encapsulation method thereof, which are used for encapsulating an MEMS sensor. The MEMS sensor encapsulation structure is characterized by comprising a ceramic base, a side wall and a top cap, wherein a plurality of metal bonding pads are respectively arranged on a top layer and a bottom layer of the ceramic base; the metal bonding pads on the top layer of the ceramic base are connected with leads of the MEMS sensor; the MEMS sensor is arranged on the ceramic base; the metal bonding pads on the bottom layer of the ceramic base are connected with an external circuit; the ceramic base adopts one-layer or multi-layer perpendicularly interconnected structure; the side wall and the top cap are both made of kovar alloy. According to the invention, the ceramic base of which coefficient of thermal expansion is approximate to that of the MEMS sensor material is selected as the encapsulation material, in order to reduce influence of the base expansion stress to the MEMS sensor; meanwhile, the ceramic base can be utilized to realize one-layer perpendicular interconnection or multi-layer perpendicular interconnection; the system-level integration between the MEMS sensor and the peripheral circuit can be realized within a small area; high-density system-level encapsulation can be realized; the encapsulation flexibility and the expansibility of the MEMS sensor can be realized.

Owner:INST OF GEOLOGY & GEOPHYSICS CHINESE ACAD OF SCI

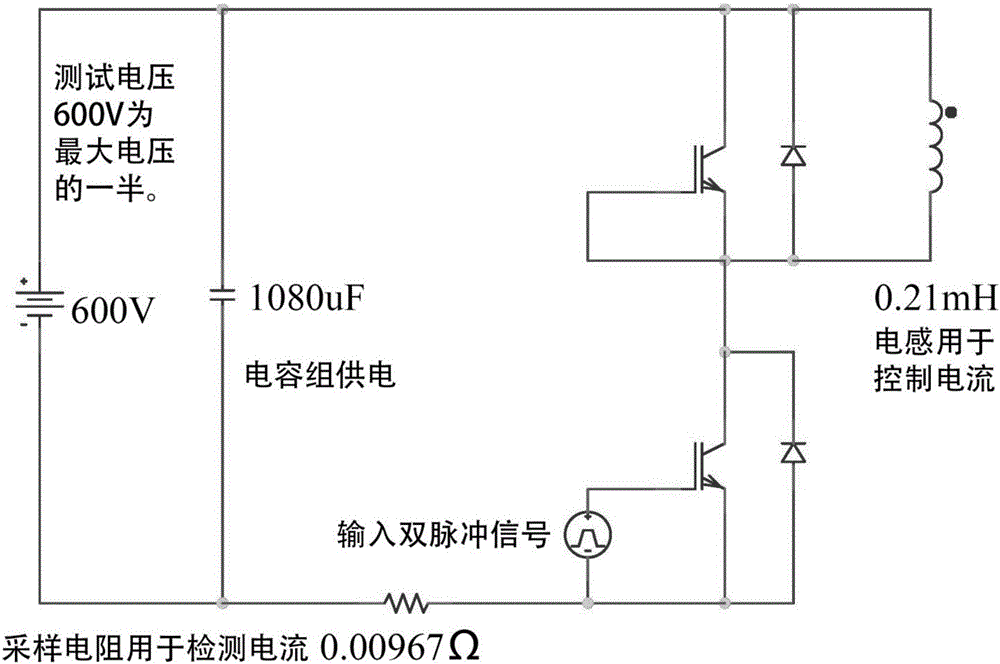

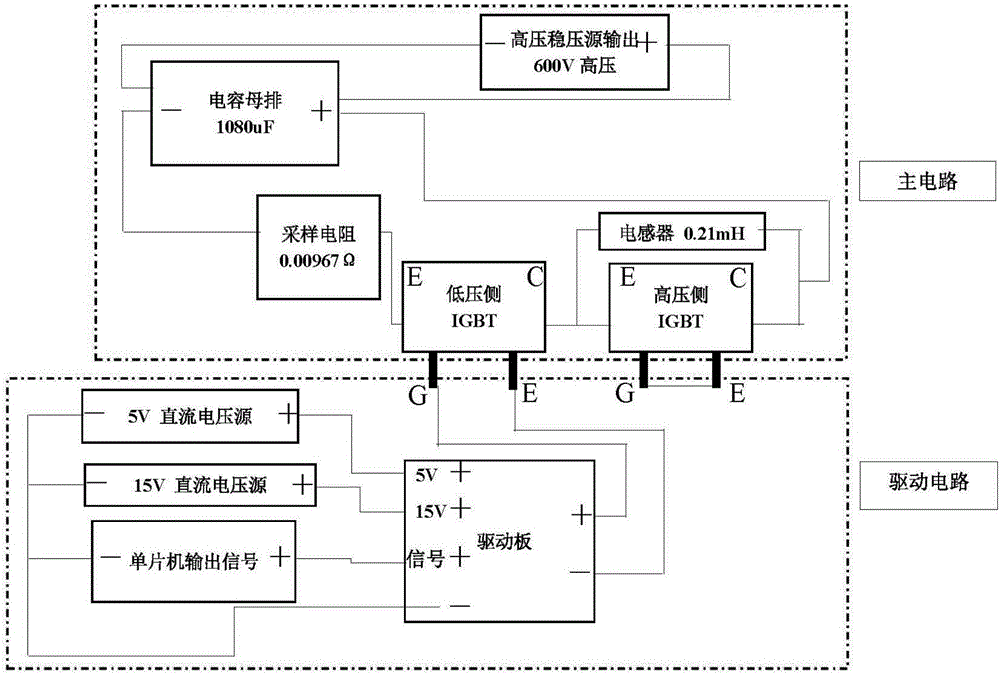

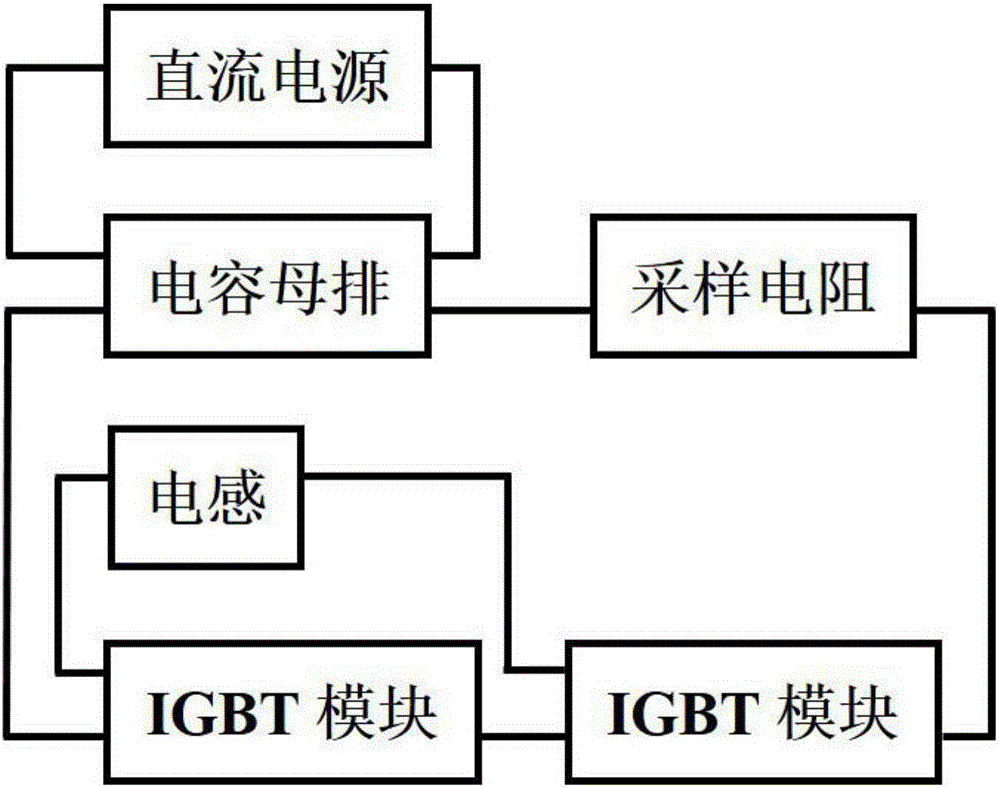

Testing method and device for dynamic switching characteristics of IGBT (Insulated Gate Bipolar Transistor) by utilizing double-pulse technology

InactiveCN106291310AReduce parasitic parametersImprove test accuracyIndividual semiconductor device testingMicrocontrollerDriver circuit

The invention relates to a testing method and device for dynamic switching characteristics of an IGBT (Insulated Gate Bipolar Transistor) by utilizing a double-pulse technology. A double-pulse signal is sent out through utilizing a signal chip microcomputer; a tested IGBT reaches rated working current by a first pulse and a second pulse is used for testing dynamic characteristics of the IGBT; and dynamic voltage and current parameters of the IGBT in a switching-on / off process are tested by utilizing an oscilloscope and a difference isolating probe. The double-pulse signal passes through an IGBT driving board to control the IGBT to be switched on / off in extremely short time; an experiment circuit and a testing circuit are isolated through an isolation transformer so that mutual interference of the signals is avoided; current of a main circuit and voltage at two ends of the IGBT, and voltage at an output end of a driving circuit are measured by utilizing the isolation transformer, the oscilloscope and the difference isolating probe; an oscillogram is recorded by the oscilloscope; and dynamic switching characteristic parameter sizes of the IGBT are calculated according to ascending and descending time, delaying time and on-off energy. Parasitic parameters in the circuits are reduced and a testing result is accurate.

Owner:TIANJIN UNIV

Microwave film resistor, microwave film resistor network module and manufacturing method thereof

InactiveCN101533693AReduce microwave lossReduce areaOther resistor networksResistors adapted for applying terminalsFilm resistanceHigh resistance

The invention discloses a microwave film resistor and a manufacturing method thereof, and belongs to the field of circuit elements. The microwave film resistor comprises a ceramic substrate, a film resistance layer which is adhered to the upper surface of the ceramic substrate and an electrode layer which is adhered to the film resistance layer. The film resistor has the advantages of high precision, high using frequency and high resistance stability. In addition, the invention also discloses a microwave film resistor network module and a manufacturing method thereof, wherein the microwave film resistor network module is formed by integrating three or more microwave film resistors on one module.

Owner:广州翔宇微电子有限公司

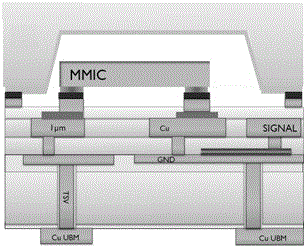

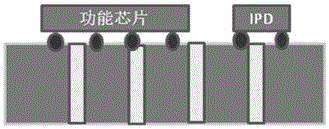

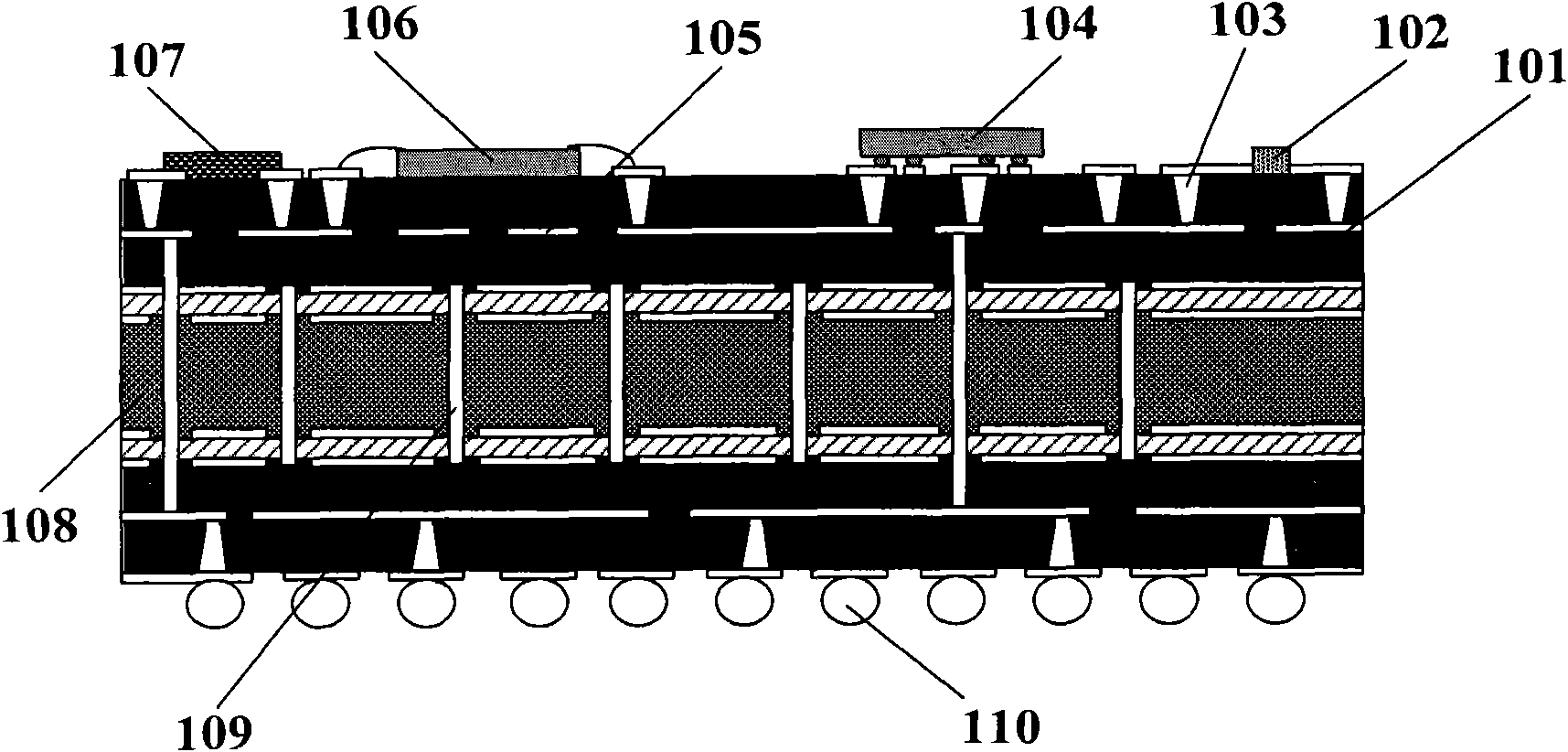

Manufacturing method of three-dimensional bonding stack interconnect integration for radio-frequency microsystem device

InactiveCN106783847AImprove efficiencyImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesBond interfaceHigh resistivity silicon

The invention provides a manufacturing method of a three-dimensional bonding stack interconnect integration for a radio-frequency microsystem device. The method comprises the steps as follows: high-resistivity silicon is taken as a substrate or an adapter plate; multi-layer dielectric-metal alternate wiring is completed for radio-frequency signal transmission and control on the substrate or the adapter plate; heterogeneous compound chips achieve heterogeneous integration through chip to wafer bonding, all chips are connected with metal bumps on the silicon substrate or the adapter plate through a bottom bonding pad to achieve signal transmission among different layers, and three-layer structure stacking and chip protection are achieved through bonding of wafers with silicon cavities and the wafer of the silicon substrate or the adapter plate; and leading-out of signals of a whole device is achieved by adopting a through-silicon via technology. The method has the advantages that the heterogeneous chips are integrated together through three-layer stacking, so that the original function of the device is greatly improved, leading-out of the signals from bonding interfaces is achieved by adopting the through-silicon via technology, a closed and compact chip structure is formed, three-dimensional heterogeneous integration of a radio-frequency device is really achieved, the technology is simplified, packaging is low in cost and the yield is high.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

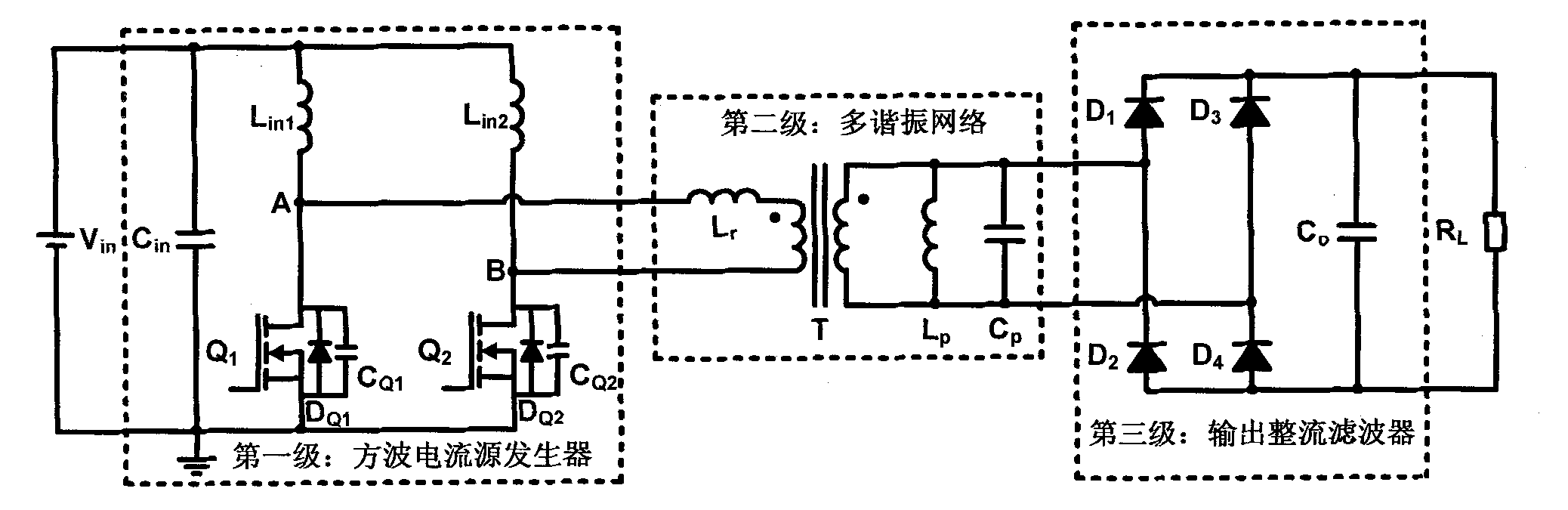

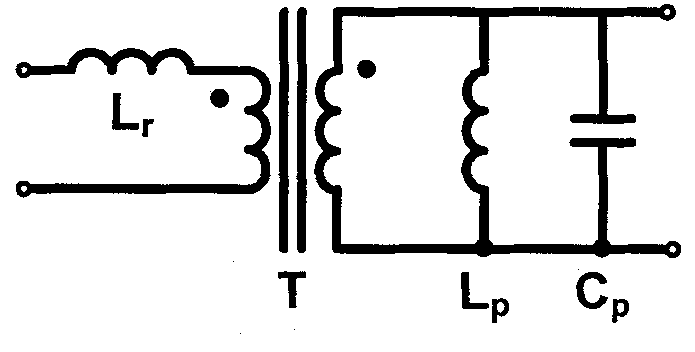

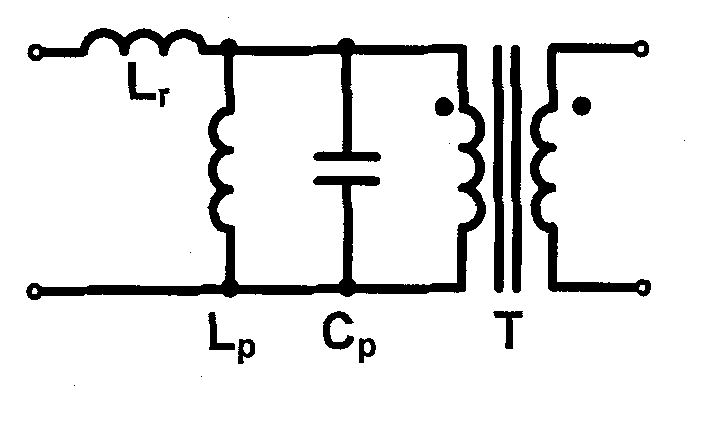

Current-type multi-resonance direct current (DC) converter

ActiveCN101902129AReduce input current rippleImplement ZCSDc-dc conversionElectric variable regulationCapacitanceResonance

The invention relates to direct current (DC) step-up power conversion technology and discloses a current-type multi-resonance DC converter. The current-type multi-resonance DC converter comprises a square-wave current source generator, a multi-resonance network and a rectification filtering output unit which are sequentially connected in series, and is characterized in that: the multi-resonance network comprises a transformer, a parallel resonant inductor, a parallel resonant capacitor and a serial resonant inductor, wherein the serial resonant inductor is connected with a primary side of the transformer; the rectification filtering output unit comprises a diode rectifying circuit and a filtering capacitor which is connected with an output end of the diode rectifying circuit in parallel.

Owner:无锡格兰德微电子科技有限公司

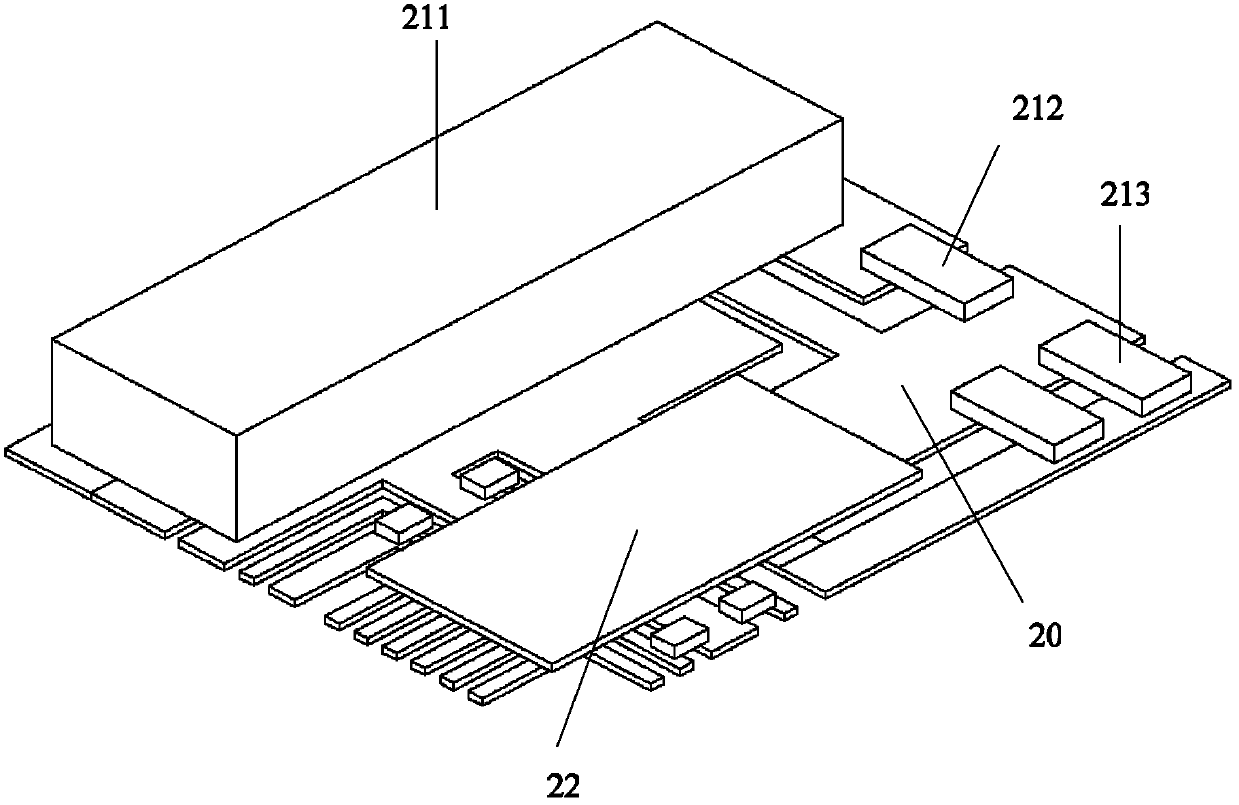

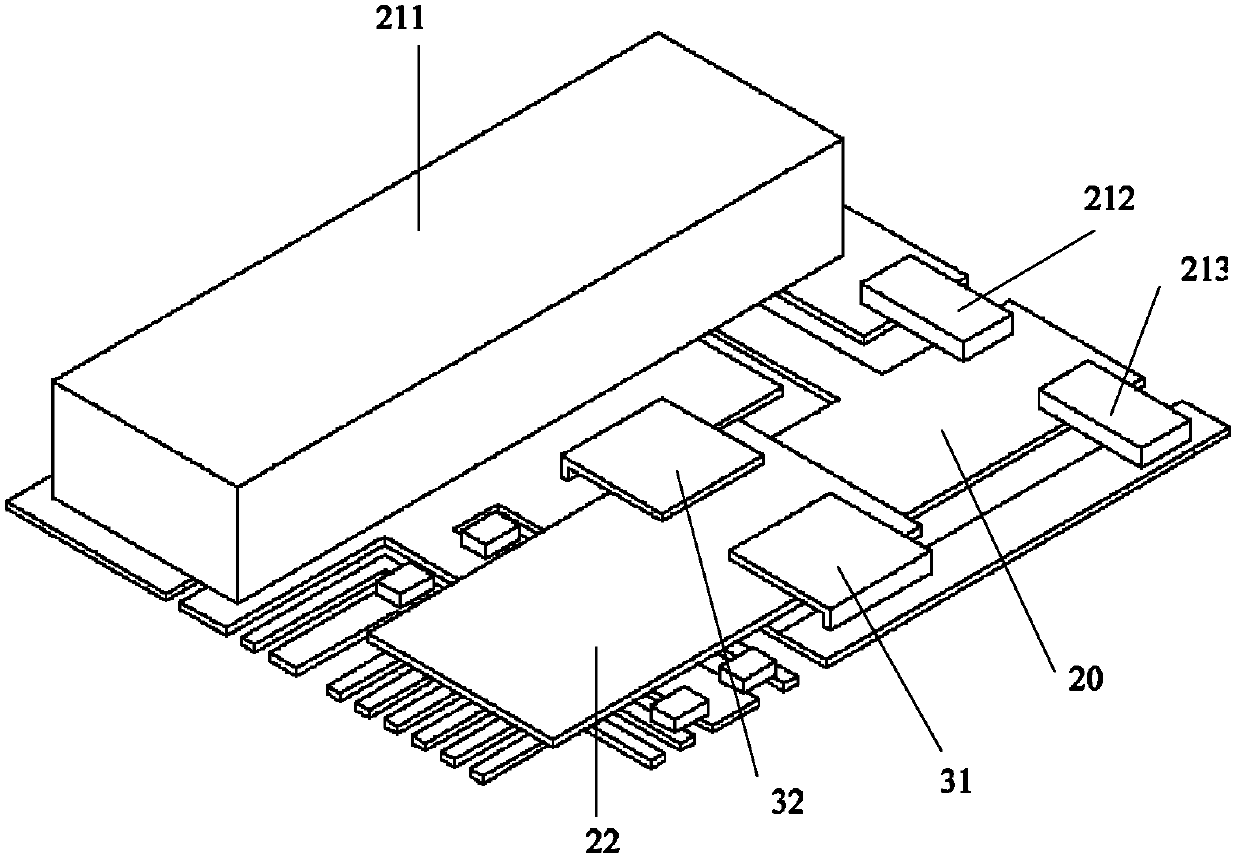

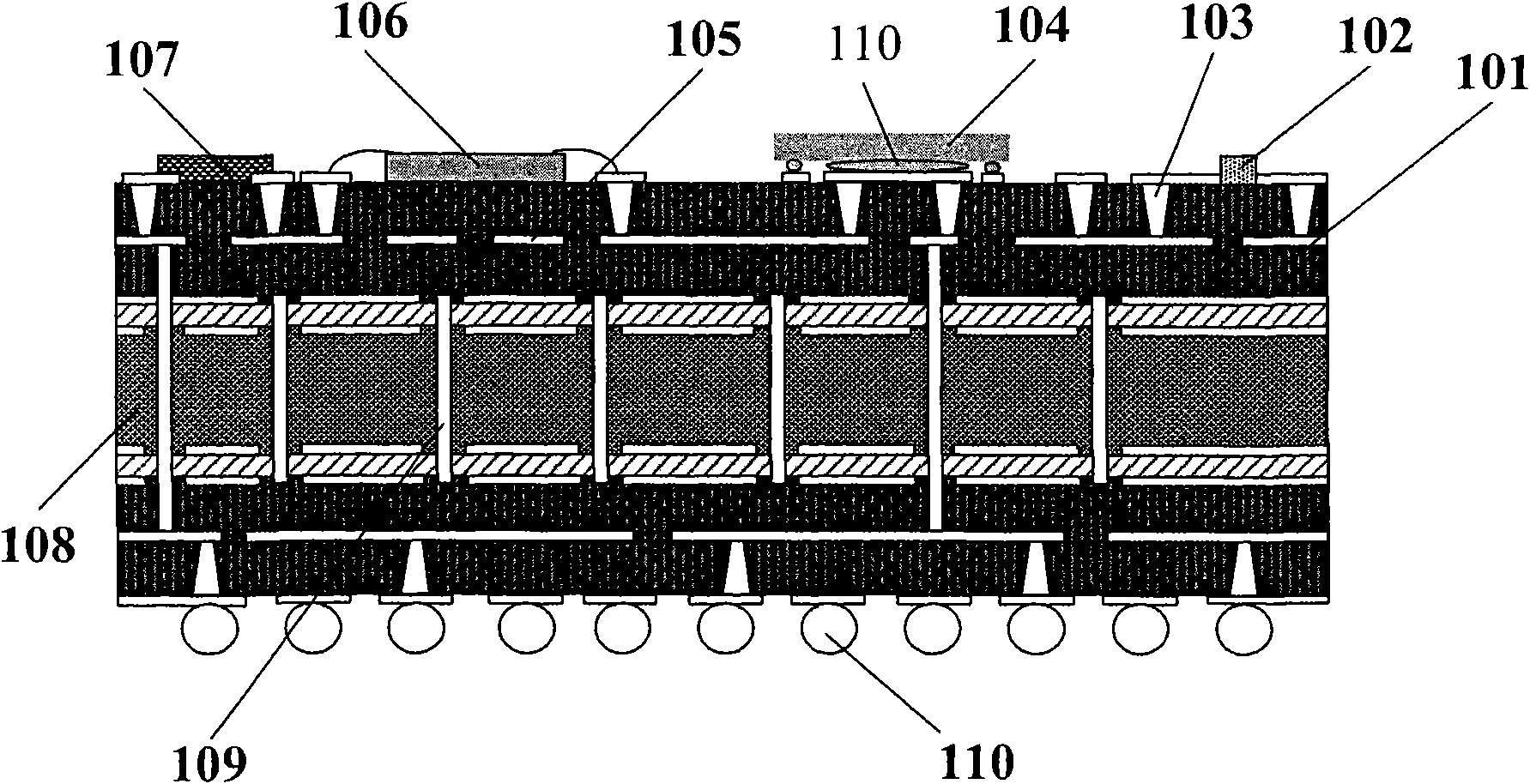

Power module and encapsulation and integration method thereof

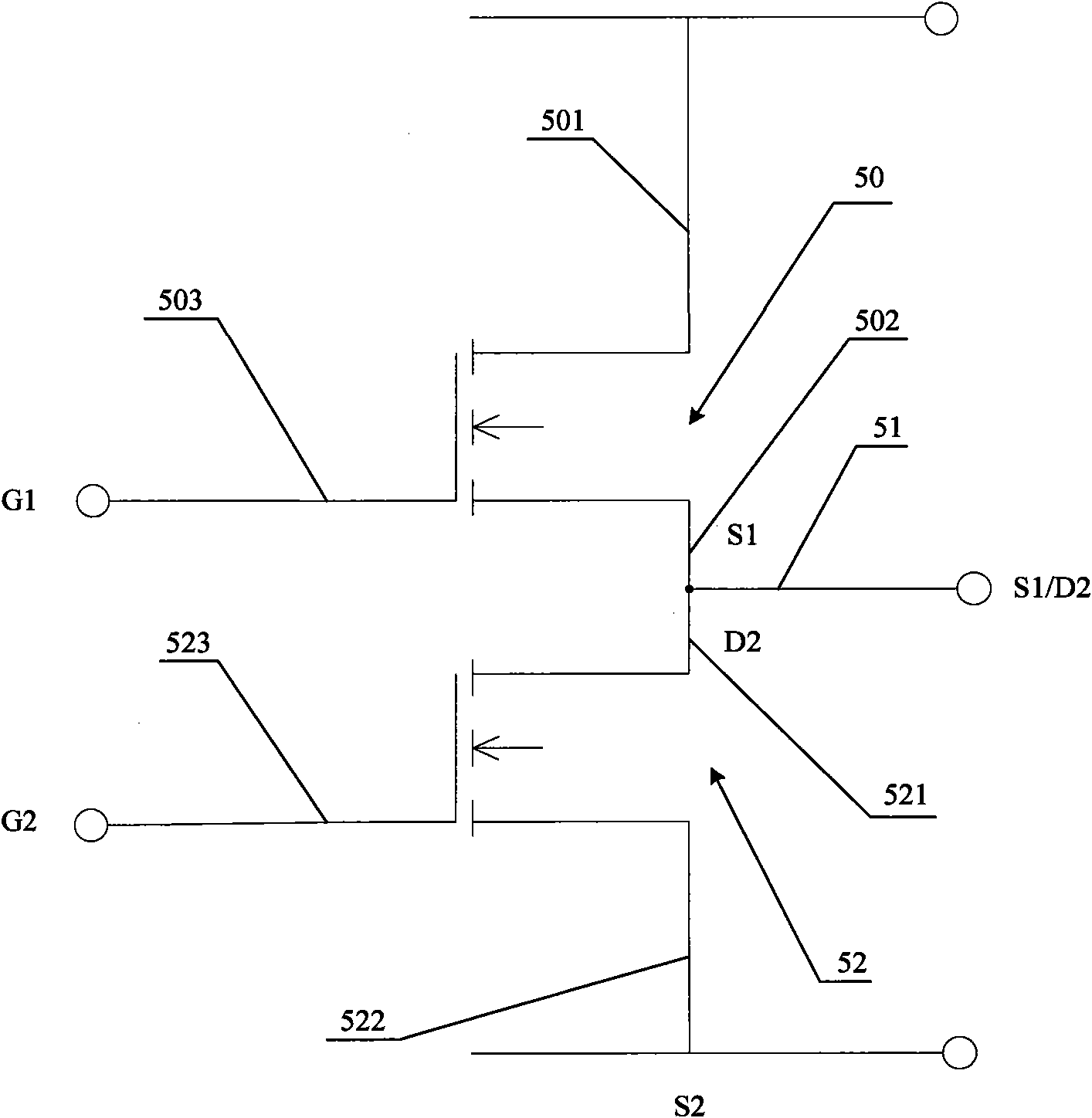

InactiveCN102171825AShort connection distanceReduce parasitic parametersConversion constructional detailsSemiconductor/solid-state device detailsMOSFETField-effect transistor

Disclosed are a power module and an encapsulation and integration method thereof. The power module comprises: a lead frame, a passive device, an integrated circuit (IC) and a power switch Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET), wherein the passive device is welded on the lead frame by Surface Mount Technology (SMT), the IC is a flip chip which is mounted and welded on the leadframe.

Owner:HUAWEI TECH CO LTD

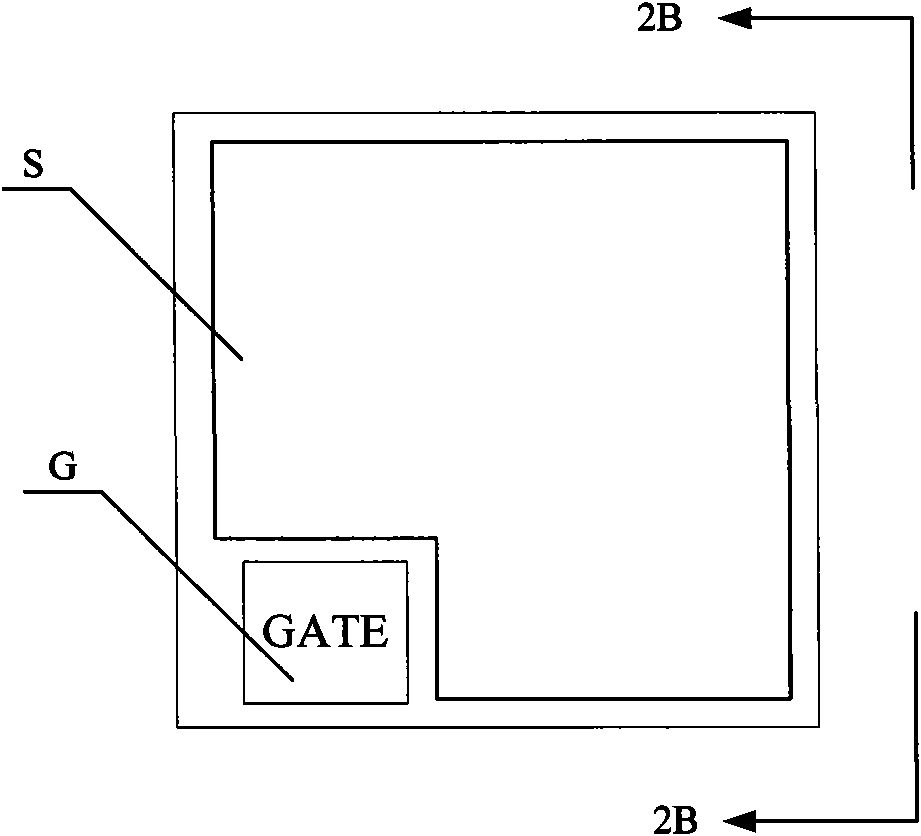

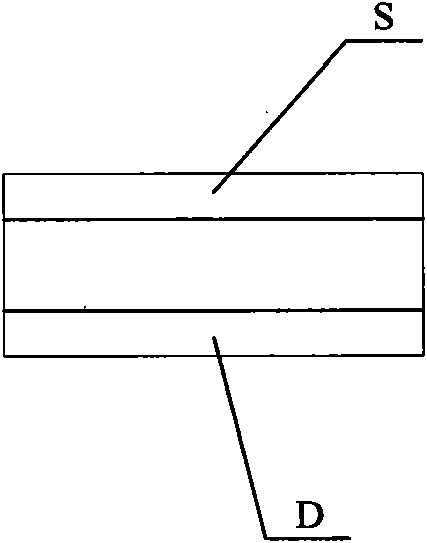

Field-effect transistor and manufacturing method thereof

ActiveCN106784001AReduce parasitic parametersImprove performanceNanoinformaticsSemiconductor/solid-state device manufacturingSemiconductor materialsEngineering

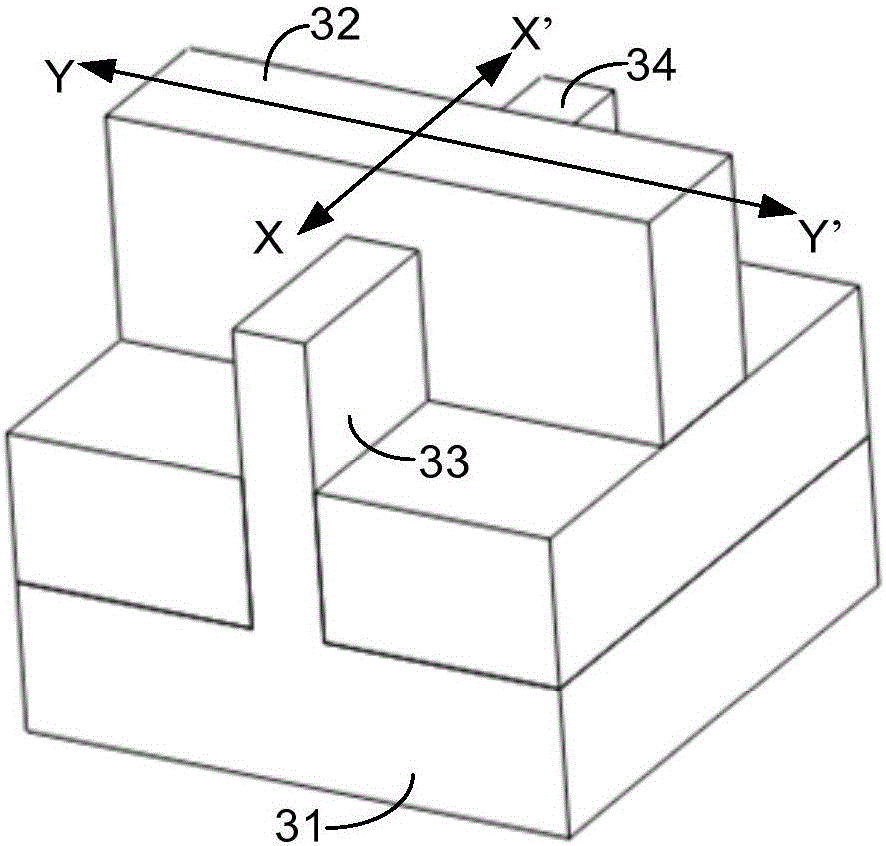

The embodiment of the invention provides a field-effect transistor and a manufacturing method thereof and relates to the technical field of semiconductors. Parasitic parameters of the field-effect transistor can be reduced to improve the reliability of the field-effect transistor. The method comprises the steps as follows: a support structure with superlattice characteristics is formed on a semiconductor substrate; the support structure comprises first semiconductor material layers and second semiconductor material layers, which are alternately arranged; isolating layers are arranged at two sides of the support structure; a false gate structure covering the support structure is formed along the juncture of the isolating layers and the support structure; the length of the false gate structure in a gate length direction is smaller than those of the first semiconductor material layers in the gate length direction; areas except for sacrificial layers in the first semiconductor material layers are removed along the gate length direction to form insulating grooves; the dielectric constants of mediums filled into the insulating grooves are smaller than those of the first semiconductor material layers; and a source and a drain are formed in preset source region and drain region along the gate length direction and the source and the drain are isolated from the sacrificial layers through the insulating grooves.

Owner:HUAWEI TECH CO LTD

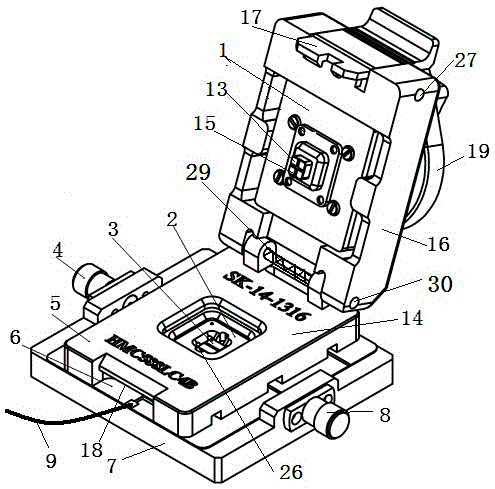

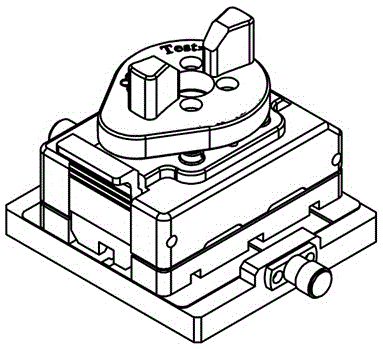

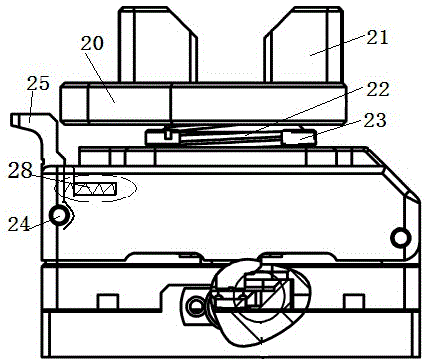

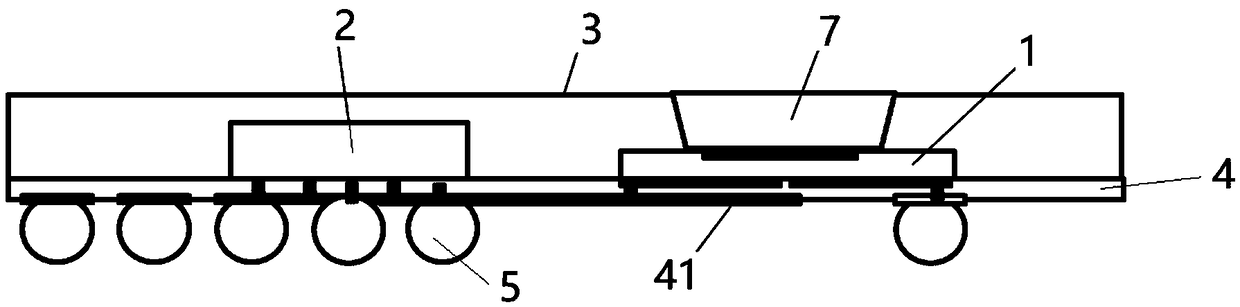

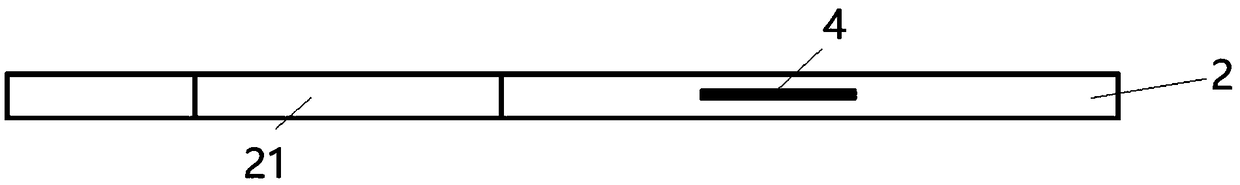

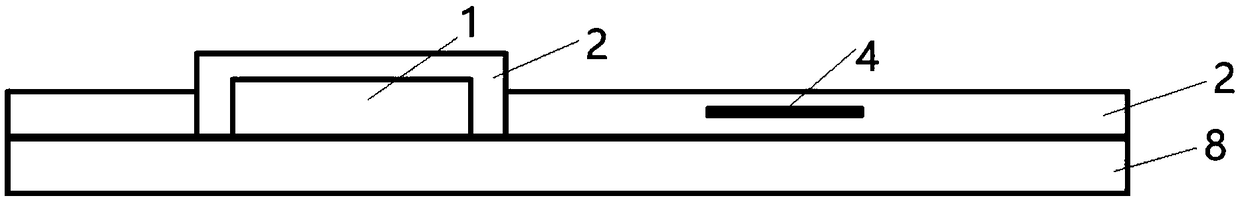

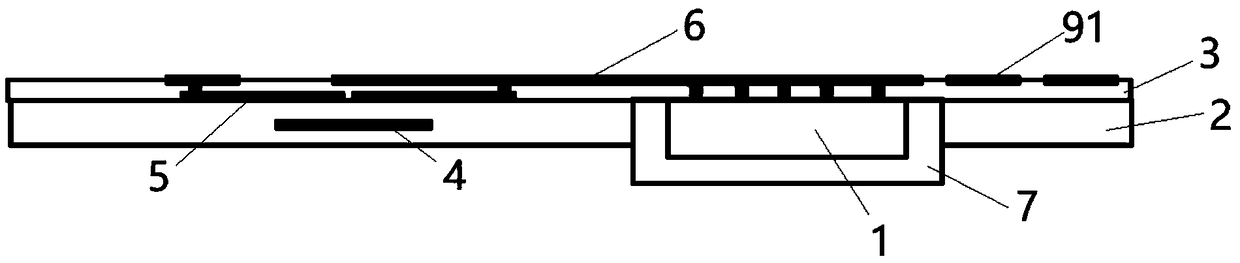

Encapsulated micro-wave voltage-controlled oscillator test device

InactiveCN105044402AReduce connection contact distanceGuaranteed normal transmissionMeasurement instrument housingTest efficiencyEngineering

The invention discloses an encapsulated micro-wave voltage-controlled oscillator test device. The device comprises a test clamp used for installing and fixing a voltage-controlled oscillator, a conductive rubber and a test adaption circuit board. The test adaption circuit board is installed on a metal base plate and is connected to monitoring equipment through a cable. The conductive rubber is pasted on a central section of an upper end surface of the test adaption circuit board. The test clamp is placed on the test adaption circuit board and is fixedly connected to the metal base plate. In the invention, an encapsulated micro-wave voltage-controlled oscillator is placed in the test clamp; and a pin of the oscillator is connected to the test adaption circuit board through the conductive rubber so that contact between a chip pin and the test adaption circuit board can be avoided, a parasitic parameter is reduced and normal transmission of microwave signals is guaranteed. Besides, because of elasticity of the conductive rubber, damages generated through carrying out hard pressing on the chip can be avoided; test reliability and test efficiency of the encapsulated micro-wave voltage-controlled oscillator are increased; and the device possesses characteristics that the structure is simple and assembling and disassembling are convenient.

Owner:GUIZHOU AEROSPACE INST OF MEASURING & TESTING TECH

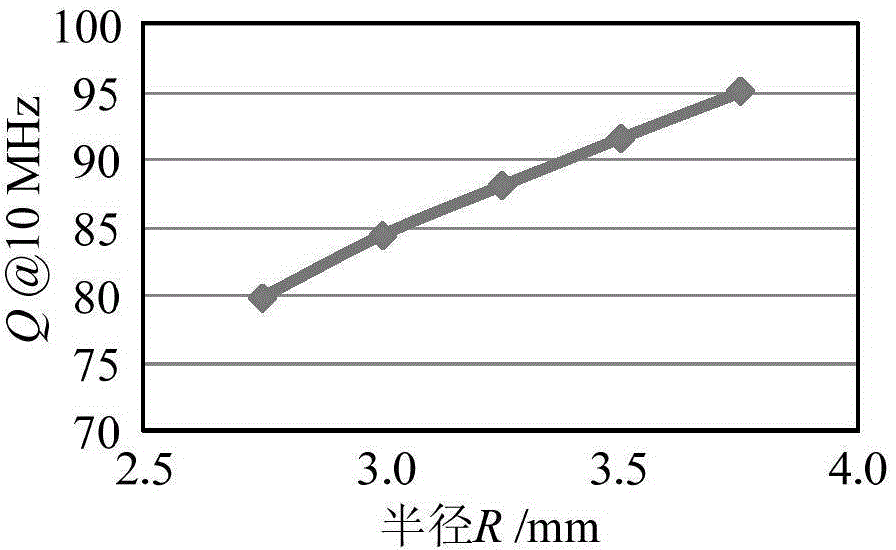

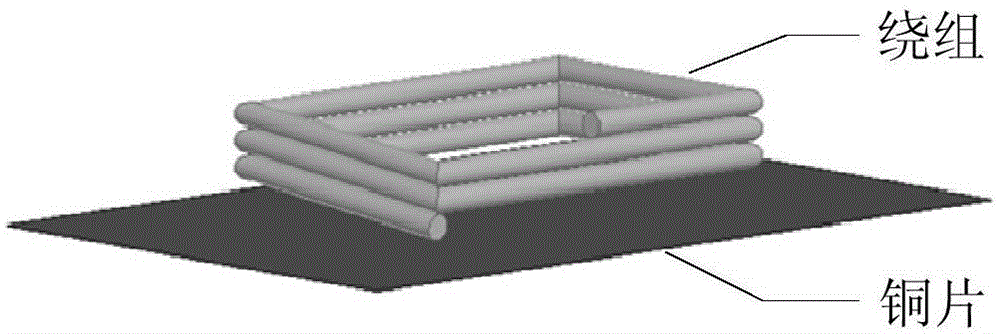

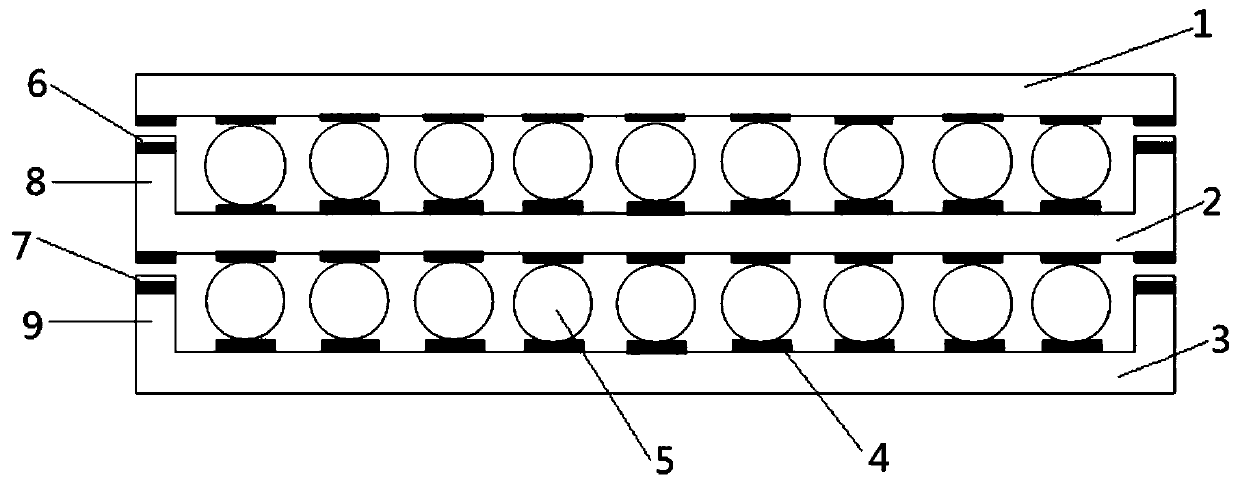

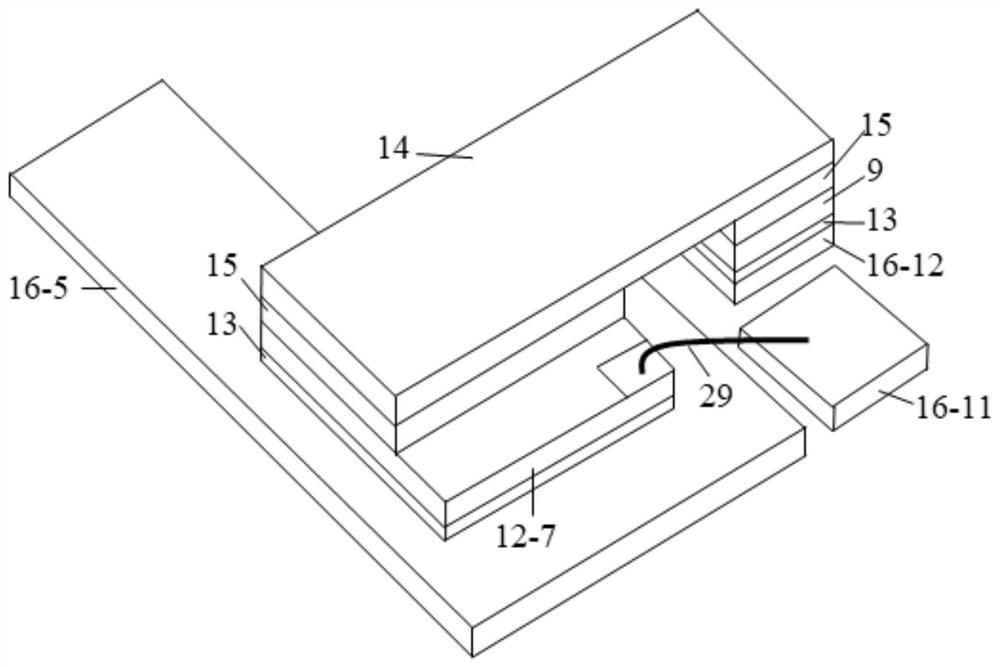

3D integrated framework of ultrahigh frequency power converter

ActiveCN104934209AReduce volumeImprove power densityTransformers/inductances coils/windings/connectionsFixed signal inductancesTransformerEngineering

The invention provides a 3D integrated framework of an ultrahigh frequency power converter. The 3D integrated framework comprises a PCB circuit layer and a winding unit erected on the PCB circuit layer. The winding unit is connected with the PCB circuit layer through a wire. The winding unit comprises winding layers formed on a first insulating layer and a first soft magnetic thin film layer formed on a second insulating layer. The first soft magnetic thin film layer is arranged below the winding layers in a laminated mode to be used for achieving magnetic shielding between the winding layers and the PCB circuit layer. Compared with the prior art, by the adoption of 3D integration, the size of the converter is reduced, and the power density is increased; soft magnetic materials are adopted to form the magnetic shielding layer, magnetic field interference between windings and the PCB circuit layer and between the windings and external metal is solved, the Q value of the windings is increased, the alternating current resistance and high-frequency loss of an inductor and a transformer are reduced, and the working efficiency of the converter is improved; a plane magnetic element is further adopted, and the miniaturization and flattening of products are guaranteed; temperature rising of the magnetic element is reduced greatly, and the working environment of a semiconductor device is improved.

Owner:MORNSUN GUANGZHOU SCI & TECH +1

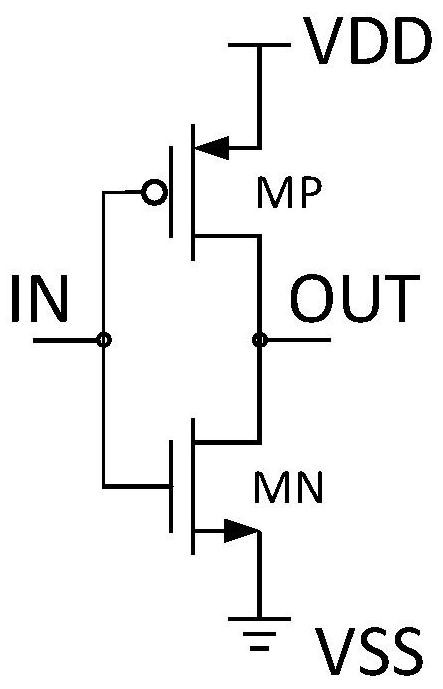

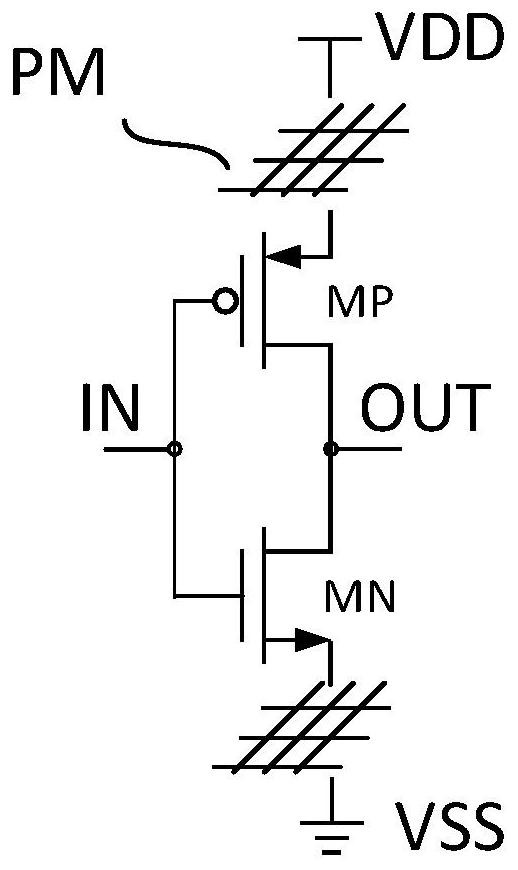

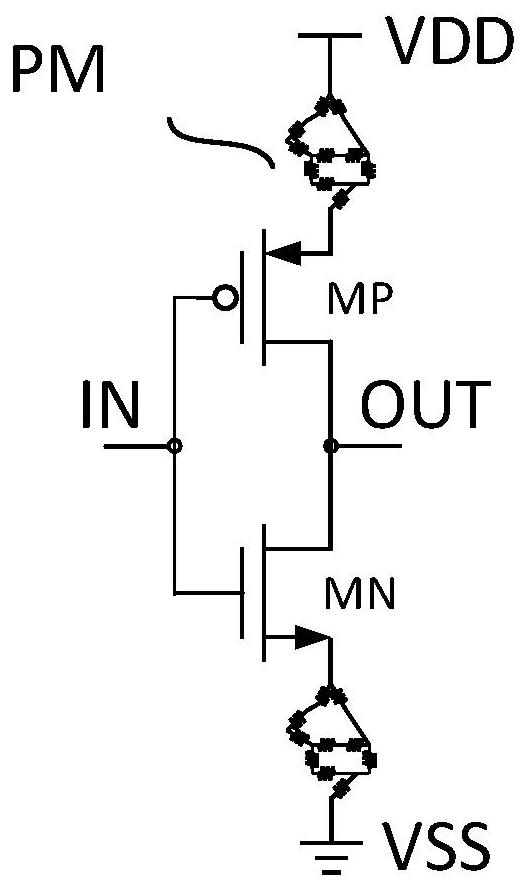

Half-bridge drive circuit chip

ActiveCN101834176ASmall footprintReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesComputer moduleLead frame

The invention discloses a half-bridge drive circuit chip comprising a lead frame, wherein three paddles mutually separated and insulated are arranged on an encapsulation face of the lead frame, each paddle is provided with at least one connecting pin, a drive control circuit module, a first power device and a second power device are respectively arranged on the three paddles and are mutually connected through metal leads, and the chip is formed by encapsulating the drive control circuit module, the first power device and the second power device by an encapsulation body. Compared with the three chips which are formed by respectively independently encapsulating the drive control circuit module and the two power devices, the chip is more compact; only one encapsulation body is adopted, therefore, the production cost is greatly reduced; and the distance of connection among components in the chip is smaller than that of connection among three independent chips, therefore, parasitic parameters are greatly reduced.

Owner:NINGBO SEMICON INT CORP

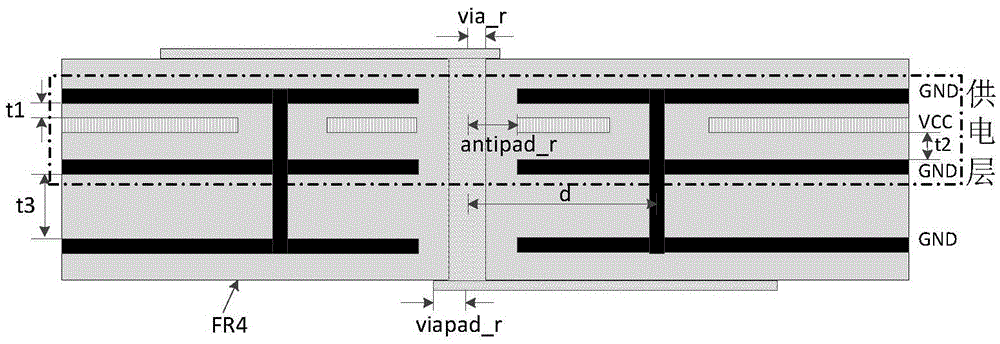

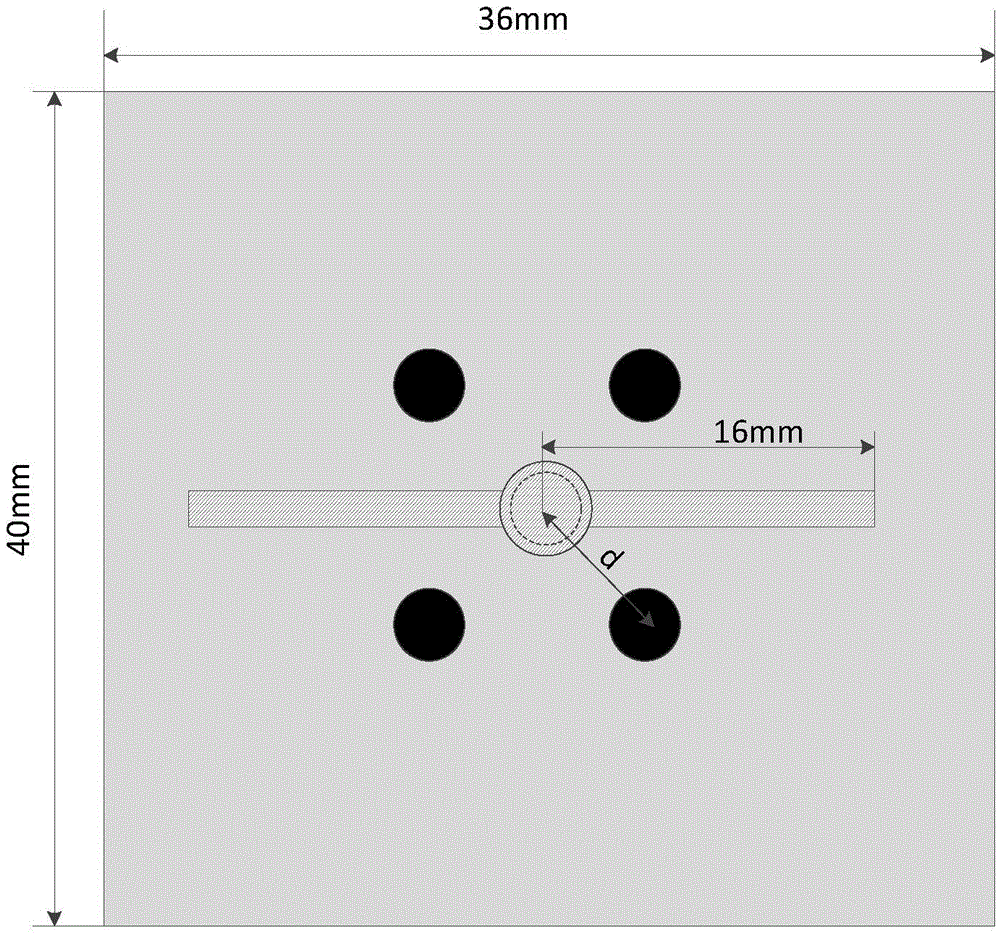

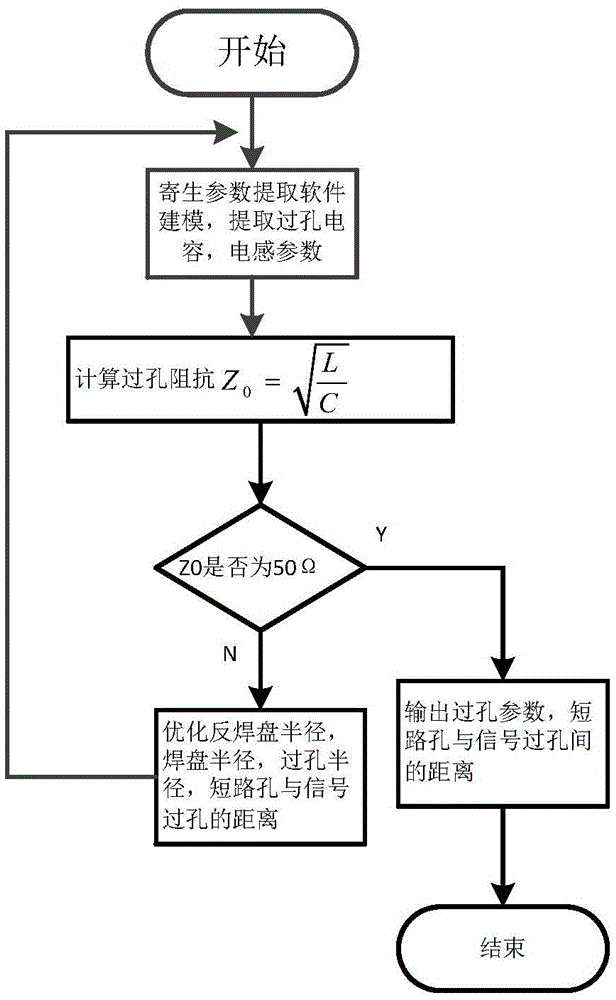

Novel lamination structure of multilayer high-speed PCB and signal via-hole optimization method

InactiveCN105578714ASolving Signal Integrity IssuesImprove SI performanceCross-talk/noise/interference reductionPrinted circuit aspectsGround planeMultiple layer

The invention relates to a novel lamination structure of a multilayer high-speed PCB. The novel lamination structure comprises multiple layers of ground planes, power supply planes arranged between every two adjacent ground planes, and two layers of signal planes arranged on the top layer and the bottom layer of a PCB, which are up-down successively arranged. Spaces between the power supply planes and adjacent two layers of ground planes are filled with medium. Each of the signal planes arranged on the top layer and the bottom layer of the PCB comprises a weld disc and a microstrip line. A signal via hole is arranged in each of the weld discs. The microstrip lines are connected together via the signal via holes. N grounding short circuit holes are uniformly arranged around each of the signal via hole. According to the invention, the grounding short circuit holes can provide ideal low-impedance returning paths for the signal via holes, and parasitic parameters of current paths among the planes are reduced.

Owner:SYSU CMU SHUNDE INT JOINT RES INST +1

Germanium-silicon photoelectric detector with high bandwidth and high responsivity

ActiveCN111048606AImprove responsivenessHigh bandwidthSemiconductor devicesHigh bandwidthPhotodetection

The invention discloses a germanium-silicon photoelectric detector with high bandwidth and high responsivity, and relates to the technical field of photoelectric detection. The germanium-silicon photoelectric detector comprises a silicon waveguide, a silicon substrate, a lightly doped silicon region, a heavily doped silicon region, a germanium absorption region, an epitaxial silicon region, an epitaxial silicon doped region, a first electrode and a second electrode. The silicon waveguide is used for transmitting incident light; the silicon substrate is used for receiving the incident light propagated by the silicon waveguide; the lightly doped silicon region is arranged in the silicon substrate; the heavily doped silicon region is arranged in the lightly doped silicon region; the germaniumabsorption region is arranged on the lightly doped silicon region, the germanium absorption region comprises a first part far away from the silicon waveguide, and the projection surface of the firstpart on the lightly doped silicon region is arc-shaped; the epitaxial silicon region surrounds and covers the germanium absorption region; the epitaxial silicon doped region covers the top of the germanium absorption region; the first electrode is arranged on the heavily doped silicon region, and the shape of the first electrode is matched with that of the heavily doped silicon region; the secondelectrode is arranged on the epitaxial silicon doped region. The germanium-silicon photoelectric detector has high responsivity and relatively high bandwidth.

Owner:WUHAN POST & TELECOMM RES INST CO LTD +1

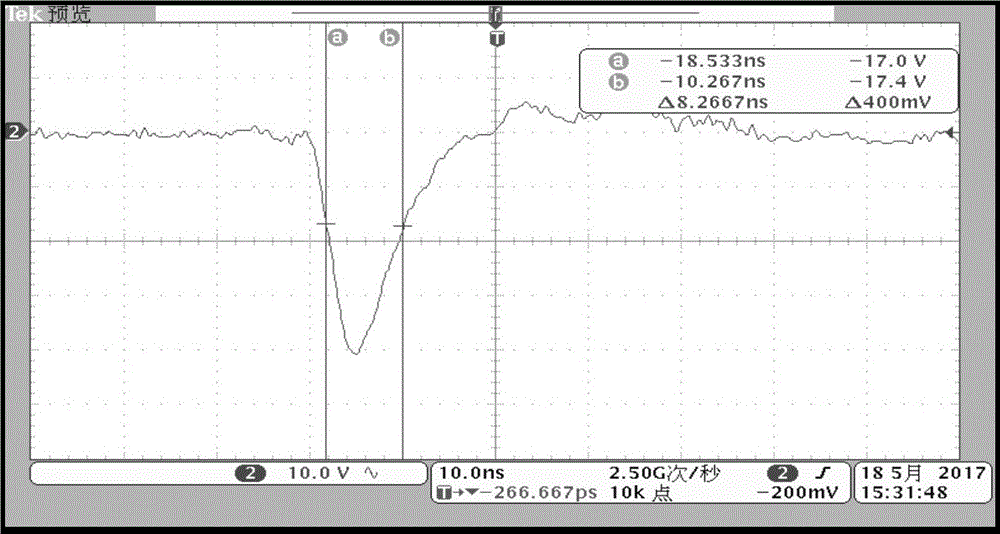

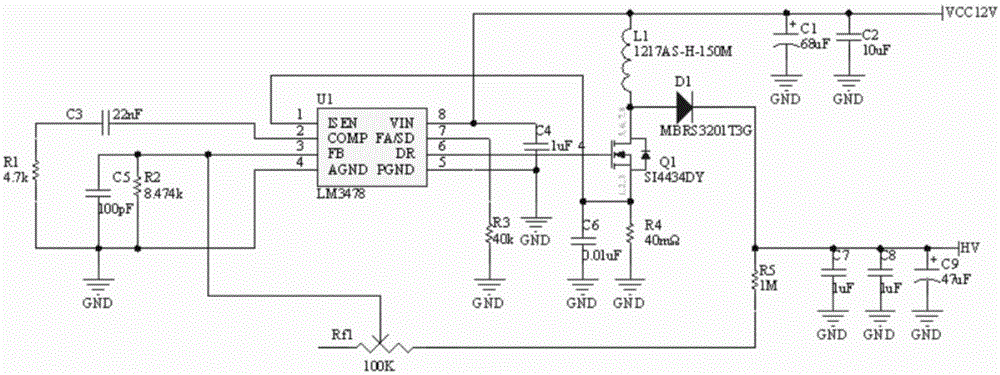

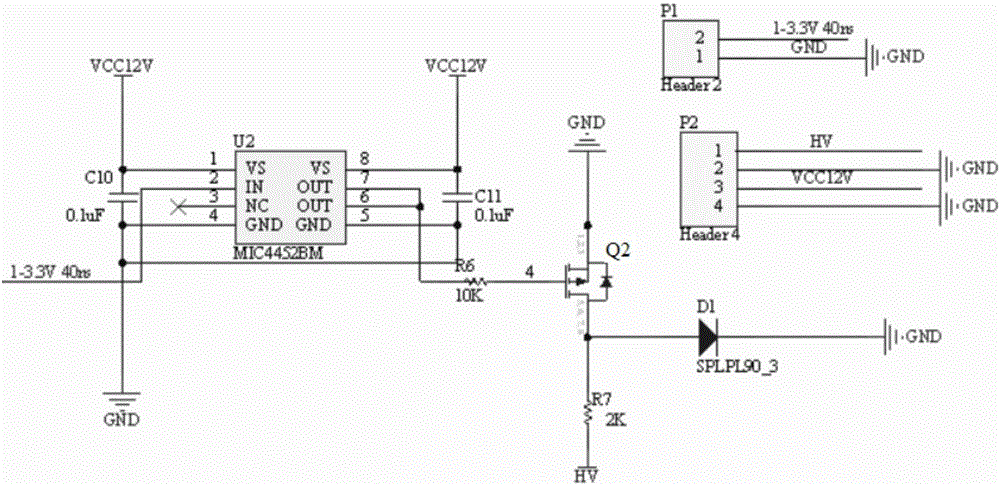

Pulse laser emission circuit

InactiveCN107436431AReduce parasitic parametersHigh precisionWave based measurement systemsApparatus without intermediate ac conversionCapacitanceStart time

The invention provides a pulse laser emission circuit. The pulse laser emission circuit comprises a high voltage generation circuit and a laser emission driving circuit, wherein a high voltage is provided for the driving circuit through the high voltage generation circuit, an laser is emitted by the driving circuit; on and off of an MOS tube are controlled by a booster controller through generating a switch signal, at the instant start moment of the MOS tube, an energy storage inductor is charged through a power source voltage, electric energy is stored in a capacitor through a loop formed by a first diode, after an MOS chip is disconnected, reverse cut-off of the diode is carried out, an output capacitor discharges to a load, and the 160V high voltage is generated; current amplification of the driving signal is carried out through a current amplification chip, the signal after amplification is inputted to a grid of the switch MOS chip, within the turn-off time of the switch MOS tube, a high voltage source provided by the high voltage generation circuit is utilized to charge the energy storage capacitor, the energy storage capacitor realizes instant discharge at the loop of the laser diode within the start time of the switch MOS tube, a heavy current is generated, and the high repetition frequency narrow pulse laser can be emitted.

Owner:NANJING UNIV OF SCI & TECH

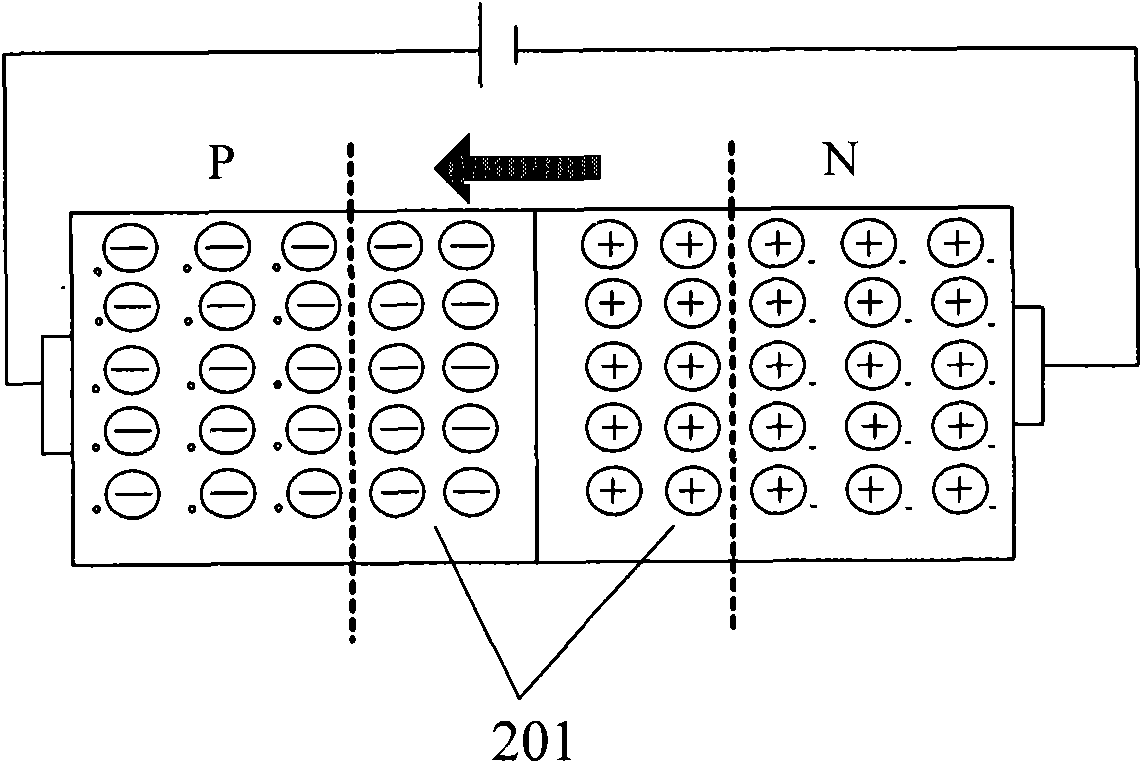

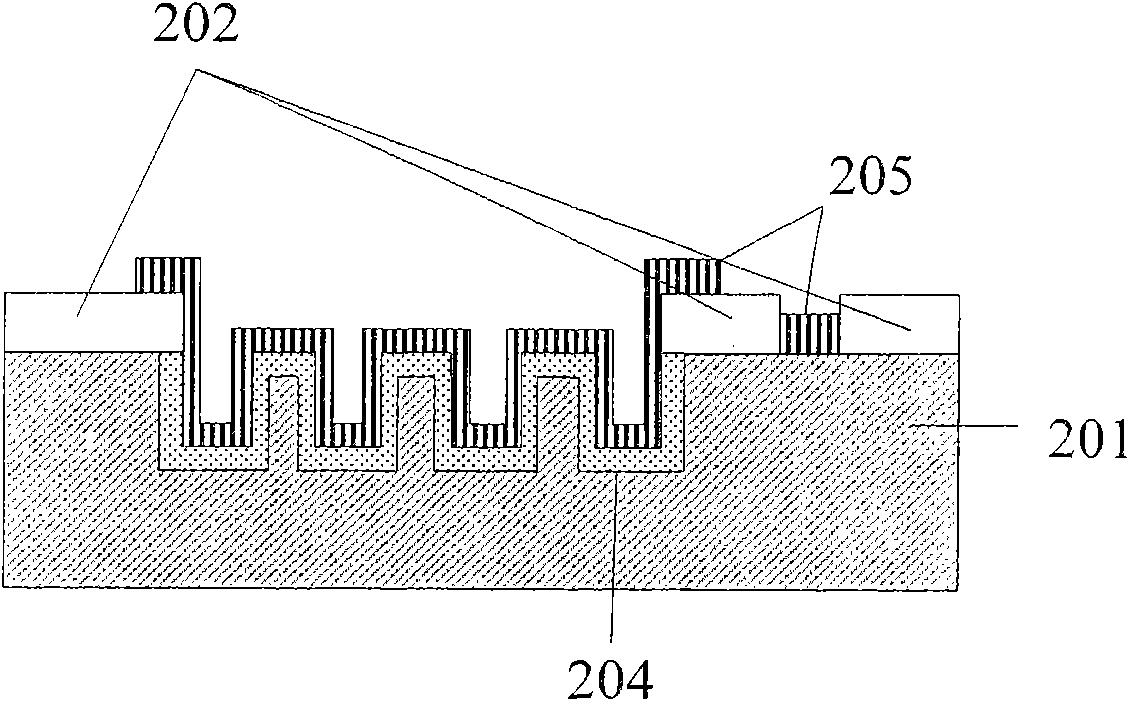

Capacitor composed by utilizing semiconductor PN junction capacitance and manufacturing method thereof

ActiveCN101814531ASimple structureIncrease capacitance densitySemiconductor/solid-state device manufacturingSemiconductor devicesDiffusion methodsCapacitance

The invention discloses a capacitor composed by utilizing a semiconductor PN junction capacitance and a manufacturing method thereof. The capacitor utilizes a semiconductor as a base material, and the capacitance of the capacitor is the semiconductor PN junction capacitance. The capacitor comprises a PN junction, a metal film layer, an electrode bump and an extraction electrode, wherein the PN junction is formed in a specific area by utilizing a diffusion method or an ion implantation method on a high-doping and low-resistance P type or N type semiconductor base material; the metal film layer is manufactured by utilizing a thermal evaporation method, an electron beam evaporation method or a sputtering method on the N type area or the P type area of the semiconductor forming the PN junction; the electrode bump is manufactured by an electroplating method or a screen printing method on the metal film; and the extraction electrode can be arranged on both faces of the semiconductor base material or only on a corrosion area face. The capacitor manufactured by the method of the invention has the characteristics of simple structure, large capacitance density, small parasitic parameters and simple manufacturing technical process, and also has protection function on static electricity and surging, thus being capable of being widely applied to electronic systems with high frequency, high speed and high power.

Owner:NAT CENT FOR ADVANCED PACKAGING

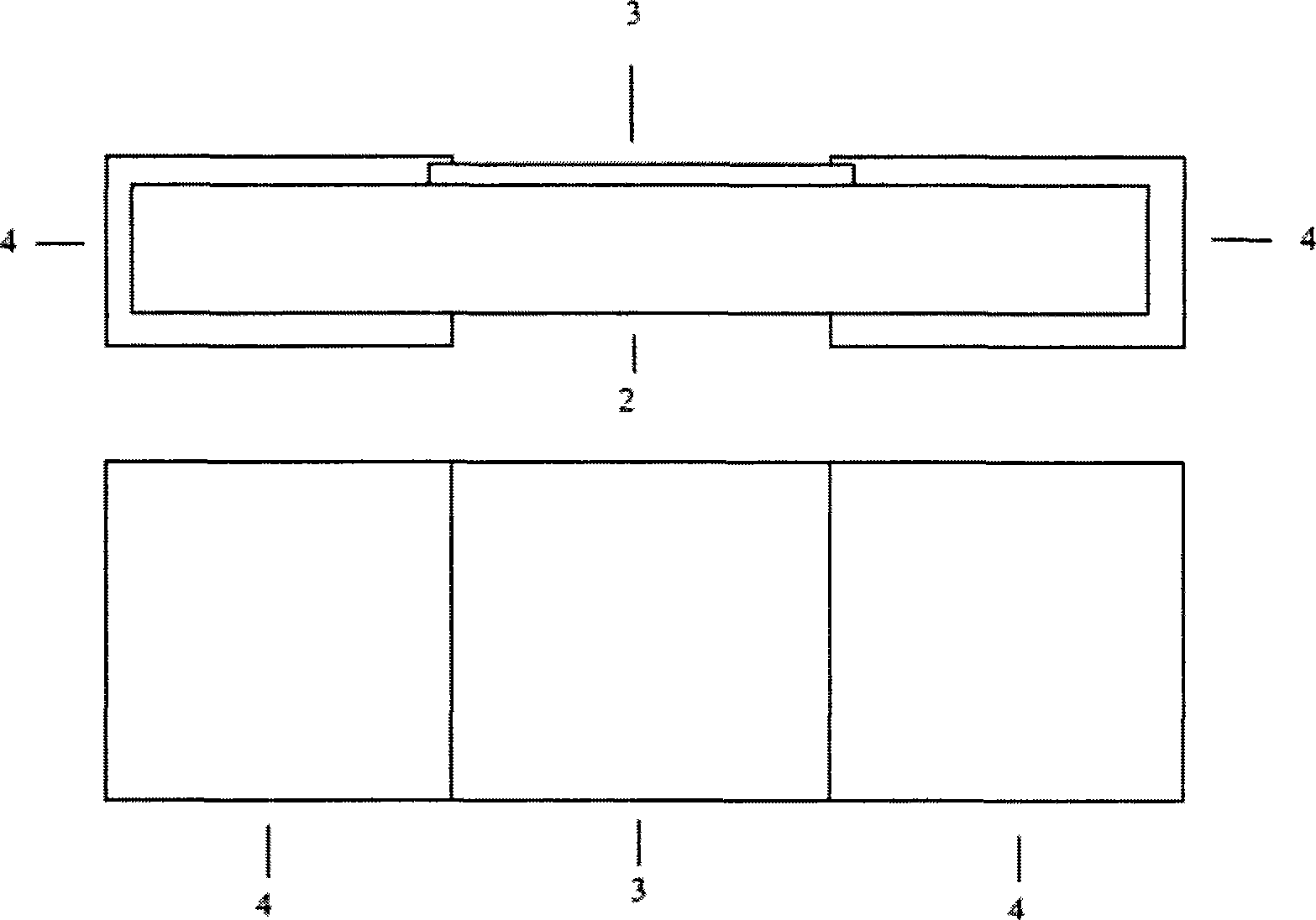

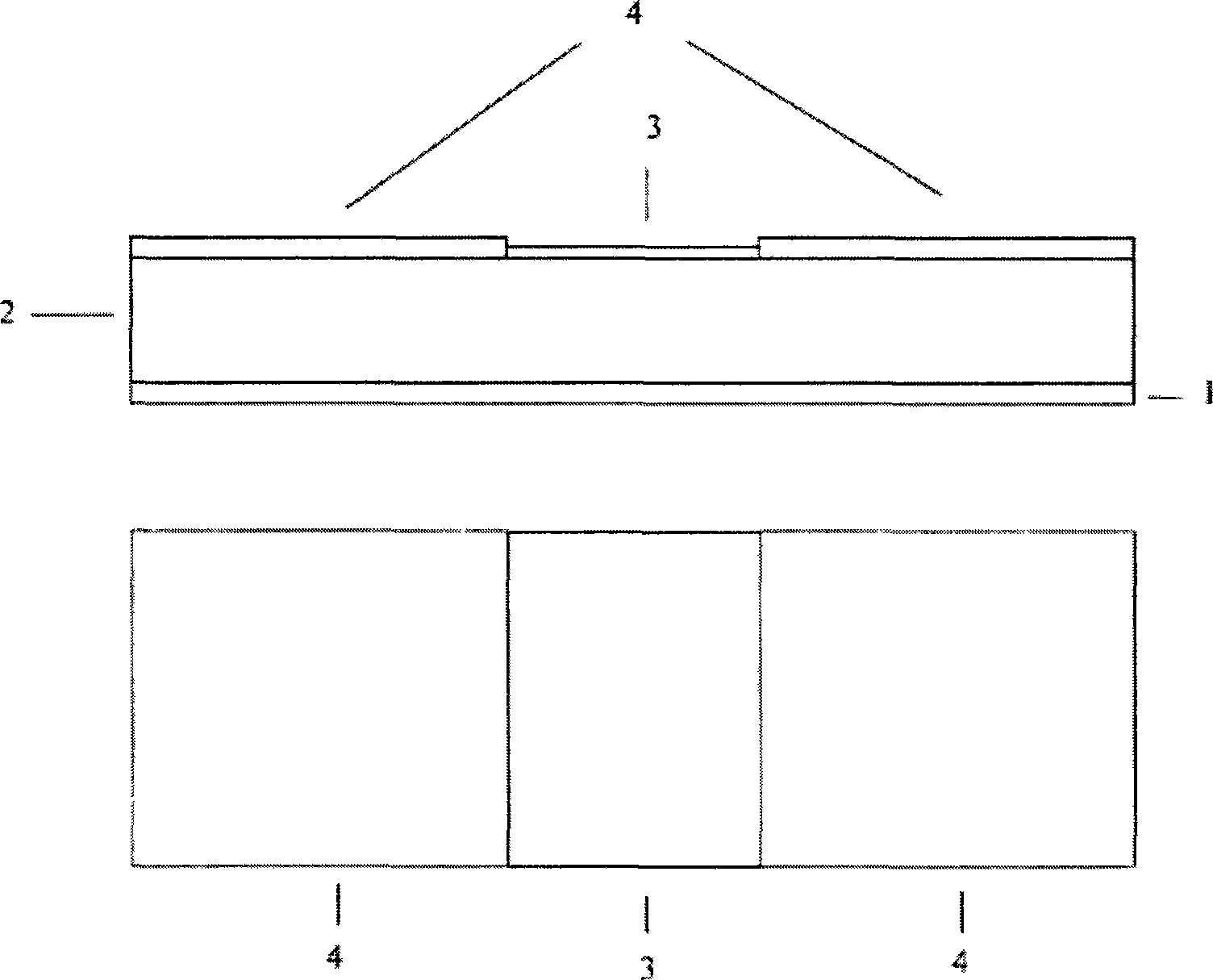

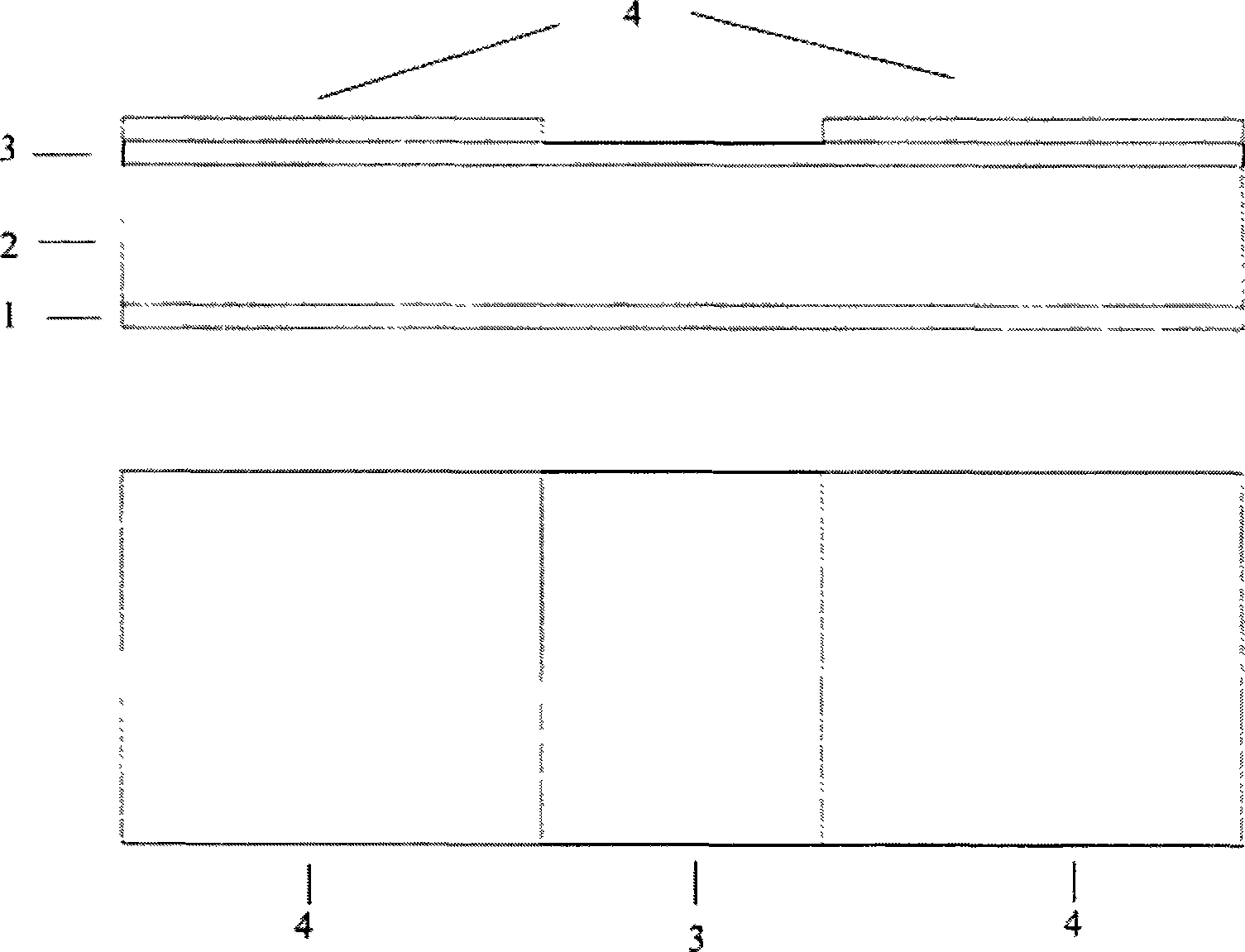

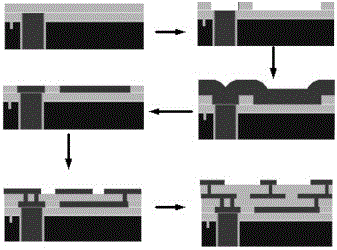

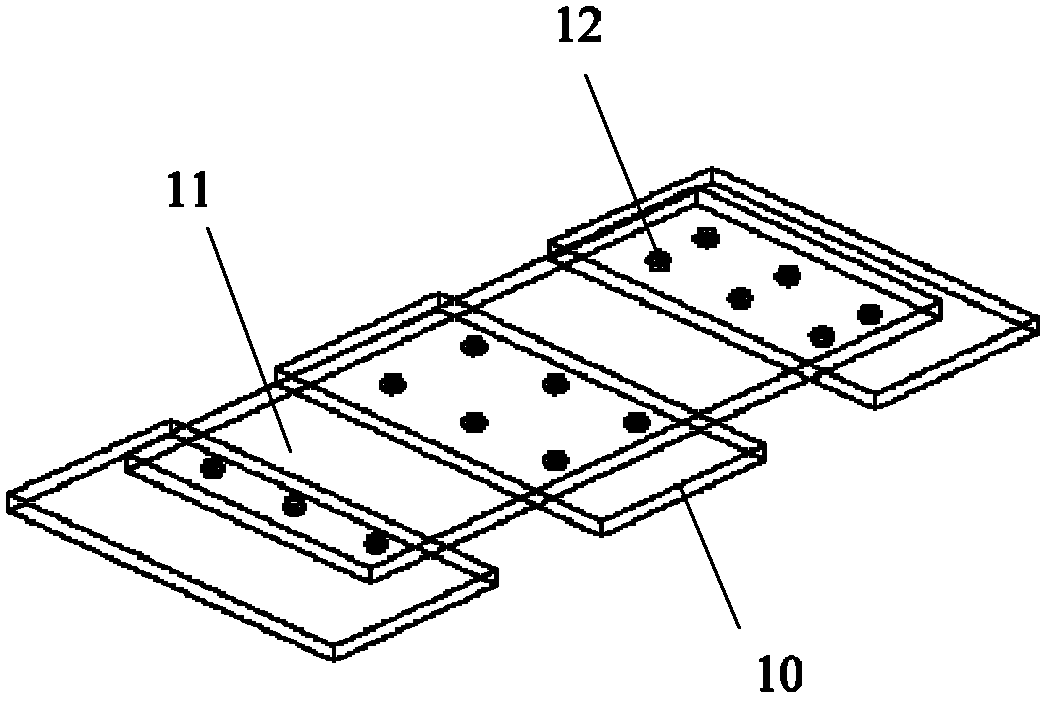

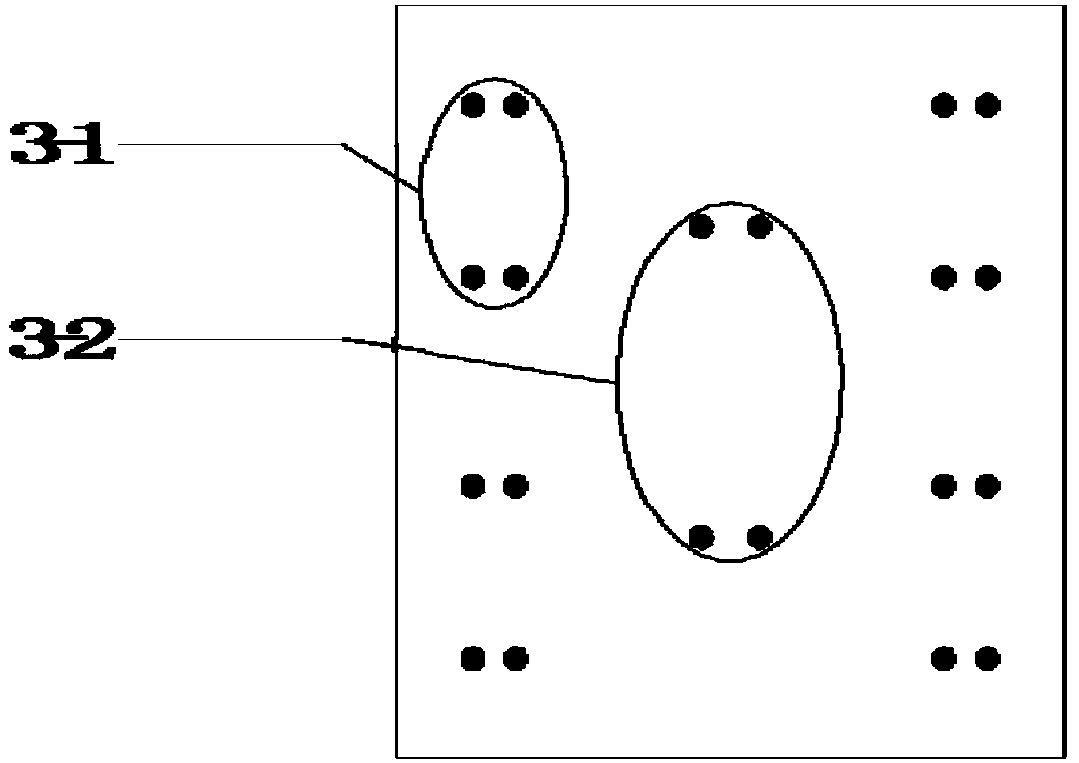

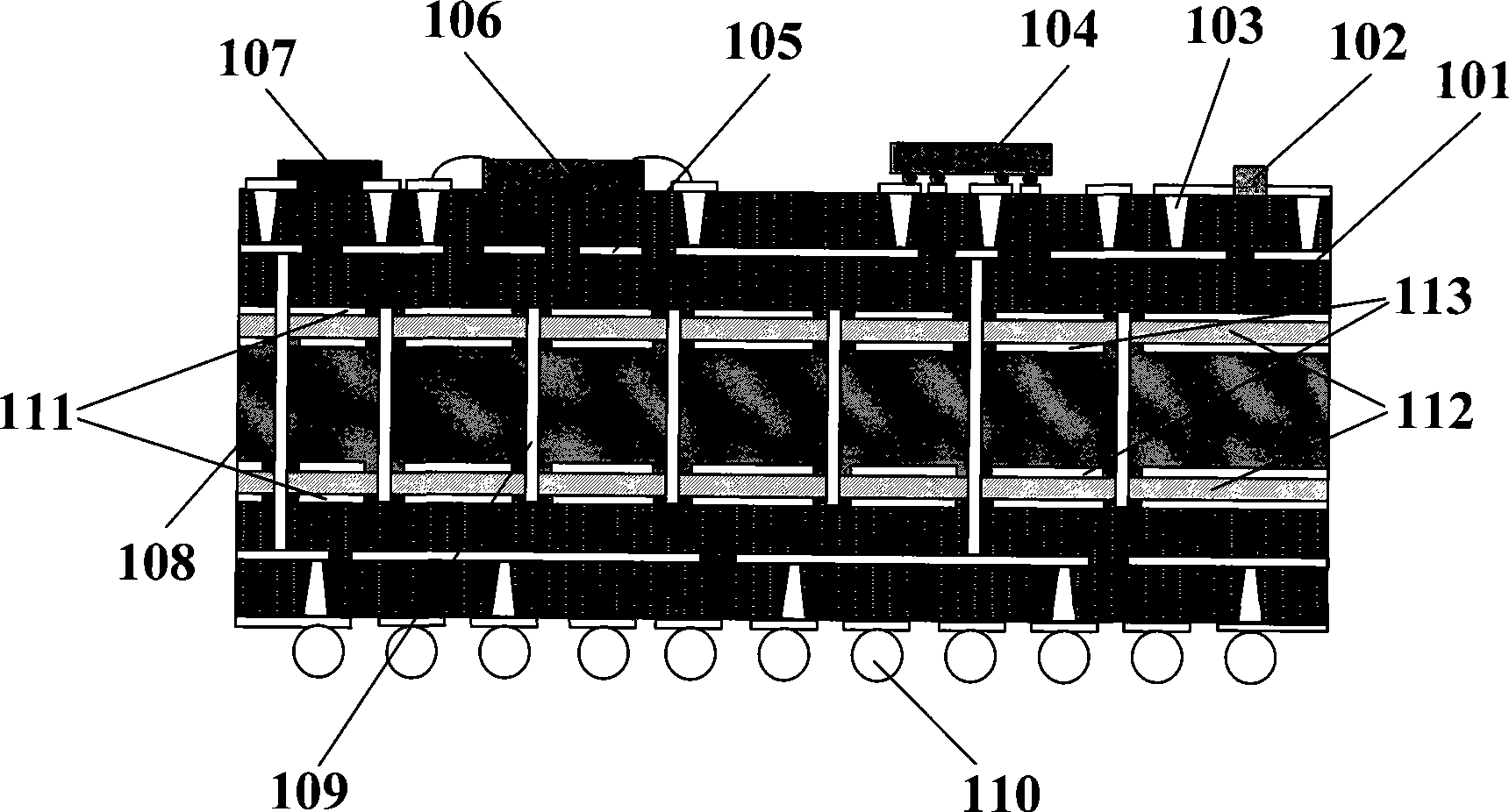

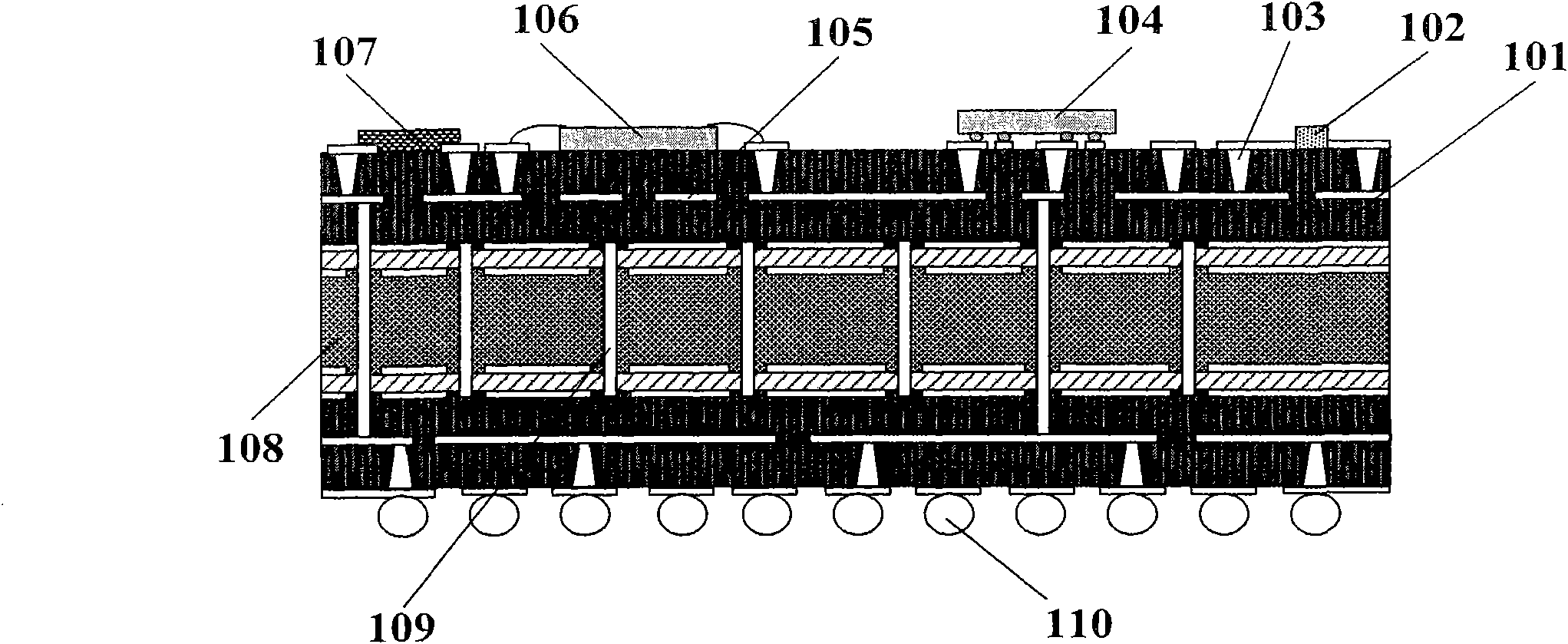

Self-alignment integrated package method of high-density three-dimensional lamination layer

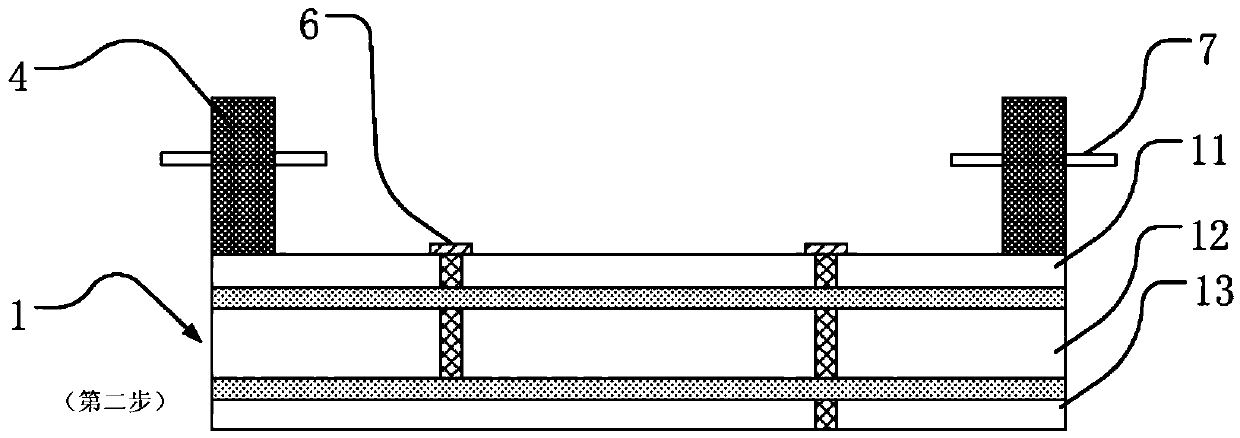

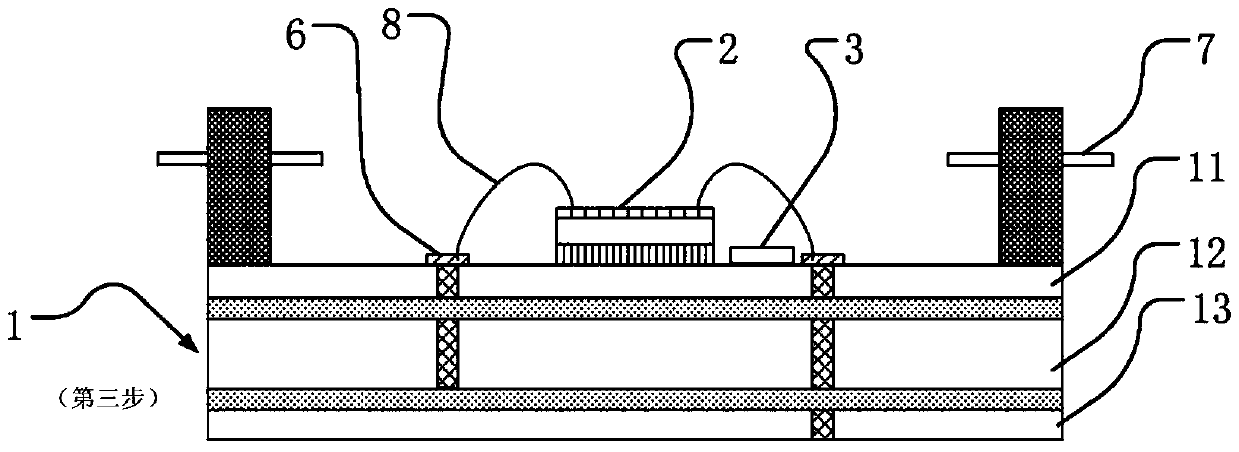

PendingCN110211884AReduced Alignment DifficultyReduce failure rateSemiconductor/solid-state device detailsSolid-state devicesHigh densityInter layer

The invention discloses a self-alignment integrated package method of a high-density three-dimensional lamination layer, and aims to provides an integrated package method which employs a BGA welding ball as an interlayer mechanical support for multi-layer substrate self-alignment three-dimensional stack and also can be a signal interconnection passage among high-density layers. The self-alignmentintegrated package method is implemented according to the technical scheme that bonding pads are arranged on a lower surface of a top-layer substrate, an upper surface and a lower surface of an intermediate-layer substrate and an upper surface of a bottom-layer substrate and are used for welding micro BGA welding balls, the micro BGA welding balls are attached onto the upper surface of the intermediate-layer substrate and the upper surface of the bottom-layer substrate, the micro BGA welding balls on the upper surface of the intermediate-layer substrate are corresponding to the lower surface of the top-layer substrate, the micro BGA welding balls on the upper surface of the bottom-layer substrate are corresponding to the lower surface of the intermediate-layer substrate, vertical and interconnection rectangular array micro BGA ball welding is formed, a hollow square boss cavity box body is arranged at the peripheries outside an upper cavity surface of the intermediate-layer substrate 2and an upper cavity surface of the bottom-layer substrate 3, the cavity box body is stacked and placed in a backflow welding furnace by a tool, and self-alignment lamination layer welding is performed to form a package body.

Owner:10TH RES INST OF CETC

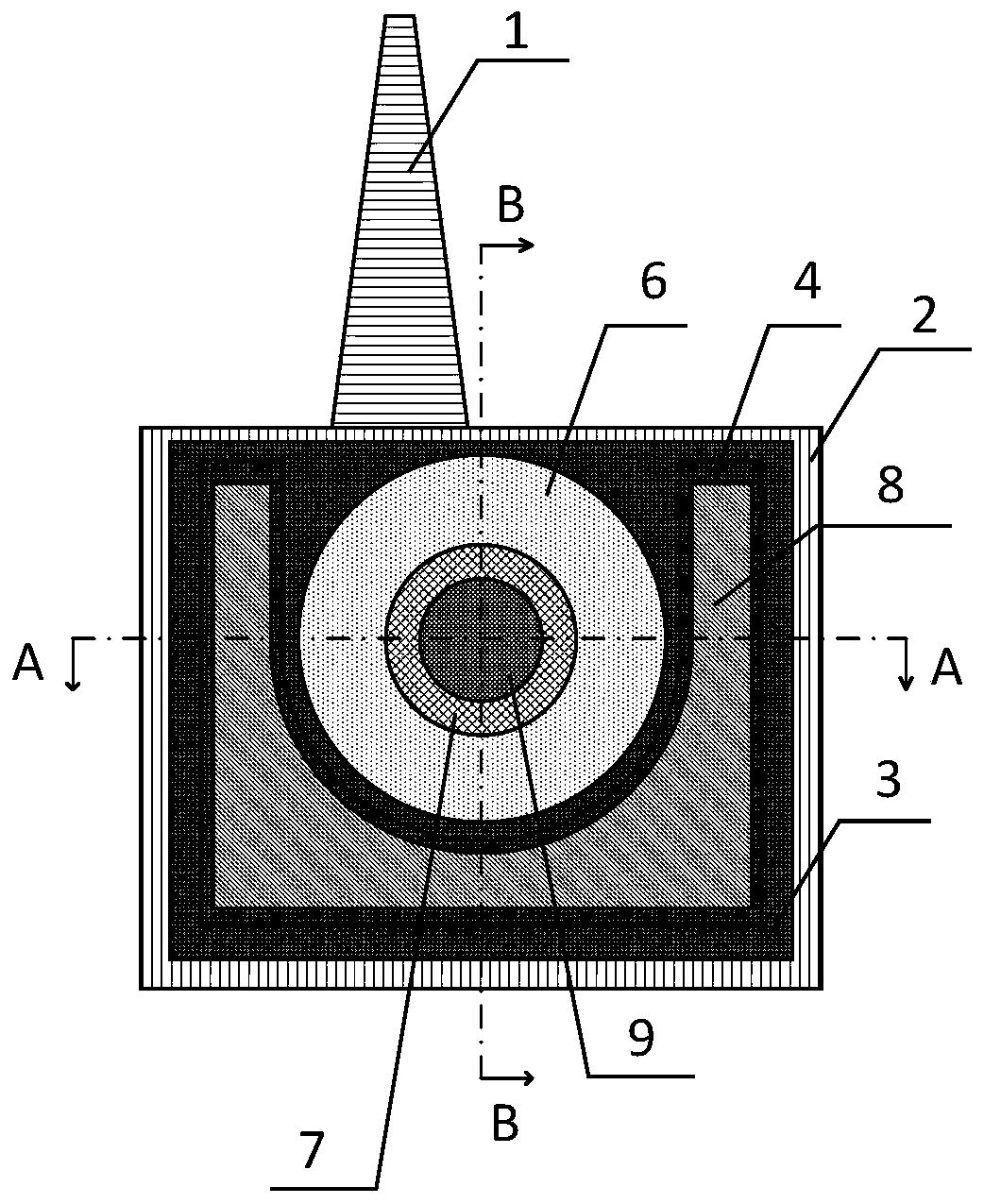

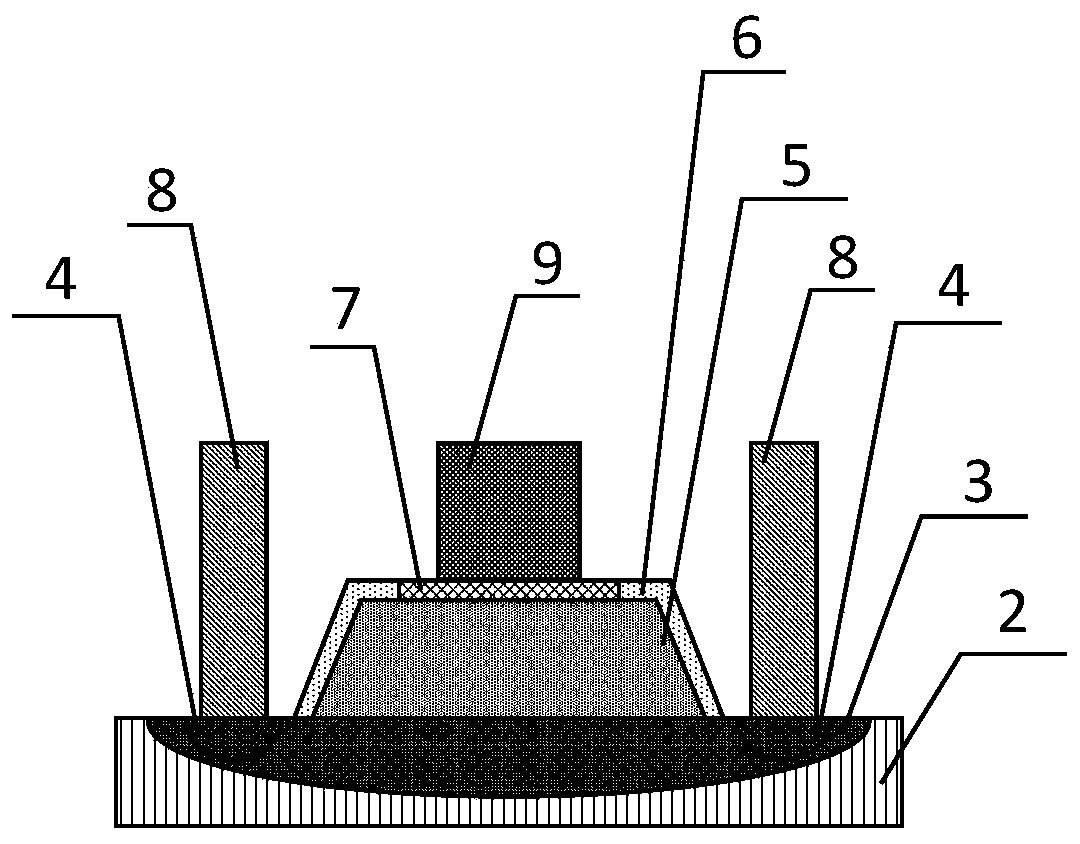

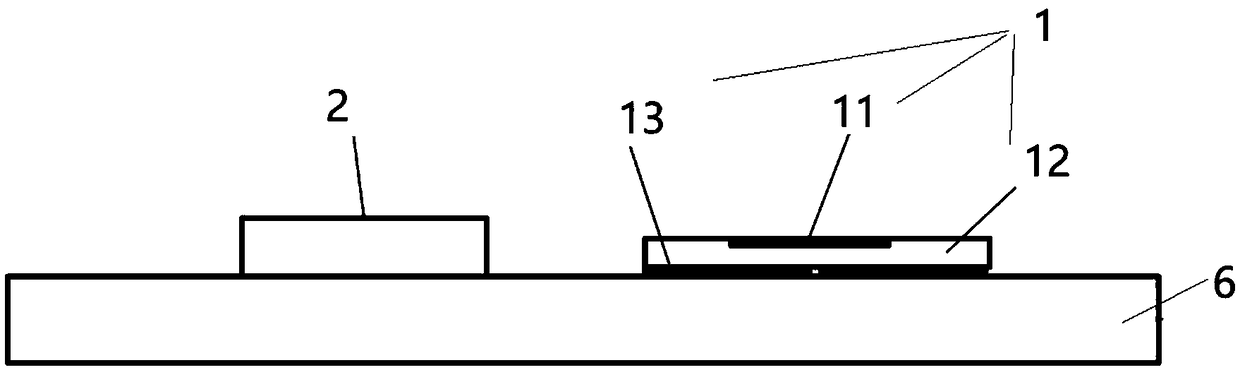

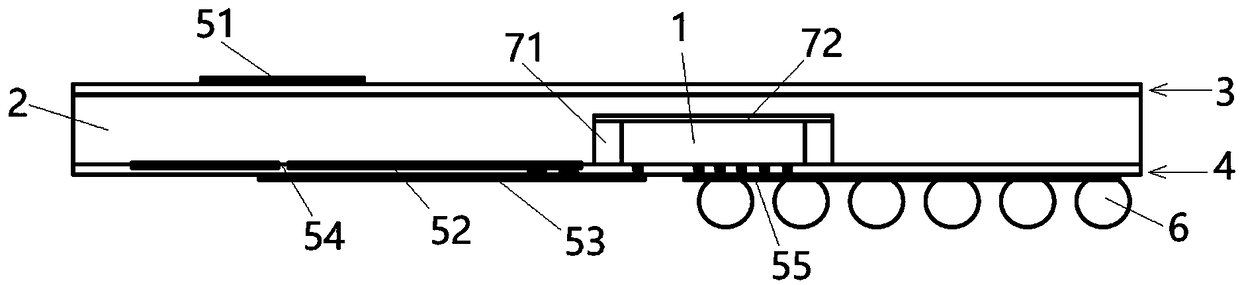

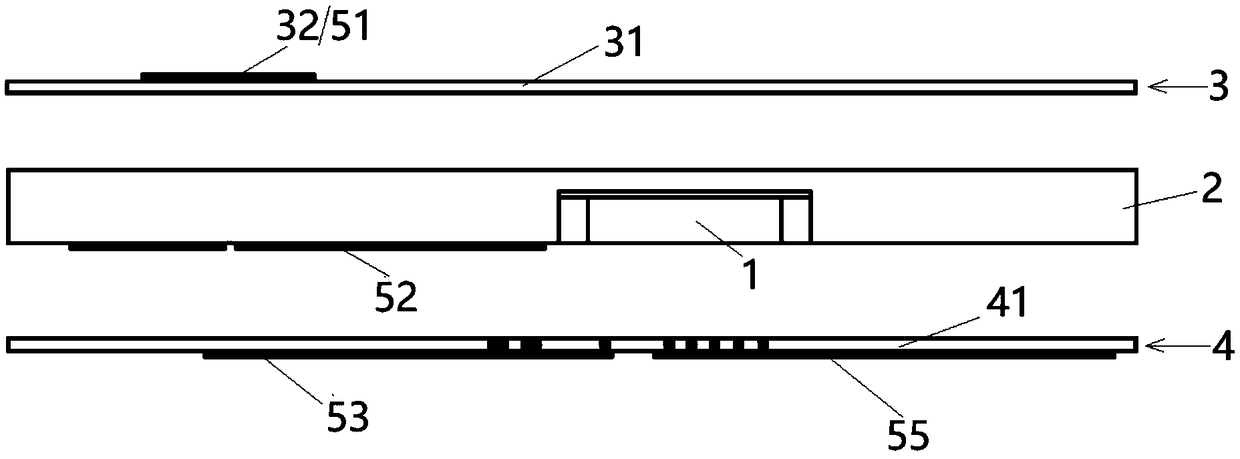

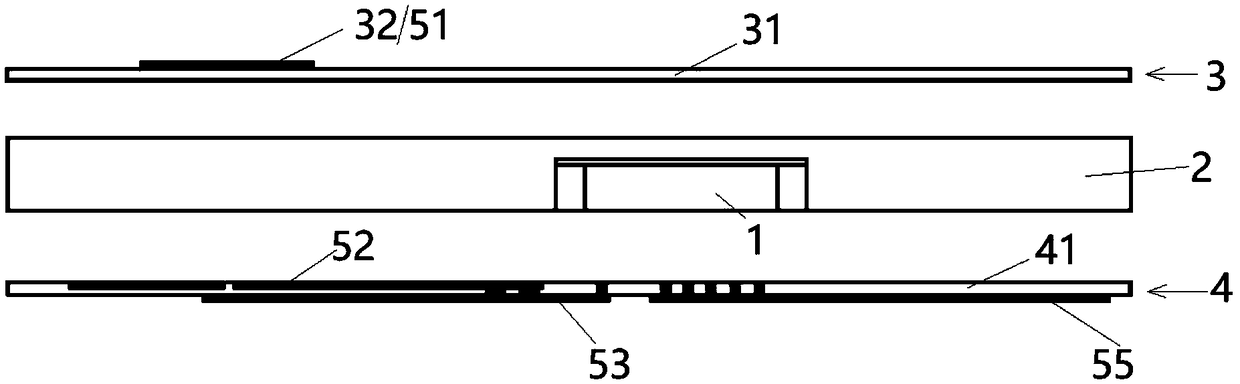

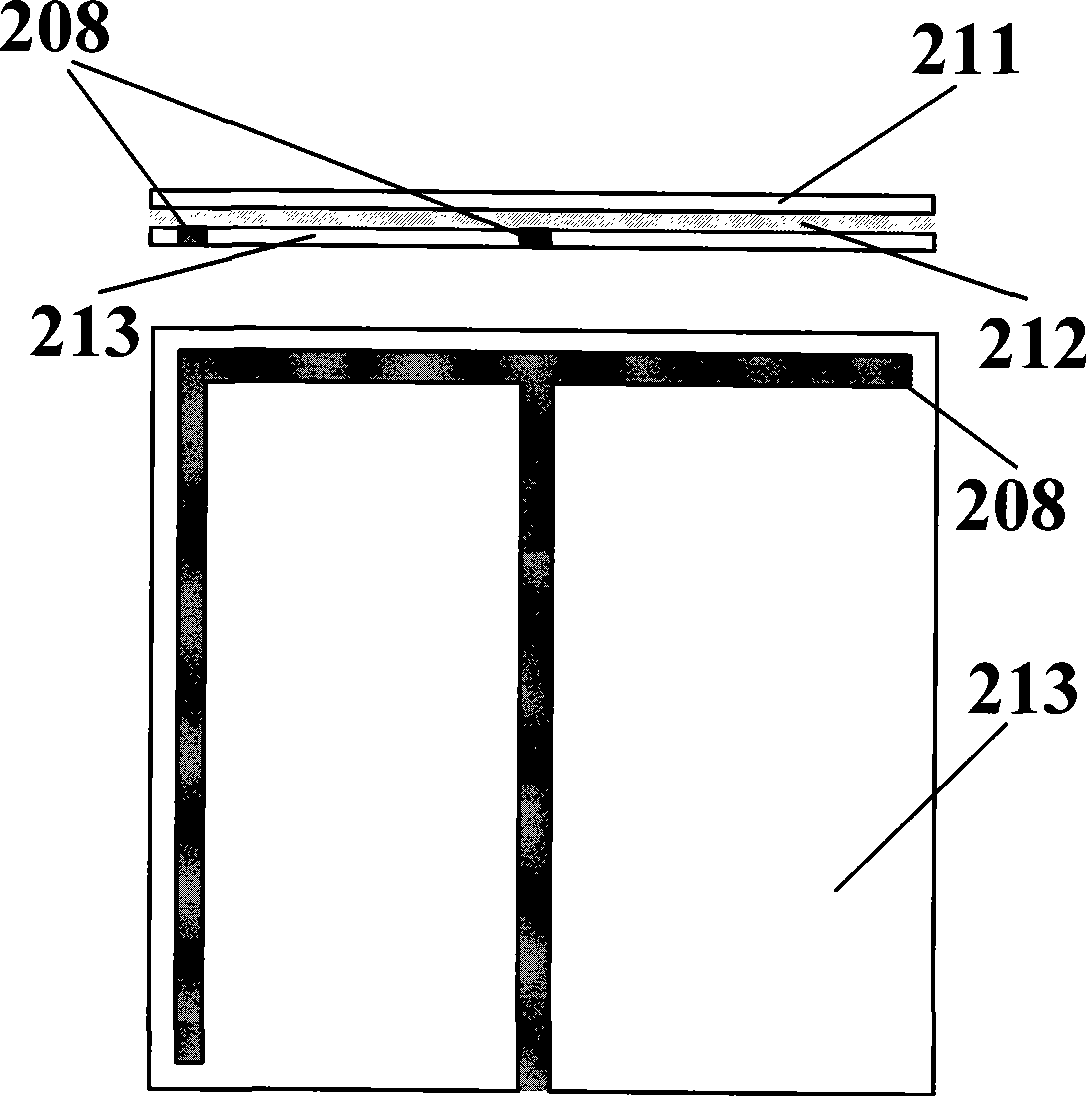

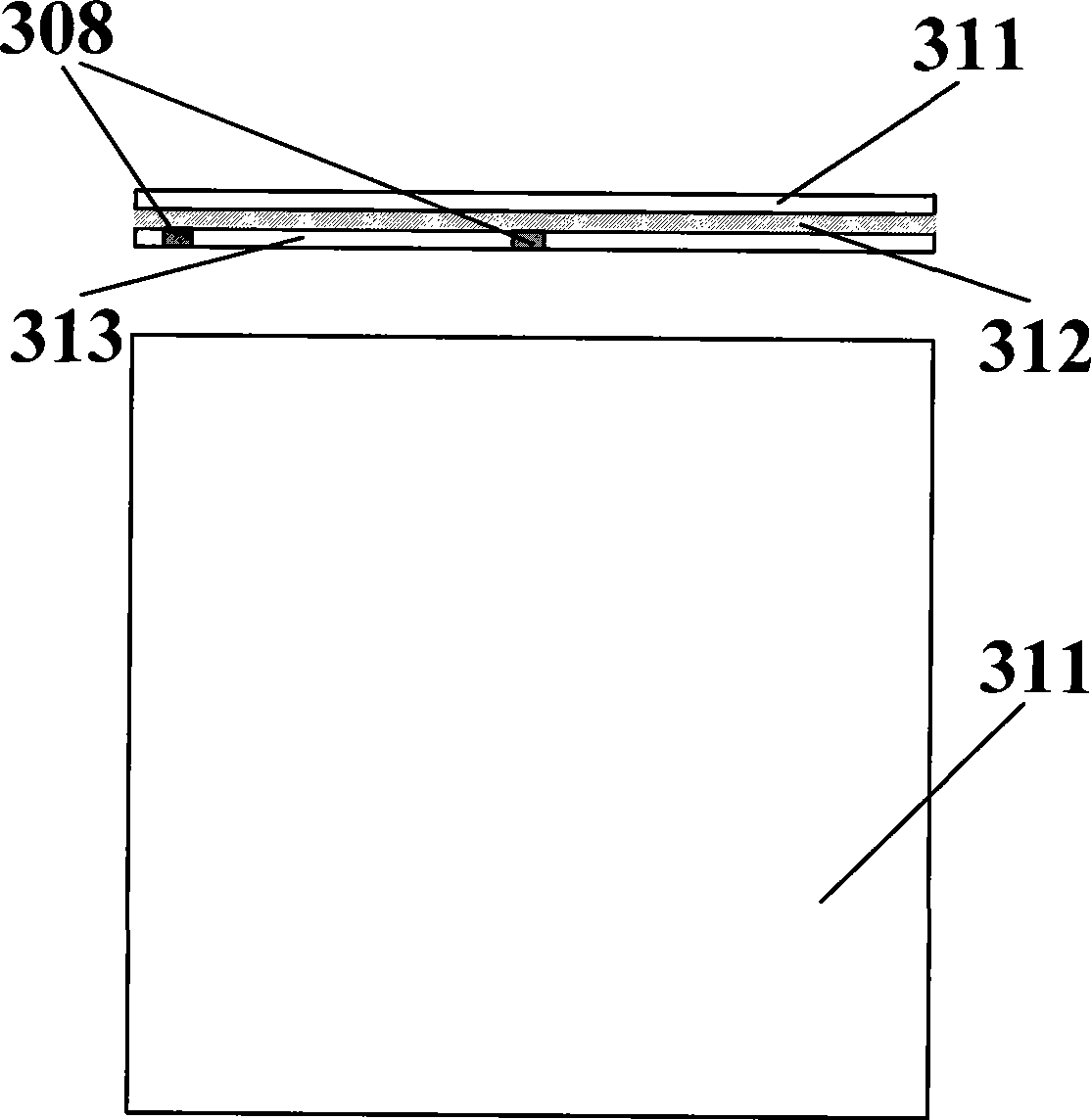

Encapsulated antenna and manufacturing method thereof

ActiveCN109244642AReduce parasitic parametersTo reduce the parasitic parameters, theSemiconductor/solid-state device detailsAntenna supports/mountingsSolder ballGround plane

A method for manufacturing an encapsulated antenna is provided. The encapsulated antenna includes an antenna structure including an antenna radiation patch, an antenna substrate dielectric layer and areflective ground plane arranged in sequence. The antenna substrate dielectric layer has a first surface and a second surface opposite to each other. The antenna radiation patch is fixed on the firstsurface and the reflective ground plane is fixed on the second surface. Chip; A package having opposite first and second faces, the front face and reflective ground plane of the chip being exposed toand flush with the second face; A rewiring layer comprising an RDL dielectric layer and an RDL metal layer, the RDL metal layer comprising a feeder, a plurality of fan-out leads and a plurality of pads, at least a portion of the pads being connected to the chip through vias in the RDL dielectric layer; And a solder ball implanted on the pad. The encapsulated antenna can reduce its own parasitic parameters while improving antenna radiation patch performance.

Owner:TSINGHUA UNIV

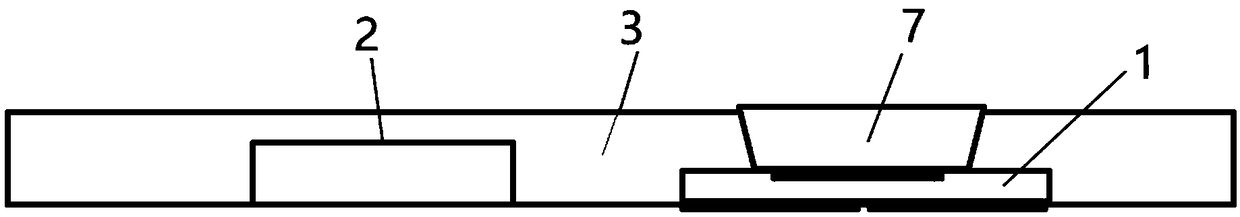

Encapsulated antenna and manufacture method thereof

ActiveCN109166845AReduce parasitic parametersAchieve high integrationSemiconductor/solid-state device detailsAntenna supports/mountingsGround planeSolder ball

The invention relates to a packaged antenna and a manufacturing method thereof. The packaged antenna comprises a circuit chip; A substrate provided with a substrate groove, the circuit chip is fixed in the substrate groove, the front surface of the circuit chip is exposed to the first surface and is flush with the first surface, the substrate is provided with a substrate metal layer, and the substrate metal layer is formed with an antenna; Rewiring layer, laminated on the first surface of the substrate and the front surface of the circuit chip, the rewiring layer includes at least one RDL metal layer, The metal layer is formed with a reflective ground plane, a feeder line, a plurality of fan-out leads and a plurality of pads, the feeder line being connected to the circuit chip to feed theantenna, the plurality of fan-out leads connecting corresponding vias to the circuit chip for connecting the circuit chip and the printed circuit board, the plurality of pads being located on a layerof RDL metal layer furthest from the second surface; And solder balls. With the above technical solution, the encapsulated antenna provided by the present disclosure can reduce its own parasitic parameters while improving antenna performance.

Owner:TSINGHUA UNIV

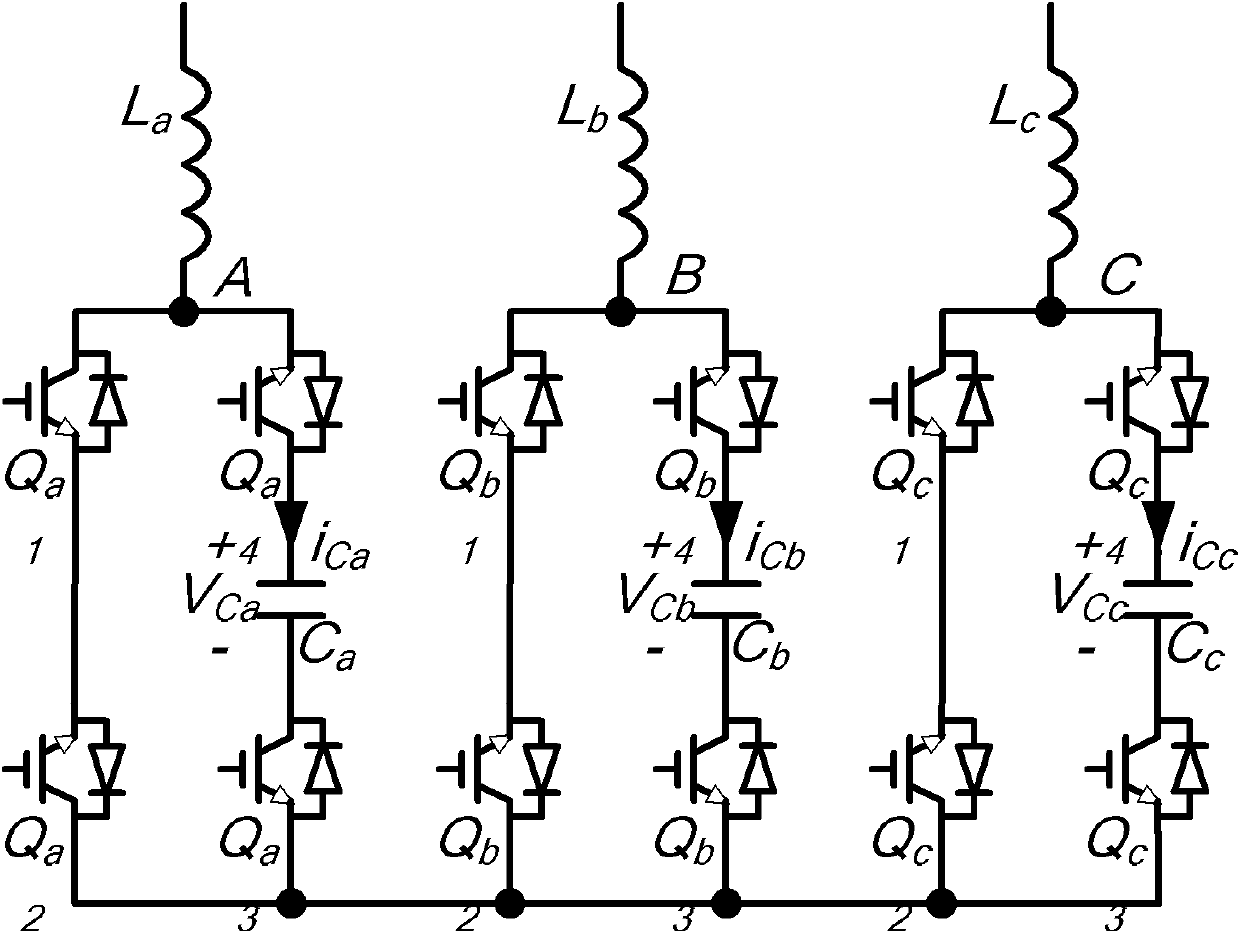

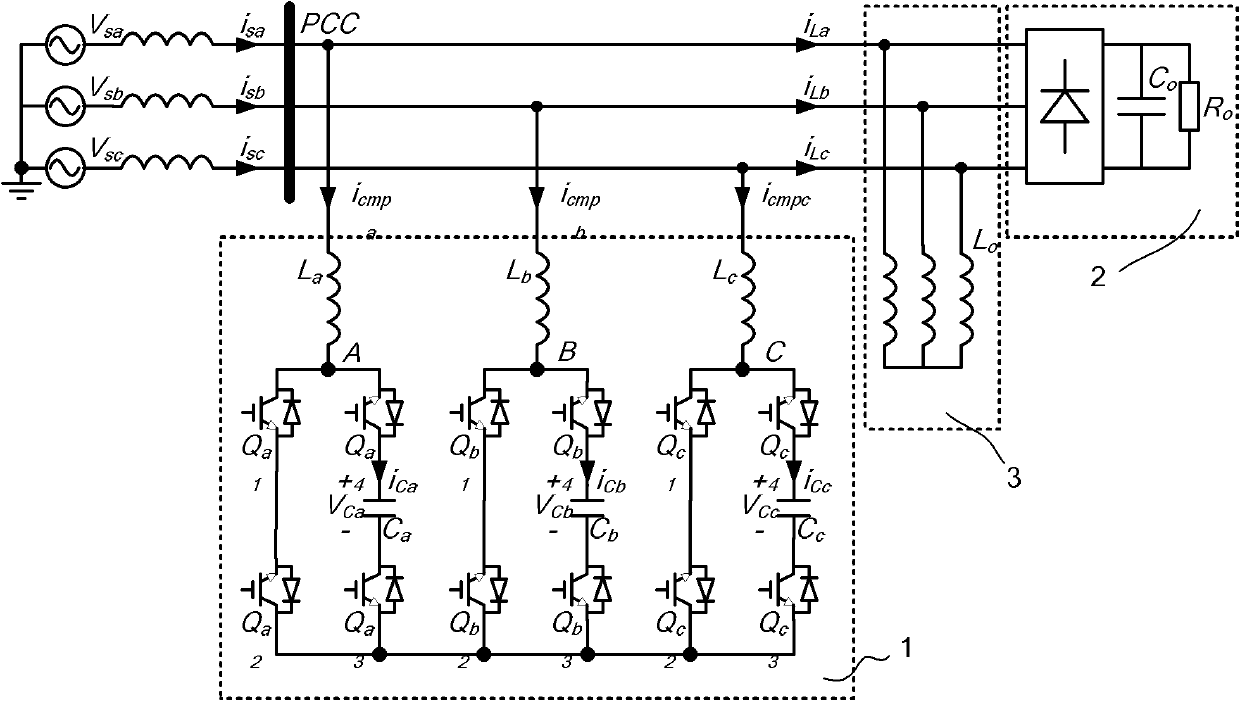

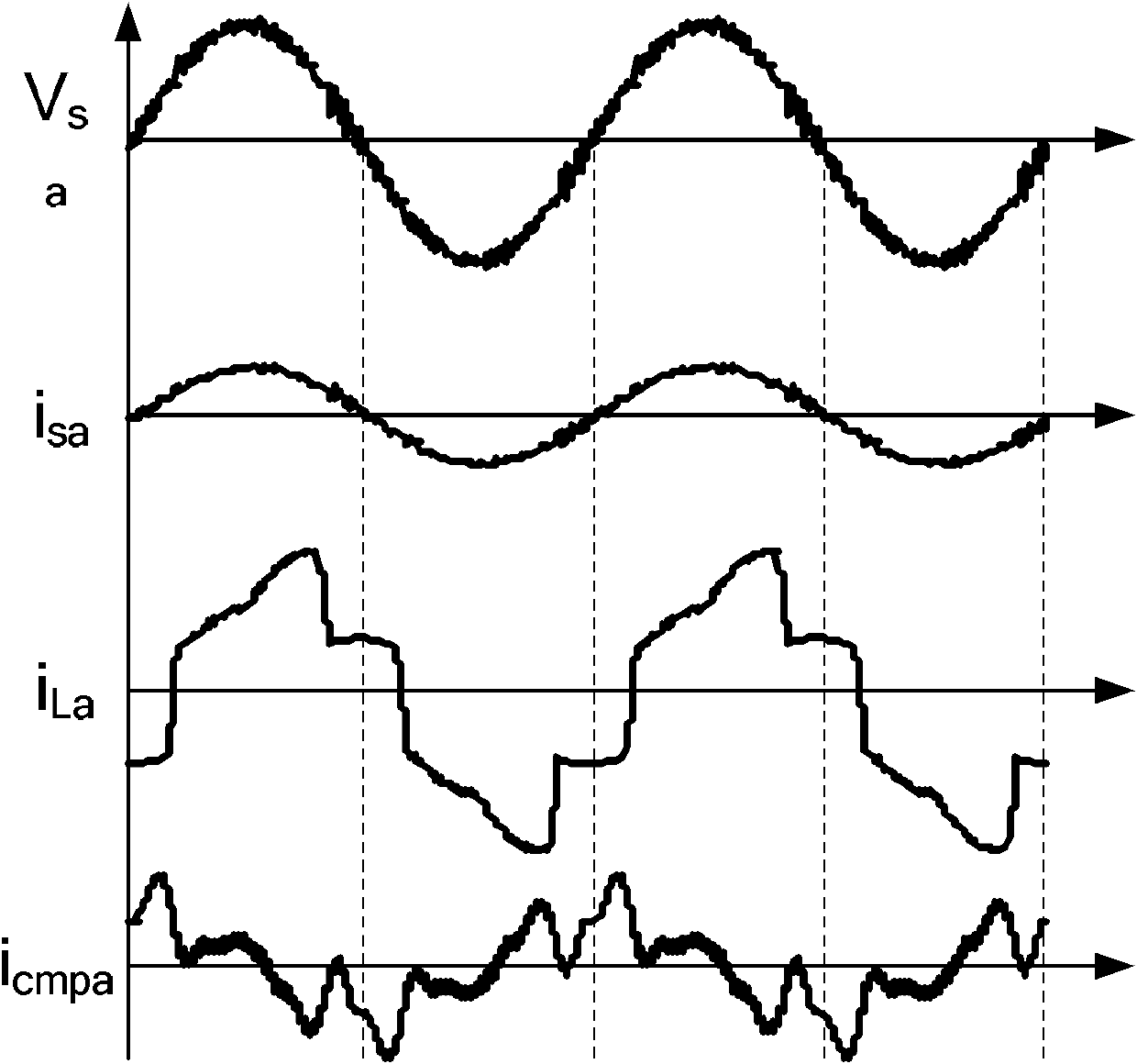

Active power filter based on boost direct current-direct current (DC-DC) conversion circuit

ActiveCN102185320AReduce volumeCompact structureActive power filteringReactive power adjustment/elimination/compensationEngineeringPhase compensation

The invention discloses an active power filter based on a boost direct current-direct current (DC-DC) conversion circuit. The active power filter comprises an A-phase compensation circuit, a B-phase compensation circuit and a C-phase compensation circuit, wherein the A-phase, B-phase and C-phase compensation circuits are connected in a Y shape. The filter uses a direct DC-DC conversion mode and can compensate for the reactive current and harmonic current of a grid by implementing a pulse width modulation on an alternative current switch and injecting even modulation harmonics to duty ratio. The phase compensation circuits of the invention are combined and sealed by using an alternative current load capacitor, a filter inductance connected grid and a power switch tube with an anti-paralleldiode and without a large-capacity energy storage device, so that the volume of the device is greatly reduced; the structure is simpler and more compact; the grid side current ripple is small; the parasitic parameter is small; and the maintaining and use cost of the device is greatly reduced; and considerable economic benefit is created.

Owner:ZHEJIANG UNIV

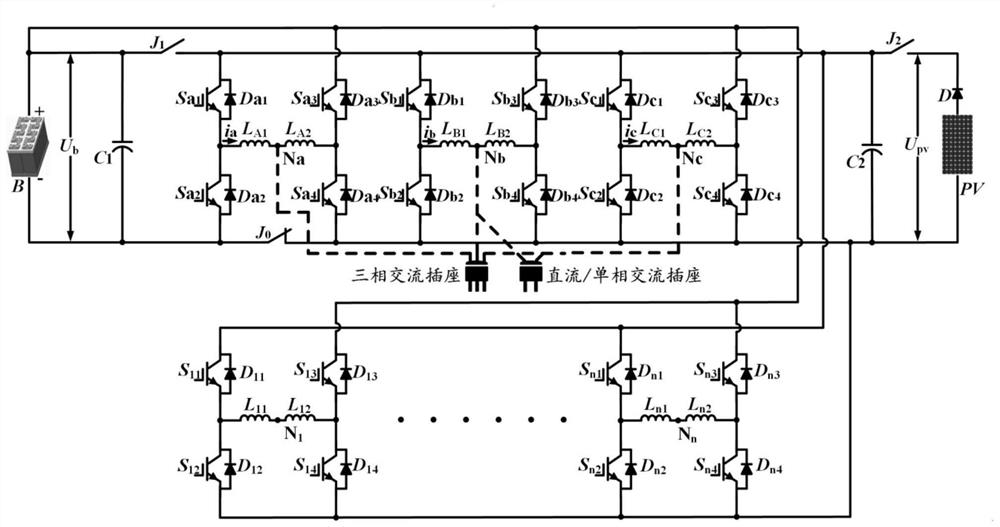

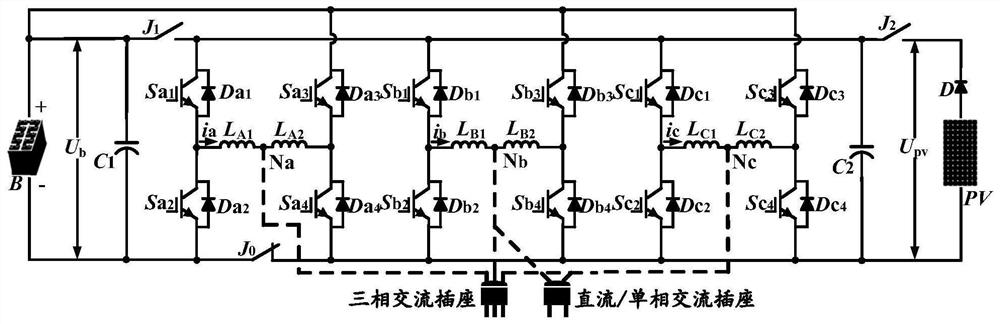

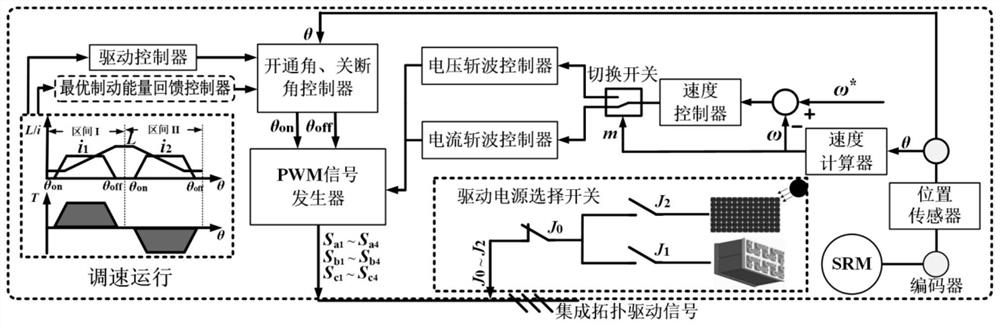

Driving reconstruction type circuit based on SRM and vehicle-mounted integrated charging and feeding system

ActiveCN113364388AReduce parasitic parametersReduce power consumptionAC motor controlAc-dc conversionHemt circuitsSingle-phase electric power

The invention discloses an SRM-based driving reconstruction type circuit and a vehicle-mounted integrated charging and feeding system. According to the circuit, three solid-state relays and a plurality of single-phase voltage type bridge inverters obtained through a DC bus reconstruction mode form an integrated power converter, and the integrated power converter is connected to a power battery and a vehicle-mounted solar photovoltaic panel; the vehicle-mounted integrated charging and feeding system adopting the driving reconstruction type circuit can be suitable for a multi-phase switched reluctance motor, and is combined with a proper control strategy; therefore, various operation modes such as a power battery driving mode, a vehicle-mounted solar photovoltaic panel driving mode, a hybrid driving mode, a regenerative braking mode, a single-phase and three-phase static charging and feeding mode and the like can be realized. The circuit is compact in structure, small in parasitic parameter, low in power consumption and high in power density, switching among different operation modes can be achieved by simply controlling the conducting state of the solid-state relay, and therefore, bidirectional flow of energy among a power battery, a power grid and a motor is achieved.

Owner:HEBEI UNIV OF TECH

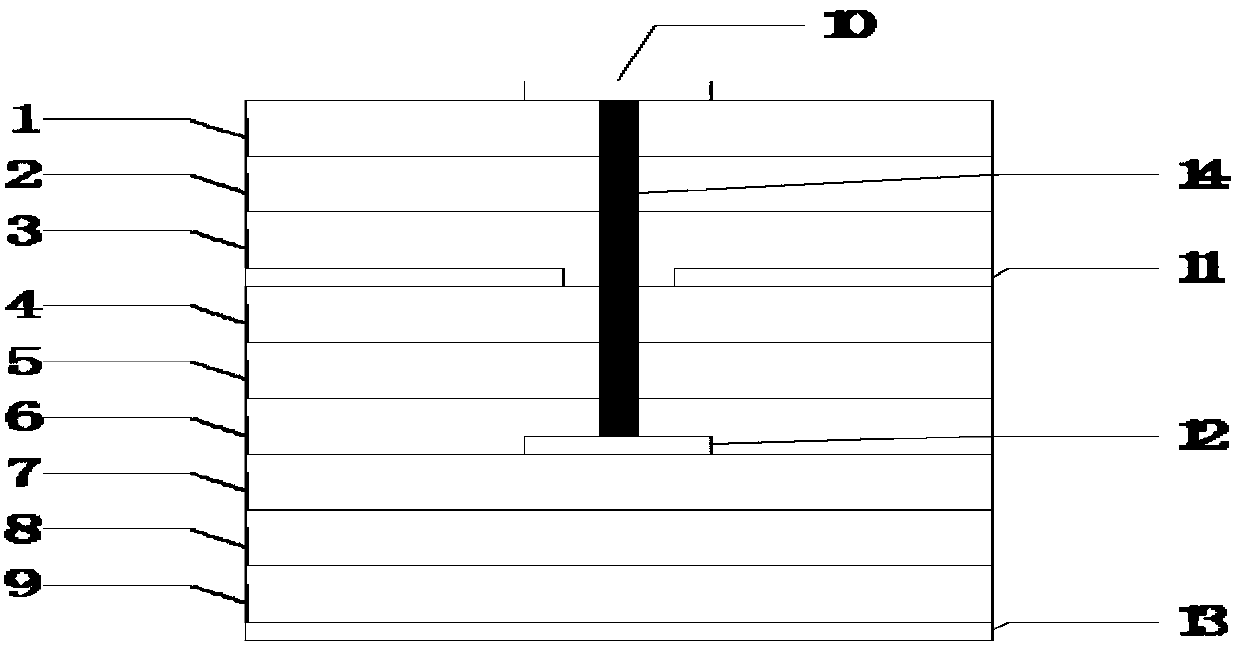

LTCC (Low Temperature Co-Fired Ceramic) miniaturization microwave passive device

The invention discloses an LTCC (Low Temperature Co-Fired Ceramic) miniaturization microwave passive device. The LTCC miniaturization microwave passive device comprises dielectric layers and metal layers which are arranged between the dielectric layers; the dielectric layers comprise a first micro-strip dielectric layer, a second micro-strip dielectric layer, a third micro-strip dielectric layer, a first strip line dielectric layer, a second strip line dielectric layer, a third strip line dielectric layer, a fourth strip line dielectric layer, a fifth strip line dielectric layer and a sixth strip line dielectric layer which are arranged from top to bottom in turn; the metal layers comprise a micro-strip line, a first grounding plane, a strip line and a second grounding plane; the micro-strip line is arranged on the first micro-strip dielectric layer; the first grounding plane is arranged between the third micro-strip dielectric layer and the first strip line dielectric layer; the strip line is arranged between the third strip line dielectric layer and the fourth strip line dielectric layer; the second grounding plane is arranged below the sixth strip line dielectric layer. According to the LTCC miniaturization microwave passive device, the multilayer wiring scheme is adopted and accordingly the circuit size and weight is reduced under the same working frequency, the problem of transmission line overlapping is effectively solved, parasitic parameters are reduced, the structure is simple, and the performance is good.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

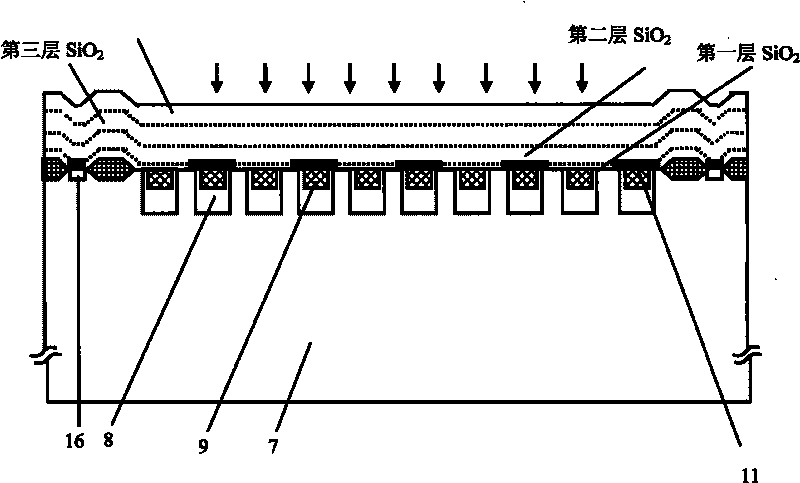

Optical receiving assembly for hundred trillion-grade 850nm optical communication and preparation method thereof

InactiveCN101718897ALower packaging costsImprove device performanceSemiconductor/solid-state device detailsSolid-state devicesOpto electronicDifferential amplifier

The invention relates to an optical receiving assembly for hundred trillion-grade 850nm optical communication and a preparation method thereof, and provides an optical receiving assembly for hundred trillion-grade 850nm optical communication, which is compatible with a commercial CMOS process and can replace the hybrid integration in the traditional 850nm optical transceiver and meet the transmission requirement, and a preparation method thereof. The optical receiving assembly is provided with a 850nm optoelectronic single integrated receiving chip, a pipe seat, a pipe cap, a pipe pin and an adapter, wherein the chip is provided with a prepositive amplifying circuit and an optoelectronic detector, and the prepositive amplifying circuit is provided with two mutual resistance type amplifying circuits, a three-grade differential amplifier, an output buffer circuit and a direct current negative feedback circuit. The optoelectronic detector is provided with a low doped P-shaped silicon substrate, a P pit, an N-shaped heavy doping silicon layer, a field oxide layer, an aluminum layer, three SiO2 insulating medium layers and a Si3N4 surface passivating layer from bottom to top in the longitudinal direction. The chip is attached to the pipe seat by a CMOS process; a welding disk of the chip is bonded with the pipe pin by a gold thread; and the pipe cap is covered to be encapsulated with the adapter according to the same shaft.

Owner:XIAMEN UNIV

Packaging antenna and manufacturing method thereof

ActiveCN109326584AMiniaturizationReduce parasitic parametersAntenna supports/mountingsSemiconductor/solid-state device detailsEngineeringGround plane

The invention relates to packaging antenna and a manufacturing method thereof. The packaging antenna comprises a chip, a substrate, a first rewiring layer and a second rewiring layer, wherein the chipis fixed in the substrate; one surface of the substrate presses the first rewiring layer, the other surface of the substrate presses the second rewiring layer, wherein the first rewiring layer manufactures an antenna pattern, the second rewiring layer manufactures a reflecting ground plane and a feeder pattern, ore the reflecting ground plane is formed by a substrate metal layer. By the packagingantenna, the parasitic parameter of the packaging antenna is reduced, and meanwhile, the performance of the antenna is improved.

Owner:TSINGHUA UNIV

Multi-chip common power supply/grounding structure for printed circuit board

InactiveCN101437368AImprove high frequency performanceShort connectionMagnetic/electric field screeningElectrical connection printed elementsNoise suppressionPrinted circuit board

The invention discloses a multi-chip sharing power supply or ground structure used in a printed circuit board, which belongs to the technical field of circuit board noise suppression. The power supply or ground structure is a typical capacitor structure of which certain three layers are in metal-medium-metal structure and constructed in the multi-layer printed circuit board, wherein the used medium is a high dielectric constant medium; large area of power supply or ground metal plane is divided into areas with the same number according to the required power supplied chip number respectively, and each area is positioned under the chip supplied with power. Through embedding technology, namely the whole power supply / ground structure is a part of the circuit board, the structure has short wiring and small parasitic parameter, can work at high frequency, and greatly widens the high frequency property of a wave filter.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

High-thermal-reliability multi-unit power integration module and processing technology thereof

ActiveCN113130455AImprove cooling efficiencyReduce lossSemiconductor/solid-state device detailsSolid-state devicesEpoxySchottky barrier

The invention relates to a structure of a high-thermal-reliability multi-unit power integration module (PIM) and a processing technology thereof. The structure comprises a silicon-based IGBT chip, a silicon carbide Schottky barrier diode chip, a silicon-based diode chip, a copper / graphene nanosheet (Cu / GN) heterogeneous thin film, graphene-based packaging resin, a copper-clad ceramic lining plate, a solder layer, a nano-silver conductive adhesive, a bonding wire, a copper gasket, a plastic packaging shell, an aluminum silicon carbide substrate, heat-conducting silicone grease and a radiator. The Cu / GN heterogeneous thin film is adopted to replace a local bonding wire, local heat of a chopper circuit IGBT chip in a high-power PIM is dissipated through an upper heat conduction path and a lower heat conduction path, and the local hot spot temperature on the chip is reduced; and meanwhile, the graphene is uniformly added into the epoxy resin to serve as a potting material so that the overall thermal resistance of the high-power PIM from a chip to the environment is reduced, and the heat dissipation efficiency is improved.

Owner:HUANGSHAN UNIV

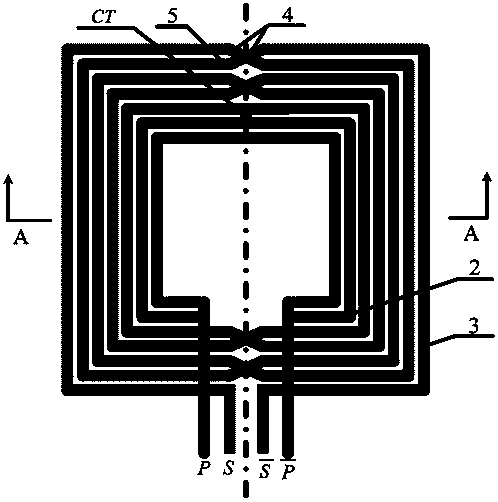

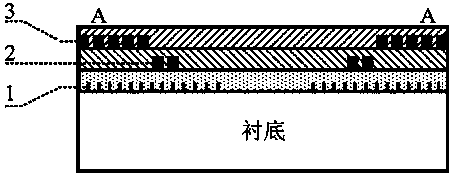

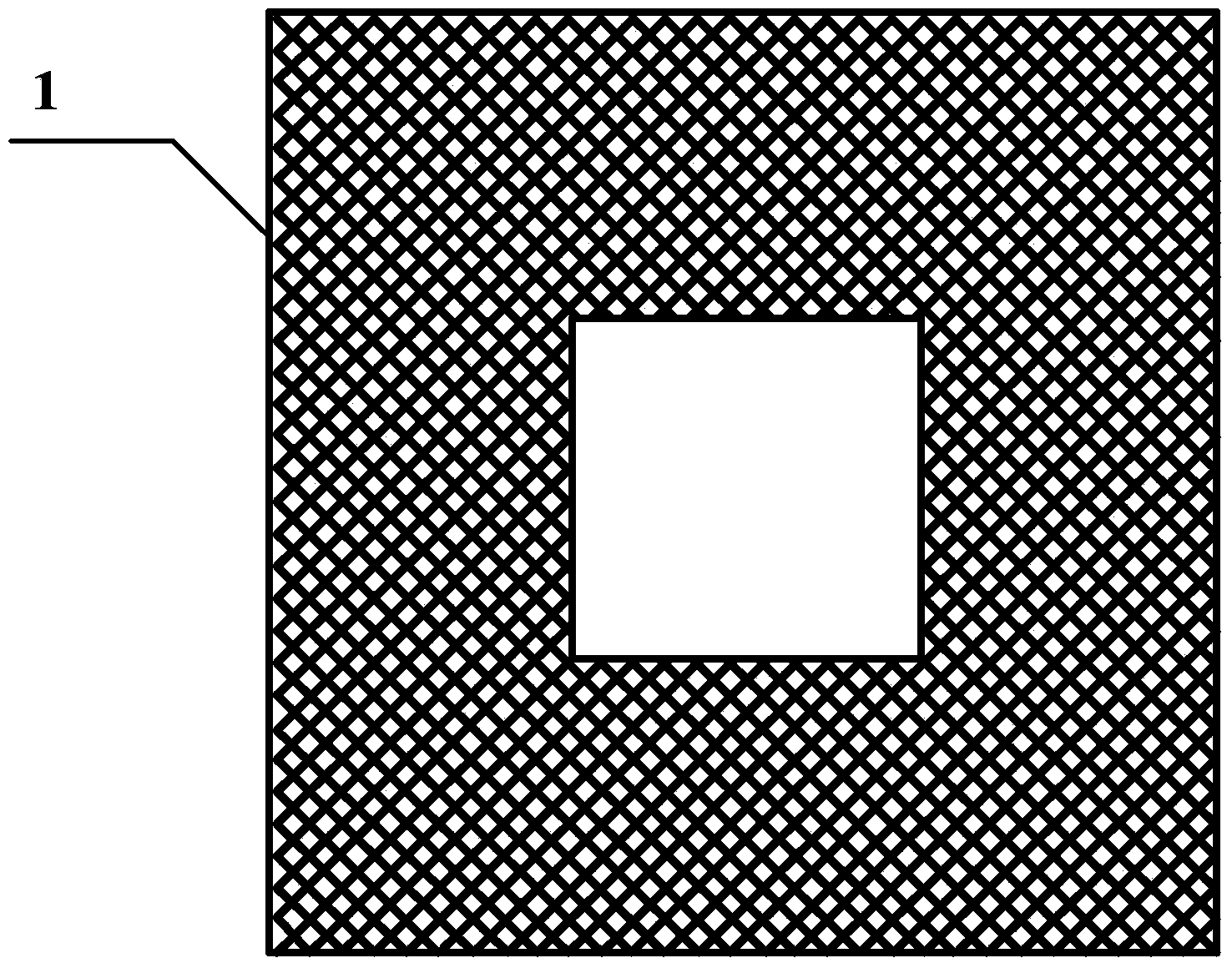

Symmetric integrated stacked transformer

InactiveCN104037158AIncrease the turns ratioHigh Magnetic InductanceSemiconductor/solid-state device detailsSolid-state devicesHigh rateCenter tap

The invention discloses a symmetric integrated stacked transformer. The symmetric integrated stacked transformer comprises a substrate, a first layer of medium, a second layer of medium and a third layer of medium, which are arranged on the substrate from bottom to top in sequence, a latticed shield grid, which is positioned in the first layer of medium, a primary coil, which is positioned in the second layer of medium, and a secondary coil, which is positioned in the third layer of medium, wherein the shield grid is arranged on the lower plane of the first layer of medium; the primary coil is formed by parallel connection of two circles of square micro-strip coils, which are separated with each other and are symmetrical around the axis, and is arranged on the lower plane of the second layer of medium; the secondary coil is formed by series connection of fives circles of square micro-strip coils, which are separated with each other and are symmetrical around the axis, and is arranged on the lower plane of the third layer of medium; the adjacent coils in pairs are crossly connected with each other at the places close to the axis through two connecting lines, one remaining circle of the coil is directly connected at the place close to the axis through the connecting line of the same metal layer, and a center tap of the secondary coil is arranged on the middle point of the coil. The symmetric integrated stacked transformer has the characteristics of good symmetry, high rate of turn and high magnetic induction coefficient.

Owner:JIANGSU UNIV OF SCI & TECH

Packaging piece based on substrate and adopting slotting technology and manufacturing process of packaging piece

InactiveCN103325757AImprove cooling effectExcellent electric heating performanceSemiconductor/solid-state device detailsSolid-state devicesPlastic packagingAdhesive

The invention discloses a packaging piece based on a substrate and adopting a slotting technology and a manufacturing process of the packaging piece. The packaging piece is mainly composed of a lead frame, a PAD, a solder ball, conducting adhesive, a chip, a bonding wire and a plastic package body. The PAD and the solder ball are arranged on the lead frame, and a notch is formed in the lead frame. The chip is connected into the notch of the lead frame through the conducting adhesive, and welding spots on the chip are connected with the PAD on the lead frame through the bonding wire. The chip, the bonding wire, the solder ball and the lead frame form a power and signal channel of a circuit. The plastic package body wraps the lead frame, the PAD, the solder ball, the chip and the bonding wire. The procedures of the manufacturing process are wafer thinning, scribing, substrate slotting and ball replacing, chip installing, installed chip baking, bonding, plasma cleaning, post curing, plastic packaging and product finishing. According to the packaging piece based on the substrate and adopting the slotting technology and the manufacturing process of the packaging piece, electric heating performance of the chip is improved, and the performance of the whole packaging piece is improved greatly.

Owner:HUATIAN TECH XIAN

Method for manufacturing multi-slot PN junction capacitor with multi-electrode ultra-low inductance

ActiveCN102117768ASimple structureIncrease capacitance densitySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceElectronic systems

The invention discloses a method for manufacturing a multi-slot PN junction capacitor with multi-electrode ultra-low inductance. Through a series of theoretical argumentation and assumption, the original semiconductor PN junction capacitor is improved, so that the improved capacitor has the characteristics of simple structure, large capacitance density, small parasitic parameter, simple manufacturing process and the like, and particularly can realize great reduction of series inductance to ensure that the capacitor works in a higher frequency range. The capacitor can be widely applied to decoupling, filtering, matching, preventing static and surge and the like in the high-frequency high-speed power electronic system.

Owner:NAT CENT FOR ADVANCED PACKAGING

Circuit simulation method and device, electronic equipment and computer readable storage medium

ActiveCN112560368AImprove Simulation EfficiencyReduce resource consumptionCAD circuit designSpecial data processing applicationsSoftware engineeringNetlist

The invention provides a circuit simulation method and device, electronic equipment and a computer readable storage medium, and the method comprises the steps: obtaining estimated power supply voltagedata determined according to a target simulation circuit comprising a power supply simulation circuit and a function simulation circuit; and performing simulation according to the estimated power supply voltage data and the function simulation circuit to obtain a parasitic parameter netlist of the target simulation circuit. Through the method in the embodiment of the invention, the circuit simulation efficiency can be improved.

Owner:HYGON INFORMATION TECH CO LTD